# PLUG and DISPLAY STANDARD

# **Video Electronics Standards Association**

920 Hillview Ct., Suite 140 Milpitas, CA 95035 Phone : (408) 957-9270 Fax : (408) 957-9277

# VESA PLUG and DISPLAY (P&D<sup>TM</sup>) STANDARD

# Version 1

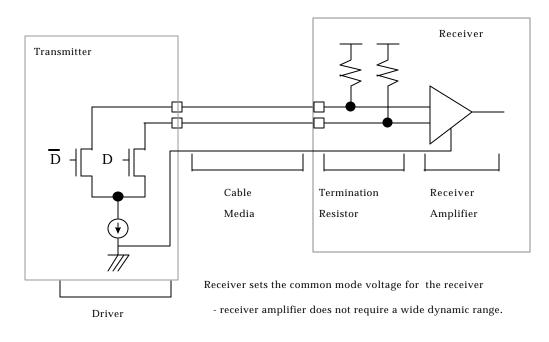

# Date : June 11<sup>th</sup>, 1997

# Purpose

This standard is intended to provide an industry standard digital interface for display devices.

# Summary

This standard defines a new video interface which provides both digital and analogue interfaces for video data, together with serial bus options.

# VESA - The Video Electronics Standards Association Plug and Display Standard

# **Intellectual Property**

©Copyright 1997 - Video Electronics Standards Association. All rights reserved.

While every precaution has been taken in the preparation of this standard, the Video Electronics Standards Association and its contributors assume no responsibility for errors or omissions, and make no warranties, expressed or implied, of functionality or suitability for any purpose.

# Trademarks

All trademarks used within this document are the property of their respective owners.

- VESA, DDC, EVC, EDID and P&D are trademarks of the Video Electronics Standards Association.

- PanelLink and TMDS are trademarks of Silicon Image Inc.

- MicroCross is a trademark of Molex Inc.

- $I^2C$  is a trademark of Philips

# **Patents**

VESA proposal and standards documents are adopted by the Video Electronics Standards Association without regard to whether their adoption may involve patents on articles, materials, or processes. Such adoption does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the proposal or standards document.

# Support for this Standard

Clarifications and application notes to support this standard may be written. To obtain the latest standard and any support documentation, contact VESA.

If you have a product which incorporates P&D, you should ask the company that manufactured your product for assistance. If you are a manufacturer, VESA can assist you with any clarification you may require. All comments or error reports should be submitted in writing to VESA using one of following methods:

- Fax +1 408 957 9277, direct this note to Technical support at VESA

- e-mail support@vesa.org

- Mail to Technical Support Video Electronics Standards Association, 920 Hillview Ct., Suite 140, Milpitas, CA 95035

# Acknowledgments

The many active participants on the VESA Plug and Display Committee all contributed to this standard through their experience and enthusiasm either in the initial stage or by participation in the committee meetings. Thanks to the following individuals and companies in particular:

| Name               | Company                    |  |

|--------------------|----------------------------|--|

| M Blashe           | Toshiba America Electronic |  |

|                    | Components, Inc.           |  |

| B Burge            | Chips and Technologies     |  |

| D Chambers         | JAE                        |  |

| M Gardner          | Molex                      |  |

| C Grant            | Madison Cable              |  |

| R Heidick          | 3M                         |  |

| H Hernandez        | 3M                         |  |

| G Hewlett          | Texas Instruments          |  |

| J Hosek            | NEC Technologies           |  |

| S Kerigan          | IBM UK                     |  |

| L Kopp             | AMP                        |  |

| K Kwiat            | Hirose Electric            |  |

| G Manchester       | Molex                      |  |

| M Marantic         | Hitachi                    |  |

| I Miller           | IBM UK                     |  |

| J Miseli           | Sun Microsystems           |  |

| B Myers            | Hewlett Packard            |  |

| E Myers            | AMP                        |  |

| J Roberts          | NIST                       |  |

| E Rodriguez-Crespo | Mitsubishi                 |  |

| B Russell          | Canon                      |  |

| J Scheussler       | National Semiconductor     |  |

| S Slinker          | Silicon Image              |  |

| O Tomita           | Toshiba America Electronic |  |

|                    | Components, Inc.           |  |

| W Uenishi          | Hosiden                    |  |

| H van der Ven      | Panasonic                  |  |

| N Vidovich         | Hitachi                    |  |

| R Visser           | Philips MM Centre          |  |

# **Terms and Abbreviations**

| Term / Abbreviation                      | Description                                                                         |

|------------------------------------------|-------------------------------------------------------------------------------------|

| ASIC                                     | Application Specific Integrated Circuit                                             |

| CRT                                      | Cathode Ray Tube                                                                    |

| DDC                                      | (VESA) Display Data Channel                                                         |

| DDC1                                     | The simplest mode defined in the VESA DDC standard                                  |

| DDC2                                     | The general term used to refer to any of the DDC2 modes (DDC2B, DDC2B+              |

|                                          | and DDC2AB) defined in the VESA DDC standard                                        |

| DDC2B                                    | Simplest of the DDC2 modes defined in VESA DDC standard                             |

| DDC2B+                                   | Adds bi-directional communications to DDC2B                                         |

| DDC2AB                                   | An ACCESS.bus mode defined in VESA DDC standard                                     |

| DPMS                                     | (VESA) Display Power Management Standard                                            |

| DSTN-LCD                                 | Dual Scan Super Twisted Nematic LCD                                                 |

| EDID                                     | (VESA) Extended Display Identification Data                                         |

| EMI                                      | Electromagnetic Interference                                                        |

| EVC                                      | (VESA) Enhanced Video Connector                                                     |

| TFT-LCD                                  | Thin Film Transistor LCD                                                            |

| FPD                                      | Flat Panel Display                                                                  |

| FPDI                                     | (VESA) Flat Panel display Interface                                                 |

| HDTV                                     | High Definition Television                                                          |

| IEEE 1394                                | Standard for High Performance Serial Bus                                            |

| IC                                       | Integrated Circuit                                                                  |

| $I^2 C^{TM}$                             | Trademark of Philips used to refer to the Inter IC or I <sup>2</sup> C - Bus        |

| LCD                                      | Liquid Crystal Display                                                              |

| LVDS                                     | Low Voltage Differential Signaling <sup>1</sup>                                     |

| Logical Layer                            | Used to indicate a section of code                                                  |

| MCS                                      | (VESA) Monitor Command Set                                                          |

| Microcross <sup>TM</sup>                 | Trademark of Molex Inc. for the quasi-coaxial section of the P&D connector          |

|                                          | system.                                                                             |

| P&D≬<br>Danall inla™ Taalanalana         | Trademark of VESA for the Plug and Display standard                                 |

| PanelLink <sup>™</sup> Technology<br>PLL | Trademark of Silicon Image for their LVDS technology                                |

|                                          | Phase Lock Loop                                                                     |

| Physical Layer                           | Used to indicate a physical layer, either electrical or mechanical                  |

| RFI<br>RGB2S                             | Radio Frequency Interference                                                        |

|                                          | Red, Green & Blue Video, Hz. and Vt. Syncs.<br>TMDS Receiver number 'n'             |

| Rxn<br>TMDS <sup>TM 2</sup>              |                                                                                     |

| TMDS <sup>TM</sup><br>TTL                | Trademark of Silicon Image used to refer to their PanelLink Technology <sup>2</sup> |

|                                          | Transistor, Transistor Logic<br>TMDS Transmitter number 'n'                         |

| Txn                                      | Universal Serial Bus                                                                |

| USB<br>VESA                              |                                                                                     |

| VESA                                     | Video Electronics Standards Association                                             |

<sup>1</sup> The term LVDS is used in this document as a generic term and does not imply any particular LVDS technology. <sup>2</sup> The term TMDS will generally be used in this document to denote PanelLink<sup>™</sup> or compatible technologies.

# **Referenced Standards and Documents**

Several Standards (listed in following table) are referenced by the P&D standard and compliance with the VESA P&D standard requires compliance with these standards.

| Standard Name                                                                                                                    | Version /<br>Reference | Date     |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|

| ANSI/EIA-3641994, Electrical Connector /Socket Test Procedures Including                                                         | С                      | Nov. '94 |

| Environmental Classifications                                                                                                    |                        |          |

| ACCESS.bus Specification                                                                                                         | 3.0                    | Sep. '95 |

| ASME Y14.5M-1994                                                                                                                 |                        | Jan. '95 |

| EIA-170, Electrical Performance Standards - Monochrome Television Studio Facilities - (formerly RS-170)                          |                        | Nov. '57 |

| EIA-343-A, Electrical Performance Standard for High Resolution Monochrome Closed<br>Circuit Television Camera                    |                        | Sep. '69 |

| IEC 801-1, Electromagnetic compatibility for industrial-process measurement and control equipment. Part 1 - General introduction | 1984-11                |          |

| IEEE-1394-1995                                                                                                                   | 1994                   | Dec. '95 |

| Universal Serial Bus Specification                                                                                               | 1.0                    | Jan. '96 |

| Universal Serial Bus Monitor Control Class Definition                                                                            | 0.9g                   | Nov. '96 |

| VESA Display Data Channel Standard                                                                                               | 2.01                   | Apr. '96 |

| VESA Display Power Management Signaling Standard                                                                                 | 1.0                    | Aug. '93 |

| VESA Enhanced Video Connector Physical Connector Standard                                                                        | 1.0                    | Feb. '96 |

| VESA Enhanced Video Connector Standard                                                                                           | 1.0                    | Nov. '95 |

| VESA Enhanced Video Connector Standard : Proposed Revision                                                                       | 1.2p                   | Mar. '97 |

| VESA Extended Display Identification Data Standard                                                                               | 2.0                    | Apr. '96 |

| VESA Flat Panel Display Interface 2 Standard Proposal                                                                            | 0.8                    | Jan. '97 |

| VESA Monitor Command Set Proposal                                                                                                | 0.2p                   | Feb. '97 |

| VESA Plug and Display Architecture Document <sup>1</sup>                                                                         | 0.1p                   | Aug. '96 |

<sup>1</sup> Access to the VESA Plug and Display Architecture Document is restricted to VESA member companies.

# <u>Index</u>

| 1. Introduction                                                              | 13 |

|------------------------------------------------------------------------------|----|

| 1.1 P&D Overview                                                             | 13 |

| 1.2 P&D Interface                                                            |    |

| 1.2.1 Interface Elements                                                     | 14 |

| 1.2.2 Digital Interface: Capabilities                                        |    |

| 1.2.3 Analogue Interface: Capabilities                                       | 14 |

| 1.3 Compatibility with Other VESA Standards                                  | 14 |

| 1.3.1 Compatibility with VESA DDC Standard (see Section 2.1)                 |    |

| 1.3.2 Compatibility with VESA EDID Standard (see Section 2.1)                | 15 |

| 1.3.3 Compatibility with VESA EVC Standard                                   |    |

| 1.3.4 Compatibility with VESA DPMS Standard                                  |    |

| 1.3.5 Compatibility with VESA FPDI-2 Standard                                | 16 |

| 1.4 Compatibility with Monitors Using Other Connectors                       | 17 |

| 1.4.1 Compatibility with Monitors Using 15-pin D-sub Connector               |    |

| 1.4.2 Compatibility with Monitors Using 13W3 Connector                       |    |

| 1.4.3 Compatibility with Monitors Using BNC Connectors                       | 17 |

| 1.5 Incompatible Display and System Interfaces                               | 17 |

| 2. Plug and Display Architectural Overview                                   | 18 |

| 2.1 Plug and Display System Overview                                         |    |

| 22 D&D A mohitantum                                                          | 18 |

| 2.2 P&D Architecture                                                         |    |

| 2.2.1 Logical Layer Concepts         2.2.2 Physical Layer Concepts           |    |

| 2.2.3 Explanation of Remaining Elements of P&D Architecture Overview Drawing |    |

| 2.3 P&D-A/D Connector Overview                                               | 21 |

| 3. Detection of Display Disconnect                                           | 22 |

| 3.1 Detection Mechanism - Host                                               | 22 |

| 3.2 Detection Mechanism - Display                                            | 22 |

| 3.3 Power Up/Down and Hot Plugging : Flowchart                               | 23 |

| 4. Electrical Layer Specification: Part 1                                    | 24 |

| 4.1 Introduction                                                             | 24 |

| 4.2 DDC2 Sublayer, Type A                                                    | 24 |

| 4.2.1 List of Signals                                                        |    |

| 4.2.2 Signal Specification and Timing                                        | 24 |

| 4.2.3 Extended Display identification Data (EDID)                            |    |

| 4.3 IEEE 1394-1995 Sublayer, Type D1                                         | 24 |

| 4.4 USB Sublayer, Type D2                                                    | 24 |

| 4.5 Analogue Sublayer, Type E1                                               | 25 |

| 4.5.1 Analogue Interface                                                     | 25 |

| 4.5.2 Analogue Video Signals                                                 | 26 |

| 4.5.3 Synchronisation Signals - VESA Video Signal Standard                   |    |

| 4.5.4 Pixel Clock                                                            | 27 |

| 4.6 Charging Power                                                            | 29 |

|-------------------------------------------------------------------------------|----|

| 4.6.1 Hot Plugging                                                            | 29 |

| 4.7 Stereo Syncronisation                                                     | 30 |

| 5. Electrical Layer Specification: Digital (TMDS) Video Transmission Overview | 31 |

| 5.1 Transition Minimised Differential Signaling Interface Overview            | 31 |

| 5.1.1 Introduction                                                            | 31 |

| 5.1.2 Logical Architecture                                                    |    |

| 5.1.3 Summary                                                                 |    |

| 5.1.5 TMDS Receiver Summary                                                   |    |

| 5.1.6 Relationship Between Controller's Output Data and Input Data Clock      |    |

| 5.2 TMDS Transition-Controlled Digital Encoding and Signal Transmission       | 40 |

| 5.3 System Debug on Differential Data Pairs                                   | 43 |

| 5.4 Implementation                                                            | 44 |

| 5.4.1 Amplitude Modulated Signal mapping (e.g. TFT)                           | 44 |

| 5.4.2 Temporal Modulated Signal Mapping (e.g. DSTN) - 16bpp                   |    |

| 5.4.3 Temporal-Modulated Signal Mapping (e.g. DSTN) - 24bpp                   | 46 |

| 5.5 Physical Layer                                                            |    |

| 5.5.1 Signal Bandwidth Characteristics                                        | 47 |

| 6. Electrical Layer Specification: TMDS Transmission Specification            | 48 |

| 6.1 Electrical Characteristics                                                | 48 |

| 6.2 DC Electrical Specifications                                              | 49 |

| 6.2.1 Differential Transmitter DC Specifications                              | 49 |

| 6.2.2 Differential Receiver DC Specifications                                 | 49 |

| 6.3 Driver Output Levels                                                      | 51 |

| 6.4 Signal Integrity                                                          | 53 |

| 6.4.1 Jitter and Skew of Clock and Differential Data Pairs                    | 53 |

| 6.5 Eye Diagram Template                                                      | 54 |

| 6.6 AC Specifications                                                         | 56 |

| 6.6.1 Timing Diagrams                                                         | 57 |

| 6.7 Error Specification for Display Interface                                 | 60 |

| 6.8 Guidance for Display Controller Implementation                            | 60 |

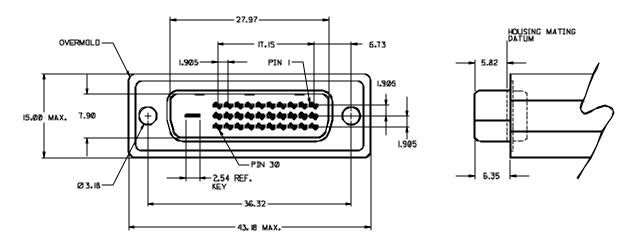

| 7. Mechanical Physical Layer: Connector                                       | 61 |

| 7.1 Introduction                                                              | 61 |

| 7.1.1 P&D-A/D Connector                                                       |    |

| 7.1.2 P&D-D Connector                                                         |    |

| 7.2 Receptacle Connector                                                      | 62 |

| 7.3 Positive Retention of Plug and Receptacle                                 | 65 |

| 7.4 Contact Finish On Plug And Receptacle Contacts                            | 65 |

| 7.5 Shell Finish On Plugs And Receptacles                                     | 65 |

| 7.6 Connector Durability                                                      | 66 |

| 7.7 Plug Connector                                                                                               | 66       |

|------------------------------------------------------------------------------------------------------------------|----------|

| 7.7.1 Plug Connector Termination                                                                                 | 66       |

| 7.8 Pinouts                                                                                                      | 67       |

| 7.8.1 Contact Sequencing                                                                                         | 67       |

| 7.8.2 P&D-A/D Signal Pin Assignments - Main Pin Field         7.8.3 Signal Pin Assignments - MicroCrossä Section |          |

| 7.8.4 P&D-D Signal Pin Assignments - Pin Field                                                                   |          |

| 7.9 Connector Performance Characteristics                                                                        | 69       |

| 7.9.1 Environmental                                                                                              | 69       |

| 7.9.2 Electrical         7.9.3 Mechanical                                                                        | 70<br>71 |

| 7.10 Connector Performance Test Criteria                                                                         |          |

| 7.10.1 Connector Performance Test Groups                                                                         | 73       |

| 8. Physical Layer: Cable Assembly Specifications                                                                 | 84       |

| 8.1 TMDS Video Sublayer, Type AT/AT'                                                                             | 84       |

| 8.2 Analogue Video Sublayer (Coax), Type A                                                                       | 85       |

| 8.3 Conductors for Vertical, Horizontal, Stereo Sync., Sync. Return and DDC, Type C $\_$                         | 85       |

| 8.4 Conductors for Charge Power and +5VDC, Type D                                                                | 85       |

| 8.5 USB Sublayer, Type USB                                                                                       | 85       |

| 8.6 IEEE 1394-1995 Sublayer, Type 1394                                                                           | 85       |

| 8.7 Cable Type Usage : P&D-A/D                                                                                   | 86       |

| 8.8 Cable Type Usage : P&D-D                                                                                     | 87       |

| 9. Compliance with Plug and Display Standard                                                                     | 88       |

| 9.1 A P&D-A/D Compliant Host System / Graphic Card / etc                                                         | 88       |

| 9.2 A P&D-D Compliant Host System / Graphic Card / etc                                                           | 88       |

| 9.3 A P&D Compliant Display                                                                                      | 88       |

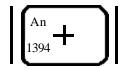

| 9.4 P&D Symbol                                                                                                   | 89       |

| 9.4.1 Upper Left Quadrant9.4.2 Upper Right Quadrant                                                              |          |

| 9.4.2 Opper Right Quadrant                                                                                       |          |

| 9.4.4 Lower Right Quadrant                                                                                       | 89       |

| 9.4.5 Example 9.4.6 Additional Information                                                                       |          |

| 10. Appendix A: Digital Monitor Cable Assembly                                                                   |          |

| 10.1 Introduction                                                                                                |          |

| 10.2 P&D-D û P&D-D Plug Connectors                                                                               |          |

| 10.2.1 WD-D I T WD-D T Hug Connectors           10.2.1 Pin Definitions                                           |          |

| 10.3 P&D-D û Microribbon Plug Connector                                                                          |          |

| 10.3.1 Assembly Drawing<br>10.3.2 Pin Definitions, P&D-D I Microribbon                                           | 93       |

| 11. Appendix B: Software Considerations at Start-Up                                                              |          |

|                                                                                                                  |          |

| 11.1 Power on Sequences                                             | 96  |

|---------------------------------------------------------------------|-----|

| 11.1.1 System Unit Powers on after Monitor Power On                 | 96  |

| 11.1.2 System Unit Powers on and Monitor Not Powered On             |     |

| 11.1.3 System Unit IPL after Monitor Power On                       | 98  |

| 12. Appendix C: Guidance on Implementation                          | 99  |

| 12.1 P&D Family of Connectors                                       | 99  |

| 12.2 Plug - Receptacle Physical Compatibility Summary               | 99  |

| 13. Appendix D: Power-Up and Hot-Plugging of P&D Hosts and Monitors | 100 |

| 13.1 Requirements of P&D Hosts                                      | 100 |

| 13.2 Requirements of P&D Monitors                                   | 100 |

| 13.3 Power-Up and Hot-Plugging Sequence of Events for P&D-A/D Host  | 101 |

| 13.3.1 P&D-D Monitor Attached to P&D-A/D Host                       | 101 |

| 13.3.2 EVC Monitor Attached to P&D-A/D Host                         |     |

| 13.3.3 Non-P&D Monitor Attached to P&D-A/D Host                     | 102 |

| 13.4 Power-Up and Hot-Plugging Sequence of Events for P&D-D Host    | 104 |

| 13.4.1 P&D-D Monitor Attached to P&D-D Host                         |     |

| 13.4.2 Monitor with Analogue Interface Attached to P&D-D Host       |     |

| 13.5 Power-Up and Hot-Plugging Sequence of Events for P&D-D Monitor | 106 |

| 14. Appendix E : Measurement Protocols                              | 108 |

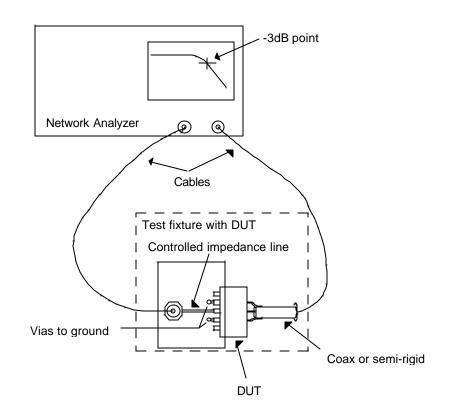

| 14.1 Bandwidth Measurements                                         | 108 |

| 14.1.1 Scope and objective                                          | 108 |

| 14.1.2 Test Equipment                                               | 108 |

| 14.1.3 Test Specimen                                                |     |

| 14.1.4 Test Fixture                                                 |     |

| 14.1.5 Test Method                                                  | 108 |

| 14.2 Shell-to-Shell and Shell-to-Bulkhead Resistance                | 110 |

| 14.2.1 Scope & Objectives                                           | 110 |

| 14.2.2 Measurement Equipment                                        |     |

| 14.2.3 Test Specimen                                                |     |

| 14.2.4 Test Procedure                                               |     |

| 14.2.5 Shell to Shell Resistance                                    |     |

| 14.2.6 Receptacle to Bulkhead Resistance                            |     |

| 14.2.7 Details to be Specified                                      |     |

| 14.2.8 Test Documentation                                           | 111 |

# Index of Tables

| Index of Tables                                                                       |    |

|---------------------------------------------------------------------------------------|----|

| TABLE 1-1 : P&D INTERFACE FEATURES                                                    | 14 |

| TABLE 1-2 : P&D DIGITAL INTERFACE CAPABILITIES                                        | 14 |

| TABLE 1-3 : EVC VIDEO CAPABILITY                                                      | 16 |

| TABLE 4-1 : ELECTRIC SUBLAYERS                                                        | 24 |

| TABLE 4-2 : DDC2 SUBLAYER SIGNALS                                                     | 24 |

| TABLE 5-1 : THEORETICAL LOW VOLTAGE SINGLE ENDED DIFFERENTIAL SWING LEVEL RELATIVE TO |    |

| R <sub>EXT_SWING</sub>                                                                | 32 |

| TABLE 5-2 : ADDRESSABILITY TABLE                                                      | 34 |

| TABLE 5-3 : ENCODER MAPPING FOR A SINGLE DIFFERENTIAL DATA PAIR                       | 36 |

| TABLE 5-4 : SIGNAL NAME DESCRIPTIONS                                                  | 39 |

| TABLE 5-5 : ENCODED DATA COMPONENTS FOR TX0 DIFFERENTIAL DATA PAIR                    | 40 |

| TABLE 5-6 : ENCODED DATA COMPONENTS FOR TX1 DIFFERENTIAL DATA PAIR                    | 41 |

| TABLE 5-7 : ENCODED DATA COMPONENTS FOR TX2 DIFFERENTIAL DATA PAIR                    | 41 |

| TABLE 5-8 : SYSTEM DEBUG PATTERNS                                                     | 43 |

| TABLE 5-9 : AMPLITUDE MODULATED COLOUR MAPPING                                        | 44 |

| TABLE 5-10 : TEMPORAL MODULATION COLOUR MAPPING - 16BPP                               | 45 |

| TABLE 5-11 : TEMPORAL MAPPING, PIXEL LOCATION ON DISPLAY                              | 45 |

| TABLE 5-12 : TEMPORAL MODULATION COLOUR MAPPING - 24BPP                               | 46 |

| TABLE 5-13 : DISTRIBUTED TRANSMISSION PATH BANDWIDTH AND RISE-TIME                    | 47 |

| TABLE 6-1 : TRANSMITTER DC SPECIFICATIONS FOR 25 - 65MHZ                              | 49 |

| TABLE 6-2 : RECEIVER DC SPECIFICATIONS FOR 25 - 65MHZ                                 | 49 |

| TABLE 6-3 : DC SPECIFICATIONS                                                         | 49 |

| TABLE 6-4 : COMPONENT VALUES, CAPACITOR COUPLING                                      | 52 |

| TABLE 6-5 : SIGNAL INTEGRITY PARAMETERS                                               | 53 |

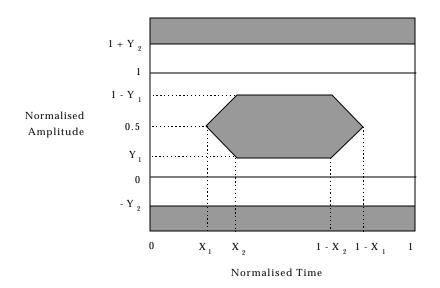

| TABLE 6-6 : EYE DIAGRAM MASK AT POINT S                                               | 54 |

| TABLE 6-7: EYE DIAGRAM MASK AT POINT R <sup>1</sup>                                   | 55 |

| TABLE 6-8 : AC SPECIFICATION (PART 1)                                                 | 56 |

| TABLE 6-9 : AC SPECIFICATION (PART 2)                                                 | 57 |

| TABLE 7-1 : P&D-A/D AND P&D-D SIGNALS                                                 | 67 |

| TABLE 7-2 : CONTACT SEQUENCING                                                        | 67 |

| TABLE 7-3 : P&D-A/D SIGNAL ASSIGNMENT - MAIN PIN FIELD                                | 68 |

| TABLE 7-4 : SIGNAL ASSIGNMENT - MICROCROSS <sup>a</sup> SECTION                       | 68 |

| TABLE 7-5 : SIGNAL ASSIGNMENT - MAIN PIN FIELD                                        | 69 |

| TABLE 7-6 : PERFORMANCE GROUP A                                                       | 73 |

| TABLE 7-7 : PERFORMANCE GROUP B                                                       | 74 |

| TABLE 7-8 : PERFORMANCE GROUP C                                                       | 75 |

| TABLE 7-9 : PERFORMANCE GROUP D                                                       | 77 |

| TABLE 7-10 : PERFORMANCE GROUP E                                                      | 78 |

| TABLE 7-11 : PERFORMANCE GROUP F                                                      | 79 |

| TABLE 7-12 : PERFORMANCE GROUP FP - GENERAL PURPOSE, SINGLE ENDED                     | 80 |

| TABLE 7-13 : PERFORMANCE GROUP FP - GENERAL PURPOSE, DIFFERENTIAL                     | 81 |

| TABLE 7-14 : PERFORMANCE GROUP FP - QUASI-COAXIAL LINES                               | 82 |

| TABLE 7-15 : PERFORMANCE GROUP G                                                      | 83 |

| TABLE 8-1 : PHYSICAL SUBLAYER DESIGNATIONS                                            | 84 |

| TABLE 8-2 : TMDS VIDEO SUBLAYER ATTRIBUTES (PART 1)                                   | 84 |

| TABLE 8-3 : TMDS VIDEO SUBLAYER ATTRIBUTES (PART 2)                                   | 84 |

| TABLE 8-4 : ANALOGUE VIDEO SUBLAYER ATTRIBUTES # 1                                    | 85 |

| TABLE 8-5 : ANALOGUE VIDEO SUBLAYER ATTRIBUTES # 2                                    | 85 |

| TABLE 8-6 : CABLE TYPE USAGE - P&D-A/D                                                | 86 |

| TABLE 8-7 : CABLE TYPE USAGE - P&D-D                                                  | 87 |

|                                                                                       |    |

# Index of Figures

| FIGURE 2-1 : P&D-A/D CONNECTOR OVERVIEW                                                                         | 21       |

|-----------------------------------------------------------------------------------------------------------------|----------|

| FIGURE 3-1 : POWER UP/DOWN AND HOT PLUGGING FLOWCHART                                                           | 23       |

| TABLE 4-1 : ANALOGUE SUBLAYER SIGNALS                                                                           | 25       |

| TABLE 4-2 : VIDEO SIGNAL AMPLITUDE AND POLARITY                                                                 | 26       |

| TABLE 4-2 : VIDEO SIGNAL ANI EN ODE AND FOLANT T<br>TABLE 4-3 : SYNCHRONISATION SIGNAL SPECIFICATION            | 20<br>27 |

|                                                                                                                 |          |

| FIGURE 4-4 : STEREO SYNC.                                                                                       | 28       |

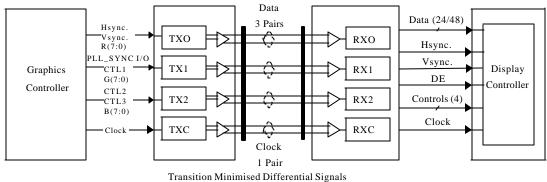

| FIGURE 5-1 : SIMPLIFIED BLOCK DIAGRAM OF A TMDS INTERFACE WITH CLOCK + RGB                                      | 31       |

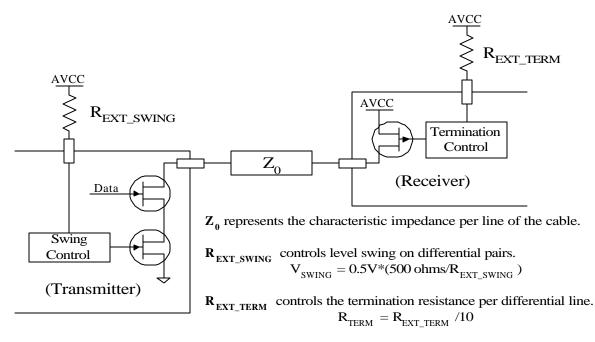

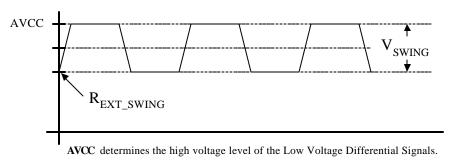

| FIGURE 5-2 : TRANSITION MINIMISED DIFFERENTIAL VOLTAGE SWING ADJUST                                             | 33       |

| FIGURE 5-3 : SINGLE ENDED TRANSITION MINIMISED DIFFERENTIAL SIGNAL ADJUSTMENT                                   | 33       |

| FIGURE 5-4 : SYSTEM ENVIRONMENT BLOCK DIAGRAM EXAMPLE                                                           | 34       |

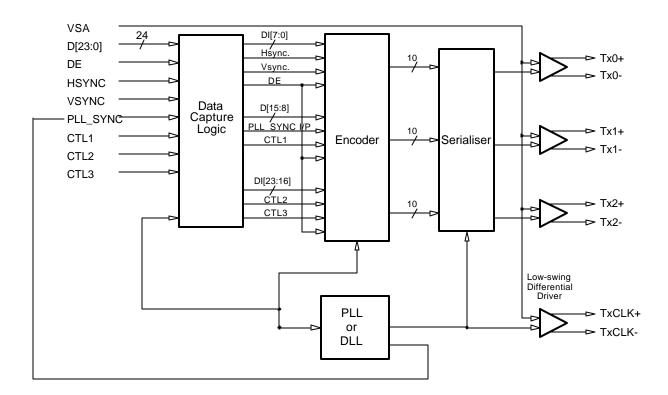

| FIGURE 5-5 : TMDS TRANSMITTER IC FUNCTIONAL BLOCK DIAGRAM                                                       | 35       |

| FIGURE 5-6 : TYPICAL CMOS CIRCUITS FOR TMDS DRIVER                                                              | 36       |

| FIGURE 5-7 : HORIZONTAL INPUT TIMING AT TYPE B INTERFACE                                                        | 38       |

| FIGURE 5-8 : VERTICAL INPUT TIMING AT TYPE B INTERFACE                                                          | 38       |

|                                                                                                                 |          |

| FIGURE 5-9 : INPUT DATA TIMING WITH RESPECT TO IDCK AT TYPE B INTERFACE                                         | 38       |

| FIGURE 5-10 : CONTROL SIGNAL TIMING WITH RESPECT TO IDCK AT TYPE B INTERFACE                                    | 38       |

| FIGURE 5-11 : CONTROL SIGNALS WITH RESPECT TO DE TIMING                                                         | 39       |

| FIGURE 5-12 : TMDS INTERFACE TRANSITION MINIMISATION TIMING DIAGRAM                                             | 40       |

| FIGURE 5-13 : ENCODED TIMING DIAGRAM FOR ALL DIFFERENTIAL DATA PAIRS                                            | 41       |

| FIGURE 5-14 : HSYNC., VSYNC., AND CTL[3:1] SAMPLING RELATIVE TO CLOCK EDGE                                      | 42       |

| FIGURE 6-1 : DIFFERENTIAL MODE IMPEDANCE                                                                        | 48       |

| FIGURE 6-2 : SIGNAL LEVELS ON TRANSMISSION MEDIA                                                                | 48       |

| FIGURE 6-3 : TEST CIRCUIT FOR MEASURING $I_{OH}$ AND $I_{OL}$                                                   | 50       |

|                                                                                                                 |          |

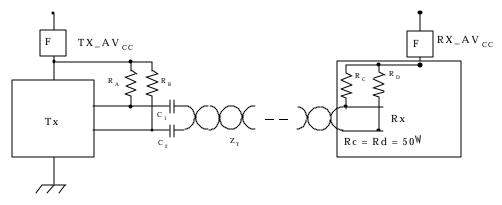

| FIGURE 6-4 : DRIVER AND RECEIVER CIRCUIT MODEL FOR ONE DIFFERENTIAL DATA PAIR                                   | 51       |

| FIGURE 6-5 : CAPACITOR COUPLED TMDS SYSTEM                                                                      | 52       |

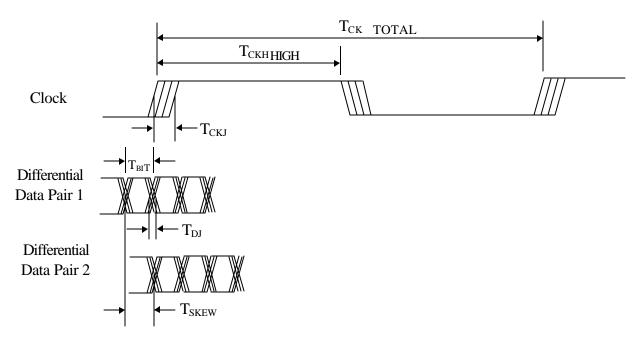

| FIGURE 6-6: TIMING DIAGRAM FOR JITTER AND SKEW SPECIFICATION                                                    | 53       |

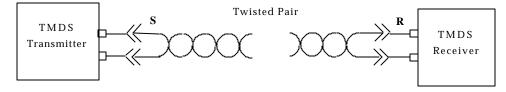

| FIGURE 6-7: TMDS CONNECTION                                                                                     | 54       |

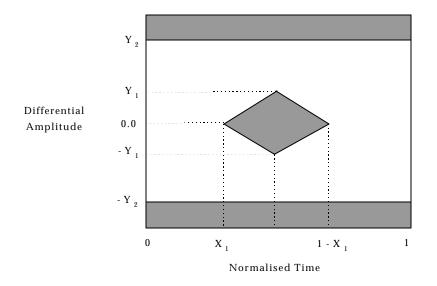

| FIGURE 6-8: EYE DIAGRAM MASK AT POINT S                                                                         | 54       |

| FIGURE 6-9: EYE DIAGRAM MASK AT POINT R                                                                         | 55       |

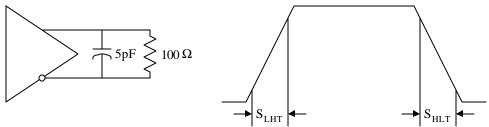

| FIGURE 6-10 : TRANSMITTER SMALL SIGNAL TRANSITION TIMES                                                         | 57       |

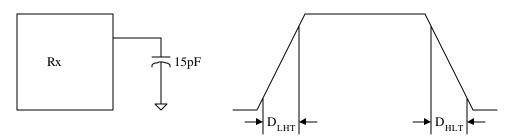

| FIGURE 6-11 : RECEIVER DIGITAL OUTPUT TRANSITION TIMES                                                          | 57       |

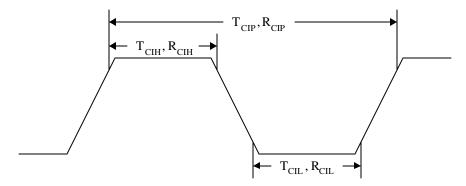

| FIGURE 6-12 : TRANSMITTER / RECEIVER CLOCK CYCLE HIGH / LOW TIMES                                               | 58       |

| FIGURE 6-13 : DIFFERENTIAL DATA PAIR TO DIFFERENTIAL DATA PAIR SKEW TIMING                                      | 58       |

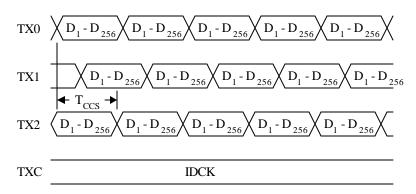

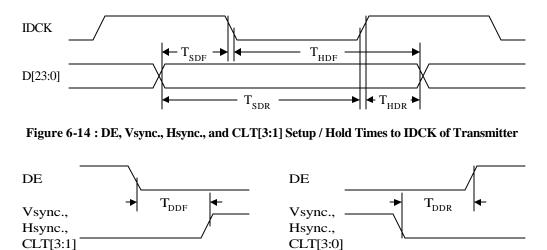

| FIGURE 6-14 : DE, VSYNC., HSYNC., AND CLT[3:1] SETUP / HOLD TIMES TO IDCK OF TRANSMITTER                        | 58       |

| FIGURE 6-15 : VSYNC., HSYNC., AND CLT[3:1] DELAY TIMES FROM DE OF TRANSMITTER                                   | 58       |

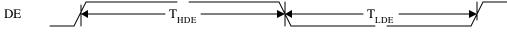

| FIGURE 6-16 : DE HIGH / LOW TIMES OF TRANSMITTER                                                                | 58       |

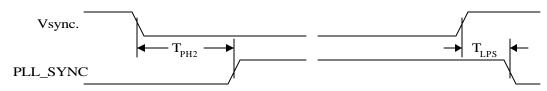

| FIGURE 6-17 : PLL_SYNC TIMING OF TRANSMITTER WITH SYNC_CONT = 1                                                 | 59       |

|                                                                                                                 |          |

| FIGURE 6-18 : PLL_SYNC TIMING OF TRANSMITTER WITH SYNC_CONT = 0                                                 | 59       |

| FIGURE 6-19 : OUTPUT SIGNALS DISABLED / ENABLED TIMING FROM PD ACTIVE / INACTIVE FROM                           |          |

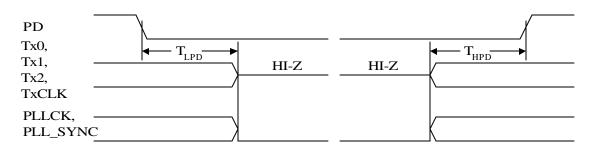

| TRANSMITTER                                                                                                     | 59       |

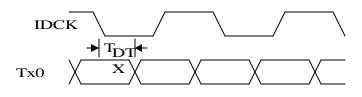

| FIGURE 6-20 : DIFFERENTIAL CLOCK DELAY FROM IDCK                                                                | 59       |

| FIGURE 6-21 : LINE ERROR RATE                                                                                   | 60       |

| FIGURE 6-22 : FULL FRAME ERROR RATE                                                                             | 60       |

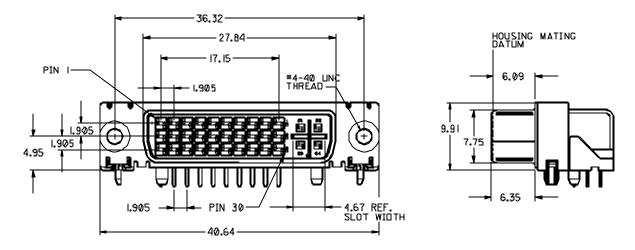

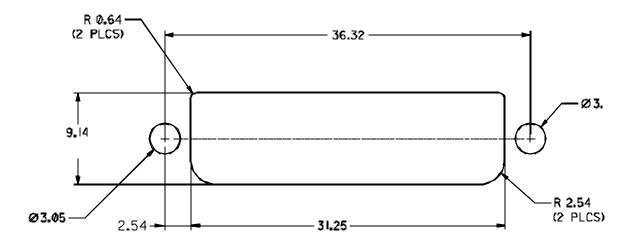

| FIGURE 7-1 : P&D-A/D RECEPTACLE CONNECTOR - BASIC MATING INTERFACE DIMENSIONS                                   | 62       |

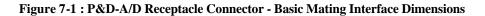

| FIGURE 7-2 : P&D-D RECEPTACLE CONNECTOR - BASIC MATING INTERFACE DIMENSIONS                                     | 62       |

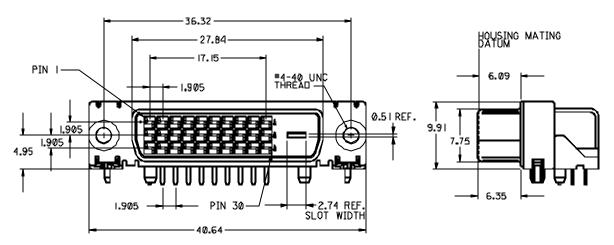

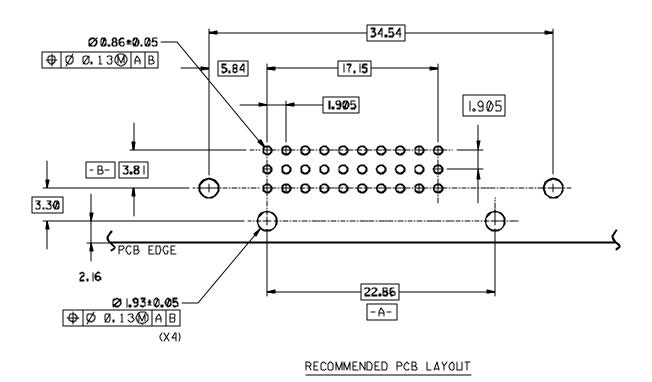

| FIGURE 7-3 : P&D-A/D REFERENCE HOLE PATTERN (RECEPTACLE)                                                        | 63       |

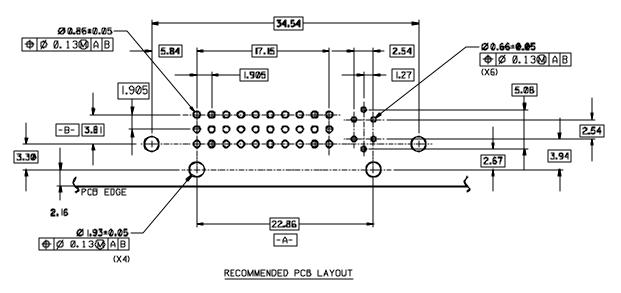

| FIGURE 7-4 : P&D-D REFERENCE HOLE PATTERN (RECEPTACLE)                                                          | 63       |

| FIGURE 7-5 : RECOMMENDED PANEL CUT-OUT                                                                          | 65       |

| FIGURE 7-5 : RECOMMENDED FARLE COT-OUT<br>FIGURE 7-6 : P&D-D PLUG CONNECTOR - BASIC MATING INTERFACE DIMENSIONS | 66       |

|                                                                                                                 |          |

| FIGURE 9-1 : P&D SYMBOL                                                                                         | 89<br>80 |

| FIGURE 9-2 : P&D SYMBOL EXAMPLE                                                                                 | 89       |

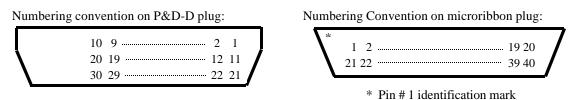

| FIGURE 10-1 : PIN DEFINITIONS, P&D-D V P&D-D                                                                    | 92       |

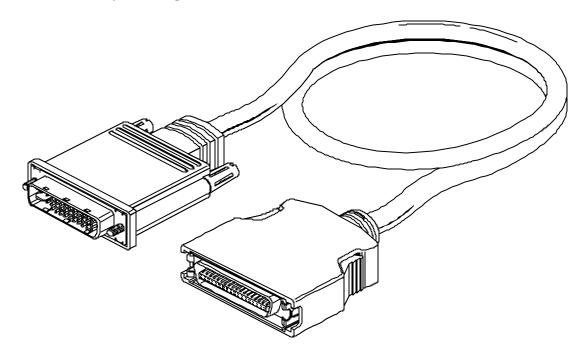

| FIGURE 10-2 : CABLE ASSEMBLY DRAWING, P&D-D ℓ MICRORIBBON                                                       | 93       |

|                                                                                                                 |          |

| FIGURE 10-3 : PIN DEFINITIONS, P&D-D ℓ MICRORIBBON                         | 94  |

|----------------------------------------------------------------------------|-----|

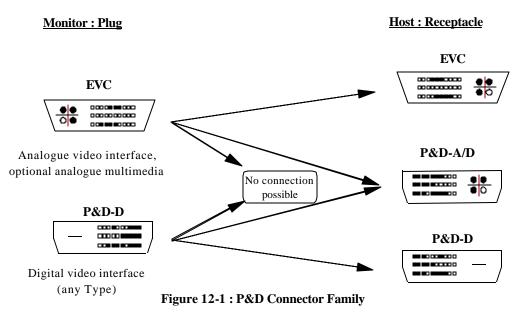

| FIGURE 12-1 : P&D CONNECTOR FAMILY                                         | 99  |

| FIGURE 12-2 : PLUG RECEPTACLE PHYSICAL COMPATIBILITY                       | 99  |

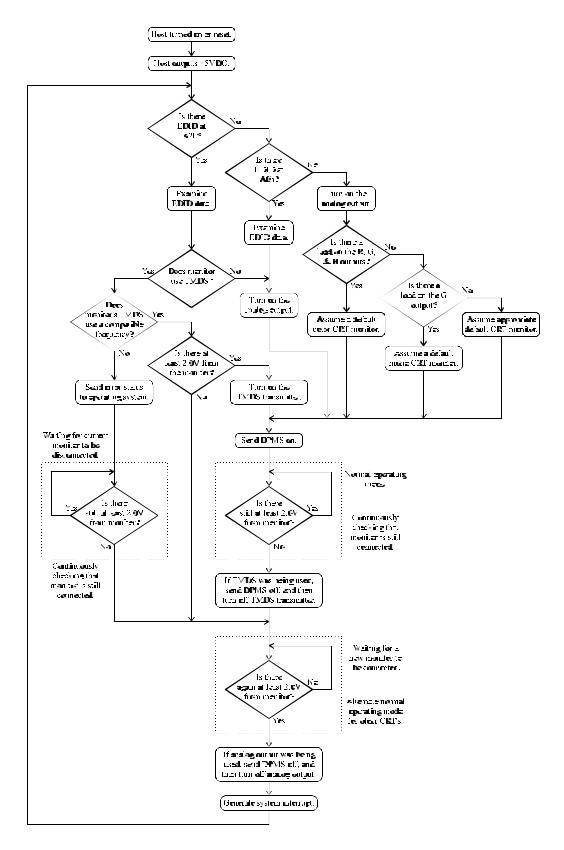

| FIGURE 13-1 : POWER-UP AND HOT PLUGGING FLOWCHART FOR P&D-A/D HOST         | 103 |

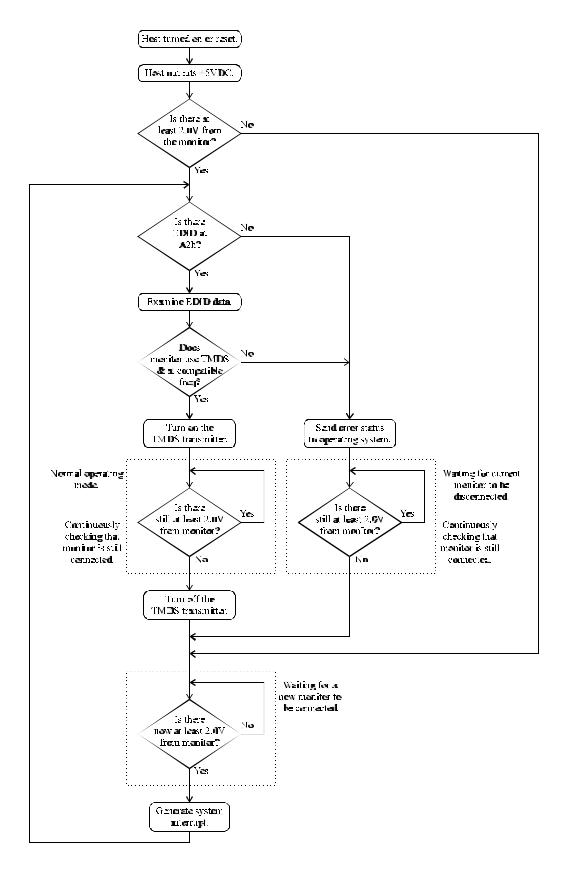

| FIGURE 13-2 : POWER-UP AND HOT-PLUGGING FLOWCHART FOR P&D-D (TMDS) HOST    | 105 |

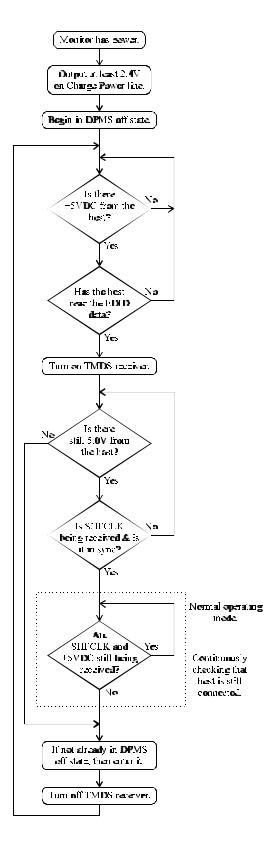

| FIGURE 13-3 : POWER-UP AND HOT-PLUGGING FLOWCHART FOR P&D-D (TMDS) MONITOR | 107 |

| FIGURE 14-1 : BANDWIDTH MEASUREMENT SET-UP                                 | 109 |

# 1. Introduction

# 1.1 P&D Overview

The purpose of this standard is to provide a digital interface and, optionally, an analogue interface for video data allowing a wide range of display devices to be attached to a single video port on the host system which may be a personal computer (PC), workstation or other device. This standard only defines the interface at the connector on the host system and provides additional recommendations regarding system implementation.

Monitors using a digital video interface generally have a fixed pixel format, typified by, but not restricted to, a Liquid Crystal Display (LCD) monitor. The objective is to retain data in a digital format thus eliminating the analogue conversion losses that cause screen artifacts. Retaining data in a digital format additionally provides opportunities for reducing system cost and simplifying the display setup.

The digital interface defined in this standard is referred to as Transition Minimised Differential Signaling (TMDS).

Analogue interface monitors are typified by, but not restricted to, CRT (cathode ray tube) based displays.

Prior to the P&D standard, the attachment of digital interface displays to PC's or workstations has required either:

- Conversion of the analogue interface to digital at the display with cost and image quality problems

- Provision of a separate graphics card with a digital interface with cost, space (slot for card), and the issues of a proprietary interface needing to be handled

Key features and benefits of the VESA P&D interface are:

- Single connector for any display device.

- Industry standard, interoperability from multiple suppliers.

- High quality display output.

- Scaleable cost and performance.

- Interoperable solution for analogue and digital monitors.

- Independent software and hardware layers.

- Operating System independent.

- Plug and Play enabled.

- Capable of using existing technology.

- Capable of working over several metres of cable.

- No DC component on interface.

- Low electromagnetic emission.

- Reduced pin count relative to parallel interface (typically 7:1 ratio).

The host receptacle interface defined in this standard is referred to as the P&D-A/D (Plug and Display - Analogue / Digital) in Section 12 which explains the relationships between this and other receptacles in the same family together with the expected monitor plugs.

The P&D-D receptacle shown in Section 12 is a logical extension of this standard for host applications not requiring an analogue option.

# 1.2 P&D Interface

The term 'logical layer' is used in this section to indicate a section of code.

## **1.2.1 Interface Elements**

| Feature                         | Comment   |

|---------------------------------|-----------|

| Digital Interface               | Mandatory |

| Analogue Interface <sup>1</sup> | Optional  |

| DDC2                            | Mandatory |

| USB                             | Optional  |

| IEEE 1394-1995                  | Optional  |

| Initialisation Logical Layer    | Mandatory |

| Command Logical Layer           | Optional  |

| Adapter Logical Layer           | Mandatory |

#### Table 1-1 : P&D Interface Features

<sup>1</sup> The analogue interface may be either:

- Red, green and blue video with Vsync. and Hsync., or

- Red, green and blue video with composite sync.

# 1.2.2 Digital Interface: Capabilities

See Section 6 for details of performance ranges, table 1.2 shows the maximum performance capability and the minimum set of features present.

| Maximum clock rate        | 112 MHz     | 160 MHz (target) |

|---------------------------|-------------|------------------|

| Maximum addressibility    | 1280 x 1024 | 1600 x 1280      |

| Maximum refresh rate      | 60 Hz       | 60 Hz            |

| Maximum colour capability | 24 bpp      | 24 bpp           |

| DDC2                      | Yes         | Yes              |

| Initialisation layer      | Yes         | Yes              |

| Adapter logical layer     | Yes         | Yes              |

### Table 1-2 : P&D Digital Interface Capabilities

<u>Note</u>: The above data rates can be achieved with a 10m cable also but it may not be possible to support either the USB or IEEE-1394 options at >5m, (see their specification documents for details).

## 1.2.3 Analogue Interface: Capabilities

Ability to support a minimum of 150MHz pixel clock.

# 1.3 Compatibility with Other VESA Standards

# 1.3.1 Compatibility with VESA DDC Standard (see Section 2.1)

The VESA P&D standard utilises the VESA DDC Interface to allow configuration data to be sent from the display to graphics subsystem.

The DDC1 protocol is not supported in P&D, but P&D is fully compatible with the DDC2 protocols.

# 1.3.2 Compatibility with VESA EDID Standard (see Section 2.1)

The VESA P&D standard utilises a configuration data structure defined in VESA Extended Display Identification Data Standard Version 3.

The VESA EDID standard should be read for details of the revised data structure required for the P&D standard.

## 1.3.3 Compatibility with VESA EVC Standard

The VESA EVC standard provides a high bandwidth analogue video interface, optional serial interfaces, and provision for analogue audio in/out and video in signals.

The VESA P&D standard provides a digital video interface and optional serial interfaces together with the same high bandwidth analogue video interface as EVC.

The VESA EVC and P&D standards share a common connector contact layout but with a different shell giving protection against mis-plugging of monitor and host. See Appendix C, Section 12 for details of plugging options.

Signals that are common to both standards include:

- Analogue video (Red, Green and Blue)

- Horizontal sync.

- Vertical sync.

- DDC bus

- USB bus

- IEEE 1394 bus

- Pixel clock

- Stereo sync.

- Charging power

All of these signals are carried on the same pins in both standards except for the charging power signals, 'Charge power +' and 'Charge power return'. Changes to the EVC standard to match the P&D standard are contained in the EVC Proposed Revision document prepared by the VESA monitor committee.

## 1.3.3.1 Charging Power

In EVC standard Version 1, charge power is defined as a floating supply. Changing to a ground referenced supply is under review by the VESA Monitor committee.

The VESA P&D standard does not support the analogue audio in and out and video in signals permitted in the EVC standard since these pins have been re-allocated to the digital interface signals.

## 1.3.3.2 Video Compatibility

| System Unit | Monitor | Video Result | Comment on Video Compatibility |

|-------------|---------|--------------|--------------------------------|

| EVC         | EVC     | OK           |                                |

| EVC         | P&D- D  | Impossible   | Incompatible Plug & Receptacle |

| P&D-A/D     | EVC     | OK           |                                |

| P&D-A/D     | P&D-D   | OK           |                                |

| P&D-D       | EVC     | Impossible   | Incompatible Plug & Receptacle |

| P&D-D       | P&D-D   | OK           |                                |

The following table addresses video compatibility (see Appendix C, Section 12 for additional details):

#### Table 1-3 : EVC Video Capability

### 1.3.4 Compatibility with VESA DPMS Standard

The VESA DPMS standard uses the absence of one or both of the horizontal and vertical synchronisation signals to indicate that the display should enter a power saving mode.

If using the analogue interface within the VESA P&D connector, then Hsync. and Vsync. should be used as usual to implement the DPMS standard.

If using the TMDS interface, then the Hsync. and Vsync. (or their equivalents for flat panel displays) signals are coded and multiplexed for transmission but demultiplexed and decoded by the TMDS receiver. They are then available to implement the DPMS standard.

If transmitting the video data over one of the serial bus options, separate provision must be made, if required, to signal power saving modes via a monitor control function. The VESA Monitor Command Set standard defines command codes to implement power saving functions.

## 1.3.5 Compatibility with VESA FPDI-2 Standard

The VESA Flat Panel Display Interface-2 (FPDI-2) Standard addresses the connection of integrated flat panel display technologies in products such as notebook PCs.

The P&D and FPDI-2 Standards use the same physical transport layer technology (PanelLink<sup>TM</sup> Technology<sup>1</sup>) with different connectors and cables.

The TMDS Technology has an adjustable output voltage. The maximum cable length in FPDI-2 is 500mm and the maximum cable length in P&D is 10m. For the same differential voltage swing at the receiver, a lower output voltage is required for FPDI-2 resulting in a reduced power requirement.

Note:

<sup>1</sup> In most cases this standard will use TMDS, Transition Minimised Differential Signaling, to indicate PanelLink<sup>TM</sup> or compatible technology.

# 1.4 Compatibility with Monitors Using Other Connectors

# 1.4.1 Compatibility with Monitors Using 15-pin D-sub Connector

These monitors will almost certainly be using an analogue interface. An adapter cable or connector can be provided which would allow attachment to the analogue section of the VESA P&D interface for virtually all monitors which have DDC capability.

Monitors without DDC capability cannot be connected to the P&D interface.

## 1.4.2 Compatibility with Monitors Using 13W3 Connector

These monitors will almost certainly be using an analogue interface. Many 13W3 implementations do not include DDC and hence they cannot be compliant with the VESA P&D interface.

Those 13W3 connections that do include DDC permit an adapter cable or connector to be provided which would allow attachment to the analogue section of the VESA P&D interface.

## 1.4.3 Compatibility with Monitors Using BNC Connectors

These monitors will almost certainly be using an analogue interface. Most BNC implementations do not include DDC and hence they cannot be compliant with the VESA P&D interface.

Those BNC connections that do include DDC permit an adapter cable or connector to be provided which would allow attachment to the analogue section of the VESA P&D interface.

# 1.5 Incompatible Display and System Interfaces

The display shall give a visible and / or audible warning if there is basic incompatibility between the display requirements and the host system capabilities.

This function shall be triggered by detecting that the display interface is connected by monitoring the presence of the DDC +5VDC, if no displayable video is received within 60s of detecting the +5VDC then the display shall indicate incompatibility.

# 2. Plug and Display Architectural Overview

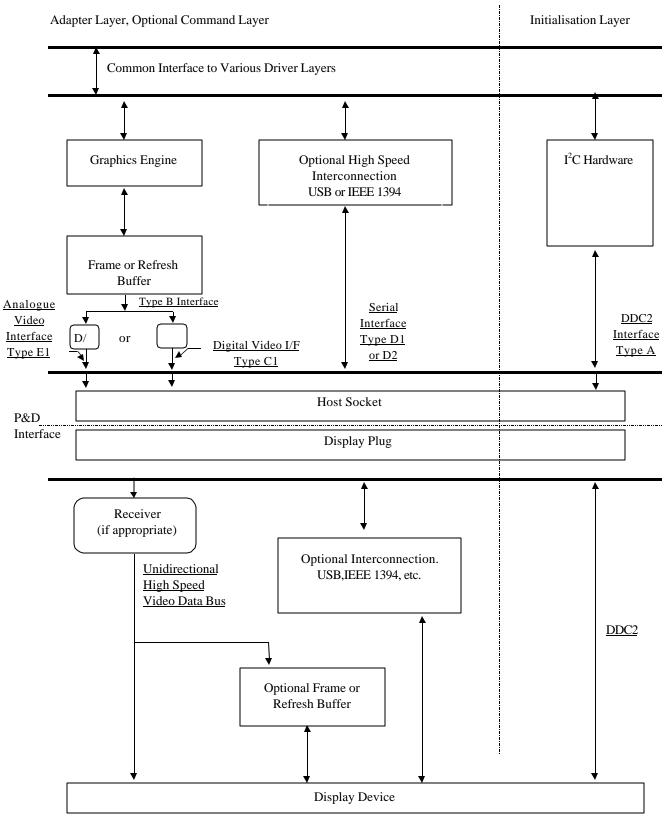

The P&D architecture is designed as an integrated graphics subsystem with a layered system design concept. The two main layers are logical (software) and physical (electrical and connector).

# 2.1 Plug and Display System Overview

The Plug and Display Standard is consistent with the VESA Plug and Display Architecture concepts. This architecture is designed to maximise interconnectability whilst allowing many degrees of freedom in choice of the particular interface(s) supported by a particular implementation.

There are two major layers:

- Logical Layer

- The Logical layer is a software layer with multiple sublayers, the Initialisation layer, the Command layer and the Adapter layer. A logical sublayer can communicate with more than one physical sublayer (Interface).

- The logical layer structure permits independence from a specific operating system and hardware implementation.

- The following logical layers are mandatory, the Initialisation layer and the Adapter layer.

- Physical Layer

- Within the physical layer optional communications sublayers (or interfaces) may be selected. More than one communications channel is permitted within the Physical Layer.

- Three sublayers are mandatory:

- The DDC2 interface to provide configuration data.

- The TMDS interface for digital video data.

- The analogue interface for video data

Other sublayers are optional and may provide such features as control of the display device, attachment of additional devices, etc.

The P&D interface is designed for point to point uni-directional video high speed data communication between a host (e.g. a PC or Workstation) and a Monitor but is also able to support bi-directional multi-port medium speed command, control and data transfer connectivity. The Monitor may be comprised not only of a display transducer but also a wide range of I/O. e.g. Digital Cameras, CD ROMs, Keyboards, Mice, Pointing Devices, Sound I/O.

# 2.2 P&D Architecture

Reference Section 2.3 for conceptual drawing.

## 2.2.1 Logical Layer Concepts

The Logical layer comprises of three sublayers:

Initialisation Layer

This layer is mandatory.

- Command Layer

The command lay

- The command layer provides support for video transducer control and low speed I/O data streams.

- Adapter Layer

The adapter layer provides transport mechanism of video data stream from the application and operating system to the display device.

#### The Initialisation Logical Layer is a mandatory section of code which :

- a) Starts and Controls the DDC2 data from the display device to the host and places the DDC2 data into a buffer.

- b) Analyses the DDC2 data and configures the communications channel(s) in the system adapter(s) to match the channel resources in the monitor and the I/O attached to the monitor.

This layer of code may function prior to the operating system being loaded or during the loading of the operating system.

#### The **Command Logical Layer** is an optional layer of code that:

Controls the monitor in terms of setting parameters (e.g. colour temperature ), reading status and running diagnostics.

For those digital monitors which do not support the command layer, power management is controlled using the protocol specified by the VESA DPMS standard.

Either USB or IEEE-1394 may be used as the Command layer.

Low speed I/O devices (keyboard, pointing devices, etc.) may be attached via USB whether it is the Command layer or not.

High speed I/O devices (CDROM, hard disk drive, camera etc.) may be attached IEEE 1394 whether it is the Command layer or not.

#### The Adapter Logical Layer provides:

The interface for the unidirectional high speed video data bus or a high speed bi-directional channel(s) which allows video devices,(in-head display adapters, digital camera) and display adapter in the PC or Workstation.

This layer is mandatory

### 2.2.2 Physical Layer Concepts

The physical layer comprises two sublayers:

- Electrical physical layers

- Mechanical physical layer

### 2.2.2.1 Electrical Physical Layers

The electrical physical sublayers may be either the electrical interface at a physical connector or an electrical interface between two function units on a logic card or within a VLSI Module. The interface defined here is at the connector pins after the output transmitters.

A DDC2B (with +Vcc and GND supplied by the system unit) physical sublayer is mandatory to carry configuration data from the display to the host during host initialisation and operating system load.

Note: DDC2B is the minimum level of performance, an implementor may choose to use DDC2B+ or DDC2AB instead.

The TMDS and DDC2 electrical sublayers are mandatory, other electrical sublayers are optional.

### 2.2.2.2 Mechanical Physical Layer

This is the layer where the type and pin assignment configuration of the connector is defined. See Section 7 for specification.

<u>Note:</u> Specification of a particular cable type is outside the scope of this standard, however, Section 8 provides guidance on likely performance requirements.

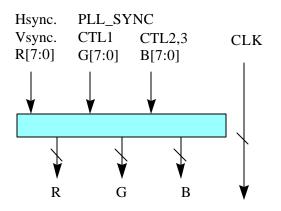

## 2.2.3 Explanation of Remaining Elements of P&D Architecture Overview Drawing

Reference: Section 2.3

• Graphics Engine

This section covers the graphics chip, graphic accelerator, etc.

- Frame or Refresh Buffer A block of memory used to store and manipulate the displayed image(s).

- Optional Interconnection USB, IEEE 1394, etc.

This represents the optional serial buses that may be used either to provide video data or to control of the display and / or provide attachment of other devices.

•  $I^2C$  Hardware

The hardware required to support a DDC2B (or DDC2B+ or DDC2AB) interface.

Host Video Receptacle

A representation of the physical receptacle on the host system.

- Display Video Cable Plug A representation of the physical plug on the host end of the video cable.

- Optional Frame or Refresh Buffer

An optional frame or refresh buffer which may be required for some technologies or be an alternate design point.

• Display Device

The actual display device.

# 2.3 P&D-A/D Connector Overview

Figure 2-1 : P&D-A/D Connector Overview

# 3. Detection of Display Disconnect

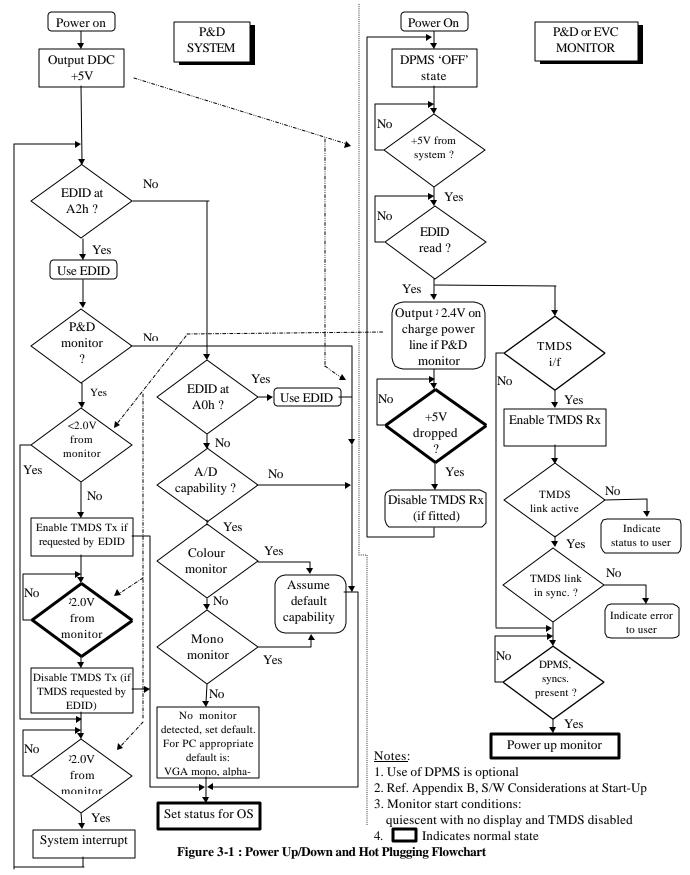

The VESA Plug and Display Standard supports hot-plugging of the display device. The primary purpose is to protect the display device from possibly dangerous conditions created by receiving data at an inappropriate frequency and/or format. There are elements of the detection mechanism at the host and display ends.

Notes:

- 1. The flowchart in Section 3.3 and following text assume that monitor design incorporates DPMS.

- 2. DPMS is optional under P&D.

## 3.1 Detection Mechanism - Host

Reference the flowchart in section 3.3 which is intended for process illustration only.

Initially the host system shall provide the +5V DDC line and then check to see if an EDID can be read at address A2h. The host should retry this operation for up to 30s.

If no EDID is detected at A2h, then the host shall check for an EDID at A0h. If an EDID is present then the EDID contents should be decoded to provide supported mode information.

If no EDID is present then carry on to check for presence of a colour or monochrome monitor by checking for load on the R/G/B lines, if a monitor is present then assume it has minimum VGA capability.

If an EDID is detected at A2h, if a P&D monitor bit is set in EDID check that the charge power line has <sup>3</sup> 2.0V from the monitor to indicate that the monitor is ready. **Note: The charge power line may be up to 20V.**

If the EDID requested use of the TMDS interface, then enable the TMDS transmitter.

Continue to monitor the Charge power line for <sup>3</sup> 2.0V, if the voltage drops then assume the monitor has been unplugged, immediately disable the TMDS transmitter (if it was enabled) and wait until the <sup>3</sup>2.0V signal is reestablished indicating that a monitor, the same one or a different one, has been attached. The graphic sub-system should raise an interrupt to the operating system which should cause the operating system to initiate action to reread the EDID and take appropriate action based on the contents of the new EDID.

A status shall be set indicating what monitor capability has been detected (or assumed) and when the TMDS transmitter is enabled or disabled.

# 3.2 Detection Mechanism - Display

Reference the flowchart in Section 3.3 which is intended for process illustration only.

When power is applied initially the display should be in a quiescent state with no displayed image and the TMDS receiver (if present) disabled. The DDC +5V line from the system shall be monitored, if +5V is present then, assuming monitor power is enabled, output <sup>2</sup>2.4V on the Charge Power line if it is a P&D monitor. If a TMDS receiver is present then enable it, then check if the link is active and synchronised. Indicate 'link inactive' and, if necessary, 'link unsynchronised' status to user.

The DPMS circuit will then power up the monitor once the Hz. and Vt. sync. signals are detected.

Continue to monitor the +5V line, if the line drops for to <2.0V for >1s after being present for >60s then a hot plug condition exists. The display shall disable the TMDS receiver, if fitted, and indicate the status to the user by an appropriate technique e.g. flashing LED, on screen message, etc. After an appropriate period, the display should return to the initial quiescent state.

# 3.3 Power Up/Down and Hot Plugging : Flowchart

VESA Plug and Display Standard Copyright© 1997 Video Electronics Standards Association Page 23 of 111 Version 1 Revision 0

# 4. Electrical Layer Specification: Part 1

The Electrical Layer Specification has been split into 3 sections. This section deals with all aspects except for the TMDS interface and Section 6 gives the detailed specification of the TMDS interface at the P&D connector. Section 5 is inserted to give an overview of the TMDS interface technology, it is not considered to be part of this standard.

# 4.1 Introduction

Each sublayer is identified by its function and also a designation of "Type x" where 'x' represents a variety of possible alphanumeric codes. These type codes are a cross-reference to the VESA P&D Architecture Document.

| Type Designation | Corresponding Sublayer      |  |  |

|------------------|-----------------------------|--|--|

| A                | DDC2                        |  |  |

| C1               | TMDS Interface <sup>1</sup> |  |  |

| D1               | IEEE 1394-1995              |  |  |

| D2               | USB                         |  |  |

| E1               | EDID Defined Analogue       |  |  |

#### Table 4-1 : Electric Sublayers

<sup>1</sup> The TMDS Interface is considered in Sections 5 and 6.

# 4.2 DDC2 Sublayer, Type A

The DDC2 sublayer interface is a simple low cost serial interface for the initialisation of the P&D. DDC2B is the minimum level required to comply with this standard, DDC2B+ or DDC2AB may, optionally, be used for control of the monitor. This a mandatory electrical sublayer.

DDC2B is a point to point bi-directional channel between the display and the host system, the VESA Display Data Channel Standard contains the full definition.

### 4.2.1 List of Signals

| Signal Name | I <sup>2</sup> C Bus Name |

|-------------|---------------------------|

| DDC Data    | SDL                       |

| DDC Clock   | SCL                       |

| +5V DC      |                           |

| DDC Return  |                           |

#### Table 4-2 : DDC2 Sublayer Signals

## 4.2.2 Signal Specification and Timing

The VESA DDC Standard Version 2 contains definitions of signal specifications and timing.

## 4.2.3 Extended Display identification Data (EDID)

The VESA EDID Version 3 standard contains a specific data format for use with this P&D Standard.

# 4.3 IEEE 1394-1995 Sublayer, Type D1

See IEEE 1394-1995 (High Speed Bus) Specification for details.

# 4.4 USB Sublayer, Type D2

See Universal Bus Specification for details.

# 4.5 Analogue Sublayer, Type E1

The analogue sublayer has a number of options (e.g. signal amplitude and polarity). The EDID transmitted by the display will define the option(s) to be used.

## 4.5.1 Analogue Interface

As a method of supporting the current variable format analogue monitors, a RGB with line sync. and frame sync. sublayer interface is supported.

# 4.5.1.1 List of Signals

| Signal                     | Signal Level      |

|----------------------------|-------------------|

| Red Video Out              | See Section 4.5.2 |

| Green Video Out            | See Section 4.5.2 |

| Blue Video Out             | See Section 4.5.2 |

| Pixel Clock Out (optional) | See Section 4.5.4 |

| Video Return               |                   |

| Hz. Sync. Out              | See Section 4.5.3 |

| Vt. Sync. Out              | See Section 4.5.3 |

| Sync. Return               |                   |

| Stereo Sync.               | See Section 4.7   |

Table 4-1 : Analogue Sublayer Signals

## 4.5.2 Analogue Video Signals

The video signals provided by the P&D shall comply with the following requirements. Please note that this standard includes the new VESA video signal standard originally introduced in the VESA EVC standard which may be used if desired. Systems may continue to use the earlier signal standards while using the P&D, as long as support for the appropriate standard is identified by the display in the EDID information, and if the overall requirements for those signals under P&D are met.

# 4.5.2.1 Signal Amplitude and Polarity

All video signals provided by systems using the P&D shall be interpreted such that increasingly positive voltages in excess of the defined black level correspond to increasing luminance in the displayed image. i.e. the P&D shall always provide "white-positive" video signals.

The signal amplitude standard expected by the display will be provided by that display via its EDID but must conform to one of the following standards:

|                           | Type 1<br>"RS-170" <sup>1</sup> | Type 2<br>"RS-343" <sup>1</sup> | Type 3<br>"Euro" | Type 4<br>VESA |

|---------------------------|---------------------------------|---------------------------------|------------------|----------------|

| White (peak) <sup>2</sup> | + 1.000 V                       | + 0.714 V                       | +0.700 V         | + 0.700 VDC    |

| Black <sup>3</sup>        | +0.075 V                        | +0.054 V                        | + 0.000 V        | + 0.000 VDC    |

| Blank                     | Reference                       | Reference                       | Reference        | + 0.000 VDC    |

| Sync. tip <sup>4</sup>    | - 0.400 V                       | - 0.286 V                       | - 0.300 V        | None           |

Table 4-2 : Video Signal Amplitude and Polarity

<sup>1</sup> - The terms "RS-170" and "RS-343" properly refer to two classes of former standards which were established by the Electronic Industries Association (EIA). As these terms have been commonly used within the computer display industry, they refer only to the signal level standards listed above. Refer to the EIA standards for full definition of these signals.

$^{2}$  - White is defined as the peak signal level, excluding overshoot, ringing, noise, and similar transients, which is transmitted during the active video time i.e. that period of the video signal exclusive of the blanking time.

<sup>3</sup> - Black is defined as the minimum signal level expected during the active video time. The RS-170 and RS-343 standards define a difference between "black" and "blank", known as the "setup". Setup may be considered optional under these standards, but the display should communicate (via the EDID) whether or not setup is expected.

<sup>4</sup>-The sync. tip level refers to the signal amplitude defined for the case of sync-on-video. In systems providing syncon-video, this information should appear only on the Green video signal except in the case where the Red, Green and Blue signal outputs are being used to provide simultaneous monochrome outputs. Sync. information shall not be provided on any video signal output when separate sync. signals are in use. Sync-on-video may not be used when operating under the VESA video signal standard.

# 4.5.2.2 Reference level

With the exception of the VESA video signal standard, the above listed standards are intended for AC-coupled video inputs and use the blank level as the signal reference. The VESA video signal standard is intended for DC-coupled systems, and the reference point under this standard is the signal common as established by the return for the video signals (pin C5 of P&D-A/D).

# 4.5.2.3 System Impedance

Any analogue video output driver, display input, cabling, etc., used in a P&D-A/D based system shall be designed assuming a nominal impedance of 75% for the analogue video signal transmission system.

# 4.5.3 Synchronisation Signals - VESA Video Signal Standard

Except as noted below, the following requirements shall apply to those systems employing the P&D-A/D and using the VESA video signal standard.

# 4.5.3.1 Combining Synchronisation and Video (Luminance) Signals

Video systems using the VESA video signal standard shall not supply or use synchronisation pulses combined with the luminance signals defined above. i.e. there shall be no sync-on-green or equivalent.

Synchronisation signals shall always be supplied to the display by means of separate, dedicated signal lines.

# 4.5.3.2 Sync Signals Under the VESA Video Standard

Horizontal sync. pulses shall at all times continue to be supplied during the vertical sync. pulse period. Under the VESA video signal standard, use of composite sync. on either separate sync. line is not permitted.

## 4.5.3.3 Synchronisation Signal levels and Tolerances

It is expected that the synchronisation signals will be communicated using one or more standard logic family levels, and that strictly defining the expected signal levels for all cases is therefore beyond the scope of this standard. However, the following standards should be recognised for the specific cases of the TTL families.

| Logic Family     | TTL (all families)                    |  |  |

|------------------|---------------------------------------|--|--|

| Logic "1" level  | min. 2.4 V (driver), 2.0 V (receiver) |  |  |

| Logic "0" level  | max. 0.5 V (driver), 0.8 V (receiver) |  |  |

| Rise / Fall time | < 10 ns (20 - 80%)                    |  |  |

#### Table 4-3 : Synchronisation Signal Specification

### 4.5.3.4 Termination of Synchronisation Signal Lines; Loading

In the case of systems using the TTL logic levels as defined above, the standard termination presented on the synchronisation lines by the display device shall be a nominal 2 KW to +5 VDC.

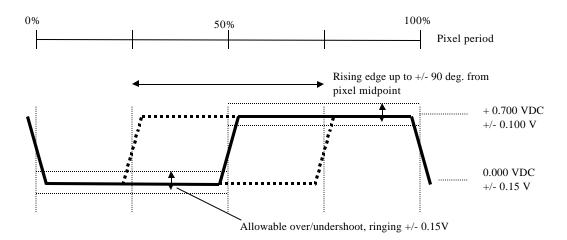

## 4.5.4 Pixel Clock

The P&D receptacle provides for an optional Pixel Clock, intended for use by flat-panel based displays or similar systems which require a clock to sample the video output signals. This pixel clock is not required to be present on the P&D unless some level of flat-panel support via the analogue interface portion is intended, and may be enabled or disabled by the host depending on whether or not the display in question requests it via the display's EDID.

When provided the clock output shall meet the following requirements, as measured at the P&D output pin and using a standard (75W +/-1%) resistive termination connected as closely as possible to that point.

## 4.5.4.1 Signal Amplitude and Offset

The clock signal amplitude shall be 0.7 Vp-p, +/- 0.1 V. The signal shall have 0.0V DC offset, meaning that the logical "0" portions of the signal shall be at 0.0V DC (as defined by the signal ground, pin C5), with the logical "1" state at a nominal + 0.7V from this reference.

## 4.5.4.2 System Impedance

75₩ nominal.

## 4.5.4.3 Active Edge

It shall be standard that the active edge of the pixel clock (the edge on which the video is expected to be sampled) shall be the rising edge i.e. the positive going transition.

# 4.5.4.4 Skew

The skew of the pixel clock shall be controlled such that the 50% point of the rising edge occurs at the midpoint (50%) of the pixel period within the green video signal +/- 90 degrees.

## 4.5.4.5 Rise / Fall Time

The rise time (positive going transition) of the pixel clock signal, as measured between the 10% and 90% points, shall not be greater than 20% of the pixel period of the fastest pixel clock supported in this mode of operation. There is no specific requirement on the clock fall time, other than it be sufficiently short so as to permit a low (logical "0") time (signal at or below 0.1 V) of not less than 35% of the clock period.

## 4.5.4.6 Overshoot / Undershoot, Ringing

The overshoot, undershoot, and ringing of the pixel clock signal shall be controlled so that no portion of the clock signal falls outside of the range  $\pm -0.15V$  of the nominal amplitude for the high or low state following the rising or falling transition, respectively.

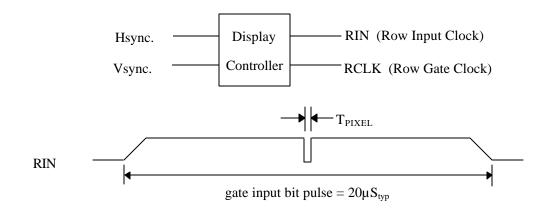

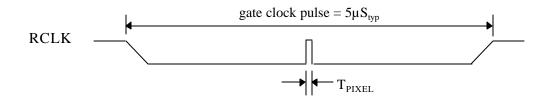

The above requirements are summarised in the following diagram:

Figure 4-4 : Stereo Sync.

# 4.6 Charging Power

The charging power input is used by the host computer (typically a notebook or similar portable computer) as a source of charging power for its internal batteries (if fitted). Support for this input is optional and a host with no need for charging power is not required to provide any connection or load on this line except for the hot plugging scheme requirements specified in Section 2. Display devices intended for connection to a host may provide charging power on this pin as desired.

The following restrictions apply:

1. Charging Voltage 18 \* 20 VDC.

#### 2. Current

Maximum of 1.5A in normal "full-on" state. The current available on this pin shall at all times be limited to not more than this value long term, and not more than 5A for not more than 2s. The device supplying the power must be designed so that no damage or safety hazard occurs under any load condition, including a short or ground applied for an indefinite period.

#### 3. Current Control, Default State, and Loss of Connection

The charging current shall at all times be under the control of the host device (the device being charged).

The default (power up) state for the charging supply shall be the trickle charge state, as described below.

- The charging supply shall be switched to the "full on" state described above only upon detection of a host connection via sensing of the +5 VDC supply on pin # 8 (any time the voltage present on this line exceeds +2.0 VDC for a continuous period of not less than 10 µs), or under the command of the host device.

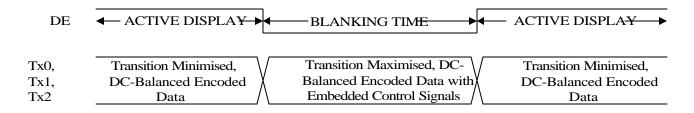

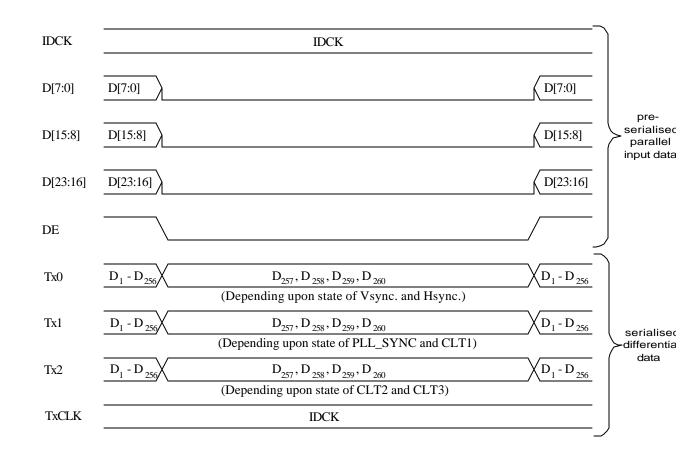

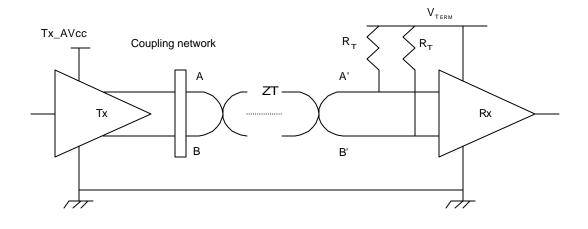

- The charging supply shall also be designed to return to the trickle charge state within 10ms of disconnection from the host, identified by loss of the +5 VDC supply (pin # 8) from the host (any time the voltage on this line is less than 0.8 VDC for a continuous period of not less than 10 µs).