# OPERATIONS MANUAL SAT-V41

WinSystems® reserves the right to make changes in the circuitry and specifications at any time without notice.© Copyright 1996 by WinSystems. All Rights Reserved.

### **REVISION HISTORY**

#### P/N 403-242-000

| ECO Number | Date Code | <b>Rev Level</b> |

|------------|-----------|------------------|

| Originated | 960426    | С                |

| 98-120     | 981209    | C1               |

# TABLE OF CONTENTS

| Section<br>Number | Paragraph<br>Title                | Page<br>Number |

|-------------------|-----------------------------------|----------------|

| 1                 | General Information               |                |

| 1.1               | Features                          | 1-1            |

| 1.2               | General Description               | 1-1            |

| 1.3               | Specifications                    | 1-2            |

| 2                 | SAT-V41 Technical Reference       |                |

| 2.1               | Introduction                      | 2-1            |

| 2.2               | V40 CPU                           | 2-1            |

| 2.3               | Memory Addressing                 | 2-2            |

| 2.4               | Memory Map Selection              | 2-3            |

| 2.5               | Memory Device Configuration       | 2-3            |

| 2.6               | Memory Paging Configuration       | 2-5            |

| 2.7               | Battery Select Options            | 2-6            |

| 2.8               | Serial Communications             | 2-6            |

| 2.9               | Parallel Printer Port             | 2-8            |

| 2.10              | Counter/Timer I/O                 | 2-9            |

| 2.11              | Watchdog Timer                    | 2-9            |

| 2.12              | DS-1202 Clock/Calendar            | 2-10           |

| 2.13              | Interrupt routing                 | 2-11           |

| 2.14              | Status LED                        | 2-11           |

| 2.15              | Analog Input                      | 2-11           |

| 2.16              | Parallel I/O                      | 2-12           |

| 2.17              | PC/104 Expansion                  | 2-13           |

| 2.18              | Power Input                       | 2-13           |

| 2.19              | Connector/Jumper Summary          | 2-14           |

| APPENDIX A        | Ι/Ο ΜΑΡ                           |                |

| APPENDIX B        | SAT-V41 Parts List                |                |

| APPENDIX C        | SAT-V41 Parts Placement Guide     |                |

| APPENDIX D        | NEC V40 Processor Data Sheet      |                |

| APPENDIX E        | 16C452 Serial/Parallel Data Sheet |                |

| APPENDIX F        | 8255A Parallel I/O Data Sheet     |                |

| APPENDIX G        | DS1202 Clock/Calendar Data Sheet  |                |

| APPENDIX H        | MAX186 A/D Data Sheet             |                |

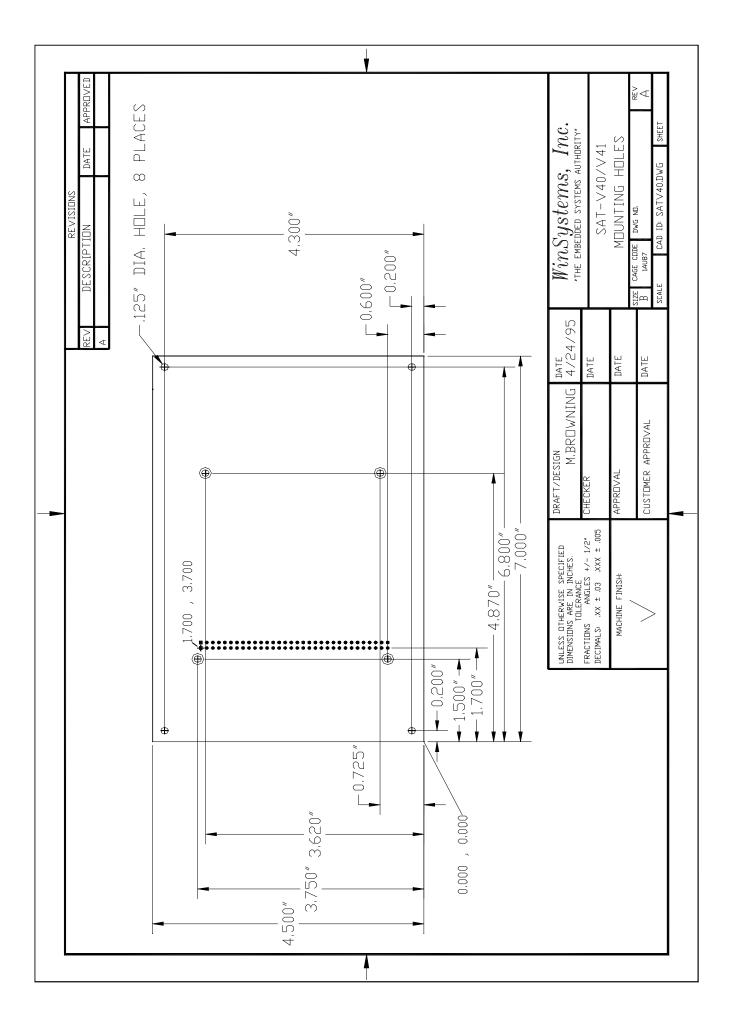

| APPENDIX I        | SAT-V41 Mechanical Drawing        |                |

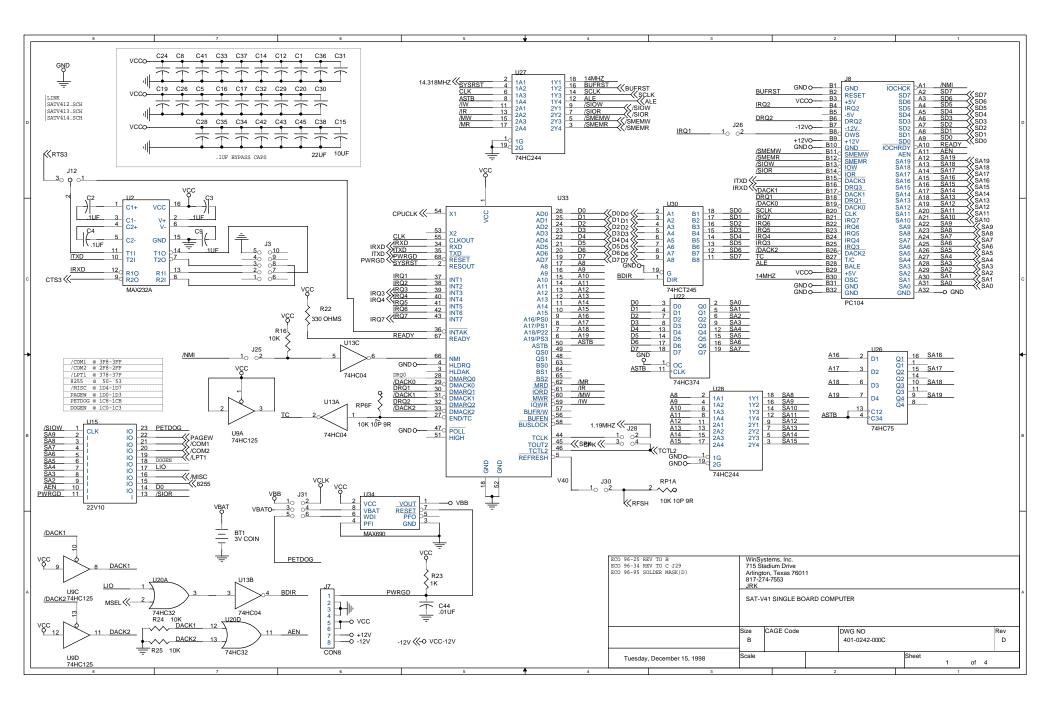

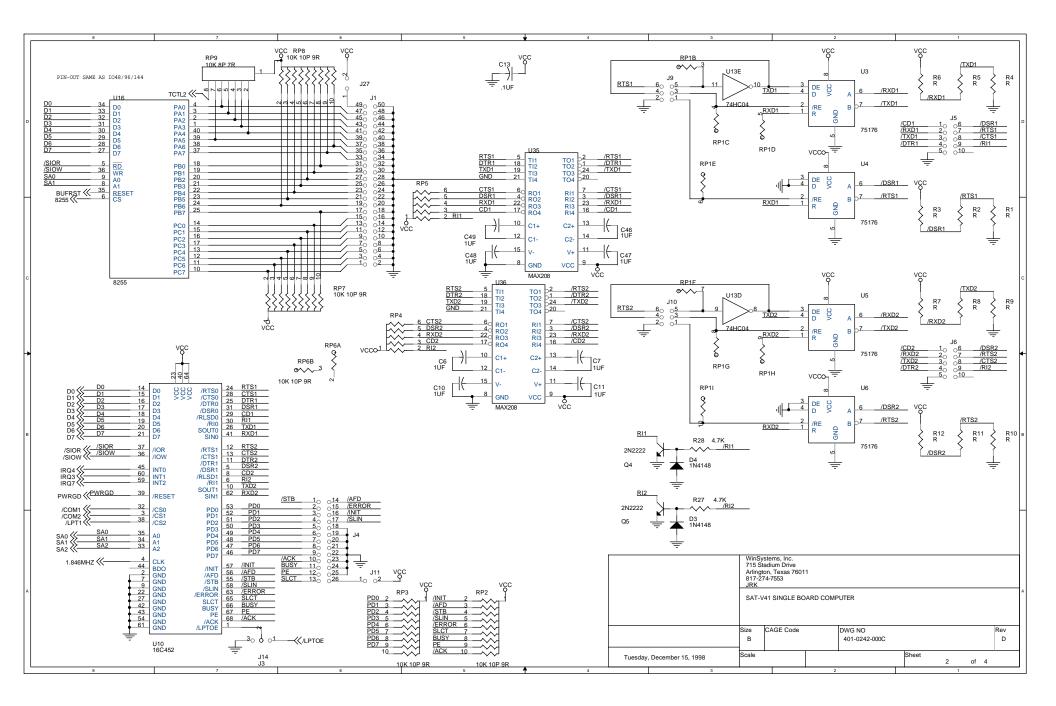

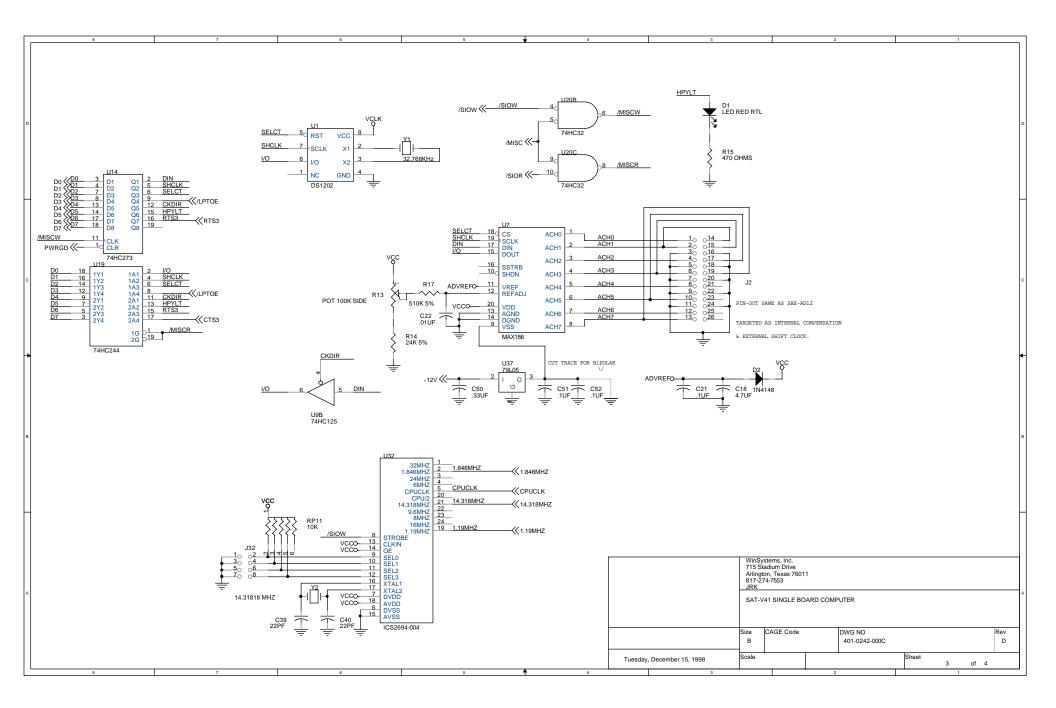

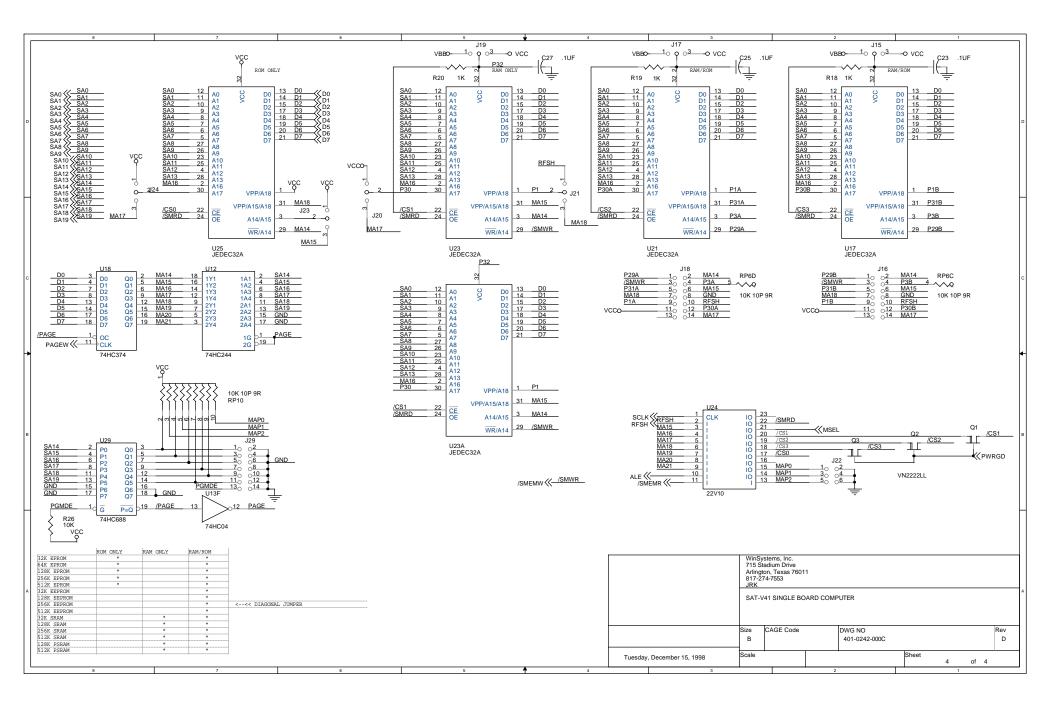

| APPENDIX J        | SAT-V41 Schematic Diagram         |                |

| 0                 |                                   |                |

THIS PAGE INTENTIONALLY LEFT BLANK

# **1** GENERAL INFORMATION

## 1.1 **FEATURES**

- 8-Mhz V40 Processor, 8088 compatible with integral peripherals

- DMA controller

- 8259 Compatible Interrupt controller

- Serial Communications Unit (SCU)

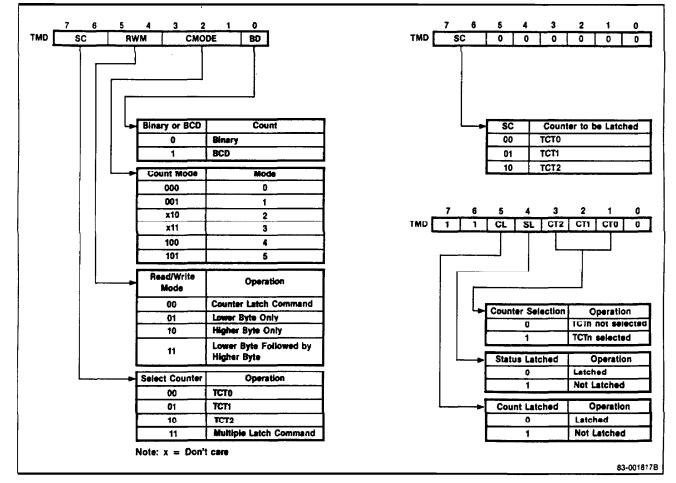

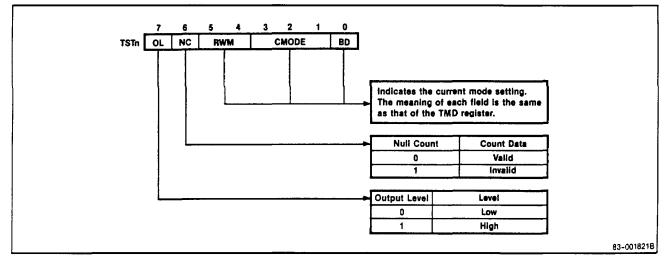

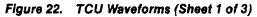

- 8254 Compatible Counter/Timer

- Refresh/Wait State Controller

- 2 Meg on board memory addressable through 4 JEDEC 32-pin sockets

- Two 8250 Compatible Serial channels, fully PC COM1, COM2 compatible.

- 1 PC Style Parallel Printer Port as LPT1

- Optional 12-Bit A/D converter

- 24 Lines of Parallel I/O using on-board 71055

- On-Board Dallas Semiconductor DS1202 Clock/Calendar/RAM

- Watchdog Timer with Software Enable/Disable capability

- Software Controlled Activity/Status LED

- Precision Power-Fail/Brown-out supervisory circuit

- Operating Temperature Range of -40°C to +85°C

- PC/104 Expansion Bus

- +5 Volt only operation

## 1.2 General Description

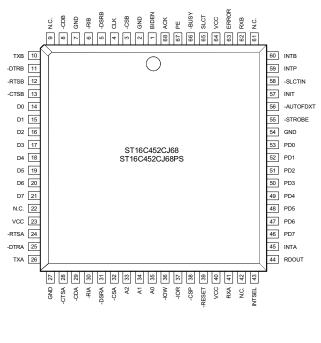

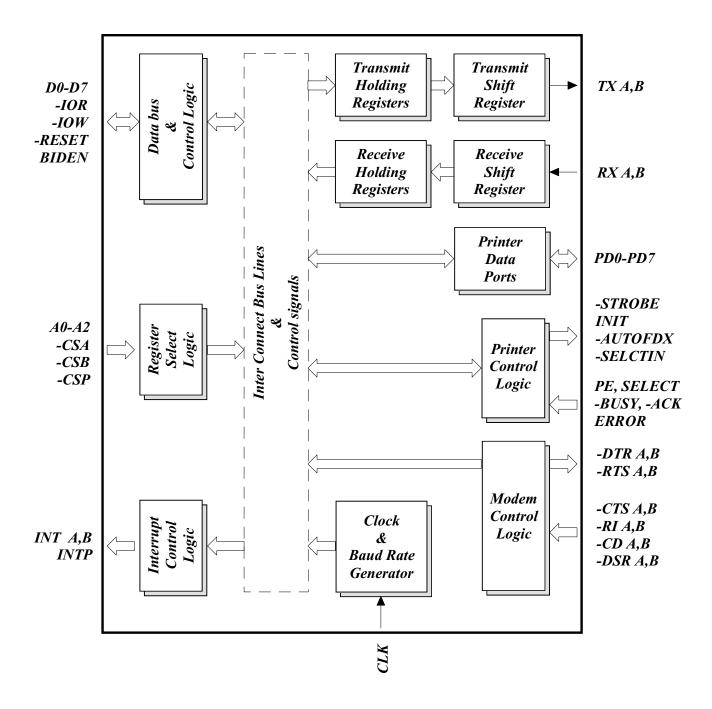

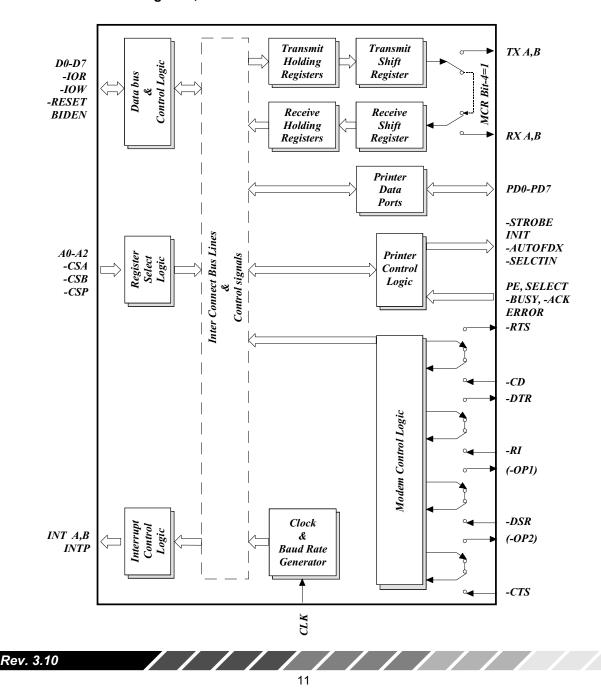

The SAT-V41 is a compact medium-performance industrial control and monitoring engine with a highly diverse set of integrated I/O peripherals. The 8088 code compatible V40 processor offers an enhanced instruction set, coupled with an improved instruction pipeline resulting in a performance increase over the 8088. The DMA controller, Timer/Counter Unit, Serial Communications Unit, Refresh Controller, 8259 Compatible interrupt controller, and wait state controller are all integrated into the V40 CPU. A memory paging scheme allows for up to 2 megabytes of SRAM, PSRAM, EPROM, and PEROM to be accessed by the processor through the 4 on-board 32-pin JEDEC standard memory sockets. An optional on-board battery allows for protection of SRAM as well as power-down time keeping for the Dallas Semiconductor DS1202 Clock/Calendar Chip. This chip also provides 24 bytes of battery backed configuration RAM. The addition of the Startech 16C452 provides two 8250 Compatible serial ports and a parallel printer port. These 2 serial ports are mapped at PC standard COM1 and COM2 addresses and can use generic PC communications I/O routines. These serial ports may be optionally configured for RS-422 or RS-485. The Parallel printer port is also fully PC compatible. To provide control capability an 71055 PPI (Intel 8255 equivalent) chip allows for 24

lines of multi-mode digital I/O, including OPTO-22 interface compatibility. An additional on-board option is for 8 channels of Analog input with 12-bit resolution. The SAT-V41 packs all of the most requested functions onto a single 4.5" x 7.0", 5 Volt only board which is function expandable through low-cost PC/104 modules from WinSystems and a variety of international suppliers.

## 1.3 SAT-V41 SPECIFICATIONS

| 1.3.1 | Electrical |

|-------|------------|

| 1.0.1 | Licculoui  |

| Bus Interface : | PC/104 8-Bit compatible                                   |

|-----------------|-----------------------------------------------------------|

| System Clock :  | 8 MHz.                                                    |

| Interrupts :    | TTL Level                                                 |

| VCC :           | +5 Volts +/-5% at 200mA with no memory devices installed. |

| VCC1 :          | +12V +/-5% for PC/104 module use only                     |

| VCC2 :          | -12V +/-5% for PC/104 module use only                     |

#### 1.3.2 **Memory**

Addressing : 1 Megabyte directly addressable. 4 Megabyte capability provided through an 8-bit page register.

Memory Sockets : Four 32-pin JEDEC compatible sockets. 1 ROM only. 1 RAM only, 2 for RAM, ROM, EPROM, or PEROM.

#### 1.3.3 Mechanical

- Dimensions : 4.5 X 7.0 X 0.6 inches

- PC Board : FR-4 epoxy glass with 2 signal layers and 2 power planes with screened component legend and plated through holes.

- Jumpers : 0.025" square posts on 0.10" centers

Connectors :

Serial Port Connectors (3) : 10 Pin RN type IDH-10-LP Printer Port : 26 Pin RN type IDH-26-LP Parallel I/O : 50 Pin RN type IDH-50-LP Analog Input : 26 Pin RN type IDH-26-LP PC/104 BUS : SAMTECH type ESQ-132-12-G-D Power Input : Molex 22-11-2082

## 1.3.4 **Environmental**

Operating Temperature : Non-condensing Humidity : -40° C to +85° C 5 to 95% THIS PAGE INTENTIONALLY LEFT BLANK

# **2** SAT-V41 TECHNICAL REFERENCE

## 2.1 Introduction

This section of the manual is intended to provide sufficient information for the configuration and usage of the SAT-V41 board. WinSystems maintains a technical support group to help answer questions regarding configuration, usage, or programming of the board. For answers to questions not adequately addressed in this manual contact Technical Support at (817) 274-7553 between 8AM and 5PM Central Time, Monday through Friday. The SAT-V41 board utilizes a number of complex VLSI devices in its design. The manufacturer's data sheets for these devices are reprinted in the Appendices. Refer to these documents for programming information.

## 2.2 **V40 CPU**

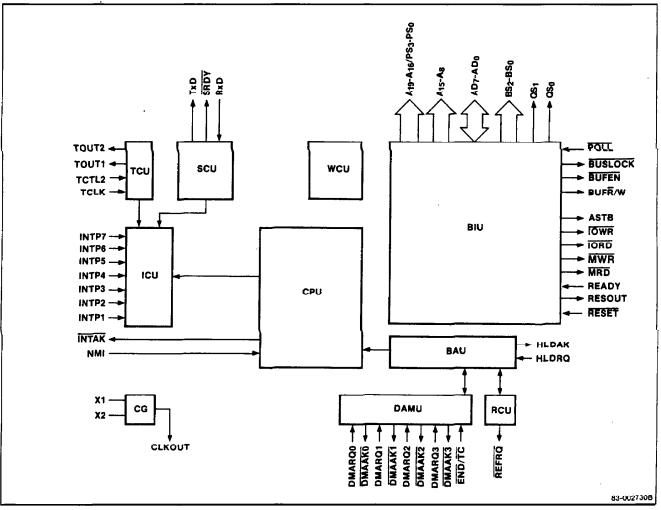

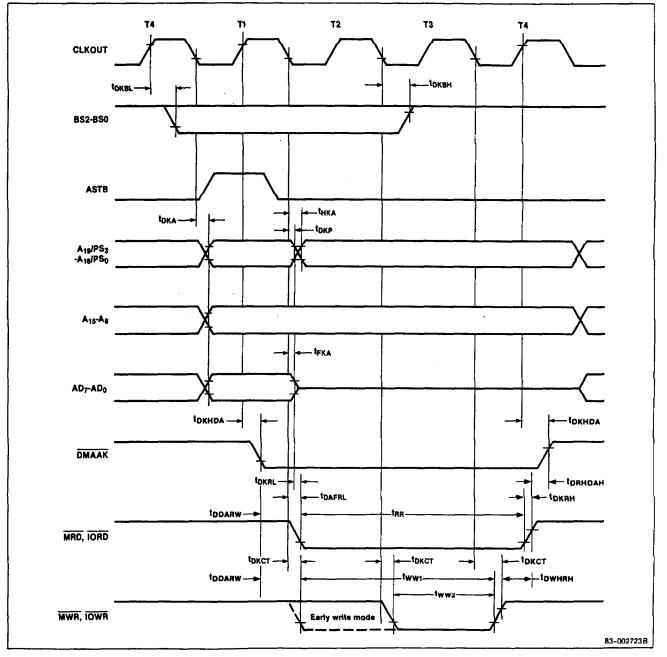

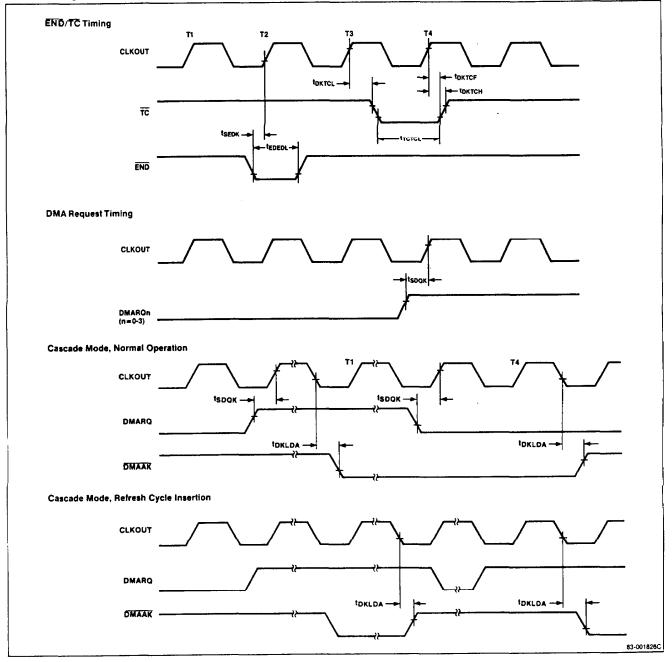

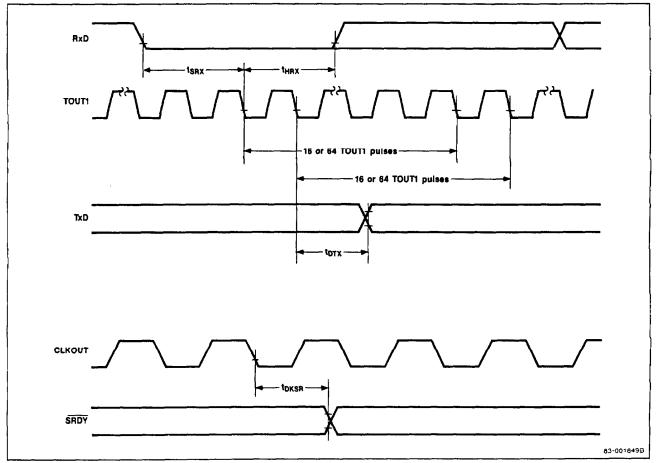

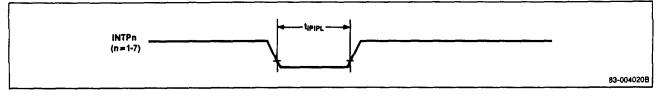

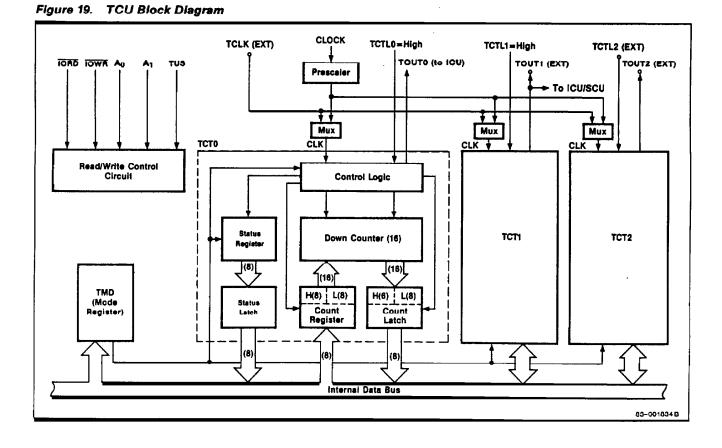

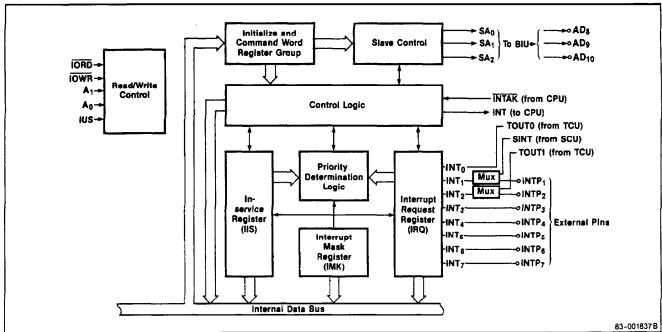

The V40 processor is a high-performance, low-power processor which incorporates a number of commonly used peripheral devices directly into the processor. The peripherals include

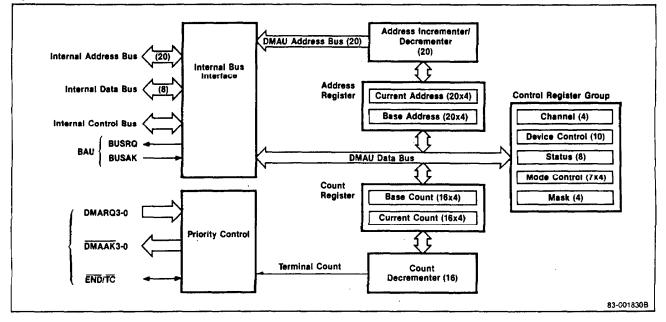

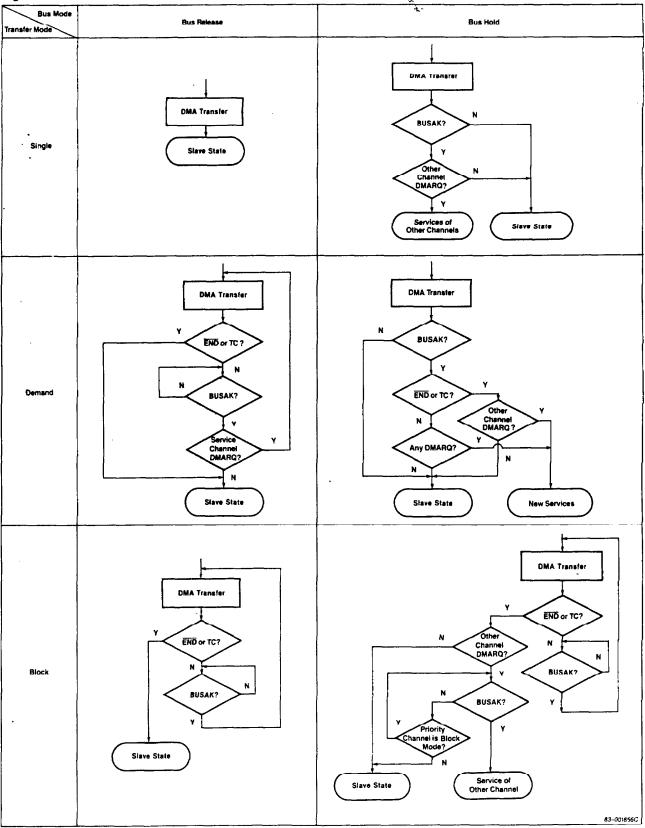

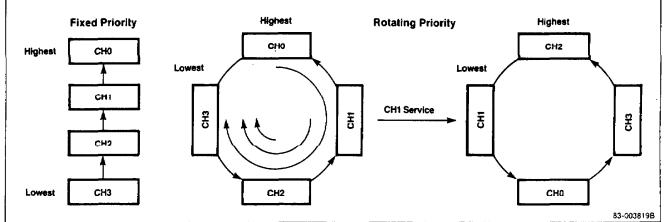

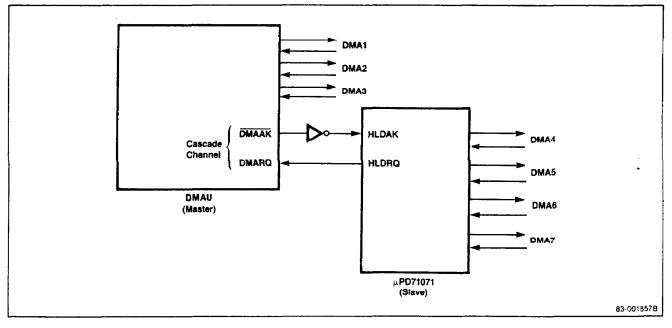

- 4 Channel 8-bit DMA controller

- Serial Communications Unit

- 8259 Compatible Interrupt Controller

- 8254 Compatible Timer/Counter

- DRAM Refresh control circuitry

- Programmable wait-state generator

The V40 CPU is fully object code compatible with the INTEL 8088 and provides hardware and instruction set enhancements for improved performance over the 8088. The SAT-V41 is easily programmed using MS-DOS based assemblers, compilers and development tools. Contact your WinSystems Application Engineer for details on available debugging and operating system options. Refer to the V40 Data Sheet reprint in the Appendix for complete information regarding the usage and programming of the V40's peripherals and features.

## 2.3 Memory Addressing

The V40 processor on the SAT-V41, like its INTEL counterparts, directly addresses 1 megabyte of memory using 20 address lines. The SAT-V40 adds an 8-bit paging register to allow accessing of up to 4 megabytes through 16K byte pages. The address bus to the memory array actually consists of 22 bits. The mapping of the individual JEDEC sockets is controlled by a PLD device at U24 and by three jumper positions on J22. The standard memory maps are shown in the following table. Note that accessing of any device at or above address 100000H must be done through the 16K page window.

| Memory<br>Map No. | J22<br>Jumpering  | U25                                             | U23                    | U21                                              | U17                        |

|-------------------|-------------------|-------------------------------------------------|------------------------|--------------------------------------------------|----------------------------|

| 0                 | 1-2<br>3-4<br>5-6 | 128K ROM<br>at 0E0000H                          | 32K RAM<br>at 000000H  | 32K ROM/RAM<br>at 008000H                        | 32K ROM/RAM<br>at 010000H  |

| 1                 | 3-4<br>5-6        | 256K ROM<br>at 0C0000H                          | 128K RAM<br>at 000000H | 128K ROM/RAM<br>at 020000H                       | 128K ROM/RAM<br>at 040000H |

| 2                 | 1-2<br>5-6        | 512K ROM<br>at 080000H                          | 512K RAM<br>at 000000H | 512K ROM/RAM<br>at 100000H                       | 512K ROM/RAM<br>at 180000H |

| 3                 | 5-6               | 64K ROM<br>at 0F0000H                           | 128K RAM<br>at 000000H | 512K ROM/RAM<br>at 100000H                       | 512K ROM/RAM<br>at 180000H |

| 4                 | 1-2<br>3-4        | 64K ROM<br>at 0F0000H                           | 512K RAM<br>at 000000H | 512K ROM/RAM<br>at 100000H                       | 512K ROM/RAM<br>at 180000H |

| 5                 | 3-4               | 64K ROM<br>at 0F0000H<br>512K ROM<br>at 100000H | 512K RAM<br>at 000000H | 512K ROM/RAM<br>at 200000H                       | 512K ROM/RAM<br>at 280000H |

| 6                 | 1-2               | 64K ROM<br>at 0F0000H<br>512K ROM<br>at 180000H | 512K RAM<br>at 000000H | 128K RAM<br>at 080000H<br>512K RAM<br>at 280000H | 512K ROM/RAM<br>at 100000H |

| 7                 | None              | 64K ROM<br>at 0F0000H<br>512K ROM<br>at 180000H | 512K RAM<br>at 000000H | 512K ROM/RAM<br>at 100000H                       | 512K ROM/RAM at<br>200000H |

### 2.4 Memory Map Selection

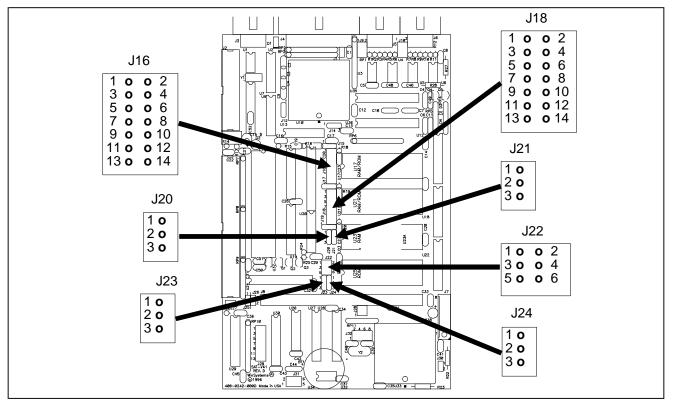

## 2.5 Memory Device Configuration

The 4 memory sockets U25, U23, U21 and U17 can be populated with standard PSRAM, SRAM, EPROM, and PEROM devices. Each socket must be configured for the actual type of device installed regardless of the memory map space allocated. A table of device types and jumpering for each socket is provided on the following page.

| Device<br>Type | U25 RO<br>J23 | M ONLY<br>J24 | U23 RA<br>J20 | M ONLY<br>J21 | U21<br>RAM/ROM<br>J18 | U17<br>RAM/ROM<br>J16 |

|----------------|---------------|---------------|---------------|---------------|-----------------------|-----------------------|

| 32K ROM        | OPEN          | 1-2           |               |               | 1-2 11-12             | 1-2 11-12             |

|                |               |               |               |               | 1-2 4-6               | 1-2 4-6               |

| 64K ROM        | 2-3           | 1-2           |               |               | 11-12                 | 11-12                 |

|                | 0.0           |               |               |               | 1-2 4-6               | 1-2 4-6               |

| 128K ROM       | 2-3           | OPEN          |               |               | 9-11                  | 9-11                  |

| 256K ROM       | 2-3           | 2-3           |               |               | 1-2 4-6               | 1-2 4-6               |

|                | 2-3           | 2-3           |               |               | 9-11 12-14            | 9-11 12-14            |

|                |               |               |               |               | 1-2 4-6               | 1-2 4-6               |

| 512K ROM       | 2-3           | 2-3           |               |               | 5-7 9-11              | 5-7 9-11              |

|                |               |               |               |               | 12-14                 | 12-14                 |

| 32K PEROM      |               |               |               |               | 1-3 2-4               | 1-3 2-4               |

|                |               |               |               |               | 11-12                 | 11-12                 |

| 128K PEROM     |               |               |               |               | 1-2 4-6               | 1-2 4-6               |

|                |               |               |               |               | 3-5                   | 3-5                   |

|                |               |               |               |               | 1-2 4-6               | 1-2 4-6               |

| 256K PEROM     |               |               |               |               | 3-5 8-9               | 3-5 8-9               |

|                |               |               |               |               | 12-14                 | 12-14                 |

|                |               |               |               |               | 1-2 4-6               | 1-2 4-6               |

| 512K PEROM     |               |               |               |               | 3-5 7-9               | 3-5 7-9               |

|                |               |               |               |               | 12-14                 | 12-14                 |

| 32K SRAM       |               |               | 1-2           | OPEN          | 1-3 2-4               | 1-3 2-4               |

|                |               |               |               |               | 11-12                 | 11-12                 |

| 128K SRAM      |               |               | 1-2           | OPEN          | 1-3 2-4               | 1-3 2-4               |

|                |               |               |               | 0. 2.1        | 5-6 11-12             | 5-6 11-12             |

| 256K SRAM      |               |               | 2-3           | OPEN          | 1-3 2-4               | 1-3 2-4               |

|                |               |               |               | <b>. .</b>    | 5-6 12-14             | 5-6 12-14             |

|                |               |               |               |               | 1-3 2-4               | 1-3 2-4               |

| 512K SRAM      |               |               | 2-3           | 2-3           | 5-6 7-9               | 5-6 7-9               |

|                |               |               |               |               | 12-14                 | 12-14                 |

|                |               |               |               |               | 1-3 2-4               | 1-3 2-4               |

| 128K PSRAM     |               |               | 1-2           | 1-2           | 5-6 9-10              | 5-6 9-10              |

|                |               |               |               |               | 11-12                 | 11-12                 |

|                |               |               |               |               | 1-3 2-4               | 1-3 2-4               |

| 512K PSRAM     |               |               | 2-3           | 2-3           | 5-6 7-9               | 5-67-9                |

|                |               |               |               |               | 12-14                 | 12-14                 |

**NOTE :** A jumper must be installed at J30 anytime a PSRAM is used in any of the sockets in order to enable REFRESH from the V40.

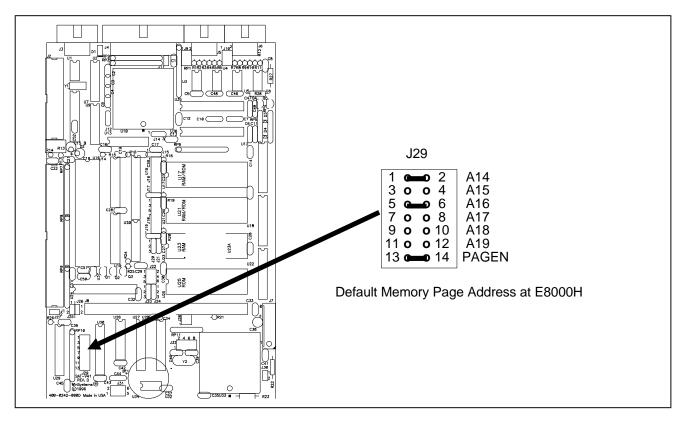

## 2.6 Memory Paging Configuration

The 16K window through which the 4 megabyte address space can be accessed is jumper addressable via jumper block J29. This jumper block sets the base address for the window. The normal setting for use with ROM-DOS and WinSystems RAM/ROM Disk drivers is at address E8000H as shown here.

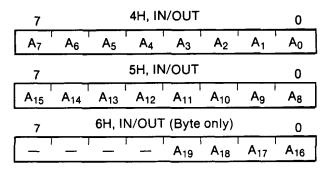

The memory page register is mapped at I/O port 1D0H and is write only. When a CPU memory access occurs that matches Address lines A19 through A14 as jumpered via J29, a translated address is generated by using the 8 bits from the page register to form Addresses A21 through A14 combining with the addresses A13 through A0 from the CPU. Access outside the 16K window are made using the CPU addresses A19 through A0 with addresses A20 through A21 always 0. The memory paging option is enabled by placing a jumper on J29 pins 13-14.

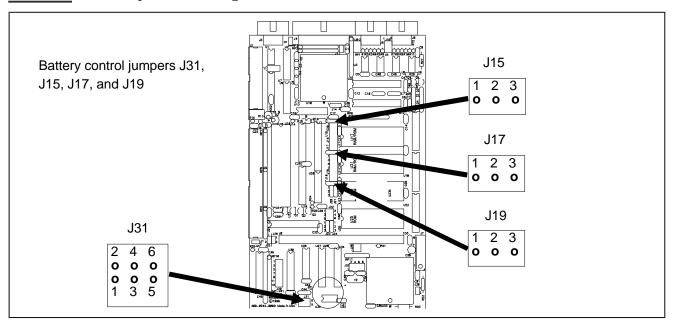

2.7 **Battery Select Options**

An optional on-board battery at BT1 provides for power-off backup of the selected RAM socket(s), and backup power for the DS-1202 Clock/Calendar/RAM. A master battery enable is provided via J31 pins 3-4. When jumpered, the battery power is provided to the supervisory circuit and is available to each of the SRAM battery select jumpers. The DS-1202 clock has a separate enable jumper on pins 1-2 of J31. RAM sockets U17, U21, and U23 each have a battery backup select jumper as J15, J17, and J19 respectively. If the jumper block pins 1-2 are connected, the installed device will receive battery power when the main power is removed. When pins 2-3 are jumpered, +5 volts from the power supply is provided to the sockets.

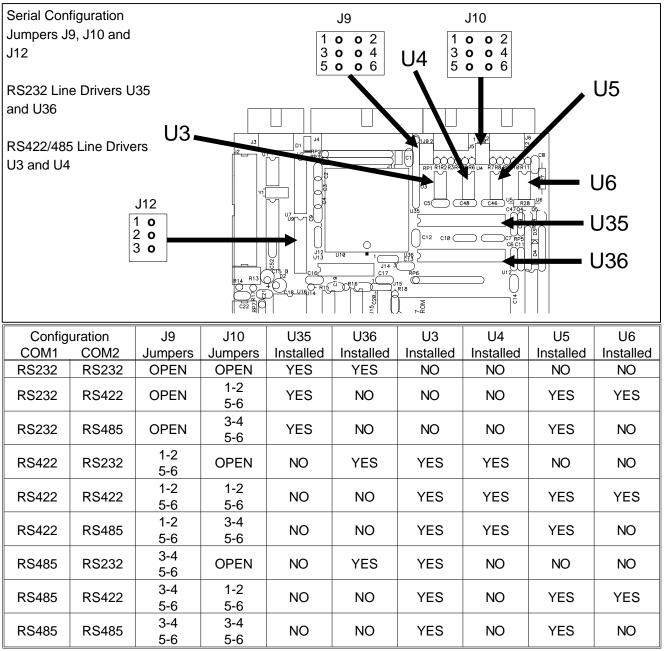

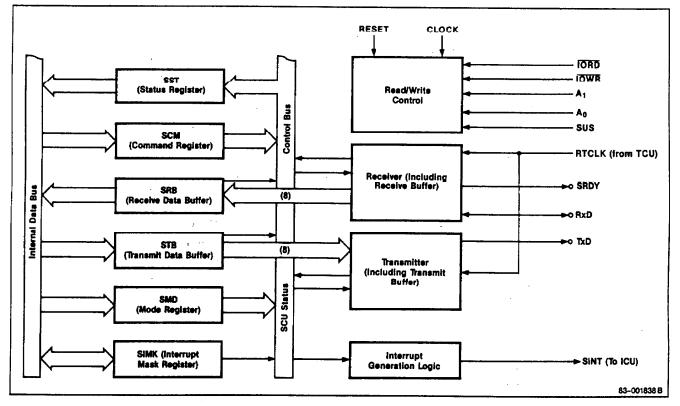

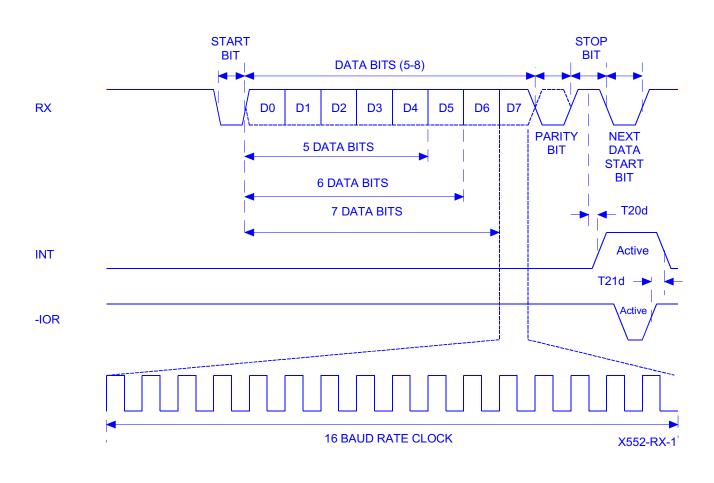

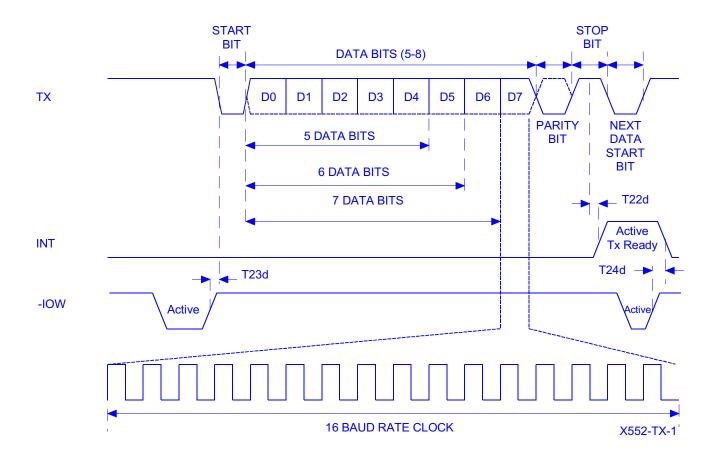

## 2.8 Serial Communications

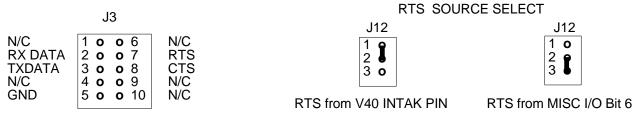

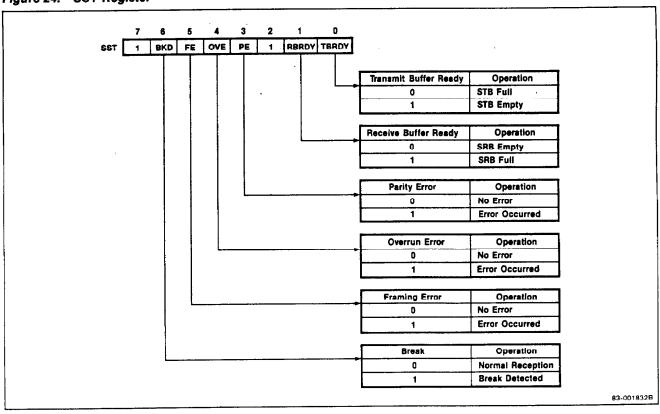

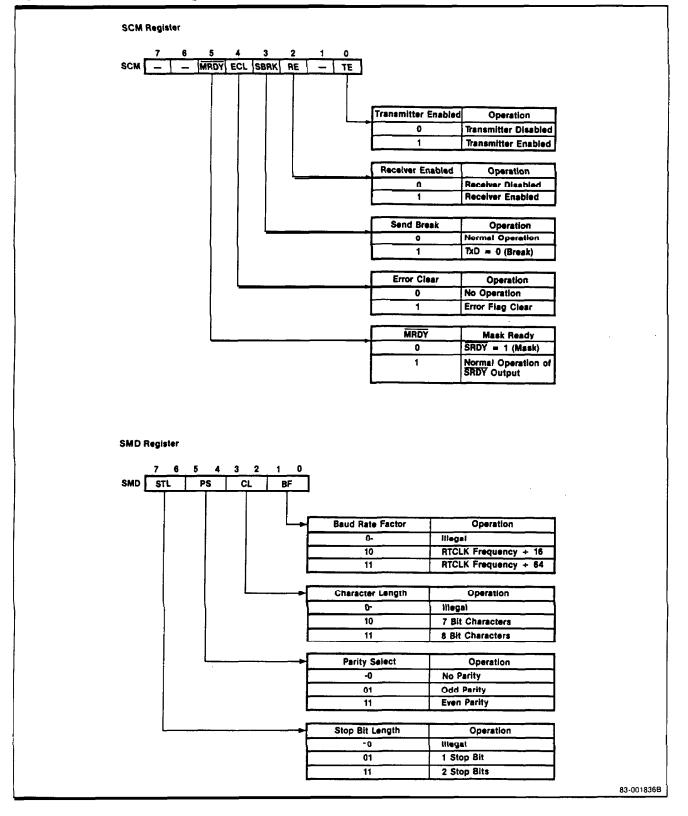

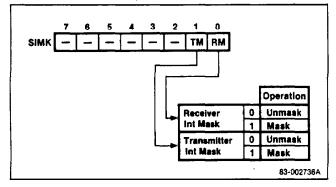

The SAT-V41 provides three serial channels, the V40 SCU and two 8250 compatible ports at PC compatible addresses of 3F8h and 2F8h terminated at J5 and J6 respectively.

The V40 Serial Communication Unit (SCU) is terminated at J3. The pinout of J3 is shown below. This serial port supports RS232 only and provides only CTS/RTS hand-shake support through auxiliary registers. Refer to APPENDIX D for programming details on the V40 SCU.

The 8250 compatible serial ports are mapped to PC compatible addresses of 3F8H for COM1 and 2F8H for COM2. Each of these ports may be individually configured for RS232, RS422, or RS485.

Optional chip kits part number CK-75176-2 are required in order to allow configuration of RS422 or RS485. One chip kit will allow one channel of RS422 or two channels of RS485. When configuring a channel for RS422 or RS485 it will be necessary to remove the RS232 line driver(s) at U35 and/or U36 as appropriate. Each of the configurations is documented below.

#### WinSystems "The Embedded Systems Authority"

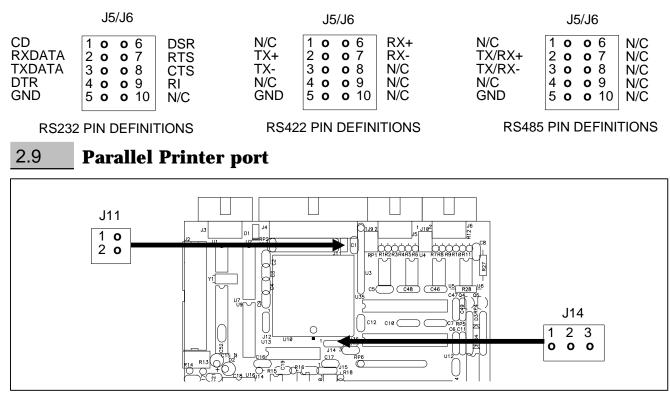

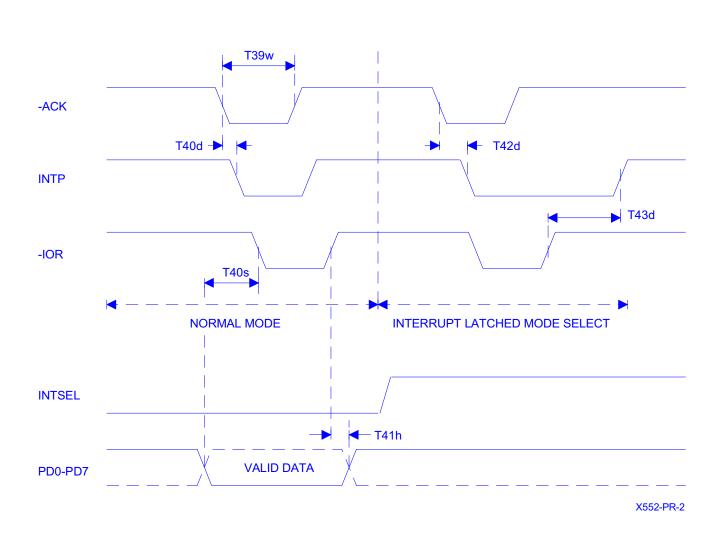

The SAT-V41 contains a PC compatible Centronics Parallel printer port terminated at J4. When used with cable CBL-122-1, standard PC printer cables can be connected to the SAT-V41. The pin definitions for J4 are shown below.

14

|                                                                                            | J4             |                                                          |                                                                                               |

|--------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| /STB<br>PD0<br>PD1<br>PD2<br>PD3<br>PD4<br>PD5<br>PD6<br>PD7<br>/ACK<br>BUSY<br>PE<br>SLCT | 3 0 0<br>4 0 0 | 15<br>16<br>17<br>18<br>20<br>21<br>22<br>23<br>24<br>25 | /AFD<br>/ERROR<br>/INIT<br>/SLIN<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>H5V / NC |

2.9.1 Bi-directional Data control

The 16C452 Serial/Parallel controller allows for a bi-directional printer port data bus. J14 allows selection of the method of control for the data port direction.

When selected for software direction control, bit 3 of the miscellaneous control register at I/O address 1D4H allows for dynamic direction control. When the bit is 0, the data port is configured for output, when set to 1, it is configured for input.

When the printer port is used as a general purpose I/O port, it may be desirable to provide power via the parallel printer I/O connector. Pin 26 of J4 can be used for this power feed by jumpering J11. Current consumption through this feed is not fused or otherwise limited on the board and it is the user's responsibility to assure adequate current limiting so as to avoid damage to the SAT-V41 board.

#### 125 20M J28 2 o o 4 1 o o 3 - الا ا -()R2 J31 4 6 2 0 ο 0 ©199 0 0 0 3 5

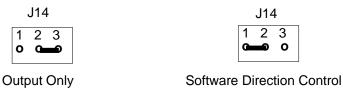

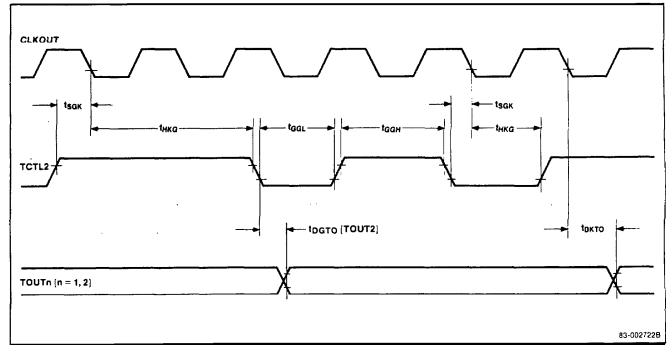

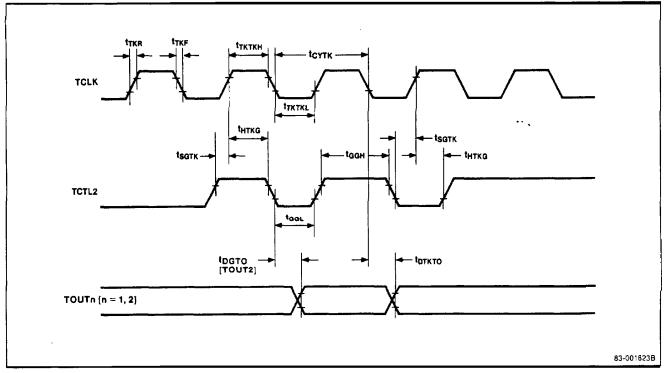

The V40 processor contains internally the equivalent of an 8254 type counter/ timer module with three separate channels. Each channel's source can be individually programmed as internal or external. External sources can be fed into J28 pin 1. A 1.19Mhz oscillator is provided on SAT-V41 boards running DOS to allow for software timing compatibility with PC hardware. Channel 0 of the counter is typically used as a periodic interrupt which is available at IRQ0 of the internal interrupt controller. Channel 1 is used as the baud rate generator for the V40 Serial Control Unit. Channel 2 is used for sound in standard PC architectures but is left available to the user on the SAT-V41. The available Output and control (gate) pins are terminated on J28. The pinout of J28 is shown below.

|               | J28     |       |  |

|---------------|---------|-------|--|

| 1.19 Mhz Osc. | 2 o o 4 | TCTL2 |  |

| TCLK Input    | 1 o o 3 | TOUT2 |  |

## 2.11 Watchdog Timer

The SAT-V41 utilizes the MAXIM 690 supervisory circuit which provides power on reset timing, power brown-out protection, battery back-up switching, and watchdog timer functions. The watchdog timer once enabled must be strobed at least once every 1.5 seconds or a reset will be asserted to the processor. This strobing or petting occurs by issuing an I/O write instruction to I/O port 1C8H. The data value written is irrelevant. In order to activate the watchdog timer, two steps are necessary. First the jumper at J31

2.10

**Counter/Timer I/O**

5-6 must be installed, and second, a write of 1 to I/O port 1C0H will start the timer. To disable the watchdog, write a 0 to I/O port 1C0H.

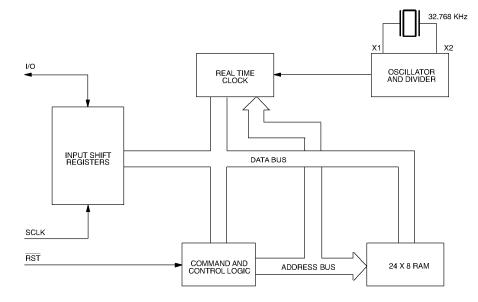

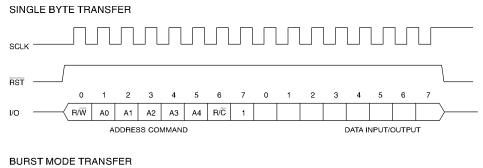

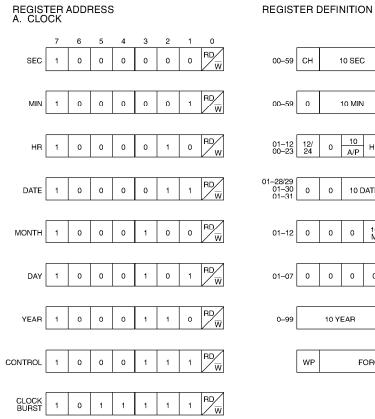

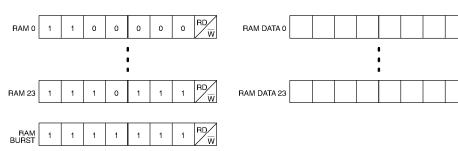

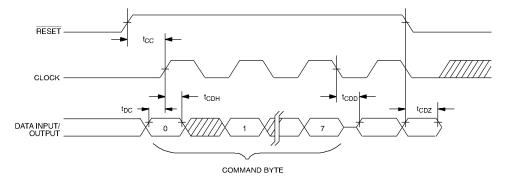

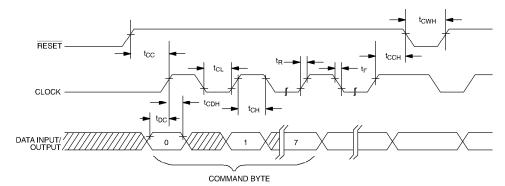

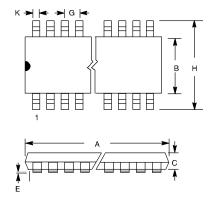

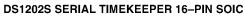

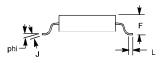

## 2.12 DS-1202 Clock/Calendar/RAM

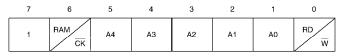

The SAT-V41 utilizes the Dallas Semiconductor DS-1202 Clock/Calendar/RAM IC for time and date keeping. Up to 24 bytes of configuration information may be stored in RAM within the clock chip. The DS-1202 is accessed in a serial fashion using bits in the miscellaneous I/O register at 1D4H. The complete bit definitions for this port I/O port are shown below.

| Bit | Write | Read  |

|-----|-------|-------|

| D7  | N/C   | CTS   |

| D6  | RTS   | RTS   |

| D5  | LED   | LED   |

| D4  | CKDIR | CKDIR |

| D3  | LPTOE | LPTOE |

| D2  | SELCT | SELCT |

| D1  | SHCLK | SHCLK |

| D0  | I/O   | I/O   |

|     |       |       |

D7 - Write no operation, Read for V40 SCU serial RTS input

D6 - Write/read for RTS on V40 SCU serial channel

D5 - Write/read 1= LED ON, 0 = LED OFF

- D4 Write/Read ,Clock Write = 0, Clock Read or Analog I/O = 1

- D3 Write/Read ,LPT Data output = 0, LPT Data input = 1

- D2 Write/Read, Device Select Clock = 1, Analog = 0

- D1 Write/Read ,Serial peripheral Shift Clock

- D0 Write/Read, Serial Peripheral Data

Refer to the Reprint of the DS-1202 Datasheet in Appendix G for complete details regarding programming and register/RAM implementation. The supplied "sample programs" diskette has sample clock/calendar, RAM, and A/D converter access routines written in 'C' that can be incorporated into the user's application program.

## 2.13 Interrupt routing

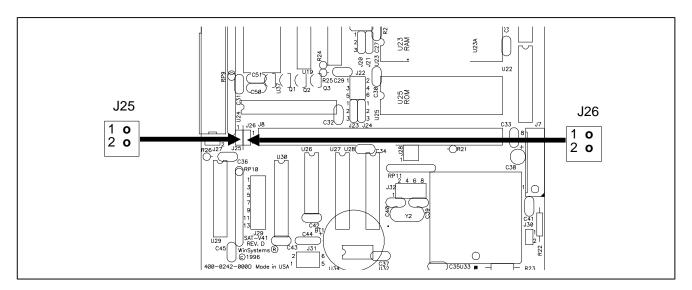

External interrupts to the V40 are provided via the PC/104 Expansion bus. (See PC/104 pinout in later section) All interrupts are rising edge active and unterminated on the bus. Two jumper blocks are provided to allow enabling and disabling of enhanced interrupt options. Jumpering J26 allows the PC/104 0WS (pin B8) line to be used as an input for IRQ1. This allows PC configured systems to use the standard interrupt for keyboard input which is normally not available on the PC/104 bus. This option would typically be jumpered only when used with the PCM-DSKIO, disk, keyboard, accessory module. The PC/104 bus defines pin A1 as a non-maskable interrupt (NMI). This input may be defeated by removing the jumper from J25.

## 2.14 Status LED

The SAT-V41 provides a status/diagnostic LED port which can be used by application software to signal activity, error or other user-defined functions. To illuminate the LED it is only necessary to set bit 5 of I/O port 1D4. Extinguishing of the LED is accomplished by clearing bit 5. The miscellaneous I/O port is read/write so the proper procedure to avoid changing outputs on other bits, is to read in the current value, set or clear bit 5 as desired and rewrite the value.

## 2.15 Analog Input

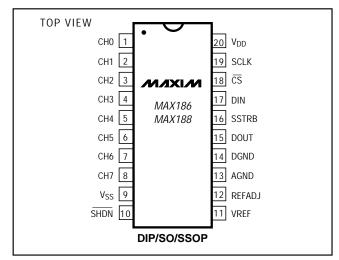

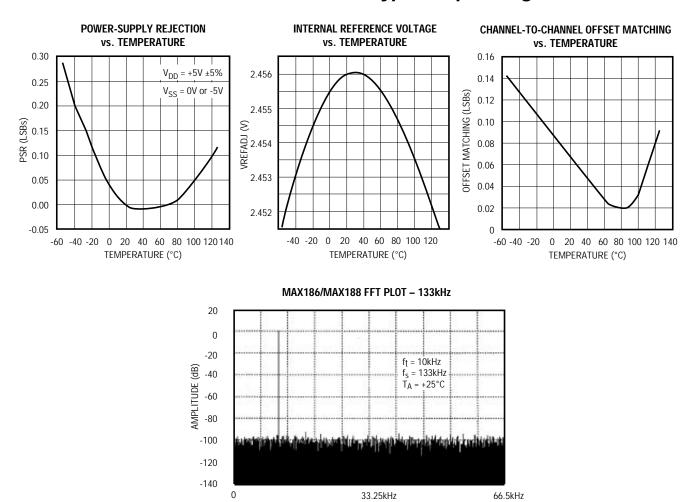

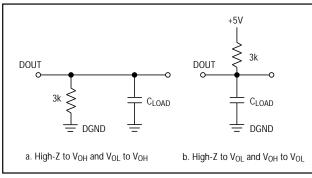

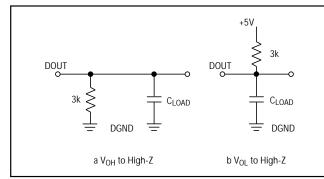

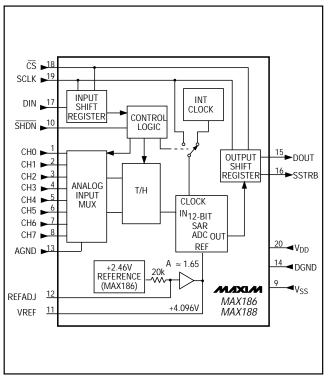

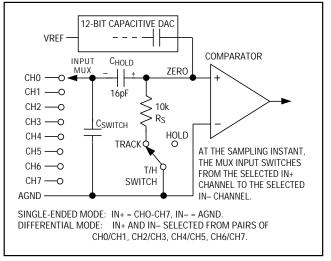

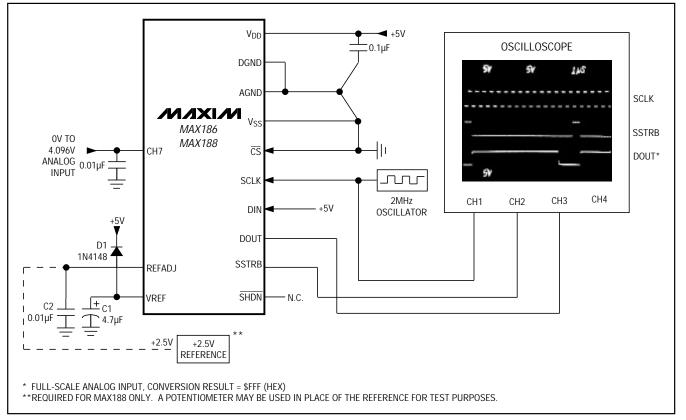

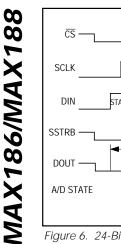

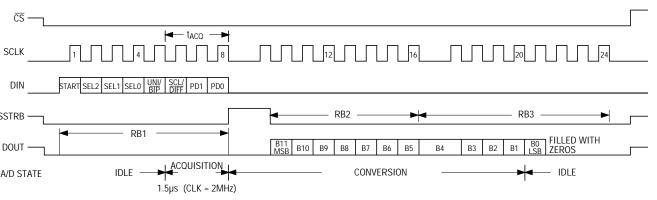

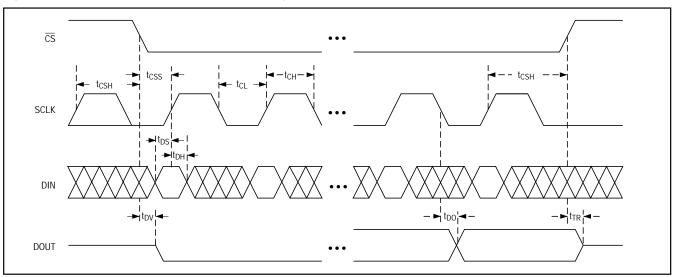

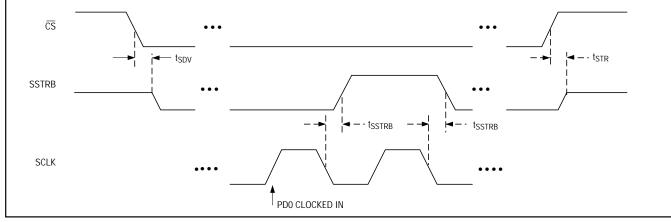

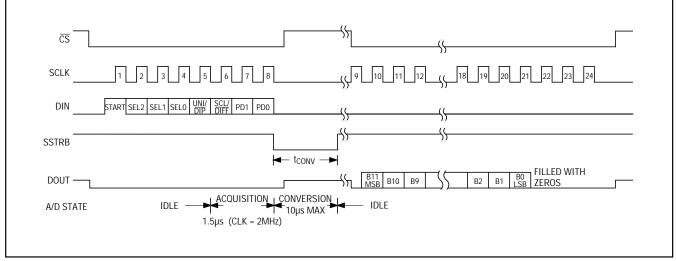

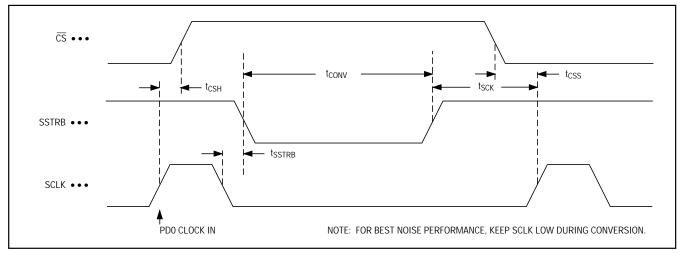

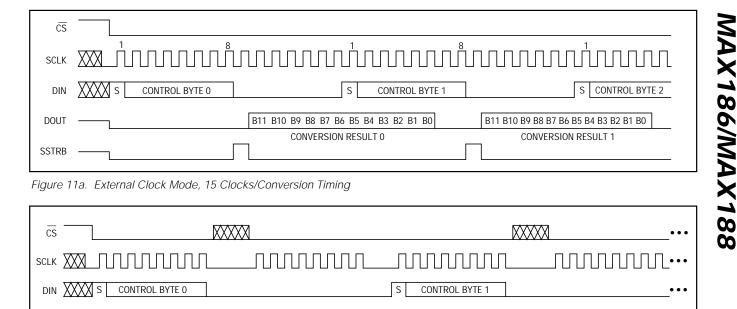

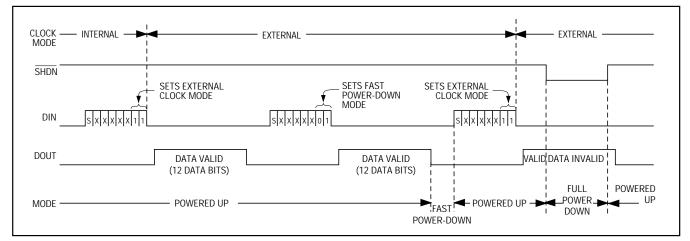

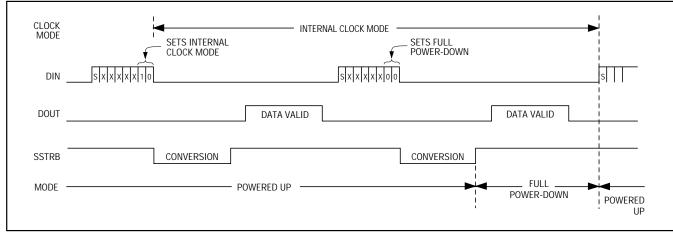

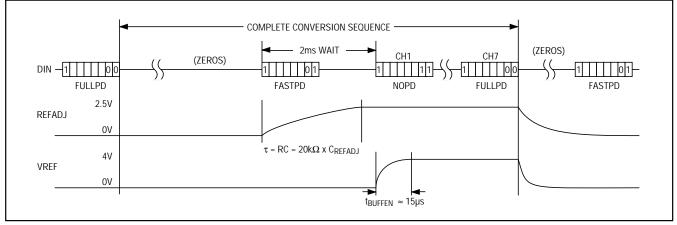

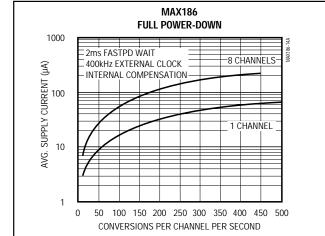

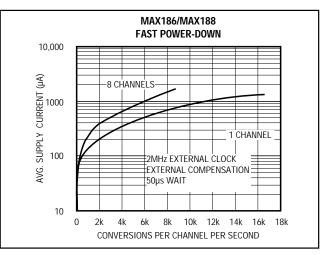

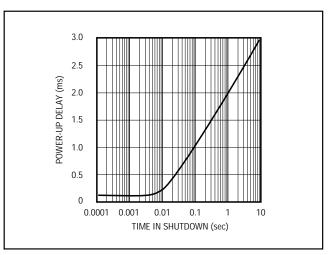

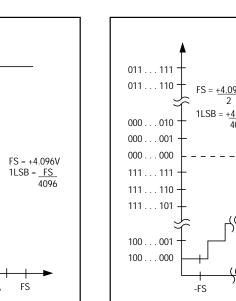

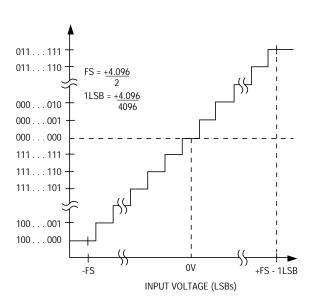

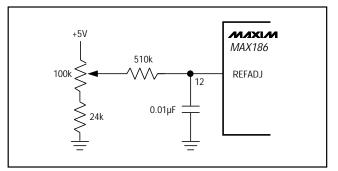

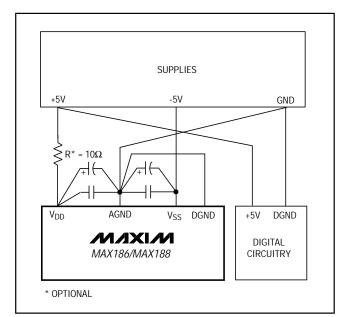

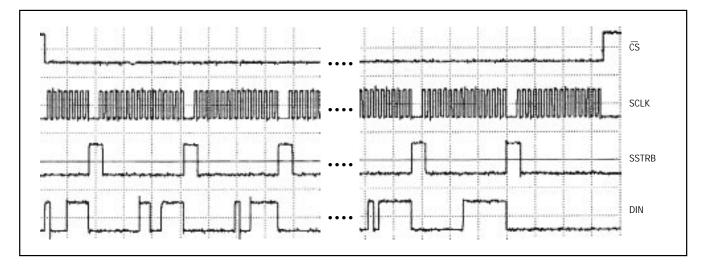

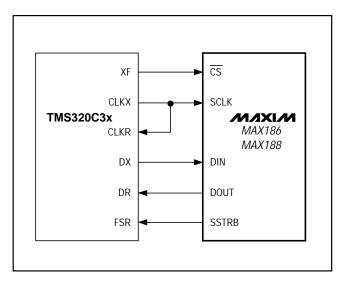

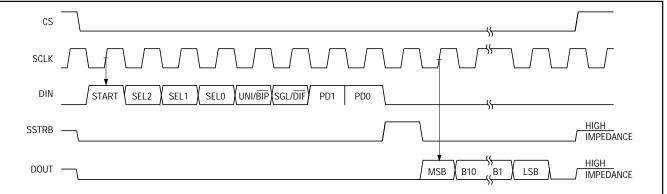

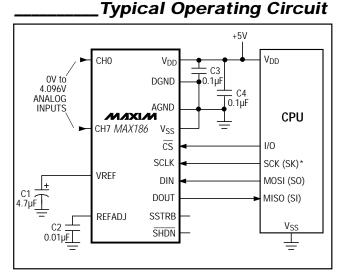

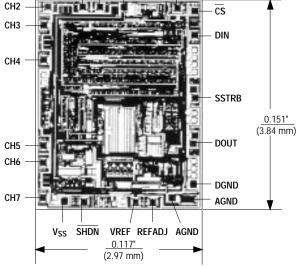

The SAT-V41 utilizes the MAX186 8-Channel Analog to Digital converter providing 12-bit resolution for a 0 to 4.096V input signal. An internal 1.7 Mhz conversion clock allows for a minimum 5.5 uS conversion time. The actual conversion throughput is highly dependent upon coding and has been demonstrated at between 2Khz and 500hz using assembly and C respectively. Each channel can be software configured for Unipolar and

Single-Ended/Differential operation. Refer to Appendix H for the MAXIM186 datasheet reprint for additional usage and programming details. The A/D converter is accessed serially through the Miscellaneous I/O register. The diagram below shows the analog input connector J2.

| J2                                                                                      |                                                      |                                                                                         |  |  |

|-----------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| CH0<br>CH1<br>GND<br>CH2<br>GND<br>CH3<br>GND<br>CH4<br>GND<br>CH5<br>GND<br>CH6<br>CH7 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | CH1<br>CH3<br>GND<br>CH5<br>GND<br>CH7<br>GND<br>N/C<br>GND<br>N/C<br>GND<br>N/C<br>N/C |  |  |

|                                                                                         |                                                      |                                                                                         |  |  |

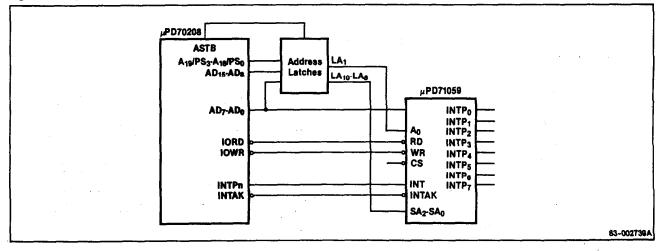

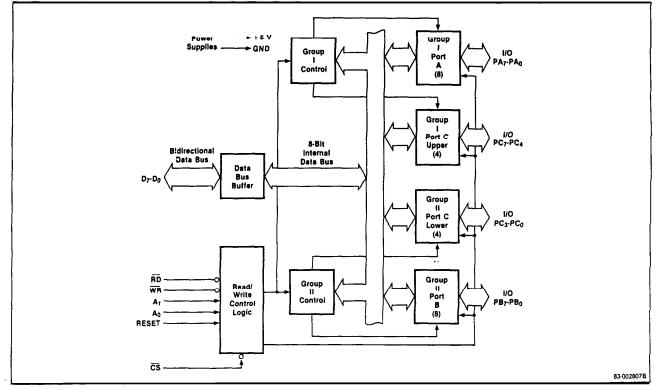

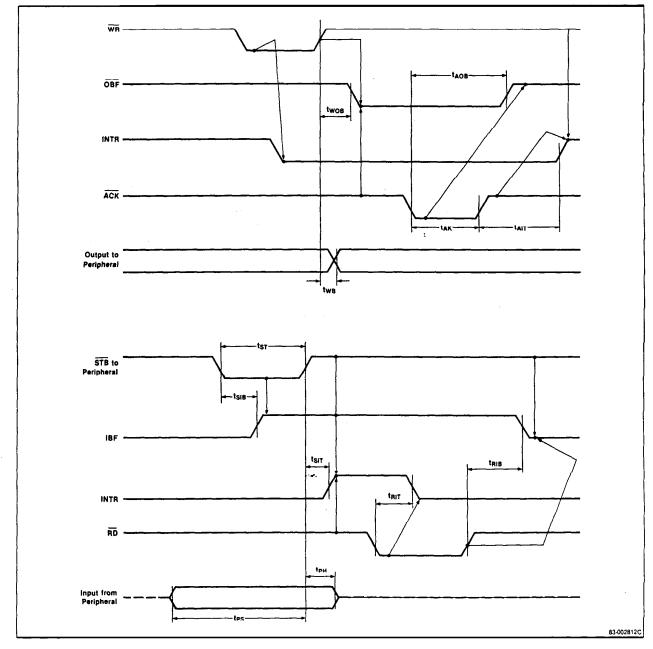

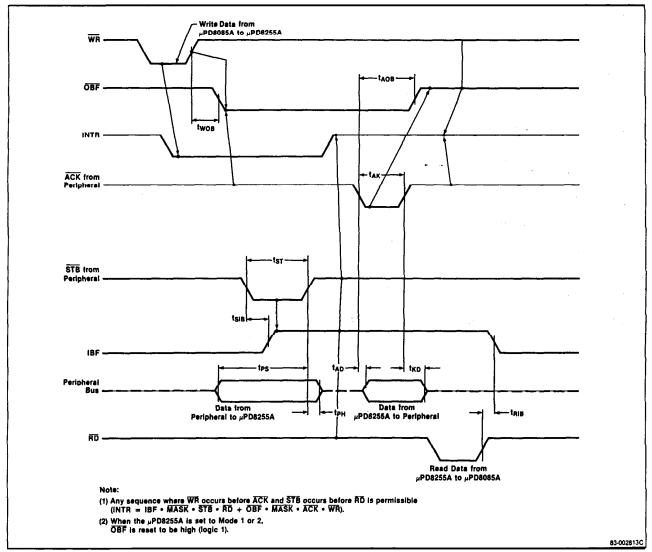

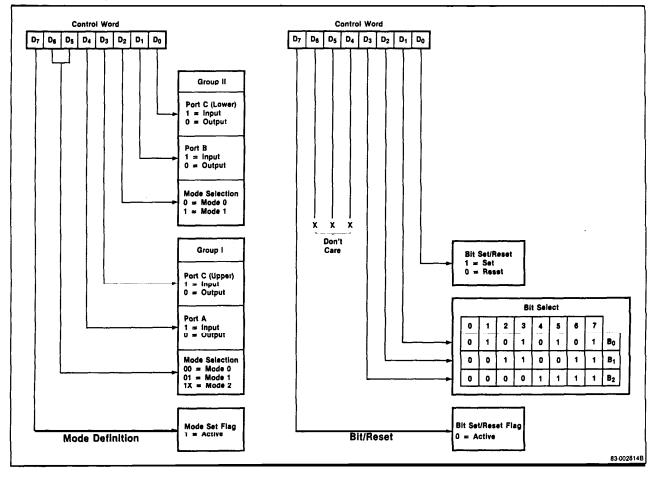

### 2.16 Parallel I/O

The SAT-V41 uses the NEC 71055 PIO chip (Intel 8255 compatible) to provide for 24 lines of digital I/O. Several modes are supported as documented in the 71055 datasheet reprint in Appendix F. The Base address of the chip is at 50H. The digital I/O is terminated at J1. The pinout of J1 is shown below :

| J1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      |                                                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|--|--|

| Port C bit 7<br>Port C bit 6<br>Port C bit 5<br>Port C bit 3<br>Port C bit 3<br>Port C bit 2<br>Port C bit 1<br>Port C bit 0<br>Port B bit 7<br>Port B bit 7<br>Port B bit 5<br>Port B bit 3<br>Port B bit 3<br>Port B bit 3<br>Port B bit 2<br>Port B bit 1<br>Port B bit 1<br>Port A bit 5<br>Port A bit 3<br>Port A bit 5<br>Port A bit 3<br>Port A bit 5<br>Port A bit 3<br>Port A bit 3<br>Port A bit 3<br>Port A bit 3<br>Port A bit 1<br>Port A bit 1<br>Port A bit 0<br>+5V/NC | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND |  |  |

Note that Pin 49 may be configured to supply + 5 volts to the I/O connector. This is accomplished by placing a jumper on J27. The current drawn from this pin should be 300 mA or less.

## 2.17 PC/104 Expansion Bus

The SAT-V41 provides for expansion through a single PC/104 8-Bit expansion connector at J8. PC/104 expansion modules are available from a number of vendors and include disk, network, digital, and analog I/O cards. The pin definitions for the PC/104 connector are shown here :

|                                                                                                                                                                                                                                                                                  | J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8                                                                                        |                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND<br>RESET<br>+5V<br>IRQ2<br>-5V<br>DRQ2<br>-12V<br>OWS<br>+12V<br>GND<br>MEMW<br>MEMR<br>IOW<br>IOR<br>DACK3<br>DRQ3<br>DACK1<br>DRQ1<br>DACK3<br>DACK1<br>DRQ1<br>DACK0<br>SYSCLK<br>IRQ7<br>IRQ6<br>IRQ5<br>IRQ4<br>IRQ3<br>DACK2<br>TC<br>BALE<br>+5V<br>OSC<br>GND<br>GND | B1 0<br>B2 0<br>B3 0<br>B4 0<br>B5 0<br>B7 0<br>B10 0<br>B11 0<br>B12 0<br>B11 0<br>B12 0<br>B12 0<br>B13 0<br>B14 0<br>B15 0<br>B14 0<br>B15 0<br>B17 0<br>B18 0<br>B17 0<br>B18 0<br>B22 0<br>B23 0<br>B22 0<br>B23 0<br>B22 0<br>B23 0<br>B22 0<br>B23 0<br>B23 0<br>B22 0<br>B23 0<br>B23 0<br>B20 0 | <ul> <li>A15</li> <li>A16</li> <li>A16</li> <li>A17</li> <li>A18</li> <li>A19</li> </ul> | IOCHK<br>BD7<br>BD6<br>BD5<br>BD4<br>BD3<br>BD2<br>BD1<br>BD0<br>IOCHRDY<br>AEN<br>SA19<br>SA18<br>SA17<br>SA16<br>SA15<br>SA14<br>SA13<br>SA12<br>SA11<br>SA10<br>SA9<br>SA8<br>SA7<br>SA6<br>SA5<br>SA4<br>SA3<br>SA2<br>SA1<br>SA0<br>GND |

## 2.18 **Power Input**

Power is supplied to the SAT-V41 through connector J7. A pre-wired harness cable CBL-174-1 is available to facilitate connection to the SAT-V41. The pin definitions for J7 are shown below.

| J                                    | 7                               |                                                    |

|--------------------------------------|---------------------------------|----------------------------------------------------|

| 8<br>7<br>6<br>5<br>4<br>3<br>2<br>1 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | -12V<br>+12V<br>+5V<br>GND<br>GND<br>GND<br>/RESET |

# 2.19 Connector/Jumper Summary

| <b>Connector/Jumper</b> | Description                      | Page Reference |

|-------------------------|----------------------------------|----------------|

| J1                      | Parallel I/O connector           | 2-12           |

| J2                      | Analog Input Connector           | 2-12           |

| J3                      | V40-SCU Connector                | 2-6            |

| J4                      | LPT1 Connector                   | 2-8            |

| J5                      | COMM1 I/O                        | 2-7            |

| J6                      | COMM2 I/O                        | 2-7            |

| J7                      | Power Connector                  | 2-13           |

| J8                      | PC/104 Bus Connector             | 2-13           |

| J9                      | COMM1 Serial Configuration       | 2-7            |

| J10                     | COMM2 Serial Configuration       | 2-7            |

| J11                     | LPT Port VCC Enable              | 2-8, 2-9       |

| J12                     | RTS Source Select V40 SCU        | 2-6, 2-7       |

| J13                     | COMM1/COMM2 RS232 Enable         | 2-7            |

| J14                     | LPT1 Direction Control           | 2-8            |

| J15                     | U17 VBAT/VCC Select              | 2-6            |

| J16                     | U17 Device Configuration Jumper  | 2-2, 2-4       |

| J17                     | U21 VBAT/VCC Select              | 2-6            |

| J18                     | U21 Device Configuration Jumper  | 2-2, 2-4       |

| J19                     | U23 VBAT/VCC Select              | 2-6            |

| J20                     | U23 Device size Select           | 2-4            |

| J21                     | U23 Device size Select           | 2-4            |

| J22                     | Memory Map Select                | 2-2, 2-3       |

| J23                     | U25 Device size Select           | 2-2, 2-4       |

| J24                     | U25 Device size Select           | 2-2, 2-4       |

| J25                     | NMI Enable                       | 2-11           |

| J26                     | IRQ1 to PC/104 Interrupt Routing | 2-11           |

| J27                     | Parallel I/O VCC enable          | 2-12           |

| J28                     | Counter/Timer config jumper      | 2-9            |

| J29                     | Memory page address select       | 2-5            |

| J30                     | Refresh enable jumper            | 2-4            |

| J31                     | VBAT/Watchdog timer control      | 2-6, 2-9       |

### SAT-V41 I/O Port Map

| I/O Address                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 050-053H<br>1C0-1C3H<br>1D0-1D3H<br>1D4-1D7H<br>1C8-1CBH<br>2F8-2FFh<br>378-37FH<br>3F8-3FF<br>FFF0H<br>FFF1H<br>FFF2H<br>FFF3h<br>FFF4H<br>FFF5H<br>FFF6H<br>FFF6H<br>FFF7H<br>FFF8H<br>FFF9H<br>FFFAH<br>FFFBH<br>FFFCH<br>FFFCH<br>FFFDH<br>FFFEH | 71055 PIO Chip<br>Watchdog Timer Enable<br>Memory Page Register<br>Misc. I/O Register<br>Watchdog Pet<br>COMM2<br>LPT1<br>COMM1<br>V40 TCKS Register<br>V40 Reserved<br>V40 RFC Register<br>V40 RFC Register<br>V40 RFC Register<br>V40 WMB Register<br>V40 WCY1 Register<br>V40 WCY1 Register<br>V40 WCY2 Register<br>V40 WCY2 Register<br>V40 SULA Register<br>V40 SULA Register<br>V40 IULA Register<br>V40 DULA Register<br>V40 OPHA Register<br>V40 OPSEL Register<br>V40 OPCN Register |

| FFFFH                                                                                                                                                                                                                                                | V40 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**NOTE :** All internal V40 peripherals are software located within the I/O space based on the content of the OPHA register and the indivdual placement registers i.e. DULA, TULA, SULA, IULA. Refer to the V40 datasheet for additional details.

This Page Intentionally Left Blank

SAT-V41 Parts List

This Page Intentionally Left Blank

| 12/09/98  |        |         |        |

|-----------|--------|---------|--------|

| 10:53:16  |        |         |        |

| BEGINNING | RANGE: | SAT-V41 | PA-8-0 |

|           |        |         |        |

ENDING RANGE: SAT-V41PA-8-0

| BEGINNING RANGE: SAT-V41PA-8-0 |                 |                                  | ENDING RANGE: SAT-V41PA-8-0          |        |                 |              |                |

|--------------------------------|-----------------|----------------------------------|--------------------------------------|--------|-----------------|--------------|----------------|

| EVEL :                         | ITEM KEY        | ITEM<br>DESCRIPTION              | BOM<br>DESCRIPTION                   | LOC    | OVHD I<br>KEY I | ITEM<br>TYPE | QTY<br>REQUIRE |

|                                |                 |                                  |                                      |        |                 |              | =              |

| 1 :                            | SAT-V41PA-8-0   | V40 SBC, 8 MHZ WITH PC BIOS & 12 | BIT A/D                              |        |                 |              | 1              |

| 2                              | 999-9999-001    | SPECIAL NOTES                    | 03-28-96 MEB (NEW)                   | ARLIN  |                 | Inv          | 1              |

| 2                              | 0242-101-0000   | ASSY SAT-V41PA-8 MHZ REV.D W/ANA | L                                    | ARLIN  |                 | Inv          | 1              |

| 3                              | >999-9999-001   | SPECIAL NOTES                    | 12-04-96 MEB ECO 96-95               | ARLIN  |                 | Inv          | 1              |

| 3                              | >999-9999-001   | SPECIAL NOTES                    | 03-28-96 MEB (NEW)                   | ARLIN  |                 | Inv          | 1              |

| 3                              | >110-0011-003   | CAP .1uF 50v 20% CER RAD .1      | C1-C5,C8,C9,C12-C14,C16,C17,C19,C20, | ARLIN  |                 | Inv          | 33             |

| 3                              | >999-9999-001   | SPECIAL NOTES                    | C23-C37,C41-C43,C45                  | ARLIN  |                 | Inv          | 1              |

| 3                              | >110-0012-003   | CAP 1uF 50v 20% CER RAD .2       | C6,C7,C10,C11,C46-C49                | ARLIN  |                 | Inv          | 8              |

| 3                              | >110-0014-005   | CAP 10uF 25v 10% TAN RAD .1      | C15                                  | ARLIN  |                 | Inv          | 1              |

| 3                              | >110-0036-003   | CAP .01uF 50v 20% CER .2 (4500)  | C44                                  | ARLIN  |                 | Inv          | 1              |

| 3                              | >110-0044-005   | CAP 22uF 10v 10% TAN RAD .1      | C38                                  | ARLIN  |                 | Inv          | 1              |

| 3                              | >114-0102-450   | RESISTOR 1K 1/4 5%               | R18-R21,R23                          | ARLIN  |                 | Inv          | 5              |

| 3                              | >114-0103-450   | RESISTOR 10K 1/4 5%, CR25 10k 5% | R16,R24-26                           | ARLIN  |                 | Inv          | 4              |

| 3                              | >114-0331-450   | RESISTOR 330 OHM 1/4 5%          | R22                                  | ARLIN  |                 | Inv          | 1              |

| 3                              | >114-0471-450   | RESISTOR 470 OHM 1/4 5%          | R15                                  | ARLIN  |                 | Inv          | 1              |

| 3                              | >114-0472-450   | RESISTOR CF 4.7K 1/4W 5%         | R27,R28                              | ARLIN  |                 | Inv          | 2              |

| 3                              | >115-0103-050   | RN SIP 6P-5 RES 10K (BKMN)L061S1 | RP4, RP5, RP11                       | ARLIN  |                 | Inv          | 1              |

| 3                              | >117-0103-050   | RN SIP 10P-9 RES 10K L101S103 (E | 8 RP1-RP3, RP6-RP8, RP10             | ARLIN  |                 | Inv          | -              |

| 3                              | >116-0103-050   | RN SIP 8P-7 RES 10K (BI)L8-1S-10 | RP9                                  | ARLIN  |                 | Inv          | 1              |

| 3                              | >124-0016-000   | LED RED RECTANGLE L-153HDT (KNGE | 3 D1                                 | ARLIN  |                 | Inv          | -              |

| 3                              | >124-0004-000   | DIODE 1N4148                     | D3,D4                                | ARLIN  |                 | Inv          | :              |

| 3                              | >125-0003-000   | TRANSISTOR VN2222LL (TO92)/ VN10 | Q1-Q3                                | ARLIN  |                 | Inv          | :              |

| 3                              | >125-0001-000   | TRANSISTOR PN2222 (TO92)         | Q4,Q5                                | ARLIN  |                 | Inv          | 1              |

| 3                              | >200-0064-000   | SOCKET 64 POS QPHF2-64-020-1W (P | J8                                   | ARLIN  |                 | Inv          | 1              |

| 3                              | >200-0083-100   | SOCKET 8 PIN ICO-083-S8A-T (4488 | U3-U6                                | ARLIN  |                 | Inv          | 4              |

| 3                              | >200-0163-100   | SOCKET 16 PIN ICO-163-S8A-T (220 | U2                                   | ARLIN  |                 | Inv          | 1              |

| 3                              | >200-0243-100   | SOCKET 24 P .3 ICO-243-S8A-T (14 |                                      | ARLIN  |                 | Inv          | 4              |

| 3                              | >200-0326-100   | SOCKET 32 P .6 ICO-326-S8A-T (72 | U17,U21,U23,U25                      | ARLIN  |                 | Inv          | 4              |

| 3                              | >200-0406-100   | SOCKET 40 P .6 ICO-406-S8A-T (60 | U16                                  | ARLIN  |                 | Inv          |                |

| 3                              | >201-0008-601   | HDR 8 POS MOLEX 22-11-2082       | J7                                   | ARLIN  |                 | Inv          |                |

| 3                              | >201-0010-121   | HDR 2X5 RA PRO IDH-10LP-SR3-TR/I | J3,J5,J6                             | ARLIN  |                 | Inv          |                |

| 3                              | >201-0026-121   | HDR 26 P RA IDH-26LP-SR3-TG/TR ( | J4                                   | ARLIN  |                 | Inv          | -              |

| 3                              | >201-0036-010   | HDR 1X36 UN TSW-136-07-G-S (SAM) | J11,J25-J27,J30=1X2 J12,J14,J15,J17, | ARLIN  |                 | Inv          | 1.02           |

| 3                              | >999-9999-001   | SPECIAL NOTES                    | J19-J21,J23,J24=1X3                  | ARLIN  |                 | Inv          |                |

| 3                              | >201-0050-021   | HDR 2X25 ST PRO IDH50LP-S3-TG/TR | . J1                                 | ARLIN  |                 | Inv          |                |

| 3                              | >201-0072-120   | HDR 2X36 UN TSW-136-07-G-D       | J13,J28=2X2 J9,J10,J22,J31=2X3       | ARLIN  |                 | Inv          | 1.02           |

| 3                              | >999-9999-001   | SPECIAL NOTES                    | J16,J18,J29=2X7                      | ARLIN  |                 | Inv          | -              |

| 3                              | >220-0056-000   | XTAL R26-32.768KHz-6pF (RALTRON) |                                      | ARLIN  |                 | Inv          | -              |

| 3                              | >220-0032-001   | XTAL-14.31818 (ABRACON) ABL-14.3 |                                      | ARLIN  |                 | Inv          |                |

| 3                              | >220-0000-000   | HC49 INSULATOR XTAL              | PLACE UNDER Y2                       | ARLIN  |                 | Inv          |                |

| 3                              | >230-0068-150   | SOCKET PLCCE-068-S1-TT (16) (RN) |                                      | ARLIN  |                 | Inv          |                |

| 3                              | >730-0072-000   | IC, DS1202                       | U1                                   | ARLIN  |                 | Inv          |                |

| 3                              | >741-0004-200   | IC, 74HC04                       | U13                                  | ARLIN  |                 | Inv          |                |

| 3                              | >741-0032-200   | IC, 74HC32                       | U20                                  | ARLIN  |                 | Inv          |                |

| 3                              | >741-0075-200   | IC, 74HC75                       | U26                                  | ARLIN  |                 | Inv          |                |

| 3                              | >741-0125-200   | IC, 74HC125                      | U9                                   | ARLIN  |                 | Inv          |                |

| 3                              | >741-0244-200   | IC, 74HC244                      | U12,U19,U27,U28                      | ARLIN  |                 | Inv          |                |

| 3                              | >741-0273-200   | IC, 74HC273                      | U14                                  | ARLIN  |                 | Inv          |                |

| 3                              | >741-0374-200   | IC, 74HC374                      | U18                                  | ARLIN  |                 | Inv          |                |

| 3                              | >741-0373-200   | IC, 74HC373                      | U22                                  | ARLIN  |                 | Inv          |                |

| 3                              | >741-0688-200   | IC, 74HC878                      | U29                                  | ARLIN  |                 | Inv          | -              |

| 3                              | >745-0245-200   | IC, 74HCT245                     | U30                                  | ARLIN  |                 | Inv          | 1              |

| 5                              | . , 15 0215 200 | 10, / 1101215                    |                                      | 111111 |                 | T11 A        |                |

This Page Intentionally Left Blank

ENDING RANGE: SAT-V41PA-8-0

| SEGINNING RANCE: SAT-V41PA-8-0 |                |                                  | ENDING RANGE: SAT-V41PA-8-0            |       |                       |                |

|--------------------------------|----------------|----------------------------------|----------------------------------------|-------|-----------------------|----------------|

| EVEL                           | ITEM KEY       | ITEM<br>DESCRIPTION              | BOM<br>DESCRIPTION                     | LOC   | OVHD ITEM<br>KEY TYPE | QTY<br>REQUIRE |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | MASK HOLES FOR R1-R12                  | ARLIN | Inv                   | 1              |

| 3                              | >730-0029-000  | IC, MAX 690CPA (MAX690CPA ONLY)  | U34                                    | ARLIN | Inv                   | 1              |

| 3                              | >622-0001-002  | IC, ICS2694 M-004 (31)           | U32                                    | ARLIN | Inv                   | 1              |

| 3                              | >400-0242-000D | PCB, SAT-V41 REV.D               |                                        | ARLIN | Inv                   | 1              |

| 3                              | >200-0203-100  | SOCKET 20 PIN ICO-203-S8A-T (176 | 17                                     | ARLIN | Inv                   | 1              |

| 3                              | >201-0026-021  | HDR 26 PIN ST IDH-26LP-S3-TG/TR  |                                        | ARLIN | Inv                   | 1              |

| 3                              | >124-0004-000  | DIODE 1N4148                     | D2                                     | ARLIN | Inv                   | 1              |

| 3                              | >114-0514-450  | RESISTOR 510K 1/4 W 5%           | R17                                    | ARLIN | Inv                   | 1              |

| 3                              | >114-0243-450  | RESISTOR 24K 1/4 W 5%            | R14                                    | ARLIN | Inv                   | 1              |

| 3                              | >113-0104-102  | POT 100K (BI) 64WR100K RJ26FW104 |                                        | ARLIN | Inv                   | 1              |

| 3                              | >110-0014-005  | CAP 10uF 25v 10% TAN RAD .1      | C18                                    | ARLIN | Inv                   | 1              |

| 3                              | >110-0011-003  | CAP .1uF 50v 20% CER RAD .1      | C21,C22                                | ARLIN | Inv                   | 2              |

| 2                              | 0242-401-0000  | SUB ASSY SAT-V41A-8 MHZ REV.D    | 021,022                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | 10-29-98 MEB (-5S)                     | ARLIN | Inv                   | 1              |

| 3                              | >111-0001-000  | BAT 3V LI COIN CR2032-H04 (SONY) |                                        | ARLIN | Inv                   | 1              |

| 3                              | >901-0012-000  | IC, 27C512-15 CER EPROM          | U25 CS=ABD9 BIOS                       | ARLIN | Inv                   | 1              |

| 3                              | >743-0005-100  | IC, MAX232CPE, SP232ACP, DS232A- |                                        | ARLIN | Inv                   | 1              |

| 3                              | >801-0045-200  | IC, D70208L-8 V40 CPU CMOS (NEC) |                                        | ARLIN | Inv                   | 1              |

| 3                              | >730-0031-000  | IC, SP238ACS, ADM238LJN, MAX238C |                                        | ARLIN | Inv                   | 2              |

| 3                              | >801-0060-200  | IC, ST16C452CJ68 (AT) (STARTECH) |                                        | ARLIN | Inv                   | 1              |

| 3                              | >901-0011-000  | IC, PALC22V10-35PC (15,TI) (17,C |                                        | ARLIN | Inv                   | 2              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | U24 CS=F78F                            | ARLIN | Inv                   | 1              |

| 3                              | >801-0031-200  | IC, uPD71055C PROG PAR INTERFACE |                                        | ARLIN | Inv                   | 1              |

| 3                              | >500-0027-002  | INSULATOR SAT BATTERY PROTECT    | * PUT IN OPEN BAG LOOSE UNTIL SHIPPING |       | Inv                   | 1              |

| 3                              | >201-0002-000  | PLUG JUMPER 999-19-310-00        | JUMPERS TO TEST 'PC' VERSION SAT-V40   | ARLIN | Inv                   | 29             |

| 3                              | >999-9999-001  |                                  | J14=1-2                                | ARLIN | Inv                   | 29             |

| 3                              |                | SPECIAL NOTES                    |                                        |       |                       | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J15=1-2                                | ARLIN | Inv                   | 1              |

|                                | >999-9999-001  | SPECIAL NOTES                    | J16=1-3 2-4 5-6 11-12                  | ARLIN | Inv                   |                |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J17=2-3                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J18=1-2 4-6 5-7 9-11 12-14             | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J19=2-3                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J20=2-3                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J21=2-3                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J22=1-2 3-4                            | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J23=2-3                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J24=1-2                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J28=1-2 ***VERTICAL (LIKE J31)***      | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J29=1-2 5-6 13-14                      | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J30=1-2                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J31=1-2 3-4 5-6                        | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J9=OPEN                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J10=OPEN                               | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J11=OPEN                               | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J12=OPEN                               | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J25=1-2                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J26=1-2                                | ARLIN | Inv                   | 1              |

| 3                              | >999-9999-001  | SPECIAL NOTES                    | J27=OPEN                               | ARLIN | Inv                   | 1              |

| 3                              | >730-0073-000  | IC, MAX186DCPP {18}              | υ7                                     | ARLIN | Inv                   | 1              |

| 2                              | 910-0024-000   | LABEL, STATIC SENSITIVE 130-02   | LABEL, STATIC SENSITIVE 130-02         | ARLIN | Inv                   | 1              |

|                                | 950-0002-000   | BAG PINK POLY 6X10 6 MIL 09-0610 |                                        | ARLIN | Inv                   | 1              |

This Page Intentionally Left Blank

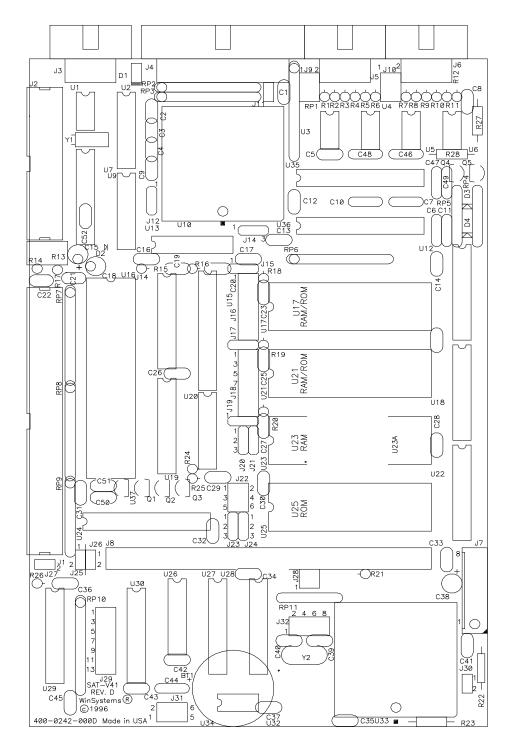

#### SAT-V41 Parts Placement Guide

This Page Intentionally Left Blank

NEC V40 Datasheet Reprint

This Page Intentionally Left Blank

#### µPD70208 (V40™) 8/16-BIT, HIGH-INTEGRATION CMOS MICROPROCESSOR

## PRELIMINARY INFORMATION

#### Description

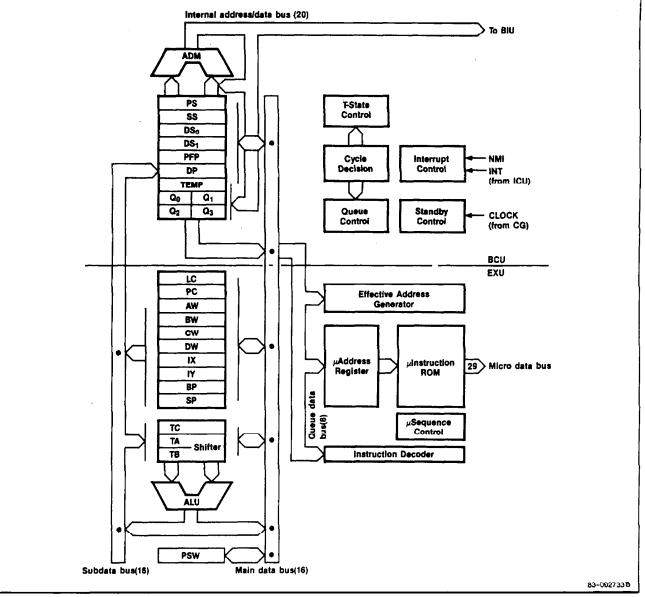

The  $\mu$ PD70208 (V40<sup>TM</sup>) is a high-performance, lowpower 16-bit microprocessor integrating a number of commonly used peripherals to dramatically reduce the size of microprocessor systems. The CMOS construction makes the  $\mu$ PD70208 ideal for the design of portable computers, instrumentation, and process control equipment.

The  $\mu$ PD70208 contains a powerful instruction set that is compatible with the  $\mu$ PD70108/ $\mu$ PD70116 (V20<sup>TM</sup>/ V30<sup>TM</sup>) and  $\mu$ PD8086/ $\mu$ PD8088 instruction sets. Instruction set support includes a wide range of arithmetic, logical, and control operations as well as bit manipulation, BCD arithmetic, and high-speed block transfer instructions. The  $\mu$ PD70208 can also execute the entire  $\mu$ PD8080AF instruction set using the 8080 emulation mode. Also available is the  $\mu$ PD70216 (V50<sup>TM</sup>), identical to the  $\mu$ PD70208 but with a 16-bit external data bus.

#### **Features**

- □ V20/V30 instruction set compatible

- □ Minimum instruction execution time: 250 ns (at 8 MHz)

- Direct addressing of 1M bytes of memory

- D Powerful set of addressing modes

- □ 14 16-bit registers

- On-chip peripherals including

- Clock generator

- Bus interface

- Bus arbitration

- Programmable wait state generator

- DRAM refresh control

- Three 16-bit timer/counters

- Asynchronous serial I/O control

- Eight-input interrupt control

- Four-channel DMA control

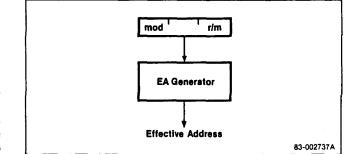

- □ Hardware effective address calculation logic

- Maskable and nonmaskable interrupts

- □ µPD72191 Floating Point Processor interface

- □ IEEE 796 compatible bus interface

- □ Low-power standby mode

- □ Low-power CMOS technology

V20, V30, V40, and V50 are trademarks of NEC Corporation.

#### **Ordering Information**

| Part Number | Package                 | Maximum Frequency |

|-------------|-------------------------|-------------------|

| µPD70208R-8 | 68-pin PGA              | 8 MHz             |

| µPD70208L-8 | 68-pin PLCC             | 8 MHz             |

| μPD70208G-8 | 80-pin plastic miniflat | 8 MHz             |

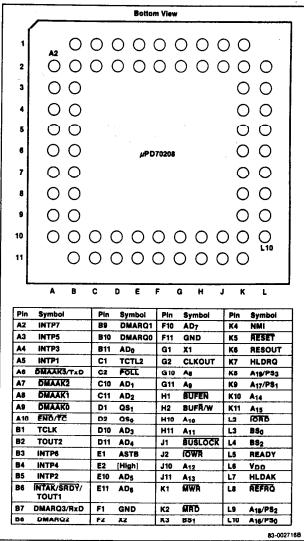

#### **Pin Configurations**

### μPD70208 (V40)

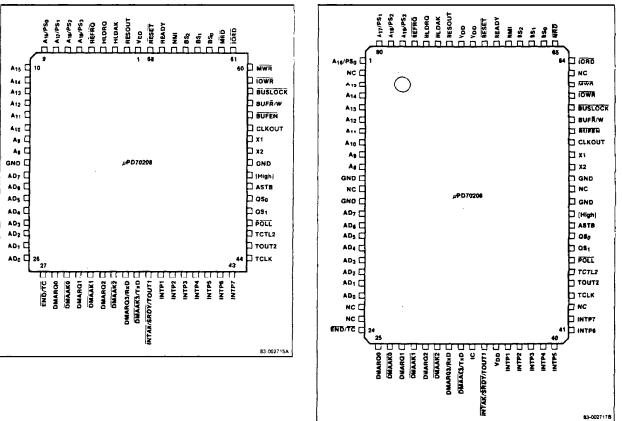

#### **Pin Configurations (cont)**

80-Pin Plastic Miniflat

## **Pin Identification**

| Symbol                           | Function                                                                                             |  |  |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A19-A16/PS3-PS0                  | Multiplexed address/processor status outputs                                                         |  |  |  |  |  |

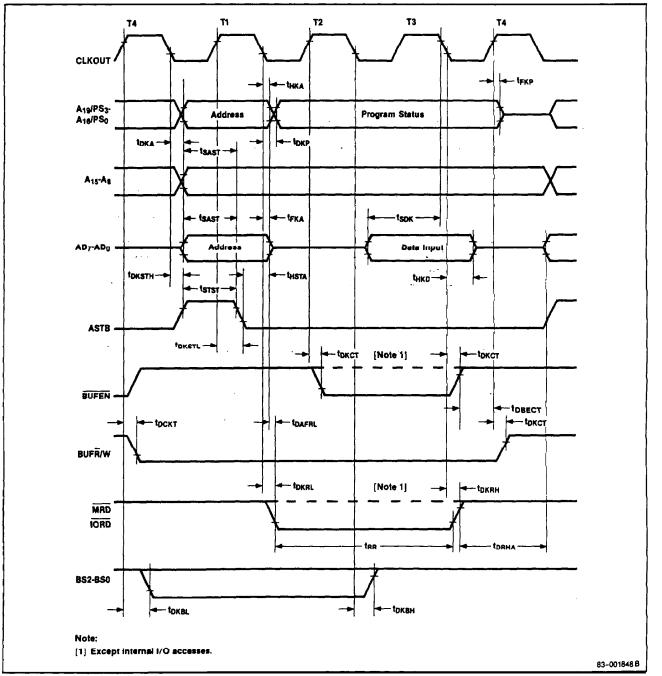

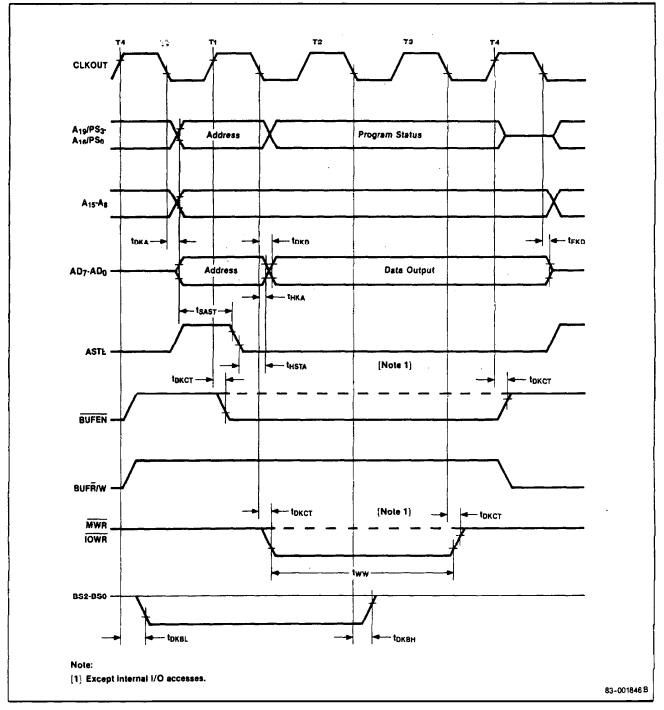

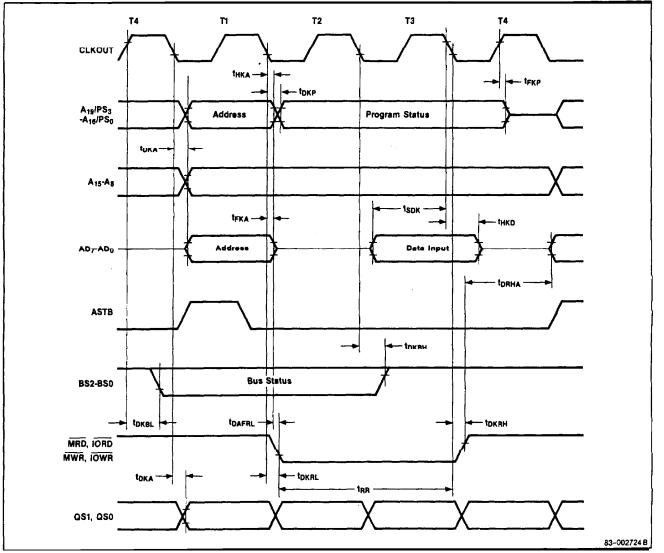

| A <sub>15</sub> -A <sub>8</sub>  | Address bus outputs                                                                                  |  |  |  |  |  |

| AD7-AD0                          | Multiplexed address/data bus                                                                         |  |  |  |  |  |

| ASTB                             | Address strobe output                                                                                |  |  |  |  |  |

| BUFEN                            | Data bus transceiver enable output                                                                   |  |  |  |  |  |

| BUFR/W                           | Data bus transceiver direction output                                                                |  |  |  |  |  |

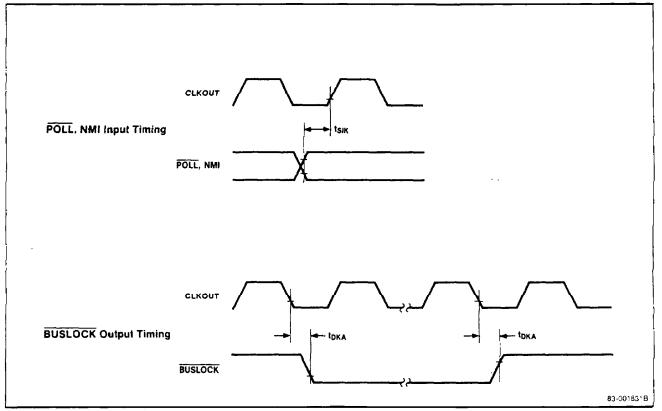

| BUSLOCK                          | Buslock output                                                                                       |  |  |  |  |  |

| BS <sub>2</sub> -BS <sub>0</sub> | Bus status outputs                                                                                   |  |  |  |  |  |

| CLKOUT                           | System clock output                                                                                  |  |  |  |  |  |

| DMAAKO                           | DMA channel 0 acknowledge output                                                                     |  |  |  |  |  |

| DMAAKI                           | DMA channel 1 acknowledge output                                                                     |  |  |  |  |  |

| DMAAK2                           | DMA channel 2 acknowledge output                                                                     |  |  |  |  |  |

| DMAAK3/TxD                       | DMA channel 3 acknowledge output/Serial transmit data output                                         |  |  |  |  |  |

| DMARQO                           | DMA channel 0 request input                                                                          |  |  |  |  |  |

| DMARQ1                           | DMA channel 1 request input                                                                          |  |  |  |  |  |

| DMARQ2                           | DMA channel 2 request input                                                                          |  |  |  |  |  |

| DMARQ3/RxD                       | DMA channel 3 request input/Serial receive data input                                                |  |  |  |  |  |

| END/TC                           | End input/Terminal count output                                                                      |  |  |  |  |  |

| GND                              | Ground                                                                                               |  |  |  |  |  |

| High                             | High-level output except during hold<br>acknowledge when it is placed in the<br>high-impedance state |  |  |  |  |  |

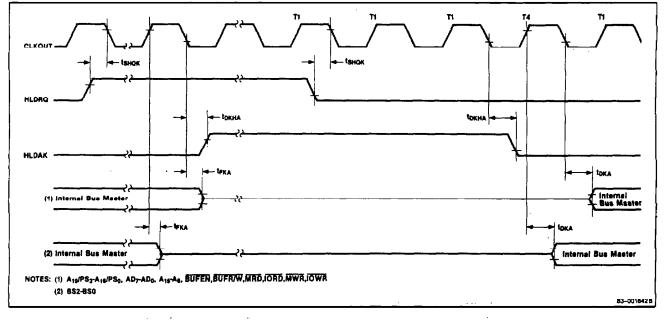

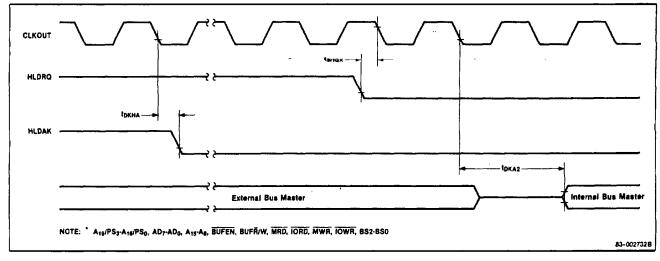

| HLDAK                            | Hold acknowledge output                                                                              |  |  |  |  |  |

| HLDRQ                            | Hold request input                                                                                   |  |  |  |  |  |

| IC                               | Internal connection; leave unconnected                                                               |  |  |  |  |  |

| INTAK/TOUT1/SRDY                 | Interrupt acknowledge output/Timer/counter 1<br>output/Serial ready output                           |  |  |  |  |  |

| INTP1-INTP7                      | Interrupt request inputs                                                                             |  |  |  |  |  |

| IORD                             | I/O read strobe output                                                                               |  |  |  |  |  |

| IOWR                             | I/O write strobe output                                                                              |  |  |  |  |  |

| MRD                              | Memory read strobe output                                                                            |  |  |  |  |  |

| MWR                              | Memory write strobe output                                                                           |  |  |  |  |  |

| NC                               | No connection                                                                                        |  |  |  |  |  |

| NMI                              | Nonmaskable interrupt input                                                                          |  |  |  |  |  |

| POLL                             | Polt input                                                                                           |  |  |  |  |  |

| QS1-QS0                          | CPU queue status outputs                                                                             |  |  |  |  |  |

| READY                            | Ready input                                                                                          |  |  |  |  |  |

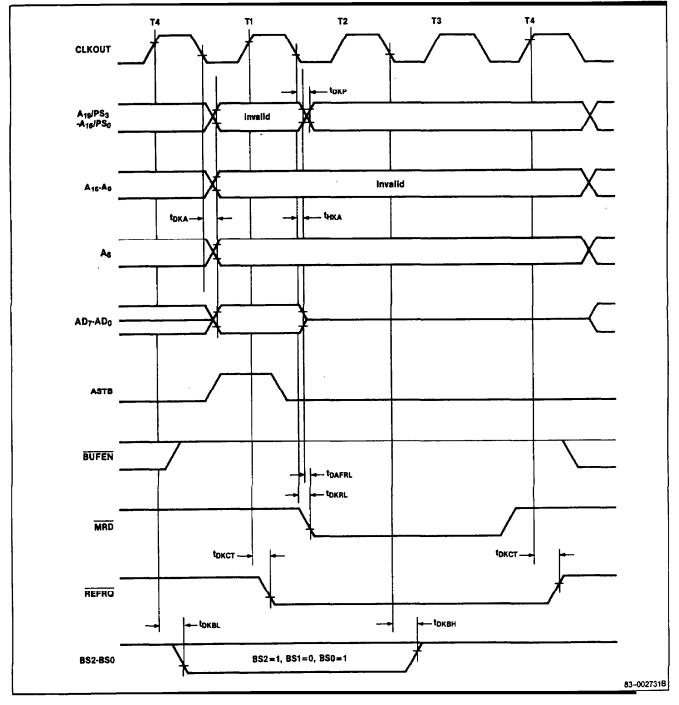

| REFRO                            | Refresh request output                                                                               |  |  |  |  |  |

| DEDET                            | Reset input                                                                                          |  |  |  |  |  |

| RESET                            |                                                                                                      |  |  |  |  |  |

| RESOUT                           | Synchronized reset output                                                                            |  |  |  |  |  |

|                                  | Synchronized reset output<br>Timer/counter external clock input                                      |  |  |  |  |  |

| Symbol          | Function                      |

|-----------------|-------------------------------|

| TOUT2           | Timer/counter 2 output        |

| V <sub>DO</sub> | +5 V power supply input       |

| X1, X2          | Crystal/external clock inputs |

## **Pin Functions**

#### A19-A16/PS3-PS0 [Address/Status Bus]

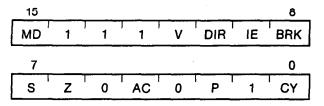

These three-state output pins contain the upper 4 bits of the 20-bit address during T1 and processor status information during T2, T3, Tw, and T4. During T1 of a memory read or write cycle, these pins contain the upper 4 bits of the 20-bit address. These pins are forced low during T1 of an 1/O bus cycle.

Processor status is output during T2, T3, Tw, and T4 of both memory and I/O bus cycles. PS<sub>3</sub> is zero during any CPU native mode bus cycle. During any DMA, refresh, or 8080 emulation mode bus cycle, PS<sub>3</sub> outputs a high level. PS<sub>2</sub> outputs the contents of the interrupt enable (IE) flag in the CPU PSW register. PS<sub>1</sub> and PS<sub>0</sub> indicate the segment register used to form the physical address of a CPU bus cycle as follows:

| PS <sub>1</sub> | PSO | Segment              |  |  |  |

|-----------------|-----|----------------------|--|--|--|

| 0               | 0   | Data segment 1 (DS1) |  |  |  |

| 0               | 1   | Stack segment (SS)   |  |  |  |

| 1               | 0   | Program segment (PS) |  |  |  |

| 1               | 1   | Data segment 0 (DS0) |  |  |  |

These pins are in the high-impedance state during hold acknowledge.

## A15-A8 [Address Bus]

These three-state pins form the active-high address bus. During any CPU, DMA, or refresh bus cycle,  $A_{15}$ - $A_8$  output the middle 8 bits of the 20-bit memory or I/O address. The  $A_{15}$ - $A_8$  pins enter the high-impedance state during hold acknowledge or an internal interrupt acknowledge bus cycle. During a slave interrupt acknowledge bus cycle,  $A_{10}$ - $A_8$  contain the address of the slave interrupt controller.

## AD7-AD0 [Address/Data Bus]

These three-state pins form the active-high, time-multiplexed address/data bus. During T1 of a bus cycle,  $AD_7-AD_0$  output the lower 8 bits of the 20-bit memory or I/O address. During the T2, T3, Tw, and T4 states,  $AD_7-AD_0$  form the 8-bit bidirectional data bus.

The  $AD_7-AD_0$  pins enter the high-impedance state during hold acknowledge or internal interrupt acknowledge bus cycles or while RESET is asserted.

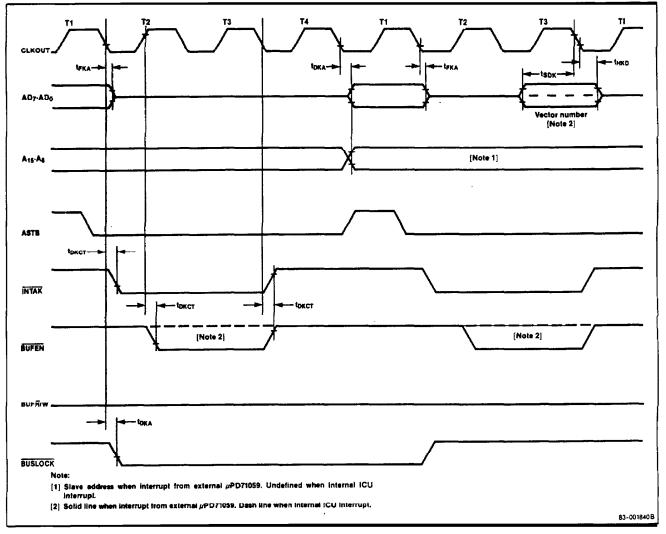

## ASTB [Address Strobe]

This active-high output is used to latch the address from the multiplexed address bus in an external address latch during T1 of a bus cycle. ASTB is held at a low level during hold acknowledge.