# IEM

# OS/390 Assembler Programming Introduction

© Copyright IBM Corp., 2000, 2004. All rights reserved.

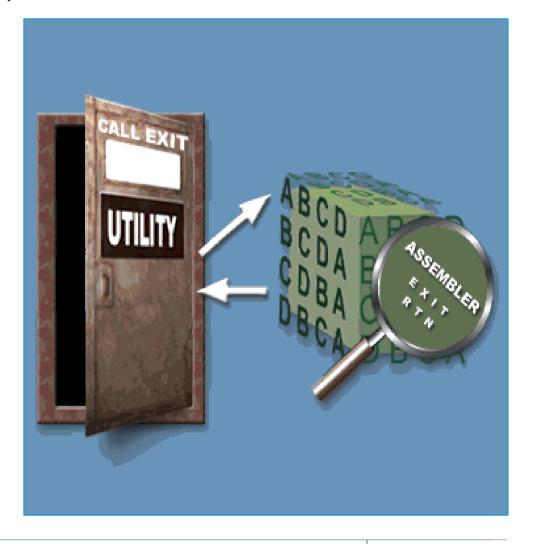

#### **Assemblers**

#### What are Assemblers?

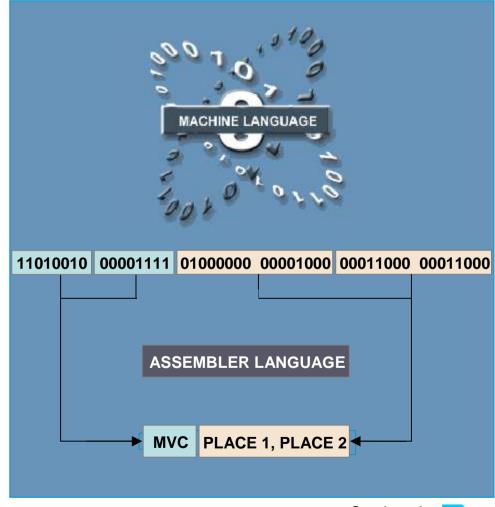

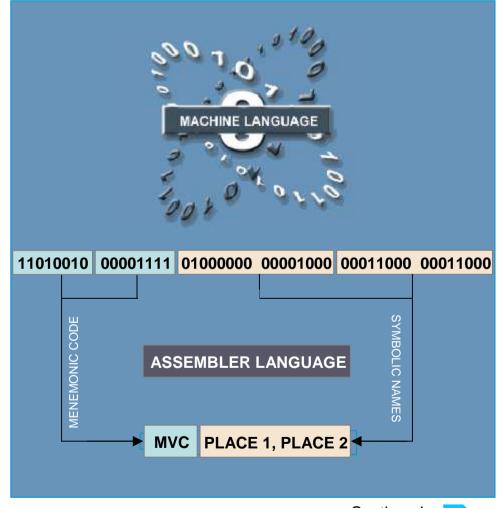

In the very early days programmers wrote in Machine Language. It was a slow, tedious and error prone process, only feasible for short and simple programs. To simplify the task of Programming and allow larger programs to be created, programs called Assemblers were created.

# Assemblers (cont'd)

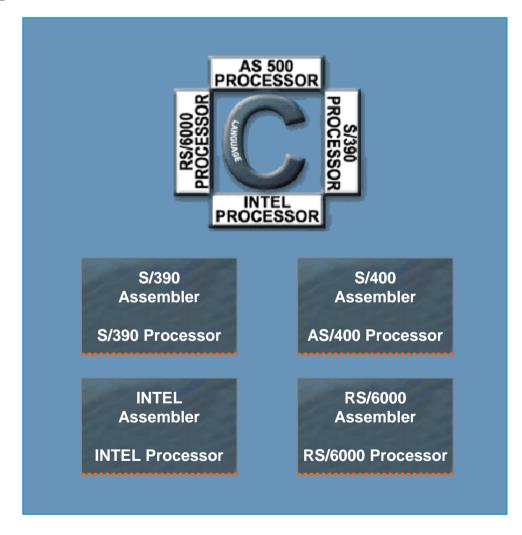

Assembler allowed programmers to write in Assembler Language. Although an Assembler Language program had the same number of instructions as the equivalent machine program, writing Assembler program is much simpler.

In Assembler Language, operations are represented by mnemonic codes (such as MVC for MOVE) and the data is represented by symbolic codes (such as PLACE1) rather than addresses.

## **High Level Languages**

## What is a High Level Language?

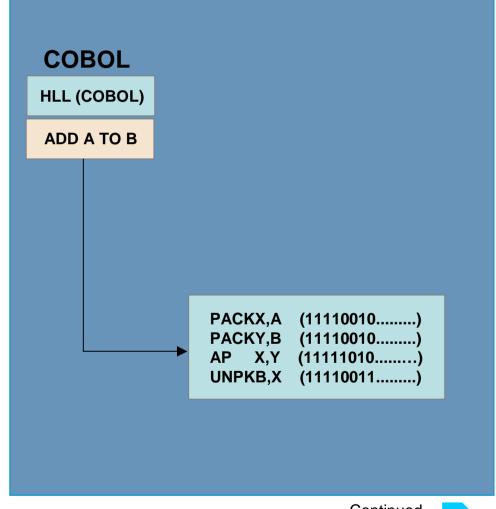

High Level Languages (HLL) go one step further than Assembler languages in simplifying the programming task.

In a HLL, the program is expressed at a higher level of abstraction.

An Assembler language program might contain five or ten times as many instructions as the same program written in a HLL.

## **High Level Languages (cont'd)**

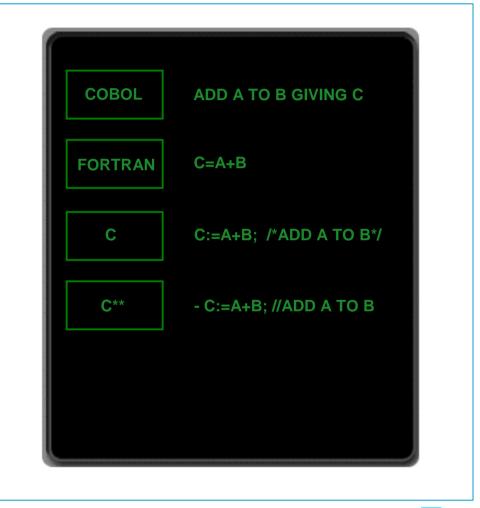

Listed below are some examples of HLL:

- Fortran first HLL language in general use, developed for scientific and general computing

- COBOL another early HLL, designed to facilitate the programming of business and commercial programs

- C most popular in use today for a wide range of programming tasks

- C++ and Smalltalk object oriented languages that are becoming increasingly popular

## **Advantages of HLL and Assembler Language**

# What are the advantages of HLL over Assembler Language?

HLL is advantageous over Assembler Language because of the following reasons:

- Ease of development

- Portability

# What is the advantage of Assembler Language?

Assembler Language contains statements that correspond instruction by instruction to the Machine Language of the computer.

## **Advantages of Assembler Language**

## Why program in Assembler Language?

Assembler Language is chosen for programming because of the following reasons:

- It provides extensive control of the hardware environment

- Assembler Language instructions correspond one-for-one with machine instructions making it possible to do anything the hardware allows

HLLs on the other hand, do not provide the programmer with extensive control of the hardware. The efficiency of a HLL program is subject to the way the compiler translates the HLL program.

#### **ASSEMBLER ADVANTAGES**

√ Control of environment

# Advantages of Assembler Language (cont'd)

Assembler may also be considered when efficiency is a major concern.

A compiler must be designed to translate all possible valid combination of HLL code, and in some cases may not translate it to produce the most efficient Machine Language. Assembler instructions are translated one-for-one into Machine Language, and a good Assembler programmer can achieve the maximum efficiency of Machine Language code.

#### **ASSEMBLER ADVANTAGES**

√ Control of environment

√ Maximum efficiency

# **Advantages of Assembler Language (cont'd)**

It may not be necessary to code a whole program in Assembler Language to achieve the benefits of increased efficiency. Coding only those parts of a program which are executed frequently may achieve significant efficiency gains.

In many cases, Assembler coding is not done for a whole system or even a whole program, but only for selected modules.

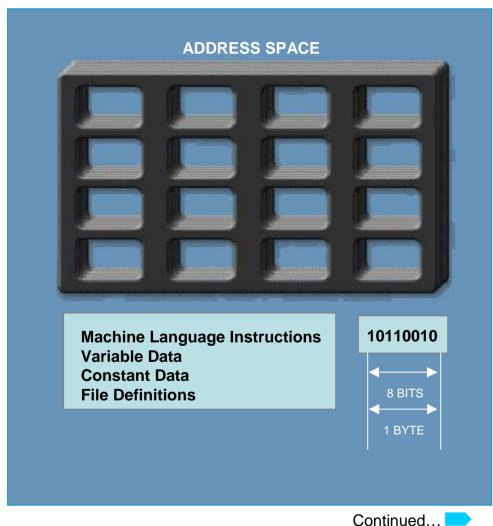

## **Program Execution**

## What is an Image?

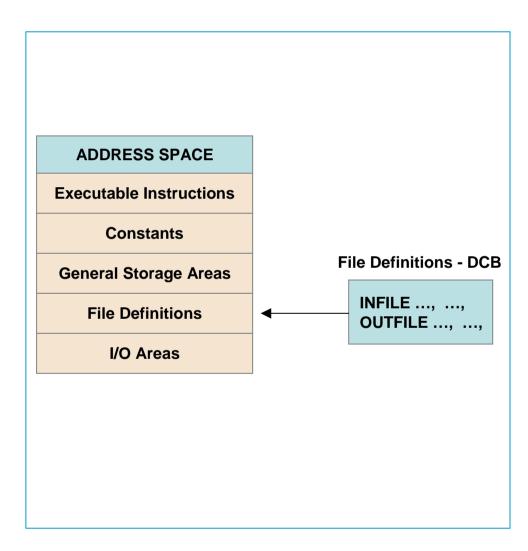

In order for a program to execute, it must be loaded into the memory or main storage area of the computer. The image is a program which is loaded into the memory in order to execute in the Assembler program space.

#### What does the program space consist of?

A program space consists of:

- **Executable Machine Language** instructions

- Areas to store the program's variable data

- The program's constant data

- File definitions for use in Input/Output operations

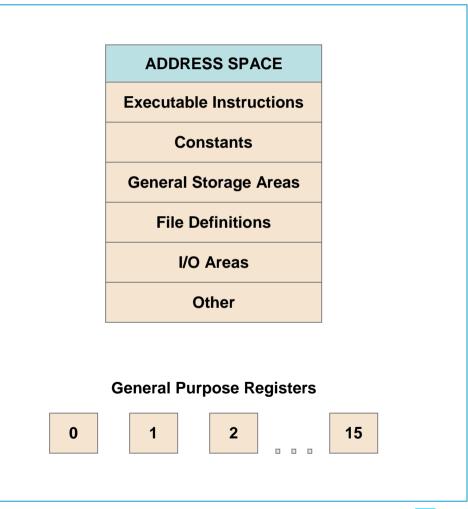

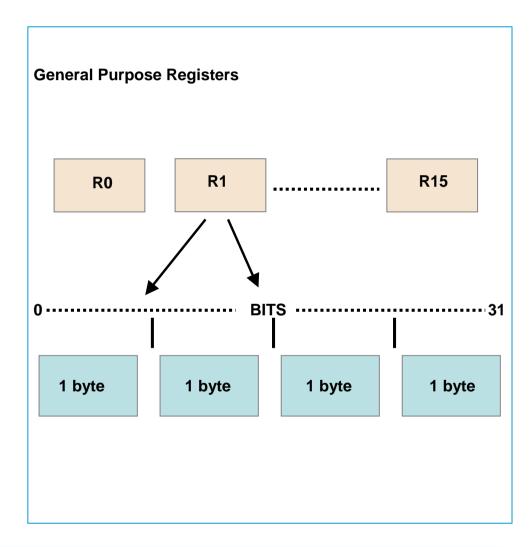

## **General Purpose Registers**

## What are General Purpose Registers?

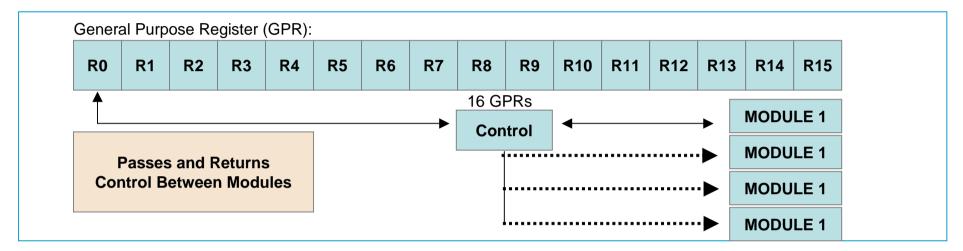

The architecture of S/390 computers provides 16 General Purpose Registers (GPRs). GPRs are part of the hardware of the computer, and can be used by any Assembler program when executing.

#### What are the functions of GPRs?

GPRs are very important to the Assembler programmer. They are used in addressing both instruction and data, and also for performing binary arithmetic, counting for loops and many other purposes.

GPRs are also used in conventional ways, passing control and data from one module to another.

# **General Purpose Registers (cont'd)**

#### **Essentials of GPRs**

Effective management of GPRs is a basic skill required of the Assembler programmer. It is important to know which registers are available and for what purposes specific GPRs must be reserved.

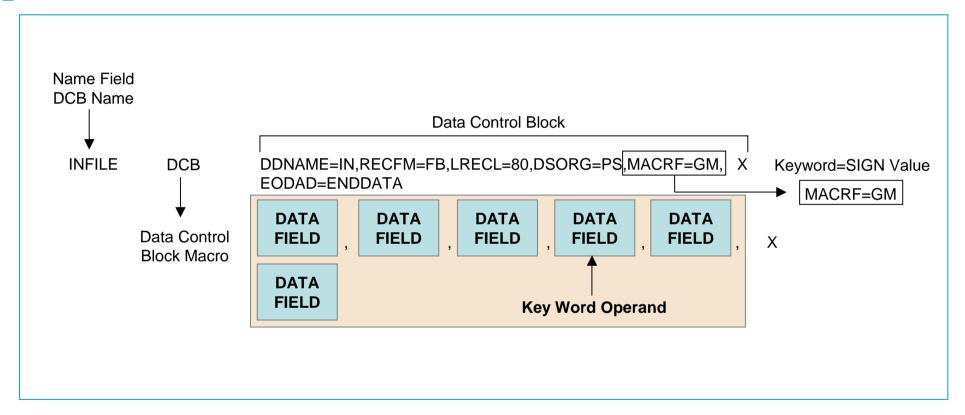

#### **Data Control Block Definition**

#### What is a DCB?

A file definition, called a Data Control Block (DCB) must be created for each file the Assembler programmer wishes to access in a program. The DCB is a special kind of data area, which maintains information about an external file. The DCB is created using a system macro instruction.

#### The DCB contains the following:

- Name used to refer to the data

- The format and size of the records and blocks within the dataset

- Types of instructions used to access the dataset and the current status of the dataset

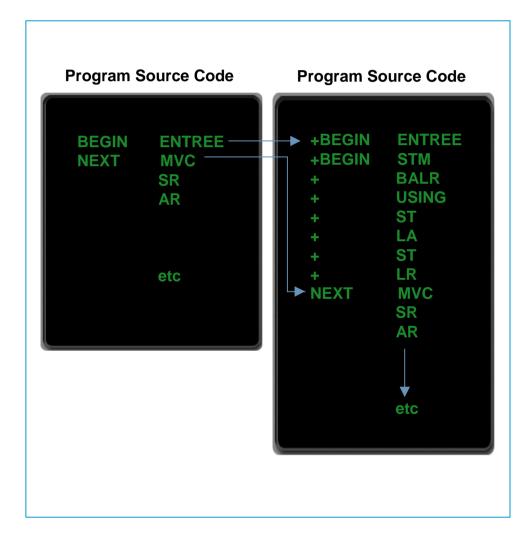

#### **Macro Instructions**

#### What are macro instructions?

Assembler Language instructions generally correspond one-for-one with Machine Language instructions. However there are some situations where it is not feasible for the Assembler Language programmer to code at this detailed level.

To help the programmer cope with such complex situations, the Assembler provides macro instructions. A macro instruction is an instruction that is processed by the assembler to generate a group of Assembler instructions.

## **Macro Instructions Definition (cont'd)**

#### What are macro instructions?

The I/O macro instructions like OPEN, CLOSE, GET, PUT and ENTRÉE create multiple Assembler instructions to perform the specific I/O operation required.

The DCB macro instruction generates the various data areas and constants necessary to maintain information about an external file. The Assembler program only has to know how to handle I/O at a high level. The expansion of the macro instruction into multiple low level instructions generates the detailed level code.

## Unit: S/390 Memory Usage Topic: Hardware Components

## Registers

## What are registers?

Registers are another location where operands reside in an Assembler Language program. There are several registers in S/390 architecture.

Types of registers in S/390 architecture are:

- General Purpose Registers (GPRs)

- Floating Point Registers (FPRs)

- Control Registers

- Access Registers

- Vector Registers

**General Purpose Registers (GPRs)**

Floating - Point Registers (FPRs)

**Control Registers**

**Access Registers**

**Vector Registers**

GPR – Used by the Programmer for Storage Address, Accumulator and Work Area.

FPR – Performs Floating Point Arithmetic.

Control Registers and Access Registers – Used by the Operating System.

Vector Registers – Used for advanced math calculations

## Unit: S/390 Memory Usage Topic: Hardware Components

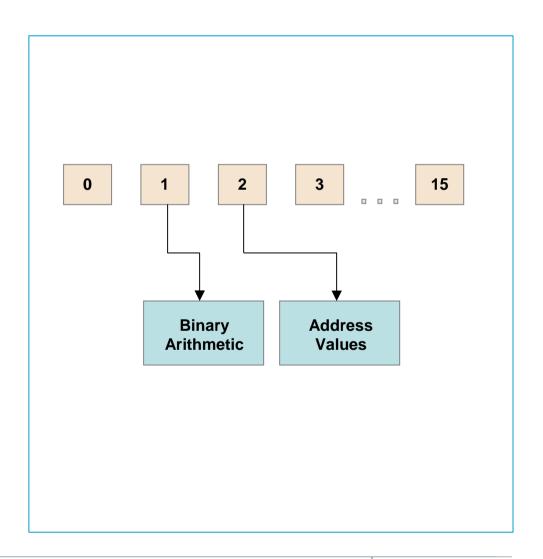

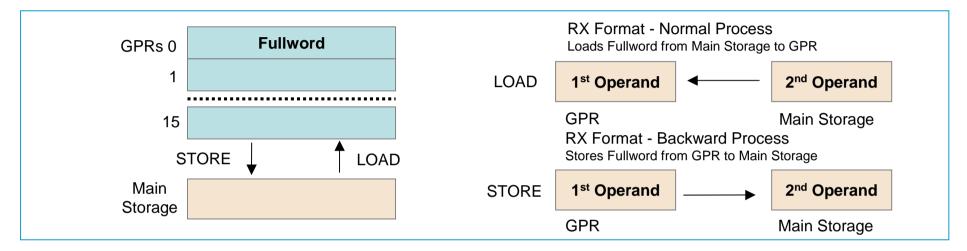

# **General Purpose Registers**

## What are General Purpose Registers (GPRs)?

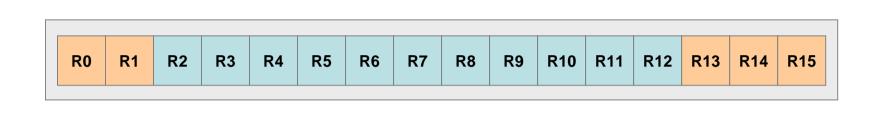

GPRs are of the most interest to programmers. There are 16 general purpose registers (GPRs), numbered from 0-15. They are referred to with a prefix of R (R0, R1, R2.... R15).

The GPRs are 32 bits in length and can hold fixed-point values between -2, 147, 483, 648, and +2, 147, 483, 647.

#### GPRs are used as:

- Part of the address for all storage operands

- As accumulators and work areas in performing fixed-point arithmetic

Unit: S/390 Memory Usage Topic: Hardware Components

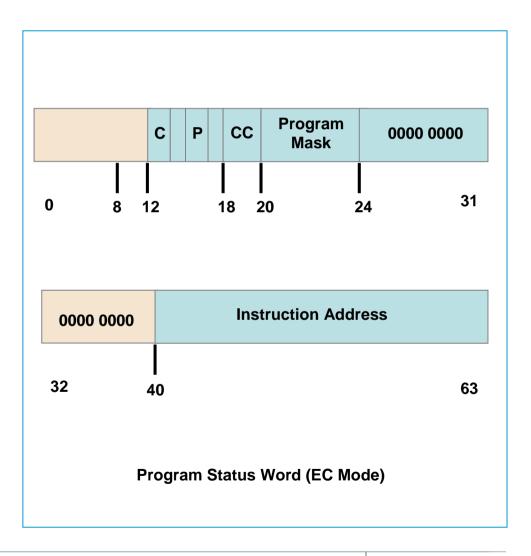

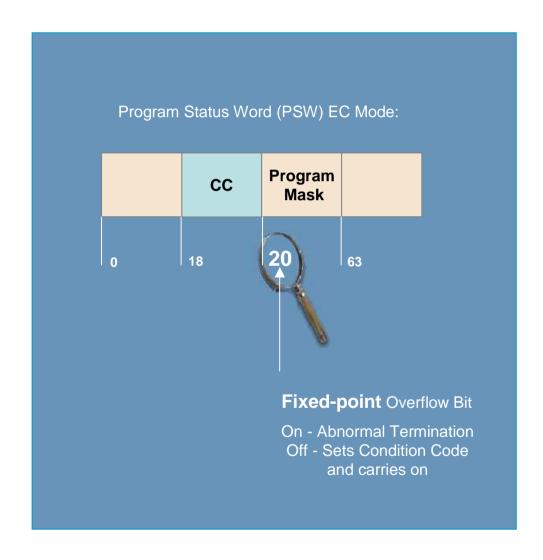

## **Program Status Word**

## What is a Program Status Word (PSW)?

The Program Status Word is a hardware location where the current status of the Central Processing Unit (CPU) is represented. It is a register that is of particular interest to the Assembler Language programmer.

Amongst other fields, the PSW contains:

- The address of the next instruction to be executed

- The current value of the condition code (CC)

- Other flags, such as the one to indicate whether the CPU is in problem state or supervisor state

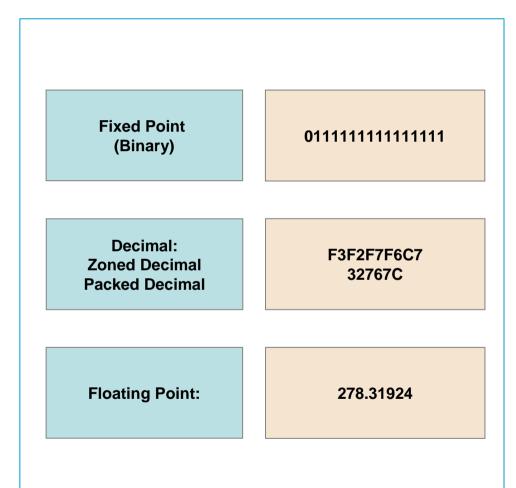

#### **Arithmetic Instructions**

Although EBCDIC represents numbers in character form, it cannot be used for arithmetic operations.

#### What are the kinds of arithmetic instructions?

Fixed-Point (Binary) arithmetic and Decimal arithmetic are integer based, handling only whole numbers . Floating-Point arithmetic handles real numbers, numbers with fractional portions.

Briefly look at each of the types and how it is used to represent numeric values.

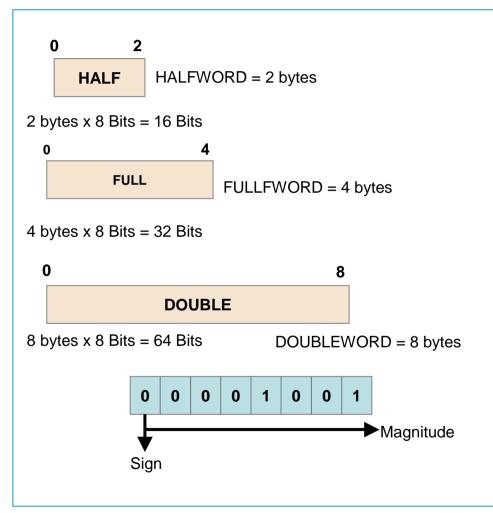

#### **Fixed-Point Arithmetic**

#### What is Fixed-Point arithmetic?

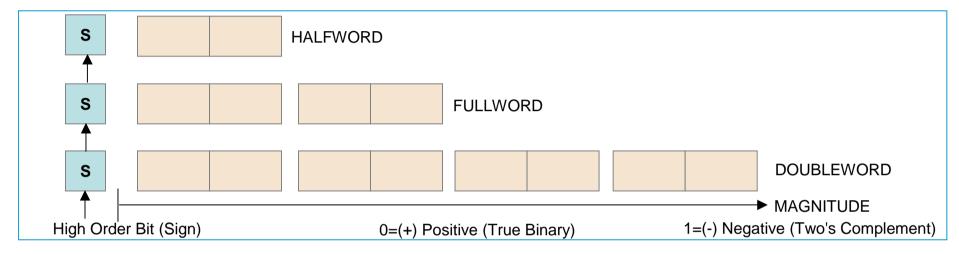

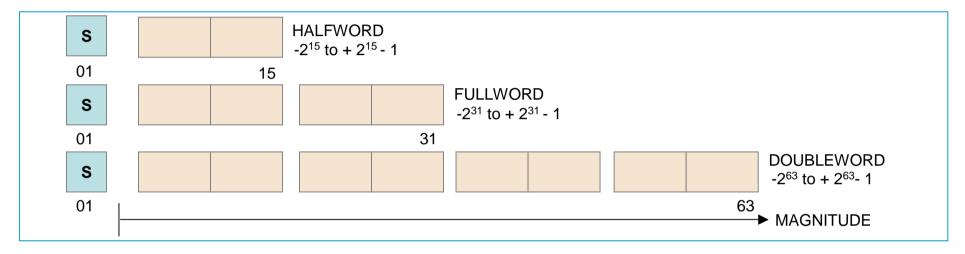

Fixed-Point arithmetic uses three data types:

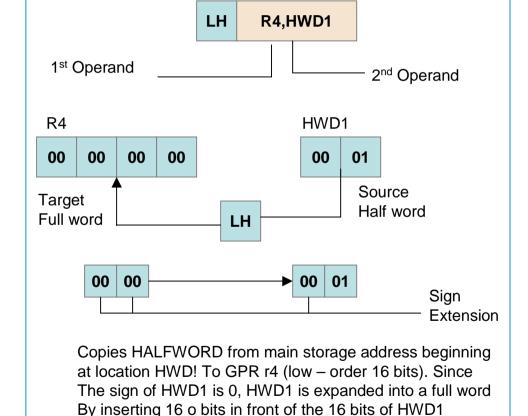

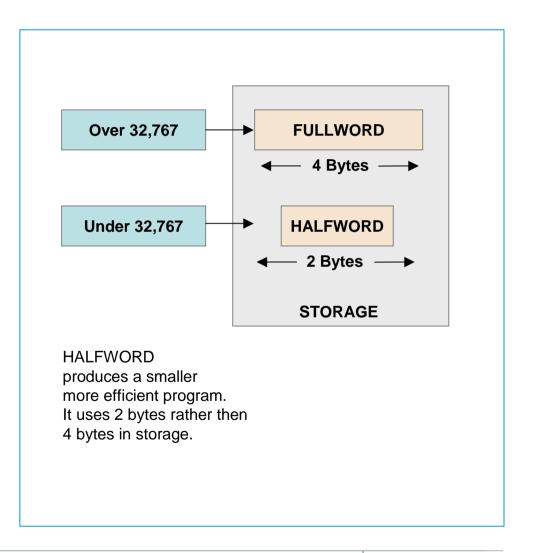

- Full words sometimes called a word, is four bytes (32 bits) in length

- Half words 2 bytes (16 bits) in length

- Double words 8 bytes (64 bits) in length

#### What do fixed-point numbers consist of?

Fixed-point numbers consist of two parts, a sign and a magnitude. The sign is in the leftmost, or high-order bit, and the magnitude occupies the rest of the field.

A zero bit represents a positive sign, a one bit a negative sign.

## **Fixed-Point Arithmetic (cont'd)**

For positive numbers, the magnitude is represented in true binary. A half word value of +25 would be represented as:

0000 0000 0001 1001

For negative numbers the magnitude is expressed in twos-complement form. To convert a binary value to twos-complement, flip all the bits, change 1s to 0 and 0s to 1, and then add one. A halfword value of -25 would be represented as:

1111 1111 1110 0111

#### Halfword Value of + 25

| 0000                   | 0000 | 0001 | 1001 |

|------------------------|------|------|------|

| 1111                   | 1111 | 1110 | 0110 |

| TWOS-COMPLEMENT        |      |      | 1    |

| 1111                   | 1111 | 1110 | 0111 |

| Halfword Value of - 25 |      |      |      |

= +25 REVERSE BITS ADD + 1 = -25

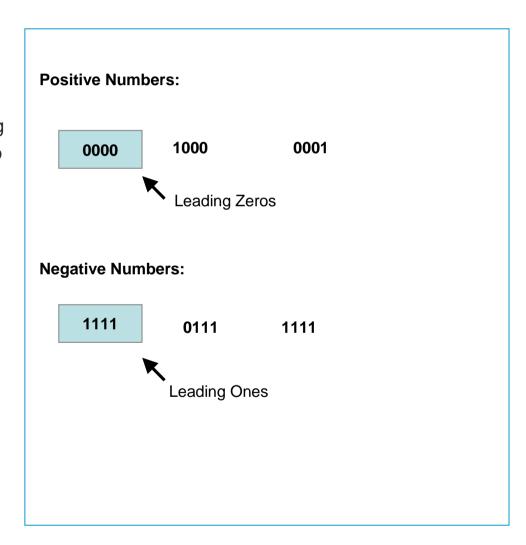

## **Leading Zeros and Twos-complement**

## **Leading zeroes**

Note that in positive numbers, leading zeroes (0s) are insignificant, and in negative numbers, leading one (1s) are insignificant. In general, bits equal to the sign bit are insignificant.

#### **Twos-complement**

Twos-complement notation used to represent negative fixed-point numbers makes doing arithmetic easy for the computer.

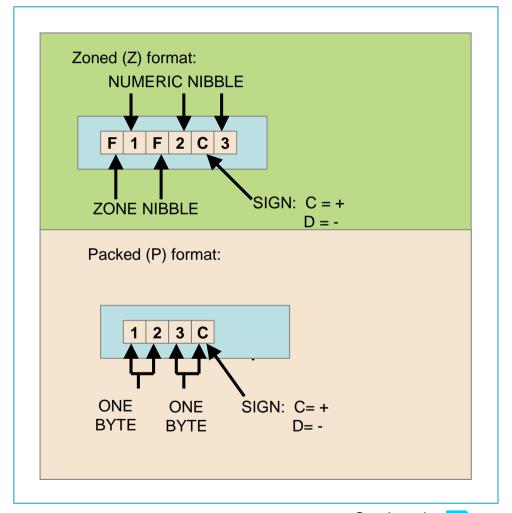

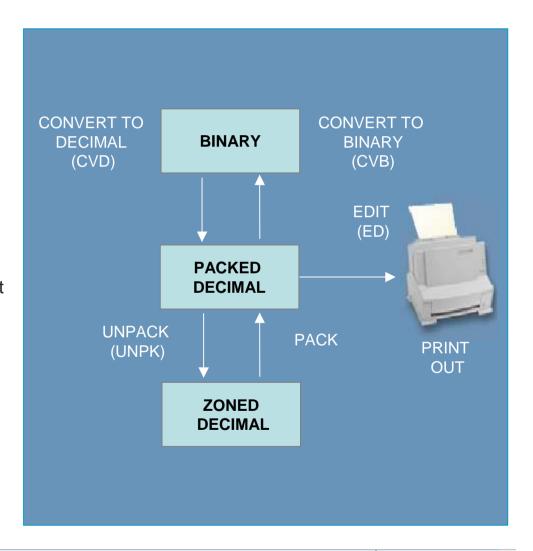

## **Types of Decimal Numbers**

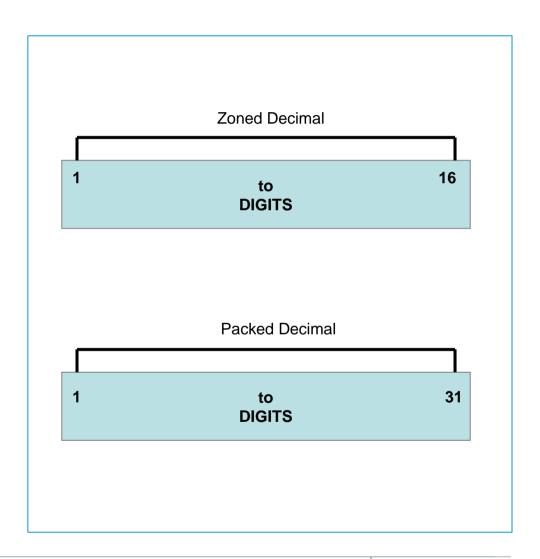

Decimal numbers are of the following two types:

- Zoned Decimal

- Packed Decimal

#### What is packed decimal?

Packed decimal requires less storage than EBCDIC, since each number is represented by half a byte (4 bits). Arithmetic is only done on packed decimal numbers.

#### What is zoned decimal?

Zoned decimal is an intermediate format, used in converting numbers from characters to packed decimal. Packed numbers can be from 1 to 31 digits in length, while zoned can be from 1 to 16 digits.

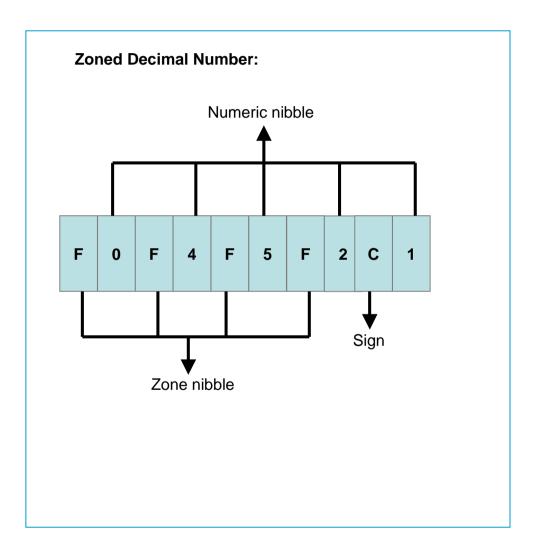

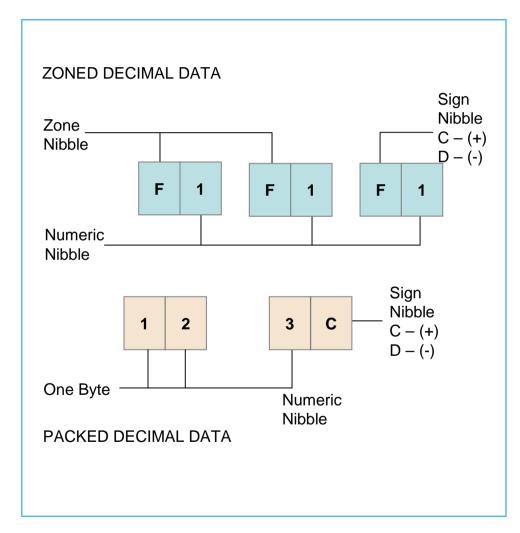

#### **Zoned Decimal Number**

#### What is a zone nibble?

Each byte in a zoned decimal number consists of a zone nibble and a numeric nibble. The zone nibble is the first half of each byte, and the numeric nibble is the second half.

Each numeric nibble contains the decimal digit value for that position. All zone nibbles except the rightmost contain the hex value F (one one binary). The rightmost nibble contains the sign. The hex character C represents a positive sign and D represents a negative sign.

A nibble is half a byte.

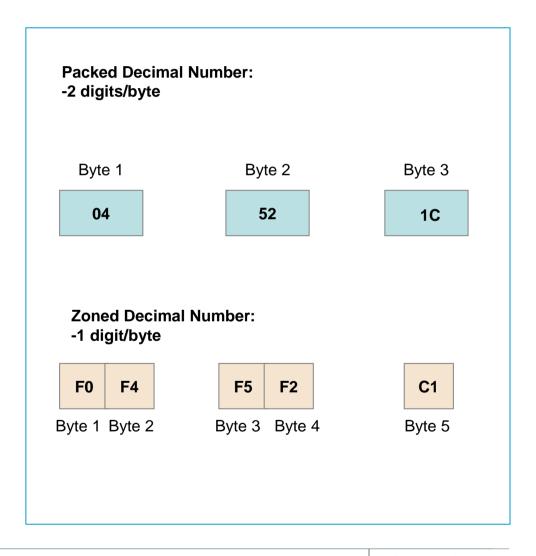

## **Packed Decimal Number**

Packed decimal notation adds one decimal digit into each nibble, except for the rightmost nibble, which contains the sign. The sign is coded the same way as for zoned decimal.

A three byte packed decimal number containing the value 4521 would be represented (in hex) as: 04521C

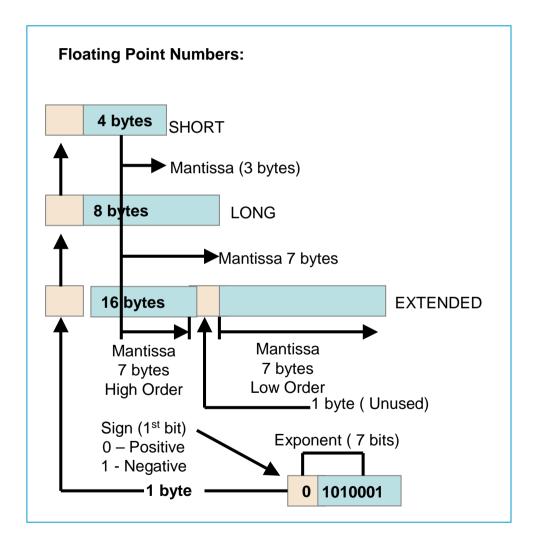

# Using Floating Point Numbers

Fixed point and decimal numbers are integers. Real numbers, numbers with a fractional part, are represented with floating point numbers. Floating point numbers allow you to represent a large range of numbers.

1.74642 X 10<sup>17</sup>

= 174642000000000000

# **Floating-Point Numbers**

Following are the 3 data types used for floatingpoint numbers?

- Short numbers 4 bytes in length

- Long 8 bytes in length

- Extended 16 bytes in length

A floating-point number consists of the following parts:

- A Sign

- A Mantissa

- An Exponent

# Floating-Point Formats

The three floating-point formats all provide for essentially identical ranges of magnitude, since the exponent is the same size in each.

Going from short to long or from long to extended simply increases the length of the mantissa, and thus provides more precision.

#### **Floating-Point Formats**

0.32641 X 10<sup>70</sup>

0.32641347961 X 10<sup>70</sup>

0.3264134796128439 X 10<sup>70</sup>

## **Modes of Operation**

## What are the two modes of operation in System /390 architecture?

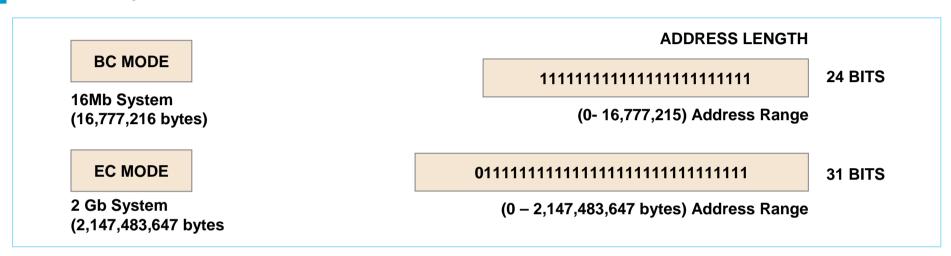

One of the most distinctive features of a computer's architecture is the way it addresses main storage. The S/390 architecture provides two modes of operation:

- Basic Control Mode (BC)

- Extended Control Mode (EC)

# **Address Space**

Flat address space means that the memory is continuously addressable, with no segmentation of memory from the programmer's point of view.

In a few cases the programmer must deal with absolute addresses. However the most common concern of a programmer is addresses within instructions.

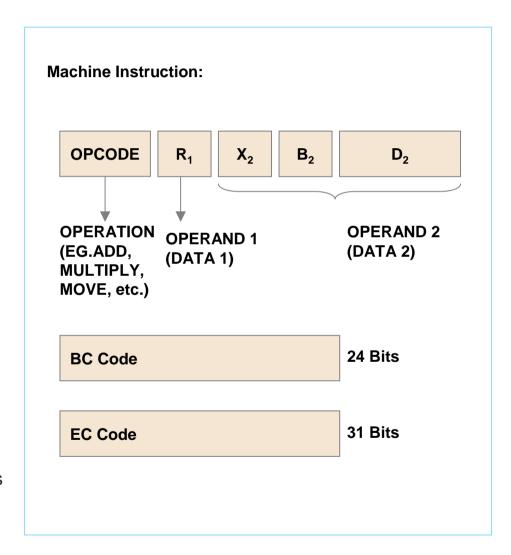

#### **Machine Instruction**

Machine instructions consist of operations (add, multiply and so on); and a number of operands, specifying the data upon which the operation is to be performed. The operands may specify registers or memory locations.

Architecture with instructions specifying absolute addresses is generally not designed because:

- The length of absolute addresses depends on the mode BC or EC.

- If absolute addresses were used in instructions, either instructions would vary in length depending on the mode, or there would be wasted space when BC mode was used. Specifying 31 bits for each address in an instruction will produce very long instructions.

- Using absolute addresses in instructions affects program relocatability.

## **Base Displacement Address**

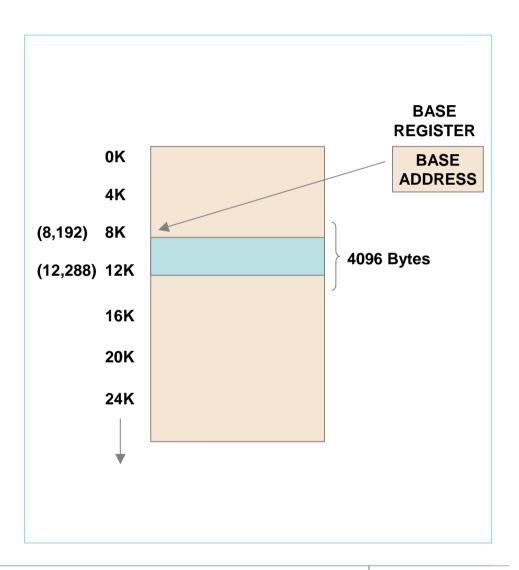

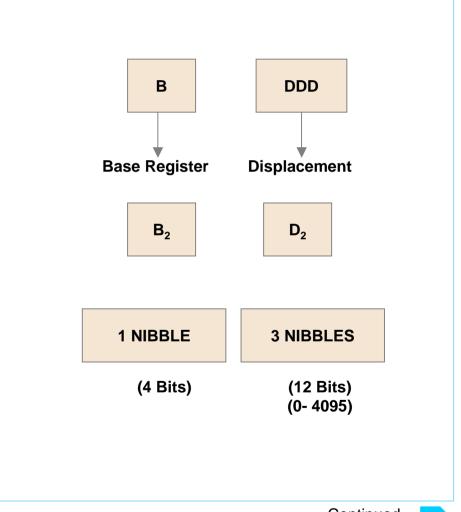

## What is Base Displacement Addressing?

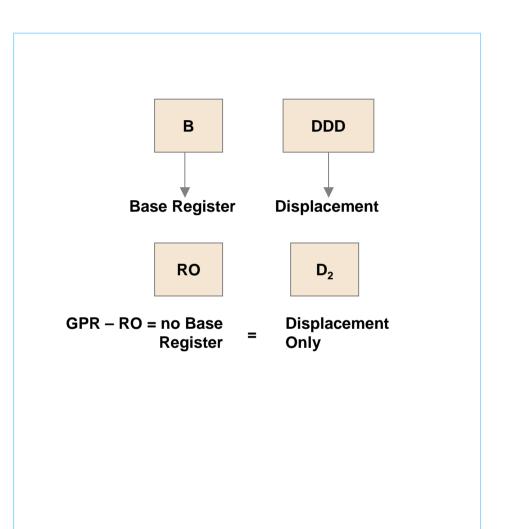

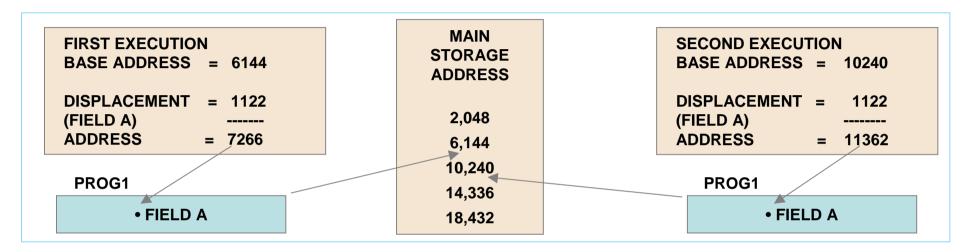

The form of address used in instructions is called base displacement addressing. In this form the address is specified as a displacement from the address contained in a GPR. This is represented as a BDDD. B stands for base, and when a GPR is used in this way it is called a base register.

There are 16 GPRs, numbered 0 – 15, so any register can be represented by one hex digit (one nibble). The displacement DDD is a 3 nibble or a 12 bit quantity, and so contains values from 0 – 4095. When the processor is decoding an instruction, it converts each base-displacement address to an absolute address by adding the specified displacement DDD to the contents of the specified base register B.

# **Base Displacement Address (cont'd)**

There is an exception to this rule of address formation. If the base register B specifies register 0, it means that no base register is to be used in the address calculation. That is, you cannot use R0 as a base register in the normal way, but to specify that you wish to use displacement only in the address calculation.

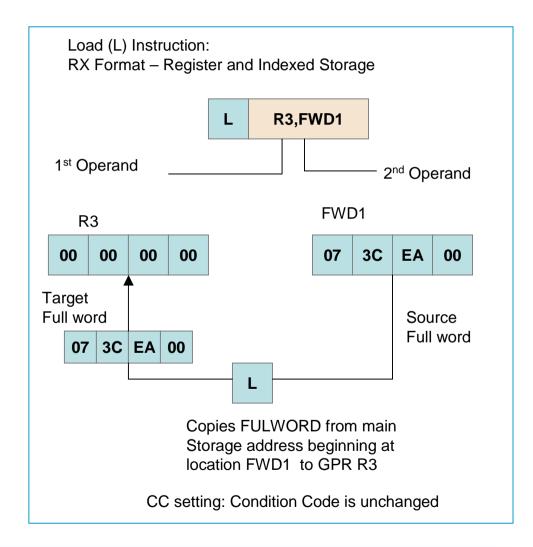

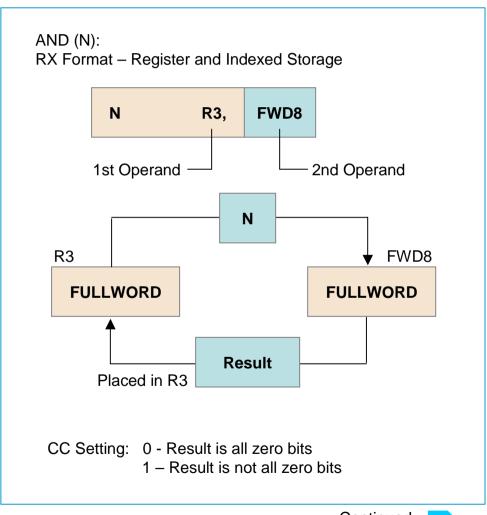

#### What are RX instructions?

It will be seen in the next section unit 2 -1, that there is one instruction type which extends this address formation process. RX instructions use two registers, a base register B and an index register X, along with a displacement in address generation.

With RX instructions, if R0 is specified as base and/or index register, it is ignored in the address calculation.

## **Base Displacement Address (cont'd)**

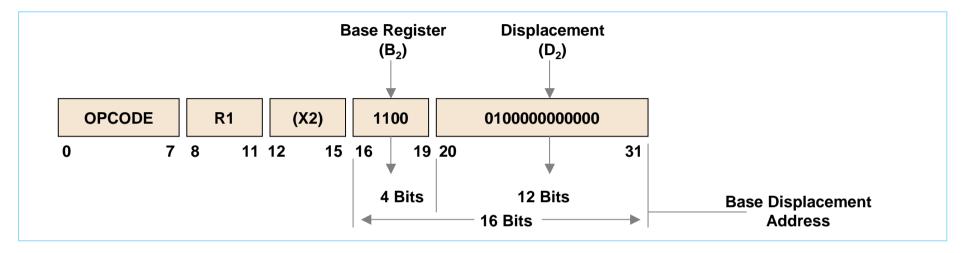

A base displacement address uses 16 bits, 4 to specify the base register, and 12 to specify the displacement.

When it decodes the instruction, prior to execution, the processor takes the contents of the base register (32 bits), adds the displacement and drops either 1 high order bit to get a 31 bit EC address, or 8 high order bits to get a 24 bit BC address. The instructions are kept short, while still specifying full address indirectly.

## **Advantages of Base Displacement**

Advantages of base displacement are:

- Base displacement addresses keep instruction length short

- It allows for common instruction format with no wasted space, regardless of processor mode

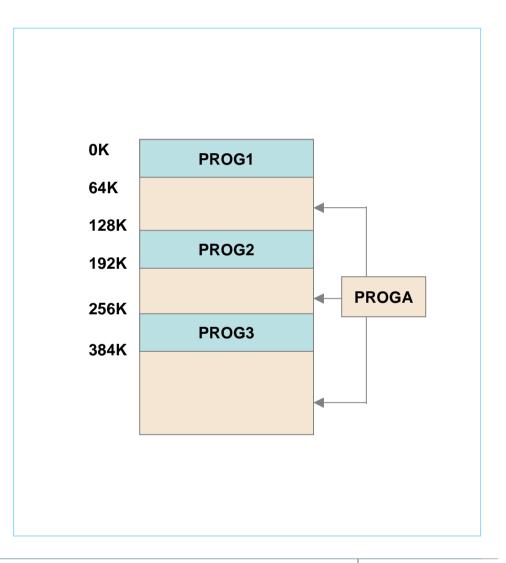

- Provides easy relocatability of programs

## Why is relocatability important?

It is highly desirable, from an operating system point of view, that programs be allowed to run on any location in main storage. If instructions used absolute addresses, they would always have to be loaded in the same storage location in order to run properly.

#### **Absolute Addresses**

Many programs do contain some absolute addresses. These addresses do have to be adjusted when the program is loaded into main storage for execution to reflect the program's actual load point. This is a relatively simple task, since the number of absolute addresses is usually very small.

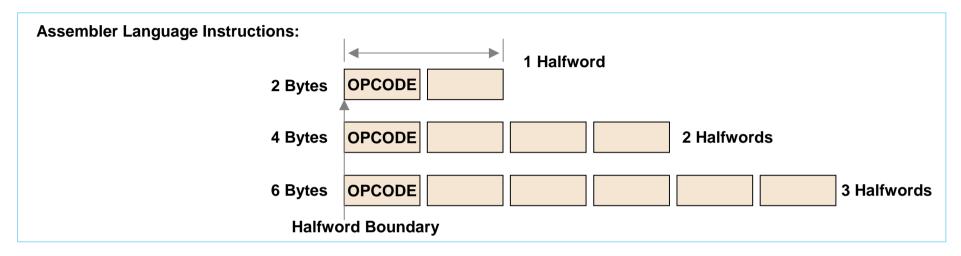

# **Assembler Language Instructions**

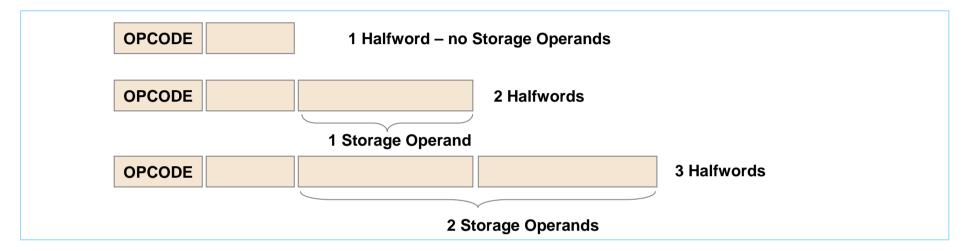

Assembler Language instructions are 1,2 or 3 halfwords in length, and are always aligned on a halfword boundary, which is an address evenly divisible by 2.

#### What are opcodes?

The first field in every instruction is the operation code (opcode), which is 1 byte in length (there are two instructions with 2 byte opcodes, but they are not commonly used in application programming). The operation code specifies what the instruction does, such as add, divide, move or compare.

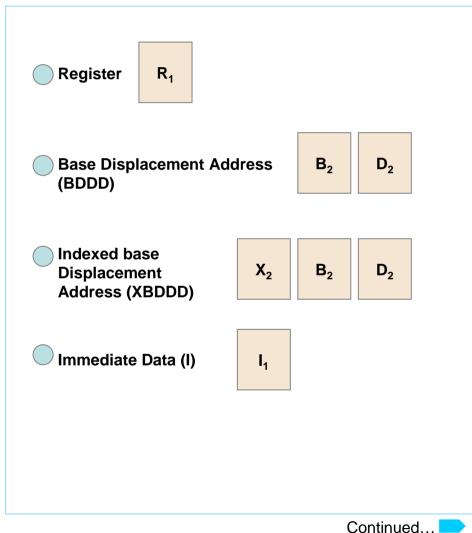

# **Types of Operands**

#### What are the different types of operands?

Most instructions have 2 operands, but some have 0, 1, 2 or 3. The different types of operands are:

- Registers, specified by a register number

- Main storage location, specified by a base displacement address (BDDD)

- Main storage locations, specified with an indexed base displacement address (XBDDD)

- A single byte of immediate data, contained within the instruction itself (I).

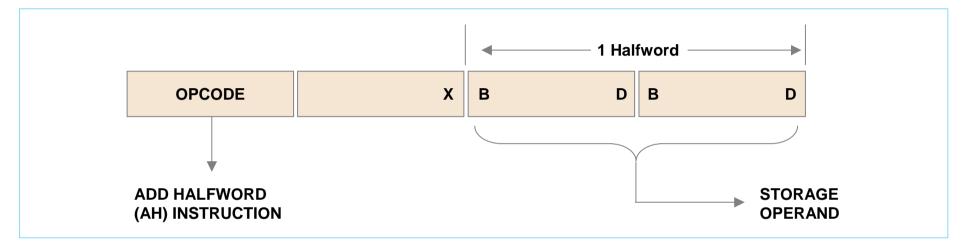

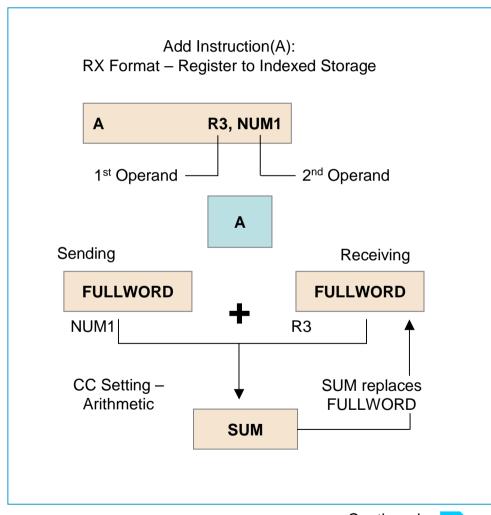

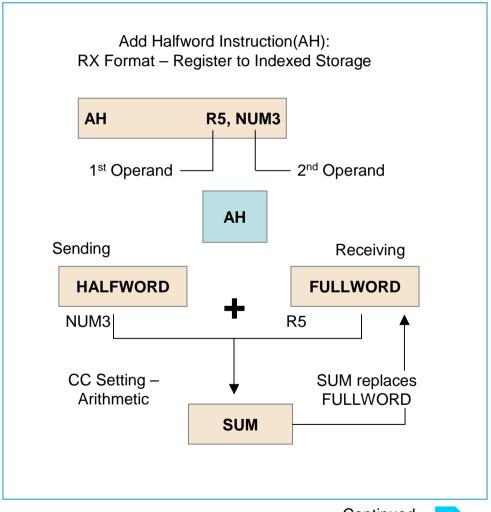

# **Types of Operands (cont'd)**

In some cases, the length of a storage operand is implied by the instruction. The storage operand for an Add Halfword (AH) instruction is a halfword in length.

In other cases, the length of a storage operand is explicitly specified as part of the instruction (L).

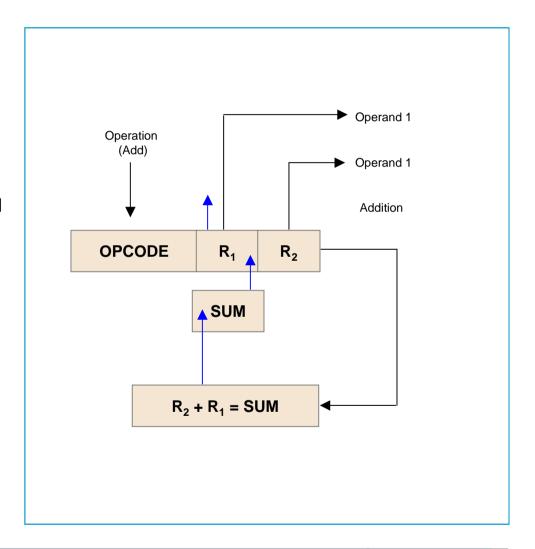

# Types of Operands (cont'd)

Most instructions have two operands. In most instructions, the result of the operations replaces the first operand. For example, Add has two operands.

The Add instruction (A) fetches both operands, adds them together and replaces the first operand with the sum.

# **Instruction Lengths**

# What are the different instruction lengths?

There are 3 possible instruction lengths, 1, 2 or 3 halfwords. They are:

- 1 halfword instructions have no storage operands

- 2 halfword instructions have one storage operand

- 3 halfword instructions have 2 storage operands

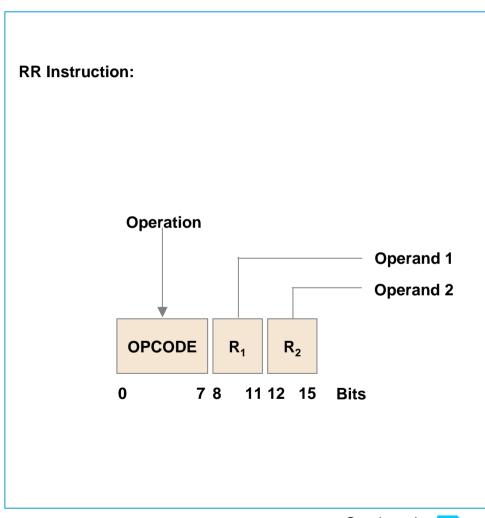

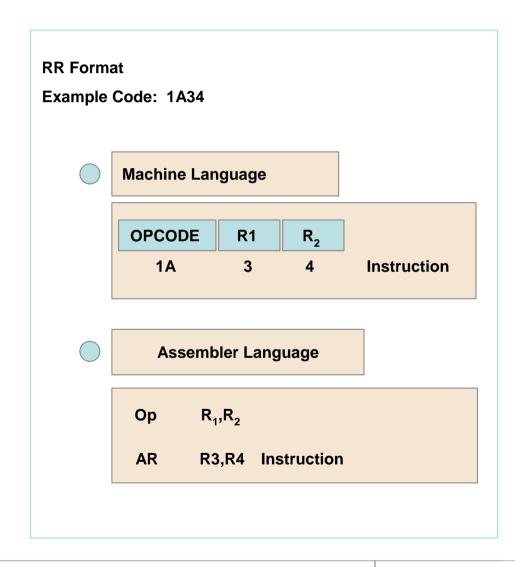

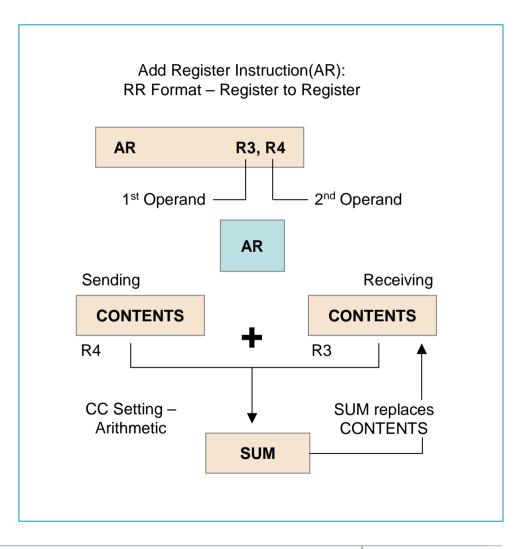

#### **RR** Instruction

#### **Format**

The instruction is 16 bits or one halfword in length. The first byte contains the opcode, and the second byte contains the two operands, both of which are registers.

In numbering the bits in the instruction format, start from zero, not one.

# RR Instruction (cont'd)

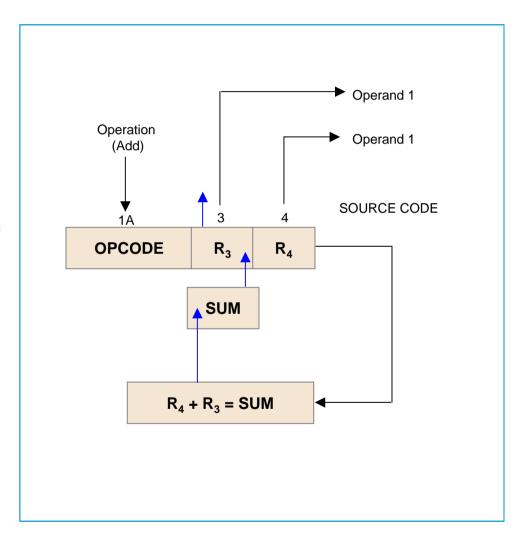

An example of RR Instruction is: 1A34

1A is the operation code for the Add Register instruction. The first operand is R3. The second operand is R4.

When this instruction is executed, the contents of R4 would be added to the contents of R3 and the sum would be placed in R3, replacing the first operand.

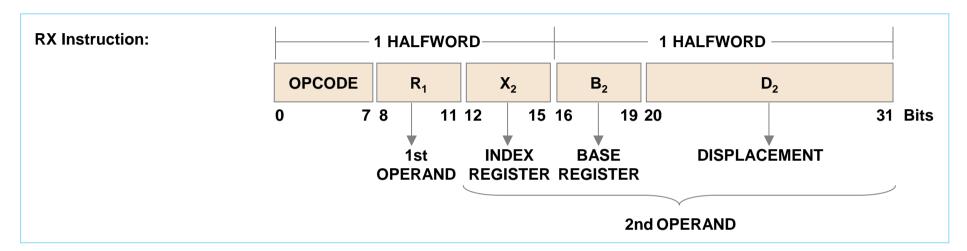

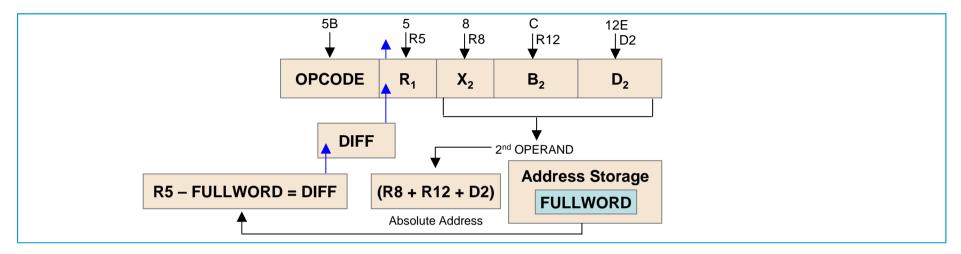

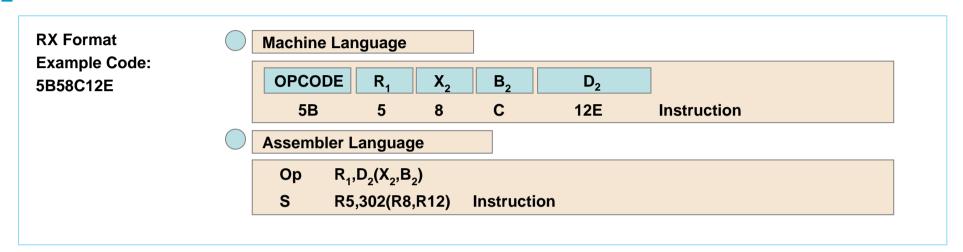

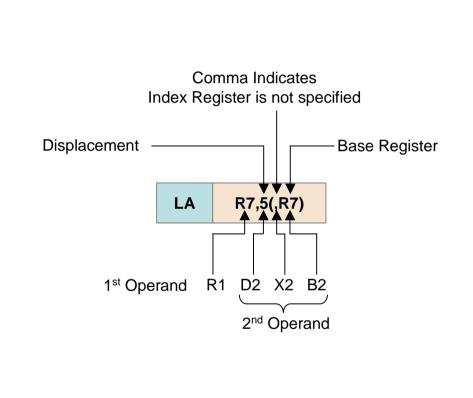

#### **RX Instruction**

#### **Format**

This instruction is 32 bits (or 2 halfwords) in length. The first byte contains the opcode. The following nibble contains the first operand, which is a register.

The remaining fields in the instruction contain the three components that specify the second operand. They are:

- X2, the index register specification

- B2, the base register specification

- D2, the 12 bit displacement of the second operand

# **RX Instruction (cont'd)**

An example of RX instruction is:

5B58C12E

5B is the operation code for the Subtract instruction. The first operand is R5. The second operand is the fullword at the storage location whose absolute address is formed by adding together the contents of R8, the contents of R12, and the value of the displacement, 12E.

When this instruction is executed, the fullword from storage will be subtracted from the value in R5 and the difference placed in R5.

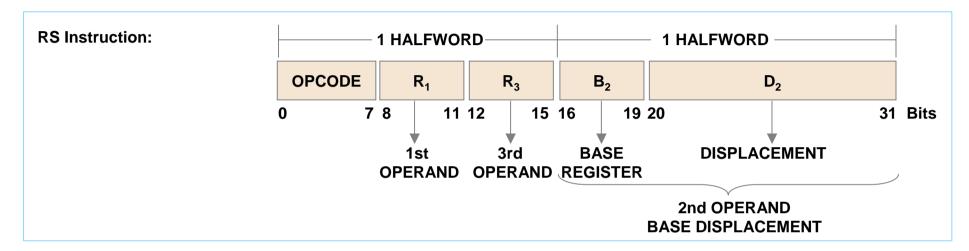

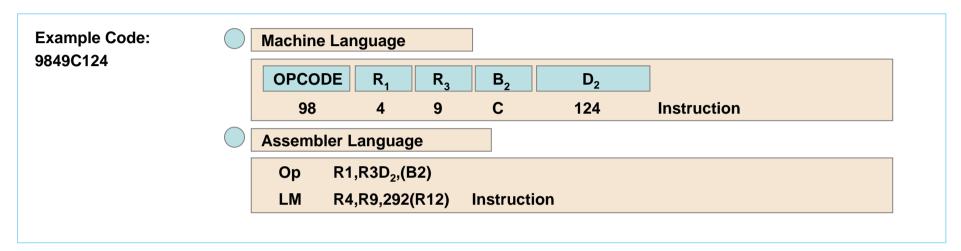

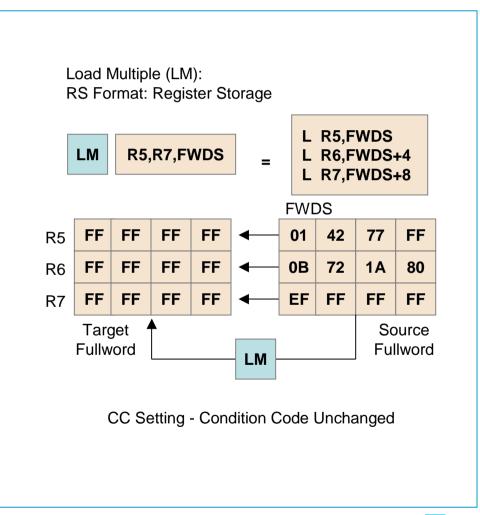

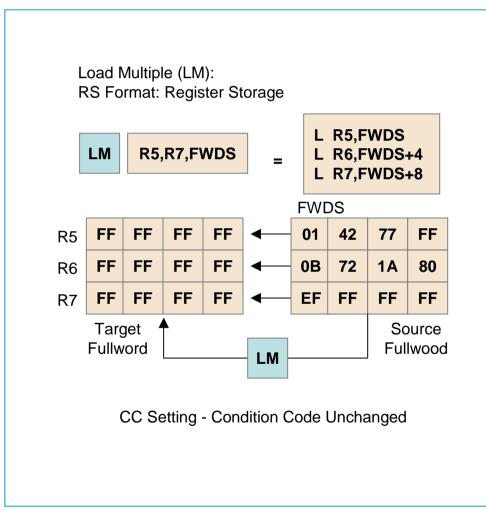

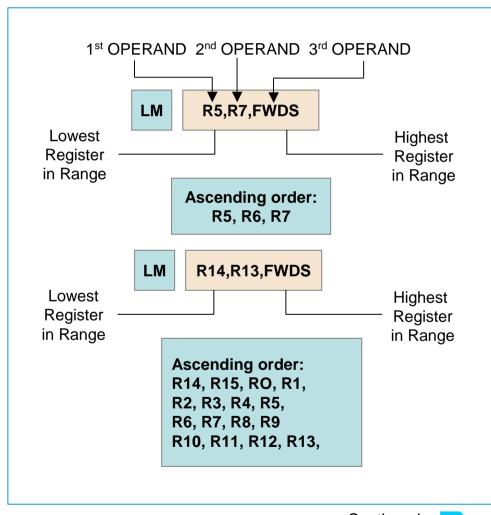

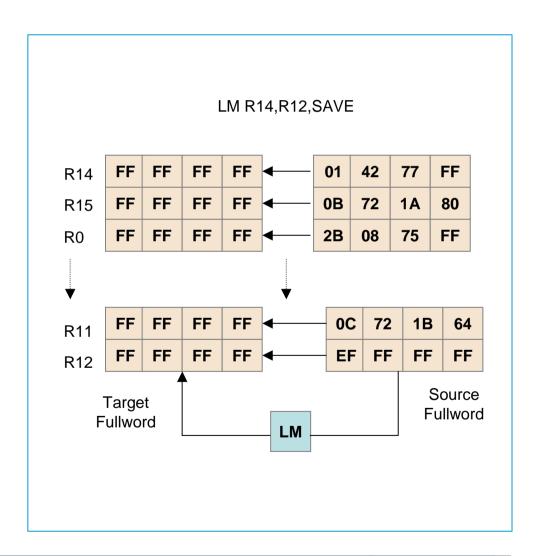

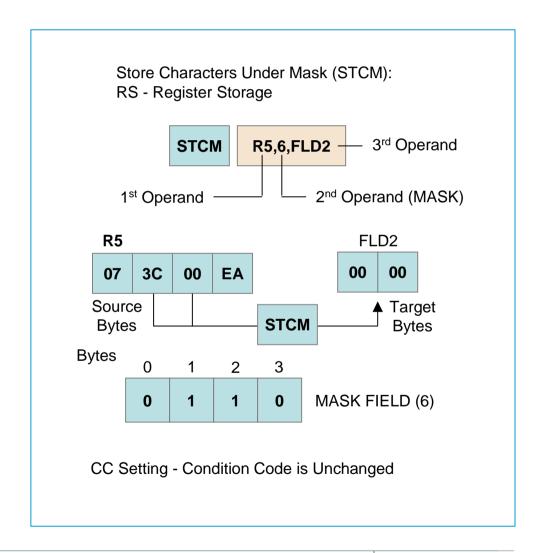

#### **RS** Instruction

#### **Format**

The instruction is 32 bits or 2 halfwords in length. The first byte of the instruction is the opcode. This is followed by the first and third operands, both registers. Finally the second operand, the storage operand, specified in base displacement form.

Note that this instruction has three operands not just two.

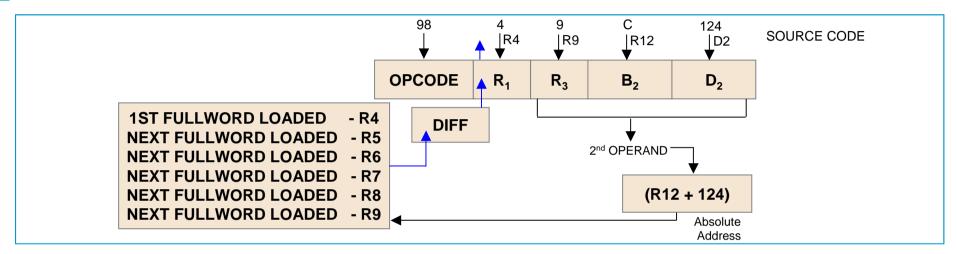

## **RS** Instruction (cont'd)

#### **Format**

9849C124

98 is the opcode for the Load Multiple instruction. The first operand is R4. The third operand is R9.

The second operand is the 6 consecutive full words starting at the storage location, whose absolute address is formed by adding the displacement 124 to the contents of R12, the base register. When this instruction is executed, the first fullword at the storage location would be loaded into R4, the next into R5, the next into R6, the next into R7, the next into R8 and the next into R9.

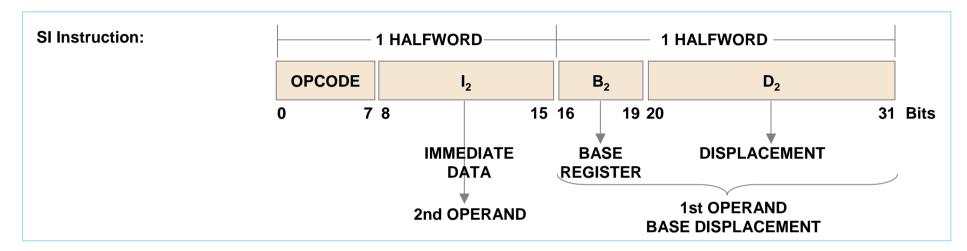

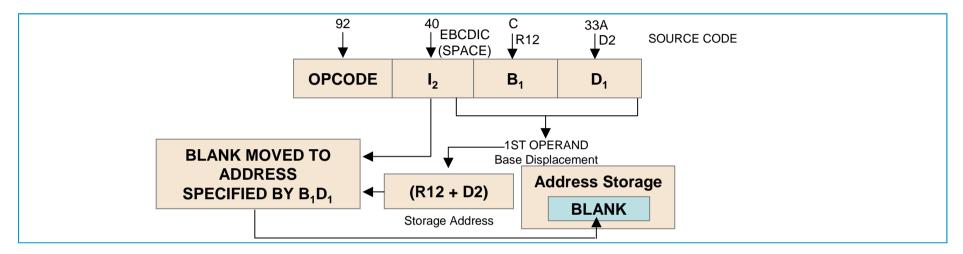

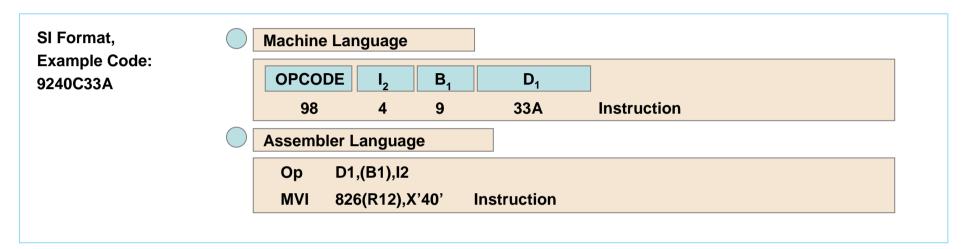

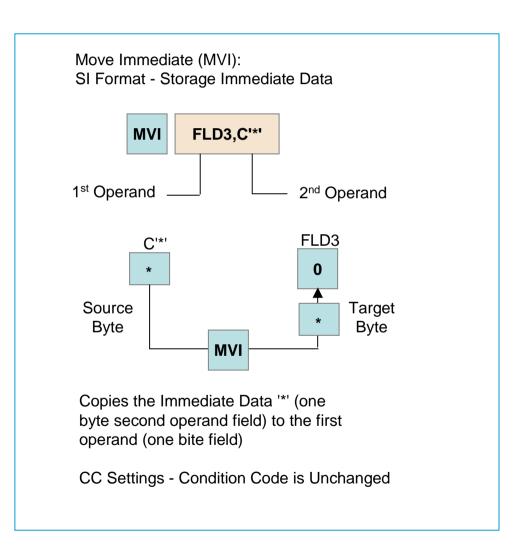

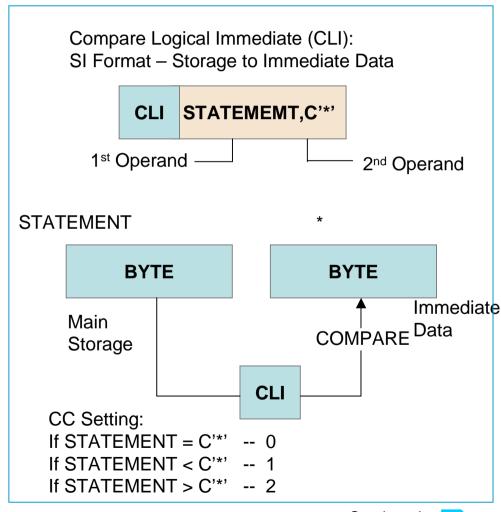

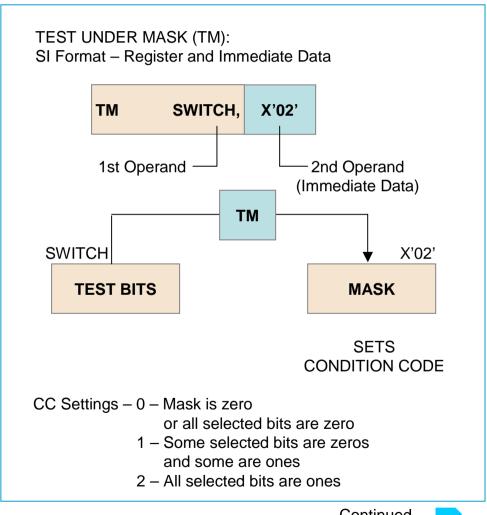

#### **SI** Instruction

#### **Format**

The instruction is 32 bits or two halfwords in length. The first byte of the instruction is the opcode. The next byte is the second operand, an immediate storage operand. This byte contains the actual operand, not an address. The operand is exactly one byte long. The rest of the instruction is the base and displacement specifying the first operand.

## SI Instruction (cont'd)

An example of SI instruction is:

9240C33A

92 is the opcode for the Move Immediate instruction. 40, the EBCDIC code for space, is the second operand.

The first operand is the byte at the absolute storage address formed by adding the displacement 33A to the contents of R12, the base register. When this instruction is executed a blank would be moved to the address specified by the first operand.

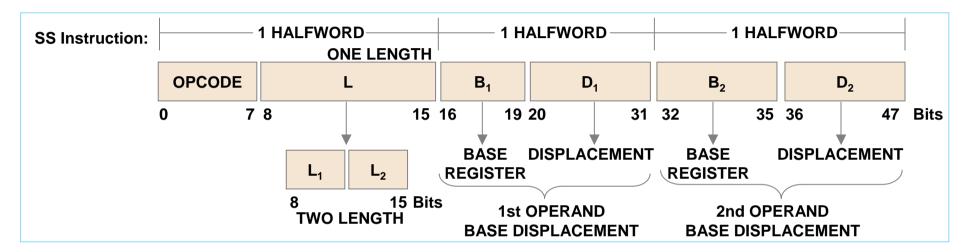

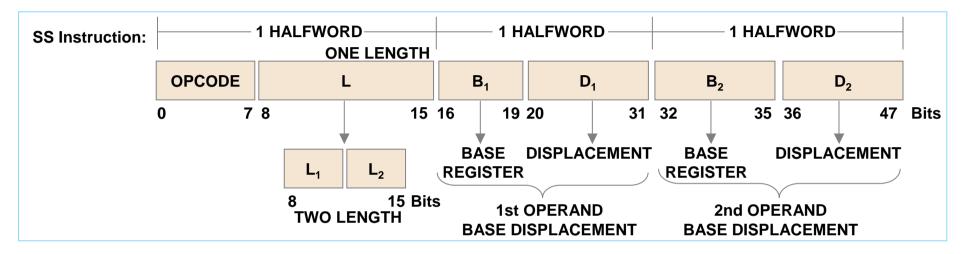

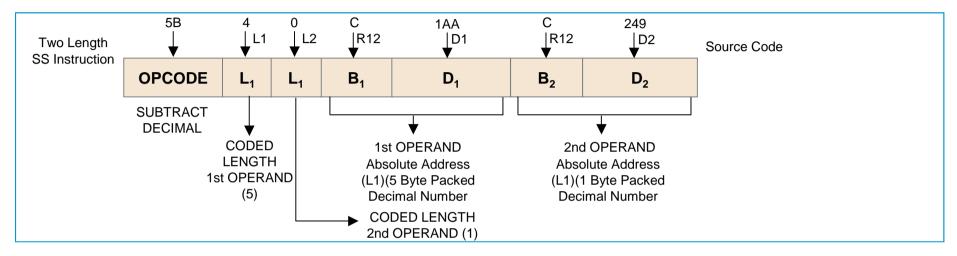

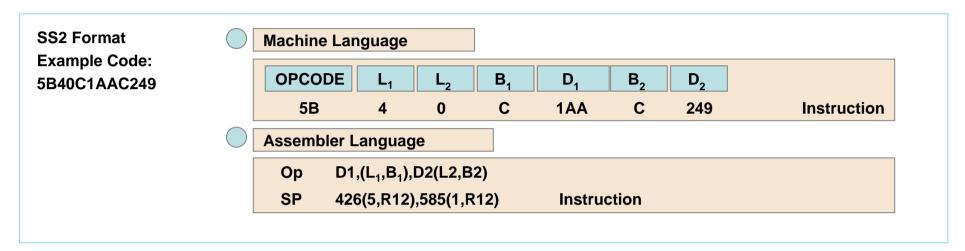

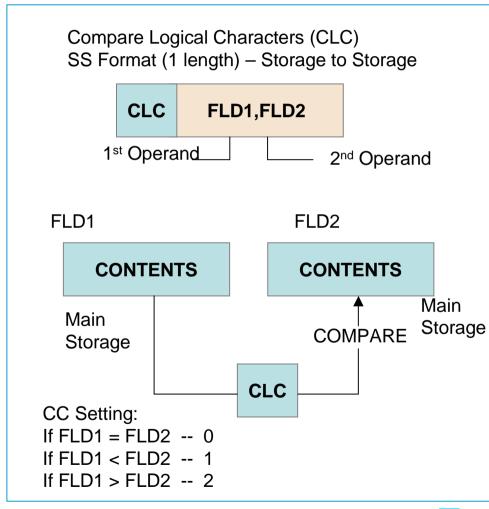

#### **SS** Instruction

#### What are the two formats of SS instructions?

The first format has single length specification, which applies to both of its operands. The second has a separate length specified for each operand.

# SS Instruction (cont'd)

When there are two lengths, each is specified as a nibble, and can contain values from 0 - 15. when there is a single length specification it is a byte in length, and can contain values from 0 - 255.

All lengths in machine instructions are coded as 1 less than the actual length. This is because a zero length dosen't make sense for an operation, and so in order to provide maximum facility, a machine length specification of 0, represents a real length of 1, 1 represents 2, and so on.

The two SS formats are shown above. The instructions are 48 bits or 3 halfwords in length. The first byte is the opcode. The next byte is the length or lengths. This is followed by operand one and operand two, both specified in base displacement format.

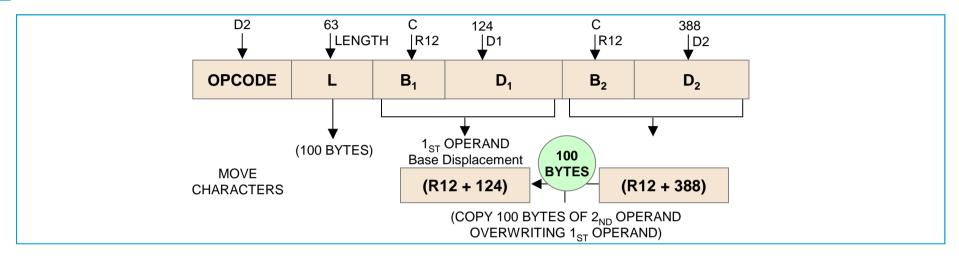

## SS Instruction (cont'd)

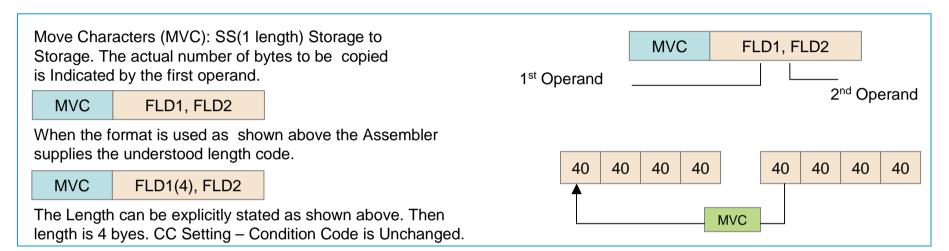

An example of one length SS instruction is:

#### D263C124C388

D2 is the opcode for the Move Characters instruction. 63 is the machine coded length, equivalent to an actual length of 100 bytes.

The first operand is the 100 character string whose absolute address is formed by adding the displacement of 124 to the contents of R12. The second operand is the 100 character string whose absolute address is formed by adding the displacement of 388 to the contents of R12. When this instruction is executed, the 100 bytes of the second operand, would be copied to the first operand, destroying the original value of the first operand.

# **SS Instruction – An Example**

An example of two length SS instruction is: 5B40C1AAC249

5B is the opcode for the Subtract Decimal instruction. 4 is the machine coded length of the first operand, equivalent to an actual length of 5. 0 is the machine coded length of the second operand, equivalent to an actual length of one.

# OS/390 Assembler Programming Introduction

Unit: S/390 Addressing and Instructions Topic: Machine Instruction Formats

# SS Instruction – An Example (cont'd)

An example of two length SS instruction (cont'd)

The first operand is the 5 byte packed decimal number whose absolute address is formed by adding the displacement of 1AA to the contents of R12. The second operand is the 1 byte packed decimal number whose absolute address is formed by adding the displacement of 249 to the contents of R12. When this instruction is executed the value of the second operand will be subtracted from the value of the first, and the difference would replace the first operand.

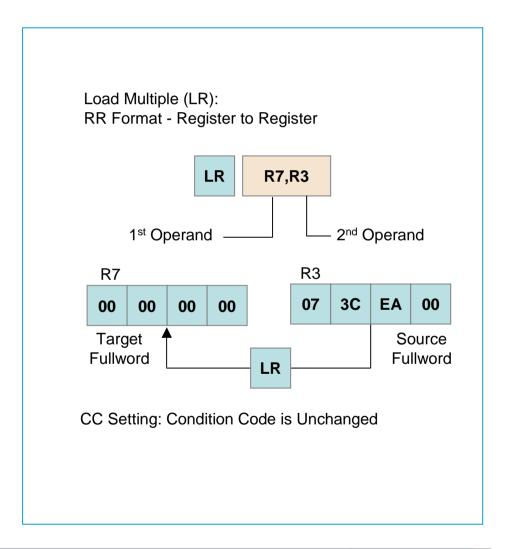

#### Difference in RR Format

In the RR format, the components for both Machine language and Assembler language follow in the same order; operation, operand 1 and operand 2.

#### **Difference in RX Format**

With RX format where we have storage operands, the syntax is quite different. Start with operation, followed by operand1. Operand2 is specified with the displacement first. Notice displacement is decimal in the Assembler language and hexadecimal in machine language.

This is followed by the index register and the base register, separated by a comma, and in parentheses (example: R8, R12).

# Difference in RX Format (cont'd)

With RS format, again notice the opcode and register operands in Assembler Language parallel the machine language format. The storage operand is specified as displacement (decimal), and is followed by the base register in parentheses.

#### **Difference in SI Format**

In SI format, the order of the operands is different in the two formats. In Machine Language, the immediate operand  $I_2$ , precedes the storage operand. In Assembler Language, the storage operand comes first. The immediate operand is specified as a hex value of 40 in the notation shown.

#### **Difference in SS1 Format**

When a length is specified with a storage operand, it is specified as the actual length, and precedes the base register, followed by a comma, within parentheses, for example (100,R12).

If there is only one length, it is placed with the first operand, not the second. Note in the example that the length is 100 decimal.  $100_{10} = 64_{16}$ . The machine length is one less than the actual length, so the machine length is 63.

#### Difference in SS2 Format

This example follows the same pattern as the previous one. In this case there are two lengths, one for each operand. Lengths are coded before the base register, within parentheses.

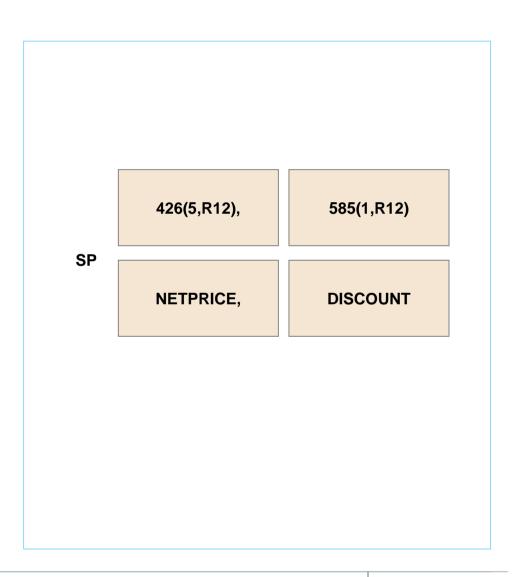

# **Assembler Program**

#### What is an Assembler Program?

Looking at all the instruction formats for both Assembler and Machine Languages may be somewhat intimidating. However the job of the Assembler programmer is not as complex as you might expect. The Assembler program converts your Assembler statements to Machine Language for you.

# Assembler Program (cont'd)

Thus, instead of writing an instruction like this:

SP 426(5,R12),585(1,R12)

You would probably write something like this:

SP NETPRICE, DISCOUNT

# Assembler Language Statements

#### What are Statements?

Assembler Language programs are made up of statements. Statements are composed of characters. Lower case alphabetic characters are considered equivalent uppercase characters by the Assembler, except when used in quoted strings.

### **Characters:**

Alphabetic characters a -z and A- Z

National characters @, \$, and #

Underscore

Digits 0 - 9

Special characters + - , = , \* () ' / &

blank

# **Assembler Language Statements (cont'd)**

# What constitutes Assembler Language Statements?

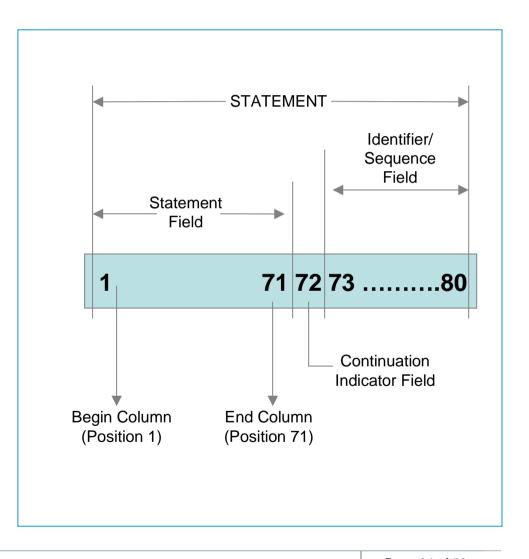

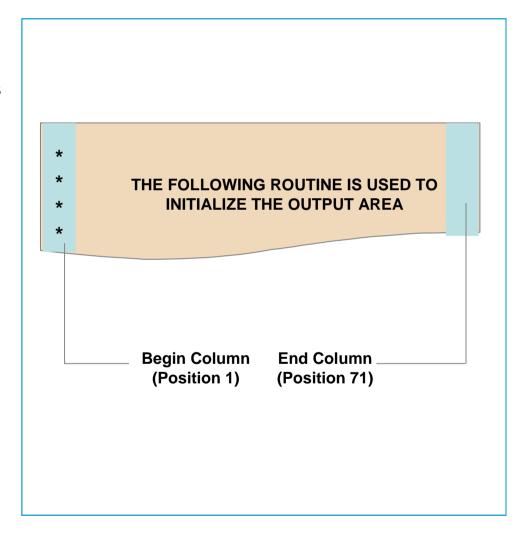

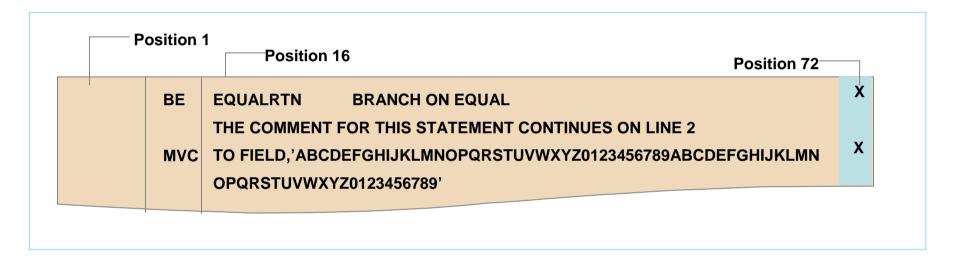

Assembler Language Statements are coded in 80 character records or lines. By default, each 80 character line consists of 3 fields; positions 1-71 constitute the statement field, 72 is the continuation indicator field, and 73-80 is the identifier/sequence field.

Assembler Language statements and comments must be written in the statement field. It consists of:

- Begin Column The first position of the statement field

- Continue Column second and subsequent statements of a continued statement begin

- Continuation Indicator Field The position following the end column

# **Assembler Language Instruction Statements**

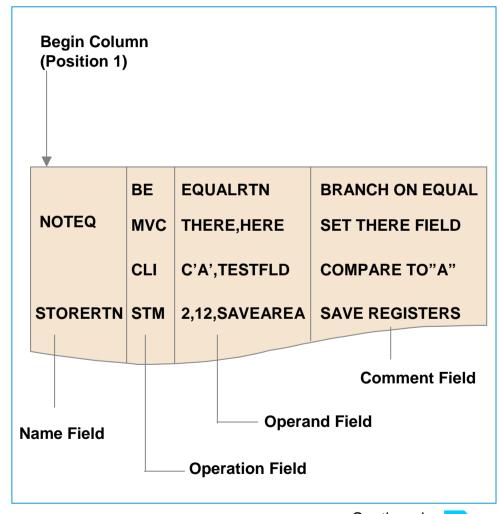

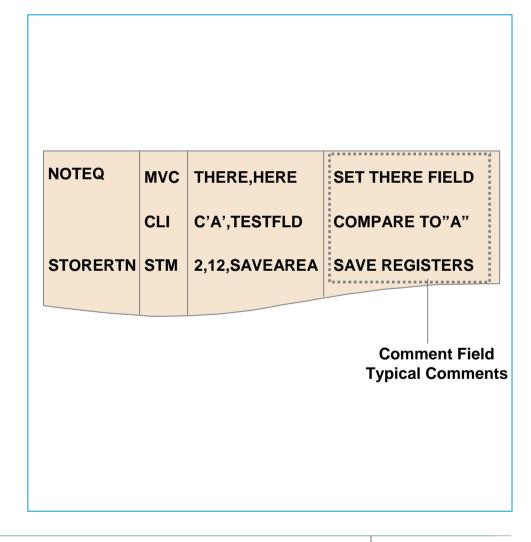

Assembler Language Instruction Statement consists of up to 4 fields, specified in the following order:

- 1. Name

- 2. Operation

- 3. Operand

- 4. Comments

# **Assembler Language Instruction Statements (cont'd)**

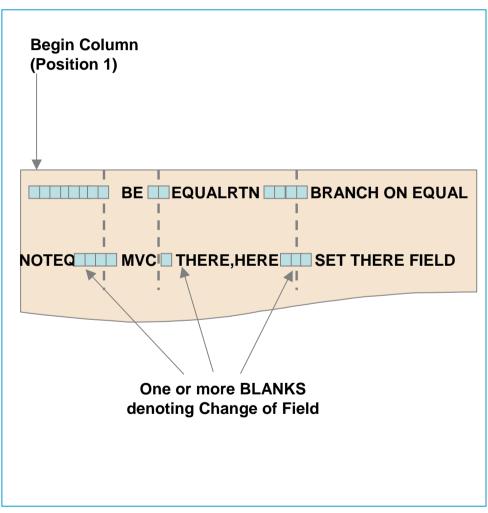

Assembler Language instructions are free format, with one or more blanks delimiting fields. The name field and operation field is separated by one or more blanks, as are the operation and the operand, and the operand and the comment.

Embedded blanks are not allowed in the operand field, unless they are part of a quoted string.

Otherwise they would indicate the end of the operand field.

The name field, if present, must begin in the begin column. If the name field is omitted, the operation field must start after the begin column.

# Assembler Language Instruction Statements (cont'd)

Although the Assembler allows free format statements, most programmers align their fields (operation, operand and comments) in specific positions for readability.

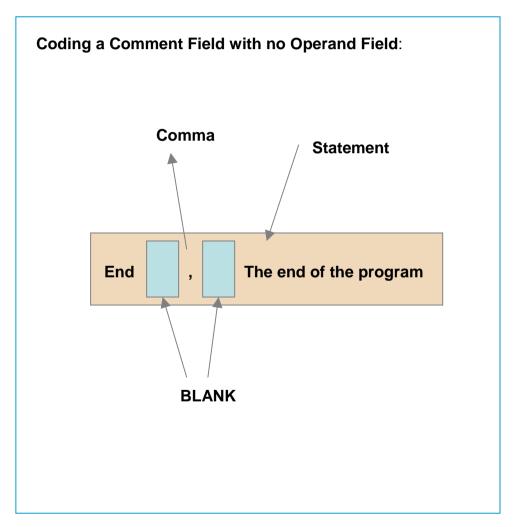

If you wish to code a comment field on a statement with no operand field, you must indicate to the Assembler, that the operand field is missing. You do this by coding a comma, preceded and followed by a blank, between the operation and the comment. An example of this is shown on the right.

#### **Use of Comments**

#### How can you use comments effectively?

As noted previously comments can be included as the fourth field on any Assembler Language instruction statement.

It is also possible to have statements in your program consisting entirely of comments.

An Assembler Language comment statement has an asterisk in the statement in the begin column. The rest of the statement, up to and including the end column, is interpreted as a comment.

# **Use of Comments (cont'd)**

#### How can you use comments effectively?

It is good programming practice to include plenty of comments. It is desirable to clearly document what your code is doing when using a low level language like Assembler Language.

A block of comment statements should describe the purpose of each module and of each major section of code.

Comments should be coded on instruction statements to indicate the purpose of each individual statement.

# **Formatting Assembler Language Statements**

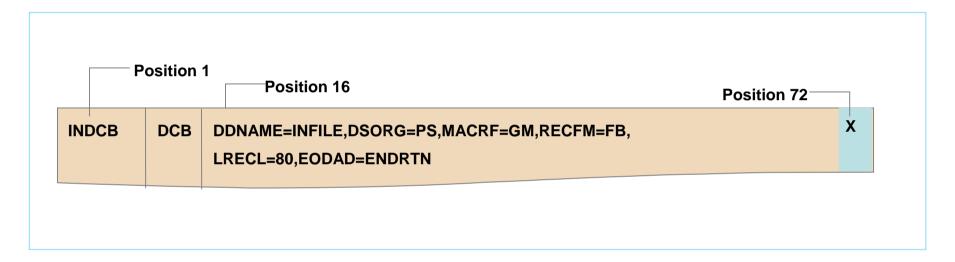

Most Assembler Language statements will easily fit in one line. Sometimes, particularly with complex macro instructions, a statement will not fit on a single line, between the start and end columns.

The example above shows a statement continued on the next line.

# **Breaking Statements**

Following are the two ways of breaking a statement for continuation:

- 1. Code the statement up to the end column, put a non-blank character in the continuation indicator column and resume coding in the continuation column of the next line

- 2. Code the statement to the end of a complete operand and its following comma, put a non-blank character in the continuation indicator column and resume coding with the start of the next operand in the continuation column of the next line

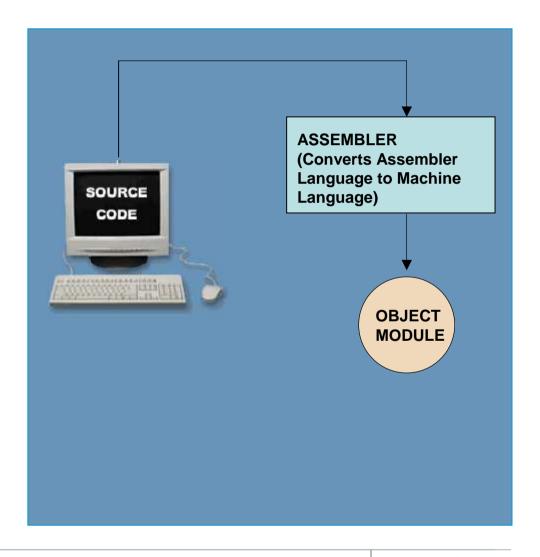

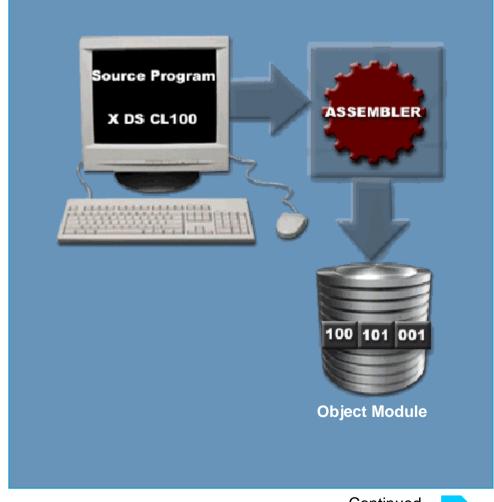

#### **Assembler Functions**

#### What are the functions of an Assembler?

The major purpose of the Assembler is to take a source program, written in Assembler Language and convert it to an object module in Machine Language. This conversion includes:

- Converting Assembler Language mnemonic opcodes into Machine Language numeric opcodes

- Converting the Assembler Language instruction formats into Machine Language forms

- Converting the numeric notation used in the source program (decimal by default) to hexadecimal form used in the Machine Language

- Determining the address of all the instructions and data areas used in the program

- Converting reference symbols into base displacement addresses

## Unit: The Program Development Process Topic: The Assembly Process

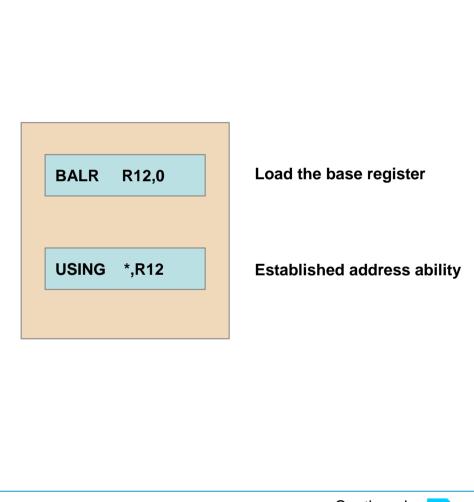

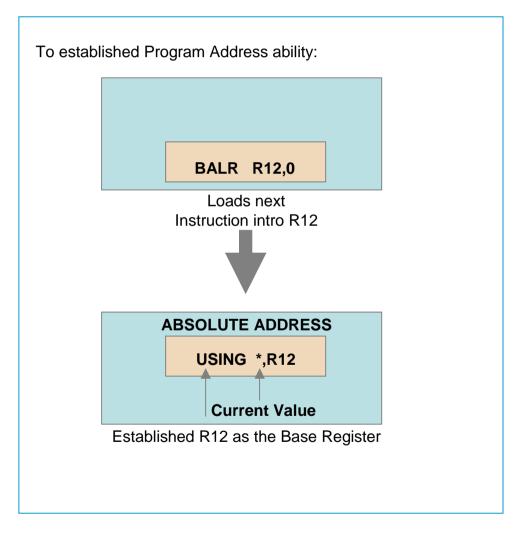

## **Converting Addresses to Base-Displacement Format**

#### What is USING Instruction?

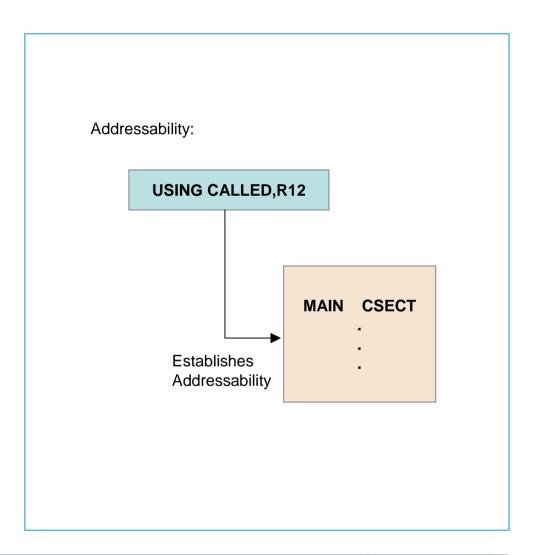

In order for the Assembler to convert addresses to base-displacement format, you must tell the Assembler what register to use as a base register, and what value the register will contain at execution time. This information is provided with the USING instruction.

You must also include machine instructions in your program, to load the proper value into the base register at execution time. A standard way of accomplishing these two actions is with the following instructions, included as part of the program initiation:

BALR R12,R0 and USING\*, R12

## Unit: The Program Development Process Topic: The Assembly Process

# Converting Addresses to Base-Displacement Format (cont'd)

The first of these instructions, a Machine instruction, places the absolute address of the next instruction after BALR into register 12. The \* symbol is used to represent the current value of the location counter in an Assembler program. The USING instruction tells the Assembler that R12 is to be used as the base register, and that R12 will contain the address of the current instruction.

Since BALR has in fact loaded R12 with the address of the instruction following BALR (which is now the current instruction) this correctly establishes addressability in the program.

## **SS Instruction Example**

As previously discussed, storage operands can be represented as either symbols, or in base displacement format. The Assembler allows certain portions of the base displacement, base index displacement, or base length displacement forms to be omitted, and uses default values for the omitted parts.

This process is indicated in the table on the right.

After the Assembler produces an object module it can be linked and executed.

| Full<br>Operand | From<br>Omission | Assembler<br>Default              |  |

|-----------------|------------------|-----------------------------------|--|

| D (B)           | D                | B=0                               |  |

| D (X,B)         | D                | X=0 , B=0                         |  |

|                 | D (X)            | B=0                               |  |

|                 | D (,B)           | X=0                               |  |

| D (1,B)         | D                | B=0 , 1=length<br>Attribute of D  |  |

|                 | D (1)<br>D (,B)  | B=0<br>1=length attribute<br>of D |  |

# **Define Storage Instruction**

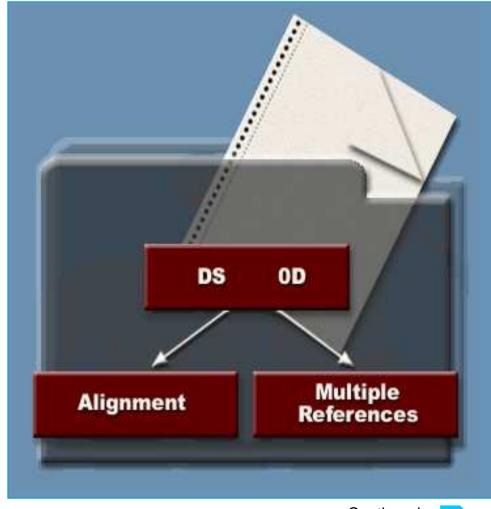

#### What is Define Storage (DS) Instruction?

The Define Storage (DS) Assembler instruction is used to define storage areas within a program.

If you wish to assign a name to the storage being defined, you specify a symbol in the name field of the DS instruction. The operation for defining storage is DS.

Since DS does not define an executable instruction, but rather sets up an area of storage, it is an Assembler instruction.

Continued...

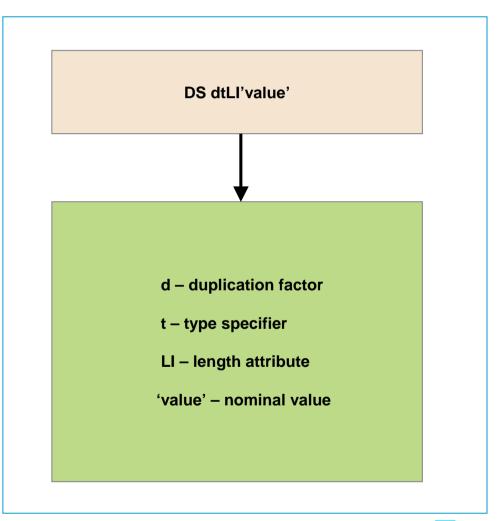

## **Define Storage Instruction (cont'd)**

#### What are the components of a DS statement?

The operand field of a DS statement consists of up to 4 components, which are:

- A duplication factor

- A type specifier

- A length modifier

- A nominal value

## **Components of a DS Statement**

The type specifier must be supplied, while the other three components are optional.

The duplication factor and the length modifier has default values when not coded explicitly.

The nominal value field is not used, and is simply considered as documentation since it is defining storage, not a constant.

A common mistake is coding a nominal value in a DS statement, when a DC statement is intended. This is not flagged as an error by the Assembler, since the syntax is correct, but will likely produce an execution time error.

## Components of a DS Statement (cont'd)

| Data Type Specifier |            | Default Length | Default Alignment |  |

|---------------------|------------|----------------|-------------------|--|

| Character           | С          | 1              | byte              |  |

| Hexadecimal         | X          | 1              | byte              |  |

| Binary              | В          | 1              | byte              |  |

| Zoned Decimal       | Z          | 1              | byte              |  |

| Packed Decimal      | Р          | 1              | byte              |  |

| Halfword            | Н          | 2              | halfword          |  |

| Fullword            | Fullword F |                | fullword          |  |

| Long Floating Point | D          | 8              | doubleword        |  |

The type specifier indicates the type of data the field should contain. Each data type is specified by a single character identifier, and has a default length and alignment. The most common field types are indicated above.

#### Example:

To define a fullword called FWD1, you would specify the following statement as indicated: FWD1 DS F

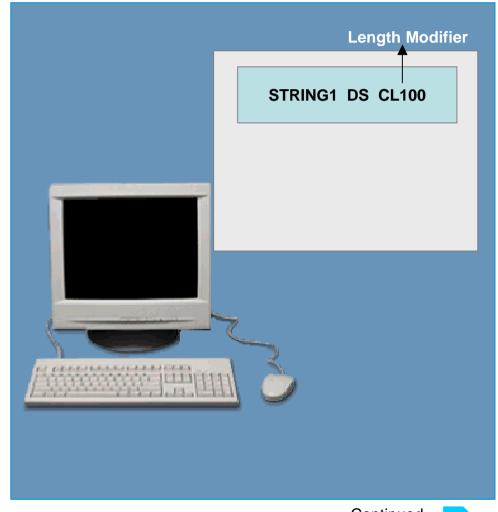

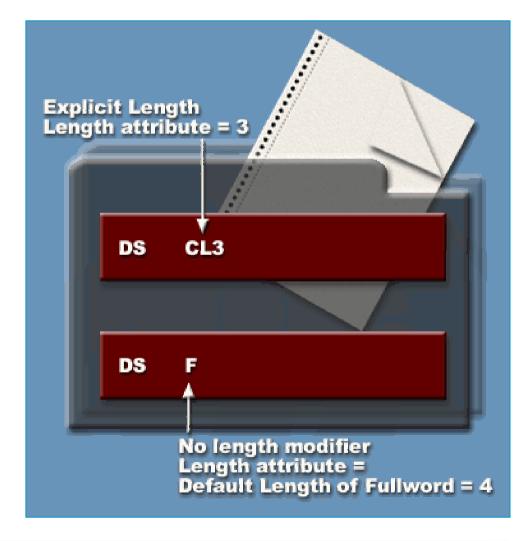

## **Length Modifier**

#### What is the function of a length modifier?

Often you wish to define a field with a length different from a default length. To do this, you specify a length modifier. This consists of the letter L, followed by the desired field length in bytes. It is placed immediately following the type specifier.

To define a character field 100 bytes long, called STRING1, you would specify:

STRING1 DS CL100

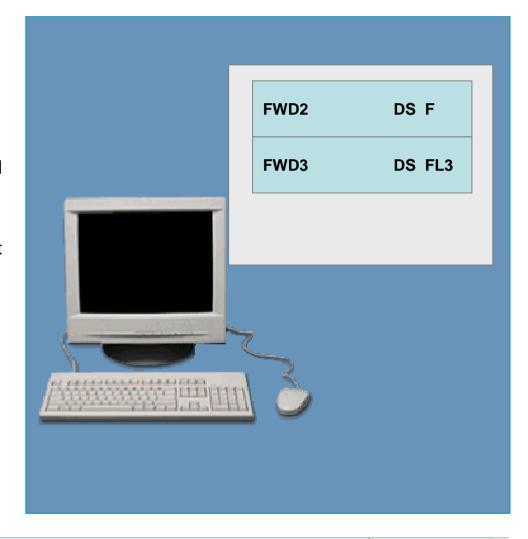

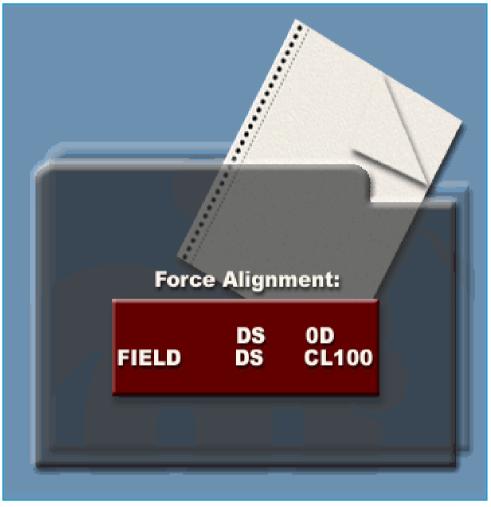

## Length Modifier (cont'd)

For fields that are aligned on other than a byte boundary, specifying a length modifier removes the alignment guarantee, and reverts to byte alignment.

There is a guarantee that FWD2 would be aligned on a fullword boundary. There is no boundary alignment guarantee for FWD3. One way to force boundary alignment even if the definition does not guarantee it, is to precede the field with another statement that forces the desired alignment.

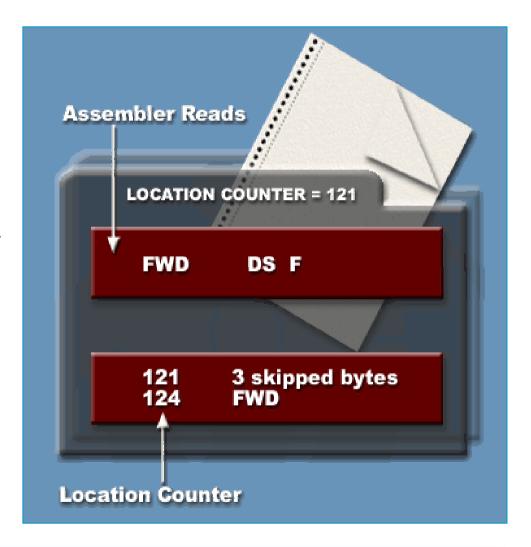

#### **Location Counter**

The Assembler assigns each new field you define immediately following the previous one, except when alignment is required.

The Assembler maintains a location counter (LC), which starts at zero at the beginning of the Assembly, and is increased by the length of each assembled instruction as the assembler proceeds. If the alignment is required, and the value of the location counter is not at an address that would provide the appropriate alignment, then the Assembler skips enough bytes to such an address that provides the required alignment. The skipped bytes are not initialized to any specific value.

## **Length Attribute**

The value specified as the length modifier, or the default length if no length modifier is coded, is the length attribute of the field. The Assembler associates a length attribute to each field you define, and you may use it in assembling SS type Machine instructions, which reference the field.

## The Duplication Factor

#### What is the duplication factor?

The duplication factor, if it is provided, is coded as the first part of the operand, preceding the type specifier. If the duplication factor is omitted, a default value of 1 is assumed. The duplication factor specifies the number of occurrences of the specified type and length specified.

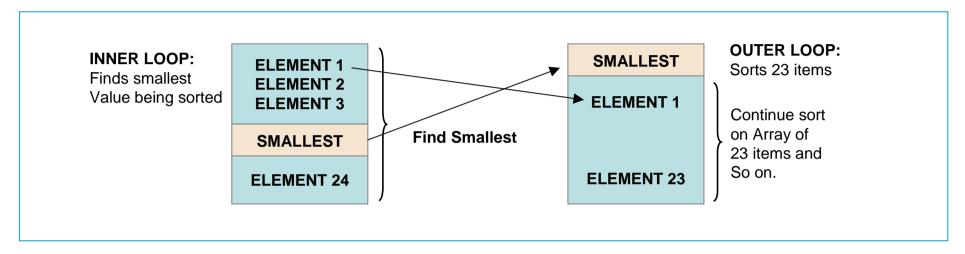

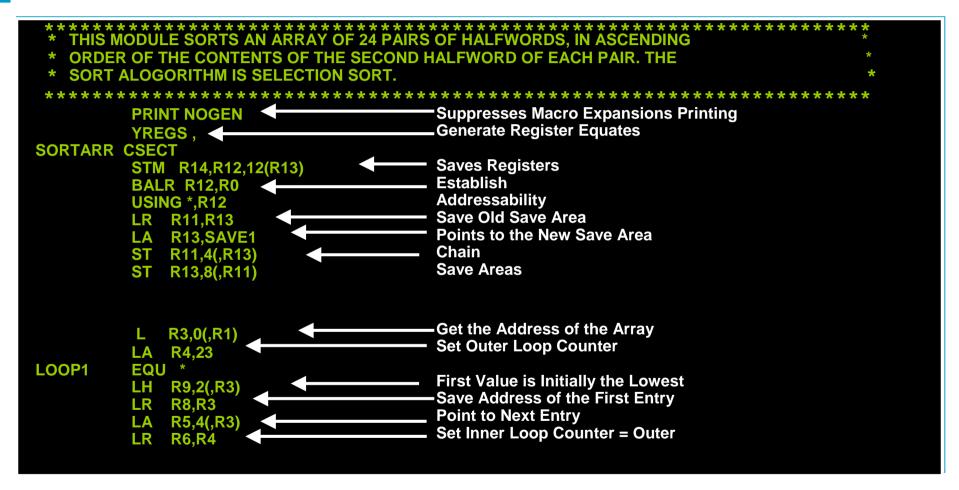

- 1 To define a program save area of 18 fullwords, we would code: SAVEAREA DS 18F

- 2 To define an array with 24 entries to hold hourly temperature readings (represented as halfwords) for one day we would code: TEMPARR DS 24H

- 3 To define an array to hold the marks of 100 students, each represented by a 2 byte packed decimal number we would code: MARKS DS 100PL2

The amount of storage allocated by a DS instruction is the product of the duplication factor and the length.

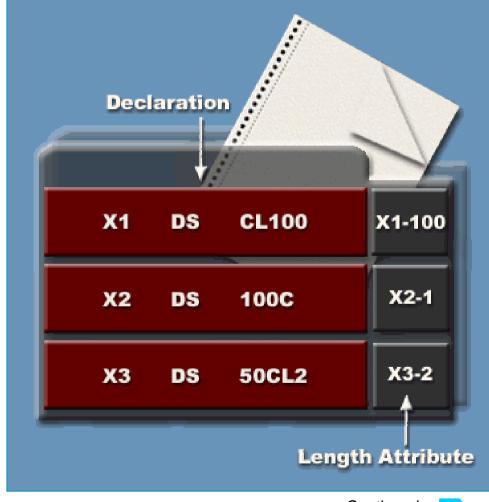

## **The Length Attribute**

#### Why is the length attribute important?

Consider the following three declarations on the right. What is the difference between them?

They all allocate 100 bytes of storage, which is defined as character type. Are they identical in effect? Not quite. Remember that each data item as a length attribute assigned to it. The length attribute is the implicit or explicit length modifier. Thus the length attribute of the three declarations are as shown on the right:

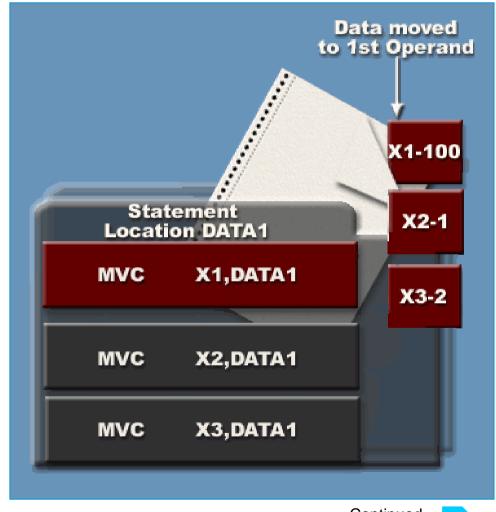

## The Length Attribute (cont'd)

# What is the effect of the following 3 statements on the right?

All three of these statements move data from the location DATA1 to the destination (first operand) field. In the first case, 100 bytes of data are moved. In the second case, only 1 byte is moved and in the third case 2 bytes are moved.

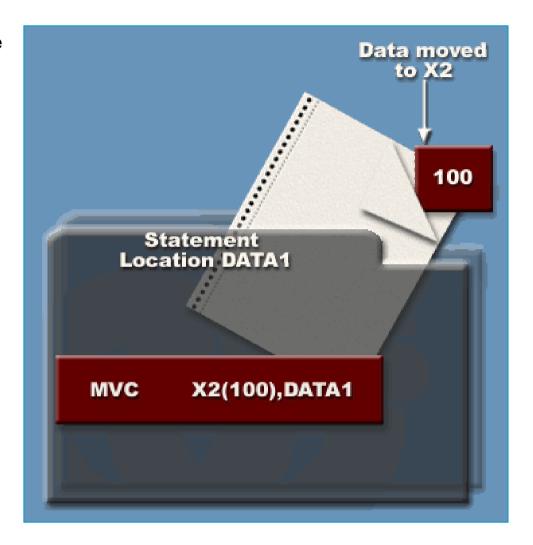

## The Length Attribute (cont'd)

To move 100 bytes of data from DATA1 to X2, the length would need to be coded explicitly in the MVC instruction. It would look like the statement on the right.

When an explicit length is omitted in an SS instruction, the length attribute of the destination field is used.

## **Use of Duplication Factors**

#### Why are zero duplication factors used?

To specify a duplication of zero is a special situation of a data declaration. Why is this done?

Remember that the amount of storage allocated is the product of the duplication factor and the length. If the duplication factor is zero, so is the product of duplication factor and length, so no storage is allocated.

#### **Use of Duplication Factors (cont'd)**

# Common reasons for using zero duplication factors:

One reason is to force alignment.

Suppose a 100 - byte character field is to be defined which is aligned on a doubleword boundary. The easiest way to do this is to define a doubleword (forcing doubleword alignment) immediately followed by the character field. Since the doubleword is not actually used for anything, other than to force alignment, it is defined with a duplication factor of zero. It does not even have to be given a name, since it will not be used. Its only purpose is to cause the Assembler to skip enough bytes to move to the doubleword boundary.

Thus the definition looks as it does on the right.

## **Use of Duplication Factors (cont'd)**

In the other situation a zero duplication factor is often used is when the same piece of storage is defined in two or more different ways.

Suppose an area of storage is to be set up to hold a record that will be read into our program from disk. The record is 120 bytes in length, but suppose this record contains 3 fields, each 40 bytes in length. When reading the record the programmer wishes to treat it as a single 120-byte field. After it is read, the programmer wants to process its fields separately. It can be accomplished using a zero duplication factor on the first definition.

The definition is shown on the right.

| MULTIPLE REFERENCES TO DATA |    |        |  |

|-----------------------------|----|--------|--|

| RECORD                      | DS | 0CL120 |  |

| FLD1                        | DS | CL40   |  |

| FLD2                        | DS | CL40   |  |

| FLD3                        | DS | CL40   |  |

| RECORD |      |      |  |

|--------|------|------|--|

| FLD1   | FLD2 | FLD3 |  |

# **Use of Duplication Factors (cont'd)**

The RECORD is defined with a zero duplication factor, the actual space assigned to it is 0 \* 120 = 0.

The length attribute of RECORD is 120. FLD1 has the same location as RECORD, but has a length attribute of 40. The space assigned by the Assembler is 1 \* 40 = 40.

The address of FLD2 is 40 higher than the address of FLD1. FLD2 also has a length attribute of 40 as does FLD3.

The fields can be broken down even further. FLD1 could consist of 4 smaller fields.

| MULTIPLE REFERENCES TO DATA |    |        |  |

|-----------------------------|----|--------|--|

| RECORD                      | DS | 0CL120 |  |

| FLD1                        | DS | 0CL40  |  |

| FLD1A                       | DS | CL5    |  |

| FLD1B                       | DS | CL15   |  |

| FLD1C                       | DS | CL8    |  |

| FLD1D                       | DS | CL12   |  |

| FLD2                        | DS | CL40   |  |

| FLD3                        | DS | CL40   |  |

|                  | RECORD                |                  |                  |      |      |

|------------------|-----------------------|------------------|------------------|------|------|

|                  | FLD1                  |                  |                  |      |      |

| F<br>L<br>D<br>1 | F<br>L<br>D<br>1<br>B | F<br>L<br>D<br>1 | F<br>L<br>D<br>1 | FLD2 | FLD3 |

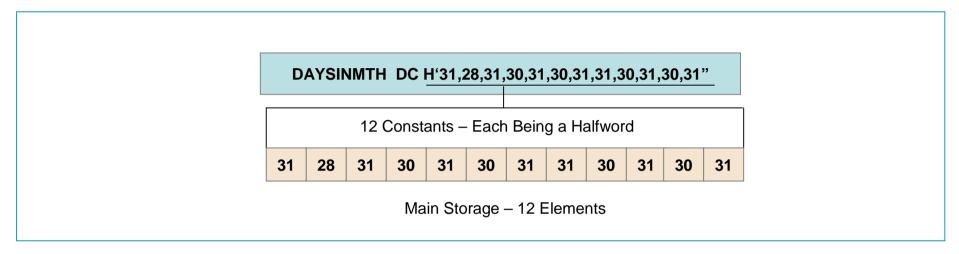

## **Define Constant (DC) Instruction**

#### What is Define Constant (DC) Instruction?

The Define Constant (DC) instruction is used to define constants. In fact the term constant is somewhat misleading since there is no guarantee that the storage set up by a DC Assembler instruction will remain constant throughout program execution. In fact, what DC does is to define storage and initialize it to the value you specify in the DC instruction.

The operand field of DC contains the same 4 components as the DS instruction, but the nominal value field is compulsory. The nominal value specifies the value to which the field is initialized.

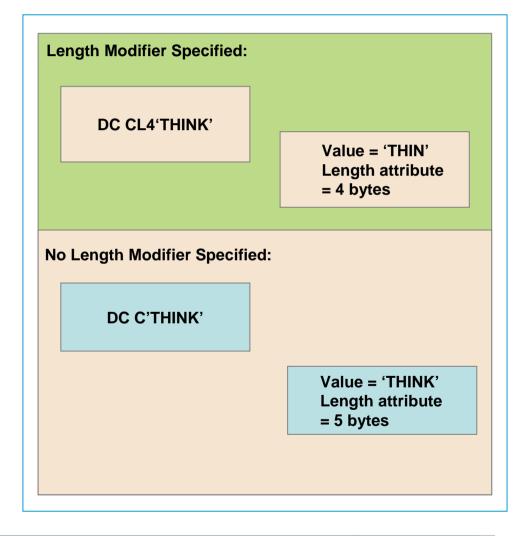

## Length of a Field

The length of a field defined by a DC statement can be established in one of two ways. If a length modifier is specified in the definition, that length is the one used.

If no length modifier is specified, then the length required to hold the nominal value is used. If an explicit length is specified, and it does not agree with the length of the nominal value, then the nominal value is either padded or truncated to fit the explicitly specified field length.

The way that padding or truncation is done depends on the field type. For character constants, the nominal value is left justified and padded on the right with blanks if it is shorter than the field length. It is truncated on the right if it is too long. The nominal value is specified as a series of characters.

#### **Character Value**

The Assembler converts the character value specified in the definition into EBCDIC code. In the following examples, we will represent the field contents (EBCDIC) in hex notation.

With no length modifier the length is determined by the nominal value

Definition Field Contents

CFLD1 DC C'ABC' C1C2C3

Explicit length of 5, the nominal value is left justified and right padded with blanks

Definition Field Contents CFLD2 DC CL5'ABC' C1C2C34040

Explicit length of 2, the nominal value is left justified and right truncated

Definition Field Contents CFLD3 DC CL2'ABC' C1C2

Duplication factor of 2, with length determined by the nominal value

Definition Field Contents CFLD4 DC 2C'ABC' C1C2C3C1C2C3

## Character Value (cont'd)

The maximum length of a character constant is 256 bytes.

Duplication factor of 2 and explicit length of 3

Definition Field Contents

CFLD5 DC 2CL3'ABC' C1C2C3C1C2C3

Explicit length of 10, the nominal value is left justified and right padded with blanks

Duplication factor of 10, length of 1 is determined by the nominal value

Definition Field Contents

CFLD7 DC 10C'\*' 5C5C5C5C5C5C5C5C5C

#### **Hexadecimal Constants**

#### When do you use hexadecimal constants?

Hexadecimal constants, like other numeric constants, are right justified in their field, padded on the left with zeroes or truncated on the left if needed. The nominal value is specified as a series of hexadecimal characters. The examples below illustrate the use of hexadecimal constant definitions.

With no length modifier the length is determined by the nominal value

Definition Field Contents

XFLD1 DC X'3C2F' 3C2F

Explicit length of 3 is longer the nominal value. Field is right justified and left padded with zeros.

Definition Field Contents XFLD2 DC XL3'3C2F' 003C2F

Explicit length of 1 is shorter then the nominal value. Field is left truncated.

Definition Field Contents XFLD3 DC XL1'3C2F' 2F

Field must contain an even number of nibbles. Leading zero is inserted.

Definition Field Contents XFLD4 DC X'ABC' 0ABC

## Hexadecimal Constants (cont'd)

With data types other than character, multiple values can be defined in a single DC statement, by separating the values with commas.

Duplication factor of 2 and and padded to an even number of nibbles.

Definition Field Contents XFLD5 DC 2X'ABC' 0ABC0ABC

Duplication factor of 3 and left truncated to 3 bytes.

Definition Field Contents XFLD6 DC 3XL3'1234567AB' 4567AB4567AB

Two values, with each length determined from the length of the nominal value.

Definition Field Contents XFLD7 DC X'AB,CDE' AB0CDE

## **Binary Constants**

#### When do you use binary constants?

As a numeric type, binary constants are right justified, truncated on the left or padded on the left with zeroes. The nominal value is specified as a string of bits (ones and zeroes).

Both binary and hexadecimal constants have a maximum length of 256.

With no length modifier, length is determined by the nominal value. Three leadings zero bits are added to form a complete byte.

Definition Field Contents (Hex)

BFLD1 DC B'10111' 17

Length modifier of 2 determines the field length. The field is padded on the left with zeros.

Definition Field Contents

BFLD2 DC BL2'10111' 0017

Length modifier of 1 determines the field length. The nominal value is right justified and left truncated.

Definition Field Contents (Hex)

BFLD3 DC BL1'10101010101' 55

Duplication factor of 2, left padded with zeros to form a complete byte.

**Definition** Field Contents (Hex)

BFLD4 DC 2B'101101' 2D2D

#### **Zoned Decimal Format**

# What are the two formats of decimal numbers?

There are two formats of decimal numbers, zoned decimal and packed decimal.

Zoned decimal is represented one digit per byte, with each byte consisting of a zone nibble and a numeric nibble.

In packed decimal format, each byte contains two numeric nibbles, except the rightmost, which contains one numeric nibble and the sign nibble.

The zone nibble is F in all nibbles except the rightmost, where it is a sign (usually C for + and D for -).

## **Zoned Decimal Format (cont'd)**

As with other numeric types, decimal constants are right justified, padded on the left with zeroes or truncated on the left.

Some examples of zoned decimal constants are shown on the right.

With no length modifier, length is determined by the nominal value.

Definition Field Contents ZFLD1 DC Z'12345' F1F2F3F4C5

Explicit length of 6, so field is left padded with a zero.

Definition Field Contents ZFLD2 DC ZL6'12345' F0F1F2F3F4C5

Explicit length of 4, so field is left truncated.

Definition Field Contents (Hex) ZFLD3 DC ZL4'12345' F2F3F4C5

Three separate constants.

Definition Field Contents (Hex) ZFLD4 DC Z'1,-2,3' C1D2C3

**Duplication factor of 2.**

Definition Field Contents ZFLD5 DC 2ZL3'125' F1F2C5F1F2C5

#### **Packed Decimal**

Although decimal numbers are integers, you can specify nominal values that have an embedded decimal point. In such cases, the decimal point is ignored. The technique can be useful for documentation purposes, if the numbers are being used to represented a quantity with a decimal, such as dollars and cents. The hardware treats the value as an integer, but the programmer can provide code to present the number with a decimal point when it is printed.

The maximum length of a decimal constant is 16 bytes.

With no length modifier, length is determined by the nominal value.

Definition Field Contents

PFLD1 DC P'12345' 12345C

Explicit length of 4, so left padded with a zeros.

Definition Field Contents

PFLD2 DC PL4'12345' 0012345C

Explicit length of 2, so left truncated.

Definition Field Contents (Hex)

PFLD3 DC PL2'12345' 345C

Three constants, last two padded.

Definition Field Contents (Hex)

PFLD4 DC P'1,37,-4892' 1C037C04892D

Decimal point is ignored, left padded with zeros.

Definition Field Contents

PFLD5 DC PL4'39.45' 0003945C

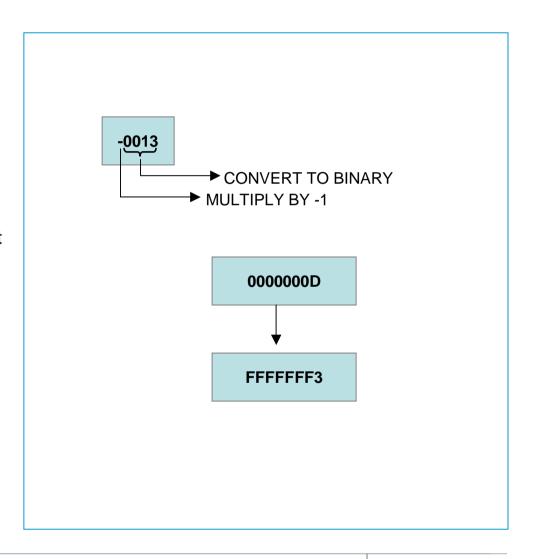

#### **Fixed Point Numbers**

Fixed-point numbers (halfwords and fullwords) are represented internally in true binary format for positive numbers and in two's complement form for negative numbers. The nominal value is coded in decimal.

Constant is 2 bytes (1 halfword) long, represented in true binary

Definition Field Contents

HFLD1 DC H'10' 000A

Constant is 2 bytes (1 halfword) long, represented in two's complement form.

Definition Field Contents

HFLD2 DC H'-5' FFFB

**Duplication factor of 2.**

Definition Field Contents (Hex) HFLD3 DC 2H5'5' 00050005

Three constants.

Definition Field Contents HFLD4 DC H'50,-10,160' 0032FFF600A0

## Fixed Point Numbers (cont'd)

The nominal value is coded in decimal.

Constant is 4 bytes (1 fullword) long, represented in two's complement.

Definition Field Contents FFLD1 DC F'255' 000000FF

Constant is 4 bytes (1 fullword) long, represented in two's complement.

Definition Field Contents FFLD2 DC F'-100' FFFFF9C

**Duplication factor of 3.**

Four constants.

Definition Field Contents

FFLD4 DC FL'31,28,31,30' 0000001F0000000

1C0000001F0000001E

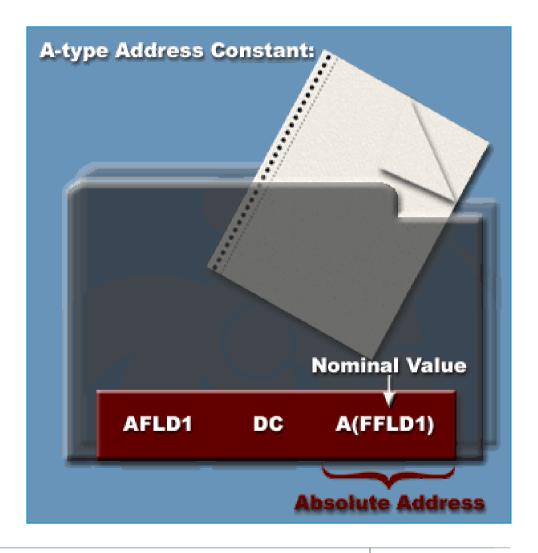

#### **Address Constant**

#### What is an Address Constant?

The final type of constant is called an address constant. There are several types of address constants, but only one will be discussed. An Atype address constant is 4 bytes long by default and is aligned on a fullword boundary. An Atype address constant contains the absolute address of its operand. The nominal value of an address constant is specified within parentheses, rather than quotes.

To have the Assembler generate an address constant containing the address of FFLD1, you would specify:

AFLD1 DC A(FFLD1)

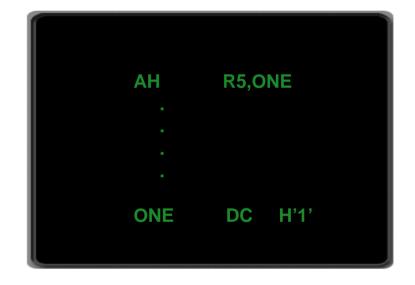

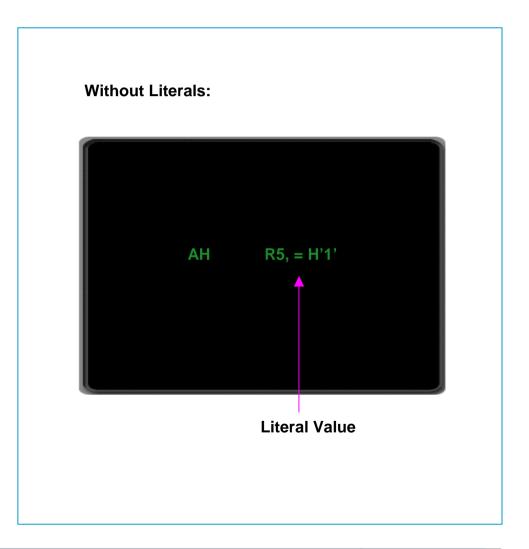

#### Literals

#### What are Literals?

Literals are used as a shortcut in Assembler Language programming.

Suppose you wished to add 1 to the fixed-point value in GPR 5.

One way to do this would be to be to code a constant with a value of 1, and then add that constant to the register. An example of the code is shown on the right.

#### Without Literals:

## Literals (cont'd)

#### What are the uses of literals?

Using a literals allows you to eliminate the separate definition of the constant. A literal is represented as an equal sign, followed by a value that would be valid in the operand field of a *DC* instruction.

In the example, =H'1' is the literal value. What actually happens when you code a literal is that the assembler sets up a constant, at some place in storage (called the literal pool) and places the address of that constant in the operand field of the *AH Instruction*.

## **Addressability**

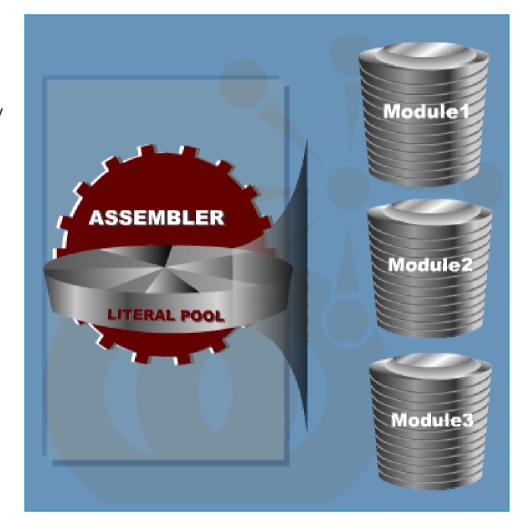

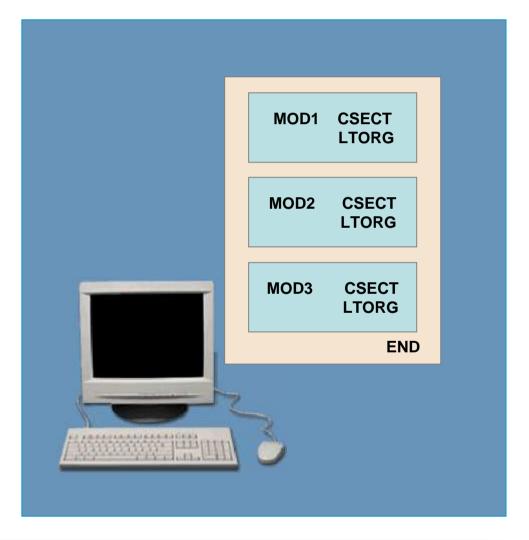

The Assembler creates an area called literal pool and places all literals into that area. The assembler provides the programmer with some control over where that literal pool is created. Why should we care? One reason is that some programs are composed of *multiple modules*, each of which establishes it own *addressability*.

A value defined in one module may not be addressable by code in another module. Each module should be self-contained. Unless we tell the Assembler differently, it will create a single literal pool for all the modules in the assembly. This is likely to produce addressability problems.

#### **Functions of LTORG Instruction**

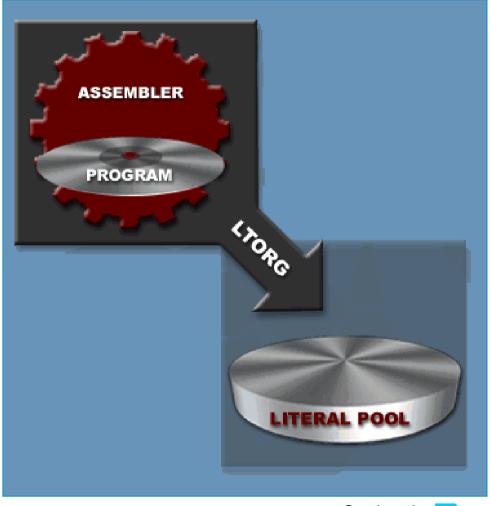

#### What is the function of the LTORG?

The assembler instruction that directs the location of the literal pool is *LTORG*. It does not have any operands. If you do not use any *LTORG* instructions in your program, the literal pool is placed at the end of the *first control section* (*CSECT*) of your program.

When the *assembler* encounters a *LTORG* instruction within a program, it creates a literal pool at that point, containing all the literals specified since the last *LTORG* instruction, or since the beginning of the program, if this is the first *LTORG*.

Unit: Defining Data Topic: Literals

# Functions of LTORG Instruction (cont'd)

To avoid addressability problems in multimodular programs, you should code a LTORG instruction as the last instruction of each control section in the program. So, each CSECT will have its own literal pool at the end of the module.

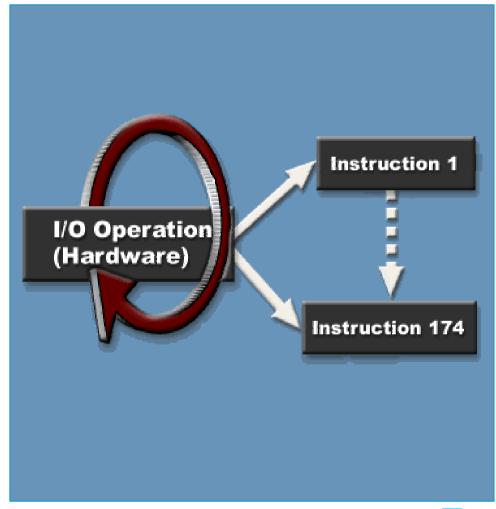

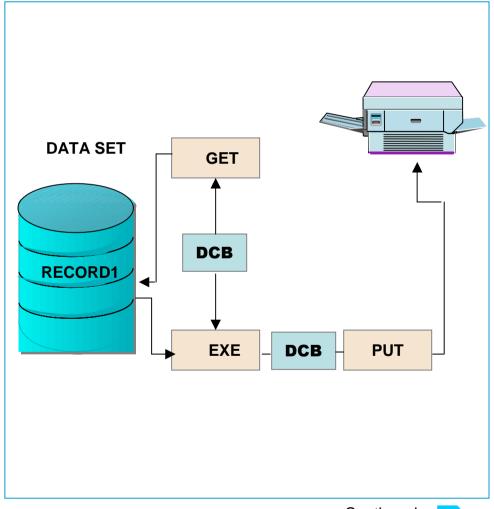

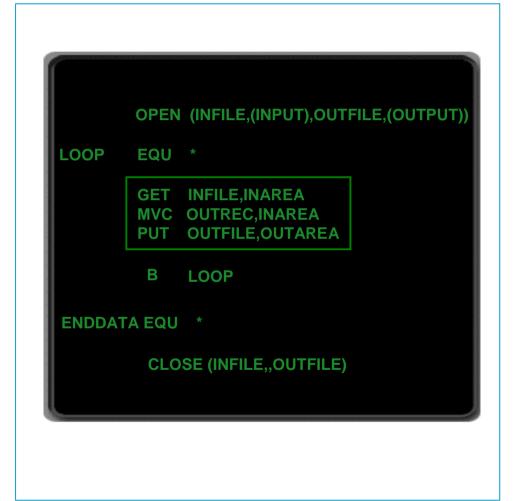

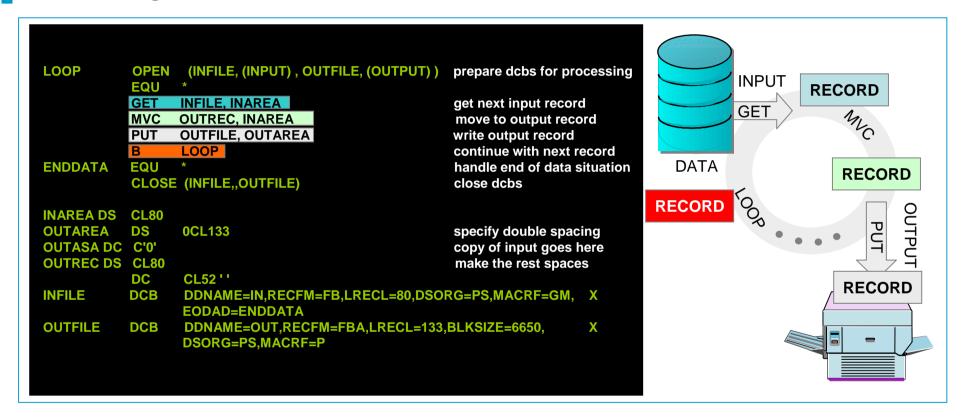

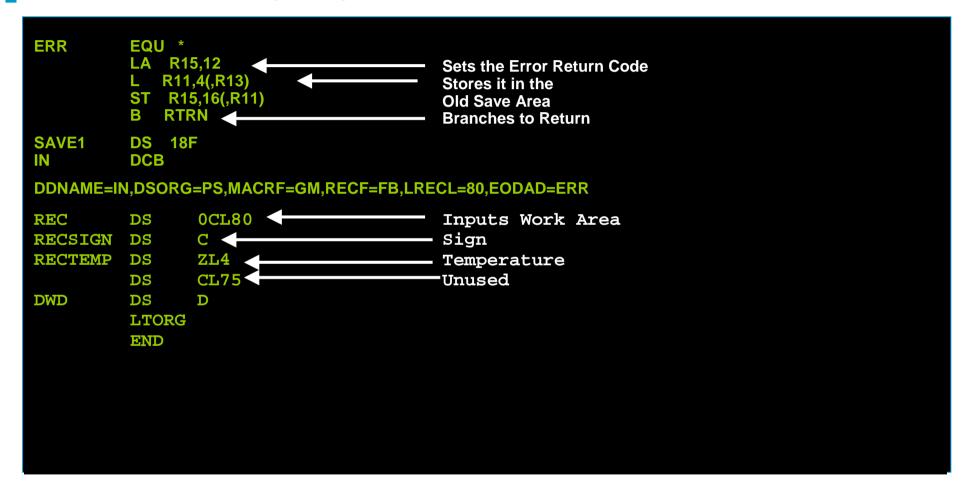

# Processing Input and Output Data

The main purpose of most assembler programs is to read in data (input), process it, and then print out the resulting data (output).

The major steps for processing input and output data in a program are shown. I/O macros are used to accomplish all of these tasks, except for the definition of I/O areas, which is done with assembler instructions.

| I/O PROCESSING TASKS           | MVS MACRO |

|--------------------------------|-----------|

| 1. Define the data set         | DCB       |

| 2. Define I/O areas            | DS,DC     |

| 3. Make the data set available | OPEN      |

| 4. Read input data             | GET       |

| 5. Write output data           | PUT       |

| 6. Free the data set           | CLOSE     |

# **Elements of Defining Data Sets**

Every Assembler program that processes I/O must provide information to the Assembler about the data sets to be processed. The data is organized sequentially and processed by the DCB (Data Control Block) macro in the same manner.

The DCB macro instruction generates a large block of constants in order to process the data set. The block of constants is a set of data fields (or parameters) that control the look of the data set being processed.

# **Elements of Defining Data Sets (cont'd)**

A DCB is a collection of data fields that contain information concerning the data set, including:

- The size and format of the records

- The I/O macros used to process the data

- The name and the current status of the data set

#### **Parameters**

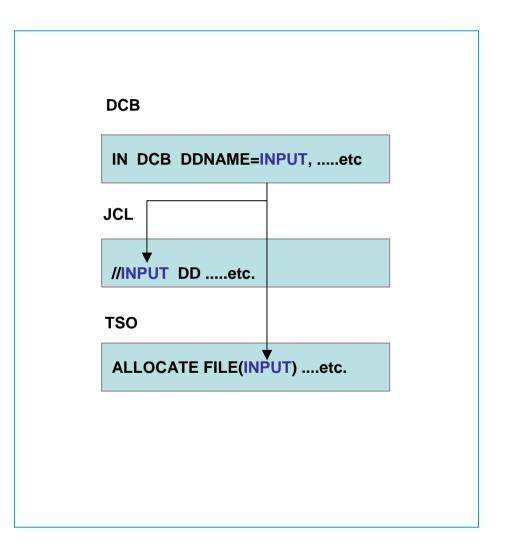

## What are the parameters used in DCBs?

A variety of keyword parameters are used with input and output DCBs.

The DDNAME parameter is used as a link to the external file this DCB represents. The value of the DDNAME parameter must match the DDNAME on the JCL DD statement for batch execution, or the FILE parameter on the ALLOCATE TSO statement for interactive execution.

### **Kinds of Parameters**

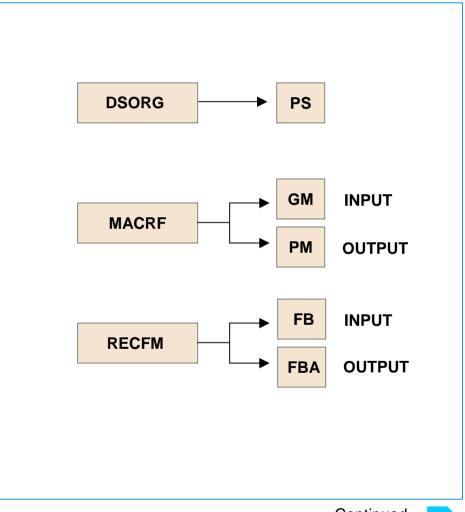

The **DSORG** parameter specifies the organization of the data set represented by this DCB. In the examples in this course, the parameter is always PS, which is an acronym for Physical Sequential.

The MACRF parameter specifies the format of macros used to access the records in the data set. You specify GM (Move mode of the GET macro) for input, and PM (Move mode of the PUT Macro) for output.

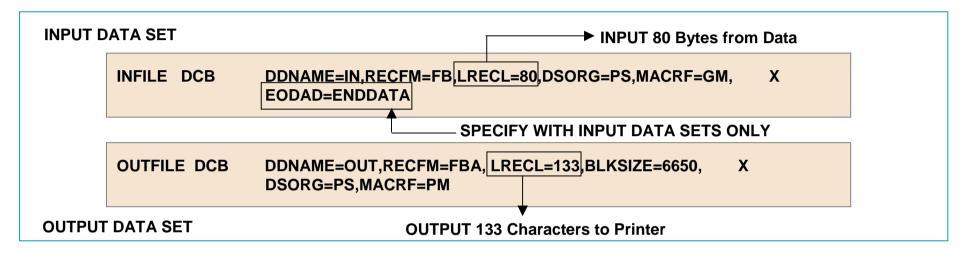

The **RECFM** parameter specifies the record format of the data set being processed. You specify FB (fixed length blocked records) for input, and FBA (fixed length blocked records with American National Standard Institute (ANSI) printer control characters) for output.

# Kinds of Parameters (cont'd)

The **LRECL** parameter specifies the length of logical records in the data set. You specify 80 for input and 133 for output.

The **BLKSIZE** parameter specifies the size of physical records, or blocks, in the data set. Omit this parameter for input data sets and use 6650 for output.

The **EODAD** parameter (End of Data Address) specifies a label in your program where control is to be transferred when a GET is attempted and no more data exists. This parameter is only specified for input data sets.

# **Defining Data Set Elements**

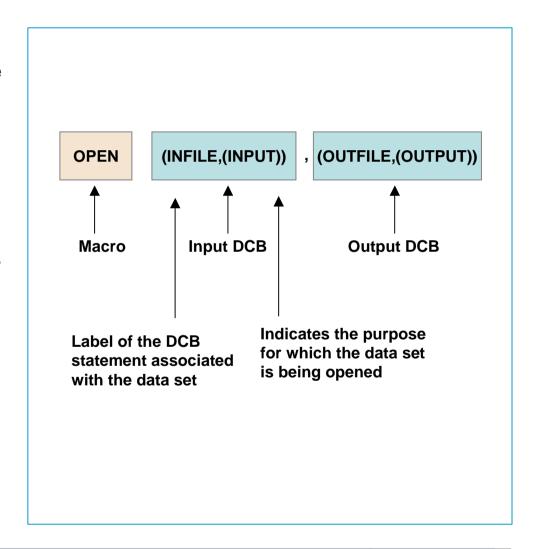

Before input and output operations on data sets can be performed, they must be opened, or made available for processing. You use the OPEN macro instruction for this purpose.

#### What is the function of the OPEN macro?

The OPEN macro generates executable instructions that invoke operating system routines to check for the presence of a data set, confirm that it matches your specifications, and prepare it for processing. For output data sets, OPEN will create a new data set if the JCL or ALLOCATE statement so specifies.

# **Defining Data Sets - Summary**

Once the DCB has been opened, code data transfer macros, GET for input and PUT for output.

These statements are discussed in more detail in the next section.

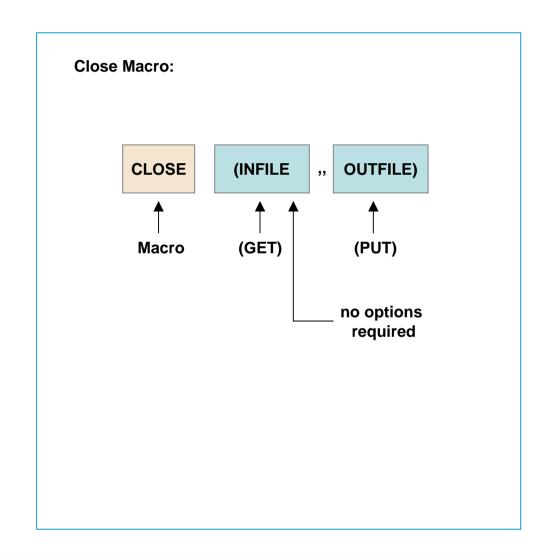

Having finished the I/O processing, close the DCBs, prior to ending the program. The CLOSE macro is used for file housekeeping.

The CLOSE macro to close the two data sets is coded as follows:

CLOSE (INFILE,,OUTFILE)

#### **Move Mode**

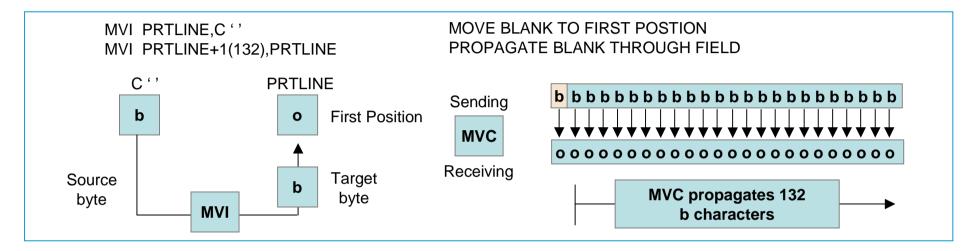

#### What is Move Mode?

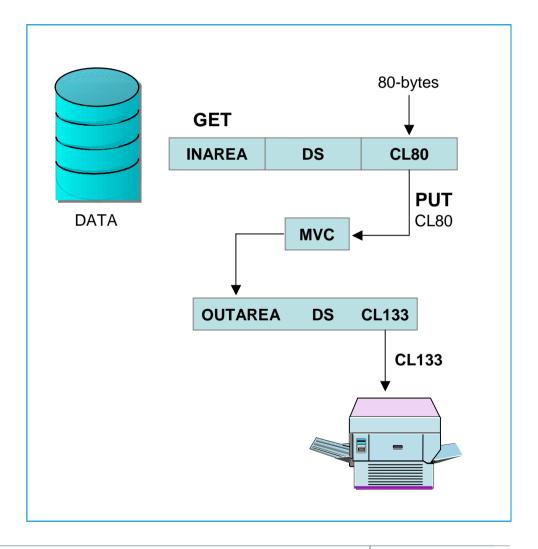

The method by which data is transferred from or to an I/O device is called Move Mode.

Although data is transferred between the I/O device and buffer is main storage, one block at a time, Move Mode I/O moves single logical record to/from a work area. When using this mode, you must define a work area for each data set.

The Move Mode data transfer macro, for input, moves the record from the data set to a buffer in main storage and from the buffer to the work area named INAREA.

The Move Mode data transfer macro, for output, moves the record from the work area named OUTAREA to the buffer in the main storage and from the buffer to the I/O device.

# Move Mode (cont'd)

The work area must be the same length as the logical record.

The logical records in the input data set are 80 bytes in length, so the input work area is defined as shown.

The output records are 133 characters in length, so the output work area is defined as shown.

These areas could be subdivided by using the zero duplication factor technique.

### **GET Macro**

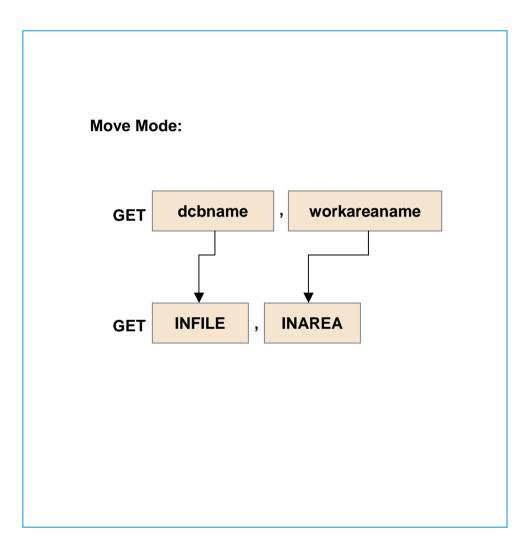

Once a data set is opened, the GET macro reads the next logical record in the data set into a work area. The format of the GET macro in the move mode is shown on the right.

Using the names used up to this point, the macro would be coded as shown on the right.

When the end of the input data is reached, and another GET macro is issued, control is transferred to the address specified as the EODAD in the DCB macro.

### **PUT Macro**

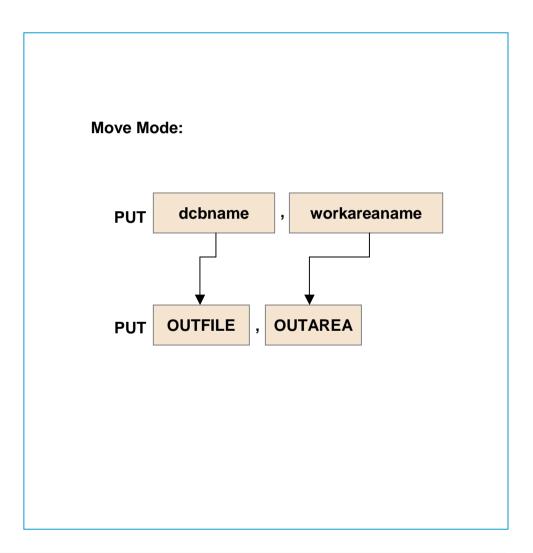

#### What is the function of the PUT Macro?

The PUT macro is used to write the next logical record from the work area to the output data set. The format of the PUT macro in move mode is shown on the right.

Using the names used up to this point, coding would appear as shown on the right.

### **ANSI Control Character**

The record format parameter we have used for our output data set is FBA and is coded as shown:

The A specifies that the first byte of each record is an ANSI control character, which is used to specify spacing on the printer.

The most common ANSI printer control characters and their meanings are shown on the right.

| ANSI Printer<br>Control Character | Meaning                              |

|-----------------------------------|--------------------------------------|

| Space                             | Single space                         |

| 0                                 | Double space                         |

| -                                 | Triple space                         |

| +                                 | Suppress space (overprint last line) |

| 1                                 | Skip to top of next page             |

# **Consolidating I/O Information**

To put all of this I/O information together, you code a program segment to read data from an input data set, and then print it out, double spaced, on the printer.

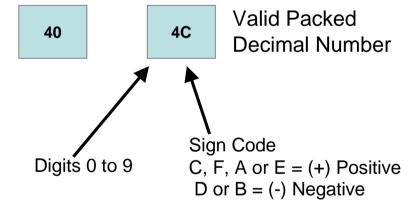

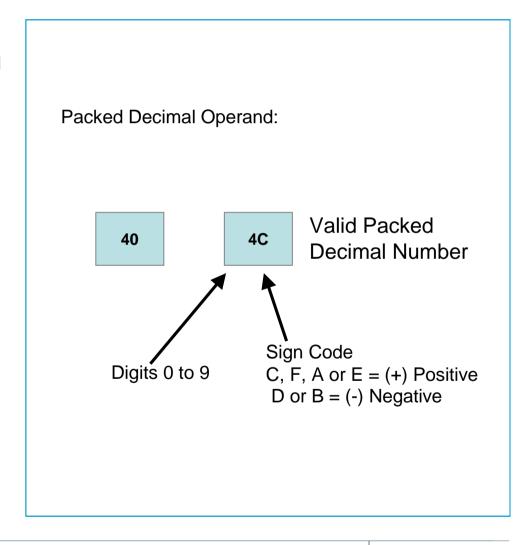

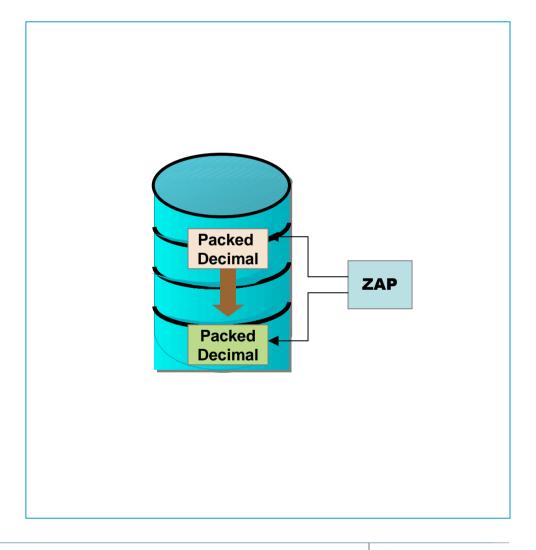

# **Packed Decimal Operands**

## What do packed decimal operands contain?

Packed decimal operands are fields in main storage from 1 to 16 bytes in length. The rightmost byte of a packed decimal field contains a decimal digit in the left nibble and a sign in the right nibble. The preferred signs for packed decimal numbers are C for positive and D for negative. The remaining bytes of a packed decimal number (other than the rightmost) contain two decimal digits, one in each nibble.

Packed Decimal Operand:

If you attempt to perform decimal arithmetic with an operand that is not in valid format, a data exception will occur.

# Packed Decimal Operands (cont'd)

A packed field n bytes long can hold 2 \* n -- 1 digits. The maximum number of digits in a packed decimal number is 31, since the maximum field length is 16. The maximum field length for a multiplier or divisor is 8 bytes.

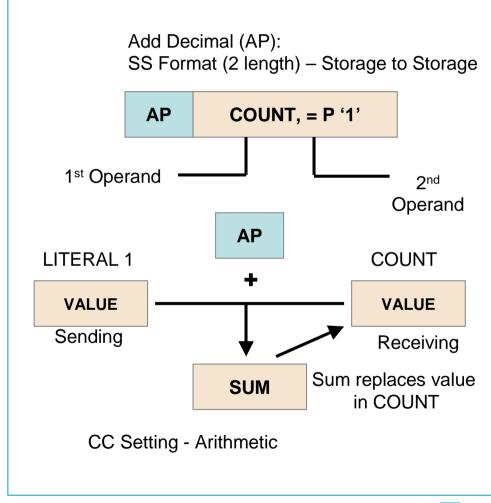

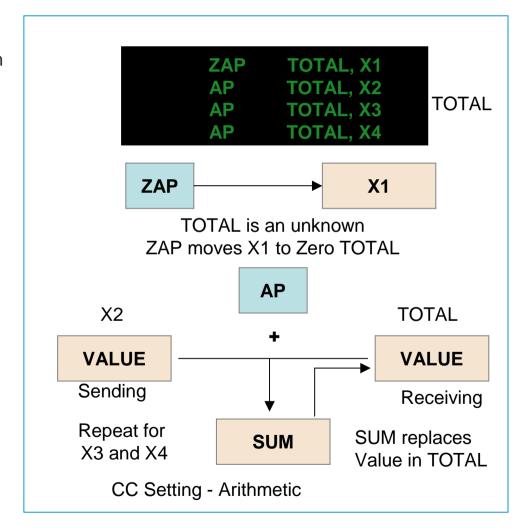

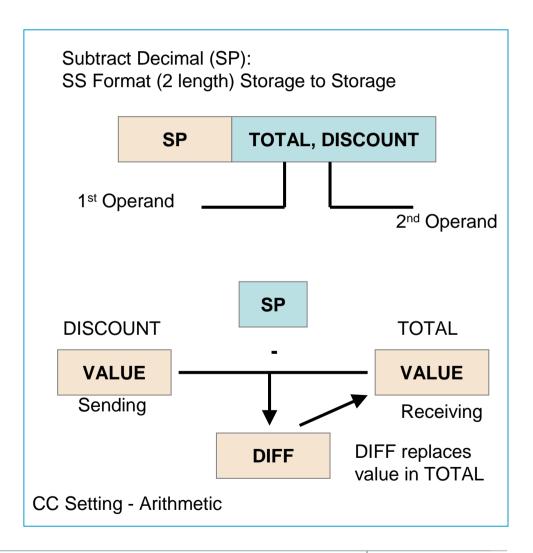

#### **Decimal Arithmetic Instructions**

#### What are decimal arithmetic instructions?

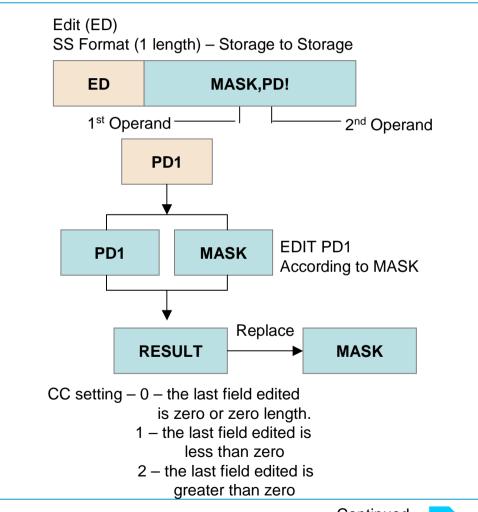

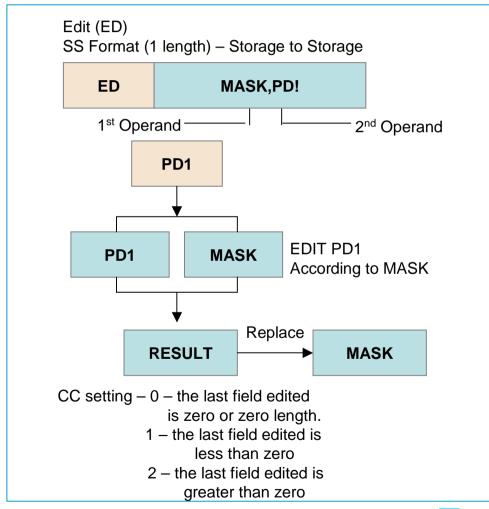

The decimal arithmetic operations are SS (Storage to Storage) (2 length) instructions.

Operands do not have to be of the same length.

Decimal arithmetic is performed in main storage.

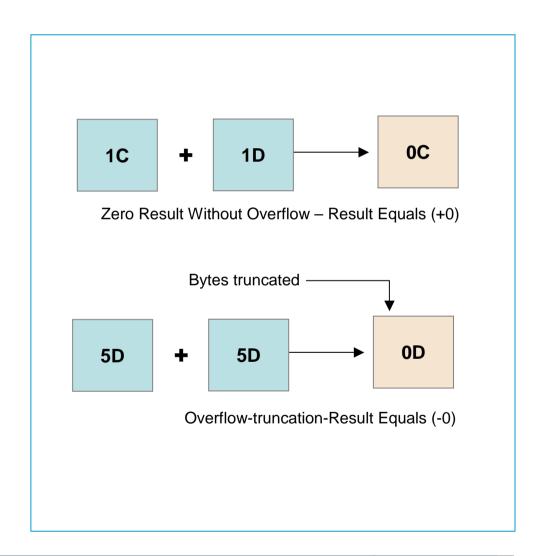

Unlike fixed-point representation, which only provides one zero value, decimal arithmetic allows both +0 and -0 to be represented. If a packed decimal arithmetic operation generates a zero result without overflow, the result will be +0. If overflow occurs, the truncated number is zero, the sign generated is that of the non-truncated number

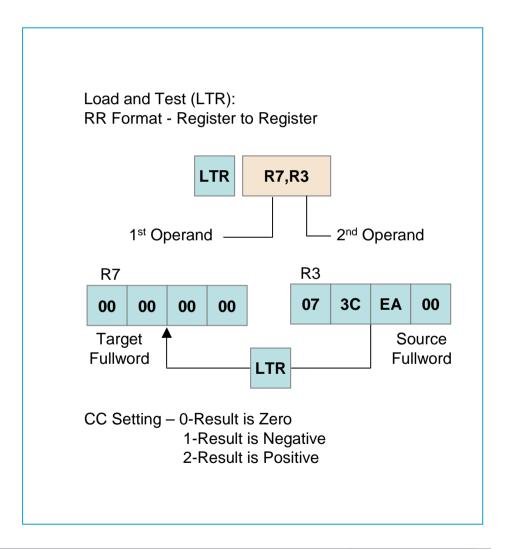

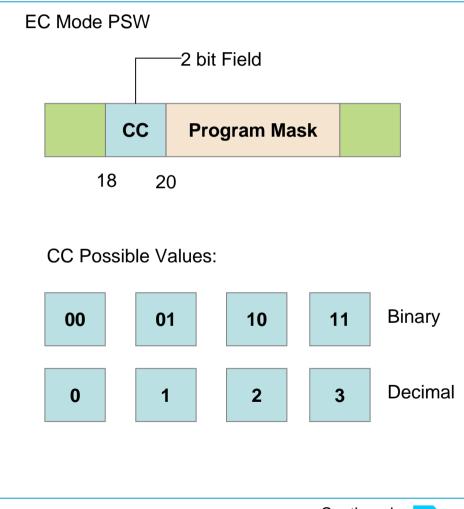

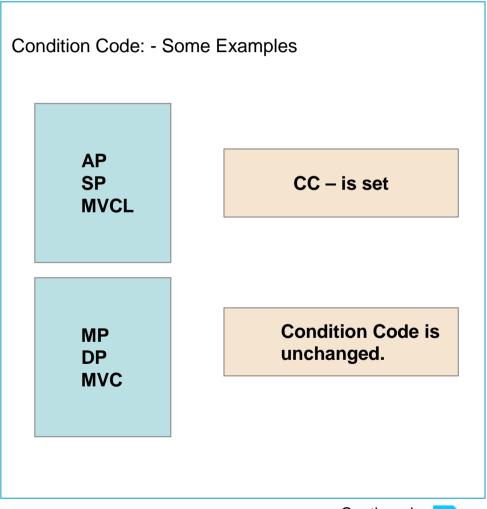

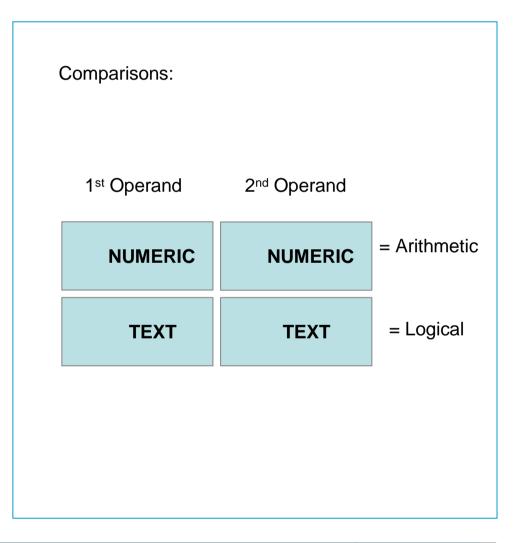

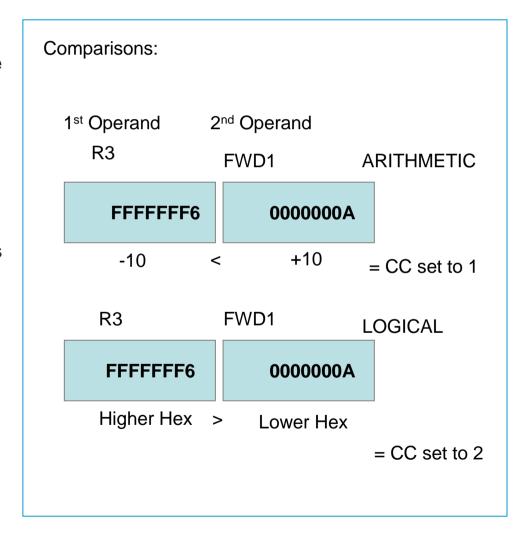

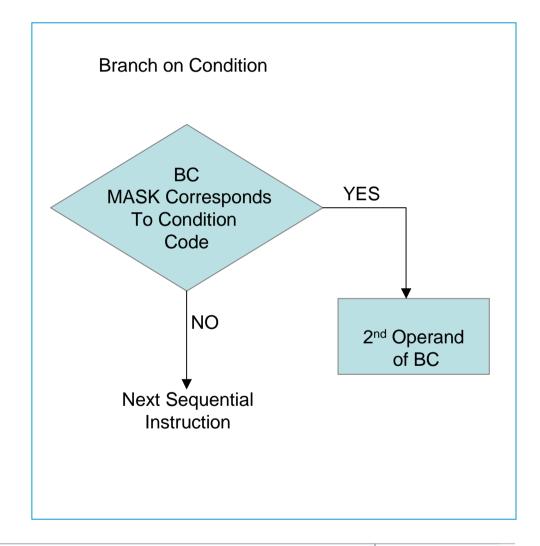

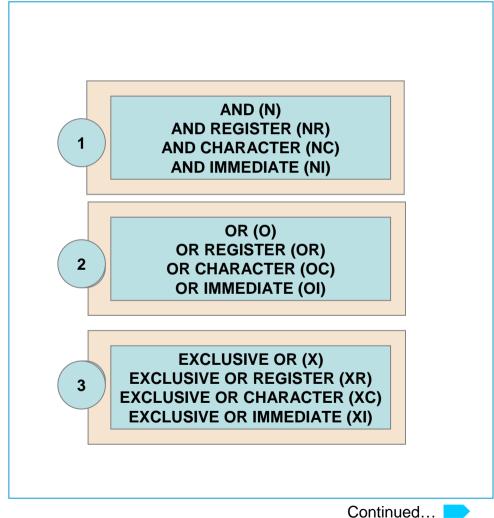

### **Condition Code**

#### What is a condition code?

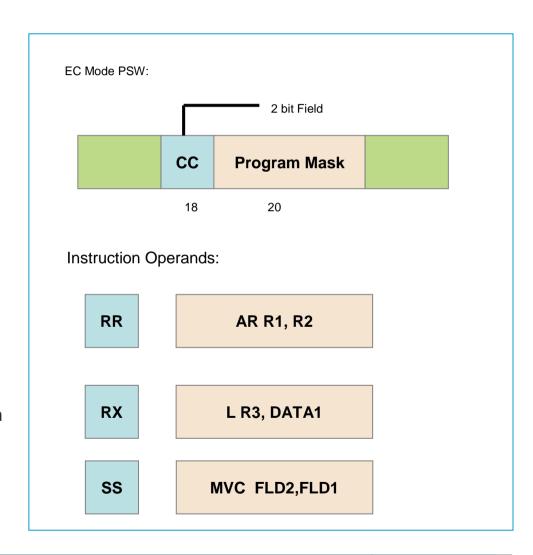

The condition code is a two-bit field in the Program Status Word (PSW) that is set by some instructions, and can then be tested by subsequent instructions to implement conditional execution.

#### Where are instruction operands located?

Instruction operands are located in main storage or in registers. The operand's instruction type determines the location of the operands for each particular instruction:

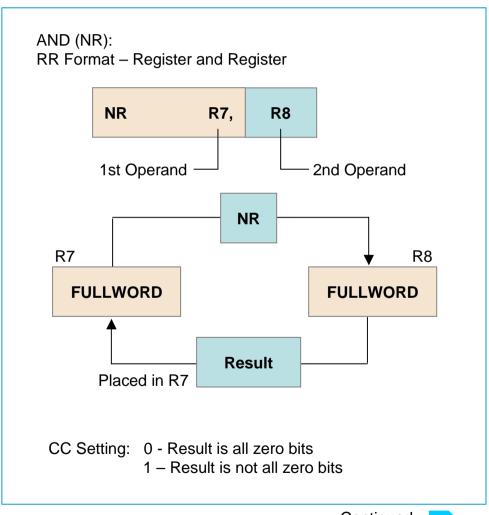

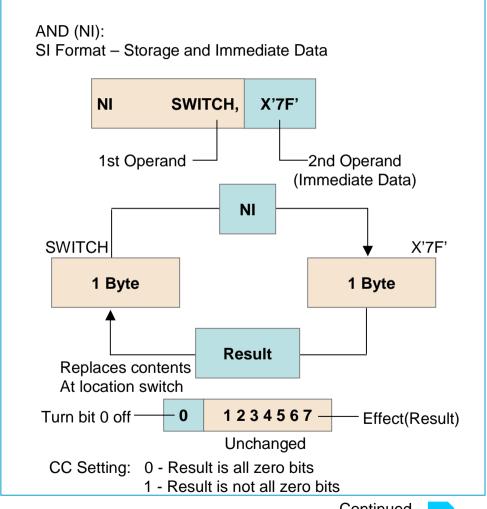

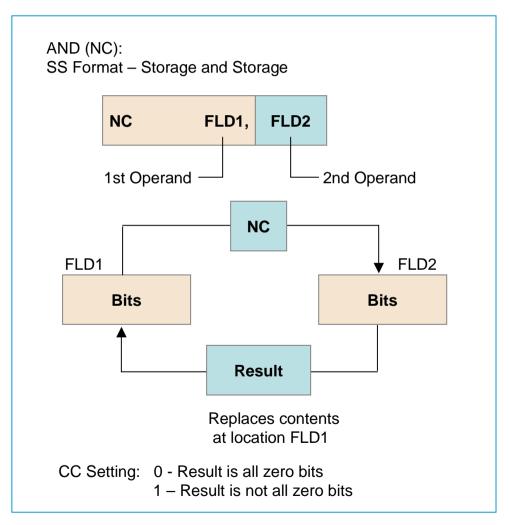

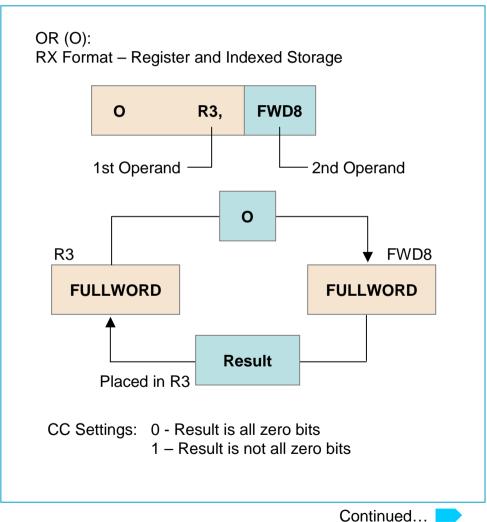

- RR instructions have two operands in registers

- RX instructions have the first operand in a register and the second in storage.

- SS instructions have both operands in storage.

# **Digits in Zoned and Packed Decimal Types**

# How many digits do zoned decimal and packed decimal data contain?

Zoned decimal data has one digit per byte, with each byte consisting of a zone nibble and a decimal numeric nibble. The zone in the rightmost byte is the sign.

Packed decimal data consists of two decimal digits per byte for the rightmost, which contains a numeric nibble followed by a sign nibble.

Numbers in character form (EDCDIC code) are zoned, with an 'F' sign.

## **Converting Zoned Decimal Numbers to Packed Decimal Numbers**

# How do you convert zoned decimal numbers to packed decimal format?

You often need to convert zoned decimal numbers to packed decimal format. The numbers are read in zoned form, but in order to be used in decimal arithmetic they must be packed.

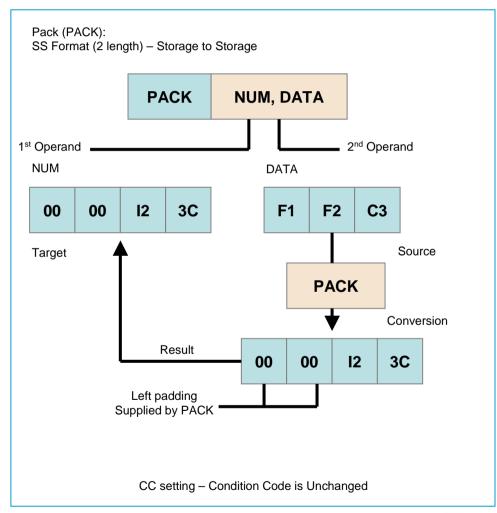

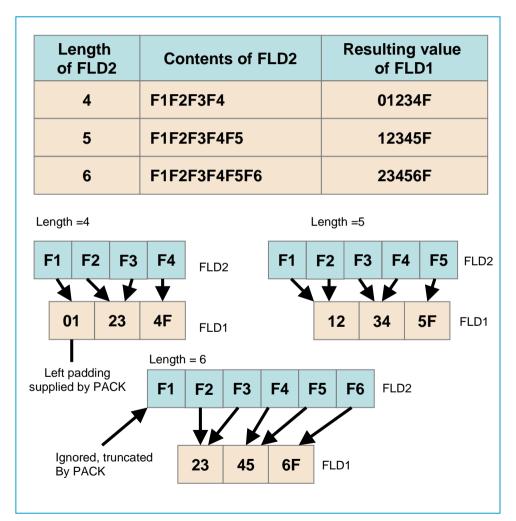

The instruction that performs this conversion is called Pack (PACK) and is shown on the right.

The second operand is converted from zoned to packed format, and the result stored in the first operand.

For example: PACK NUM, DATA

# Converting Zoned Decimal Numbers to Packed Decimal Numbers (cont'd)

The operation of PACK is as follows:

- It processes each operand right to left.

The rightmost byte of the second

operand has its nibbles reversed in

order and the result is stored in the

rightmost byte of the first operand.

- Pairs of bytes are selected from the second operand and combined into a single byte by combining numeric nibbles and discarding zone nibbles. The combined single byte is stored in the first operand.

- If the length of the second operand, L<sub>2</sub>, is greater than 2\*L<sub>1</sub>-1, left truncation occurs. If L<sub>2</sub> is less than 2\*L<sub>1</sub>-1, left padding with zeroes occurs.

# **Converting from Packed Decimal to Zoned Decimal Numbers**

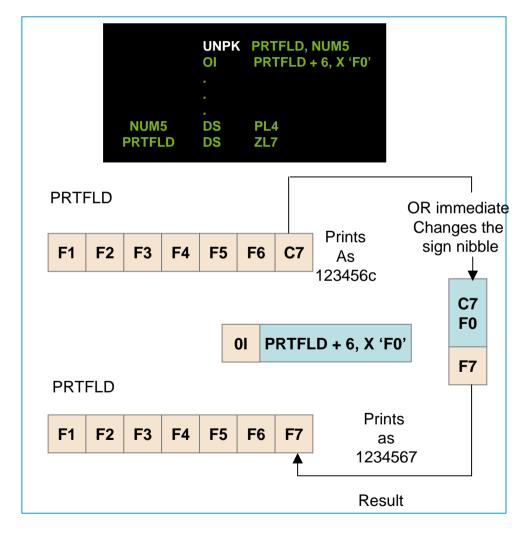

# How do you convert from packed decimal to zoned decimal numbers?

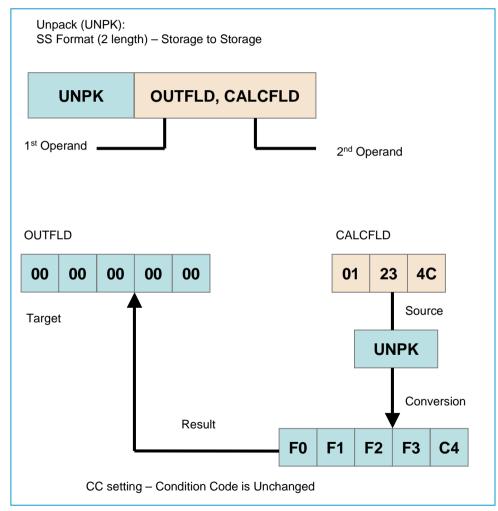

The reverse conversion, from packed decimal to zoned decimal is performed by the Unpack (UNPK) instruction.

The second operand is converted from packed to zoned format and the result stored in the first operand.

For example: UNPK OUTFLD, CALCFLD

# Converting from Packed Decimal to Zoned Decimal Numbers (cont'd)

The operation of UNPK is as follows:

- 1. It proceeds from right to left through its two operands. The nibbles of the rightmost byte of the second operand are swapped and stored in the rightmost byte of the first operand.

- 2. Each nibble of the second operand is expanded to a byte by inserting an 'F' in the zone nibble. It is then stored in the first operand.

- 3. If L<sub>1</sub> is not equal to 2\*L<sub>2</sub>-1, left truncation, or left padding with zero will occur.

For example: UNPK FLD3, FLD4

| Length<br>Of FLD4 | Contents of FLD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Resulting value<br>Of FLD3 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

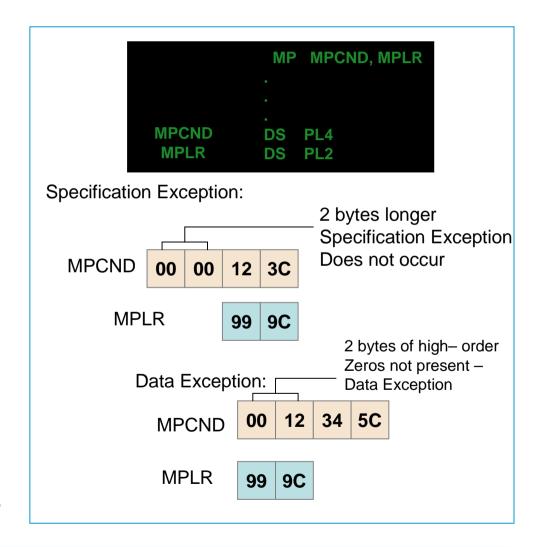

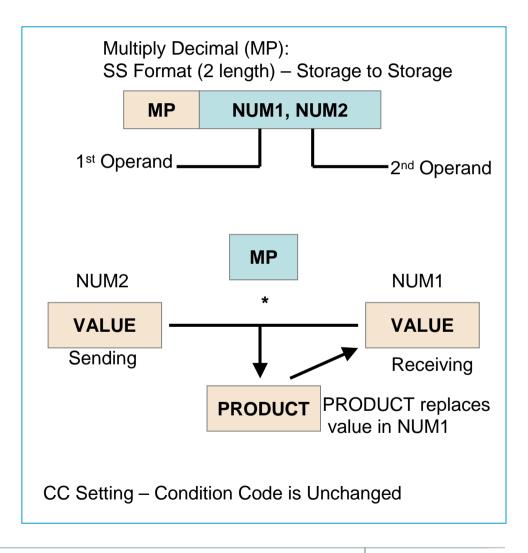

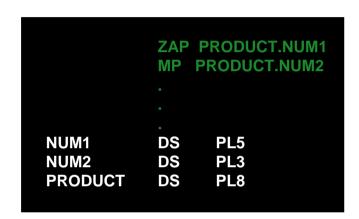

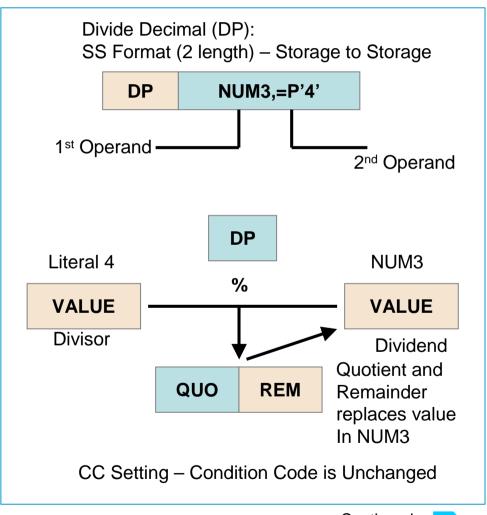

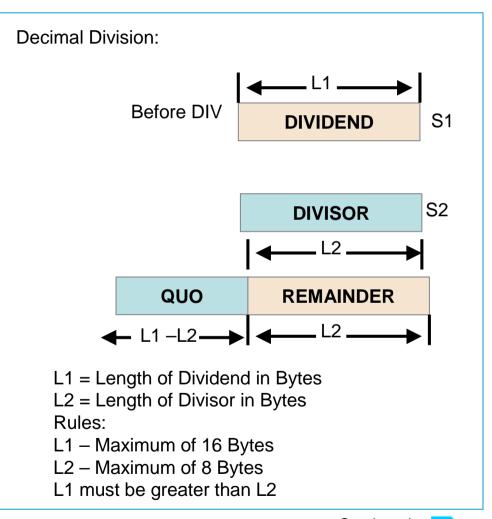

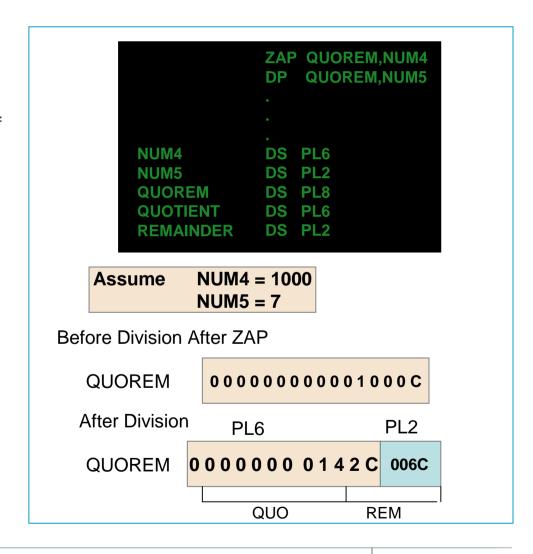

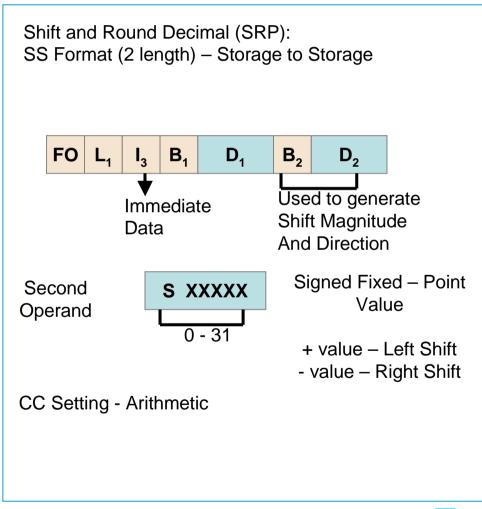

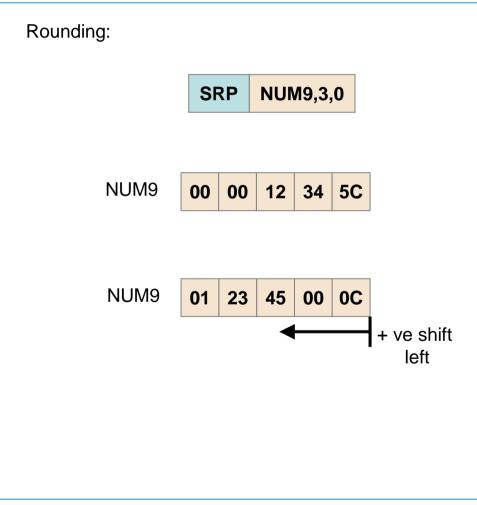

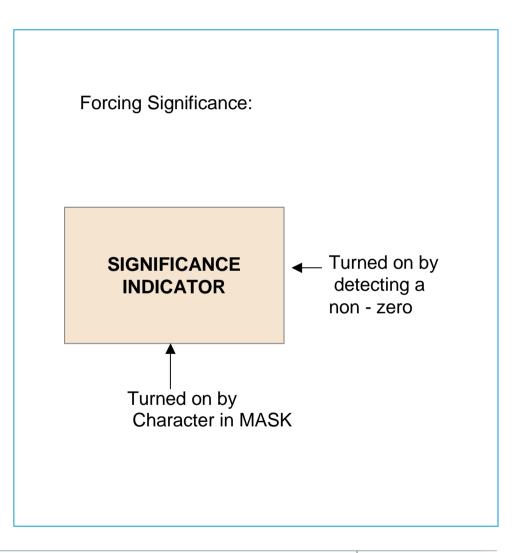

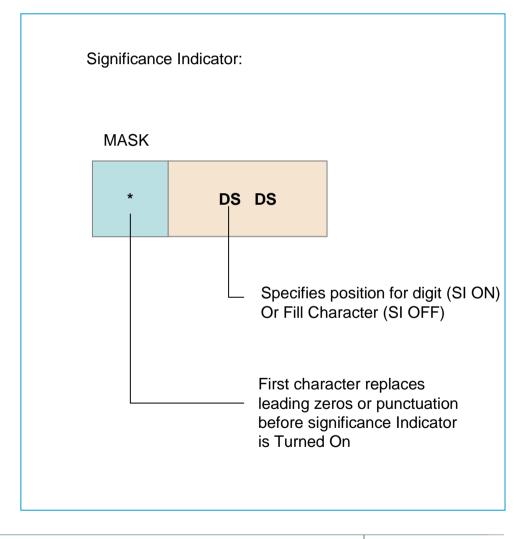

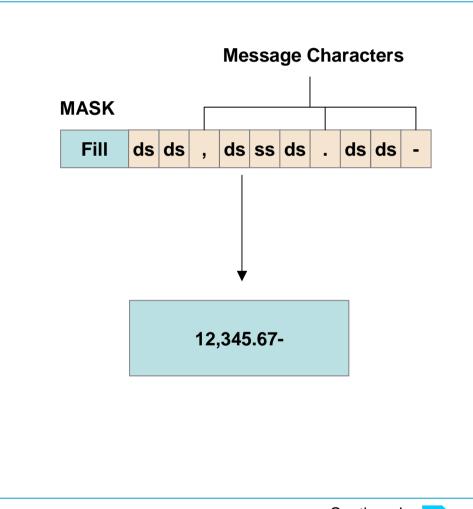

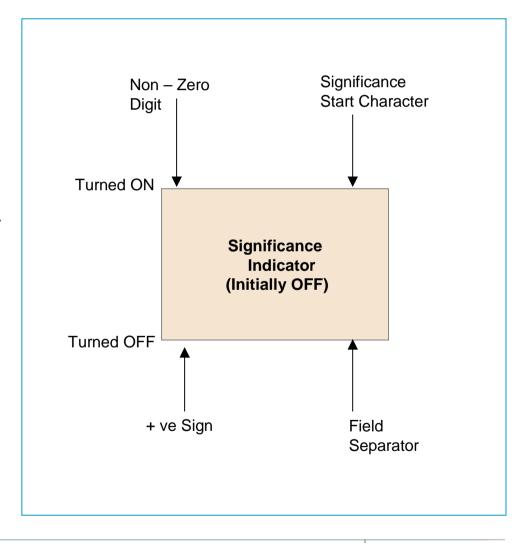

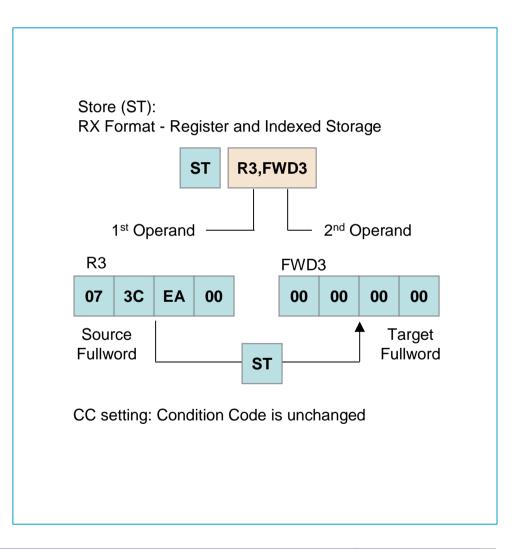

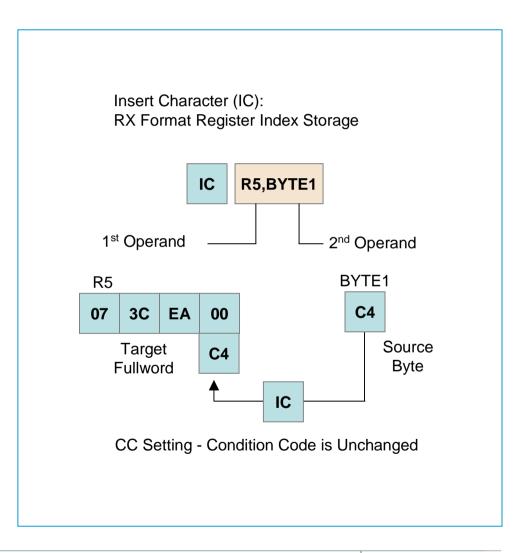

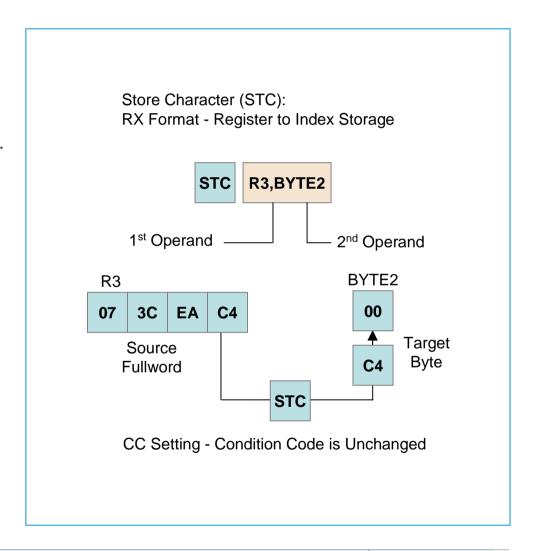

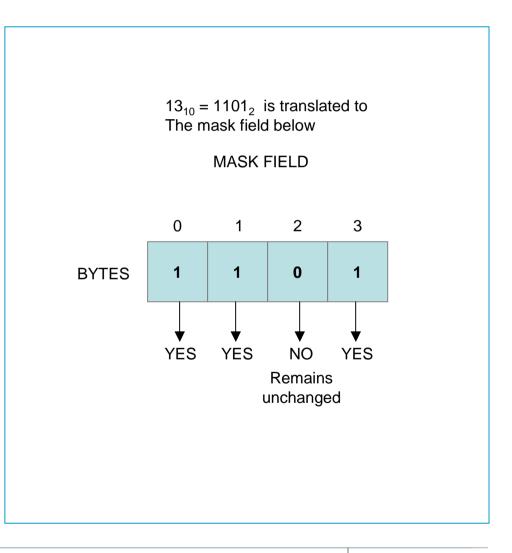

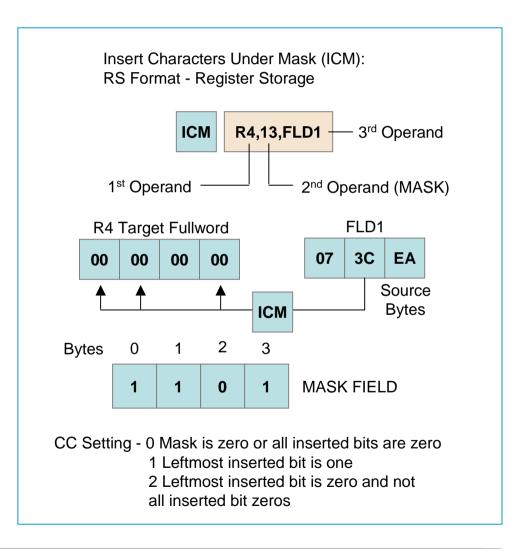

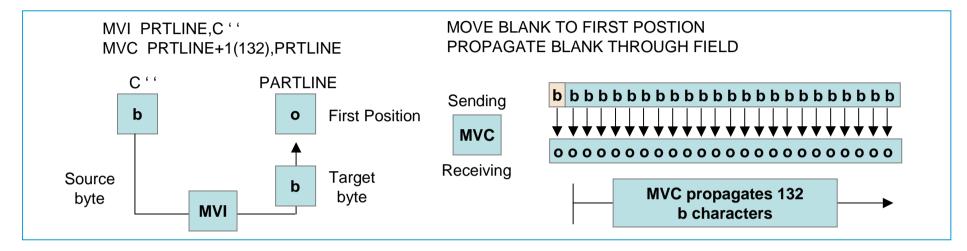

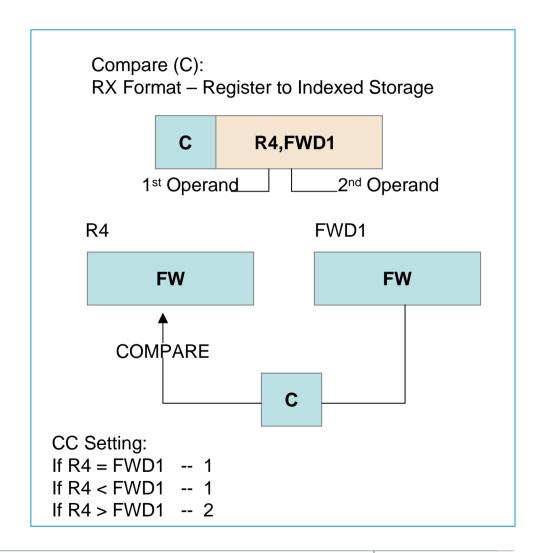

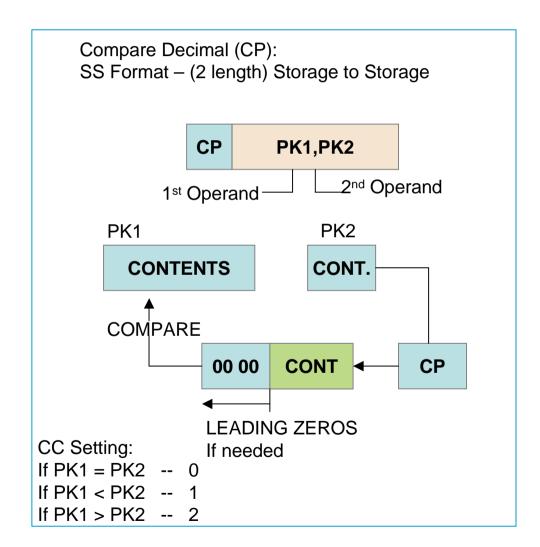

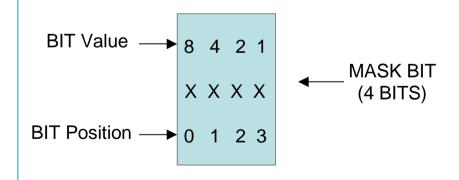

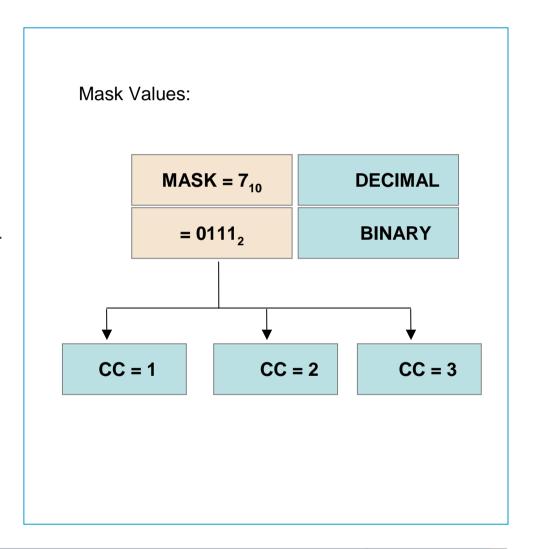

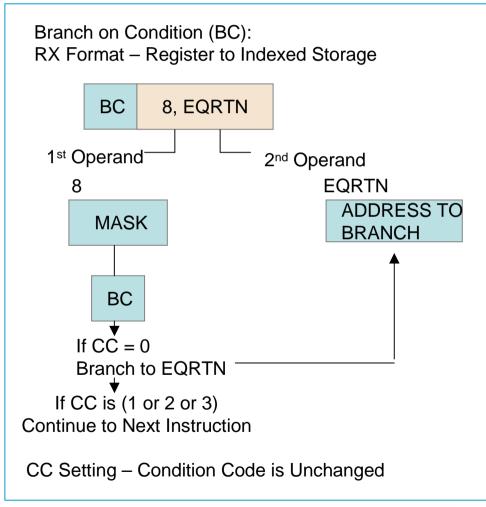

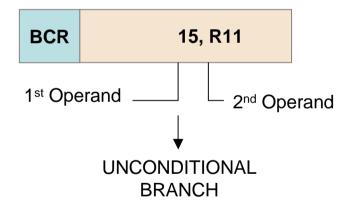

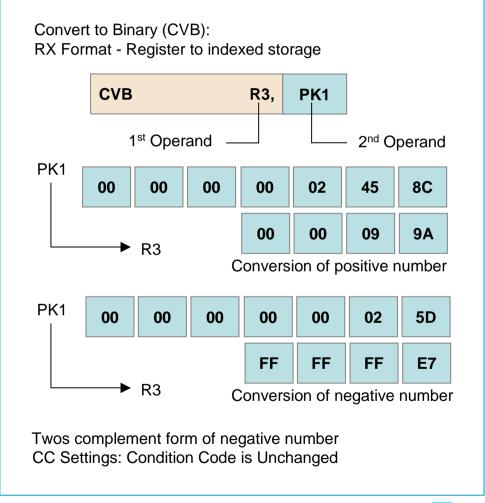

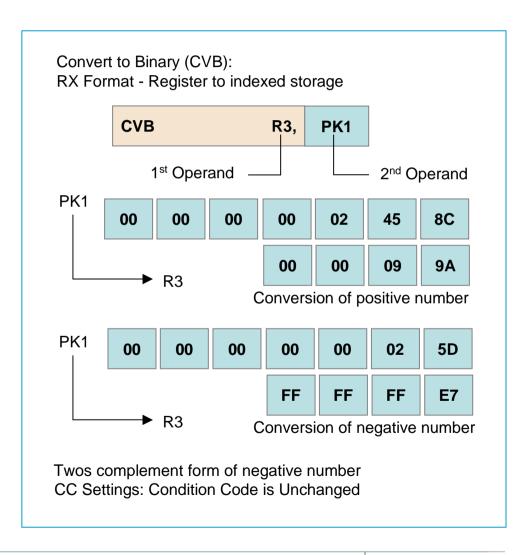

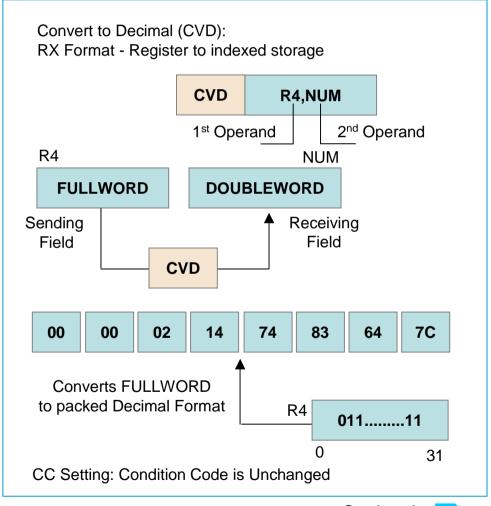

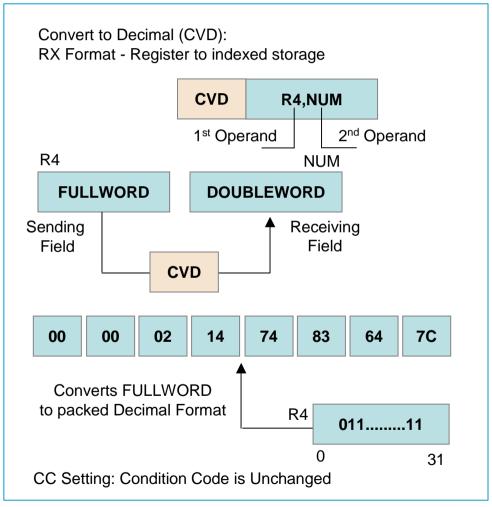

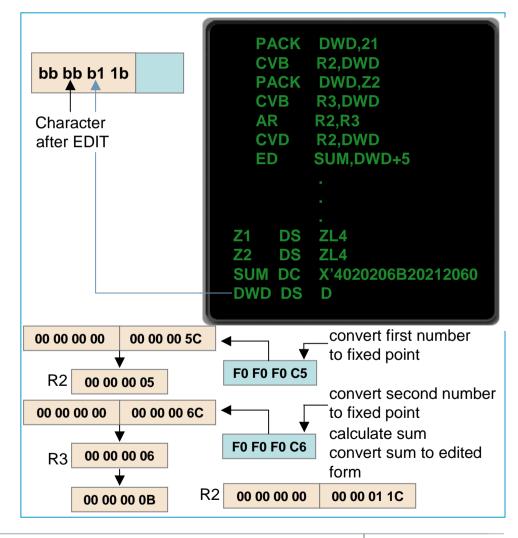

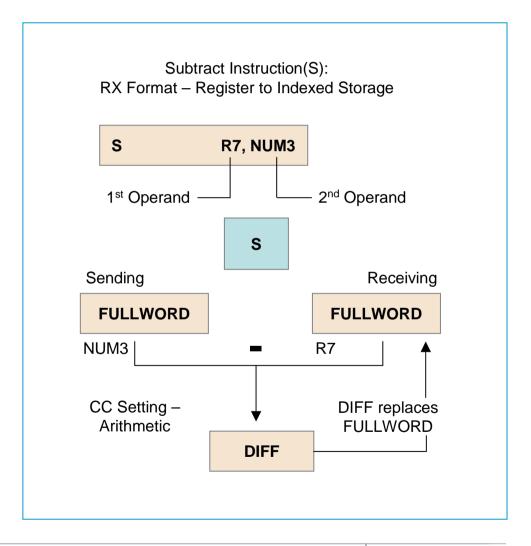

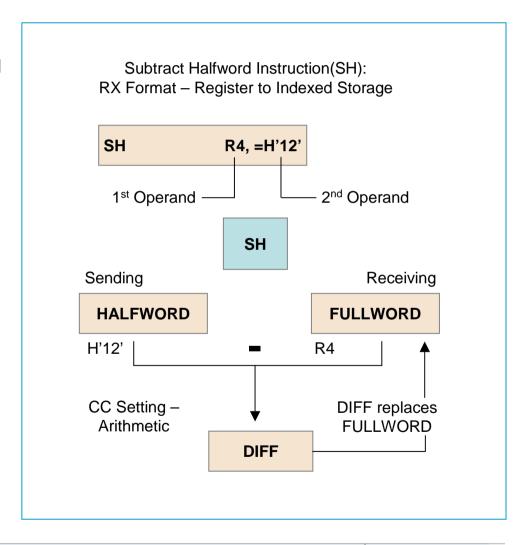

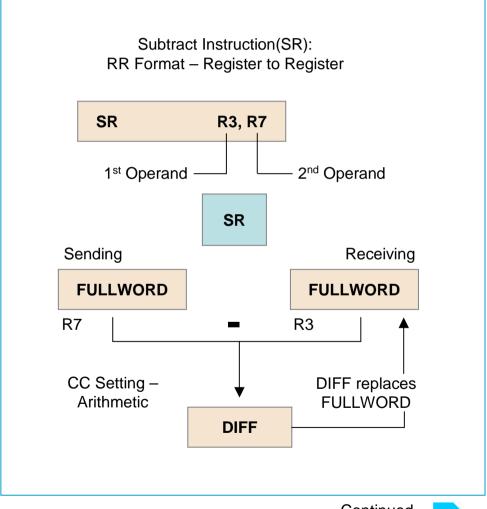

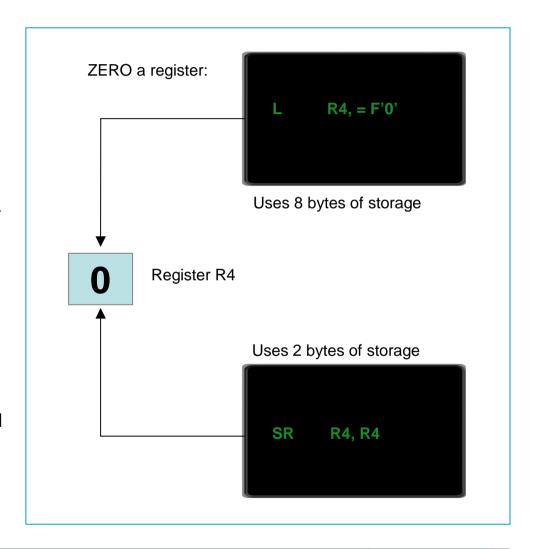

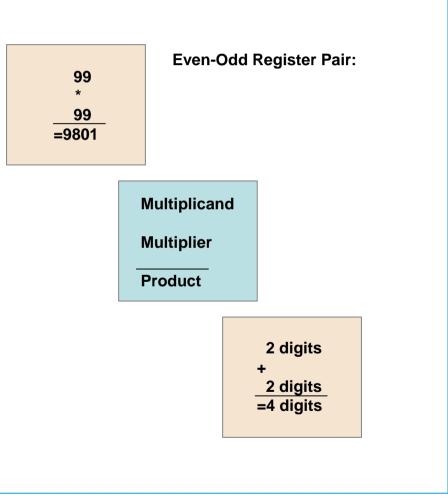

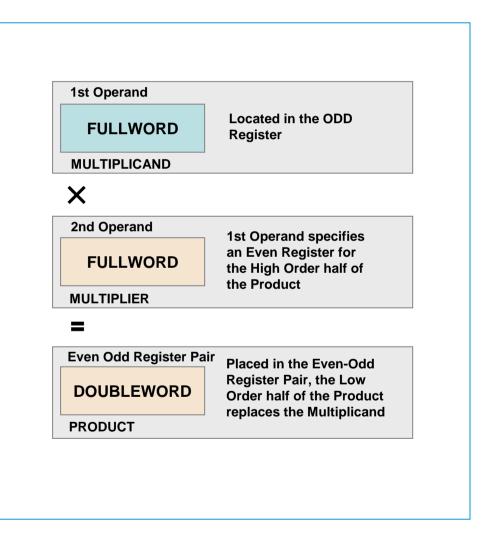

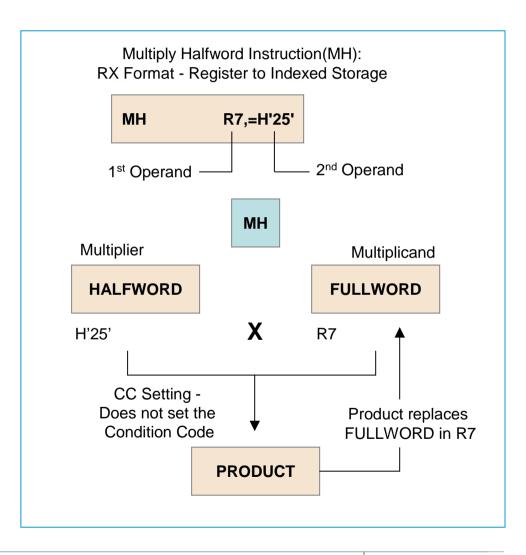

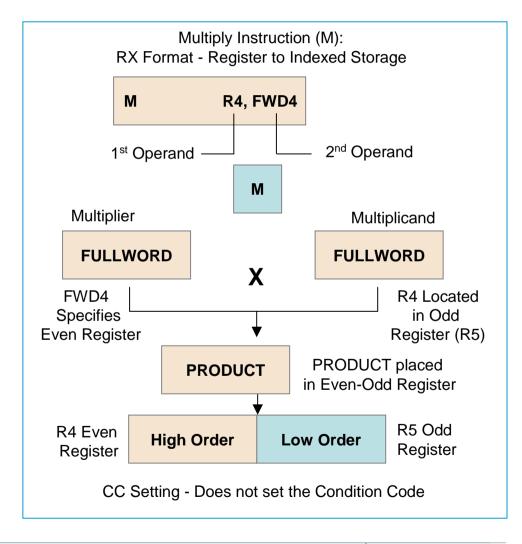

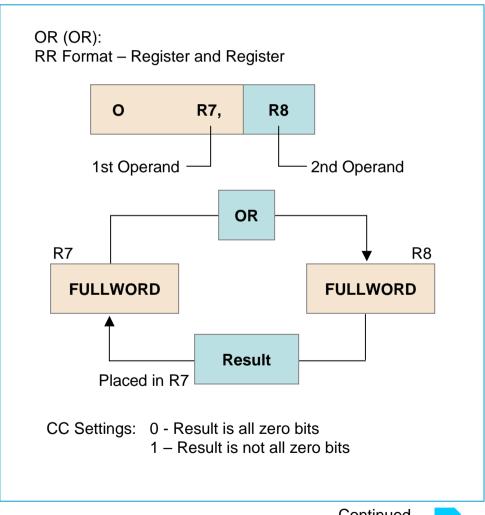

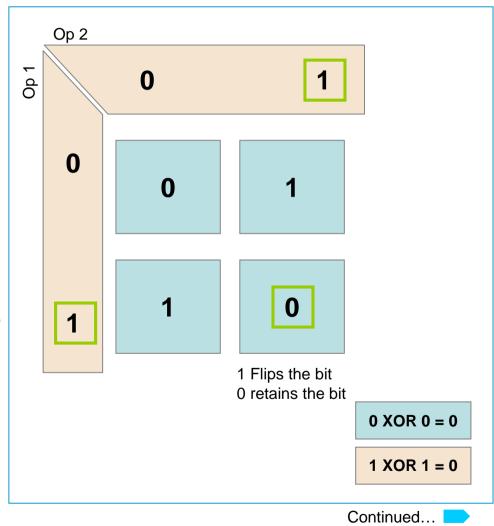

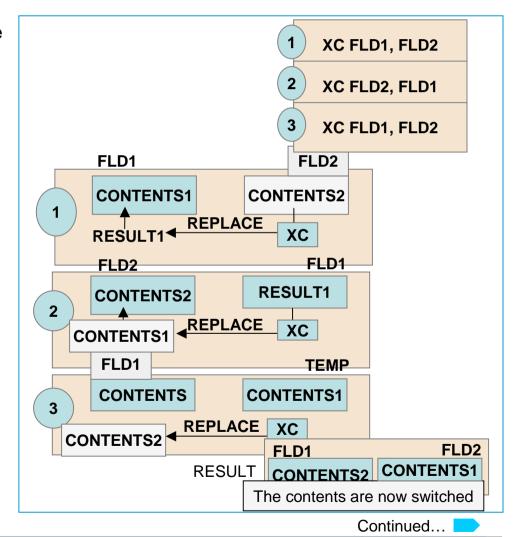

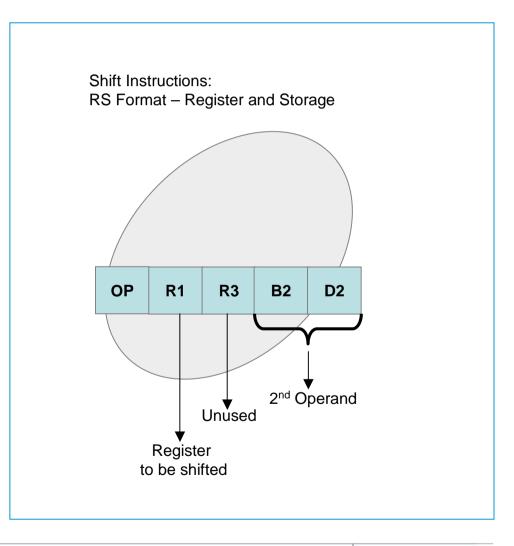

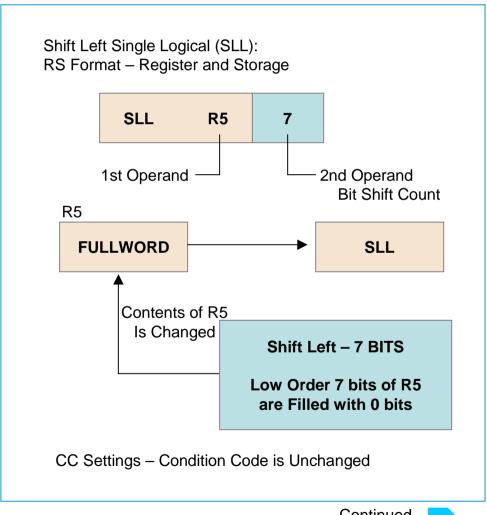

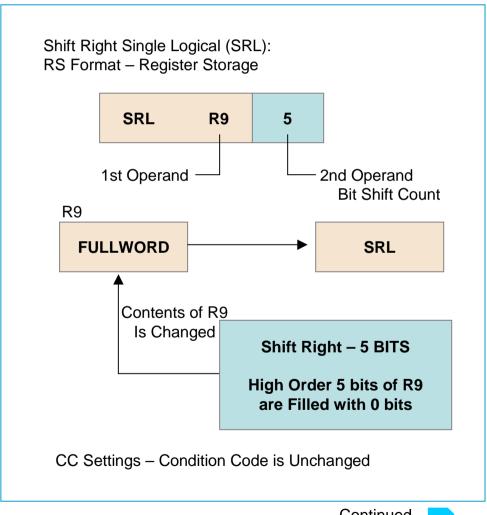

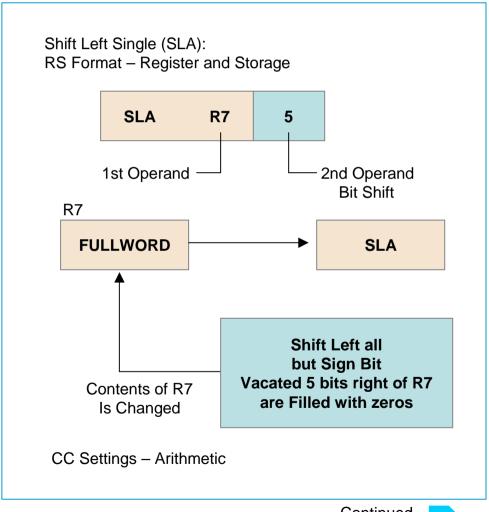

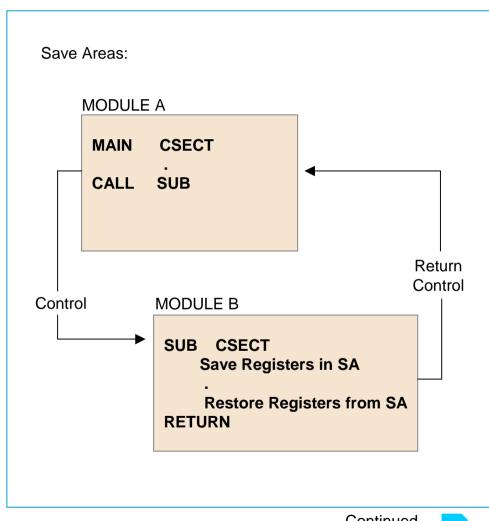

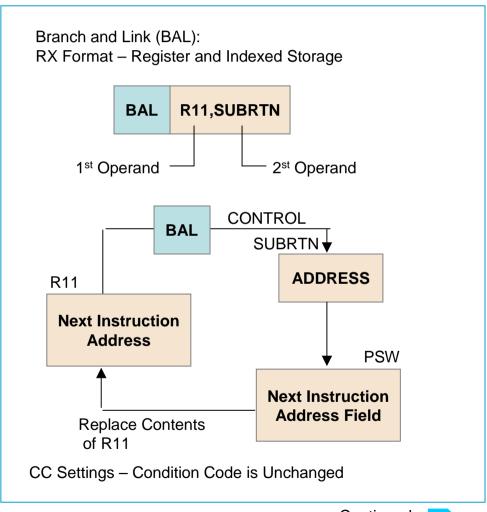

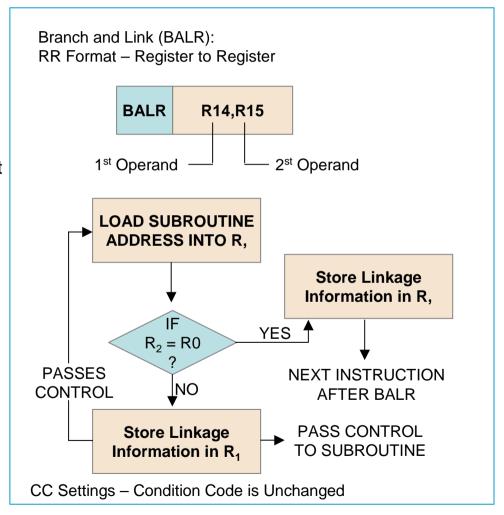

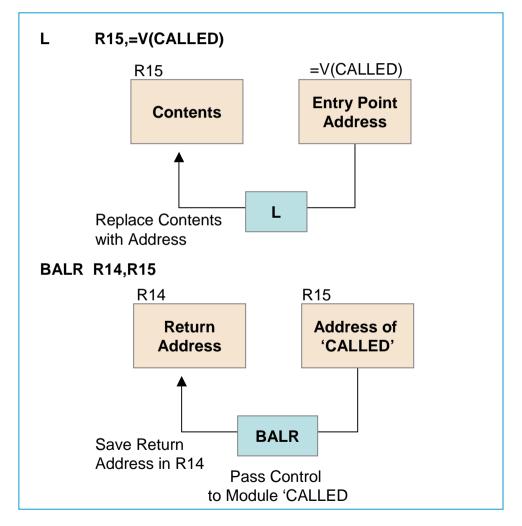

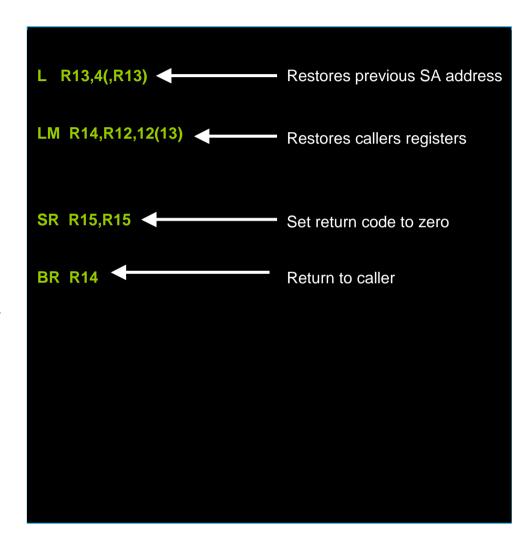

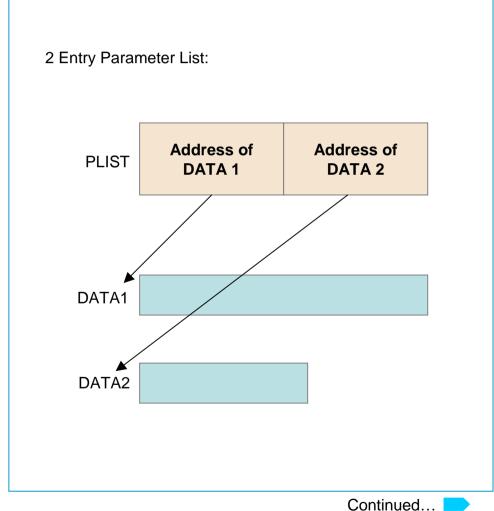

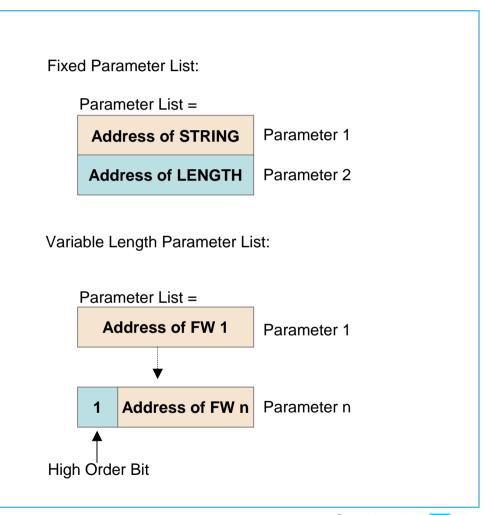

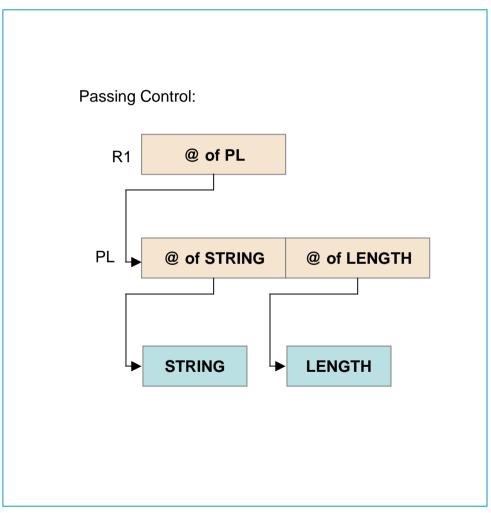

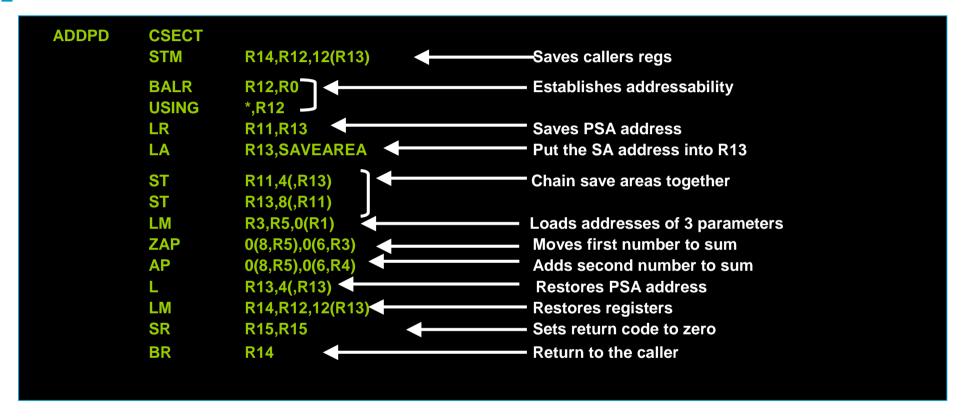

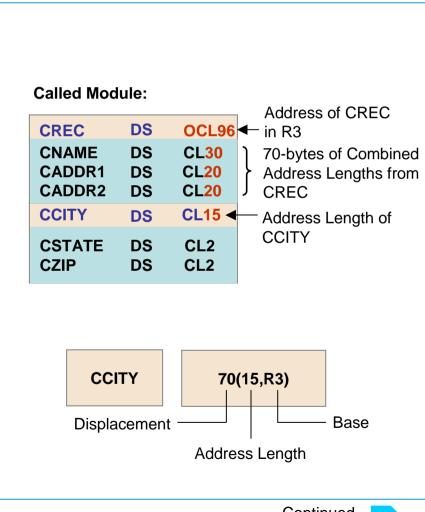

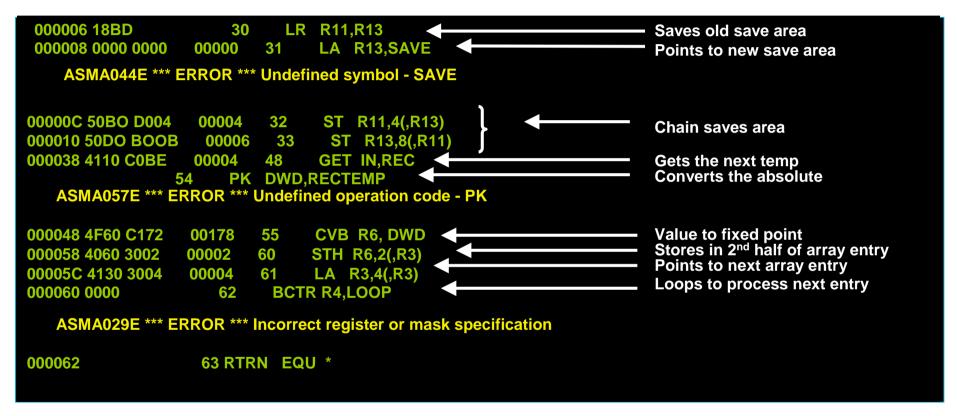

| 2                 | 123C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | F0F0F1F2C3                 |