# TSK80x MCU

# Summary

Core Reference CR0117 (v1.6) August 28, 2006 The TSK80x is a fully functional, 8-bit microcontroller, incorporating the von Neumann architecture. This core reference includes architectural and hardware descriptions, instruction sets and on-chip debugging functionality for the TSK80x family.

The TSK80x is a fully functional 8-bit embedded processor which is instruction set compatible with the Zilog Z80CPU<sup>1</sup>. The TSK80x supports hardware interrupts, halt and wait states for low speed memory and I/O devices.

**Important Notice**: Supply of this soft core under the terms and conditions of the Altium End-User License Agreement does not convey nor imply any patent rights to the supplied technologies. Users are cautioned that a license may be required for any use covered by such patent rights.

## **Features**

- Control Unit

- 8-bit Instruction decoder

- Arithmetic Logic Unit

- 8-bit arithmetic and logical operations

- 16-bit arithmetic operations

- Boolean manipulations

- Register File Unit

- Duplicate set of both general purpose and flag registers

- Two 16-bit index registers

- Interrupt Controller

- Three modes of maskable interrupts

- Non-maskable interrupt

- External Memory Interface

- Can address up to 64KB of Program memory

- Can address up to 64KB of Data memory

<sup>&</sup>lt;sup>1</sup> The TSK80A is instruction set compatible. The TSK80A\_D is instruction set compatible with the exception of instruction LD H, H. This opcode is reserved and is used to represent a software breakpoint.

- Can address up to 64KB of external I/O peripheral devices

## **Available Devices**

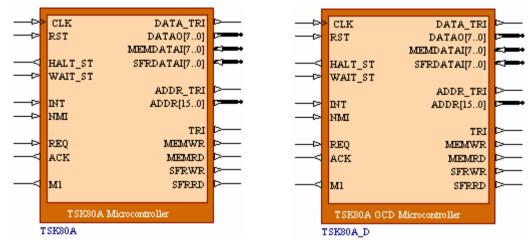

Both standard and debug-enabled (OCD) versions of the microcontroller are available – the TSK80A and TSK80A\_D respectively.

**Note**: Unless specified otherwise, the feature/description described for the standard version of the controller applies to the debug-enabled version in exactly the same way.

These devices can be found in the FPGA Processors integrated library (\Program Files\Altium Designer 6\Library\Fpga\FPGA Processors.IntLib).

# **Architectural overview**

## **Symbols**

## **Pin description**

The pinout of the TSK80x is described in Table 1 below.

| Table 1. | TSK80x pin description |

|----------|------------------------|

|----------|------------------------|

| Name    | Туре | Polarity/Bus<br>size | Description                                                                                                                                                                                          |

|---------|------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |      | С                    | PU Control Signals                                                                                                                                                                                   |

| CLK     | Ι    | Rise                 | External system clock (used for internal clock counters and all other synchronous circuitry).                                                                                                        |

| RST     | Ι    | High                 | External system reset. A High on this pin for at least one clock cycle while the external system clock (CLK) is running resets the device.                                                           |

| HALT_ST | 0    | High                 | A High state on this pin indicates that the CPU has<br>executed a Halt instruction and is awaiting either a non-<br>maskable or maskable interrupt before operation can<br>resume.                   |

| WAIT_ST | I    | High                 | A High on this pin indicates to the CPU that the addressed<br>memory or I/O device is not ready for a data transfer. The<br>CPU continues to enter a wait state as long as this signal<br>is active. |

| Name  | Туре | Polarity/Bus<br>size | Description                                                                                                                                                                                                                                                                                                              |

|-------|------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT   | Ι    | High                 | Maskable Interrupt Request. This signal is generated by<br>the I/O device. The CPU honors a request at the end of<br>the current instruction, if the internal software-controlled<br>interrupt enable flip-flop is enabled.                                                                                              |

| NMI   | I    | Rise                 | Non-maskable Interrupt Request. This signal has a higher<br>priority than INT and is always recognized at the end of<br>the current instruction, irrespective of the status of the<br>interrupt enable flip-flop, and forces the CPU to restart at<br>address 0066h.                                                     |

|       |      | Sys                  | stem Control Signals                                                                                                                                                                                                                                                                                                     |

| M1    | 0    | High                 | This signal is used to distinguish between a memory fetch<br>operation and a normal data memory read operation.<br>When active together with MEMRD, it indicates that the<br>current machine cycle is the Opcode fetch cycle of an<br>instruction execution                                                              |

| TRI   | 0    | Low                  | Tri-state bus control. This signal is used to enable off-core tri-state buffering for the MEMWR, MEMRD, SFRWR and SFRRD signals.                                                                                                                                                                                         |

| MEMWR | 0    | High                 | This signal indicates that the CPU data bus holds valid data to be stored at the addressed memory                                                                                                                                                                                                                        |

| MEMRD | 0    | High                 | This signal indicates that the CPU wants to read data from memory and memory should use this signal to gate data onto the CPU data bus                                                                                                                                                                                   |

| SFRWR | 0    | High                 | This signal indicates that the CPU data bus holds valid data to be written to the I/O device                                                                                                                                                                                                                             |

| SFRRD | 0    | High                 | This signal indicates that the CPU wants to read data from<br>an I/O device and the device should use this signal to gate<br>data onto the CPU data bus                                                                                                                                                                  |

|       |      | В                    | us Control Signals                                                                                                                                                                                                                                                                                                       |

| REQ   | I    | High                 | This signal has a higher priority than NMI and is always<br>recognized at the end of the current machine cycle. When<br>this signal is active, the CPU address bus, data bus and<br>associated control signals are forced to go to a high-<br>impedance state, so that other devices can take control of<br>these lines. |

| Name     | Туре | Polarity/Bus<br>size | Description                                                                                                                                                                                                                       |

|----------|------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK      | 0    | High                 | When this signal is active, it indicates to the requesting<br>device that the CPU address bus, data bus and<br>associated control signals have entered their high-<br>impedance state and it can now take control of these lines. |

|          |      |                      | Data Bus Signals                                                                                                                                                                                                                  |

| DATA_TRI | 0    | Low                  | Data bus tristate control                                                                                                                                                                                                         |

| DATAO    | 0    | 8                    | Data bus output                                                                                                                                                                                                                   |

| MEMDATAI | I    | 8                    | Data bus input from external memory space                                                                                                                                                                                         |

| SFRDATAI | I    | 8                    | Data bus input from external peripheral I/O space                                                                                                                                                                                 |

|          |      | Ad                   | ddress Bus Signals                                                                                                                                                                                                                |

| ADDR_TRI | 0    | Low                  | Address bus tristate control                                                                                                                                                                                                      |

| ADDR     | 0    | 16                   | Address bus output. This 16-bit signal specifies I/O and<br>memory addresses to be accessed. The bus is an input<br>when the external master is accessing the on-chip<br>peripherals                                              |

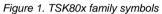

#### **Memory organization**

The TSK80x has a 16-bit address bus capable of addressing up to 64KB of memory space. This same memory space is used to store both code (program) and data. The microcontroller does not distinguish between Program and Data memory space; if a different space is required for Data and Program memory, separate external memory blocks must be used. When separate memory blocks are used, an additional external device must be used in order to switch between the two.

The TSK80A can also communicate with external peripheral devices. To address I/O ports, it uses the same 16-bit address bus, so the addressable I/O space is also 64KB. However, full access in both directions is only available within the first 256 bytes (0000h – 00FFh).

The memory and I/O space are different. This is described in more detail in the following sections.

#### **Memory map**

The TSK80x can address up to 64KB of memory space, from 0000h to FFFFh. After a reset, the CPU starts program execution from location 0000h. From this location, the first instruction Opcode is fetched and executed.

The lower part of the Program memory includes a non-maskable interrupt (stored at address 0066h), a maskable interrupt vector in mode 1 (stored at address 0038h) and all restart vectors.

When the CPU reads data from memory, the MEMRD signal goes to an active state (High) and then memory is read. When an instruction Opcode is read, an additional signal, M1, goes into active state

(High). Controlling the state of M1 gives information on what kind of memory access is being processed.

The memory map is illustrated in the figure below.

Figure 2. Memory map

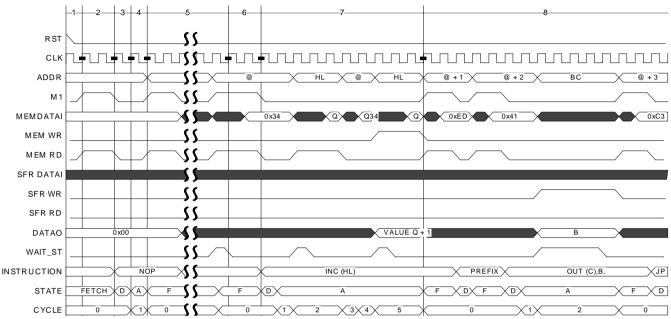

## **Memory fetch operation**

Signal M1 is used to distinguish between normal data read from memory and an instruction fetch. It goes to an active state (High) on the rising edge of the clock in cycle 1 when the instruction fetch cycle starts and it returns to invalid state on the rising edge of the clock in cycle 2, when the fetch cycle finishes.

In summary, a memory fetch operation is distinguished from a memory read by the active state of signal M1.

For slow memory devices, the CPU can add additional cycles and wait on data.

#### External I/O ports space

The TSK80x can address up to 64KB of external I/O space, from 0000h to FFFFh. Only ports addressed in the lowest 256 bytes of this space are fully accessible (both read and write). Addressing of ports above this range is made possible by special features inherent to the execution of the input and output instructions.

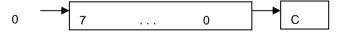

When addressing I/O space, all signals on the address bus have an active state, but only the lowest eight are valid (equating to 256 bytes). One of the general purpose registers is passed on the top half of the address bus at the same time. This behavior makes it possible to utilize all 64KB of I/O space.

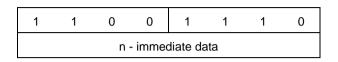

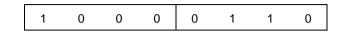

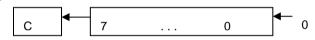

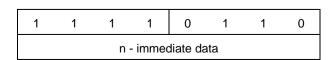

During instructions IN A,(n) and OUT (n),A, immediate data *n* is passed on to the low order byte of the address bus and the contents of the Accumulator are passed on to the high order byte. This feature gives free access to any port in the entire 64KB I/O address space, but only when reading data. When

writing data, the data that is to be written (contained in the Accumulator and subsequently put onto the data bus) is the same value that is put onto the high order byte of the address bus. The range of addressable space is therefore limited by the value of the data that is to be written. For example, if the data to be written is FFh (stored in the Accumulator), you could conceivably use any value in the range 00h - FFh for n and hence write to any port in the I/O space (0000h - FFFFh). However, if the data to be written from the Accumulator was 20h, then the addressable I/O space would be limited to the range 0000h - 20FFh.

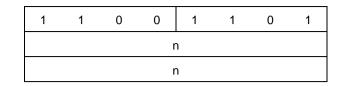

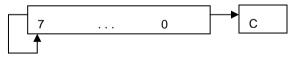

The instructions IN  $r_{r}(C)$  and OUT (C), r are more flexible, but they have limitations too. In these instructions, the contents of register C are placed on to the low order byte of the address bus and the contents of register B on to the high order byte.

# Hardware description

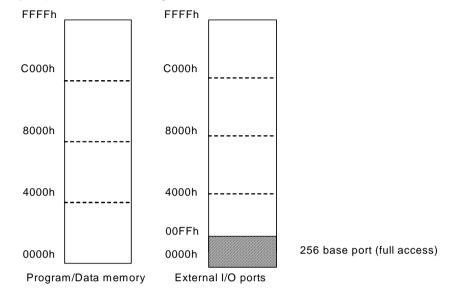

## **Block diagram**

Figure 3 shows the block diagram for the TSK80x. The processor is essentially divided into four subblocks:

- the main State Machine (FSM)

- the Decoder

- the ALU

- the Internal Registers.

Figure 3. TSK80x block diagram

## Finite State Machine (FSM)

The processor's state machine has two main functions – it controls the processor's control outputs during an instruction cycle and also manages exception vectors (interrupts, halt and external bus request).

The state machine controls all access to external memory and peripheral devices. It also ensures that the current instruction has completed before an exception is processed and executed.

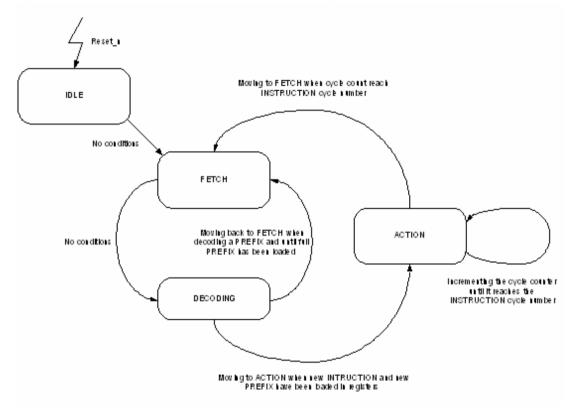

Figure 4 summarizes the states involved in an instruction cycle and the transitions between each.

Figure 4. TSK80x main state machine: Instruction cycle

The IDLE state is the initial state, entered upon reception of an external reset (RST). As can be seen, the actual instruction cycle consists of the following three states (stages):

- FETCH the processor loads a new instruction byte from memory

- **DECODING** the processor interprets the instruction byte loaded during the FETCH stage, determines if it is a prefix byte and, if it is, returns to the FETCH state to load the rest of the instruction. After the full instruction has been loaded, the processor enters the ACTION state, to start the execution of the instruction

- ACTION the processor activates the relevant control signals to complete the instruction. In the

case of a multi-clock cycle instruction (e.g. an addition between two registers) the state machine

increments the cycle counter, activating the relevant control signals as required.

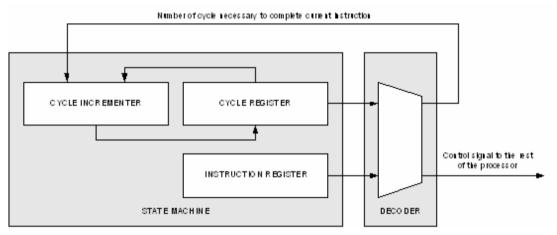

## Decoder

Where the state machine controls external access and general data flow inside the processor, the Decoder controls all of the instruction-specific internal control signals. The state machine passes the value of a newly-loaded instruction to the Decoder. The Decoder uses this value to generate the required internal control signals.

Upon entering the ACTION state, the Decoder sends the number of cycles required for the instruction, back to the state machine. The state machine increments its internal cycle counter until it reaches this value, after which it knows that the current instruction has completed and it can FETCH the next instruction from memory. Figure 5 summarizes the interaction between the state machine and the Decoder.

Figure 5. FSM-Decoder interaction in the TSK80x

## ALU

The Arithmetic Logic Unit (ALU) is involved in every operation on the data. The CPU executes the following operations:

- Add 8-bit data with or without Carry flag

- Subtract 8-bit data with or without Carry flag

- Increment and decrement 8-bit data

- Logic operation AND, OR, XOR on 8-bit data

- Compare 8-bit data with Accumulator

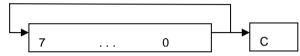

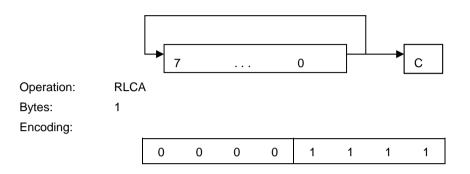

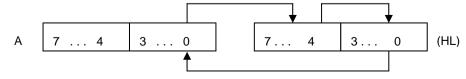

- Shift, rotate 8-bit data with or without Carry flag

- Set, reset or test any bit in 8-bit data

- Convert Accumulator into packed BCD

- Negate Accumulator (0 A)

- Logic operation NOT on data in Accumulator

- Add 16-bit data with or without Carry flag

- Subtract 16-bit data with Carry flag

Increment and decrement 16-bit data.

The result of all 8-bit operations is stored in the Accumulator and reflected in the status of various flags in the flag register (F).

For 16-bit operations, the result is stored in register HL (which acts as the Accumulator). For instructions with an Opcode prefix of DD or FD, the result is stored in the IX and IY registers respectively.

The Flag register (F) tests the following conditions:

- S sign (first bit of result)

- Z zero (is set (1) if the result of the operation is 0)

- H half carry (is set (1) if the add or subtract operation produced a carry into or a borrow from bit 4

of the result

- P/V parity/overflow (is set (1) if the result of the operation is even or produced an overflow)

- N add/subtract (is set (1) if last executed operation was a subtract

- C carry (set (1) if the operation produced a carry from the MSB of the result.

The Flag register can also be changed by other instructions not connected with logical or arithmetic operations. In such cases, the conditions tested as listed above may not necessarily apply. Examples are block transfer instructions or set carry flag instructions (SCF) that only write to the Carry flag.

#### Registers

All registers in the TSK80x can be changed under program control. They can be split into three groups, as described below.

The first group consists of two duplicate sets of 8-bit registers - base and alternative. Only one set can be used at a time. Switching between sets is executed by software (instructions EXX and EX AF, AF'). Both sets in this group consist of the following registers:

- A (Accumulator)

- F (Flag register)

- B, C, D, E, H and L (General Purpose registers)

Although they are 8-bit registers, they can be treated as 16-bit registers. In this case, registers can be joined in the following pairings: B and C as BC; D and E as DE; H and L as HL; A and F as AF.

The second group consists of five registers with assigned functions. These are:

- Index registers (IX and IY) used in index addressing mode

- Stack Pointer (SP) used to store address on top of Stack

- · Program Counter (PC) used to store address of next instruction to be executed

- Interrupt register (I) used to store the interrupt address and the device requesting the service

The third group consists of two Interrupt Status registers (IFF1, IFF2) and the Interrupt Mode register (IM). The Interrupt Status registers store information as to whether a maskable interrupt request should be serviced or not. Its state can be changed by the Enable Interrupt instruction (EI) and Disable Interrupt instruction (DI). The actual state can be tested only indirectly with the results of executed instruction LD A,I which changes the flag P/V depending on the state of the register IFF2. Additionally,

when servicing non-maskable interrupts, the state of register IFF1 is stored into IFF2 and IFF1 is reset (disable maskable interrupts).

The RETN instruction is used for copying the contents of IFF2 back into IFF1 (setting IFF1 back to its original state, prior to the non-maskable interrupt being serviced).

The IM register is less flexible (no way to test its value). Its state can be set only by execution of instructions IM0, IM1, or IM2. Each one sets a different interrupt service mode.

## The B, C, D and E registers

The B, C, D and E registers are 8-bit registers set to 00h after a reset of the processor. They are used as general purpose registers to store data. In some of the instructions, they are connected in a pair (B to C and D to E) and are then treated as 16-bit registers. As a 16-bit register, they can contain a 16-bit data value, be used as an address register (storing an address of a location in memory space), or act as a transfer counter (BC pair only).

### The H and L registers

The H and L registers are 8-bit registers set to 00h after a reset of the processor. They are used as general purpose registers to store data and as a 16-bit register pair to store the address of an operand.

As an address register, HL is more flexible than register pairs BC and DE. Almost all operations appear in addressing mode using register HL. In transfer data operations, the HL register is used as the source or destination address register. For 16-bit arithmetic operations, HL is used as a register that stores the result of an operation (acting as the Accumulator).

## The IX and IY registers

The Index registers (IX and IY) are 16-bit registers set to 0000h after a reset of the processor. They mainly store addresses used in indexed addressing mode but can also be used as general purpose registers. They can be used the same way as register HL but not in instructions which operate on 8-bit data. (There are no instructions that operate on the high or low order bytes of registers IX and IY only).

## **Program Counter (PC)**

The Program Counter (PC) is a 16-bit wide register that is set to 0000h after a reset of the processor. Its value is incremented in every FETCH cycle after reading the instruction Opcode.

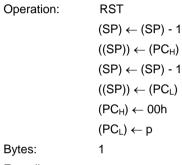

## **Stack Pointer (SP)**

The Stack Pointer (SP) is a 16-bit register set to 0000h after a reset of the processor. It is automatically incremented at the beginning of execution of instructions POP or RET and is decremented in instructions PUSH, CALL and RST. The SP always contains the address of the last stored data on the external memory stack.

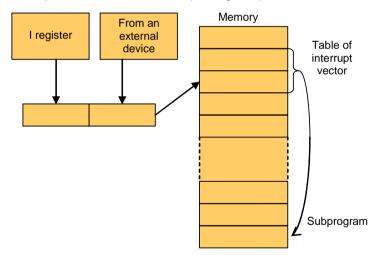

#### Interrupt register (I)

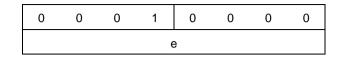

The Interrupt register (I) is an 8-bit register set to 00h after a reset of the processor. It stores the basic addresses of the interrupts vector table.

In an interrupt acknowledge cycle, in interrupt mode 2, its value (placed in high order byte of address bus) along with data from the serviced device (placed in low order byte of address bus) comprises the address of the first instruction of the interrupt service routine.

### **Bus request cycle**

On the rising edge of the last clock cycle of every machine cycle, the state of signal REQ is tested. If it is Low, no special action is made. If it is High, the CPU disconnects itself from all buses.

Signal ACK is set to High to show other devices that the processor is disconnected from the system and other devices can take control of all lines. The rest of the signals are set to a non-active state. The exception is signal HALT\_ST which does not change state (if it was High it will remain High, if it was Low, it will stay Low).

The CPU remains in this state, only testing the state of signal REQ (on every rising edge of the clock). When the tested signal changes to Low, the CPU leaves this suspended state and resumes program execution from the next instruction. If the CPU was in the middle of executing an instruction before it was disconnected from the bus lines, it will not resume execution of this same instruction, rather it will resume by executing the subsequent instruction. On the falling edge of the clock, signal ACK (at the same time finding a Low on signal REQ) is set to Low.

The REQ signal has higher priority than interrupts and, during a bus request/acknowledge cycle, the processor cannot be interrupted.

**Note**: Off-core tristate buffers can be wired into a design in order to place bus signals in a high impedance state. Tristate control signals are provided for this very purpose:

- ADDR\_TRI for the ADDR bus

- DATA\_TRI for the DATAO, MEMDATAI and SFRDATAI buses

- TRI for the MEMWR, MEMRD, SFRWR and SFRRD lines.

#### Halt Acknowledge

| CLK     |         |

|---------|---------|

| HALT_ST |         |

|         | ♀sample |

| NMI     |         |

Figure 6. Halt acknowledge

Note: sample - point at which signal is tested.

The result of the execution of the HALT instruction is that the CPU goes into a loop, which looks as though the NOP instruction is continuously being executed. The difference is that the CPU does not fetch the next instruction. Instead, the Program Counter does not change its value and the HALT\_ST signal is set to High (on the falling edge of the fourth clock cycle in the machine cycle in which the HALT instruction is executed).

The processor does not take any action. It tests interrupt signals on the rising edge of the fourth clock cycle in each machine cycle. The processor can be in this state without any time restriction, but if the CPU starts to service an interrupt, this cycle is suspended and the CPU returns to normal work.

### Hardware Reset (RST)

All registers are synchronously reset by the external reset signal (RST). After a reset, all bits in the registers are set to zero. The processor's main state machine is put into the IDLE state, maskable interrupts are masked and all external control signals go to an inactive state.

The processor stays in this state as long as a reset condition occurs. After reset (when signal RST changes to Low), the CPU starts executing an instruction fetch. The first instruction is fetched from address 0000h.

#### Interrupts

The TSK80x microcontroller has two interrupt request inputs – INT (maskable interrupt) and NMI (non-maskable interrupt). Interrupt service processing depends on the type of interrupt that was detected.

#### Non-maskable interrupt

The non-maskable interrupts cannot be disabled by program control and therefore will be accepted at all times by the CPU. They have a higher priority than maskable interrupts and are serviced first when both NMI and INT active signals are received at the same time.

After an interrupt is detected, the processor makes a special machine cycle (shown in Figure 7). This cycle is similar to the FETCH cycle but no data is read. The CPU then pushes the contents of the Program Counter onto the stack and makes a jump to address 0066h (the first instruction of the non-maskable service routine should be placed at this location).

In addition, maskable interrupts are disabled, preventing any further interrupts during the servicing of the non-maskable interrupt. The enable status of maskable interrupts is stored in the Interrupt Enable flip-flop IFF1. When a non-maskable interrupt is accepted, this flip-flop is reset (0), disabling maskable interrupts from being accepted. Its previous state (enabled or disabled) is stored however, enabling the interrupt state prior to the non-maskable interrupt to be restored after the current interrupt has been serviced. The state of the maskable interrupt is stored by copying the contents of interrupt enable flip-flop IFF1 into IFF2.

**Note:** The non-maskable interrupt input is edge-triggered. The signal is tested on the rising edge of the last cycle during the current instruction.

The NMI signal is an asynchronous input. If signal NMI changes value (from 0 to 1) before the last clock period of an instruction cycle, for the interrupt to be recognized the rising edge must be  $t_{set}$  before the rising edge of that last clock ( $t_{set}$  is equal to the delay time on one level logic). Otherwise the next instruction will be executed and the interrupt will be handled after its completion.

| CLK       |          |

|-----------|----------|

|           |          |

| NMI       |          |

| ADDR[150] | ) PC ) ( |

| M1        |          |

|           |          |

| MEMRD     |          |

|           |          |

#### Figure 7. Non-maskable interrupt

#### Note: PC - instruction address (contents of Program Counter (PC))

#### **Maskable interrupts**

The maskable interrupt input (INT) is level-sensitive and is tested at the rising edge of the last clock cycle of any instruction. If it is High, the interrupt service is enabled and, providing interrupts have been enabled and there is no non-maskable interrupt request or bus request, the special interrupt acknowledge cycle begins.

Note that after a reset of the processor, interrupts are, by default, disabled. The EI instruction should be used to enable interrupts. After the EI instruction is executed, any interrupt request that is waiting for acknowledgement will not be accepted until the instruction after the EI instruction has been executed.

The interrupt acknowledge cycle is similar to the FETCH cycle, with the difference being that signal SFRRD becomes active rather than MEMRD and additional wait cycles are inserted. These additional wait cycles force the processor to wait before reading data and therefore enables an external device to properly synchronize. Figure 8 shows a maskable interrupt request/ acknowledge cycle.

| CLK          |                                       |

|--------------|---------------------------------------|

| ADDR[150]    | PC ( )                                |

| INT          | ⊊sample                               |

| M1           |                                       |

| SFRRD        |                                       |

| WAIT_ST      | φsample φsample φsample               |

| SFRDATAI[70] | • • • • • • • • • • • • • • • • • • • |

| Figure 8. Maskable | interrupt r | eauest and | acknowledge cycle |

|--------------------|-------------|------------|-------------------|

|                    |             |            |                   |

| Note: | PC     | - instruction address (contents of Program Counter PC)               |

|-------|--------|----------------------------------------------------------------------|

|       | read   | - point at which the data is read into the CPU                       |

|       | sample | <ul> <li>point at which signal is tested (SFRRD, WAIT_ST)</li> </ul> |

When an interrupt request is detected, the next cycle starts as a normal FETCH cycle (the contents of the PC are put onto the address bus and M1 is activated).

On the falling edge of the second clock cycle after M1 goes active, the SFRRD signal changes to High and the CPU waits on data. On the falling edge of the next clock cycle, signal WAIT\_ST is tested and if it is active (High), the processor stays in this same state until the WAIT\_ST signal is changed to Low.

Each accepted interrupt request causes a clear of the IFF1 flip-flop - to disable interrupts.

On the rising edge of the next clock cycle after WAIT\_ST goes Low, the CPU reads data from the data bus. How this information will be used depends on the interrupt mode. This mode is changed under program control and, by default, after a reset of the processor it is set in mode 0. The TSK80x has three maskable interrupt modes described in the following section.

**Note:** Maskable interrupts are requested by a High level on signal INT, as opposed to a rising edge on the NMI signal, used to request a non-maskable interrupt.

#### TSK80x MCU

### Maskable interrupt modes

The interrupt request/acknowledge cycle is the same for every mode. The difference is how the data is read during this cycle.

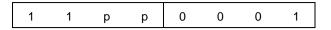

**MODE 0** – In this mode, the peripheral device requesting the interrupt can place any instruction on the data bus. For single byte instructions, the processor reads the instruction during acknowledgement of the interrupt request and executes it in the normal way. In general, it is a restart instruction, but all other instructions can be used.

For instructions that require more than one byte of data (e.g. CALL), the external device must disconnect memory and place the needed data onto the data bus in the correct time period (the processor reads only one byte during the interrupt request/acknowledge cycle; all other bytes of data are read in accordance with the processor's normal data memory read cycle).

**MODE 1** – In this mode, a normal interrupt acknowledge cycle is made, but data put onto the data bus is not read by the processor, it is ignored. This mode is very similar to that of a non-maskable interrupt request/acknowledge but the CPU jumps to another address (0038h) for the first instruction of the service routine.

**MODE 2** – This is the most flexible interrupt mode. In this mode, during the interrupt cycle, the processor reads a byte of data from the data bus and treats it not as an instruction (like in MODE 0), but as the low order byte of the address bus. The high order byte of the address bus is loaded from the processor's Interrupt register (I). This address points to the location in memory where the first instruction of the interrupt service routine is stored (see Figure 9).

#### Figure 9. Call interrupt routine in mode 2.

This method of address construction allows different interrupt service routines for different devices to be used, or many interrupt service routines for one device depending on the situation. Additionally, all interrupt service routines can be placed in any memory location.

# **On-Chip Debugging**

The debug-enabled version of the microcontroller (TSK80A\_D) provides the following set of additional functional features that facilitate real-time debugging of the microcontroller:

- Reset, Go, Halt processor control

- Single or multi-step debugging

- · Read-write access for internal processor registers including IX, IY, SP and PC

- Read-write access for memory and I/O space

- Hardware execution breakpoints (configurable number of breakpoint address registers and breakpoint data registers) allows trigger address and data for memory and I/O space.

- Hardware triggers can be set on an address range and/or data with masking bits

- Unlimited software breakpoints.

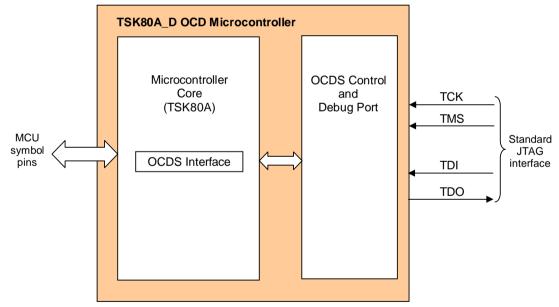

# Adding debug functionality to the standard core

The debug functionality of the TSK80A\_D is provided through the use of an On-Chip Debug System unit (OCDS). The simplified block diagram of Figure 10 shows the connection between this unit and the standard TSK80A core.

Figure 10. Simplified TSK80A\_D block diagram

The host computer is connected to the target core using the IEEE 1149.1 (JTAG) standard interface. This is the physical interface, providing connection to physical pins of the FPGA device in which the core has been embedded.

The Nexus 5001 standard is used as the protocol for communications between the host and all devices that are debug-enabled with respect to this protocol. This includes all OCD-version microcontrollers, as well as other Nexus-compliant devices such as frequency generators, logic analyzers, counters, etc.

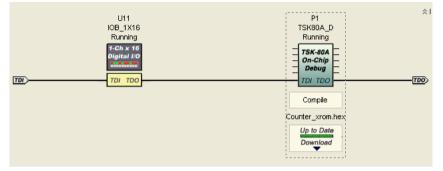

All such devices are connected in a chain – the Soft Devices chain – which is determined when the design has been implemented within the target FPGA device and presents in the **Devices** view (Figure 11). It is not a physical chain, in the sense that you can see no external wiring – the connections required between the Nexus-enabled devices are made internal to the FPGA itself.

Figure 11. Nexus-enabled microcontroller appearing in the Soft Devices chain

For microcontrollers such as the TSK80A\_D, the Nexus protocol enables you to debug the core through communication with the OCDS Unit.

## Accessing the debug environment

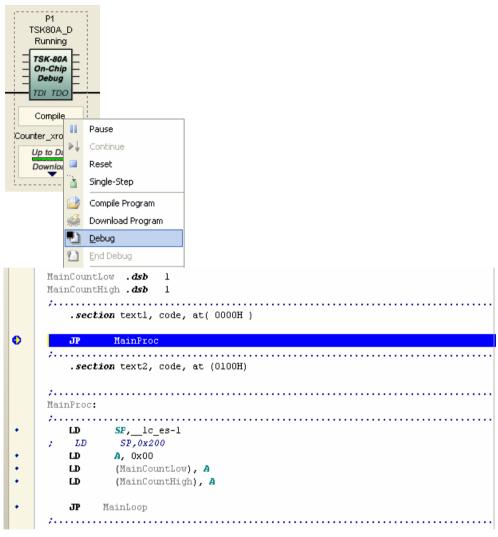

Debugging of the embedded code within an OCD-version microcontroller is carried out by starting a debug session. Prior to starting the session, you must ensure that the design, including one or more OCD-version microcontrollers and their respective embedded code, has been downloaded to the target physical FPGA device.

To start a debug session for the embedded code of a specific microcontroller in the design, simply right-click on the icon for that microcontroller, in the Soft Devices region of the view, and choose the **Debug** command from the pop-up menu that appears. Alternatively, click on the icon for the microcontroller (to focus it) and choose **Processors » Pn » Debug** from the main menus, where n corresponds to the number for the processor in the Soft Devices chain.

The embedded project for the software running in the processor will initially be recompiled and the debug session will commence. The relevant source code document (either Assembly or C) will be opened and the current execution point will be set to the first line of executable code (see Figure 12).

**Note**: You can have multiple debug sessions running simultaneously – one per embedded software project associated with a microcontroller in the Soft Devices chain.

Figure 12. Starting an embedded code debug session.

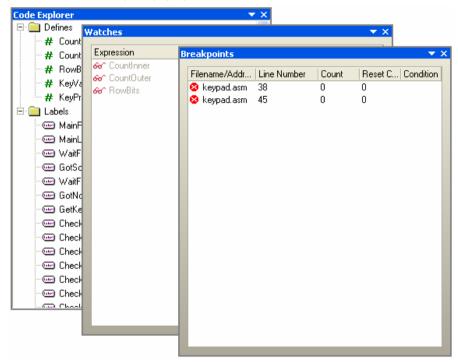

The debug environment offers the full suite of tools you would expect to see in order to efficiently debug the embedded code. These features include:

- Setting Breakpoints

- Adding Watches

- Stepping into and over at both the source (\*.C) and instruction (\*.asm) level

- Reset, Run and Halt code execution

- Run to cursor

All of these and other feature commands can be accessed from the **Debug** menu or the associated **Debug** toolbar.

#### TSK80x MCU

Various workspace panels are accessible in the debug environment, allowing you to view/control codespecific features, such as Breakpoints, Watches and Local variables, as well as information specific to the microcontroller in which the code is running, such as memory spaces and registers.

These panels can be accessed from the **View** » **Workspace Panels** » **Embedded** sub menu, or by clicking on the **Embedded** button at the bottom of the application window and choosing the required panel from the subsequent pop-up menu.

Figure 13. Workspace panels offering code-specific information and controls

|                                                                                        | H                                      | legisti                | er   |              |    | W  | ʻidth |    |    | D    | ecin         | nal             |       | Hexa              | adeci        | mal                     |              | Bin      | ary  |              |       |            |          |      | C    | har          |      |          |            |                      |                      |                                                               |

|----------------------------------------------------------------------------------------|----------------------------------------|------------------------|------|--------------|----|----|-------|----|----|------|--------------|-----------------|-------|-------------------|--------------|-------------------------|--------------|----------|------|--------------|-------|------------|----------|------|------|--------------|------|----------|------------|----------------------|----------------------|---------------------------------------------------------------|

|                                                                                        | 0 A                                    |                        |      |              |    |    |       |    |    | 8    |              |                 | 2     |                   |              |                         | 02           |          |      |              |       | 00         | 00-1     | 0010 | ).   |              |      | 1        |            |                      |                      |                                                               |

|                                                                                        | 1 F                                    |                        |      |              |    |    |       |    |    | 8    |              |                 | 2     |                   |              |                         | 02           |          |      |              |       | 00         | 00-1     | 0010 | ).   |              |      |          |            |                      |                      |                                                               |

|                                                                                        | 2 B                                    |                        |      |              |    |    |       |    |    | 8    |              |                 | 112   |                   |              |                         | 70           |          |      |              |       | 01         | 11-      | 0000 | ) р  |              |      |          |            |                      |                      |                                                               |

|                                                                                        | 3 C                                    |                        |      |              |    |    |       |    |    | 8    |              |                 | 58    |                   |              |                         | 34           |          |      |              |       | 00         | )11-     | 1010 | ) :  |              |      |          |            |                      |                      |                                                               |

|                                                                                        | 4 D                                    |                        |      |              |    |    |       |    |    | 8    |              |                 | 0     |                   |              |                         | 00           |          |      |              |       | 00         | 00-1     | 0000 | ).   |              |      |          |            |                      |                      |                                                               |

|                                                                                        | 5 E                                    |                        |      |              |    |    |       |    |    | 8    |              |                 | 0     |                   |              |                         | 00           |          |      |              |       | 00         | 00-1     | 0000 | ).   |              |      |          |            |                      |                      |                                                               |

|                                                                                        | 6 H                                    |                        |      |              |    |    |       |    |    | 8    |              |                 | 0     |                   |              |                         | 00           |          |      |              |       | 00         | 00-1     | 0000 | ).   |              |      |          |            |                      |                      |                                                               |

|                                                                                        | 7 L                                    |                        |      |              |    |    |       |    |    | 8    |              |                 | 0     |                   |              |                         | 00           |          |      |              |       | 00         | 00-1     | 0000 | ).   |              |      |          |            |                      |                      |                                                               |

|                                                                                        | 8 A                                    | F                      |      |              |    |    |       |    | 1  | 6    |              |                 | 514   |                   |              |                         | 0202         |          |      | 0000         | 0-001 | 0-00       | 00-1     | 0010 | )    |              |      |          |            |                      |                      |                                                               |

|                                                                                        | 9 B                                    | С                      |      |              |    |    |       |    | 1  | 6    |              | 2               | 28730 |                   |              |                         | 703A         |          |      | 0111         | -000  | 0-00       | 11-      | 1010 | ) D: |              |      |          |            |                      |                      |                                                               |

| gram M                                                                                 | 1em c                                  | ry                     |      |              |    |    |       |    |    |      |              |                 |       |                   |              |                         |              |          | -    | ×            | 0-000 | 0-00       | 00-1     | 0000 |      |              |      |          |            |                      |                      |                                                               |

| 0x000                                                                                  | 0000                                   |                        |      |              |    |    |       |    |    |      |              |                 |       |                   |              |                         |              |          |      |              | 0-000 |            |          |      |      |              |      |          |            |                      |                      |                                                               |

| Address                                                                                | °.                                     | 0 1                    | 2    | 3            | 4  | 5  | 6     | 7  | 8  | 9    | A            | вc              | D     | EF                | Data         |                         |              |          |      |              | 0-000 | 0-00       | 00-1     | 0000 | )    |              |      |          |            |                      |                      |                                                               |

| 00 000                                                                                 |                                        | C3 00                  | _    | 00 0         |    | -  | 00    |    | _  |      |              |                 |       | 00 00             |              |                         |              |          |      |              | 0-000 | 0-00       | 00-1     | 1000 | 1    |              |      |          |            |                      |                      |                                                               |

| 00 001                                                                                 | .0                                     | 00 00                  | 00   | 00           | 00 | 00 | 00    | 00 | 00 | 00   | 00 0         | 0 00            | 00 0  | 00 00             |              |                         |              |          |      |              | 0-010 |            |          |      |      |              |      |          |            |                      |                      |                                                               |

| 00 002                                                                                 | 0                                      | 00 00                  | 00   | 00           | 00 | 00 | 00    | 00 | 00 | 00 ( | 00 0         | C SFR           | ξ     |                   |              |                         |              |          |      |              |       |            |          |      |      |              |      |          |            |                      |                      |                                                               |

| 00 003                                                                                 | 0                                      | 00 <b>0</b> 0          | 00   | 00           | 00 | 00 | 00    | 00 | 00 | 00 ( | 00 0         | 0 🛃             | 0xl   | 000000            | 1            |                         |              |          |      |              |       |            |          |      |      |              |      |          |            |                      |                      |                                                               |

| 00 004                                                                                 |                                        | 00 00                  | 00 ( | 00           | 00 | 00 | 00    | 00 | 00 | 00 ( | 00 0         | 9 -             | Addr  |                   | 0            | 1 2                     | 23           | 4        | 5    | 6            | 78    | 9          | A        | В    | С    | D            | - c  | Da       | at a       |                      |                      |                                                               |

| 00 005                                                                                 |                                        | 00 00                  |      | 00           |    |    |       |    |    |      | 00 0         | 100             | 00 00 |                   | FFF          |                         | 2 3<br>F 00  | FF       | -    | O<br>FF F    | 7 O   | -          |          | -    |      | FF           |      |          |            |                      |                      |                                                               |

| 00 006                                                                                 |                                        | 00 00                  |      | 00 (         |    |    |       |    |    |      | 00 0         | 0               | 00 0  |                   | FF           |                         | FFF          | FF       | FF   | FFF          | FFF   | FF         | FF       | FF   | FF   | FF           |      |          |            |                      |                      | 1111                                                          |

| 00 007                                                                                 |                                        | 00 00                  |      |              |    |    |       |    |    |      |              | 1 00            | 00 0  | 020               | FF           | F F                     | FFF          | FF       | FF   | FFF          | FFF   | FF         | FF       | FF   | FF   | FF           | FFF  |          |            |                      |                      | vyyy                                                          |

| 00 008                                                                                 |                                        | 00 00                  |      |              |    |    |       |    |    |      | 00 0         | 1 00            | 00 0  | 030               | FF F         | F F                     | FFF          | FF       | FF   | FFF          | FFF   | FF         | FF       | FF   | FF   | FF           | FFF  | ÿÿ       | ÿÿÿ        | <u> </u>             | 7999                 | -                                                             |

|                                                                                        |                                        | 00 00                  |      | 00 0         |    |    |       |    |    |      | 00 0<br>00 0 | 1 00            | 00 0  | 040               | FF F         |                         | FFF          | FF       | FF   | FFF          | FFF   | FF         | FF       | FF   | FF   | FF           | FFF  |          |            |                      |                      | vyyyy                                                         |

|                                                                                        |                                        | 00 00                  |      |              |    |    |       |    |    |      | 00 0         | 100             | 00 0  | 050               | FF           | F                       | FF           | FF       | FF   | FFF          | FFF   | FF         | FF       | FF   | FF   | FF           | FFF  | ÿÿ       | ÿÿÿ        | ÿÿÿÿ                 | ryyy                 | yyyy                                                          |

| 00 00A                                                                                 |                                        |                        |      |              |    |    |       |    |    |      |              | 100             | 00 0  | 060               | FF I         | F                       | FFF          | FF       | FF   | FF F         | FFF   | FF         | FF       | FF   | FF   | F F          | FFF  | ÿÿ       | ÿÿÿ        | ÿÿÿÿ                 | 7999                 | -<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y<br>Y |

| 00 00A                                                                                 |                                        |                        |      |              |    |    |       |    |    |      |              | 1 00            | 00 0  | 070               | FFF          | F F                     | FF           | FF       | FF   | FF F         | FFF   | FF         | FF       | FF   | FF   | F F          | FFF  | ÿÿ       | ÿÿÿ        | ÿÿÿÿ                 | 7999                 | <del>, 2222</del>                                             |

| 00 00A<br>00 00B<br>00 00C                                                             | :0                                     | 20.00                  |      |              |    |    |       |    |    |      | 00 0         | 1 00            | 00 0  | 080               | FF           | F F                     | FFF          | FF       | FF   | FF F         | F FF  | FF         | FF       | FF   | FF   | F F          | FFF  | ÿÿ       | ÿÿÿ        | 9993                 | ryyy                 | <del>YYYY</del>                                               |

| 00 00A<br>00 00B<br>00 00C                                                             | 0                                      | 00 00                  | ) 00 | _            |    |    |       |    |    |      |              | o 00            | 00 0  |                   | FF           | F F                     | FF           | FF       | FF   | FF F         | FFF   | FF         | FF       | FF   | FF   | FF F         | F FF | 'ÿÿ      | ÿŸŸ        | ÿŸŸŠ                 | rÿÿÿ                 | ŶŶŶŶŶ                                                         |

| 00 00A<br>00 00B<br>00 00C<br>00 00D<br>00 00B                                         | :0<br>:0<br>:0                         |                        |      | 00           | 00 | 00 |       |    |    |      |              |                 |       |                   | FF           | F F                     | FFF          | FF       | FF   | FF F         | FFF   | FF         | FF       | FF   | FF 1 | FF F         | FFF  | ÿÿ       | ÿÿÿ        | ŸŸŸŸ                 | 7777                 | ŶŸŸŸŸ                                                         |

| 00 00A<br>00 00B<br>00 00C<br>00 00D<br>00 00B                                         | 00000000000000000000000000000000000000 | 00 00                  | 00   |              |    |    |       |    |    |      | 04 C         | 3 00            | 00 00 | DAO               |              |                         |              |          |      |              |       |            |          |      |      |              |      |          |            |                      |                      |                                                               |

| 00 00A<br>00 00B<br>00 00C<br>00 00D<br>00 00B<br>00 00F<br>00 010                     |                                        | 00 00                  | 00   | 3 <b>e</b> ( | 00 | 32 | 00    | 04 | 32 | 01 ( |              | 3 00            | 00 0  |                   | FF I         | F                       | FFF          | FF       | FF   | FF F         | FFF   | FF         | FF       | FF   | FF   | F F          | FFF  | ÿÿ       | ÿÿÿ        |                      |                      | -<br>YYYYY<br>Y                                               |

| 00 00A<br>00 00B<br>00 00C<br>00 00D<br>00 00B<br>00 00F<br>00 010                     |                                        | 00 00<br>00 00<br>31 0 | 00   | 3 <b>e</b> ( | 00 | 32 | 00    | 04 | 32 | 01 ( |              | 3<br>9 00<br>00 | 00 0  | 080<br>0C0        | FF F         | F F                     | F FF<br>F FF | FF<br>FF | FF : | FF F<br>FF F | F FF  | F F<br>F F | FF<br>FF | FF : | FF I | 7F F<br>7F F | F FF |          |            | ÿÿÿS                 | עעעי                 |                                                               |

| 00 009<br>00 00A<br>00 00B<br>00 00C<br>00 00D<br>00 00B<br>00 00B<br>00 010<br>00 011 |                                        | 00 00<br>00 00<br>31 0 | 00   | 3 <b>e</b> ( | 00 | 32 | 00    | 04 | 32 | 01 ( |              | 3<br>9 00<br>00 | 00 0  | 0B0<br>0C0<br>0D0 | FF F<br>FF F | 7F F:<br>7F F:<br>7F F: | • • •        | FF       | FF   | FFF          | FFF   | FF         | FF       | FF   | FF   | F F          | FFF  | ÿÿ<br>ÿÿ | 999<br>999 | 9993<br>9993<br>9993 | 9999<br>9999<br>9999 | פעעעי                                                         |

Figure 14. Workspace panels offering information specific to the parent processor.

Full-feature debugging is of course enjoyed at the source code level – from within the source code file itself. To a lesser extent, debugging can also be carried out from a dedicated debug panel for the processor. To access<sup>2</sup> this panel, first double-click on the icon representing the microcontroller to be debugged, in the **Soft Devices** region of the view. The *Instrument Rack – Soft Devices* panel will appear, with the chosen processor instrument added to the rack (Figure 15).

<sup>&</sup>lt;sup>2</sup> The debug panels for each of the debug-enabled microcontrollers are standard panels and, as such, can be readily accessed from the **View** » **Workspace Panels** » **Instruments** sub menu, or by clicking on the **Instruments** button at the bottom of the application window and choosing the required panel – for the processor you wish to debug – from the subsequent pop-up menu.

| P1<br>TSK80A_D     |                   |                   |                                   |            |

|--------------------|-------------------|-------------------|-----------------------------------|------------|

| Running            |                   |                   |                                   |            |

| TSK-80A<br>On-Chip |                   |                   |                                   |            |

| Debug              |                   |                   |                                   |            |

|                    |                   |                   |                                   |            |

| C Instrument Ra    | ck - Soft Devices |                   |                                   | <b>•</b> × |

| Counte JTAG        | CORE P1 (TSK80A_D | ))                |                                   | •          |

| PRO                | CESSOR CONTROL    | PROCESSOR STAT    |                                   |            |

|                    | Pause Continue    | PC: 0x0000        | F : 0x02 - 2 - 0000-0010          |            |

| Step               | Nexus Debugger    | SP: 0x05FB        | A: 0x02 - 2 - 0000-0010           |            |

| OPollin            |                   | 🔵 Running 🧕 Reset | TSK-80 Nexus Processor Controller | -          |

Figure 15. Accessing debug features from the microcontroller's instrument panel

**Note**: Each core microcontroller that you have included in the design will appear, when double-clicked, as an Instrument in the rack (along with any other Nexus-enabled devices).

The **Nexus Debugger** button provides access to the associated debug panel (Figure 16), which in turn allows you to interrogate and to a lighter extent control, debugging of the processor and its embedded code, notably with respect to the registers and memory.

One key feature of the panel is that it enables you to specify (and therefore change) the embedded code (HEX file) that is downloaded to the microcontroller, quickly and efficiently.

For more information on the content and use of processor debug panels, press **F1** when the cursor is over one of these panels.

For further information regarding the use of the embedded tools for the TSK80x, see the *Using the TSK80x Embedded Tools* guide.

For comprehensive information with respect to the embedded tools available for the TSK80x, see the *TSK80x Embedded Tools Reference*.

| SK80                                                                         | essor Re                                                                                                                        | nieto                                                                                                                  |                                                                          |                                        |                                                                                       |                                                               |                                                      |                                                                       |                                        |                                                                                                               |                                                                   |                                                                                                                |                                                   |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                               |                                                                       |       |     |        |       |      |   |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------|-------|-----|--------|-------|------|---|

| Proce<br>Name                                                                |                                                                                                                                 | -                                                                                                                      |                                                                          | Hex                                    |                                                                                       | 1                                                             |                                                      |                                                                       |                                        | D:.                                                                                                           |                                                                   |                                                                                                                |                                                   |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                               | C:-                                                                   |       | 1 1 |        |       | Char | ľ |

| Name<br>A                                                                    | Wie                                                                                                                             | _                                                                                                                      | r                                                                        | чех                                    |                                                                                       |                                                               |                                                      |                                                                       |                                        | BI                                                                                                            | hary                                                              |                                                                                                                |                                                   |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                               | Sig                                                                   | ined  | -   | Insigr |       | Char | - |

| а<br>:                                                                       |                                                                                                                                 | 8                                                                                                                      |                                                                          |                                        | 0                                                                                     |                                                               |                                                      |                                                                       |                                        |                                                                                                               |                                                                   |                                                                                                                | 000                                               |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                               |                                                                       | (     |     |        | 0     |      |   |