# Summary

Core Reference CR0121 (v2.0) July 15, 2006 The TSK3000A is a fully functional, 32-bit load/store, Wishbone-compliant processor that employs RISC architecture with a streamlined set of single word instructions. This core reference includes architectural and hardware descriptions, instruction sets and on-chip debugging functionality for the TSK3000A.

The TSK3000A is a 32-bit, Wishbone-compatible, RISC processor. Most instructions are 32-bits wide and execute in a single clock cycle. In addition to fast register access, the TSK3000A features a user-definable amount of zero-wait state block RAM, with true dual-port access.

The TSK3000A has been specifically designed to simplify the development of 32-bit systems targeted for FPGA implementation and to allow the migration of existing 8-bit systems to the 32-bit domain with relative ease and low-risk. As a result, complications typically associated with 32-bit system design, such as complex memory management, are minimized.

The TSK3000A, although a "classic RISC" processor and internally based on the Harvard architecture, features a greatly simplified memory structure and sophisticated interrupt handling to make coding simpler. The processor also simplifies the connection of peripherals with support for the Wishbone microprocessor bus.

The TSK3000A can be used with any FPGA device of suitable capacity supported by Altium Designer, giving a completely device and FPGA vendor-independent 32-bit system hardware platform.

## **Features**

- 5-stage pipelined RISC processor

- 32x32- to 64-bit hardware multiplier, signed and unsigned

- 32x32-bit hardware divider

- 32-bit single-cycle barrel shifter

- 32 input interrupts, individually configurable to be level or edge sensitive and used in one of two modes:

- Standard Mode all interrupts jump to the same, configurable base vector

- Vectored Mode providing 32 vectored priority interrupts, each jumping to a separate interrupt vector

- Internal Harvard architecture with simplified external memory access

- 4GByte address space

- Wishbone I/O and memory ports for simplified peripheral connection

- Full Viper-based software development tool chain C compiler/assembler/source-level debugger/profiler

- C-code compatible with other Altium Designer 8-bit and 32-bit Wishbone-compliant processor cores, for easy design migration

- FPGA device-independent implementation

## **Available Devices**

The TSK3000A device can be found in the FPGA Processors integrated library (\Program Files\Altium Designer 6\Library\Fpga\FPGA Processors.IntLib).

# **RISC Processor Background**

RISC, or Reduced Instruction Set Computer, is a term that is conventionally used to describe a type of microprocessor architecture that employs a small but highly-optimized set of instructions, rather than the large set of more specialized instructions often found in other types of architectures. This other type of processor is traditionally referred to as CISC, or Complex Instruction Set Computer.

## **History**

The early RISC processors came from research projects at Stanford and Berkeley universities in the late 1970s and early 1980s. These processors were designed with a similar philosophy, which has become known as RISC. The basic design architecture of all RISC processors has generally followed the characteristics that came from these early research projects and which can be summarized as follows:

- One instruction per clock cycle execution time: RISC processors have a CPI (clock per instruction) of one cycle. This is due to the optimization of each instruction on the CPU and a technique called pipelining. This technique allows each instruction to be processed in a set number of stages. This in turn allows for the simultaneous execution of a number of different instructions, each instruction being at a different stage in the pipeline.

- Load/Store machine with a large number of internal registers: The RISC design philosophy typically uses a large number (commonly 32) of registers. Most instructions operate on these registers, with access to memory made using a very limited set of Load and Store instructions. This limits the need for continuous access to slow memory for loading and storing data.

- Separate Data Memory and Instruction Memory access paths: Different stages of the pipeline perform simultaneous accesses to memory. This Harvard style of architecture can either be used with two completely different memory spaces, a single dual-port memory space or, more commonly, a single memory space with separate data and instruction caches for the two pipeline stages.

Over the last 20-25 years, RISC processors have been steadily improved and optimized. In one sense, the original simplicity of the RISC architecture has been lost – replaced by super-scalar, multiple-pipelined hardware, often running in the gigahertz range.

## "Soft" FPGA Processors

With the advent of low-cost, high-capacity programmable logic devices, there has been something of a resurgence in the use of processors with simple RISC architectures. Register-rich FPGAs, with their synchronous design requirements, have found the ideal match when paired with these simple pipelined processors.

As a result, most 32-bit FPGA soft processors are adopting this approach. They could even be considered as "Retro-processors".

## Why use "Soft" Processors?

There are a number of benefits to be gained from using soft processors on reconfigurable hardware. The following sections explore some of the more significant of these benefits in more detail.

### Field reconfigurable hardware

For certain specific applications, the ability to change the design once it is in the field can be a significant competitive advantage. Applications in general can benefit from this ability also. It allows commitment to shipping early in the development cycle. It also allows field testing to be used to help drive the latter part of the design cycle without requiring new "board-spins" based on the outcome. This is very similar to the way in which alpha, beta, pre-release and release cycles currently drive the closure of software products.

The ability to update embedded software in a device in the field has long been an advantage enjoyed by designers of embedded systems. With FPGAs, this has now become a reality for the hardware side of the design. For end-users, this translates as "Field Upgradeable Hardware".

### Faster time to market

FPGAs offer the fastest time to market due to their programmable nature. Design problems, or feature changes, can be made quickly and simply by changing the FPGA design – with no changes in the board-level design.

### Improving and extending product life-cycles

Fast time to market is usually synonymous with a weaker feature set – a traditional trade-off. With FPGA-based system designs you can have the best of both worlds. You can get your product to market quickly with a limited feature set, then follow-up with more extensive features over time, upgrading the product while it is already in the field.

This not only extends product life-cycles but also lowers the risk of entry, allowing new protocols to be added dynamically and hardware bugs to be fixed without product RMA.

### Creating application-specific coprocessors

Algorithms can easily be moved between hardware and software implementations. This allows the design to be initially implemented in software, later off-loading intensive tasks into dedicated hardware, in order to meet performance objectives. Again, this can happen even after commitment to the board-level design.

### Implementing multiple processors within a single device

Extra processors can be added within a single FPGA device, simply by modifying the design with which the device is programmed. Once again, this can be achieved after the board-level design has been finalized and a commitment to production made.

#### Lowering system cost

Processors, peripherals, memory and I/O interfaces can be integrated into a single FPGA device, greatly reducing system complexity and cost. Once the FPGA-based embedded application moves to 32-bit, cost becomes an even more powerful driver.

As large FPGAs become cheaper, both Hybrids and soft cores move into the same general cost area as dedicated processors. At the heart of this argument is also the idea that once you have paid for the FPGA, any extra IP that you place in the device is free functionality.

### Avoiding processor obsolescence

As products mature, processor supply may become an increasing problem, particularly where the processor is one of many variants supplied by the semiconductor vendor. Switching to a new processor usually requires design software changes or logical hardware changes.

With FPGA implementations, the design can be easily moved to a different device with little or no change to the hardware logic and probably no change to the application software. Peripherals are created dynamically in the hardware, so lack of availability of specific processor variants is never a problem.

## The TSK3000A

The TSK3000A is a 32-bit RISC machine that follows the classic RISC architecture previously described. It is a load/store machine with 32 general purpose registers.

Most instructions are 32-bits wide and execute in a single clock cycle.

In addition to fast register access the TSK3000A, relying on the commonly available fast block RAM in FPGA devices, also features a user-definable amount of zero-wait state block RAM, with true dual-port access.

## **Wishbone Bus Interfaces**

The TSK3000A has been built to use the Wishbone bus standard. This standard is formally described as a "System-on-Chip Interconnection Architecture for Portable IP Cores". The current standard is the *Revision B.3 Specification*, a copy of which is included as part of the software installation and can be found by navigating to the Documentation Library » Designing with FPGAs section of the **Knowledge Center** panel.

The Wishbone standard is not copyrighted and resides in the public domain. It may be freely copied and distributed by any means. Furthermore, it may be used for the design and production of integrated circuit components without royalties or other financial obligations. It is also implicitly device and vendor independent, making it very simple to create highly portable designs.

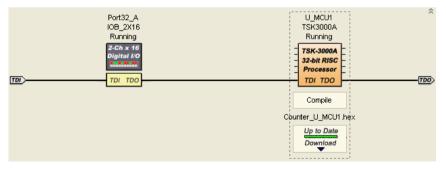

## Wishbone OpenBUS Processor Wrappers

To normalize access to hardware and peripherals, each of the 32-bit processors supported in Altium Designer has a Wishbone OpenBUS-based FPGA core that 'wraps' around the processor. This enables peripherals defined in the FPGA to be used transparently with any type of processor. An FPGA OpenBUS wrapper around discrete, hard-wired peripherals also allows them to be moved seamlessly between processors.

The OpenBUS wrappers can be implemented in any FPGA and allow the designer to implement FPGA-based portable cores, taking advantage of the device driver system in Altium Designer for both FPGA-based soft-core peripherals as well as connections to off-chip discrete peripherals and memory devices.

## **Processor Abstraction System**

Use of OpenBUS wrappers creates a plug-in processor abstraction system that normalizes the interface to interrupt systems and other hardware specific elements. The system provides an identical

interface to the processor's interrupt system, whether soft or hard-vectored. This allows different processors to be used transparently with identical source code bases.

## **Design Migration**

With each 32-bit processor encased in a Wishbone OpenBUS wrapper, an embedded software design can be seamlessly moved between soft-core processors, hybrid hard-core processors and discrete processors.

The Wishbone OpenBUS wrapper around the TSK3000A processor makes it architecturally similar to the other 32-bit processors included with Altium Designer, both in terms of its memory map and its pinout. This allows for easy migration from the TSK3000A to any of the following devices:

- **PPC405A** 'hard' PowerPC<sup>®</sup> 32-bit RISC processor immersed on the Xilinx<sup>®</sup> Virtex<sup>®</sup>-II Pro.

- Nios<sup>®</sup> II 32-bit RISC processor targeted to Altera FPGA platforms.

- MicroBlaze<sup>™</sup> 32-bit RISC processor targeted to Xilinx FPGA platforms.

- **PPC405CR** AMCC<sup>®</sup> PowerPC 32-bit RISC Microprocessor.

- ARM<sup>®</sup>720T\_LH79520 Sharp Bluestreak<sup>®</sup> LH79520 with built-in ARM720T (32-bit RISC microprocessor).

Altium Designer also features Wishbone-compliant versions of its TSK52x 8-bit processor. These Wishbone variants, along with true C-code compatibility between these and the Nios II, allow designs to be easily moved between the 8- and 32-bit worlds.

- For further information on the PPC405A, refer to the *PPC405A 32-bit RISC Processor* core reference.

- EF For further information on the Nios II, refer to the Nios II 32-bit RISC Processor core reference.

- For further information on the MicroBlaze, refer to the *MicroBlaze 32-bit RISC Processor* core reference.

- EF For further information on the TSK52x, refer to the TSK52x MCU core reference.

# **Architectural Overview**

## Symbol

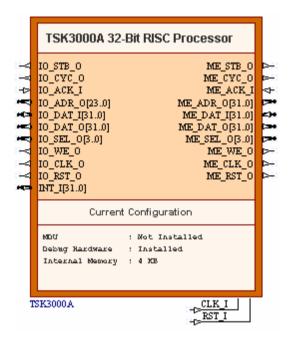

Figure 1. TSK3000A symbol

## **Pin Description**

The pinout of the TSK3000A has not been fixed to any specific device I/O - allowing flexibility with user application. The TSK3000A contains only unidirectional pins (inputs or outputs).

| Name  | Туре            | Polarity/Bus size | Description                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|-------|-----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|       | Control Signals |                   |                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |

| CLK_I | I               | Rise              | External (system) clock                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

| RST_I | I               | High              | External (system) reset                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

|       |                 | Inte              | errupt Signals                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

| INT_I | I               | 32                | Interrupt inputs. Each input can be configured to operate as level-sensitive or edge-triggered by clearing or setting the corresponding bit in the IMode register respectively. |  |  |  |  |  |  |  |  |  |  |  |

|       |                 |                   | Interrupts can be configured in one of two modes –<br>Standard or Vectored – determined by the VIE bit of<br>the Status register (Status.9)                                     |  |  |  |  |  |  |  |  |  |  |  |

| Name     | Туре            | Polarity/Bus size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|----------|-----------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|          | •               | Wishbone Externa  | al Memory Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| ME_STB_O | 0               | High              | Strobe signal. When asserted, indicates the start of a valid Wishbone data transfer cycle                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| ME_CYC_O | 0               | High              | Cycle signal. When asserted, indicates the start of a valid Wishbone bus cycle. This signal remains asserted until the end of the bus cycle, where such a cycle can include multiple data transfers                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| ME_ACK_I | I               | High              | Standard Wishbone device acknowledgement signal.<br>When this signal goes High, an external Wishbone<br>slave memory device has finished execution of the<br>requested action and the current bus cycle is<br>terminated                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| ME_ADR_O | 0               | 32                | Standard Wishbone address bus, used to select an<br>address in a connected Wishbone slave memory<br>device for writing to/reading from                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| ME_DAT_I | I               | 32                | Data received from an external Wishbone slave memory device                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| ME_DAT_O | 0               | 32                | Data to be sent to an external Wishbone slave memory device                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| ME_SEL_O | 0               | 4                 | Select output, used to determine where data is placed<br>on the ME_DAT_O line during a Write cycle and from<br>where on the ME_DAT_I line data is accessed during<br>a Read cycle. Each of the data ports is 32-bits wide<br>with 8-bit granularity, meaning data transfers can be<br>8-, 16- or 32-bit. The four select bits allow targeting of<br>each of the four active bytes of a port, with bit 0<br>corresponding to the low byte (70) and bit 3<br>corresponding to the high byte (3124) |  |  |  |  |  |  |

| ME_WE_O  | ME_WE_O O Level |                   | Write enable signal. Used to indicate whether the current local bus cycle is a Read or Write cycle.<br>0 = Read<br>1 = Write                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| ME_CLK_O | 0               | Rise              | External (system) clock signal (identical to CLK_I),<br>made available for connecting to the CLK_I input of a<br>slave memory device. Though not part of the standard<br>Wishbone interface, this signal is provided for<br>convenience when wiring your design                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Name     | Туре | Polarity/Bus size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|----------|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ME_RST_O | 0    | High              | Reset signal made available for connection to the<br>RST_l input of a slave memory device. This signal<br>goes High when an external reset is issued to the<br>processor on its RST_l pin. When this signal goes<br>Low, the reset cycle has completed and the processor<br>is active again. Though not part of the standard<br>Wishbone interface, this signal is provided for<br>convenience when wiring your design                                                                           |  |  |  |  |  |

|          |      | Wishbone Perip    | heral I/O Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| IO_STB_O | 0    | High              | Strobe signal. When asserted, indicates the start of a valid Wishbone data transfer cycle                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| IO_CYC_O | 0    | High              | Cycle signal. When asserted, indicates the start of a valid Wishbone bus cycle. This signal remains asserted until the end of the bus cycle, where such a cycle can include multiple data transfers                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| IO_ACK_I | I    | High              | Standard Wishbone device acknowledgement signal.<br>When this signal goes High, an external Wishbone<br>slave peripheral device has finished execution of the<br>requested action and the current bus cycle is<br>terminated                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| IO_ADR_O | 0    | 24                | Standard Wishbone address bus, used to select an<br>internal register of a connected Wishbone slave<br>peripheral device for writing to/reading from                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| IO_DAT_I | I    | 32                | Data received from an external Wishbone slave peripheral device                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| IO_DAT_O | 0    | 32                | Data to be sent to an external Wishbone slave peripheral device                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|          |      | 4                 | Select output, used to determine where data is placed<br>on the IO_DAT_O line during a Write cycle and from<br>where on the IO_DAT_I line data is accessed during a<br>Read cycle. Each of the data ports is 32-bits wide with<br>8-bit granularity, meaning data transfers can be 8-,<br>16- or 32-bit. The four select bits allow targeting of<br>each of the four active bytes of a port, with bit 0<br>corresponding to the low byte (70) and bit 3<br>corresponding to the high byte (3124) |  |  |  |  |  |

| IO_WE_O  | 0    | Level             | Write enable signal. Used to indicate whether the current local bus cycle is a Read or Write cycle.<br>0 = Read<br>1 = Write                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Name     | Туре | Polarity/Bus size | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO_CLK_O |      |                   | External (system) clock signal (identical to CLK_I),<br>made available for connecting to the CLK_I input of a<br>slave peripheral device. Though not part of the<br>standard Wishbone interface, this signal is provided<br>for convenience when wiring your design                                                                                                                                                        |

| IO_RST_O | 0    | High              | Reset signal made available for connection to the<br>RST_I input of a slave peripheral device. This signal<br>goes High when an external reset is issued to the<br>processor on its RST_I pin. When this signal goes<br>Low, the reset cycle has completed and the processor<br>is active again. Though not part of the standard<br>Wishbone interface, this signal is provided for<br>convenience when wiring your design |

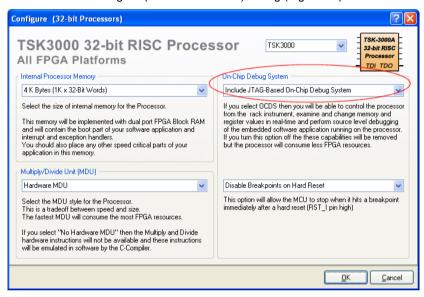

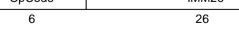

## **Configuring the Processor from the Schematic Design**

The architecture of the TSK3000A can be configured after placement on the schematic sheet. Simply right-click and choose the command to configure the processor from the pop-up menu that appears (e.g. **Configure U\_MCU1 (TSK3000A)** for a processor with designator U\_MCU1). Alternatively, click on the **Configure** button, available in the *Component Properties* dialog for the processor.

The Configure (32-bit Processors) dialog will appear as shown in Figure 2.

| Configure (32-bit Processors)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ? 🛛                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Processor Memory         ▲ K. Bytes (1K × 32-Bit Words)         Select the size of internal memory for the Processor.         This memory will be implemented with dual port FPGA Block RAM and will contain the boot port of your software application and interrupt and exception handlers.         You should also place any other speed critical parts of your application in this memory.         Multiply/Divide Unit (MDU)         Hardware MDU         Select the MDU style for the Processor.         This is a tradeoff between speed and size.         The fastest MDU will consume the most FPGA resources.         If you select "No Hardware MDU" then the Multiply and Divide hardware instructions will be emulated in software by the C-Compiler. | TSK3000         SOT         TSK3000         32-bit RISC<br>Processor<br>TD TDD         On-Chip Debug System         Include JTAG-Based On-Chip Debug System         If you select OCDS then you will be able to control the processor<br>from the rack instrument, examine and change memory and<br>register values in real-time and perform source level debugging<br>of the embedded software application running on the processor.<br>If you turn this option off the these capabilities will be removed<br>but the processor will consume less FPGA resources.         Disable Breakpoints on Hard Reset       ✓         This option will allow the MCU to stop when it hits a breakpoint<br>immediately after a hard reset (RST_l pin high) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <u>D</u> K <u>C</u> ancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Figure 2. Options to configure the architecture of the TSK3000A

The drop-down field at the top-right of the dialog enables you to choose the type of processor you want to work with. As the pinouts between the 32-bit processors are essentially the same, you can easily change the processor used in your design without having to extensively rewire the external interfaces.

As you select the processor type, the *Configure (32-bit Processors)* dialog will change accordingly to reflect the architectural options available. The symbol on the schematic will also change to reflect the type of processor and configuration options chosen.

The following sections explore each of the regions in the dialog, providing configurable options specific to the TSK3000A processor.

### **Internal Processor Memory**

This region of the dialog allows you to define the size of the internal memory for the processor. This memory, also referred to as 'Low' or 'Boot' memory is implemented using true dual port FPGA Block RAM and will contain the boot part of a software application and the interrupt and exception handlers.

Speed-critical (or latency-sensitive) parts of an application should also be placed in this memory space.

The following memory sizes are available to choose from:

- 1KB (256 x 32-bit Words)

- 2KB (512 x 32-bit Words)

- 4KB (1K x 32-bit Words)

- 8KB (2K x 32-bit Words)

- 16KB (4K x 32-bit Words)

- 32KB (8K x 32-bit Words)

- 64KB (16K x 32-bit Words)

- 128KB (32K x 32-bit Words)

- 256KB (64K x 32-bit Words)

- 512KB (128K x 32-bit Words)

- 1MB (256K x 32-bit Words).

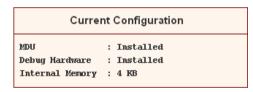

Your configuration choice will be reflected in the **Current Configuration** region of the processor's schematic symbol (Figure 3).

Figure 3. Current configuration settings for the processor.

## Multiply/Divide Unit (MDU)

This region of the dialog allows you to define whether the processor should incorporate an MDU or not. Either choose to include an MDU in the architecture by selecting the <code>Hardware MDU</code> option, or leave the MDU out of the architecture by choosing <code>No MDU Hardware</code>.

With no MDU included in the architecture, the multiply (MULT, MULTU) and divide (DIV, DIVU) hardware instructions will not be available and these instructions will be emulated in software by the C Compiler.

Your configuration choice will be reflected in the **Current Configuration** region of the processor's schematic symbol (Figure 3).

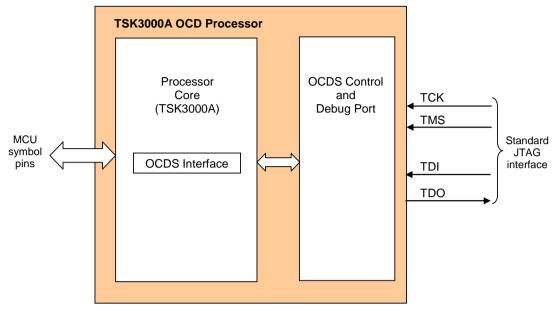

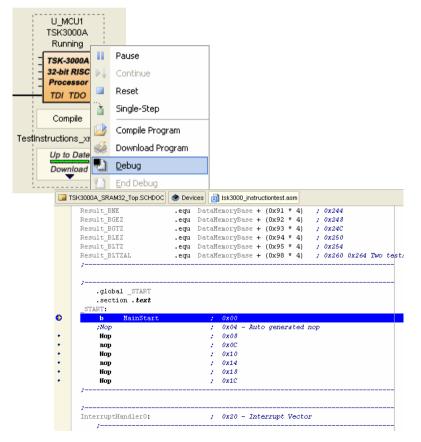

## **On-Chip Debug System**

This region of the dialog allows you to add an On-Chip Debug System (OCDS) unit to the processor's architecture, allowing you to:

- control the processor from its associated instrument panel, which can be added to the Instrument Rack – Soft Devices panel

- interrogate and modify memory and register values in real-time

- perform source level debugging of the embedded software application running on the processor.

- Simply ensure that the option is set to Include JTAG-Based On-Chip Debug System.

- For further information with respect to real-time debugging of the processor, refer to the *On-Chip Debugging* section of this reference.

By specifying No On-Chip Debug System for the processor, the above capabilities will be removed, but the processor will naturally consume less FPGA resources.

Again, your configuration choice will be reflected in the **Current Configuration** region of the processor's schematic symbol (Figure 3).

### **Breakpoints on Reset**

This region of the dialog allows you to specify whether debugging of the processor from a Hard Reset is enabled or not. If you choose the option to Enable Breakpoints on Hard Reset, then the processor will stop upon encountering a breakpoint immediately after an external reset is received on its RST\_I input pin.

# Memory & I/O Management

The TSK3000A uses 32-bit address buses providing a 4GByte linear address space. All memory access is in 32-bit words, which creates a physical address bus of 30-bits.

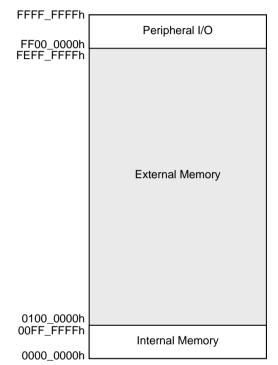

Memory space is broken into three main areas, as illustrated in Figure 4 and described in the section – *Division of Memory Space*.

Before detailing the nature of each of these memory regions, it is worthwhile discussing the difficulties with mapping devices into this memory, and the solution that Altium Designer brings to the problem.

## **Defining the Memory Map**

An area that can be difficult to manage in an embedded software development project is the mapping of memory and peripherals into the processor's address space.

The memory map, as it is often called, is essentially the bridge between the hardware and software projects – the hardware team allocating each of the various memory and peripheral devices their own chunk of the processor's address space, the software team then writing their code to access the memory and peripherals at the given locations.

To help manage the process of allocating devices into the space there are a number of features available to both the hardware designer and the embedded software developer in Altium Designer.

Figure 4. Memory organization in the TSK3000A

This discussion is based around the TSK3000A processor, however the overall approach can be applied to any of the 32-bit processors available in Altium Designer.

### Building the Bridge Between the Hardware and Software

Defining the memory map on the hardware (FPGA project) side is essentially a 3 stage process:

- Place the peripheral or memory

- Define its addressing requirements (this is most easily done using a Wishbone Interconnect device)

- Bring that definition into the processor's configuration, which can then be accessed by the embedded tools

Figure 5 shows an example of the addressable memory and IO space for the TSK3000A, with a number of memory and peripheral devices mapped into it.

|             | OxFFFF_FFFF                         | OxFFFF_FFF                        |                |

|-------------|-------------------------------------|-----------------------------------|----------------|

| OxFFFF_FFFF | Processor I/O Space                 | MOUSE<br>U2                       | 0xFF60_0001    |

| 0xFF00_0000 | of the processor                    | 02                                | 0xFF60_0000    |

| OxFEFF_FFFF |                                     |                                   | 0xFF50_0003    |

|             |                                     | SPI<br>U2                         | 0xFF50_0000    |

|             |                                     |                                   |                |

|             |                                     | 12C<br>U2                         | 0xFF40_0007    |

|             |                                     |                                   | 0xFF40_0000    |

|             |                                     | EMAC<br>U2                        | 0xFF30_001F    |

|             |                                     |                                   | 0xFF30_0000    |

|             |                                     | VGA<br>U2                         | 0xFF20_0FFF    |

|             |                                     |                                   | 0xFF20_0000    |

|             |                                     | VIDED<br>U2                       | 0xFF10_0007    |

|             |                                     | 52                                | 0xFF10_0000    |

|             |                                     |                                   | 0xFF00_0000    |

|             |                                     | 10<br>U2                          | 0xFF00_0000    |

|             | External-Memory Space               |                                   | 0x041F_FFFF    |

|             |                                     | NANOBOARD_RAM (Volatile RAM<br>U4 | 4) 0x0400_0000 |

|             |                                     | EMAC_RAM (Volatile RAM)<br>U4     | 0x0200_7FFF    |

|             |                                     |                                   | 0x0200_0000    |

|             |                                     | VIDEO_RAM (Volatile RAM)<br>U4    | 0x011F_FFFF    |

| 0x0100_0000 |                                     |                                   | 0x0100_0000    |

| 0x00FF_FFFF | <b>Internal-Memory</b><br>Where the | U3 (ROM)                          | 0x0000_3FFF    |

| 0x0000_0000 | boot code resides                   |                                   | 0x0000_0000    |

Figure 5. The TSK3000A's  $2^{32}$  addressable space (left) and the current set of memory and peripheral devices that have been mapped into it (right)

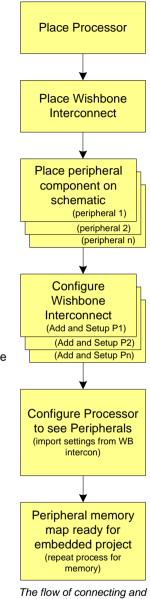

The adjacent flow chart shows the process that was followed to build this memory map in the FPGA project. This flow chart is only a guide, during the course of development it is likely that you will jump back and forth through this process as you build up the design.

## **Dedicated System Interconnect Components**

This process of being able to quickly build up the design and resolve the processor to memory & peripheral interface is possible because of the specialized interconnection components, including the **Wishbone Interconnect**, the **Wishbone Dual Master** and the **Wishbone Multi-Master**.

These three components solve the common system interconnect issues that face the designer, these being:

- Interfacing multiple peripheral and memory blocks to a processor (handled by the Wishbone Interconnect component)

- Allowing two or more system components, that must each be able to control the bus, to share access to a common resource (provided by the Wishbone Dual Master or Wishbone Multi-Master components).

Use of the Wishbone Interconnection Architecture for all part s of the system that connect to the processor contributes to the system's 'building block' behavior. The Wishbone standard resolves data exchange between system components – supporting popular data transfer bus protocols, while defining clocking, handshaking and decoding requirements (amongst others).

With the lower-level physical interface requirements being resolved by the Wishbone interface, the other challenge is the structural aspects of the system – defining where components sit in the address space, providing address decoding, and allocating and interfacing interrupts to the processor.

- For more information on the Wishbone Interconnect component, refer to the *WB\_INTERCON Configurable Wishbone Interconnect* core reference.

- For more information on the Wishbone Dual Master component, refer to the WB\_DUALMASTER Configurable Wishbone Dual Master core reference.

- For more information on the Wishbone Multi-Master component, refer to the WB\_MULTIMASTER Configurable Wishbone Multi-Master core reference.

## **Configurable Interconnect Components**

Structuring the system is greatly simplified by the configurable nature of these system interconnect components. When you initially place a Wishbone Interconnect it has a single slave interface defined by default, as shown in Figure 6.

The flow of connecting and mapping the peripherals (or memory) to the processor

Configuring the device is done by right-clicking on the component symbol and selecting **Configure** from the context menu. In the Interconnect's *Configure (Wishbone Intercon)* dialog you can add in peripherals or memory, and define their addressing, data and interrupt requirements. Once this is done the component symbol will actually change, to reflect the configuration requirements you just defined.

As you configure the interconnect to cater for further peripherals, the symbol will grow to accommodate additional Wishbone Slave interfaces for those peripherals.

|             | U?                      |        |     |  |  |  |  |  |  |  |  |  |  |

|-------------|-------------------------|--------|-----|--|--|--|--|--|--|--|--|--|--|

|             | Wishbone Interconnect   |        |     |  |  |  |  |  |  |  |  |  |  |

|             | s0_STB_O m0;            | STB_I  | 4   |  |  |  |  |  |  |  |  |  |  |

|             |                         |        | 4   |  |  |  |  |  |  |  |  |  |  |

|             | s0_ACK_I m0_A           | CK_0   | p÷  |  |  |  |  |  |  |  |  |  |  |

| 100         | s0_ADR_0[20.0] m0_ADR_I | 31.0]  | -   |  |  |  |  |  |  |  |  |  |  |

| <b>H</b> (3 | s0_DAT_I[31.0] m0_DAT_0 | 31.0]  |     |  |  |  |  |  |  |  |  |  |  |

| 100         | s0_DAT_0[31.0] m0_DAT_1 | 31.0]  | -7  |  |  |  |  |  |  |  |  |  |  |

| 1           | s0_SEL_0[3.0] m0_SEL_   | I[3.0] | - 1 |  |  |  |  |  |  |  |  |  |  |

| 1-4         | s0_WE_0 m0_             | WE_I   | ⇒+  |  |  |  |  |  |  |  |  |  |  |

|             | s0_CLK_O m0_0           | LK_I   | 4   |  |  |  |  |  |  |  |  |  |  |

|             | s0_RST_0 m0_)           | RST_I  | ⊲-  |  |  |  |  |  |  |  |  |  |  |

|             |                         |        |     |  |  |  |  |  |  |  |  |  |  |

| 1           | WB_INTERCON             |        |     |  |  |  |  |  |  |  |  |  |  |

Figure 6. An interconnect which has not been configured for any memory or peripherals.

For more information, refer to the *WB\_INTERCON Configurable Wishbone Interconnect* core reference.

| U                        | 13                                                                                                                                                                                                                                                                                                                                                              | _    |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                          | Wishbone Interconnect                                                                                                                                                                                                                                                                                                                                           |      |

| <b>A &amp; A</b> & A A A | s0_STB_0         m0_STB_0           s0_CYC_0         m0_CYC_0           s0_ACK_I         m0_ACK_0           s0_ADR_0[1.0]         m0_DAT_0[31.0]           s0_DAT_0[31.0]         m0_DAT_0[31.0]           s0_SEL_0[31.0]         m0_SEL_1[32.0]           s0_SEL_0[30.0]         m0_WE_0           s0_WE_0         m0_WE_1           s0_RST_0         m0_RST_0 | 4744 |

|                          | m0_INT_0[31.0]                                                                                                                                                                                                                                                                                                                                                  | 1444 |

|                          | s1_STB_0<br>s1_CYC_0<br>s1_ACK_I<br>s1_ACR_0[6.0]<br>s1_DAT_U[15.0]<br>s1_DAT_0[15.0]<br>s1_SEL_0[3.0]<br>s1_WE_0<br>s1_CLK_0<br>s1_RST_0                                                                                                                                                                                                                       |      |

|                          | Spare_INT_I[31.0]<br>JB_INTERCON                                                                                                                                                                                                                                                                                                                                |      |

Figure 7. An interconnect configured for two peripherals.

## **Configuring the Processor**

Each configurable component has its own configuration dialog, including the different processors. The processor has separate commands and dialogs to configure memory and peripherals, but it does support mapping peripherals into memory space (and the memory into peripheral space), if required.

An important feature to point out is the **Import from Schematic** button in the processor's *Configure* dialogs, clicking this will read in the settings from the Interconnects attached to the processor. This lets

you quickly build the memory map, as shown in the figure earlier. You now have the memory map defined in the hardware, this data is stored with the processor component.

The processor's *Configure* dialogs includes options to generate assembler and C hardware description files that can be included in your embedded project, simplifying the task of declaring peripheral and memory structures in your embedded code. You can also 'pull' the memory map configurations directly into the embedded project by enabling the **Automatically import when compiling FPGA project** option in the **Configure Memory** tab of the *Options for Embedded Project* dialog.

For more information on mapping physical memory devices and I/O peripherals into the processor's address space, refer to the application note *Allocating Address Space in a 32-bit Processor*.

## **Division of Memory Space**

As illustrated previously (Figure 4), the TSK3000A'S 4GB address space is divided into three distinct areas (or ranges). These areas are detailed in the following sections.

### **Internal Memory**

The internal "Low" or "Boot" RAM is contained within the processor core and is built using true dualport FPGA block RAM memory. As such, it can be read or written on both sides, simultaneously, in a single cycle.

This memory still has the standard limitation of load delay slots, because the load from memory happens further down the pipeline, after the Execute stage. As a result, any operation that requires loaded data in the cycle immediately after the load will cause the processor to insert a load stall, holding the first half of the pipeline for one cycle while the data becomes available.

Other than this single limitation, the RAM block is as fast as the internal processor registers themselves.

The size of the RAM can vary between 1KB and 16MB, dependent on the availability of embedded block RAM in the physical FPGA device used. Memory size is configured in the **Internal Processor Memory** region of the *Configure (32-bit Processors)* dialog (see the *Internal Processor Memory* section).

Covering the processor's address space between 0000\_0000h and 00FF\_FFFFh, it will contain the reset and interrupt vectors, as well as any speed or latency-sensitive code or data.

## **External Memory**

The processor's Wishbone External Memory Interface is used by both the instruction and data sides of the processor and provides access to the majority of the address space of the processor. It covers the address space between  $0100_0000h$  and FF00\_0000h – 1.

There are no caches on external memory.

#### **External Memory Interface Time-out**

A simple time-out mechanism for the interface handles the case when attempting to access an address that does not exist, or if the addressed target slave device is not operating correctly. This mechanism ensures that the processor will not be 'locked' indefinitely, waiting for an acknowledgement on its ME\_ACK\_I input.

After the ME\_STB\_O output is taken High, the processor will wait 4096 cycles of the external clock signal (CLK\_I) for an acknowledge signal to appear from the addressed slave memory device, before forcibly terminating the current data transfer cycle.

If a time-out occurs, the ACK bit of the Status register (Status.10) will be taken High. This can be cleared to zero under software control to allow for detection of further Wishbone time-outs.

The ACK\_O signal from a slave device should not be used as a 'long delay' hand-shaking mechanism. Where such a mechanism needs to be implemented, either use polling or interrupts.

## **Peripheral I/O**

The processor's Wishbone Peripheral I/O Interface is a one-way Wishbone Master, handling I/O in a very similar way to external memory. The port can be used to communicate with any Wishbone Slave peripheral device and covers the address space between FF00\_0000h and FFFF\_FFFh. This address space of 16MB allows a physical address bus size of 24 bits.

#### Peripheral I/O Interface Time-outs

A simple time-out mechanism for the interface handles the case when attempting to access an address that does not exist, or if the addressed target slave device is not operating correctly. This mechanism ensures that the processor will not be 'locked' indefinitely, waiting for an acknowledgement on its IO\_ACK\_I input.

After the IO\_STB\_O output is taken High, the processor will wait 4096 cycles of the external clock signal (CLK\_I) for an acknowledge signal to appear from the addressed slave peripheral device, before forcibly terminating the current data transfer cycle.

If a time-out occurs, the ACK bit of the Status register (Status.10) will be taken High. This can be cleared to zero under software control to allow for detection of further Wishbone time-outs.

The ACK\_O signal from a slave peripheral should not be used as a 'long delay' hand-shaking mechanism. Where such a mechanism needs to be implemented, either use polling or interrupts.

For more information on connection of slave physical memory and peripheral I/O devices to the processor's Wishbone interfaces, refer to the application note *Connecting Memory and Peripheral Devices to a 32-bit Processor*.

## **Data Organization**

Data organization refers to the ordering of the data during transfers. There are two general types of ordering:

- BIG ENDIAN the most significant portion of an operand is stored at the lower address

- LITTLE ENDIAN the most significant portion of an operand is stored at the higher address.

Although the Wishbone specification supports both of these methods for ordering data, the TSK3000A is always BIG ENDIAN.

## Words, Half-Words and Bytes

The TSK3000A operates on the following data sizes:

- 32-bit words

- 16-bit half-words

- 8-bit bytes.

There are dedicated load and store instructions for these three data types.

Figure 8 shows how these different sizes of data are organized relative to each other over an 8-byte memory range in the TSK3000A.

| Word-0 |    |    |    |    |   |   |   |    |    |    | Word | -1 |   |   |   |

|--------|----|----|----|----|---|---|---|----|----|----|------|----|---|---|---|

| 31     | 24 | 23 | 16 | 15 | 8 | 7 | 0 | 31 | 24 | 23 | 16   | 15 | 8 | 7 | 0 |

|    |   | На | lf-1 |    | Half-2 |   |   |    | Half-3 |   |   |    |   |   |   |

|----|---|----|------|----|--------|---|---|----|--------|---|---|----|---|---|---|

| 15 | 8 | 7  | 0    | 15 | 8      | 7 | 0 | 15 | 8      | 7 | 0 | 15 | 8 | 7 | 0 |

|   | Byte-0 Byte-1 |   | Byte-2 |   | Byte-3 |   | Byte-4 |   | Byte-5 |   | Byte-6 |   | Byte-7 |   |   |

|---|---------------|---|--------|---|--------|---|--------|---|--------|---|--------|---|--------|---|---|

| - | 7 0           | 7 | 0      | 7 | 0      | 7 | 0      | 7 | 0      | 7 | 0      | 7 | 0      | 7 | 0 |

Figure 8. Organization of data types for the TSK3000A

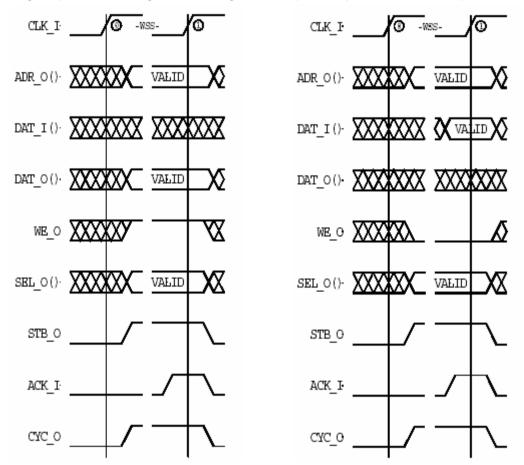

### **Physical Interface to Memory and Peripherals**

The TSK3000A's physical interface to the outside world is always 32 bits wide. Since the addressing has a byte-level resolution, this means that up to four "packets" of data (bytes) can be loaded or stored during a single memory access. To accommodate this requirement all memory accesses (8-bit, 16-bit and 32-bit) are handled in a specific way.

Each 32-bit read and write can be considered as a read or write through four "byte-lanes". These bytelanes are marked as valid by the corresponding bits in the SEL\_O[3..0] signal of the relevant Wishbone interface (External Memory or Peripheral I/O). Each of these bits will be High if the byte data in that lane is valid. This allows a single byte to be written to 32-bit wide memory without needing to use a slower read-modify-write cycle.

The instructions of the TSK3000A require that all 32-bit load/store operations be aligned on 4-byte boundaries and all 16-bit load/store operations be aligned on 2-byte boundaries. Byte operations (8-bit) can be to any address.

To complete a byte load or store, the TSK3000A will position the byte data in the correct byte-lane and set the SEL\_O signal for that lane High. The memory hardware must then only enable writing on the relevant 8-bits of data from the 32-bit word.

When reading, the TSK3000A will put the relevant 8- or 16-bit value into the LSB's of the 32-bit word. What happens with the remaining bits depends on the operation:

- for an unsigned read, the processor will pad-out the remaining 24 or 16 bits respectively with zeroes

- for a byte load/store, the processor will sign-extend from bit 8

- for a half-word load/store, the processor will sign-extend from bit 16.

## **Peripheral I/O**

For memory I/O the process described happens transparently, because memory devices are always seen by the processor as 32 bits wide. Even when connecting to small 8- or 16-bit physical memories, the interfacing Memory Controller device will, as far as the processor is concerned, make the memory look like it is 32 bits wide.

For peripheral devices, the process is not so simple. 32-bit wide peripheral devices behave like memory devices, although they may or may not support individual byte-lanes. These devices should therefore be accessed using the 32-bit LW and SW instructions. For C-code, this means declaring the interface to the device as 32 bits wide, for example:

#define Port32 (\*(volatile unsigned int\*) Port32\_Address)

This will result in the software using LW and SW instructions to access the device.

If the 32-bit peripheral does support byte-lanes (i.e. it has a SEL\_I[3..0] input), then smaller accesses can be performed using the 8-bit LBU and SB or 16-bit LHU and SH instructions.

For smaller devices, there needs to be translation of the 8- or 16-bit values into the relevant byte-lanes in the processor. This is automatically handled by the Wishbone Interconnect device if it is used to access slave peripheral I/O devices. There is, however, some hardware penalty for this since it requires an extra 4:1 8-bit multiplexer for 8-bit devices or a 2:1 16-bit multiplexer for 16-bit devices.

16-bit peripheral devices should be accessed using the 16-bit LHU and SH instructions. For C-code, this means declaring the interface to the device as 16 bits wide, for example:

#define Port16 (\*(volatile unsigned short\*) Port16\_Address)

This will result in the software using LHU and SH instructions to access the device.

8-bit peripheral devices should be accessed using the 8-bit LBU and SB instructions. For C-code, this means declaring the interface to the device as 8 bits wide, for example:

#define Port8 (\*(volatile unsigned char\*) Port8\_Address)

This will result in the software using LBU and SB instructions to access the device.

There are some trade-offs that may need to be considered when deciding whether to use 8-, 16- or 32bit wide devices. It may require significantly less hardware to implement a single 32-bit wide I/O port than it would to implement four separate 8-bit ports. If however, the natural format of the data packets is 8-bits and hardware size is not a constraint, then it may be better to use 8-bit ports since there will be no need to use software to break up a 32-bit value into smaller components.

If you are only accessing 8-bits at any one time, then software may also execute faster when using 8bit wide peripherals, since there is need for extra instructions to extract the 8-bit values from the 32-bit values.

# **Hardware Description**

## **Block Diagram**

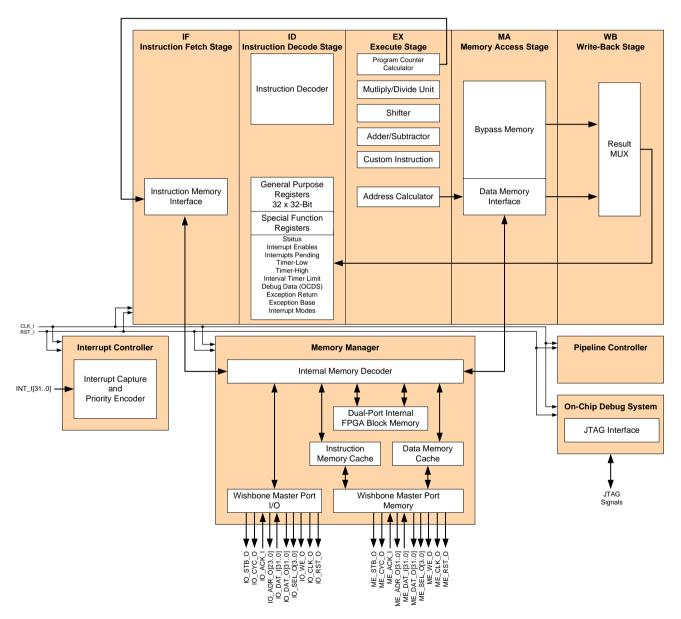

Figure 9 shows the hardware block diagram for the TSK3000A.

Figure 9. TSK3000A block diagram

## **Pipeline**

## **Pipeline Architecture**

The TSK3000A uses a 5-stage execution pipeline structure. The execution of a single instruction is therefore performed in five different stages, as summarized in Figure 10 and detailed in the sections that follow.

| Instru | uction Fetch | Instruction Decode | Execute | Memory Access | Write Back |

|--------|--------------|--------------------|---------|---------------|------------|

|        | IF           | ID                 | EX      | MA            | WB         |

Figure 10. Structure of the 5-stage execution pipeline

#### Instruction Fetch Stage (IF)

In this stage, the content of the Program Counter is used to access memory and fetch the next instruction to be executed.

#### Instruction Decode Stage (ID)

During this stage, the instruction is decoded and the required operands are retrieved from the general purpose registers (GPRs) or special function registers (SFRs).

#### **Execute Stage (EX)**

Any calculations are performed during this stage. This includes effective address calculation for Load or Store instructions. The next Program Counter value is also calculated during this stage of the pipeline so that branches, where applicable, can be executed.

Some initial pre-calculation for memory decoding is also performed in this stage.

#### Memory Access Stage (MA)

If the instruction being executed is of the Load or Store variety, then the data memory is accessed during this stage. The previously calculated effective address is applied to the data memory and the read or write is performed in accordance with the instruction type.

#### Write Back Stage (WB)

During this stage, the results of the calculation from the Execute stage, or the memory load from the Memory Access stage, are updated into the general purpose registers or special function registers.

#### Simultaneous Instruction Execution

The technique of pipelining allows for the simultaneous execution of a number of different instructions, each instruction being at a different stage in the pipeline. For the TSK3000A, up to five different instructions can be executed simultaneously in the processor's pipeline, as illustrated in Figure 11.

|         |    |    |    |    | Current<br>Instruction |    |    |    |    |

|---------|----|----|----|----|------------------------|----|----|----|----|

| Cycle 1 | IF | ID | EX | MA | WB                     |    |    |    |    |

| Cycle 2 |    | IF | ID | EX | MA                     | WB |    |    |    |

| Cycle 3 |    |    | IF | ID | EX                     | MA | WB |    |    |

| Cycle 4 |    |    |    | IF | ID                     | EX | MA | WB |    |

| Cycle 5 |    |    |    |    | IF                     | ID | EX | MA | WB |

|         |    |    |    |    |                        |    |    |    |    |

Figure 11. Achieving the simultaneous execution of 5 instructions per clock cycle

### **Pipeline Hazards**

With a pipelined processor such as the TSK3000A, there are a number of events that can disrupt the pipeline, lowering its overall instruction execution rate.

#### **Data Forwarding Hazards**

If an instruction in the Execute stage requires the result of a previous instruction as one of its operands, and that instruction is still in the pipeline, then the instruction cannot complete until the prior instruction has completed the pipeline.

To avoid stalling the pipeline in this case, the TSK3000A "forwards" the data from the prior instruction, making it immediately available to the current instruction in the Execute stage. This process happens transparently to the application software.

#### Long Instruction Hazards

Some instructions, notably multiply and divides, require more than one cycle to execute. In these cases the pipeline will be stalled while the instruction completes.

#### Load Hazards

If the instruction in the Execute stage requires the result of a Load instruction that is in the Memory Access stage, then that data will not be available since it has not been loaded from memory yet. In this case the processor will stall the first half of the pipeline and let the memory access complete, effectively inserting a NOP instruction into the instruction flow. Again, this will be transparent to the application software.

#### **Branch Hazards**

When the processor encounters a branch or jump in the Execute stage and decides to take the branch, then the instructions in the IF and ID stages will no longer be valid since execution will continue from a different location.

In this case, on the next rising clock edge (the beginning of the next clock cycle) as the new Program Counter value is loaded, the processor will kill the instruction that is being loaded from the instruction memory, effectively converting it into a NOP. The instruction that was in the ID stage will move into the EX stage and be executed. This instruction is said to be in the 'branch delay slot'.

Any instruction that follows a Branch or Jump instruction will be executed before the first instruction at the new address. This technique allows the processor to only lose one cycle when taking a branch. Optimizing compilers will attempt to fill the branch delay slots with useful instructions, increasing the overall throughput of the processor.

## **General Purpose Registers**

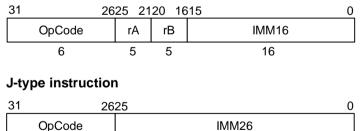

The TSK3000A has a bank of 32 x 32-bit general purpose registers (GPRs). These registers can be accessed by the R-Type instructions.

The register bank can perform two simultaneous reads and one write, from three different addresses within the bank.

The first register in the bank, R0 at index zero, can be used as the destination register in assembly instructions but will always return a zero value (even after a write).

The last register in the bank, R31 at index 31, is used by hardware as the Return Address register. This is the register in which the various "Branch and Link" and "Jump and Link" instructions store their return address. The return is accomplished using a jr \$31 instruction.

On power-on, the GPR bank of registers are all initialized to 0000\_0000h. After a subsequent reset, the values in the registers do not change.

### **Conventional Usage of General Purpose Registers**

In addition to the registers that are used directly by the hardware (R0 and R31), there are a number of registers that are used for special purpose by convention.

For assembler code, R1 is used by the Assembler to implement macro instructions when it needs to create an intermediate result. Assignment to this register using generic assembly instructions will result in warnings being generated by the Assembler, only if it uses this register during one or more machine instructions required to implement the generic instruction.

For C-code, there are also a number of registers in the GPR bank that have conventional usage. Table 2 lists the General Purpose Registers for the processor, identifying and summarizing the conventional usage of each.

| Register  | Name                           | Description                                                                                                                           |

|-----------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| \$0       |                                | Always returns a zero value                                                                                                           |

| \$1       | at                             | Assembler Temporary register – used for intermediate macro instruction results                                                        |

| \$2-\$3   | \$v0 - \$v1                    | Used for expression evaluations and to hold the integer and pointer type function return values                                       |

| \$4-\$7   | \$a0 - \$a3                    | Used for passing arguments to functions; values are not preserved across function calls. Additional arguments are passed on the stack |

| \$8-\$15  | \$t0 - \$t7                    | Temporary registers used for expression evaluation; values are not preserved across function calls                                    |

| \$16-\$23 | \$s0 - \$s7                    | Saved registers; values are preserved across function calls                                                                           |

| \$24-\$25 | \$t8 - \$t9                    | Temporary registers used for expression evaluation; values are not preserved across function calls                                    |

| \$26-\$27 | \$kt0 - \$kt1<br>(\$k0 - \$k1) | Used by the operating system. \$kt0 is also used by the Compiler in interrupt handling routines                                       |

| \$28      | \$gp                           | Global pointer and context pointer                                                                                                    |

| \$29      | \$sp                           | Stack pointer                                                                                                                         |

| \$30      | \$s8 (or \$fp)                 | Saved register (like \$s0 - \$s7) (or frame pointer)                                                                                  |

| \$31      | \$ra                           | Return Address register - used by Branch and Link and Jump and Link instructions to store their return address                        |

Table 2. Conventional usage of General Purpose Registers

## **Special Function Registers**

Special Function Registers (SFRs) in the TSK3000A are implemented as COP0 registers (Coprocessor 0). They can be read and written (where possible) in a single instruction cycle using the MFC0 and MTC0 instructions, respectively.

Table 3 summarizes the special function registers for the TSK3000A.

| Register                             | Name     | Description                                                                                                                  | Read | Write | Index |

|--------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|

| Control/Status                       | Status   | Individual Control and Status bits                                                                                           | Yes  | Yes   | \$0   |

| Interrupt Enable                     | IEnable  | Enable/Disable individual interrupts                                                                                         | Yes  | Yes   | \$1   |

| Interrupts Pending                   | IPending | View of the interrupt values after<br>individual enable gating (i.e.<br>interrupts that are pending or yet to<br>be handled) | Yes  | Yes   | \$2   |

| Time Base Low                        | TBLO     | Least significant 32-bits of the 64-bit time base                                                                            | Yes  | No    | \$3   |

| Time Base High                       | ТВНІ     | Most significant 32-bits of the 64-bit time base                                                                             | Yes  | No    | \$4   |

| Programmable<br>Interval Timer Limit | PIT      | Interval length (in clock cycles) of the interval timer                                                                      | Yes  | Yes   | \$5   |

| Debug Data                           | Debug    | Register for OCDS to exchange data with the processor                                                                        | Yes  | Yes   | \$6   |

| Exception Return                     | ER       | Register in which to store the return address for interrupts and exceptions                                                  | Yes  | Yes   | \$7   |

| Exception Base                       | EB       | Specifies base address for the interrupt vector table                                                                        | Yes  | Yes   | \$8   |

| Interrupt Mode                       | IMode    | Configures interrupt input pins to<br>operate as either level-sensitive or<br>edge-triggered                                 | Yes  | Yes   | \$9   |

Table 3. TSK3000A special function registers (SFRs)

### **Control/Status register (Status)**

This 32-bit register (COP0-\$0) is used to control aspects of the processor's operation and to determine the current state of the processor. Only bits 0..15 are currently used. All other bits are reserved for future use.

After a reset, this register is initialized to 0000\_0000h.

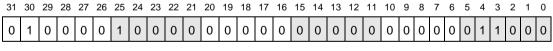

Table 4. The Status register

MSB LSB 31 2 0 16 15 14 13 12 11 10 9 8 7 6 5 4 3 1 ACK VIE ITE ITR 0 UMo IEo UMp IEp Interrupt Priority UMc IEc -