**Preliminary User's Manual**

# V30MZ<sup>™</sup>

## **16-Bit Microprocessor Core**

Hardware

Document No. A13761EJ1V0UM00 (1st edition) Date Published December 1998 N CP(K)

© NEC Corporation 1998 Printed in Japan [MEMO]

#### **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

## **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### NEC Electronics Inc. (U.S.) Santa Clara, California

Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### NEC Electronics (UK) Ltd.

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

NEC Electronics (France) S.A. Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### NEC Electronics (France) S.A. Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

NEC Electronics (Germany) GmbH Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore 1130 Tel: 65-253-8311 Fax: 65-250-3583

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Rodovia Presidente Dutra, Km 214 07210-902-Guarulhos-SP Brasil Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

J98. 11

[MEMO]

## INTRODUCTION

| Readers :                | This manual is intended for users who have an understanding of the V30MZ hardware which is the CPU core of CBIC functions and wish to design an application system using the V30MZ functions.                                                                                                                                             |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Purpose :                | This manual is intended for users to understand the V30MZ hardware functions described in the Organization below.                                                                                                                                                                                                                         |  |  |  |

| Organization :           | This V30MZ User's Manual mainly consists of the following chapters.                                                                                                                                                                                                                                                                       |  |  |  |

|                          | • General Description• Interrupt functions• Pin functions• Standby functions• CPU functions• Reset functions• Bus control functions• Test functions                                                                                                                                                                                       |  |  |  |

| How to read this manual: | This manual assumes that users have a general understanding of electric circuits, logical circuits, and microcontrollers.                                                                                                                                                                                                                 |  |  |  |

|                          | To understand the overall functions of the V30MZ functions $\rightarrow$ Read this manual in the order of the <b>TABLE OF CONTENTS</b> .                                                                                                                                                                                                  |  |  |  |

|                          | To find the differences between V30HL <sup>™</sup> and V30MX <sup>™</sup> → Refer to <b>Section 1.3 Differences between V30MZ and V30HL, V30MX.</b>                                                                                                                                                                                       |  |  |  |

|                          | To find the details of instruction functions<br>→ Refer to the separate volume of the <b>16-Bit V Series<sup>™</sup> Instruction User's Manual</b> .                                                                                                                                                                                      |  |  |  |

| Conventions :            | Data significance: Higher digits on the left and lower digits on the rightActive low representation: xxxB (B after pin or signal name)Note: Footnote for item marked with Note in the textCaution: Information requiring particular attentionRemark: Supplementary informationNumerical representation: Binary xxxx or xxxxBDecimal xxxxH |  |  |  |

|                          | Prefixes indicating power of 2 (address space, memory capacity) :<br>$K \text{ (kilo)} : 2^{10} = 1024$ $M \text{ (mega)} : 2^{20} = 1024^{2}$ $G \text{ (giga)} : 2^{30} = 1024^{3}$                                                                                                                                                     |  |  |  |

## **Related documents** : Note that the related documents may be preliminary versions, but there are not indicated as such in this document.

- 16-Bit V Series Instruction User's Manual (U11301E)

- CB-C9 Family VX/VM Type Design Manual User's Manual (A12745E)

- CB-C9 Family VX/VM Type Core Library CPU Core User's Manual (A13195E)

## CONTENTS

| CHAP  | IER 1 GENERAL DESCRIPTION                        | 13 |

|-------|--------------------------------------------------|----|

| 1.1   | Features                                         | 13 |

| 1.2   | Symbol Diagram                                   |    |

| 1.3   | Differences between V30MZ and V30HL, V30MX       | 14 |

| CHAPT | TER 2 PIN FUNCTIONS                              | 17 |

| 2.1   | Pin List                                         | 17 |

| 2.2   | Pin Statuses                                     |    |

| 2.3   | Description of Pin Statuses                      |    |

|       | 2.3.1 Normal pins                                |    |

|       | 2.3.2 Test Pins                                  |    |

|       | 2.3.3 Reserved pins                              |    |

| 2.4   | Handling of Unused Pins                          | 23 |

| CHAPT | FER 3 CPU FUNCTIONS                              | 25 |

| 3.1   | Register Configuration                           |    |

|       | 3.1.1 General-purpose registers (AW, BW, CW, DW) |    |

|       | 3.1.2 Segment registers (PS, SS, DS0, DS1)       |    |

|       | 3.1.3 Pointer (SP, BP)                           |    |

|       | 3.1.4 Program counter (PC)                       |    |

|       | 3.1.5 Program status word (PSW)                  |    |

|       | 3.1.6 Index register (IX, IY)                    |    |

| 3.2   | Address Space                                    |    |

|       | 3.2.1 Memory space                               |    |

|       | 3.2.2 I/O space                                  |    |

| 3.3   | Instruction Prefetch                             |    |

| 3.4   | Logical Address and Physical Address             |    |

|       | 3.4.1 Segment system                             |    |

|       | 3.4.2 Segment configuration                      |    |

|       | 3.4.3 Dynamic relocation                         |    |

| 3.5   | Effective Address                                | 39 |

| 3.6   | Instruction Set                                  | 40 |

|       | 3.6.1 List of instruction sets by function       | 40 |

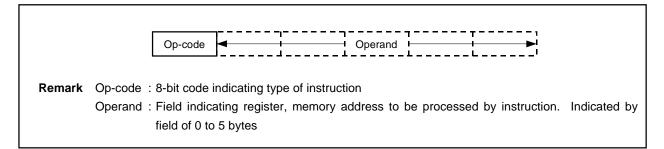

|       | 3.6.2 Format of object code                      |    |

| 3.7   | Addressing Mode                                  |    |

|       | 3.7.1 Instruction address                        |    |

|       | 3.7.2 Data address                               |    |

| CHAPT | FER 4 BUS CONTROL FUNCTIONS                      | 47 |

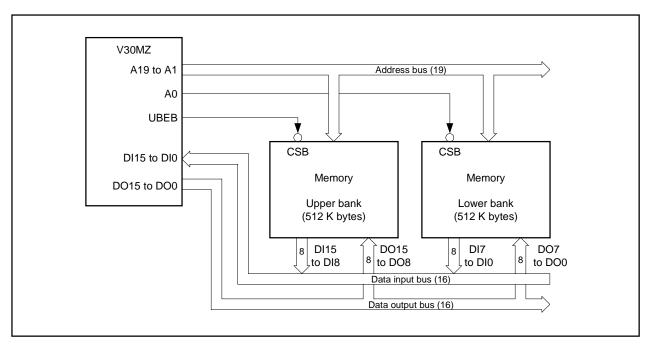

| 4.1   | Interface between V30MZ and Memory               |    |

|       | 4.1.1 Cautions on accessing word data            |    |

| 4.2   | Interface between V30MZ and I/O                  |    |

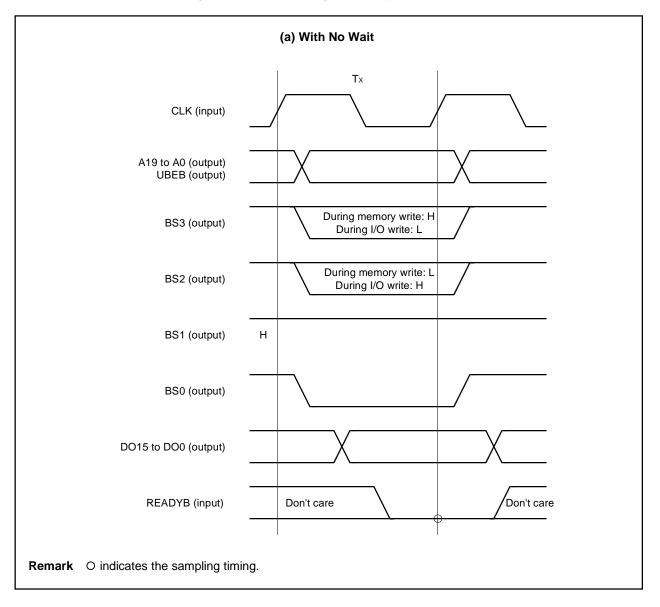

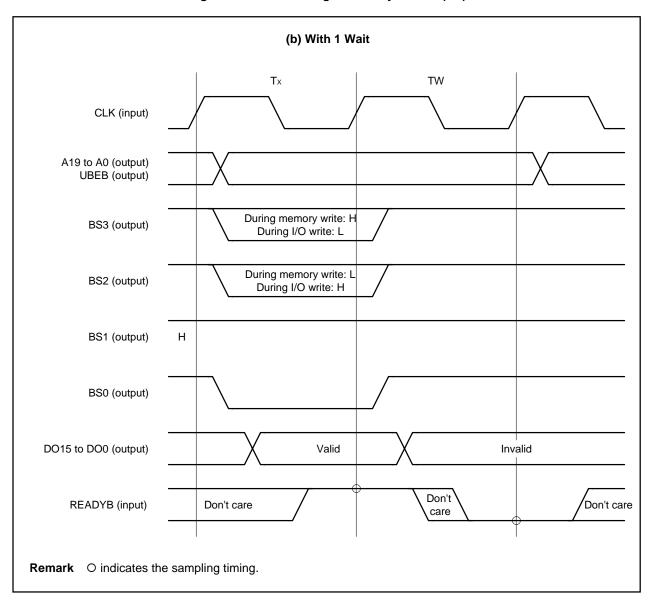

|       | Read/Write Timing of Memory and I/O              |    |

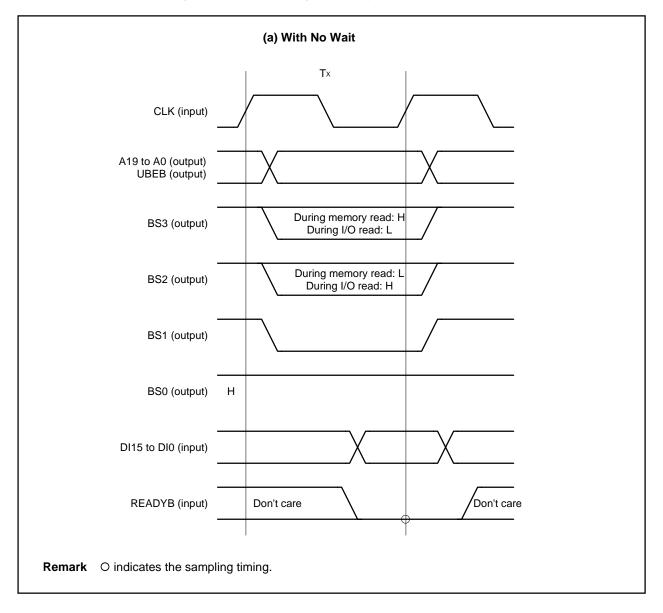

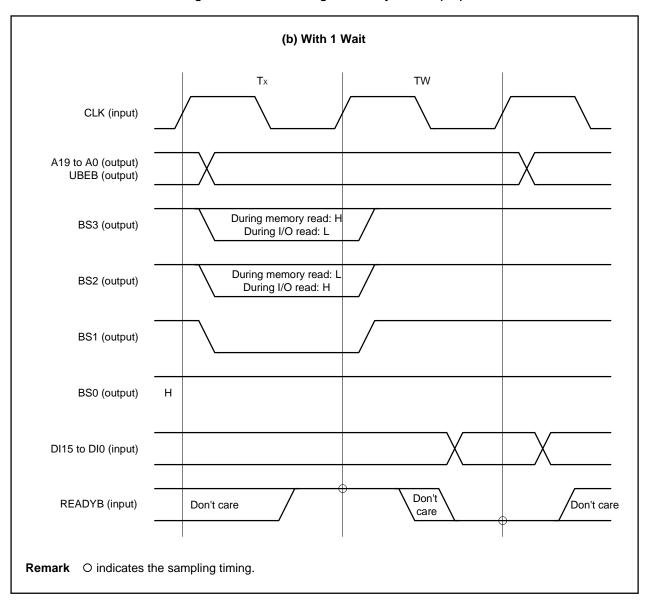

|       | 4.3.1 Read timing of memory and I/O              |    |

|       | 4.3.2 Write timing of memory and I/O             |    |

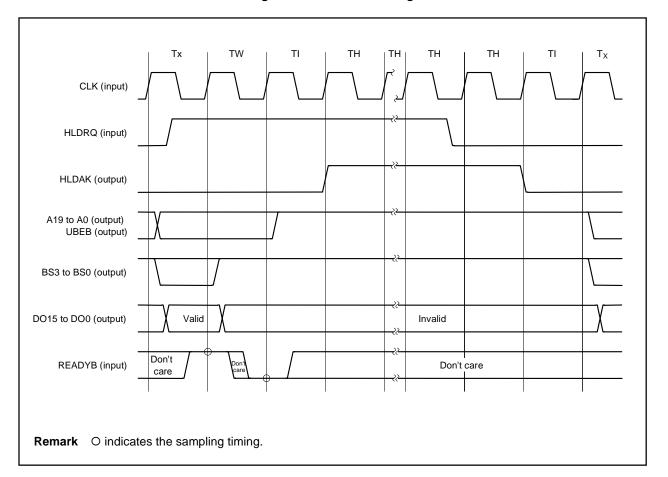

| 4.4   | Bus Hold Function                                |    |

| CHAPT                             | FER 5 INTERRUPT FUNCTIONS                                                                                         | 55                                      |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 5.1                               | Hardware Interrupt                                                                                                | 58                                      |

|                                   | 5.1.1 Non-maskable interrupt (NMI)                                                                                | 58                                      |

|                                   | 5.1.2 Maskable interrupt (INT)                                                                                    | 58                                      |

| 5.2                               | Software Interrupts                                                                                               | 60                                      |

| 5.3                               | Timing at which Interrupt is Not Acknowledged                                                                     | 61                                      |

| 5.4                               | Interrupt Servicing in Execution of Block Processing Instruction                                                  | 62                                      |

| СНАРТ                             | FER 6 STANDBY FUNCTIONS                                                                                           | 65                                      |

| 6.1                               | Setting of Standby Mode                                                                                           | 65                                      |

| 6.2                               | Standby Mode                                                                                                      | 65                                      |

| 6.3                               | Release of Standby Mode                                                                                           | 66                                      |

|                                   | 6.3.1 Release by hardware interrupt request                                                                       | 66                                      |

|                                   | 6.3.2 Release by RESET input                                                                                      | 67                                      |

|                                   |                                                                                                                   |                                         |

| СНАРТ                             | ER 7 RESET FUNCTIONS                                                                                              | 69                                      |

|                                   | TER 7 RESET FUNCTIONS                                                                                             |                                         |

| СНАРТ                             |                                                                                                                   | 71                                      |

| СНАРТ                             | TER 8 TEST FUNCTIONS                                                                                              | 71                                      |

| СНАРТ                             | TER 8 TEST FUNCTIONS                                                                                              | 71<br>71<br>71                          |

| <b>CHAPT</b><br>8.1               | TER 8 TEST FUNCTIONS<br>Test Pins<br>8.1.1 Test bus pins (TBI22 to TBI0, TBO42 to TBO0)                           | 71<br>71<br>71<br>71                    |

| <b>CHAPT</b><br>8.1<br>8.2        | TER 8 TEST FUNCTIONS<br>Test Pins<br>8.1.1 Test bus pins (TBI22 to TBI0, TBO42 to TBO0)<br>8.1.2 BUNRI, TEST pins | <b>71</b><br>71<br>71<br>71<br>72       |

| <b>CHAPT</b><br>8.1<br>8.2        | TER 8 TEST FUNCTIONS<br>Test Pins                                                                                 | <b>71</b><br>71<br>71<br>71<br>72<br>72 |

| <b>CHAPT</b><br>8.1<br>8.2        | Test Pins                                                                                                         | 71<br>71<br>71<br>71<br>72<br>72<br>72  |

| <b>CHAPT</b><br>8.1<br>8.2<br>8.3 | Test Pins<br>8.1.1 Test bus pins (TBI22 to TBI0, TBO42 to TBO0)                                                   | 71<br>71<br>71<br>72<br>72<br>72<br>72  |

| Figure No | . Title                                                                    | Page |

|-----------|----------------------------------------------------------------------------|------|

|           |                                                                            |      |

| 3-1       | Program Status Word (PSW)                                                  | 27   |

| 3-2       | Memory Map                                                                 | 31   |

| 3-3       | Configuration of Word Data and Double Word Data                            |      |

| 3-4       | I/O Мар                                                                    | 32   |

| 3-5       | Conceptual Diagram of Segment System                                       |      |

| 3-6       | Relationship between Segment Register, Offset Address and Physical Address | 35   |

| 3-7       | Relationship between Each Segment Register, Segment and Memory Space       | 36   |

| 3-8       | Dynamic Relocation                                                         |      |

| 3-9       | Memory Address Calculation                                                 |      |

| 3-10      | Object Code Format                                                         | 41   |

| 4-1       | Interface between V30MZ and Memory                                         | 47   |

| 4-2       | Read Timing of Memory and I/O                                              |      |

| 4-3       | Write Timing of Memory and I/O                                             |      |

| 4-4       | Bus Hold Timing                                                            | 54   |

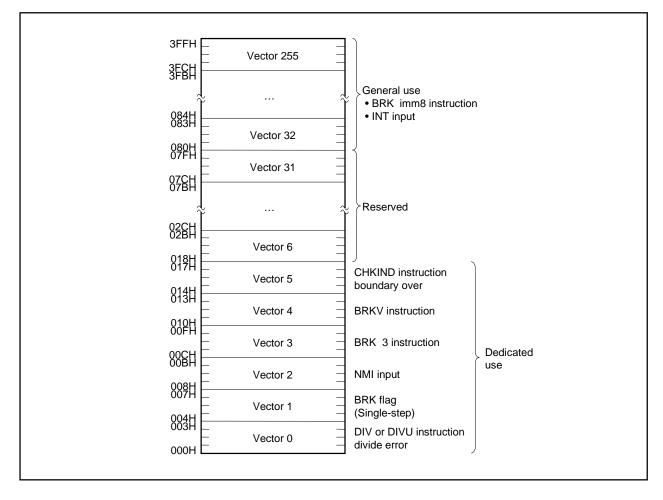

| 5-1       | Interrupt Vector Table Configuration                                       |      |

| 5-2       | Interrupt Acknowledge Cycle                                                | 59   |

| 6-1       | Timing to Enter Standby Mode                                               | 65   |

## LIST OF FIGURES

## LIST OF TABLES

| Table No. | Title                                                         | Page |

|-----------|---------------------------------------------------------------|------|

| 2-1       | Relationship among Operand and UBEB, A0, and Bus Cycles       |      |

| 2-2       | Relationship between BS3 to BS0 Signal and Bus Cycle          |      |

| 3-1       | Address and Data Configuration of Each Memory Element         |      |

| 3-2       | Segment Registers and Offset Addressing                       |      |

| 3-3       | List of Instruction Sets by Function                          |      |

| 4-1       | V30MZ Data Access                                             |      |

| 5-1       | Interrupt Source List                                         |      |

| 5-2       | Number of Bus Cycles Required until Interrupt is Acknowledged |      |

| 7-1       | Status of Output Pins after Reset                             |      |

| 7-2       | Initial Value of Registers after Reset                        | 69   |

| 8-1       | Test Mode Selection List                                      | 71   |

| A-1       | List of Number of Instruction Execution Clocks                | 74   |

#### **CHAPTER 1 GENERAL DESCRIPTION**

The V30MZ is a CPU core that is an improved version of the V30MX, which itself enhances the bus efficiency of the  $\mu$ PD70116H (other name: V30HL), an original NEC microprocessor.

The V30MZ raises the bus efficiency by realizing 1 clock/bus cycle. The incorporation of an internal pipeline considerably raises the instruction execution time, enabling fast processing comparable to that of RISC microprocessors.

Compared to the V30MX's 4.3 MIPS (33-MHz operation, no wait), the V30MZ realizes a processing performance of 35 MIPS (66-MHz operation, no wait).

#### 1.1 Features

- (1) Processing performance: 35 MIPS (66-MHz operation, no wait)

- (2) CMOS static design (internal system clock can be fully stopped)

- (3) 1 bus cycle: 1 clock

- (4) External bus interface

- Address bus: 20 bits

- Data bus: 16 bits (separate input/output buses)

- (5) Bus hold function

- (6) Standby function (HALT mode)

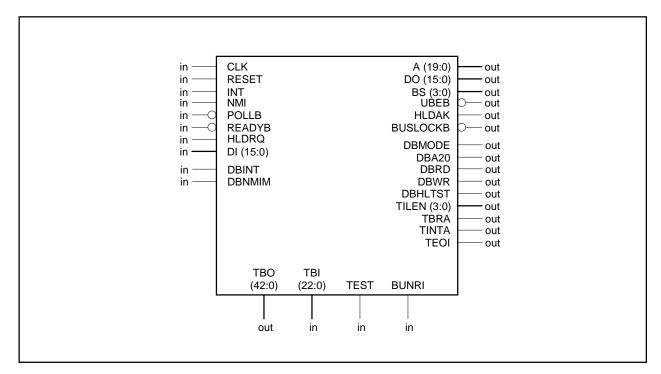

### 1.2 Symbol Diagram

#### 1.3 Differences between V30MZ and V30HL, V30MX

| Item                                                                                                             | V30MZ                                                                                                                                                                                                                                                                                                                                                                                      | V30HL                                              | V30MX                   |  |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------|--|

| Address/data bus                                                                                                 | A19 to A0, DI15 to DI0, DO15 to DO0                                                                                                                                                                                                                                                                                                                                                        | A19 to A16,<br>AD15 to AD0                         | A23 to A0, D15<br>to D0 |  |

| Large-scale mode/small-scale mode                                                                                | Not provided                                                                                                                                                                                                                                                                                                                                                                               | Provided                                           | Not provided            |  |

| Pin functions                                                                                                    | Following pins of V30HL are removed <sup>№™</sup> :<br>ASTB, PS3 to PS0, BUFEN, QS1, QS0, BUFR/W, RD,<br>RQ/AK0, INTAK, S/LG, LBS0, WR, NC                                                                                                                                                                                                                                                 | IC, RQ/AK1,                                        | _                       |  |

| $\mu$ PD8080AF emulation function                                                                                | Not provided                                                                                                                                                                                                                                                                                                                                                                               | Provided                                           | Not provided            |  |

| Connection to numerical operation co-processor                                                                   | Not possible                                                                                                                                                                                                                                                                                                                                                                               | Possible                                           |                         |  |

| LIM EMS4.0 function                                                                                              | Not provided                                                                                                                                                                                                                                                                                                                                                                               | Not provided                                       | Provided                |  |

| Test function as CBIC core                                                                                       | Provided (TBI22 to TBI0, TBO42 to TBO0, BUNRI, TEST)                                                                                                                                                                                                                                                                                                                                       | Not provided                                       | Provided                |  |

| BUSLOCKB pin status in case<br>of BUSLOCK instruction<br>execution prior to HALT<br>instruction                  | High-level output                                                                                                                                                                                                                                                                                                                                                                          | Low-level output                                   |                         |  |

| Status of UBEB pin during<br>interrupt acknowledge cycle                                                         | High-level output                                                                                                                                                                                                                                                                                                                                                                          | Low-level output                                   | Low-level output        |  |

| Status of output pins during bus hold                                                                            | See section 2.2. Pin Statuses                                                                                                                                                                                                                                                                                                                                                              | High impedance                                     |                         |  |

| Relationship between<br>BUSLOCK instruction and bus<br>hold request                                              | Bus hold request is acknowledged even if BUSLOCK<br>instruction is executed immediately before an<br>instruction that does not perform access to memory<br>or I/O. The BUSLOCKB output remains high.                                                                                                                                                                                       | BUSLOCK instruction effective for all instructions |                         |  |

| Bus hold request acknowledged<br>between first and second bus<br>cycle when odd address word<br>data is accessed | Not possible                                                                                                                                                                                                                                                                                                                                                                               | Possible                                           |                         |  |

| Bus status output at recovery<br>from bus hold status to standby<br>mode                                         | No (remains in idle status)                                                                                                                                                                                                                                                                                                                                                                | Provided                                           |                         |  |

| Instruction execution time                                                                                       | The number of instruction clocks for each instruction ar<br>the V30MZ have been improved, so that the instruction<br>reduced. Note that programs that depend on the number<br>such as consecutive I/O accesses, may not function no                                                                                                                                                        | execution time is a<br>er of instruction exe       | considerably            |  |

| Interrupt response time                                                                                          | The V30MZ performs pipeline processing internally, executing multiple instruction in parallel. Therefore, in cases such as when a hardware interrupt synchronized with a given bus cycle is requested, the V30MZ may acknowledge the interrupt request after performing a larger number of instructions than the V30HL and V30MX. However, this does not apply with regard to I/O accesses |                                                    |                         |  |

| Undefined flag change                                                                                            | If an arithmetic operation defined as an indefinite flag change is executed, the contents of the flag immediately after the execution may differ from the V30HL and V30MX. This is especially likely to occur in the case of multiply and divide instruction.                                                                                                                              |                                                    |                         |  |

| Interrupt request acknowledge disable timing                                                                     | The timing at which interrupt requests are not acknowle<br>Timing at which Interrupt is Not Acknowledged.)                                                                                                                                                                                                                                                                                 | edged differs. (Refe                               | er to Section 5.3       |  |

Note The BS3 pin of the V30MZ has the same functions as the  $\overline{IO}/M$  pin of the V30HL, except for the output timing.

**Remark** Active low pins are indicated with  $\overline{xxx}$  (overscore added) in the case of the V30HL, whereas they are indicated with xxxB (B added) in the case of the V30MZ.

| Item                                                            | V30MZ                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V30HL                                                                                                                                                                                                                                                                                                                                                                                                             | V30MX                                                                                                               |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| Supported instructions                                          | V30MX. An undefined result is obtained by executing th                                                                                                                                                                                                                                                                                                                                                                                                      | es not support the following instructions supported by the V30HL and defined result is obtained by executing these instructions.<br>KEM, CALLN, CLR1 <sup>Note 1</sup> , CMP4S, EXT, FPO2, INS, NOT1 <sup>Note 2</sup> , REPC, TEM, ROL4, ROR4, SET1 <sup>Note 3</sup> , SUB4S, TEST1                                                                                                                             |                                                                                                                     |  |  |

| Number of instruction prefixes                                  | Up to 7 instruction prefixes can be used (for all<br>instructions). Even if instruction prefixes are used<br>redundantly, normal processing is performed as long<br>as their total number doesn't exceed 7.<br>If there are more than 7 prefixes for one instruction,<br>the execution result of the instruction (to which<br>prefixes have been attached) is not guaranteed.<br>Furthermore, normal recovery from interrupt<br>processing is not possible. | For repeat string instructions<br>(REP, MOVBK, etc.), 3 types of<br>prefixes MAX. can be used (REP<br>is also counted as 1 type). If there<br>are redundant instruction prefixes,<br>repeat string instructions cannot<br>be performed normally after the<br>end of interrupt processing. In the<br>case of instructions other than<br>string instructions, the number of<br>instruction prefixes is not limited. |                                                                                                                     |  |  |

| Decimal correction instruction                                  | Performs a correction operation for the second byte of CVTDB and DVTBD instructions.                                                                                                                                                                                                                                                                                                                                                                        | Decimal correction operation is<br>performed regardless of the value<br>of the second byte of the CVTDB<br>and CVTBD instructions.                                                                                                                                                                                                                                                                                |                                                                                                                     |  |  |

| Multiple bit shift and rotate instructions                      | Only the lower 5 bits of the number of shifts are valid.                                                                                                                                                                                                                                                                                                                                                                                                    | All 8 bits of the nu<br>(immediate, or sp<br>register) are valid                                                                                                                                                                                                                                                                                                                                                  | ecification by CL                                                                                                   |  |  |

| PREPARE instruction                                             | Only the lower 5 bits of the second operand are valid.                                                                                                                                                                                                                                                                                                                                                                                                      | All 8 bits of the se<br>are valid.                                                                                                                                                                                                                                                                                                                                                                                | econd operand                                                                                                       |  |  |

| POP R instruction                                               | Executes memory read cycle 8 times. However, data corresponding to SP is not used.                                                                                                                                                                                                                                                                                                                                                                          | Except for SP, 7<br>cycles are perforr                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                     |  |  |

| Repeat prefixed CMPBK,<br>CMPBKB, and CMPBKW<br>instructions    | Memory read is performed in the order $IX\toIY$                                                                                                                                                                                                                                                                                                                                                                                                             | Memory read is p<br>order IY $\rightarrow$ IX.                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |  |  |

| CALL memptr32 instruction                                       | Reads new PC, PS values after saving current PC, PS values to the stack.                                                                                                                                                                                                                                                                                                                                                                                    | Current PC and F<br>saved on to the s<br>new PC and PS v                                                                                                                                                                                                                                                                                                                                                          | tack after the                                                                                                      |  |  |

| When number of shifts = 0 for<br>shift, and rotate instructions | Executes also write cycle of memory operand. Z flag,<br>P flag, and S flag change for SHL, SHR, and SARA<br>instructions. These flags are set/cleared depending<br>on the execution result of shift instruction.                                                                                                                                                                                                                                            | If the operand is r<br>read cycle is perf<br>write cycle of the<br>performed. For th<br>SARA instruction<br>flag, and S flag de<br>These flags retain<br>to instruction exe                                                                                                                                                                                                                                       | ormed, and the<br>shift result is not<br>e SHL, SHR, and<br>s, the Z flag, P<br>o not change.<br>h the status prior |  |  |

Notes 1. Excluding CLR1 CY and CLR1 DIR.

- 2. Excluding NOT1 CY.

- 3. Excluding SET1 CY and SET1 DIR.

|                     |                                                                                                                                                                                     |                                                                                                                                                                                                           | (3/3                                                                                                                 |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Item                | V30MZ                                                                                                                                                                               | V30HL                                                                                                                                                                                                     | V30MX                                                                                                                |

| BUSLOCK instruction | Only valid for instruction performing memory or I/O<br>access, and not valid for other instructions. Moreover,<br>during bus lock period, code fetch bus cycle is not<br>performed. | Effective for all in<br>During execution<br>instructions follow<br>BUSLOCK instru<br>BUSLOCK output<br>during this period<br>requests are not<br>Moreover, during<br>period, a code fe<br>may be performe | of the<br>ving the<br>ction, the<br>t is low level, and<br>l, bus hold<br>accepted.<br>the bus lock<br>tch bus cycle |

## CHAPTER 2 PIN FUNCTIONS

### 2.1 Pin List

| Pin              | Input/Output | Function                                    |  |  |

|------------------|--------------|---------------------------------------------|--|--|

| A19 to A0        | Output       | Address signal output                       |  |  |

| DI15 to DI0      | Input        | Data signal input                           |  |  |

| DO15 to DO0      | Output       | Data signal output                          |  |  |

| UBEB             | Output       | Data bus upper byte enable signal output    |  |  |

| BS3 to BS0       | Output       | Bus status signal output                    |  |  |

| READYB           | Input        | Wait state generation signal input          |  |  |

| BUSLOCKB         | Output       | Bus lock signal output                      |  |  |

| POLLB            | Input        | External system period sense signal input   |  |  |

| RESET            | Input        | System reset signal input                   |  |  |

| HLDRQ            | Input        | Bus hold request signal input               |  |  |

| HLDAK            | Output       | Bus hold acknowledge signal output          |  |  |

| NMI              | Input        | Non-maskable interrupt request signal input |  |  |

| INT              | Input        | Maskable interrupt request signal input     |  |  |

| CLK              | Input        | System clock input                          |  |  |

| BUNRI            | Input        | Pin for performing test using test bus      |  |  |

| TEST             | Input        |                                             |  |  |

| TBI22 to TBI0    | Input        |                                             |  |  |

| TBO42 to TBO0    | Output       |                                             |  |  |

| DBINT            | Input        | Reserved for NEC                            |  |  |

| DBMODE           | Output       |                                             |  |  |

| DBA20            | Output       |                                             |  |  |

| DBRD             | Output       |                                             |  |  |

| DBWR             | Output       |                                             |  |  |

| DBNMIM           | Input        | ]                                           |  |  |

| DBHLTST          | Output       |                                             |  |  |

| TEOI             | Output       |                                             |  |  |

| TILEN3 to TILEN0 | Output       |                                             |  |  |

| TBRA             | Output       |                                             |  |  |

| TINTA            | Output       |                                             |  |  |

## 2.2 Pin Statuses

The status of each output pin in the different operation modes is listed in the table below.

| Pin           | Pin Status |                        |           |                   |                |

|---------------|------------|------------------------|-----------|-------------------|----------------|

|               |            | Normal Mode            |           |                   | Mode           |

|               | Bus Hold   | Standby (HALT)<br>mode | Reset     | Standby test mode | Unit test mode |

| A19 to A0     | Н          | Н                      | Н         | Undefined         | Undefined      |

| DO15 to DO0   | Undefined  | Undefined              | Undefined | Undefined         | Undefined      |

| UBEB          | Н          | Н                      | н         | Undefined         | Undefined      |

| BS3 to BS0    | н          | Н                      | н         | Undefined         | Undefined      |

| BUSLOCKB      | Н          | Н                      | н         | Undefined         | Undefined      |

| HLDAK         | Н          | L                      | L         | Undefined         | Undefined      |

| TBO42 to TBO0 | Hi-Z       | Hi-Z                   | Hi-Z      | Hi-Z              | Operating      |

Remark H : High-level output

L

: Low-level output

Hi-Z : High impedance

Operating : Outputs valid signal

#### 2.3 Description of Pin Statuses

#### 2.3.1 Normal pins

#### (1) A19 to A0 (Address)...Output

Bus for outputting 20-bit address. None of the pins ever go into high impedance.

#### (2) DI15 to DI0 (Data input)...Input

Dedicated input bus for inputting 16-bit data. Always input high-level or low-level signal (do not make signal high impedance).

#### (3) DO15 to DO0 (Data output)...Output

Dedicated output bus for outputting 16-bit data. None of the pins ever go into high impedance.

#### (4) UBEB (Upper byte enable)...Output

Outputs low-active signal indicating that higher 8 bits of 16-bit data bus are to be used with memory or I/O access cycle. This pin does not go into high impedance.

The bus cycles for which this signal becomes active are as follows.

- Bus cycle through byte access of odd address

- · Bus cycle through first byte access of odd address for word data

- Bus cycle through access of even address for word data

Combined with the A0 signal, the bus cycle can be identified as follows.

#### Table 2-1. Relationship among Operand and UBEB, A0, and Bus Cycles

| Operand           |               | UBEB pin output level | A0 pin output level | Number of bus cycles |

|-------------------|---------------|-----------------------|---------------------|----------------------|

| Even address word |               | L                     | L                   | 1                    |

| Odd address word  | 1st bus cycle | L                     | Н                   | 2                    |

|                   | 2nd bus cycle | Н                     | L                   |                      |

| Even address byte |               | Н                     | L                   | 1                    |

| Odd address byte  |               | L                     | Н                   | 1                    |

Remark L: Low level

H: High level

#### (5) BS3 to BS0 (Bus status)...Output

Outputs status signal to external to notify state of the bus cycle. During reset and bus hold acknowledge, go into idle state (high-level output).

This pin does not go into high-impedance.

The BS3 pin has the same functions as the IO/M pin of the V30HL, except for output timing (only names differ).

|     | Pin Out | Bus Cycle (Status) |     |                       |

|-----|---------|--------------------|-----|-----------------------|

| BS3 | BS2     | BS1                | BS0 |                       |

| L   | L       | L                  | L   | Interrupt acknowledge |

| L   | н       | L                  | Н   | I/O read              |

| L   | Н       | Н                  | L   | I/O write             |

| н   | L       | L                  | L   | Standby (HALT) mode   |

| Н   | L       | L                  | Н   | Memory data read      |

| н   | L       | Н                  | L   | Memory data write     |

| Н   | Н       | L                  | Н   | Code fetch            |

| Н   | н       | Н                  | н   | Idle status           |

Remarks 1. L: Low level

H: High level

2. No output with combinations other than above.

#### (6) READYB (Ready)...Input

Performs wait control.

When memory or I/O data read/write operation cannot be completed within the basic bus cycle (1 clock), the bus cycle can be extended by inputting an inactive level (high level) to this pin.

#### (7) BUSLOCKB (Bus lock)...Output

It outputs a low-active signal to other bus masters requesting that they do not use the system bus during execution of 1 instruction following the BUSLOCK instruction. It also outputs the signal during interrupt acknowledge.

It does not go into high impedance.

#### (8) POLLB (Poll)...Input

It is used to synchronize between program execution by the V30MZ and operation of an external device. Input to this pin are checked by the POLL instruction: if a low level is input, the next instruction is processed; if a high level is input, program execution is halted until this pin is driven low.

Input of a low level to this pin should be done for at least 9 clocks.

#### (9) RESET (Reset)...Input

Inputs a reset signal. Following reset release, the V30MZ starts program execution from memory address FFFF0H (segment value: FFFFH, offset value: 0000H).

#### (10) HLDRQ (Hold request)...Input

Inputs a signal to the V30MZ to request that the external bus master release the address bus, data bus, and control bus (bus hold).

Inputting a high level to this pin causes the bus hold acknowledge status to be entered upon completion of the currently executing bus cycle, and while the high level is input, the bus hold acknowledge status continues. Input a high level for at least 3 clock cycles.

#### (11) HLDAK (Hold acknowledge)...Output

Outputs a signal indicating that the HLDRQ signal has been acknowledged and that the bus hold acknowledge status is entered.

#### (12) NMI (Non-maskable interrupt)...Input

Inputs a non-maskable interrupt signal by software.

The NMI signal is active at the rising edge and detected in any clock cycle, however, it starts interrupt servicing after the end of the instruction being executed.

The interrupt start address for this interrupt is determined by interrupt vector 2.

Input an active level (high level) for at least 5 cycles after a rising edge.

When inputting NMI requests consecutively, keep NMI low for at least one clock cycle.

The priority order of interrupt request signals is as follows.

#### INT < NMI < HLDRQ

**Remark** The standby mode can also be released by an NMI signal.

#### (13) INT (Interrupt request)...Input

Inputs an interrupt request signal that can be masked by software. Input an active level (high level) to this until the interrupt acknowledge status is output from the BS3-BS0 pins.

#### (14) CLK (Clock)...Input

Inputs a clock signal. Input to this CLK pin and internal operation of the V30MZ are performed at the same frequency.

When the CLK input is stopped, the supply current enters 0A.

### 2.3.2 Test Pins

## (1) TBI22 to TBI0 (Test bus input)...Input

Input test bus pin.

(2) TBO42 to TBO0 (Test bus output)...Output

Output test bus pin.

(3) TEST (Test bus control)...Input

Test bus control input pin.

## (4) BUNRI (Test bus control)...Input

Input pin for selecting normal mode/test mode.

Remark For details on the functions of each pin, see CHAPTER 8 TEST FUNCTIONS.

### 2.3.3 Reserved pins

The following each pin is reserved for NEC.

According to Section 2.4 Handling of Unused Pins, connect each pin.

- DBINT

- DBMODE

- DBA20

- DBRD

- DBWR

- DBNMIM

- DBHLTST

- TEOI

- TILEN3 to TILEN0

- TBRA

- TINTA

## 2.4 Handling of Unused Pins

| Pin              | Input/Output | Recommended Handling |

|------------------|--------------|----------------------|

| A19 to A0        | Output       | Leave open.          |

| DO15 to DO0      | Output       |                      |

| UBEB             | Output       |                      |

| BS3 to BS0       | Output       |                      |

| READYB           | Input        | Input low level.     |

| BUSLOCKB         | Output       | Leave open.          |

| POLLB            | Input        | Input low level.     |

| HLDRQ            | Input        |                      |

| HLDAK            | Output       | Leave open.          |

| NMI              | Input        | Input low level.     |

| INT              | Input        |                      |

| DBINT            | Input        |                      |

| DBMODE           | Output       | Leave open.          |

| DBA20            | Output       |                      |

| DBRD             | Output       |                      |

| DBWR             | Output       |                      |

| DBNMIM           | Input        | Input low level.     |

| DBHLTST          | Output       | Leave open.          |

| TEOI             | Output       |                      |

| TILEN3 to TILEN0 | Output       |                      |

| TBRA             | Output       |                      |

| TINTA            | Output       |                      |

[MEMO]

### **CHAPTER 3 CPU FUNCTIONS**

#### 3.1 Register Configuration

#### 3.1.1 General-purpose registers (AW, BW, CW, DW)

There are four 16-bit registers. These can be not only used as 16-bit registers, but also accessed as 8-bit registers (AH, AL, BH, BL, CH, CL, DH, DL) by dividing each register into the higher 8 bits and the lower 8 bits.

Therefore, these registers are used as 8-bit registers or 16-bit registers for a wide range of instructions such as transfer instruction, arithmetic operation instruction, logical operation instruction.

Furthermore, the following registers are used as the default registers for specific instruction processing.

- AW : Word multiplication/division, word input/output, data conversion

- AL : Byte multiplication/division, byte input/output, BCD rotate, data conversion

- AH : Byte multiplication/division

- BW : Data conversion (table reference)

- · CW : Loop control branch, repeat, and prefix

- CL : Shift instruction, rotation instruction

- DW : Word multiplication/division, indirect addressing input/output

#### 3.1.2 Segment registers (PS, SS, DS0, DS1)

The V30MZ can divide the memory space into logical segments in 64 K-byte units and control up to 4 segments simultaneously (segment system). The start address of each segment is specified by the following 4 segment registers.

- Program segment register (PS) : Specifies the base address of the segment that stores instructions.

- Stack segment register (SS) : Specifies the base address of the segment that performs stack operations.

- Data segment 0 register (DS0) : Specifies the base address of the segment that stores data.

- Data segment 1 register (DS1) : Specifies the base address of the segment that is used as a data destination by data transfer instructions.

For details of the segment system and segment registers, refer to **Section 3.4 Logical Address and Physical Address**.

#### 3.1.3 Pointer (SP, BP)

The pointer consists of two 16-bit registers (stack pointer (SP) and base pointer (BP)).

Each register is used as a pointer to specify a memory address and can be referenced in an instruction and is also used as an index register during a memory data reference.

The SP indicates the address in the stack segment at which the latest data is stored and is used as the default register during stack operation.

The BP is used to fetch the data stored on the stack.

#### 3.1.4 Program counter (PC)

The PC is a 16-bit binary counter that holds the offset information of the memory address of the program that the execution unit (EXU) is about to execute.

The PC value is automatically incremented (+1) every time the microprogram fetches an instruction code from an instruction queue.

Furthermore, in execution of a branch instruction with branch or condition, subroutine control instruction, and interrupt instruction, a new location is loaded and the PC value becomes the same as that of the prefetch pointer (PFP).

#### 3.1.5 Program status word (PSW)

The PSW consists of 6 kinds of status flag and 4 kinds of control flag.

#### (1) Status flag

- Overflow flag (V)

- Sign flag (S)

- Zero flag (Z)

- Auxiliary carry flag (AC)

- Parity flag (P)

- Carry flag (CY)

#### (2) Control flag

- Mode flag (MD)

- Direction flag (DIR)

- Interrupt enable flag (IE)

- Break flag (BRK)

The status flag is automatically set (1) and cleared (0) according to the execution result (data value) of each instruction. The CY flag can directly be set/ cleared or inverted by an instruction.

The control flag is set/cleared by an instruction and controls the operation of the V30MZ. The IE flag and BRK flag are cleared (0) when interrupt servicing is started.

RESET input clears (0) all flags (except MD flag).

The PSW is manipulated in byte units or word units by the processing shown below. Processing in byte units is only carried out on the lower 8 bits (including the status flags except the V flag).

Figure 3-1. Program Status Word (PSW)

| 15 | 14 | 13 | 12 | 11 | 10  | 9  | 8   | 7 | 6 | 5 | 4  | 3 | 2 | 1 | 0  |

|----|----|----|----|----|-----|----|-----|---|---|---|----|---|---|---|----|

| MD | 1  | 1  | 1  | v  | DIR | IE | BRK | S | z | 0 | AC | 0 | Р | 1 | СҮ |

Bits 7 to 0 can be stored or restored in AH by a MOV instruction.

All bits of the PSW are saved to the stack when an interrupt is generated or in execution of a call instruction (CALL) and restored by a return instruction (RET, RETI).

The PSW can be saved or restored to the stack independently by a PUSH PSW instruction or POP PSW instruction.

The flags are set to the states shown below after execution of each instruction.

#### (a) Carry flag (CY)

#### <1> Binary addition/subtraction

In the case of processing in byte units, CY is set when there is a carry or borrow from operation result bit 7, and cleared otherwise.

In the case of word operation, CY is set when there is a carry or borrow from operation result bit 15, and cleared otherwise.

It is not changed by an increment or decrement instruction.

#### <2> Logical operation

CY is cleared without regard to the operation result.

#### <3> Binary multiplication

CY is cleared if AH is other than 0 as a result of an unsigned byte operation.

CY is cleared if AH is AL sign extension as a result of a signed byte operation and set otherwise.

CY is cleared if DW is 0 as a result of an unsigned word operation and set otherwise.

CY is cleared if DW is AW sign extension as a result of an unsigned word operation and set otherwise. In the case of an 8-bit immediate operation, CY is cleared when the product is within 16 bits and set otherwise.

#### <4> Binary division

Undefined.

#### <5> Shift/rotate

In the case of a shift or rotate including the CY flag, CY is set when the bit shifted to the CY flag is 1 and cleared if 0.

#### (b) Parity flag (P)

#### <1> Binary addition/subtraction, logical operation, shift

Set when the number of "1" bits of the lower 8 bits of the operation result is even and cleared when it is odd.

Set when the result is all 0.

## <2> Binary multiplication/subtraction

Undefined.

#### (c) Auxiliary carry flag (AC)

#### <1> Binary addition/subtraction

In the case of processing in byte units, it is set when there is a carry from the lower 4 bits to the higher 4 bits or a borrow from the higher 4 bits to the lower 4 bits, and cleared otherwise. In a word operation, it performs the same operation as for a byte operation with respect to the lower bytes.

<2> Logical operation, binary multiplication/division, shift/rotate Undefined.

#### (d) Zero flag (Z)

#### <1> Binary addition/subtraction, logical operation, shift/rotate

It is set when the 8 bits and 16 bits of the result are all 0 for a byte operation and word operation, respectively, and cleared otherwise.

#### <2> Binary multiplication/division Undefined.

#### (e) Sign flag (S)

#### <1> Binary addition/subtraction, logical operation, shift/rotate

Set when bit 7 of the result is 1 and cleared when it is 0 in the case of a byte operation. Set when bit 15 of the result is 1 and cleared when it is 0 in the case of a word operation.

#### <2> Binary multiplication/division

Undefined.

#### Overflow flag (V) (f)

#### <1> Binary addition/subtraction

Set when carries from bit 7 and bit 6 are different and cleared when they are the same in the case of a byte operation.

Set when carries from bit 15 and bit 14 are different and cleared when they are the same in the case of a word operation.

#### <2> Binary multiplication

As a result of an unsigned byte operation, cleared if AH is 0 and set otherwise.

As a result of a signed byte operation, cleared if AH is sign extension of AL and set otherwise.

As a result of an unsigned word operation, cleared if DW is 0 and set otherwise.

As a result of a signed word operation, cleared if DW is sign extension of AW and set otherwise.

In the case of an 8-bit immediate operation, cleared if the product is within 16 bits and set if the product exceeds 16 bits.

#### <3> Binary division

Cleared.

#### <4> Logical operation

Cleared.

#### < 5 > Shift/rotate

In the case of a left 1-bit shift/rotate, the status of the overflow flag is as follows depending on the operation result.

- When CY = MSB: Cleared

- When CY  $\neq$  MSB: Set

In the case of a right 1-bit shift/rotate, its status is as follows depending on the operation result.

- When MSB = next lower bit of MSB: Cleared

- When MSB ≠ next lower bit of MSB: Set

In the case of a multi-bit shift/rotate, it is undefined.

### (g) Break flag (BRK)

Only when it is saved to the stack as part of the PSW, it can be set by a memory manipulation instruction, and becomes valid when restored to the PSW after it is set.

If the BRK flag is set, executing one instruction automatically generates a software interrupt (interrupt vector 1) allowing tracing of one instruction at a time.

#### (h) Interrupt enable flag (IE)

IE is set by an EI instruction and the maskable interrupt (INT) is enabled. It is cleared by a DI instruction and the maskable interrupt (INT) is disabled.

#### (i) Direction flag (DIR)

When the DIR flag is set, processing is carried out from the higher addresses to the lower addresses in block transfer and/or I/O system instructions. When it is cleared, processing is carried out from the lower addresses to the higher addresses.

#### (j) Mode flag (MD)

This is a  $\mu$ PD8080AF emulation function related flag that conforms to the previous V30HL. Since the V30MZ is not provided with the emulation function, this flag is invalid.

#### 3.1.6 Index register (IX, IY)

This consists of two 16-bit registers (IX, IY). In a memory data reference, it is used as an index register to generate effective addresses (each register can also be referenced in an instruction).

Furthermore, in specific instruction processing, it has the following special roles.

- IX: Address register for source operand in block data manipulation instruction Address register for source operand in BCD string operation instruction

- IY: Address register for destination operand in block data manipulation Address register for destination operand in BCD string operation instruction

#### 3.2 Address Space

#### 3.2.1 Memory space

The V30MZ uses 20-bit address information and can access 1 M bytes (512 K words) of memory.

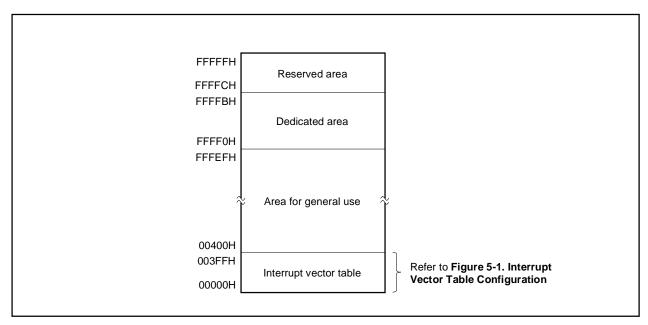

Figure 3-2 shows the memory map. The 1 K byte from 00000H to 003FFH is allocated to the interrupt vector table. However, the table area that is not used by the system can be used for other purposes.

The start address after a reset is FFFF0H. The 12 bytes from FFFF0H to FFFFBH are automatically used for a reset start, etc., and cannot be used for other purposes. The 4 bytes from FFFFCH to FFFFFH are also reserved for future use and are not available for users.

The elements stored in the memory area include operation codes, interrupt start addresses, stack data, general variables, and consist of two kinds; byte units and word units.

Addresses generated by an instruction for these elements can be even (A0 = 0) or odd (A0 = 1). Word data in the V30MZ is designed to be accessible for both even and odd addresses. Both even and odd addresses are possible for generation of an instruction. For the access method, refer to **Section 4.1 Interface between V30MZ and Memory**.

Table 3-1 shows the address and data configuration of each memory element.

| Table 3-1. | Address and | Data Co | nfiguration | of Each | Memory Element |

|------------|-------------|---------|-------------|---------|----------------|

|------------|-------------|---------|-------------|---------|----------------|

| Memory Element         | Address  | Data Configuration    |

|------------------------|----------|-----------------------|

| Operation code         | Even/odd | 1 to 6 bytes          |

| Interrupt vector table | Even     | 2 words/vector        |

| Stack                  | Even/odd | Word                  |

| General variable       | Even/odd | Byte/word/double word |

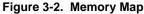

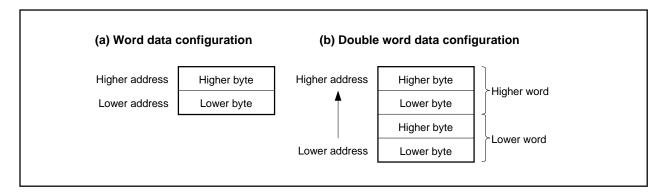

The word data configuration and double word data configuration are as follows.

#### 3.2.2 I/O space

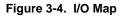

The V30MZ can access an I/O space of up to 64 K bytes (32 K words) in an area independent of the memory space.

The I/O space is addressed by I/O address information output from the lower 16 bits of the address bus. Figure 3-4 shows the I/O map. The 256 bytes of FF00H to FFFFH are reserved for future use and are not available for users.

For the access method, refer to Section 4.2 Interface between V30MZ and I/O.

#### 3.3 Instruction Prefetch

The V30MZ performs pipeline processing internally, performing instruction fetch (prefetch), instruction decode, and instruction execution in parallel. For this reason, it is difficult to determine what part of the program is currently being executed by monitoring the output of the address bus for the instruction code fetch.

If there are conditional branch instructions, even in case branching does not occur, the address of the branch destination is prefetched (only one time), so that further monitoring of the program is difficult.

The V30MZ has 8 prefetch queues (16 bytes).

#### 3.4 Logical Address and Physical Address

There are two kinds of memory space address; logical address and physical address.

The physical address means an address that directly corresponds to hardware. The V30MZ can access a 1 Mbyte memory space and so the range of a physical address value is 00000H to FFFFFH. A physical address is generated every time the bus control unit (BCU) is started which fetches an instruction and transfers data, etc.

The logical address means an address used for addressing in the segment system.

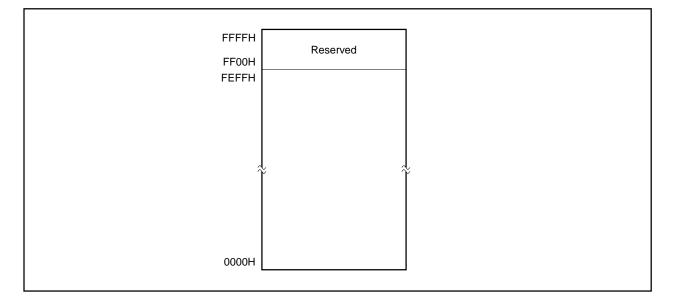

#### 3.4.1 Segment system

The segment means an address space in small units (MAX. 64 K bytes) which do not directly depend on program creation.

Each segment consists of continuous memory and can be specified individually.

Physical addresses cannot be controlled directly in program creation in machine language. The V30MZ specifies memory addresses in a segment system.

Addressing in the segment system uses the following two types of address.

- Segment base address : Start address of segment (address in 1 M-byte memory space)

- Offset address

Address allocated to each segment

In the segment system, the segment base address is fixed as a reference point and only the offset address is treated as an address in processing within each segment.

The segment base address is specified by the segment register.

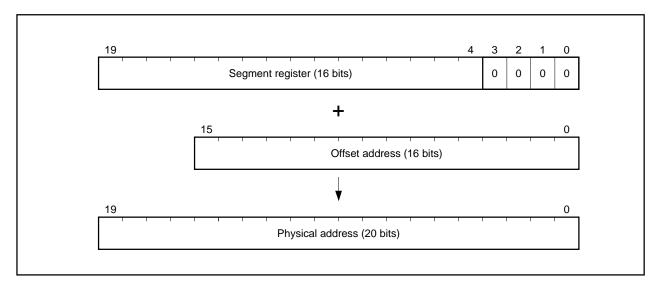

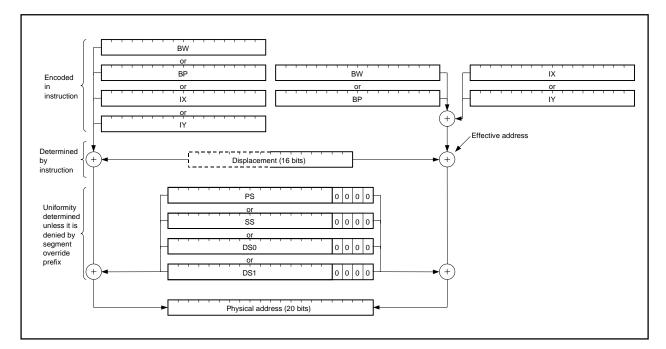

The physical address is a sum of the segment base address and offset address. Figure 3-6 shows the relationship between the segment register and offset address, and physical address.

As shown in Figure 3-6, the physical address is a sum of 16 times the segment register content (4 bits shifted to left) and offset value. At this time, the segment register content and offset value are treated as unsigned data.

In a program which is created as a set of multiple segments for which allocation addresses are specified by physical addresses, each segment is compiled and assembled individually and becomes one or a number of object modules. Each object module has a segment name, size, content classification, control information, etc., and becomes a parameter in execution of link processing.

Multiple object modules are linked and the segment base addresses corresponding the physical addresses are specified and become ready to be loaded to actual memory.

#### 3.4.2 Segment configuration

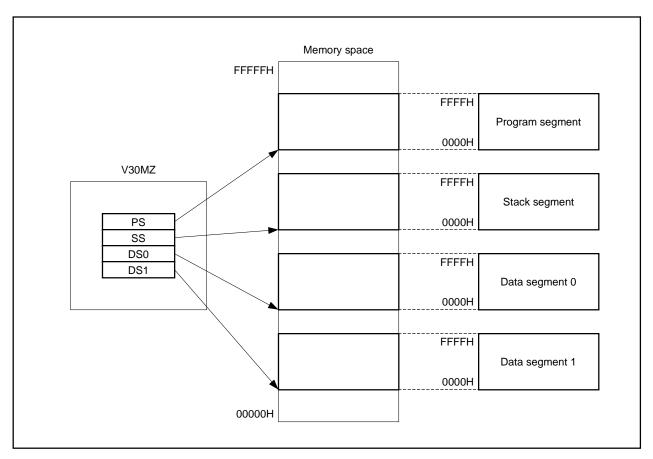

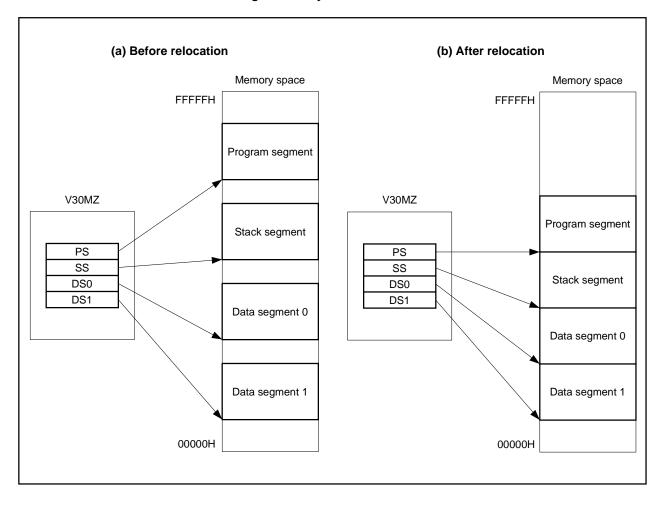

The V30MZ can distinguish 4 kinds of segment (program, stack, data 0, data 1) and define them. For each segment the start address is specified by one of the following 4 segment registers.

The BCU uses different segment registers for generation of physical addresses depending on the type of memory bus cycle.

- Program segment register (PS)

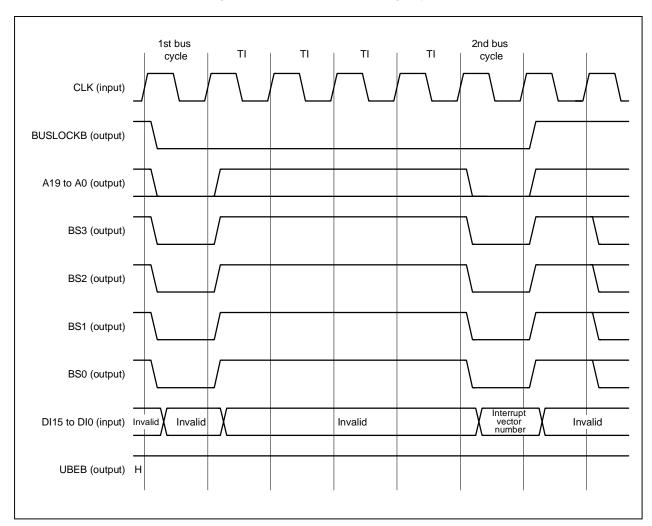

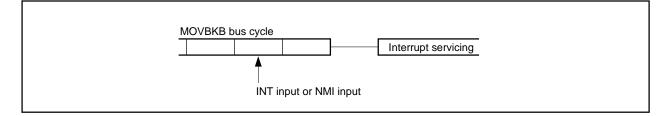

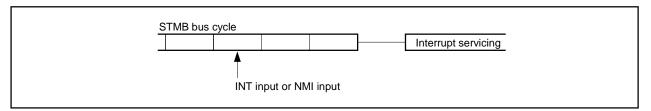

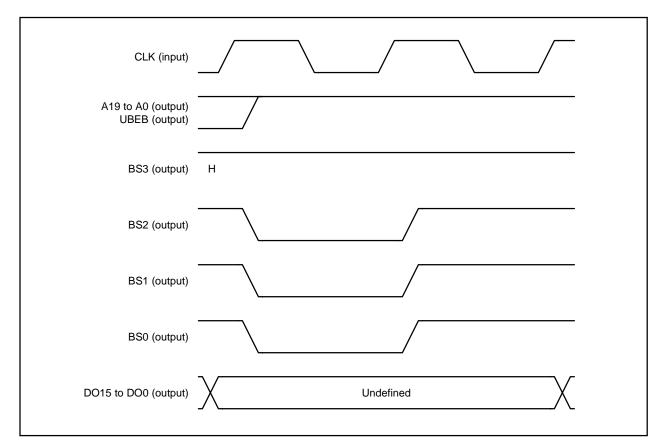

- Stack segment register (SS)