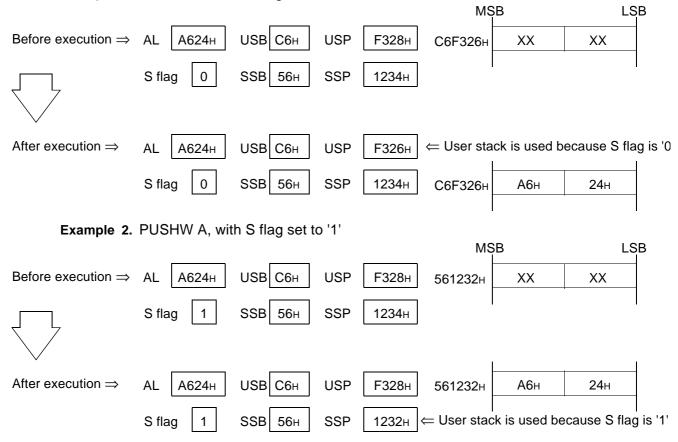

FUJITSU SEMICONDUCTOR CONTROLLER MANUAL

CM42-10108-1E

# F<sup>2</sup>MC-16F FAMILY 16-BIT MICROCONTROLLERS MB90242A SERIES

HARDWARE MANUAL

# PREFACE

This manual contains important information about your Fujitsu semiconductor product. Please read it through carefully.

The MB90242A Series is a proprietary 16-bit single-chip microcontroller, developed as a general-purpose version of the  $F^2MC-16F$  series of microcontrollers and is capable of use with ASIC (application specific IC) products.

This manual is intended for engineers using this semiconductor product in actual applications, and presents descriptions of MB90242A series functions and operation. Be sure to read the entire manual carefully. For details about instructions used with this product, refer to the "F<sup>2</sup>MC-16F Programming Manual."

\*: F<sup>2</sup>MC is an abbreviation for FUJITSU Flexible Microcontroller, and is a registered trademark.

This manual is organized as follows.

#### Section 1. Overview

This section presents the models available in the MB90242A series, with an overview of each model.

#### Section 2. Hardware Configuration

This section presents the internal configuration and operating modes of the  $F^2MC-16F$  Family CPU, as well as the specifications of hardware components in the MB90242A series.

Section 3. Operation

This section describes the use of the MB90242A series including reset sequences, external bus operation and power saving modes.

#### Appendix

The appendix describes  $F^2MC-16F$  address notation, and provides a instruction list and instruction maps.

- The products described in this manual and the specifications thereof may be changed without prior notice. To obtain up-to-date information and/or specifications, contact your Fujitsu sales representative or Fujitsu authorized dealer.

- 2. Fujitsu will not be liable for infringement of copyright, industrial property right, or other rights of a third party caused by the use of information or drawings described in this manual.

- 3. The contents of this manual may not be transferred or copied without the express permission of Fujitsu.

- 4. The products contained in this document are not intended for use with equipments which require extremely high reliability such as aerospace equipments, undersea repeaters, nuclear control systems or medical equipments for life support.

- 5. Some of the products described in this manual may be strategic materials (or special technology) as defined by the Foreign Exchange and Foreign Trade Control Law. In such cases, the products or portions thereof must not be exported without permission as defined under the Law.

© 1996 FUJITSU LIMITED Printed in Japan

# Contents

| Chapter 1:                                                 |     |

|------------------------------------------------------------|-----|

| 1.1 Features                                               | 1   |

| 1.2 Model Lineup                                           |     |

| 1.3 Blok Diagram                                           |     |

| 1.4 Pin Assignment                                         | 5   |

| 1.5 External Dimensions                                    |     |

| 1.6 Pin Description                                        |     |

| 1.7 Handling of Semiconductor Devices                      |     |

| Chapter 2:                                                 |     |

| 2.1 CPU                                                    | 21  |

| 2.2 Maps                                                   | 66  |

| 2.3 Parallel Ports                                         | 74  |

| 2.4 IIR Filter DSP Unit                                    |     |

| 2.5 UART                                                   |     |

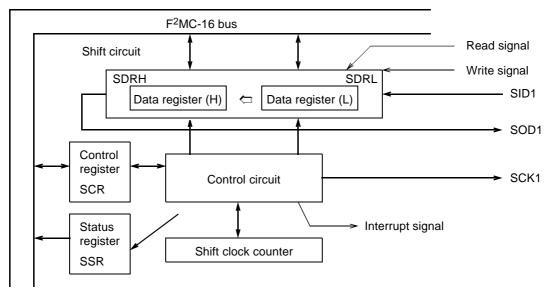

| 2.6 SSI (Simple Serial Interface)                          | 109 |

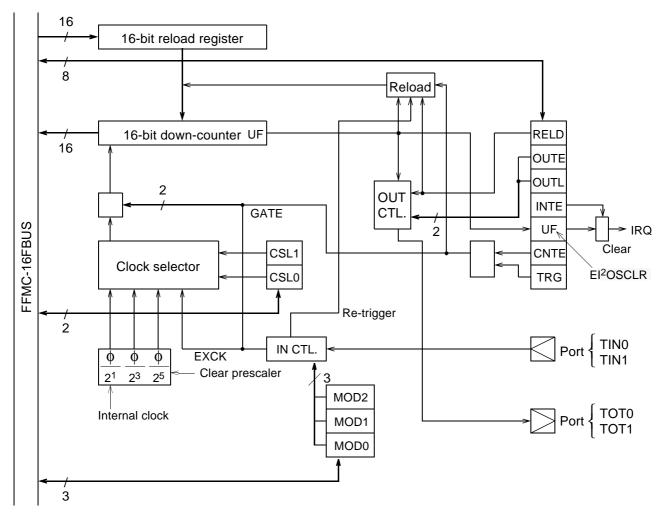

| 2.7 16-Bit Reload Timer (With Event Count Function)        |     |

| 2.8 16-Bit I/O Timer                                       |     |

| 2.9 A/D Converter                                          |     |

| 2.10 External Interrupts                                   | 141 |

| 2.11 Delayed Interrupt Generator Module                    |     |

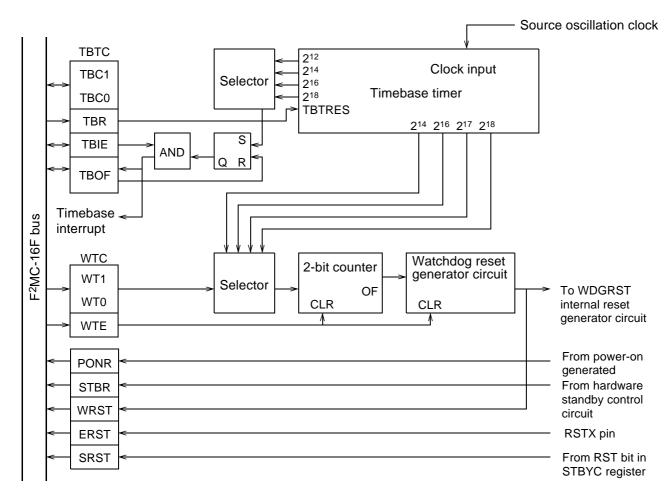

| 2.12 Watchdog Timer, Timebase Timer Functions              |     |

| Chapter 3:                                                 |     |

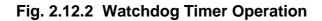

| 3.1 Clock Generator                                        |     |

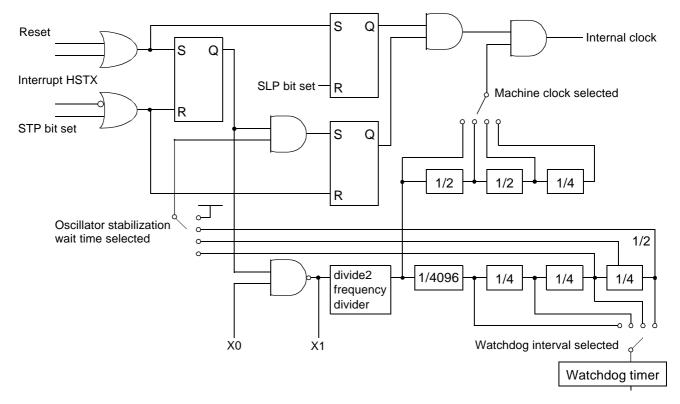

| 3.2 Reset                                                  |     |

| 3.3 Memory Access Mode                                     | 161 |

| 3.4 External Memory Access                                 | 166 |

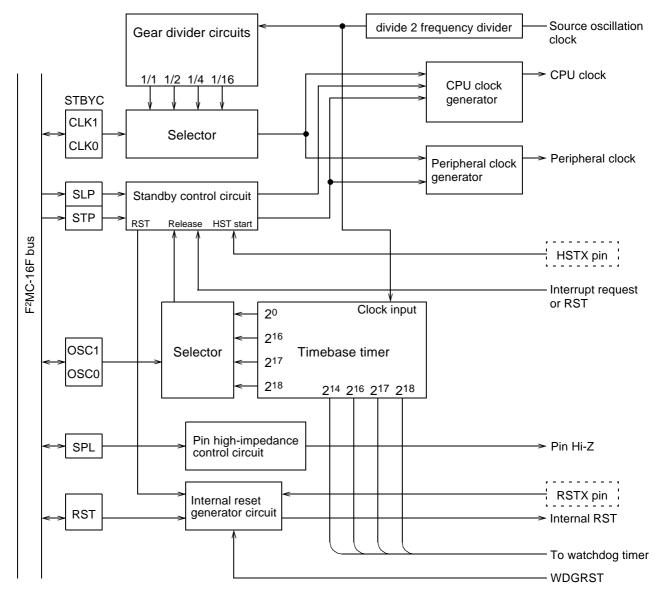

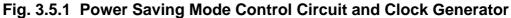

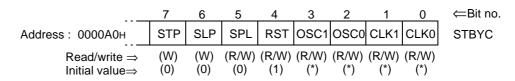

| 3.5 Power Saving Modes                                     |     |

| 3.6 Pin Status in Sleep, Stop, Hold and Reset Modes        |     |

| APPENDIX                                                   |     |

| APPENDIX A F <sup>2</sup> MC-16F Addressing Specifications |     |

| A.1 Effective Address Fields                               |     |

| A.2 Detailed Addressing Format Specifications              |     |

| APPENDIX B F <sup>2</sup> MC-16F Instruction Lists         |     |

| B.1 Instruction List Heading Descriptions                  |     |

| B.2 Instruction List Symbols                               |     |

| B.3 Effective Address Fields                               |     |

| B.4 Calculation of Execution Cycle Counts                  |     |

| B.5 Transfer Instructions                                  |     |

| B.6 Numerical Calculation Instructions                     |     |

| B.7 Logical Calculation Instructions                       |     |

| B.8 Shift Instructions                             |  |

|----------------------------------------------------|--|

| B.9 Branching Instructions                         |  |

| B.10 Other Instructions                            |  |

| B.11 Execution Cycle Counts for Special Operations |  |

| APPENDIX C F <sup>2</sup> MC-16F Instruction Map   |  |

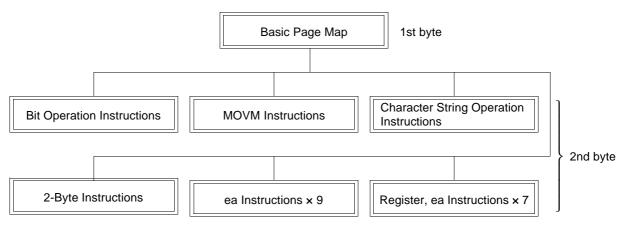

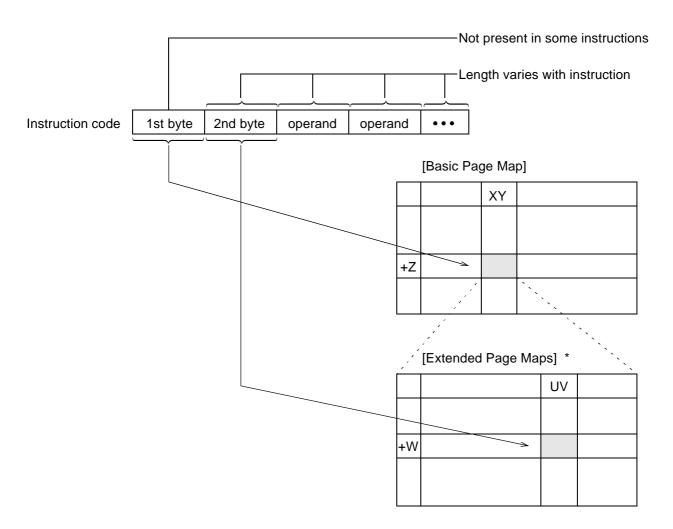

| C.1 Basic Map Structure                            |  |

| C.2 Basic Page Map                                 |  |

| C.3 Bit Operation Instruction Map                  |  |

| C.4 MOVM Instruction Map                           |  |

| C.5 Character String Operation Map                 |  |

| C.6 2-Byte Instruction Map                         |  |

| C.7 ea Instructions                                |  |

| C.8 MOVEA RWi, ea                                  |  |

| C.9 MOV Ri, ea                                     |  |

| C.10 MOVW RWi, ea                                  |  |

| C.11 MOV ea, Ri                                    |  |

| C.12 MOVW ea, RWi                                  |  |

| C.13 XCH Ri, ea                                    |  |

| C.14 XCHW RWi, ea                                  |  |

|                                                    |  |

# Chapter 1: Overview

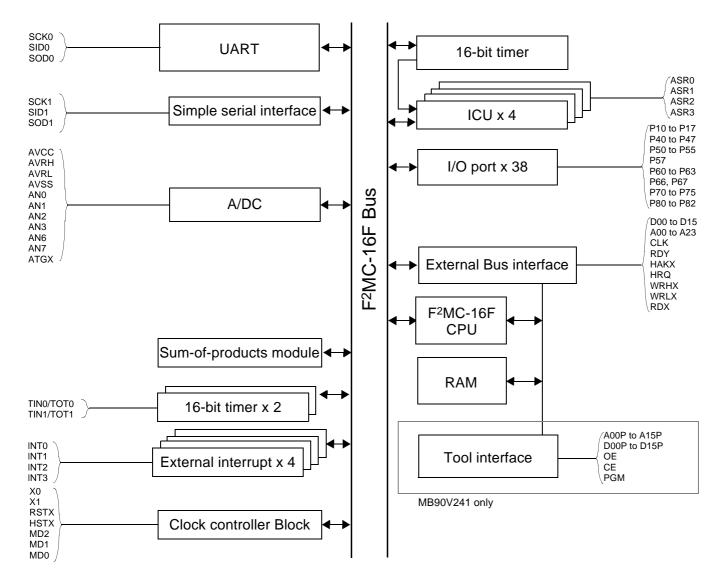

The MB90242A family of 16-bit single-chip microcontrollers is optimized for electro-mechanical control of devices such as hard disk drive devices.

The instruction system preserves the AT architecture used in the F<sup>2</sup>MC-16 and 16H series, with the addition of instructions for supporting high-level languages, expanded addressing mode, enhanced multiplication and division instructions and improved bit processing instructions. Also, the addition of a 32-bit accumulator enables processing of long-word data.

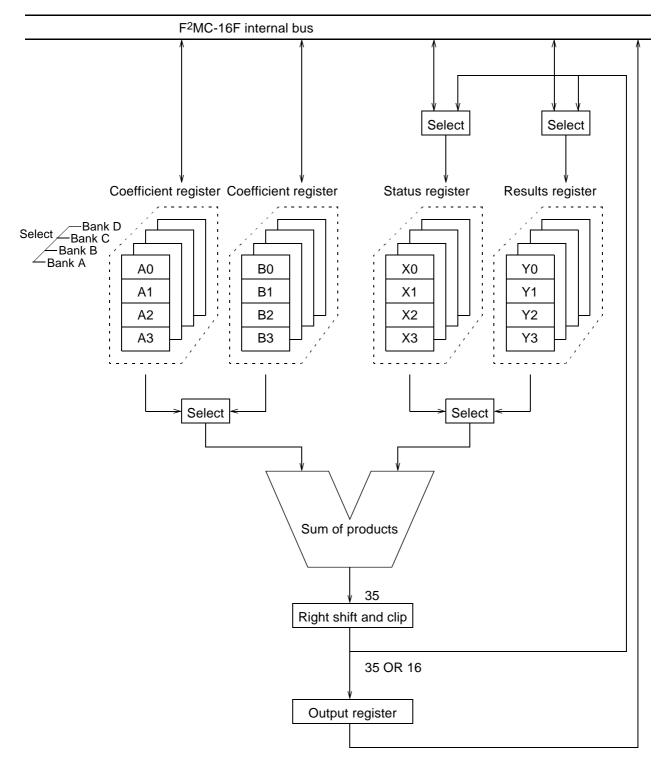

Peripheral resources include a sum-of-products calculation unit for easier realization of IIR or FIR digital filter functions. A wealth of additional on-chip components include 6-channel 8/10-bit ADC, UART, 2+1-channel timer, 4-channel input capture, and 4-channel external interrupt.

## 1.1 Features

- F<sup>2</sup>MC-16F CPU Core

- Optimum instruction system for controller applications

- Instructions enhanced for high-level language (C) and multitasking

- Improved execution speed ......8-byte queuing

- Powerful interrupt functions (interrupt processing time 1.0µs: at crystal oscillator frequency 32 MHz)

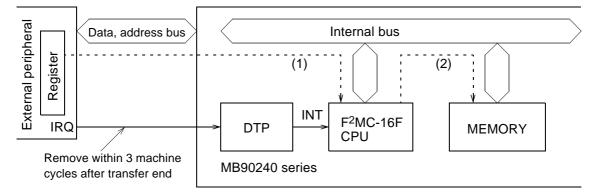

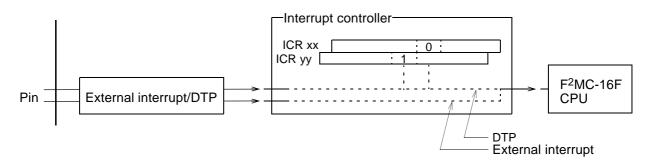

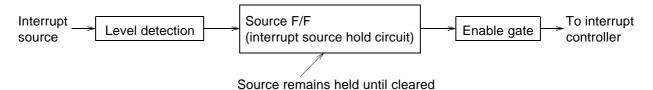

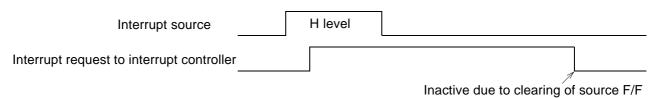

- Instruction-independent automatic transfer function

- Expanded intelligent I/O service

- DSP Unit

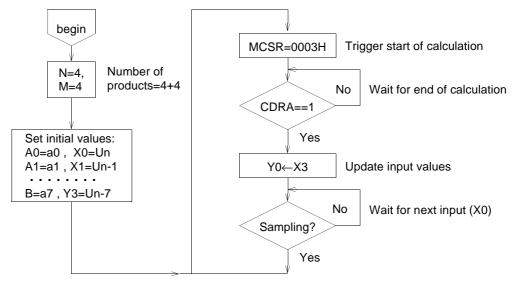

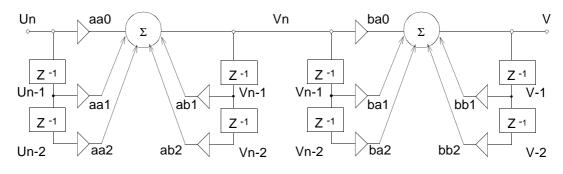

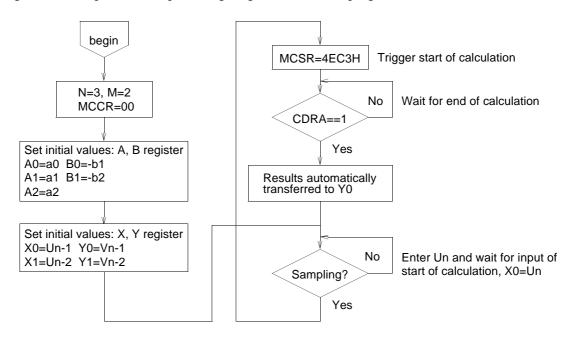

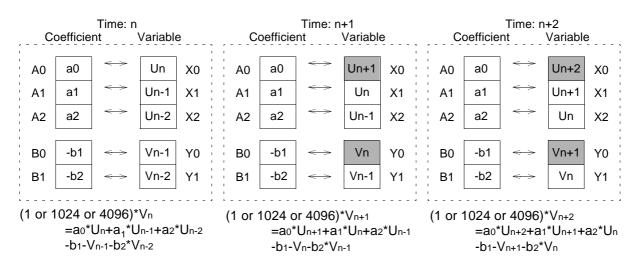

- Functions tailored for IIR calculation

- Adds up to 8-term multiplication results using 16-bit x 16-bit coding

- The following formula  $Y_{k=2} \sum_{n=0}^{M} Y_{k-n} + \sum_{m=0}^{M} a_m X_{k-m}$  execution time 0.625 ns (at crystal oscillator frequency 32 MHz, N=M=3)

- Up to 3 independent settings for N and M in the above formula

- Internal RAM RAM: 2 Kbytes

- Mode selection allows RAM data to execute as CPU instructions

- General-Purpose PortsUp to 38 ports

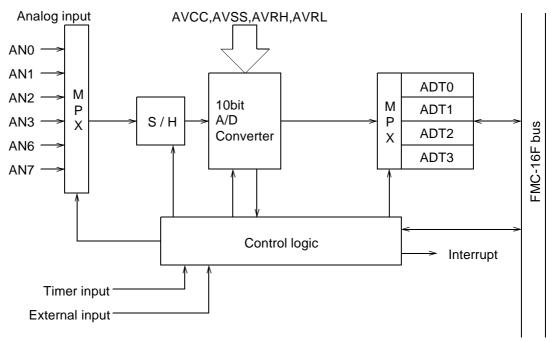

- A/D Converter ...... Analog inputs: 6

- Resolution: 10 bits

- Conversion time: 1.25 µs (minimum)

- 8/10-bit switching available

- Conversion results storage registers: 4

#### 1.1 Features

8-Bit UART.....1 channel • • 8/16-Bit I/O Simple Serial Interface (max 8 Mbps)...1 channels • 16-Bit Free-Run Timer ...... Operating clock: 0.25 µs • Selection of edge detectors • 16-Bit Reload Timer......2 channels • • Watchdog Timer • Clock Gear Function • Power Saving Modes • Sleep mode • Stop mode • Hardware disk standby mode • Low Voltage Operation • Package......SQFP-80 • CMOS 0.8 µm technology

# 1.2 Model Lineup

Table 1.2 shows the models in the MB90242A series.

|          | Package | RAM capacity | Remarks                |

|----------|---------|--------------|------------------------|

| MB90242A | SQFP-80 | 2 Kbytes     | Mass production device |

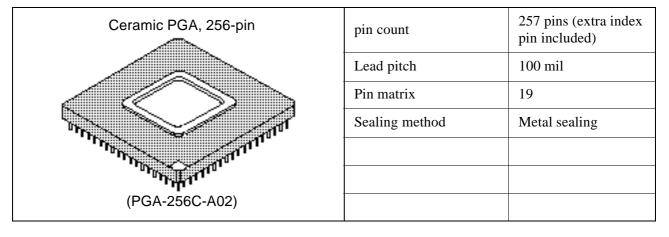

| MB90V241 | PGA-256 | 4Kbytes      | Evaluation device      |

Table 1.2 MB90242A Model lineup

Note: RAM capacity shown above is exclusive of 64-byte RAM used in sum-of-products calculation.

## 1.3 Blok Diagram

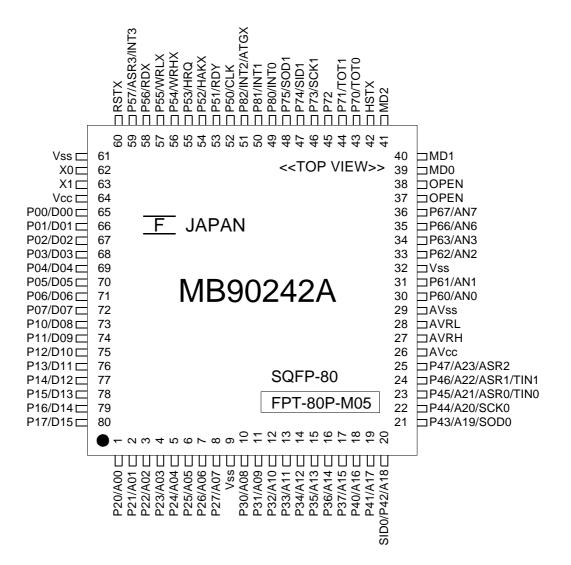

## 1.4 Pin Assignment

#### MB90242A

#### ■ MB90V241

| _            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |

|--------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

|              | 0          | $\bigcirc$ |

|              | 1          | 72         | 71         | 70         | 69         | 68         | 67         | 66         | 65         | 64         | 63         | 62         | 61         | 60         | 59         | 58         | 57         | 56         | 55         |

|              | $\bigcirc$ |

|              | 2          | 73         | 136        | 135        | 134        | 133        | 132        | 131        | 130        | 129        | 128        | 127        | 126        | 125        | 124        | 123        | 122        | 121        | 54         |

|              | $\bigcirc$ |

|              | 3          | 74         | 137        | 192        | 191        | 190        | 189        | 188        | 187        | 186        | 185        | 184        | 183        | 182        | 181        | 180        | 179        | 120        | 53         |

|              | $\bigcirc$ |

|              | 4          | 75         | 138        | 193        | 240        | 239        | 238        | 237        | 236        | 235        | 234        | 233        | 232        | 231        | 230        | 229        | 178        | 119        | 52         |

|              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            | $\bigcirc$ |            | $\bigcirc$ |            | $\bigcirc$ |            | $\bigcirc$ |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

|              | 5          | 76         | 139        | 194        | Index      |            | 256        |            | 255        |            | 254        |            | 253        |            |            | 228        | 177        | 118        | 51         |

|              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            |            |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | 0          | $\bigcirc$ |

|              | 6          | 77         | 140        | 195        | $\frown$   |            |            |            |            |            |            |            |            |            | $\frown$   | 227        | 176        | 117        | 50         |

|              | ()<br>7    | <b>78</b>  | ()<br>141  | )<br>196   | 〇<br>241   |            |            |            |            |            |            |            |            |            | ()<br>252  | ()<br>226  | ()<br>175  | $\bigcirc$ |            |

|              |            | ~          | $\sim$     | ~          | 241        |            |            |            |            |            |            |            |            |            | 292        | $\sim$     | $\sim$     | 116        | 49         |

|              | 8          | ()<br>79   | ()<br>142  | ()<br>197  |            |            |            |            |            |            |            |            |            |            |            | ()<br>225  | ()<br>174  | ()<br>115  | ()<br>48   |

|              | Õ          | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

|              | 9          | 80         | 143        | 198        | 242        |            | /          | TC         | D          | •          | VIE        | ۱۸/-       |            |            | 251        | 224        | 173        | 114        | 47         |

|              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            | JF         |            |            |            | ~>         |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

|              | 10         | 81         | 144        | 199        |            |            |            |            |            |            |            |            |            |            |            | 223        | 172        | 113        | 46         |

|              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

|              | 11         | 82         | 145        | 200        | 243        |            |            |            |            |            |            |            |            |            | 250        | 222        | 171        | 112        | 45         |

|              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            |            |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

|              | 12         | 83         | 146        | 201        |            |            |            |            |            |            |            |            |            |            |            | 221        | 170        | 111        | 44         |

|              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

|              | 13         | 84         | 147        | 202        | 244        |            |            |            |            |            |            |            |            |            | 249        | 220        | 169        | 110        | 43         |

|              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |            |            |            |            |            |            |            |            |            |            |            | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ |

|              | 14         | 85         | 148        | 203        |            |            | $\bigcirc$ |            | $\frown$   |            | $\frown$   |            | $\bigcirc$ |            |            | 219        | 168        | 109        | 42         |

|              | )<br>15    | 0<br>86    | 〇<br>149   | 0<br>204   |            |            | <br>245    |            | <u> </u>   |            | <u> </u>   |            | ()<br>248  |            |            | <b>218</b> | 0<br>167   | 108        | ()<br>41   |

|              | 10         | 00         | ()         | 204        | $\cap$     | $\bigcirc$ | 245        | $\bigcirc$ | 240        | $\bigcirc$ | 247        | $\bigcirc$ | 246        | $\bigcirc$ | $\bigcirc$ |            |            | $\bigcirc$ | 41         |

|              | 16         | 87         | 150        | 205        | 206        | 207        | 208        | 209        | 210        | 211        | 212        | 213        | 214        | 215        | 216        | 217        | 166        | 107        | 40         |

|              | $\bigcirc$ |

|              | 17         | 88         | 151        | 152        | <br>153    | 154        | 155        | 156        | 157        | 158        | 159        | 160        | 161        | 162        | 163        | 164        | 165        | 106        | 39         |

|              | $\bigcirc$ |

|              | 18         | 89         | 90         | 91         | 92         | 93         | 94         | 95         | 96         | 97         | 98         | 99         | 100        | 101        | 102        | 103        | 104        | 105        | 38         |

|              | $\bigcirc$ |

| l            | 19         | 20         | 21         | 22         | 23         | 24         | 25         | 26         | 27         | 28         | 29         | 30         | 31         | 32         | 33         | 34         | 35         | 36         | 37         |

| $\mathbf{i}$ |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |            |

| Pin No. | Pin<br>Name | Pin No. | Pin Nam |

|---------|-------------|---------|-------------|---------|-------------|---------|-------------|---------|-------------|---------|-------------|---------|---------|

| 1       | I.C.        | 38      | MD2         | 75      | N.C.        | 112     | I.C.        | 149     | P42         | 186     | I.C.        | 223     | Vss     |

| 2       | I.C.        | 39      | P82         | 76      | P01         | 113     | I.C.        | 150     | P46         | 187     | I.C.        | 224     | I.C.    |

| 3       | N.C.        | 40      | P53         | 77      | P04         | 114     | I.C.        | 151     | N.C.        | 188     | AVRH        | 225     | I.C.    |

| 4       | P00         | 41      | N.C.        | 78      | P07         | 115     | I.C.        | 152     | P74         | 189     | P60         | 226     | Vss     |

| 5       | P03         | 42      | N.C.        | 79      | P12         | 116     | I.C.        | 153     | P81         | 190     | P66         | 227     | I.C.    |

| 6       | P05         | 43      | I.C.        | 80      | P16         | 117     | I.C.        | 154     | D01P        | 191     | I.C.        | 228     | Vss     |

| 7       | P10         | 44      | I.C.        | 81      | P21         | 118     | I.C.        | 155     | D05P        | 192     | I.C.        | 229     | N.C.    |

| 8       | P13         | 45      | I.C.        | 82      | P23         | 119     | I.C.        | 156     | D08P        | 193     | I.C.        | 230     | Vss     |

| 9       | P17         | 46      | I.C.        | 83      | P27         | 120     | I.C.        | 157     | D12P        | 194     | Vss         | 231     | I.C.    |

| 10      | N.C.        | 47      | I.C.        | 84      | P31         | 121     | N.C.        | 158     | A00P        | 195     | X1          | 232     | Vss     |

| 11      | P22         | 48      | I.C.        | 85      | P34         | 122     | I.C.        | 159     | A02P        | 196     | Vss         | 233     | I.C.    |

| 12      | P26         | 49      | I.C.        | 86      | P37         | 123     | I.C.        | 160     | A06P        | 197     | N.C.        | 234     | I.C.    |

| 13      | N.C.        | 50      | I.C.        | 87      | P43         | 124     | I.C.        | 161     | CE          | 198     | P14         | 235     | Vss     |

| 14      | P33         | 51      | I.C.        | 88      | P45         | 125     | I.C.        | 162     | A11P        | 199     | Vss         | 236     | RSTX    |

| 15      | P35         | 52      | I.C.        | 89      | N.C.        | 126     | I.C.        | 163     | A15P        | 200     | P25         | 237     | N.C.    |

| 16      | P40         | 53      | I.C.        | 90      | P73         | 127     | I.C.        | 164     | P.D.        | 201     | P30         | 238     | Vss     |

| 17      | P44         | 54      | I.C.        | 91      | P80         | 128     | N.C.        | 165     | N.C.        | 202     | Vss         | 239     | DVRL    |

| 18      | P47         | 55      | I.C.        | 92      | D00P        | 129     | I.C.        | 166     | N.C.        | 203     | P41         | 240     | Vss     |

| 19      | P71         | 56      | I.C.        | 93      | D03P        | 130     | I.C.        | 167     | P51         | 204     | Vss         | 241     | Vcc     |

| 20      | P72         | 57      | I.C.        | 94      | D06P        | 131     | AVcc        | 168     | P55         | 205     | P70         | 242     | Vcc     |

| 21      | P75         | 58      | I.C.        | 95      | D09P        | 132     | AVss        | 169     | N.C.        | 206     | Vss         | 243     | Vcc     |

| 22      | N.C.        | 59      | I.C.        | 96      | D13P        | 133     | P62         | 170     | I.C.        | 207     | N.C.        | 244     | Vcc     |

| 23      | D02P        | 60      | I.C.        | 97      | N.C.        | 134     | P67         | 171     | I.C.        | 208     | Vss         | 245     | Vcc     |

| 24      | D04P        | 61      | I.C.        | 98      | A01P        | 135     | I.C.        | 172     | I.C.        | 209     | D07P        | 246     | Vcc     |

| 25      | N.C.        | 62      | I.C.        | 99      | A05P        | 136     | I.C.        | 173     | I.C.        | 210     | D11P        | 247     | Vcc     |

| 26      | D10P        | 63      | N.C.        | 100     | PGM         | 137     | N.C.        | 174     | I.C.        | 211     | Vss         | 248     | Vcc     |

| 27      | D14P        | 64      | N.C.        | 101     | A09P        | 138     | I.C.        | 175     | N.C.        | 212     | A03P        | 249     | Vcc     |

| 28      | D15P        | 65      | I.C.        | 102     | A12P        | 139     | X0          | 176     | I.C.        | 213     | P.D.        | 250     | Vcc     |

| 29      | N.C.        | 66      | N.C.        | 103     | OE          | 140     | P02         | 177     | I.C.        | 214     | Vss         | 251     | Vcc     |

| 30      | A04P        | 67      | AVRL        | 104     | P.D.        | 141     | P06         | 178     | I.C.        | 215     | A14P        | 252     | Vcc     |

| 31      | A07P        | 68      | P61         | 105     | VPP         | 142     | P11         | 179     | N.C.        | 216     | Vss         | 253     | Vcc     |

| 32      | A08P        | 69      | P61         | 106     | HSTX        | 143     | P15         | 180     | I.C.        | 217     | MD0         | 254     | Vcc     |

| 33      | A10P        | 70      | DVRH        | 107     | P50         | 144     | P20         | 181     | I.C.        | 218     | Vss         | 255     | Vcc     |

| 34      | A13P        | 71      | I.C.        | 108     | P54         | 145     | P24         | 182     | I.C.        | 219     | P52         | 256     | Vcc     |

| 35      | P.D.        | 72      | I.C.        | 109     | P56         | 146     | N.C.        | 183     | I.C.        | 220     | Vss         |         |         |

| 36      | P.D.        | 73      | I.C.        | 110     | P57         | 147     | P32         | 184     | I.C.        | 221     | I.C.        |         | 1       |

| 37      | MD1         | 74      | I.C.        | 111     | I.C.        | 148     | P36         | 185     | I.C.        | 222     | I.C.        | 1       | 1       |

P.D. (Pull Down): Requires an external pull-down resistor.

N.C. (Non Connection): Not connected.

I.C. (Internal Connection): Connected to internal pin protection circuit.

## Fig. 1.4.3 Pin Assignment

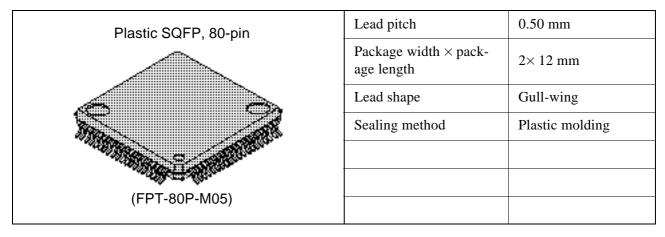

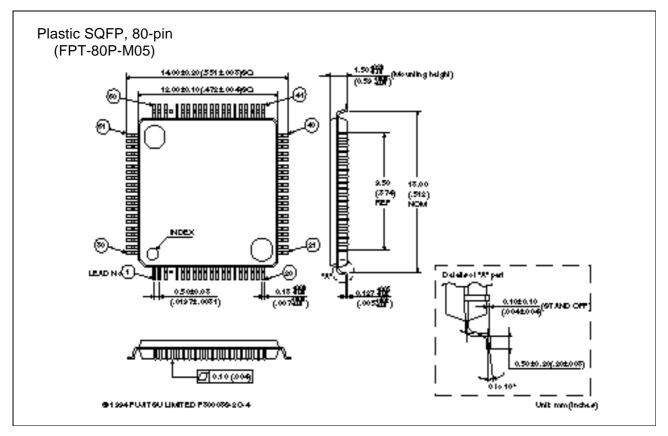

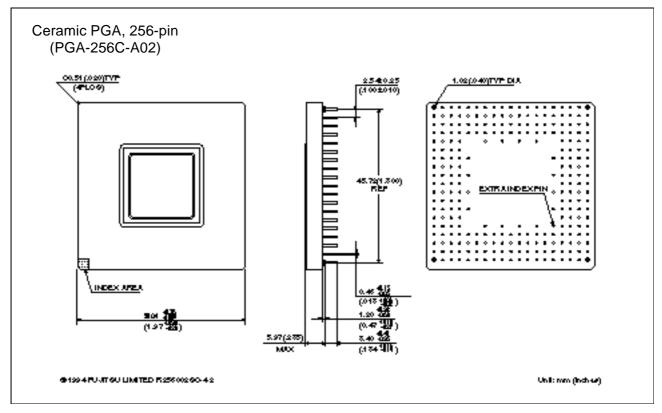

# **1.5 External Dimensions**

#### MB90242A

## FPT-80P-M05

#### EIAJ Code: \*QFP080-P-1212-1

MB90V241

PGA-256C-A02

#### EIAJ Code: \*PGA257-C-S19U-2

# 1.6 Pin Description

| Pin No.     | Name                  | Circuit type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-----------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 8      | P20/A00 to<br>P27/A07 | F            | P20 to P27 are not available for use as general-purpose ports.<br>A00 to A07 are the output pins for the lower 8 bits of the<br>external address bus.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9           | VSS                   | power supply | Ground level pin for digital circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10 to<br>17 | P30/A08 to<br>P37/A15 | F            | P30 to P37 are not available for use as general-purpose ports.<br>A08 to A15 are the output pins for the middle 8 bits of the<br>external address bus.                                                                                                                                                                                                                                                                                                                                                                                                        |

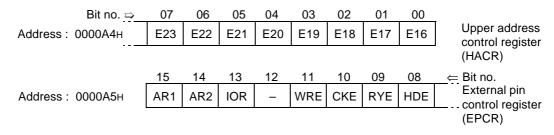

| 18          | P40/A16               | F            | <ul><li>P40 is a general-purpose I/O port. This function is enabled when the corresponding bit in the upper address control register is set to 'port.'</li><li>A16 is the output pin for bit 16 of the external address bus. This function is enabled when the corresponding bit in the upper address control register is set to 'address.'</li></ul>                                                                                                                                                                                                         |

| 19          | P41/A17               | F            | <ul><li>P41 is a general-purpose I/O port. This function is enabled when the corresponding bit in the upper address control register is set to 'port.'</li><li>A17 is the output pin for bit 17 of the external address bus. This function is enabled when the corresponding bit in the upper address control register is set to 'address.'</li></ul>                                                                                                                                                                                                         |

| 20          | P42/A18/SID0          | F            | <ul> <li>P42 is a general-purpose I/O port. This function is enabled when the corresponding bit in the upper address control register is set to 'port.'</li> <li>A18 is the output pin for bit 18 of the external address bus. This function is enabled when the corresponding bit in the upper address control register is set to 'address.'</li> <li>SID0 is the data input pin for UART #0. Because this function is in continual use during UART #0 input operations, I/O access from other functions should not be attempted unless intended.</li> </ul> |

| 21          | P43/A19/<br>SOD0      | F            | <ul> <li>P43 is a general-purpose I/O port. This function is enabled when UART #0 data output is disabled and the corresponding bit in the upper address control register is set to 'port.'</li> <li>A19 is the output pin for bit 19 of the external address bus. This function is enabled when UART #0 data output is disabled and the corresponding bit in the upper address control register is set to 'address.'</li> <li>SOD0 is the data output pin for UART #0. This function is enabled when UART #0 data output is enabled.</li> </ul>              |

## Table 1.6 Pin Description

| Pin No. | Name                  | Circuit type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|-----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22      | P44/A20/SCK0          | F            | <ul> <li>P44 is a general-purpose I/O port. This function is enabled when UART #0 clock output is disabled and the corresponding bit in the upper address control register is set to 'port.'</li> <li>A20 is the output pin for bit 20 of the external address bus. This function is enabled when UART #0 clock output is disabled and the corresponding bit in the upper address control register is set to 'address.'</li> <li>SCK0 is the clock signal output pin for UART #0. This function is enabled when UART #0 clock output is enabled.</li> </ul>                                                                                                                                                                                                                                                                            |

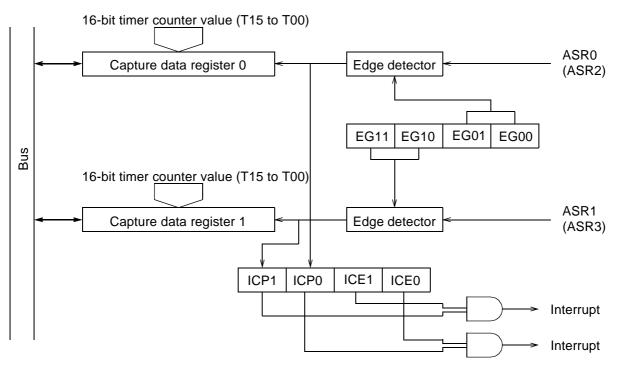

| 23      | P45/A21/ASR0<br>/TIN0 | F            | <ul> <li>P45 is a general-purpose I/O port. This function is enabled when the corresponding bit in the upper address control register is set to 'port.'</li> <li>A21 is the output pin for bit 21 of the external address bus. This function is enabled when the corresponding bit in the upper address control register is set to 'address.'</li> <li>ASR0 is the data input pin for input capture #0. This function is used for input at all times when input capture #0 is receiving input, and therefore I/O access from other functions should not be attempted unless intended.</li> <li>TIN0 is the data input pin for 16-bit timer #0. This function is used for input at all times when 16-bit timer #0 is receiving input, and therefore I/O access from other functions should not be attempted unless intended.</li> </ul> |

| 24      | P46/A22/ASR1<br>/TIN1 | F            | <ul> <li>P46 is a general-purpose I/O port. This function is enabled the corresponding bit in the upper address control register is set to 'port.'</li> <li>A22 is the output pin for bit 22 of the external address bus. This function is enabled when the corresponding bit in the upper address control register is set to 'address.'</li> <li>ASR1 is the data input pin for input capture #1. This function is used for input at all times when input capture #1 is receiving input, and therefore I/O access from other functions should not be attempted unless intended.</li> <li>TIN1 is the data input pin for 16-bit timer #1. This function is used for input at all times when 16-bit timer #1 is receiving input, and therefore I/O access from other functions should not be attempted unless intended.</li> </ul>      |

| 25      | P47/A23/ASR2          | F            | <ul> <li>P47 is a general-purpose I/O port. This function is enabled when the corresponding bit in the upper address control register is set to 'port.'</li> <li>A23 is the output pin for bit 23 of the external address bus. This function is enabled when the corresponding bit in the address high control register is set to 'address.'</li> <li>ASR2 is the data input pin for input capture #2. This function is used for input at all times when input capture #2 is receiving input, and therefore I/O access from other functions should not be attempted unless intended.</li> </ul>                                                                                                                                                                                                                                        |

| Pin No.     | Name                   | Circuit type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26          | AVCC                   | Power supply | Analog circuit power supply. Power must only be switched on<br>or off when a potential greater than AVCC is applied to the<br>VCC terminal.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 27          | AVRH                   | Power supply | This is an A/D converter external reference voltage input pin.<br>This pin should only be switched on or off when a potential<br>greater than AVRH is applied to the AVCC pin.                                                                                                                                                                                                                                                                                                                                                                                       |

| 28          | AVRL                   | Power supply | This is an A/D converter external reference voltage input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 29          | AVSS                   | Power supply | Analog circuit ground level pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

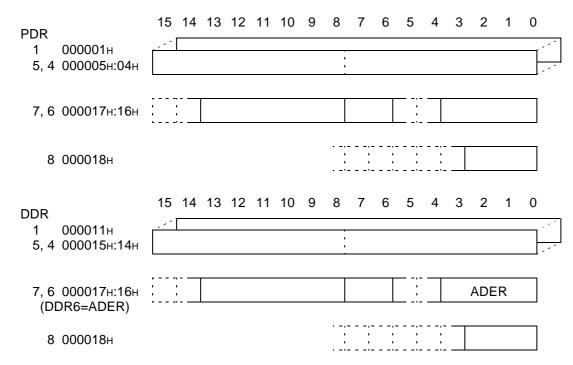

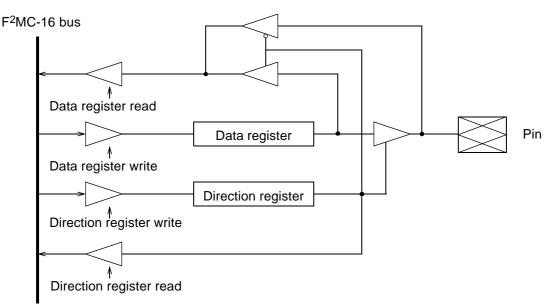

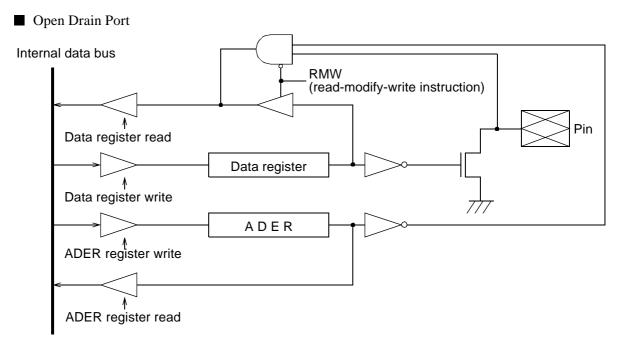

| 30 to<br>31 | P60/AN0 and<br>P61/AN1 | Н            | <ul> <li>P60 and P61 are N-channel open drain type I/O ports. When the corresponding bits in the ADER register is set to '0,' the level of these pins is read, resulting from read access to data registers by all read instructions (except for read-modify-write instructions). Values written in data registers are output directly from these pins.</li> <li>AN0 and AN1 are A/D converter analog input pins. To use this function, set the corresponding bit in the ADER register to '1' and set the corresponding bits in the data register to '1.'</li> </ul> |

| 32          | VSS                    | Power supply | Digital circuit ground level pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 33 to<br>34 | P62/AN2 and<br>P63/AN3 | н            | <ul> <li>P62 and P63 are N-channel open drain type I/O ports. When the corresponding bits in the ADER register is set to '0,' the level of these pins is read, resulting from read access to data registers by all read instructions (except for read-modify-write instructions). Values written in data registers are output directly from these pins.</li> <li>AN2 to AN3 are A/D converter analog input pins. To use this function, set the corresponding bit in the ADER register to '1' and set the corresponding bits in the data register to '1.'</li> </ul>  |

| 35 to<br>36 | P66/AN6 and<br>P67/AN7 | н            | <ul> <li>P66 and P67 are N-channel open drain type I/O ports. When the corresponding bits in the ADER register is set to '0,' the level of these pins is read, resulting from read access to data registers by all read instructions (except for read-modify-write instructions). Values written in data registers are output directly from these pins.</li> <li>AN6 and AN7 are A/D converter analog input pins. To use this function, set the corresponding bit in the ADER register to '1' and set the corresponding bits in the data register to '1.'</li> </ul> |

| 37          | OPEN                   |              | Open terminal. No internal connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 38          | OPEN                   |              | Open terminal. No internal connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

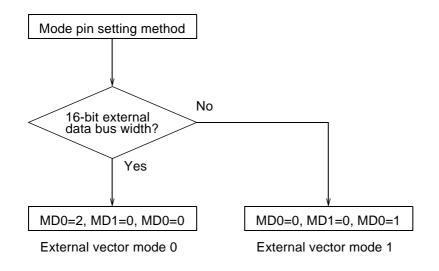

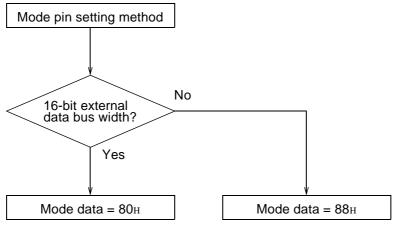

| 39 to<br>41 | MD0 to MD2             | С            | Operating mode setting input pins. These pins should be directly connected to Vcc or Vss.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 42          | HSTX                   | D            | Hardware standby input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 1.6 Pin Description (Continued)

| Pin No.     | Name                        | Circuit type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-----------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43 to<br>45 | P70/TOT0, P71/<br>TOT1, P72 | Ι            | <ul><li>P70 to P72 are general-purpose I/O ports. This function is enabled when output from 16-bit timers #0 to #1 is also disabled.</li><li>TOT0 to TOT1 are 16-bit timer output pins. This function is enabled when output from 16-bit timers #0 to #1 is also enabled.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 46          | P73/SCK1                    | F            | P73 is a general-purpose I/O port. This function is enabled<br>when clock output from SSI #1 is disabled.<br>SCK1 is the SSI #1 clock output. This function is enabled<br>when clock output from SSI #1 is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 47          | P74/SID1                    | F            | P74 is a general-purpose I/O port. This function is enabled at all times.<br>SID1 is the data input pins for SSI #1. This function is used for input at all times when SSI #1 is receiving input, and therefore I/O access from other functions should not be attempted unless intended.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 48          | P75/SOD1                    | F            | P75 is a general-purpose I/O port. This function is enabled<br>when data output from SSI #1 is disabled.<br>SOD0 is the SSI #1 data output. This function is enabled when<br>data output from SSI #1 is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 49 to<br>50 | P80/INT0 and<br>P81/INT1    | G            | <ul><li>P80 and P81 are general-purpose I/O ports. This function is enabled at all times.</li><li>INT0 to INT1 are external interrupt input pins. This function is used for input at all times when the external interrupt function is enabled, and therefore I/O access from other functions should not be attempted unless intended.</li></ul>                                                                                                                                                                                                                                                                                                                                                                               |

| 51          | P82/INT2<br>/ATGX           | F            | P82 is a general-purpose I/O port. This function is enabled at<br>all times.<br>INT2 is an external interrupt input pin. This function is used<br>for input at all times when the external interrupt function is<br>enabled, and therefore I/O access from other functions should<br>not be attempted unless intended. This pin is held at low level<br>when the CPU is in stop mode, and therefore the signal for<br>recovery from stop mode should be input at INT0 or INT1.<br>ATGX is the A/D converter start trigger input pin. This func-<br>tion is used for input at all times when the A/D converter is in<br>standby mode, and therefore I/O access from other functions<br>should not be attempted unless intended. |

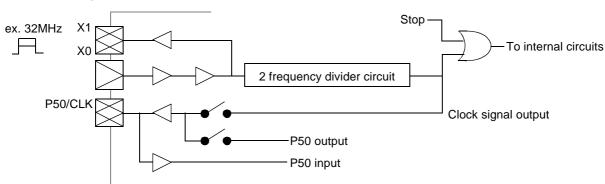

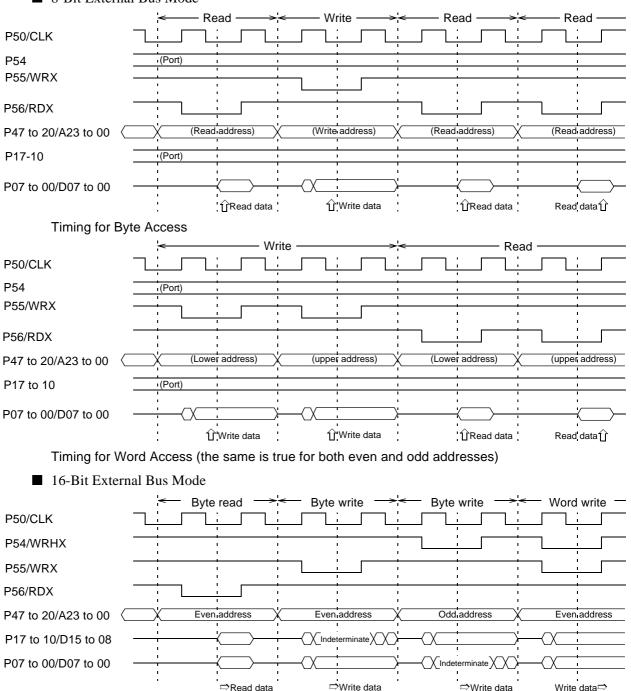

| 52          | P50/CLK                     | F            | P50 is a general-purpose I/O port. This function is enabled<br>when the clock signal output setting is disabled.<br>CLK is the clock signal output pin. This function is enabled<br>when clock signal output setting is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 53          | P51/RDY                     | Е            | P51 is a general-purpose I/O port. This function is enabled<br>when the ready function is disabled.<br>RDY is the ready signal input pin. This function is enabled<br>when the ready function is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 1.6 Pin Description (Continued)

| Pin No.     | Name                  | Circuit type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 54          | P52/HAKX              | Е            | <ul><li>P52 is a general-purpose I/O port. This signal is enabled when the hold function is disabled.</li><li>HAKX is the hold acknowledge signal output pin. This function is enabled when the hold function is enabled.</li></ul>                                                                                                                                                                                                                                                                                                                  |

| 55          | P53/HRQ               | Е            | <ul><li>P53 is a general-purpose I/O port. This signal is enabled when the hold function is disabled.</li><li>HRQ is the hold request signal input pin. This function is enabled when the hold function is enabled.</li></ul>                                                                                                                                                                                                                                                                                                                        |

| 56          | P54/WRHX              | F            | <ul><li>P54 is a general-purpose I/O port. This function is enabled when operating in 8-bit external bus mode or when WR pin output is disabled.</li><li>WRHX is the write strobe signal output pin for the high 8-bit portion of the data bus. This function is enabled when operating in 16-bit external bus mode, or when WR pin output is enabled.</li></ul>                                                                                                                                                                                     |

| 57          | P55/WRLX              | F            | P55 is a general-purpose I/O port. This function is enabled<br>when the WR pin 'output' setting is disabled.<br>WRLX is the write strobe signal output pin for the low 8-bit<br>portion of the data bus. This function is enabled when WR pin<br>output is enabled.                                                                                                                                                                                                                                                                                  |

| 58          | P56/RDX               | F            | P56 is not available for use as a general-purpose port.<br>RDX is the read strobe output signal for the data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 59          | P57/ASR3/INT3         | F            | <ul> <li>P57 is a general-purpose I/O port.</li> <li>ASR3 is the data input pin for input capture #3. This function is used for input at all times when input capture #3 is enabled for input, and therefore I/O access from other functions should not be attempted unless intended.</li> <li>INT3 is the data input pin for external interrupt #3. This function is used for input at all times when external interrupt #3 is enabled for input, and therefore I/O access from other functions should not be attempted unless intended.</li> </ul> |

| 60          | RSTX                  | В            | External reset request input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 61          | VSS                   | Power supply | Digital circuit ground level pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

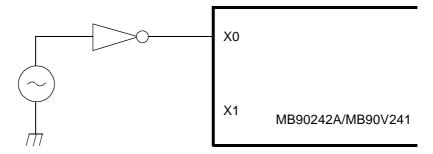

| 62<br>63    | X0<br>X1              | А            | Crystal oscillator signal pins (32 MHz).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 64          | VCC                   | Power supply | Digital circuit power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

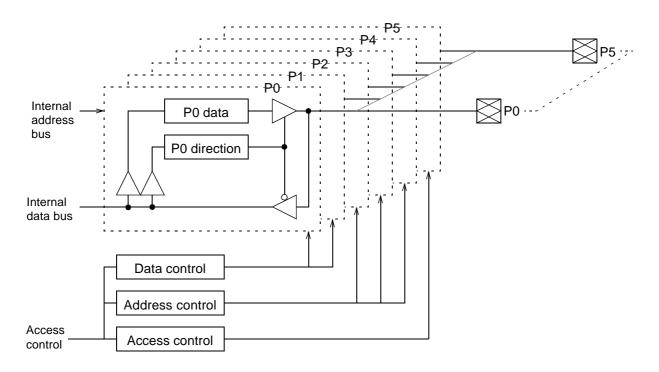

| 65 to<br>72 | P00/D00 to<br>P07/D07 | Е            | P00 to P07 are not available for use as general-purpose ports.<br>D00 to D07 are I/O pins for the lower 8 bits of the external<br>data bus.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 73 to<br>80 | P10/D08 to<br>P07/D15 | E            | <ul><li>P10 to P17 are general-purpose I/O ports. This function is enabled when in 8-bit external bus mode.</li><li>D08 to D15 are I/O pins for the upper 8 bits of the external data bus. This function is enabled when in 16-bit external bus mode.</li></ul>                                                                                                                                                                                                                                                                                      |

Table 1.6 Pin Description (Continued)

| Pin No. | Name         | Circuit type | Function                                                                                                       |

|---------|--------------|--------------|----------------------------------------------------------------------------------------------------------------|

| -       | A15P to A00P | F            | Piggyback address pins. ROM connected to these pins is treated as having equivalent operation to internal ROM. |

| -       | D15P to D00P | F            | Piggyback address pins. ROM connected to these pins is treated as having equivalent operation to internal ROM. |

| -       | CE, OE, PGM  | F            | Piggyback address pins. Connect to pins corresponding to ROM.                                                  |

Table 1.6 Pin Description (Continued)

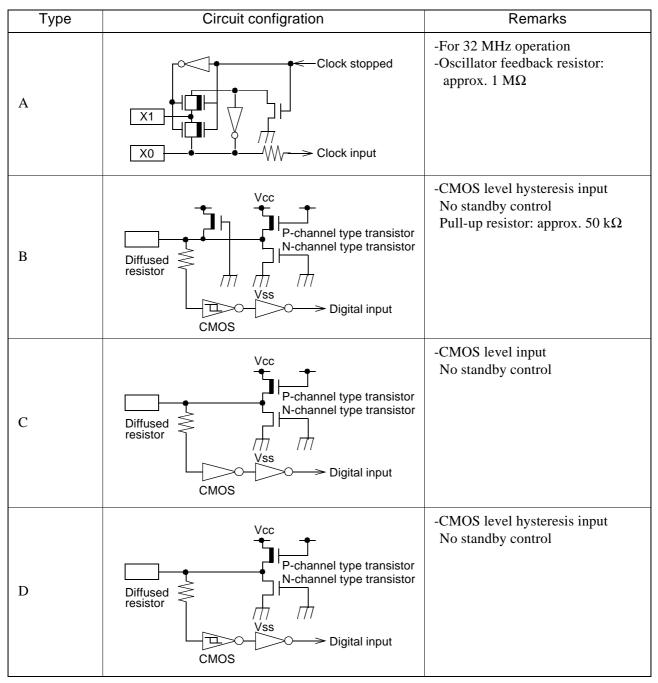

#### Table 1.6.1 Input/Output Circuit Configurations (1)

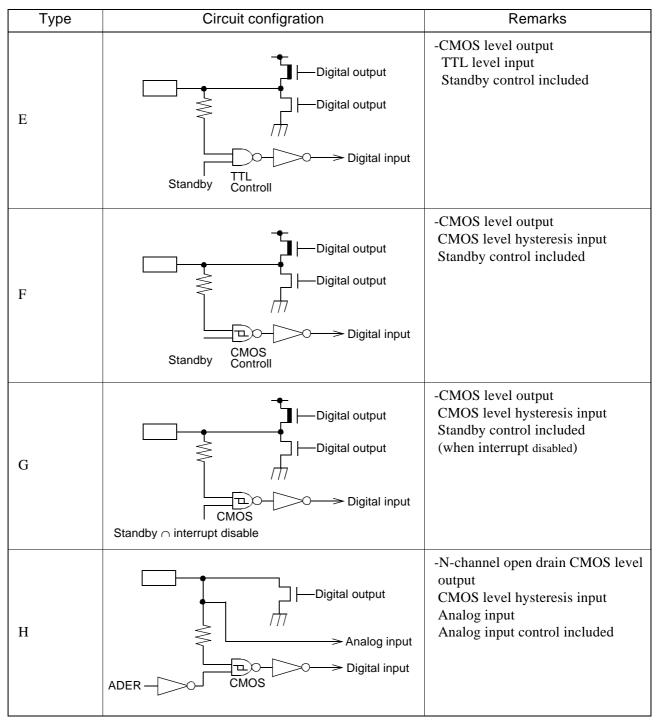

Table 1.6.1 Input/Output Circuit Configurations (2)

| Туре | Circuit configration                                                                                 | Remarks                                                                                        |

|------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Ι    | Digital output     Digital output     Digital output     Analog output     CMOS     Standby Controll | -CMOS level output<br>Analog output<br>CMOS level hysteresis input<br>Standby control included |

# Table 1.6.1 Input/Output Circuit Configurations (3)

# 1.7 Handling of Semiconductor Devices

#### (1) Preventing Latch-Up

A phenomenon called latch-up may occur on CMOS IC devices if voltage higher than Vcc or lower than Vss is applied to input and output pins, or if voltage exceeding the rated voltage is applied between Vcc and Vss. When latch-up occurs, supply current levels increase rapidly and can result in thermal damage to semiconductor elements. Sufficient care must be taken to avoid exceeding maximum rated values.

For the same reason, care must be taken to ensure that analog power supply levels do not exceed the level of the digital power supply.

#### (2) Handling Unused Input Pins

Unused input pins can cause devices to malfunction if left open, and should therefore be pulled up or down as needed.

#### (3) Precautions for Use of External Clock

When an external clock is used, the signal should drive the X0 pin only, the X1 pin should be left open.

Figure 1.7.1 shows an example of an external clock connection.

Fig. 1.7.1 Example: Use of an External Clock

#### (4) Power Supply Pins

When there are multiple Vcc or Vss pins, semiconductor device design requires that in order to prevent malfunctions such as latch-up, all internal elements of equivalent potential be connected. Also, to prevent abnormal strobe signal operation due to unwanted lowering of emission or increases in ground level, and to maintain standards for total output current, all elements must be connected to external power supplies and grounds.

In addition it is recommended that Vcc and Vss of this device be connected with as little impedance as possible from the current supply source.

It is further recommended that an approx.  $0.1 \ \mu$ F ceramic capacitor be placed near the device and connected between the Vcc and Vss terminals as a bypass capacitor.

#### (5) Crystal Oscillator Circuits

Noise in the vicinity of the X0 and X1 pins can be a cause of abnormal operation in this device. Designers should ensure that the X0 and X1 pins, and the crystal (or ceramic) oscillators as well as the bypass capacitor to ground be placed as close together as possible, and that PC board wiring layouts provide as little interference as possible from other wiring.

Also, PC board artwork can contribute toward stable of operation by surrounding the X0 and X1 pins with ground. This is strongly recommended.

(6) CLK Signal Pin

\* In external bus mode, the CLK output from the P50/CLK pin is selected as the initial value.

#### (7) HSTX pin

Make the HSTX pin high upon power-up. If the HSTX pin is used as low level, make the RSTX pin high.

# Chapter 2: Hardware Configuration

# 2.1 CPU

The F<sup>2</sup>MC-16F CPU core is a high-performance 16-bit CPU designed for applications requiring highspeed, real-time processing such as industrial applications, office automation (OA) products, and automotive devices. The F<sup>2</sup>MC-16F instruction set is designed to be optimized for controller applications, and can handle a wide variety of control functions with high speed and high efficiency. In addition, while the F<sup>2</sup>MC-16F core is designed as a 16-bit data processing CPU, an on-chip 32-bit accumulator is included for handling of 32-bit data. This enables a number of instructions to include 32-bit data processing capability. Memory space can be expanded to a maximum of 16 Mbytes, and can be accessed by either the linear pointer or bank access method. The instruction set, based on F<sup>2</sup>MC-16 architecture, has been enhanced with additional instructions for high level languages, expanded addressing mode and additional coded multiplication and division instructions. The F<sup>2</sup>MC-16F is upwardly compatible with F<sup>2</sup>MC-16 CPUs at object code level.

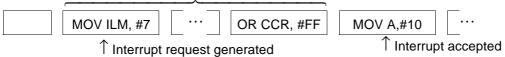

The principal features of the F<sup>2</sup>MC-16F CPU are:

- Instruction set adapted for high level language (C) and multitasking

- System stack pointer Wide variety of pointers High-symmetry instruction set Barrel shift instructions Stack check function

- Improved execution speed

.....Instruction operations revised for higher speed

2.1 CPU

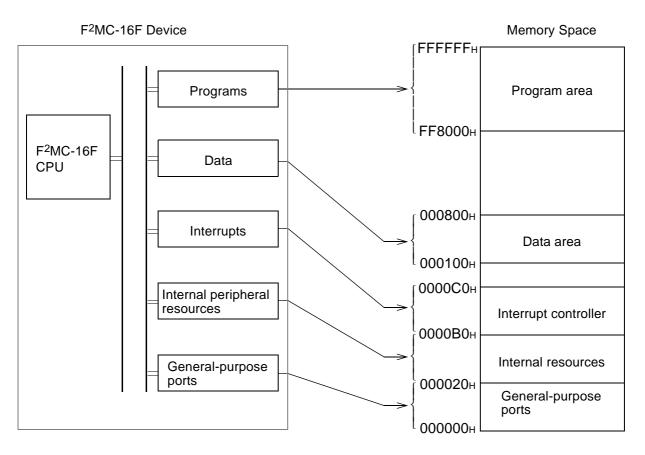

#### 2.1.1 Memory Space

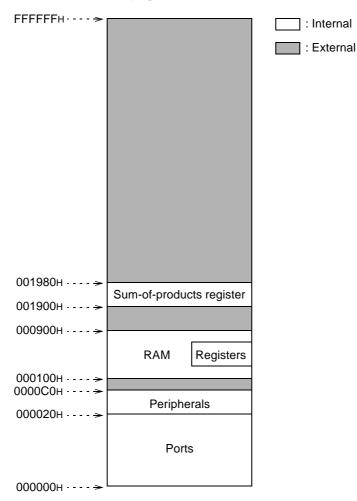

All data, programs and internal resources controlled by the  $F^2MC-16F$  CPU are stored in the chip's memory area of 16 Mbytes. The CPU is able to access each address in memory as well as each internal resource through the 24-bit address bus (Figure 2.1.1).

For memory space allocation on the MB90242A series, see Section 2.2, "Map."

Fig. 2.1.1 Memory Map in Relation to F<sup>2</sup>MC-16F Device

#### Types of Addressing

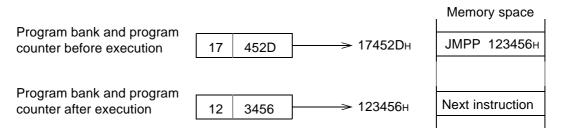

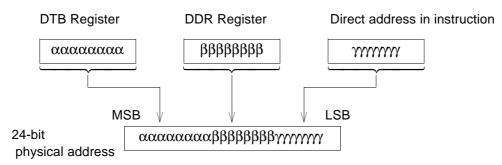

The F<sup>2</sup>MC-16F CPU uses two main methods to generate addresses. In linear addressing, a instruction designates one entire 24-bit address, and in bank addressing, the upper 8 bits of the address designate a bank register for a specific purpose, and the lower 16 bits are used as the addressing operand.

#### Linear Addressing

Two types of linear addressing are used, including direct designation of a 24-bit address as operand, as well as use of the lower 24 bits of a 32-bit general-purpose register or accumulator (Figure 2.1.2).

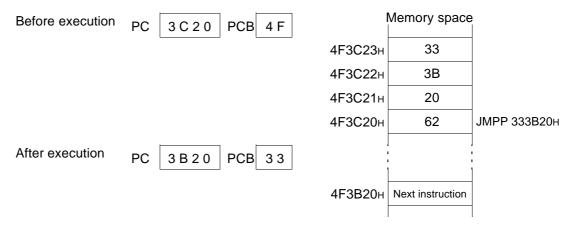

Example 1. Linear Addressing: Designation of 24-bit Operand

<u>JMPP 123456н</u> (Instruction branches to address designated by operand.)

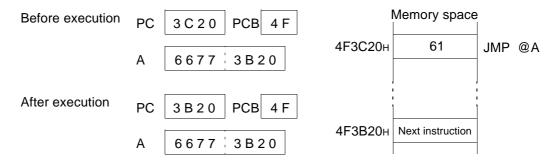

Example 2. Linear Addressing: Indirect Designation Through 32-Bit Register

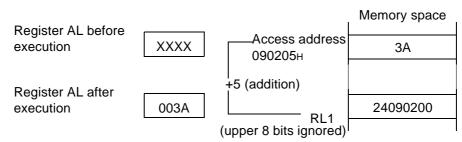

MOV A@RL1+5 (Instruction reads byte-length results of lower 24-bits from RL1 plus 8-bit offset, and stores results in AL.)

Fig. 2.1.2 Sample Linear Address Designation

#### Bank Addressing

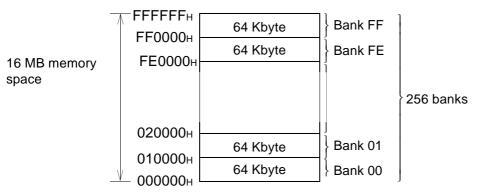

In bank addressing the 16 Mbytes of memory space is divided into 256 banks of 64 Kbytes each, with bank addresses designated by bank registers. Figure 2.1.3 illustrates the division of the 16 MB memory space into 256 banks.

#### Fig. 2.1.3 Schematic Representation of Banks

There are five types of bank registers. Table 2.1.1 lists bank registers, the space accessed by each register, and principal uses.

| Bank register                       | Space name               | Principal uses                                                                                                                                                 | Initial value<br>at reset |

|-------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Program bank register<br>(PCB)      | Program (PC) space       | Storage of instruction codes, vector tables, and immediate data                                                                                                | FFн                       |

| Data bank register (DTB)            | Data (DT) space          | Storage of readable/writable data,<br>access to internal and external periph-<br>eral resource control registers and data<br>registers                         | 00н                       |

| User stack bank register<br>(USB)   | Stack (SP) register      | Area used for stack access to registers<br>for saving PUSH/POP instructions and<br>interrupt instructions etc. SSB is used<br>when CCR S=1, USB used when S=0. | 00н                       |

| System stack bank register<br>(SSB) | Stack (SI ) register     |                                                                                                                                                                | 00н                       |

| Additional bank register<br>(ADB)   | Additional (AD)<br>space | Storage of data overflow from data (DT) space                                                                                                                  | 00н                       |

Table 2.1.1 Spaces Accessed by Bank Registers

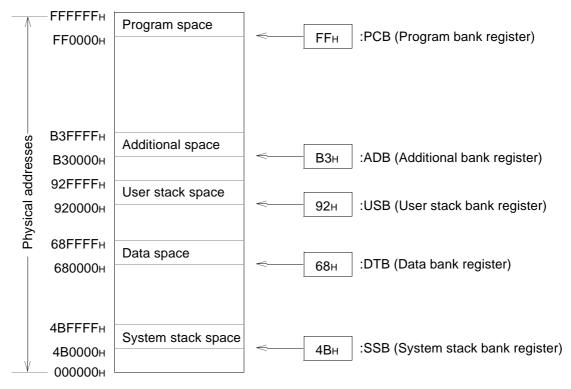

After reset, DT, SP and AD spaces are located in bank 00 (000000H - 00FFFFH), and PC space is located in bank FF (FF0000H - FFFFFFH).

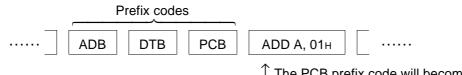

In order to improve coding efficiency, each instruction has defined default spaces for each type of addressing as shown in Table 2.1.2. To use a space other than its default space in any addressing mode, a prefix code corresponding to the desired bank is designated ahead of the instruction to allow access to the bank space designated by that prefix code.

| Default space    | Addressing method                                           |  |  |

|------------------|-------------------------------------------------------------|--|--|

| Program space    | PC indirect, program access, branching                      |  |  |

| Data space       | @A, addr16, dir, addressing using @RW0, @RW1, @RW4 and @RW5 |  |  |

| Stack space      | Addressing using PUSHW, POPW, @RW3, @RW7                    |  |  |

| Additional space | Addressing using @RW2, @RW6                                 |  |  |

Table 2.1.2 Default Spaces

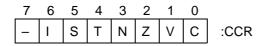

Figure 2.1.4 shows an example of memory space divided into banks, and the corresponding register bank settings.

Fig. 2.1.4 Example: Bank Space Settings and Physical Addresses

Memory Space Allocation with Multi-Byte Data Lengths

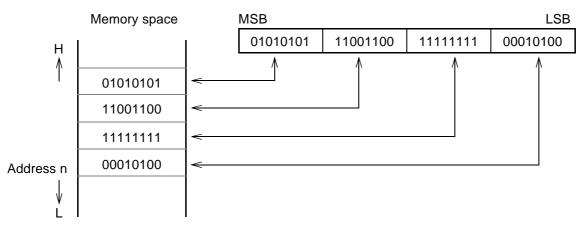

Figure 2.1.5 shows the configuration of data in memory when multi-byte data lengths are used. Data is positioned with the lowest 8 bits at address n, and each subsequent 8 bits at address n+1, n+2, n+3, ...

#### Fig. 2.1.5 Example: Memory Space Allocation with Multi-Byte Data Lengths

Writing to memory is executed starting with the lowest addresses first. For 32-bit data, the lower 16 bits are transferred first, followed by the upper 16 bits.

**[CAUTION]** If a reset signal is applied immediately after the lower 16 bits are written, the upper 16 bits may not be written to memory.

Access to Multi-Byte Data

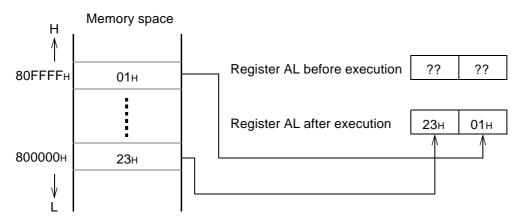

All accesses are based on bank units, so that for instructions accessing multi-byte data at address FFFFH, the next byte will be located within the same bank at address 0000H. Figure 2.1.6 shows an example of instruction of access to multi-byte data.

#### Fig. 2.1.6 Execution of Instruction MOVPW A, 080FFFFH

#### 2.1.2 Registers

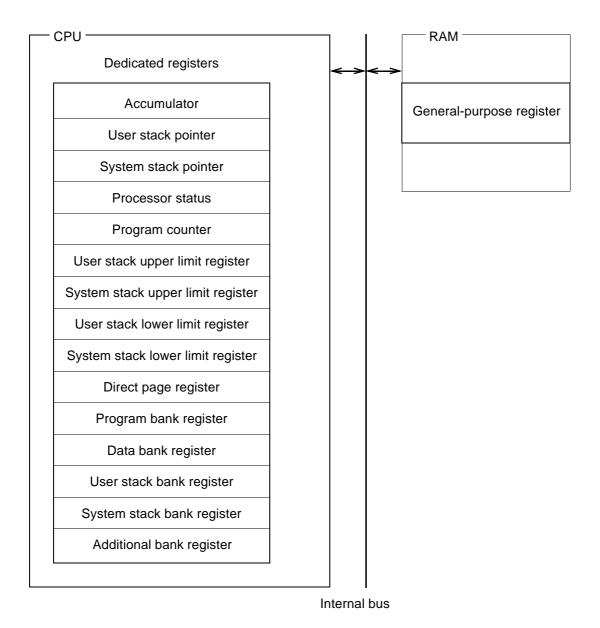

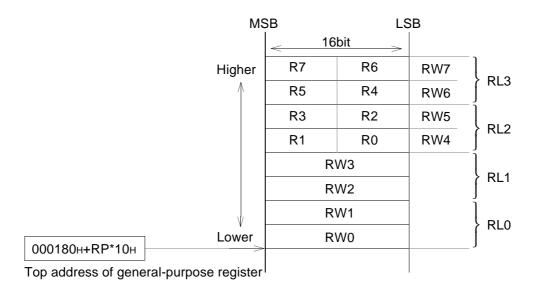

$F^2MC-16F$  registers are broadly divided into internal dedicated registers on CPU and general-purpose registers in internal RAM. The dedicated registers are dedicated hardware located inside the CPU, and their use is limited by the architecture of the CPU itself. In contrast, the general-purpose registers coexist within RAM in CPU address space, and are similar to the dedicated registers in that they may be accessed without designation of addresses, but differ in that they may be used for user-defined purposes in the same way as ordinary memory. Figure 2.1.7 shows the arrangement of dedicated registers and general-purpose registers within the  $F^2MC-16F$  device.

Fig. 2.1.7 Dedicated Registers and General-Purpose Registers

#### Dedicated Registers

Figure 2.1.8 lists the 15 dedicated registers in the F<sup>2</sup>MC-16F CPU.

| Configuration | Register name                        | Function                                                                                                          |

|---------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| AH AL         | Accumulator                          | Two 16-bit registers used to store results of calculation, etc. May be concatenated for use as a 32-bit register. |

| USP           | User stack pointer                   | 16-bit pointer indicating the user stack area                                                                     |

| SSP           | System stack pointer                 | 16-bit pointer indicating the system stack area                                                                   |

| PS            | Processor status                     | 16-bit register indicating system status                                                                          |

| PC            | Program counter                      | 16-bit register with the address where the program is stored                                                      |

| USPCU         | User stack upper<br>limit register   | 16-bit register designating the upper limit of the user stack                                                     |

| SSPCU         | System stack<br>upper limit register | 16-bit register designating the upper limit of the system stack                                                   |

| USPCL         | User stack lower<br>limit register   | 16-bit register designating the lower limit of the user stack                                                     |

| SSPCL         | System stack<br>lower limit register | 16-bit register designating the lower limit of the system stack                                                   |

| DPR           | Direct page register                 | 8-bit register indicating the direct page                                                                         |

| PCB           | Program bank reg-<br>ister           | 8-bit register indicating program space                                                                           |

| DTB           | Data bank register                   | 8-bit register indicating the data space                                                                          |

| USB           | User stack bank<br>register          | 8-bit register indicating the user stack space                                                                    |

| SSB           | System stack bank<br>register        | 8-bit register indicating system stack space                                                                      |

| ADB           | Additional bank<br>register          | 8-bit register indicating additional space                                                                        |

# Fig. 2.1.8 Dedicated Registers

#### Accumulator (A)

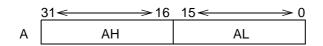

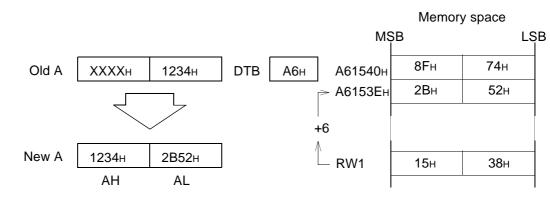

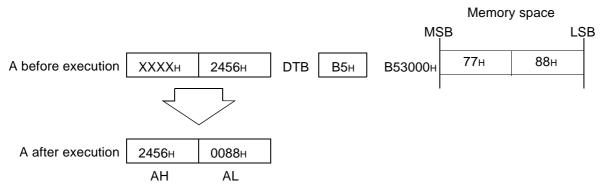

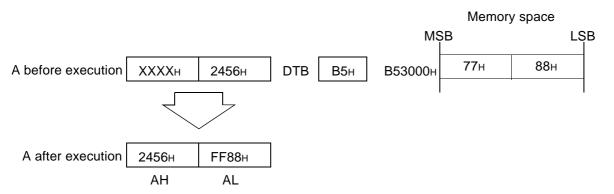

The accumulator (A) consists of two 16-bit registers for arithmetic operation, labeled AH and AL, used to hold the results of calculations, and also used as temporary memory for data transfers. Figure 2.1.9 shows the configuration of the accumulator. The AH and AL registers can be linked for 32-bit data processing, and only the AL register is used for processing of data in 16-bit word units or 8-bit byte units.

Data stored in the accumulator may be used for calculations involving data in memory/registers (Ri, RWi, RLi). As with the F<sup>2</sup>MC-8/16/16H CPU, the F<sup>2</sup>MC-16F is designed so that when data of word length or less is transferred to the AL register, the previous contents (immediately before transfer) of the AL register are automatically transferred to the AH register. This is called the data preservation function, and increases efficiency by enabling various types of processing using calculations from the contents of the AL and AH registers.

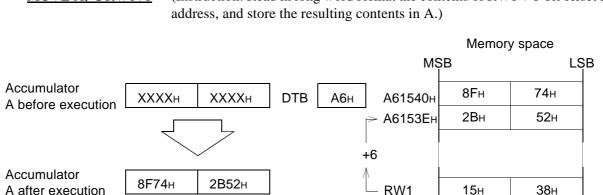

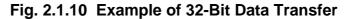

Figure 2.1.10 shows an example of 32-bit data transfer, and Figure 2.1.11 shows an example of data transfer between the AL and AH registers.

AH

#### Fig. 2.1.9 Accumulator (A) Configuration

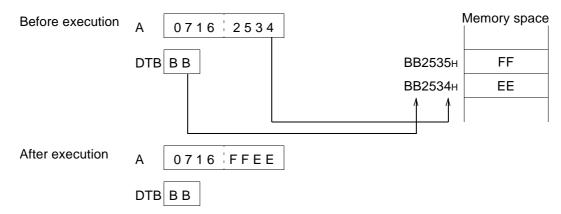

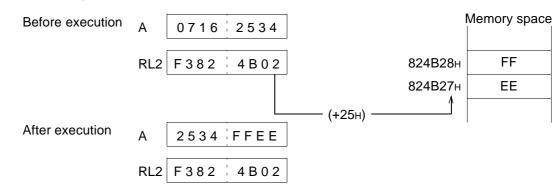

$\underline{MOVL A, @RW1+6} \qquad (Instruction: Read in long word format the contents of RW1 + 8-bit offset as an$

AL

<u>MOVW A, @RW1+6</u> (Instruction: Read in word format the contents of RW1 + 8-bit offset, and store the resulting contents in A.)

Fig. 2.1.11 Example of AL - AH Transfer

When transferring byte-length or shorter data to register AL, the data is given a coded extension or zero extension and stored in AL in 16-bit length. Also, data in the AL register can be handled in either word length or byte length. When an arithmetic calculation instruction is performed on the contents of AL in byte processing, the upper 8 bits of the value of AL before processing are ignored and the upper 8 bits in the result will all be set to zero.

MOV A, 3000H (Instruction: Extend the contents of address 3000H with zeros, and store the results in AL.)

#### Fig. 2.1.12 Example of Zero Extension

MOVX A, 3000<sub>H</sub> (Instruction: Extend the contents of address 3000<sub>H</sub> with coding, and store the results in AL.)

Fig. 2.1.13 Example of Coded Extension

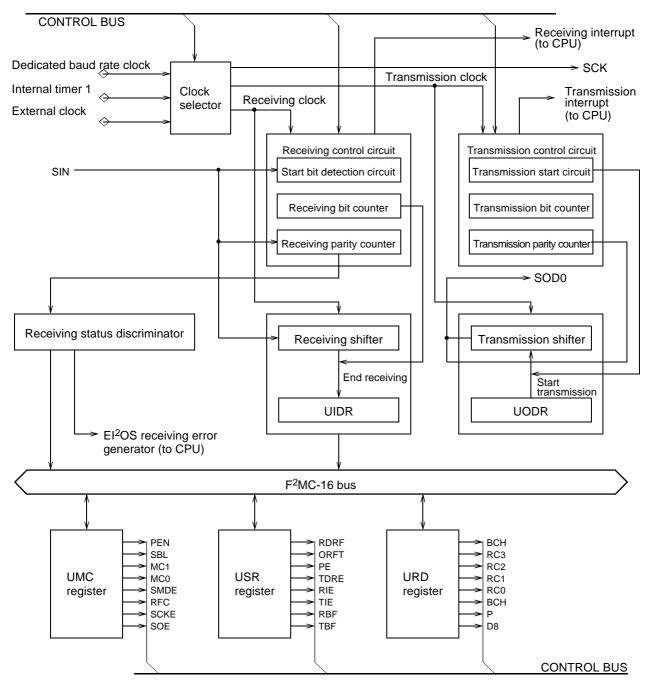

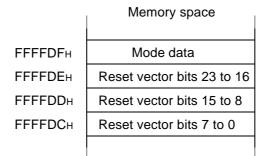

30