**Developer Note**

# Power Mac G4 Computer

Technical Publications © Apple Computer, Inc. 1999  Apple Computer, Inc.

© 1999 Apple Computer, Inc. All rights reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, mechanical, electronic, photocopying, recording, or otherwise, without prior written permission of Apple Computer, Inc., except to make a backup copy of any documentation provided on CD-ROM.

The Apple logo is a trademark of Apple Computer, Inc. Use of the "keyboard" Apple logo (Option-Shift-K) for commercial purposes without the prior written consent of Apple may constitute trademark infringement and unfair competition in violation of federal and state laws.

No licenses, express or implied, are granted with respect to any of the technology described in this book. Apple retains all intellectual property rights associated with the technology described in this book. This book is intended to assist application developers to develop applications only for Apple-labeled or Apple-licensed computers.

Every effort has been made to ensure that the information in this manual is accurate. Apple is not responsible for typographical errors.

Apple Computer, Inc. 1 Infinite Loop Cupertino, CA 95014 408-996-1010

Apple, the Apple logo, FireWire, iMac, Mac, Macintosh, and Power Macintosh are trademarks of Apple Computer, Inc., registered in the United States and other countries.

AirPort and Power Mac are trademarks of Apple Computer, Inc. Adobe is a trademark of Adobe Systems Incorporated or its subsidiaries and may be registered in certain jurisdictions. Helvetica and Palatino are registered trademarks of Heidelberger Druckmaschinen AG, available from Linotype Library GmbH.

ITC Zapf Dingbats is a registered trademark of International Typeface Corporation.

OpenGL is a registered trademark of Silicon Graphics, Inc.

PowerPC is a trademark of International Business Machines Corporation, used under license therefrom.

Simultaneously published in the United States and Canada. Even though Apple has reviewed this manual, APPLE MAKES NO WARRANTY OR REPRESENTATION, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL, ITS QUALITY, ACCURACY, MERCHANTABILITY, OR FITNESS FOR A PARTICULAR PURPOSE. AS A RESULT, THIS MANUAL IS SOLD "AS IS," AND YOU, THE PURCHASER, ARE ASSUMING THE ENTIRE RISK AS TO ITS QUALITY AND ACCURACY.

IN NO EVENT WILL APPLE BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT OR INACCURACY IN THIS MANUAL, even if advised of the possibility of such damages.

THE WARRANTY AND REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND IN LIEU OF ALL OTHERS, ORAL OR WRITTEN, EXPRESS OR IMPLIED. No Apple dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which vary from state to state.

# Contents

Figures and Tables 9

About This Note Preface 11 Topics Described in This Note 11 Supplemental Reference Documents 12 **3D Graphics** 12 12 **RAM Expansion Modules** PowerPC G4 Microprocessor 13 AltiVec 13 Mac OS 9 13 **Open Firmware** 14 PCI Cards 15 ATA Devices 15 **USB** Interface 15 **FireWire Interface** 16 Introduction Chapter 1 17 Hardware Features 18 Features of the Enclosure 20 21 **Compatibility Issues** 21 Software Issues System Software 21 **Machine Identification 21 Booting From External Drives 21** 22 **Expansion Issues Internal Storage Devices 22 RAM Expansion 22**

No L2 Cache Expansion 22

Proprietary Modem Slot 22

Digital A/V Connections 23

AC Power Issues 23

Line Voltage Switch 23 Monitor Power Socket 23 Legacy I/O Issues 23 No SCSI Ports 24 No LocalTalk Serial Ports 24 No ADB or Serial Ports 24

Chapter 2 Architecture 25

**Block Diagram and Buses** 26 **Processor Module** 28 PowerPC G4 Microprocessor 28 Level2 Cache 29 Uni-N Bridge and Memory Controller 29 **Processor Bus** 29 Main Memory Bus 30 **Accelerated Graphics Port Bus** 30 PCI Buses and Bridge 31 Boot ROM 31 **Ethernet Controller** 31 **FireWire Controller** 32 KeyLargo I/O Controller 32 32 **DMA Support Interrupt Support** 33 **USB** Interface 33 Ultra DMA/66 Interface 33 Enhanced IDE Interface 34 Modem Slot Support 34 Wireless LAN Module 34 Sound IC Support 34 **Power Controller** 35 AGP Graphics Card 35 **Graphics Controller IC** 36 **Display Memory** 37

#### Chapter 3 Input and Output Devices 39

**USB** Ports 40 **USB** Connectors 40 **USB** Features 41 Power Off During Sleep 41 **USB Storage Devices 42 USB** Compatibility Issues 42 ADB Compatibility 42 Serial Port Compatibility 43 Not for Networking 43 **FireWire Ports** 43 **FireWire Connector** 44 Ethernet Port 45 46 **Disk Drives** Ultra DMA/66 Hard Disk 47 **DVD-ROM Drive** 47 **Optional DVD-RAM Drive** 48 **ATAPI** Zip Drive 48 Optional Ultra2 SCSI (LVD) Drive 49 Internal Modem 49 AirPort Card Wireless LAN Module 50 50 Data Security Hardware Components 50 Software Components 51 Keyboard 52 **Keyboard Layout** 52 Keyboard and USB 53 Mouse 53 Sound System 53 Sound Output 54 Sound Input 54 **Digitizing Sound** 55 Video Monitor Ports 55 Digital Monitor Connector 55 **Digital Display Resolutions** 57 Analog Monitor Connector 57 Monitor Adapter 58

Analog Display Resolutions 58

#### Chapter 4 Expansion 61

RAM Expansion62DIMM Specifications62Mechanical Specifications62Electrical Specifications63DIMM Configurations63RAM Addressing65PCI Expansion Slots66

#### Chapter 5 Software 67

68 ROM in RAM Aspects of the New Approach 68 **RAM Footprint 68** Startup Disk Control Panel 69 Data Structures and Files 69 Memory Mapping 69 **Boot Process** 70 **Boot ROM Contents** 71 Hardware Initialization Code 71 **Open Firmware** 72 Interrupts 72 Mac OS ROM Image File 72 73 System Software Modifications **Computer Identification** 73 **Power Manager** 74 Suspend and Resume 75 76 ATA Manager 4.0 **USB** Drivers 76 Other New Drivers 77 77 Legacy Drivers Floppy Disk Legacy 78 ADB Legacy 78

SCSI Legacy 78 AltiVec Acceleration and Support 78

Appendix A Conventions and Abbreviations 81

Typographical Conventions 81 Abbreviations 81

Index 85

# **Figures and Tables**

| Chapter 2 | Architecture                                                                            | 25                                                                                                                                                                                                                                                               |

|-----------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Figure 2-1                                                                              | Simplified block diagram 27                                                                                                                                                                                                                                      |

| Chapter 3 | Input and Outp                                                                          | ut Devices 39                                                                                                                                                                                                                                                    |

|           | Figure 3-1<br>Figure 3-2<br>Figure 3-3<br>Figure 3-4<br>Figure 3-5                      | USB connector 40<br>FireWire connector 44<br>ANSI keyboard layout 52<br>Digital monitor connector 56<br>Analog monitor connector 57                                                                                                                              |

|           | Table 3-1<br>Table 3-2<br>Table 3-3<br>Table 3-4<br>Table 3-5<br>Table 3-6<br>Table 3-7 | Pin assignments on the USB connector41Pin assignments on the FireWire connector44Signals on the Ethernet connector46Signals on the digital monitor connector56Digital display resolutions57Signals on the analog monitor connector57Analog display resolutions59 |

| Chapter 4 | Expansion 6<br>Table 4-1<br>Table 4-2                                                   | Sizes of RAM expansion devices and modules 64<br>Address multiplexing modes for SDRAM DIMMs 65                                                                                                                                                                   |

# About This Note

This developer note describes the Power Mac<sup>®</sup> G4 computer. The note provides information about the features of the computer, the logic board architecture and expansion capabilities, and issues affecting compatibility.

This developer note is intended to help hardware and software developers design products that are compatible with the Macintosh products described here. If you are not already familiar with Macintosh computers or if you would simply like additional technical information, you may wish to read the related technical manuals listed in the section "Supplemental Reference Documents."

## Topics Described in This Note

The information is arranged in five chapters, an appendix, and an index:

- Chapter 1, "Introduction," gives a summary of the features of the Power Mac G4 computer, describes the physical appearance of the enclosure, and lists the available configurations and options. This chapter also includes a section describing compatibility issues that developers need to be aware of to take advantage of the features available with the Power Mac G4 computer.

- Chapter 2, "Architecture," describes the internal organization of the Power Mac G4 computer. It includes a functional block diagram and descriptions of the main components on the logic board.

- Chapter 3, "Input and Output Devices," describes the built-in input/output (I/O) devices and the external I/O ports.

- Chapter 4, "Expansion," describes the expansion slots on the logic board and provides descriptions of the expansion modules.

- Chapter 5, "Software," describes the system software that comes with the computer, with emphasis on the Open Firmware features and the software support for the new hardware features.

- Appendix A, "Conventions and Abbreviations," describes the typographical conventions and lists the abbreviations used in this note.

## Supplemental Reference Documents

For more information about the technologies mentioned in this developer note, you may wish to consult some of the references listed in the following sections.

You should also have copies of the relevant books describing the system software for Macintosh computers available in technical bookstores and on the World Wide Web at

http://developer.apple.com/techpubs/mac/mac.html

#### **3D Graphics**

Developers of 3D graphics for games should know about OpenGL<sup>®</sup> for Macintosh<sup>®</sup>, a new version of SGI's application programming interface (API) and software library for 3D graphics.

Information is available on the World Wide Web at

http://www.apple.com/opengl

Developer support and documentation is available at

http://developer.apple.com/opengl/

If you are interested in taking advantage of the 3D graphics acceleration features available on the graphics card, you should have *3D Graphics Programming With QuickDraw 3D.* The current documentation for QuickDraw 3D is part of the QuickTime documentation and is available on the World Wide Web at

http://developer.apple.com/techpubs/quicktime/qtdevdocs/QD3D/ qd3d\_book.htm

#### **RAM Expansion Modules**

The Power Mac G4 computer uses PC100 compliant, 168-pin SDRAM DIMMs. The mechanical characteristics of the DIMM are given in the JEDEC specification for the 168-pin 8-byte DRAM DIMM. The specification number is JEDEC MO-161; the specification is available from the Electronics Industry Association's website at

#### PREFACE

http://www.jedec.org/download/freestd/pub95/mo161C.pdf

The electrical characteristics of the DIMM are given in section 4.5.6 of the JEDEC Standard 21-C, release 7. The specification is available from the Electronics Industry Association's website at

http://www.jedec.org/download/freestd/pub21/

The RAM DIMMs are required to be PC100 compliant. The PC100 specification is available from Intel's website at

http://developer.intel.com/design/chipsets/memory/sdram.htm#S1

#### PowerPC G4 Microprocessor

Information about the PowerPC  $^{^{\rm TM}}$  G4 microprocessor used in the Power Mac G4 computer is available on the World Wide Web at

http://www.mot.com/SPS/PowerPC/index.html

#### AltiVec

AltiVec Technology Programming Environments Manual (AltiVec PEM) is a reference guide for programmers. It contains a description for each instruction and information to help in understanding how the instruction works. You can ontain a copy of the AltiVec PEM through the Motorola AltiVec site on the World Wide Web, at

http://www.mot.com/SPS/PowerPC/AltiVec/facts.html

Apple provides support for developers who are starting to use the AltiVec technology. Documentation, development tools, and sample code are now available on the World Wide Web, at

http://developer.apple.com/hardware/altivec/index.html

#### Mac OS 9

For a description of the version of the Mac OS that comes with the new models, you should refer to the technote for Mac OS 9. Other technotes contain information about the NewWorld software architecture and the API changes for Power Manager 2.0 referred to in Chapter 5, "Software." The technotes are available on the Technote website at

http://developer.apple.com/technotes/

You should also have copies of the relevant books describing the system software for Macintosh computers available in technical bookstores and on the World Wide Web at

http://developer.apple.com/techpubs/mac/mac.html

#### **Open Firmware**

The NewWorld software architecture implemented on the Power Mac G4 computer follows some of the standards defined by the Open Firmware IEEE 1274-1994 specification and the CHRP binding.

The primary Open Firmware reference is the *IEEE 1275-1994 Standard for Boot* (*Initialization, Configuration*) *Firmware: Core Requirements and Practices.* You can order that document electronically from the IEEE Standards Department website at

http://standards.ieee.org/catalog/bus.html

or you can order it by mail from

IEEE Standards Department 445 Hoes Lane, P. O. Box 1331 Piscataway, NJ 08855-1331 Telephone 800-678-4333 (US), 908-562-5432 (International)

The basis for the bootinfo file format and use is described in the document *PowerPC Microprocessor Common Hardware Reference Platform (CHRP) System Binding to: IEEE Std 1275-1994 Standard for Boot (Initialization, Configuration) Firmware.* A bootinfo file contains Open Firmware script, a description, information for individual operating systems, icons, along with other information.

An introduction to Open Firmware as used with PCI expansion cards on the Macintosh computer is given in *Designing PCI Cards and Drivers for Power Macintosh Computers*.

Three technotes provide additional information about Open Firmware on the Macintosh computer. They are

TN 1061: Open Firmware, Part I, which introduces Forth programming, describes a typical device tree, and outlines a technique for debugging Open Firmware drivers. It is available on the Technote website at http://developer.apple.com/technotes/tn/tn1061.html

- TN 1062: Open Firmware, Part II, which describes the contents of an expansion ROM for Open Firmware and lists properties common to all device types. It is available on the Technote website at http://developer.apple.com/technotes/tn/tn1062.html

- TN 1044: Open Firmware, Part III, which describes a typical device tree. It is available on the Technote website at: http://developer.apple.com/technotes/tn/tn1044.html

Additional information about Open Firmware is provided at Apple's developer Q&A site

http://developer.apple.com/qa/hw/hw-1.html

## **PCI** Cards

For information about PCI expansion cards, refer to *Designing PCI Cards and Drivers for Power Macintosh Computers.* The Power Mac G4 computer supports version 2.1 of the PCI standard.

## **ATA Devices**

For the latest information about the system software for ATA devices such as the IDE drive, see *ATA Device Software for Macintosh Computers.* That book is available on the reference library issue of the developer CD (June, 1999) and on the World Wide Web at

http://developer.apple.com/techpubs/hardware/DeviceManagers/ata/ ata\_ref/frameset.html

## **USB** Interface

For more information about USB on the Macintosh computer, you should refer to Apple Computer's *Mac OS USB DDK API Reference*. Information is also available on the World Wide Web, at:

http://developer.apple.com/techpubs/hardware/DeviceManagers/usb/usb.html

#### PREFACE

USB game controllers are supported by the InputSprocket component of the Apple Games Sprockets software architecture. InputSprocket software and information about the InputSprocket APIs can be found at

http://developer.apple.com/games/

For full specifications of the Universal Serial Bus, you should refer to the USB Implementation Forum on the World Wide Web, at:

http://www.usb.org/developers/index.html

#### **FireWire Interface**

For additional information about the FireWire IEEE 1394a interface and the Apple APIs for FireWire software, refer to the resources available on the Apple FireWire website at

http://www.apple.com/firewire/

The IEEE 1394a draft standard is available from the IEEE; you can order that document electronically from the IEEE Standards Department website at

http://standards.ieee.org/catalog/bus.html

You may also find useful information at the 1394 trade association's website at

http://www.1394ta.org/

#### CHAPTER 1

Introduction

The Power Mac G4 computer is a new Power Macintosh desktop computer using the PowerPC G4 microprocessor with a higher performance system bus and several improved I/O features. It is intended for use in content creation, desktop publishing, multimedia, and other activities that require high performance.

## Hardware Features

Here is a list of the hardware features of the Power Mac G4 computer. The major features are described more fully later in this note.

- Microprocessor: PowerPC G4 microprocessor running at a clock frequency of 350, 400, or 450 MHz depending on model and configuration. For more information, see "PowerPC G4 Microprocessor" (page 28).

- **Cache:** 1 MB of backside level 2 (L2) cache on the processor module. The cache runs at half the clock frequency of the microprocessor.

- Processor system bus: 64-bit wide data and 32-bit wide address, 100 MHz clock, supporting MaxBus protocol. For more information, see "Processor Bus" (page 29).

- RAM: Four DIMM slots for 168-pin PC100 DIMMs (dual inline memory modules) using SDRAM (synchronous dynamic access memory) or ESDRAM (enhanced SDRAM) devices. A minimum of 64 MB of RAM is installed in one of the slots. For more information, see "RAM Expansion" (page 62).

- ROM: NewWorld ROM-in-RAM implementation with 1 MB of boot ROM. For information about the ROM, see "Boot ROM" (page 31). For information about the ROM-in-RAM implementation, see "ROM in RAM" (page 68).

- Graphics acceleration: A graphics card in the AGP slot provides 2D and 3D hardware graphics acceleration using the ATI RAGE 128 PRO graphics controller. For more information, see "AGP Graphics Card" (page 35).

- Sound: Supports 16 bits/channel stereo input and output on built-in 3.5 mm line-level stereo input and output jacks, one built-in speaker. For more information, see "Sound System" (page 53).

- Hard disks: One internal Ultra DMA/66 hard disk; provision for adding either a second Ultra DMA/66 disk or an ATA-3 storage device. For more information, see "Disk Drives" (page 46).

- **Expansion bays:** Three expansion bays, one of which is occupied by an Ultra DMA/66 hard disk. Two bays are available for adding one internal 3.5 x 1-inch Ultra DMA/66 or two ATA-3 devices, or other devices connected to a PCI controller card. For more information, see "Disk Drives" (page 46).

- DVD-ROM drive: ATAPI DVD-ROM drive providing support for 24x-speed CD-ROM and 6x-speed DVD-ROM media, as well as DVD-Video playback with DVD MPEG2 decode in software.

- **DVD-RAM drive:** Optional ATAPI DVD-RAM drive reads and writes 2.6 GB and 5.2 GB DVD-RAM media in addition to supporting 2x-speed DVD-ROM, 20x CD-ROM, and DVD-Video playback with DVD MPEG2 decode in software.

- **Zip drive:** 100 MB ATAPI Zip drive.

- USB ports: Two USB ports, described in "USB Ports" (page 40). The computer comes with a USB mouse and a USB keyboard that has two additional USB ports.

- **Ethernet:** Built in Ethernet port for a 10Base-T or 100Base-TX operation with an RJ-45 connector. For more information, see "Ethernet Port" (page 45).

- Wireless LAN: An internal wireless LAN module is available as a build-to-order option or as a user-installable upgrade. For more information, see "AirPort Card Wireless LAN Module" (page 50).

- **FireWire ports:** Two external and one internal IEEE 1394a high-speed serial FireWire ports, which support transfer rates of 100, 200, and 400 Mbps. For more information, see "FireWire Ports" (page 43).

- Modem: Slot for an optional built-in Apple 56 Kbps modem. The modem supports K56flex and V.90 modem standards. For more information, see "Internal Modem" (page 49).

- **Keyboard:** Apple USB keyboard with function keys and inverted-T arrow keys. It is also a bus-powered USB hub with two USB ports. For more information, see "Keyboard" (page 52).

- **Mouse:** Apple USB mouse operating as a low-speed (1.5 Mbps) USB device. For more information, see "Mouse" (page 53).

- **PCI card expansion slots:** Three slots for 33 MHz, 64-bit or 32-bit, 12-inch PCI cards. For more information, see "PCI Expansion Slots" (page 66).

- AGP-2X graphics card slot: The computer is always shipped with an accelerated graphics card installed in this slot. For more information, see "AGP Graphics Card" (page 35).

- **Startup button:** Startup and sleep are controlled from the Apple USB keyboard and a front power button.

- Voltage switch: Can be set to either 115 for voltages of 100–130 V or 230 for voltages of 200–250 V, depending on the voltage where the computer is installed. The voltage selection must be set manually.

- **Fan speed control:** The speed of the fan is thermally controlled and is automatically set to the lowest possible speed to minimize noise. This is a function provided by the fan and is not under software control.

- **Energy saving:** Sleep, startup, and shutdown scheduling can be controlled with an Energy Saver control panel.

## Features of the Enclosure

The Power Mac G4 computer's enclosure is a mini-tower design with opaque side panels and transparent handles.

The front of the Power Mac G4 computer's enclosure has the slots for the DVD-ROM or DVD-RAM drive and the optional Zip drive, the power button, the reset button, the NMI button, and the power-on light.

The back panel includes the A/C power socket, the monitor power socket, the I/O ports, and the openings for PCI cards.

The user can get access to the main logic board to add memory or PCI cards by opening the case and swinging the door down.

An internal 56 Kbps modem card can be installed as an option at the time of purchase. The modem is compatible with V.34 and V.90 protocols.

# **Compatibility Issues**

The Power Mac G4 computer incorporates several changes from earlier models. This section describes key issues you should be aware of to ensure that your hardware and software work properly.

#### Software Issues

Like other recent Macintosh computers, the Power Mac G4 computer uses the RAM-in-ROM approach with Open Firmware booting. Software developers should follow the recommended practices for the new approach.

#### System Software

The system software that comes with the Power Mac G4 computer is Mac OS 9 with extensions and control panels required for product-specific features. Features specific to the Power Mac G4 computer are described in "Mac OS ROM Image File" (page 72). For a general description of the Mac OS 9 release, refer to the Technote for Mac OS 9. The technote is available on the Technote website at

http://developer.apple.com/technotes/

#### Machine Identification

With the RAM-in-ROM system software, it is no longer possible to use the box flag to identify the computer model. For guidelines about machine identification, see "Computer Identification" (page 73).

#### **Booting From External Drives**

The Power Mac G4 computer can boot from a USB storage device that follows the USB Mass Storage Class specification.

Class drivers are software components that are able to communicate with many USB devices of a particular kind. If the appropriate class driver is present, any number of compliant devices can be plugged in and start working immediately without the need to install additional software. The Mac OS for the Power Mac

#### CHAPTER 1

Introduction

G4 computer includes USB Mass Storage Support 2.0, a class driver that supports devices that meet the USB Mass Storage Class specification.

#### **Expansion Issues**

The expansion features of the Power Mac G4 computer are similar to those of the Power Macintosh G3 1999 computer.

#### Internal Storage Devices

Standard configurations of the Power Mac G4 computer include two unused expansion bays in the bottom of the enclosure. The expansion bays accommodate 1.6-inch-high 3.5-inch devices. Power connectors are provided for both expansion bays. For more information, see "Disk Drives" (page 46).

#### **RAM Expansion**

The main logic board uses JEDEC-standard SDRAM DIMM cards that are 64-bit bus, nonparity, 168-pin, 3.3-volt, unbuffered, and PC100 compliant. The speed of the devices must be 125 MHz (8 ns) or faster.

#### IMPORTANT

DIMMs with registers or buffers, DIMMs with PLLs, and DIMMs with EDO RAM are not supported in the Power Mac G4 computer. ▲

The maximum supported height of SDRAM DIMM cards is 2 inches. The maximum number of devices supported on a DIMM is 16 SDRAM devices. For more information, see "RAM Expansion" (page 62).

#### No L2 Cache Expansion

The backside L2 cache is integrated into the microprocessor module. Cache expansion is not supported.

#### **Proprietary Modem Slot**

The 70-pin modem connector in the Power Mac G4 computer is the same as the connector on the modem slot in the blue-and-white Power Macintosh G3 computers. The modem slot is a proprietary design specifically for Apple modem cards.

## **Digital A/V Connections**

Composite and S-Video connectors are not available on the Power Mac G4 computer. Digital video input and output features of the Power Mac G4 computer are provided by the FireWire ports and the USB ports.

The Power Mac G4 computer does not include RCA jacks for analog stereo audio input and output. The built-in 3.5 mm sound input and sound output connectors can be used for analog stereo audio input and output. Digital audio input and output is supported by the FireWire interface. For information about the analog sound connectors, see "Sound System" (page 53). For information about the FireWire interface, see "FireWire Ports" (page 43).

## **AC Power Issues**

Users should be made aware of the following power issues.

#### Line Voltage Switch

The power supply is not self-configuring for different input voltages. The voltage switch is delivered preconfigured for the input voltage of the region in which the unit is originally purchased. If the computer is moved to another location where the input voltage is different, a voltage switch must be adjusted to accommodate the voltage change. The switch has two positions that support voltage ranges of 100 to 130 V or 220 to 270 V.

#### Monitor Power Socket

The monitor power socket is not switched. Any time power is connected to the power supply, power is available on the monitor power socket. A monitor that does not support energy saving features that is connected to the monitor power socket will not power off when the computer is shut down. Monitors that do not support energy saving features have to be switched manually.

## Legacy I/O Issues

The Power Mac G4 computer does not include certain I/O features found on previous Macintosh computers.

#### No SCSI Ports

The Power Mac G4 computer does not include built-in internal or external SCSI device connectors. Adding an internal or external SCSI device requires the use of a SCSI PCI card. Ultra2 SCSI (LVD) drives and PCI controller cards are available as options at the time of purchase.

#### No LocalTalk Serial Ports

The Power Mac G4 computer does not include RS-422 LocalTalk serial ports found on earlier Macintosh models. Serial I/O for external USB devices is provided by two USB ports. USB adapters are available from third parties to support Macintosh-compatible legacy serial devices.

#### No ADB or Serial Ports

The USB ports take the place of the ADB and serial I/O ports found on earlier Macintosh computers. Software shims have been implemented in the system software to allow existing applications that use ADB devices to work with USB devices.

The Power Mac G4 computer uses a USB keyboard and mouse similar to the USB keyboard and mouse introduced with the iMac computer.

USB game controllers are supported by the InputSprocket component of the Apple Games Sprockets software architecture. InputSprocket software and information about the InputSprocket APIs can be found at

http://developer.apple.com/games/

#### CHAPTER 2

Architecture

This chapter describes the architecture of the Power Mac G4 computer. It includes information about the major components on the logic boards: the microprocessor, the other main ICs, and the buses that connect them to each other and to the I/O interfaces.

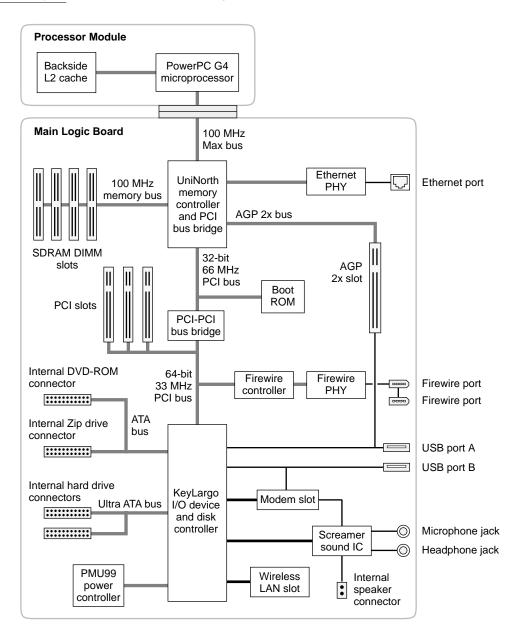

## **Block Diagram and Buses**

Figure 2-1 is a simplified block diagram of the Power Mac G4 computer. The diagram shows the main ICs and the buses that connect them together.

The architecture of the Power Mac G4 computer is based on the PowerPC G4 microprocessor and two new custom ICs: the Uni-N memory controller and bus bridge, and the KeyLargo I/O controller.

The Power Mac G4 computer has four separate buses, not counting the processor's dedicated interface to the backside cache.

- Processor bus: 100-MHz, 64-bit bus connecting the processor module to the Uni-N IC

- **Memory bus:** 100-MHz, 64-bit bus connecting the main memory to the Uni-N IC

- AGP bus: 66 or 132-MHz, 32-bit bus connecting the AGP graphics card to the Uni-N IC

- PCI bus: 66-MHz, 32-bit bus connecting the boot ROM and the PCI-PCI bridge IC to the Uni-N IC; 33-MHz, 64-bit bus connecting the KeyLargo I/O controller and the PCI slots to the PCI-PCI bridge IC

The remainder of this chapter describes the architecture in three parts centered around the processor module, the Uni-N memory controller and bridge IC, and the KeyLargo I/O controller IC.

#### Figure 2-1 Simplified block diagram

## **Processor Module**

The processor module is a separate PC card that contains the G4 microprocessor and the backside L2 cache.

The processor module is connected to the main logic board by way of a 300-pin connector. To achieve the required level of performance, the signal lines that connect the processor module and the main logic board are carefully matched in length, loading, and impedance.

## PowerPC G4 Microprocessor

The processor in the Power Mac G4 computer is a PowerPC G4 microprocessor running at a clock frequency of 350, 400, or 450 MHz.

The PowerPC G4 microprocessor uses a new pipelined system bus that is more efficient than the system bus on the PowerPC G3 microprocessors. The new bus design, called MaxBus, allows for much greater efficiency of bus utilization than was possible with the previous design.

Features of the PowerPC G4 include:

- 32-bit PowerPC implementation

- superscalar PowerPC core

- AltiVec technology: 128-bit-wide vector execution unit

- dual 32 KB instruction and data caches (the same as PowerPC G3)

- support for up to 2 MB backside L2 cache

- on-chip L2 tag storage (twice as much as PowerPC G3)

- high bandwidth MaxBus (also compatible with 60x bus)

- fully symmetric multiprocessing capability

For technical details, see the PowerPC web pages at

http://www.mot.com/SPS/PowerPC/index.html

#### Level2 Cache

The backside level2 (L2) cache consists of 1 MB of high-speed SRAM. The clock frequency of the L2 cache is one half the clock frequency of the PowerPC G4 microprocessor.

Note

The Power Mac G4 computer does not use jumpers to control the clock speeds of the processor and cache. •

# Uni-N Bridge and Memory Controller

The Uni-N custom IC is at the heart of the Power Mac G4 computer. It provides the bridging functionality between the processor, the memory system, the PCI-based I/O system, the AGP graphics slot, and the Ethernet interface.

#### **Processor Bus**

The processor bus is a 100-MHz, 64-bit bus connecting the processor module to the Uni-N IC. In addition to the increased bus clock speed, the bus uses MaxBus protocols, supported by the Uni-N IC, for improved performance.

The MaxBus protocol includes enhancements that improve bus efficiency and throughput over the 60x bus. The enhancements include

- out of order completion

- address bus streaming

- intervention

Out of order completion allows the memory controller to optimize the data bus efficiency by transferring whichever data is ready, rather than having to pass data across the bus in the order the transactions were posted on the bus. This means that a fast DRAM read can pass a slow PCI read, potentially enabling the processor to do more before it has to wait on the PCI data.

Address bus streaming allows a single master on the bus to issue multiple address transactions back-to-back. This means that a single master can post addresses at the rate of one every two clocks, as opposed to one every three clocks, as it is in the 60x bus protocol.

#### CHAPTER 2

#### Architecture

Intervention is a cache coherency optimization that improves performance for multiprocessor systems. If one processor modifies some data, that data first gets stored "dirty" in that processor's cache. If the other processor then wants that data, it needs to get the new modified values. In previous systems, the first processor must write the dirty data to memory and then the second processor can read the correct values from memory. With intervention, the first processor sends the data directly to the second processor, reducing latency by a factor of ten or more.

#### Main Memory Bus

The main memory bus is a 100-MHz, 64-bit bus connecting the main memory to the Uni-N IC.

Main memory is provided by up to four PC100 DIMMs. Supported DIMM sizes are 16, 32, 64, 128, 256, and 512 MB. Four 512-MB DIMMs make a total of 2 GB, which is the maximum supported memory size.

For more information, see "RAM Expansion" (page 62).

#### Note

At present, the Mac OS supports up to 1 GB of memory for applications. Future releases of the Mac OS will support the full 2 GB.  $\blacklozenge$

## Accelerated Graphics Port Bus

The accelerated graphics port (AGP) bus is a 66 or 132-MHz, 32-bit bus connecting the AGP graphics card to the Uni-N IC. The AGP bus provides faster access to main memory than previous designs using the PCI bus.

The AGP bus is a superset of the PCI bus, but it has separate address lines so it does not multiplex address and data as PCI does. Having a separate address bus allows the AGP bus to pipeline addresses, thereby improving performance.

To further improve the performance of the AGP bus, the Uni-N IC supports a graphics address remapping table (GART). Because the virtual memory system organizes main memory as randomly distributed 4 KB pages, DMA transactions for more than 4 KB of data must perform scatter-gather operations. To avoid this necessity for AGP transactions, the GART is used by the AGP bridge in the Uni-N to translate a linear address space for AGP transactions into physical addresses in main memory.

## PCI Buses and Bridge

The Power Mac G4 computer has two PCI buses. The first PCI bus is a 66-MHz, 32-bit bus from the Uni-N IC. The second PCI bus is a 33-MHz, 64-bit bus to the KeyLargo I/O controller and the PCI slots. The PCI-PCI bridge IC provides the conversion between the two PCI buses. The rationale behind this arrangement has to do with reducing the number of pins on the Uni-N IC.

The PCI-to-PCI bridge IC is a DEC 21154-66 device. In addition to bridging between the two PCI buses, it provides performance enhancing features such as write buffering, memory read-ahead buffering, and transaction optimization.

The PCI-to-PCI bridge IC also provides arbitration for the 33 MHz secondary PCI bus. This arbiter is a two-tier round-robin arbiter. The low-priority tier gets one slot in the high-priority round-robin arbitration scheme. Placement of devices in the arbitration scheme is under software control, so any device may be placed in either the high-priority tier or the low-priority tier. For more details of the arbiter, see the DEC 21154-66 databook.

## Boot ROM

The boot ROM contains the Open Firmware boot code.

To minimize the number of pins on Uni-N, the boot ROM is connected to the 66 MHz PCI bus. The boot ROM uses the thirty two PCI AD lines and four PCI byte enable lines for address and data. Uni-N has separate pins for Chip Enable, Output Enable, and Write Enable signals to keep the ROM from interfering with proper PCI bus operation.

The boot ROM consists of 1 MB of on-board flash EPROM. The boot ROM includes the hardware-specific code and tables needed to start up the computer, to load an operating system, and to provide common hardware access services.

The components that comprise what is referred to as the Mac OS Toolbox are no longer in the on-board firmware ROM. The Mac OS Toolbox image file, called Mac OS ROM, is copied from the boot device (hard disk or CD-ROM) into RAM before the Mac OS begins operation. For more information about this ROM-in-RAM approach, see "ROM in RAM" (page 68).

## **Ethernet Controller**

The Uni-N IC includes an Ethernet media access controller (MAC). As a separate I/O channel on the Uni-N IC, it can operate at its full capacity without

degrading the performance of other peripheral devices. The Uni-N IC provides DB-DMA support for the Ethernet interface.

The MAC implements the link layer. It is connected to a PHY interface IC that is capable of operating in either 10-BaseT or 100-BaseT mode. The actual speed of the link is automatically negotiated by the PHY and the bridge or router to which it is connected. For more information, see "Ethernet Port" (page 45).

## **FireWire Controller**

The PCI bus supports an IEEE 1394a FireWire controller with a maximum data rate of 400 Mbits (50 MBytes) per second. The controller implements the FireWire link layer. A physical layer IC, called a PHY, implements the electrical signaling protocol of the FireWire interface. The PHY supports three FireWire ports. Two of the ports go to external connectors on the rear panel of the base unit. The third port is available for devices inside the case.

The computer is capable of accepting external power through the FireWire connector to operate the PHY when the computer is turned off. While the PHY is operating, it acts as a repeater from one port to another so that the FireWire bus remains connected. For more information, see "FireWire Ports" (page 43).

# KeyLargo I/O Controller

The KeyLargo custom IC is the third major component of the architecture. It provides all the I/O functions except Ethernet and FireWire. The KeyLargo IC provides two USB root hubs, an Ultra DMA/66 interface, an EIDE interface, and support for the communication slot and the sound IC.

## **DMA Support**

The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the following I/O channels:

- Ultra DMA/66 interface

- EIDE interface

- communication slot interface

■ DAV channel to the sound IC

The DB DMA system provides a scatter-gather process based on memory-resident data structures that describe the data transfers. The DMA engine is enhanced to allow bursting of data files for improved performance.

## Interrupt Support

The interrupt controller for the Power Mac G4 system is an MPIC cell in the KeyLargo IC. In additition to accepting all the KeyLargo internal interrupt sources, the MPIC controller accepts external interrupts from dedicated interrupt pins and serial interrupts from the Uni-N serial interrupt stream. The signals from the Uni-N IC are synchronized to the operation of the MPIC circuitry, so there is no additional interrupt latency on the Uni-N interrupts.

## **USB** Interface

The KeyLargo IC implements two independent USB root hubs, each of which is connected to one of the ports on the back panel of the computer. The use of two independent hubs allows both USB ports to support high data rate devices at the same time with no degradation of their performance. If a user connects a high-speed device to one port and another high-speed device to the other, both devices can operate at their full data rates.

The two external USB connectors support USB devices with data transfer rates of 1.5 Mbps or 12 Mbps. For more information, see "USB Ports" (page 40).

Internally, the second port of one controller is routed to the USB signal pair on the AGP slot. The second port of the other controller is routed to the modem slot for an internal USB modem.

The USB ports comply with the Universal Serial Bus Specification 1.0 Final Draft Revision. The USB register set complies with the Open Host Controller Interface (OHCI) specification.

## Ultra DMA/66 Interface

The KeyLargo IC implements a single Ultra DMA/66 hard disk interface. This interface supports the boot drive as a master and a second hard drive as a slave.

The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the Ultra DMA/66 interface.

## Enhanced IDE Interface

In the Power Mac G4 computer, the KeyLargo IC provides an enhanced IDE (EIDE) interface. The EIDE interface supports the DVD drive and an optional Iomega Zip removable media drive.

The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the EIDE interface.

## Modem Slot Support

The KeyLargo IC has a traditional Macintosh serial port that is connected to the modem slot. The KeyLargo IC also provides digital audio to the slot in the form of an  $I^2S$  port that shares pins with the serial port.

The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the modem slot interface.

The internal hardware modem is a separate module that contains a modem controller IC, a datapump, and the interface to the telephone line (DAA). For more information about the modem, see "Internal Modem" (page 49).

## Wireless LAN Module

The interface between the wireless LAN module and the KeyLargo IC is similar to a PC Card interface.

The AirPort Card wireless LAN module contains a media access controller (MAC), a digital signal processor (DSP), and a radio-frequency (RF) section. The module has a connector for the cable to the antennas, which are built into the computer's case.

The wireless LAN module is based on the IEEE 802.11 standard. The wireless LAN module transmits and receives data at up to 11 Mbps and is compatible with older systems that operate at 1 or 2 Mbps. For information about its operation, see "AirPort Card Wireless LAN Module" (page 50).

## Sound IC Support

The KeyLargo IC has a traditional DAV port that connects to the Screamer sound IC. The KeyLargo IC provides DB-DMA (descriptor-based direct memory access) support for the DAV port.

The Screamer sound IC is an audio codec with added input and output controls. It is a 16-bit device with two analog stereo input channels and two analog stereo output channels. Either stereo pair of input channels can be selected for digitization by the internal A-to-D converter.

For a description of the features of the sound system, see "Sound System" (page 53).

## **Power Controller**

The power management controller in the Power Mac G4 computer is a custom IC called the PMU99. It supports new modes of power management that provide significantly lower power consumption than previous systems. For more information, see "Power Manager" (page 74).

# AGP Graphics Card

The computer comes with an AGP graphics card installed. The graphics card has the following specifications:

- ATI's RAGE 128 PRO graphics IC

- 16 MB SDRAM on a 128-bit, 125-MHz SDRAM bus

- 3-row mini DB-9/15 connector for an analog video monitor

- support for up to 1920 by 1440 pixels on an analog monitor

- 24-pin standard digital-only DVI connector for a digital monitor

- support for up to 1600 by 1024 pixels on a digital monitor

For more information about the features of the graphics card and the monitors it supports, see "Video Monitor Ports" (page 55).

## **Graphics Controller IC**

The ATI RAGE 128 PRO graphics controller IC on the accelerated graphics card contains the logic for the video display. The ATI RAGE 128 PRO graphics controller includes the following features:

- advanced 128-bit rendering engine

- architecture optimized to support high-speed SDRAM video memory

- display memory controller, built-in drawing coprocessor, video scaler, color space converter, clock generator, and true color palette video DAC (digital-to-analog converter)

- video CLUT (color lookup table)

- integrated support for digital flat panel monitors

- hardware graphics acceleration with a 16-bit Z-buffer

- accelerated QuickDraw 3D rendering up to six times that of software-only acceleration

- true color palette DAC supporting pixel clock rates to 250 MHz

- graphics and video line buffer for superior video scaling and playback quality

- hardware cursor up to 64 x 64 x 2

- DDC1 and DDC2B+ for plug-and-play monitor support

- graphics control accessible through the QuickDraw, QuickDraw 3D, QuickDraw 3D RAVE, and QuickTime components APIs

A separate data bus handles data transfers between the ATI RAGE 128 PRO graphics controller and the display memory. The display memory data bus is 128 bits wide, and all data transfers consist of 128 bits at a time. The RAGE 128 PRO IC breaks each 128-bit data transfer into several pixels of the appropriate size for the current display mode—4, 8, 16, 24, or 32 bits per pixel.

The ATI RAGE 128 PRO graphics controller uses several clocks. Its transactions are synchronized with the AGP bus. Data transfers from the frame-buffer RAM are clocked by the MEM\_CLK signal. Data transfers to the CLUT and the video output are clocked by the dot clock, which has a different rate for different display monitors.

Architecture

The 2D graphics accelerator is a fixed-function accelerator for rectangle fill, line draw, polygon fill, panning/scrolling, bit masking, monochrome expansion, and scissoring.

## **Display Memory**

The display memory on the AGP graphics card is separate from the main memory. The display memory consists of 16 MB of 125 MHz/8ns SDRAM devices configured to make a 64-bit data bus. The display memory cannot be expanded by the user.

The graphics card has 16 MB of video memory, allowing the analog monitor display to have pixel depths of 8, 16, or 32 bpp for displays up to 1280 by 1024 pixels and 8 or 16 bpp for displays up to 1920 by 1080 pixels. The digital flat-panel display can have pixel depths of 8, 16, or 32 for a display up to 1600 by 1024 pixels.

For information about the monitor connector and display resolutions, see "Video Monitor Ports" (page 55).

Architecture

Input and Output Devices

This chapter describes the Power Mac G4 computer's built-in I/O devices and the ports for connecting external I/O devices. Each of the following sections describes an I/O port or device.

# **USB** Ports

The Power Mac G4 computer has two external Universal Serial Bus (USB) ports that are used for connecting the keyboard and mouse as well as additional I/O devices such as printers, scanners, and low-speed storage devices.

The USB ports are connected to separate USB root hubs, allowing both USB ports to support 12 Mbps devices at the same time with no degradation of their performance.

For more information about USB on Macintosh computers, please refer to Apple Computer's *Mac OS USB DDK API Reference* and the other sources listed in "About This Note" (page 11).

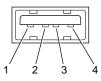

### **USB** Connectors

The USB ports use USB Type A connectors, which have four pins each. Two of the pins are used for power and two for data. Figure 3-1 shows the connector and Table 3-1 shows the pin assignments.

Figure 3-1 USB connector

#### Input and Output Devices

| Table 3 | -1 Pin assignm | Pin assignments on the USB connector |  |  |  |

|---------|----------------|--------------------------------------|--|--|--|

| Pin     | Signal name    | Description                          |  |  |  |

| 1       | VCC            | +5 VDC                               |  |  |  |

| 2       | D-             | Data –                               |  |  |  |

| 3       | D+             | Data +                               |  |  |  |

| 4       | GND            | Ground                               |  |  |  |

|         |                |                                      |  |  |  |

The Power Mac G4 computer provides power for the USB ports at 5 V and up to 500 mA on each port. The ports have individual overcurrent protection; an overcurrent condition on one port leaves the other functional.

The USB ports support both low-speed and high-speed data transfers, at 1.5 Mbits per second and 12 Mbits per second, respectively. High-speed operation requires the use of shielded cables.

The Power Mac G4 computer comes with version 1.3 of the Macintosh USB system software, which supports all four data transfer types defined in the USB specification.

### USB Features

Features of the USB ports include power saving modes and the ability to start up the computer from an USB mass-storage device.

"Power Off During Sleep"

"USB Storage Devices"

#### Power Off During Sleep

In the Power Mac G4 computer, the USB port can be completely powered down during Sleep mode. USB devices must be able to start up again when the computer wakes up from Sleep mode. This functionality is part of the USB-suspend mode defined in the USB specification. Information about the operation of USB-suspend mode on Macintosh computers is included in the Mac OS USB DDK API Reference, available on the World Wide Web at

http://developer.apple.com/techpubs/hardware/DeviceManagers/usb/ usb.html

#### Input and Output Devices

In addition to restarting themselves out of Sleep mode, USB devices can also provide a remote wakeup function for the computer. The USB root hub in the computer is set to support remote wakeup whenever a device is attached to or disconnected from the bus. The mouse and keyboard that come with the computer use this method to wake the computer on a key press or mouse motion.

#### **USB Storage Devices**

The Power Mac G4 computer can boot from a USB storage device that follows the USB Mass Storage Class specification.

Class drivers are software components that are able to communicate with many USB devices of a particular kind. If the appropriate class driver is present, any number of compliant devices can be plugged in and start working immediately without the need to install additional software. The Mac OS for the Power Mac G4 computer includes USB Mass Storage Support 2.0, a class driver that supports devices that meet the USB Mass Storage Class specification.

### **USB** Compatibility Issues

The USB ports take the place of the ADB and serial I/O ports found on earlier Macintosh computers, but they do not function the same way. The following sections describe the differences.

#### **ADB** Compatibility

Apple provides an ADB/USB shim to support processes that control ADB devices by making calls to the ADB Manager and the Cursor Device Manager. The ADB/USB shim makes it possible for processes that support an ADB keyboard to work with the USB keyboard equivalent.

For example, the ADB/USB shim allows applications to set the caps lock and num lock LEDs on the Apple USB keyboard. The ADB/USB shim also allows the Cursor Device Manager to support a USB mouse.

Keyboards other than the Apple USB keyboard can be used with the Power Mac G4 computer, but they will be treated as having an ADB device ID of 2.

#### IMPORTANT

The ADB/USB shim does not support USB devices other than the keyboard and mouse.  $\blacktriangle$

Input and Output Devices

#### Note

The ADB/USB shim is built into the Mac OS ROM image on the Power Mac G4 computer, as it is on all Power Macintosh systems that have USB ports. ◆

#### Serial Port Compatibility

Mac OS 9 includes a serial shim, called SerialShimLib, that enables processes that use the Communications Toolbox CRM to find and use a USB modem device. For more information about the shim, and a sample modem driver that shows how to use it, please refer to the Mac OS USB DDK, available from the Apple Developer Development Kits page on the World Wide Web, at

http://developer.apple.com/sdk/

Apple also provides a USB Communication Class driver, so modem vendors whose devices comply with the USB Communication Class specification do not need to write their own vendor-specific USB class drivers. See "USB Drivers" (page 76).

#### Not for Networking

USB is a serial communications channel, but it does not replace LocalTalk functionality on Macintosh computers; you cannot connect two Macintosh computers together using the USB. The best method for networking Power Mac G4 computers is through the built-in Ethernet port.

# **FireWire Ports**

The Power Mac G4 computer includes two external FireWire IEEE 1394a ports on the rear panel of the enclosure and one inside the computer. The FireWire ports

- support serial I/O at 100, 200, and 400 Mbps (megabits per second)

- provide 15 watts of power when the computer system is on

- accept external power input on the bus when the computer is off

The FireWire hardware and software provided with the Power Mac G4 computer are capable of all asynchronous and isochronous transfers defined by

IEEE standard 1394a. Developers of FireWire peripherals are required to provide device drivers.

It is possible to connect two computers to each other using a FireWire cable, but no software is provided to make use of such a connection.

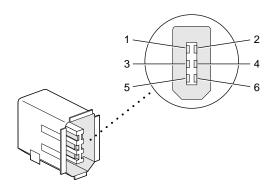

# **FireWire Connector**

The FireWire connector has six contacts, as shown in Figure 3-2. The connector pin assignments are shown in Table 3-2.

Figure 3-2 FireWire connector

Table 3-2

Pin assignments on the FireWire connector

| Pin   | Signal name | Description                                    |

|-------|-------------|------------------------------------------------|

| 1     | Power       | Unregulated DC; 30 V no load                   |

| 2     | Ground      | Ground return for power and inner cable shield |

| 3     | TPB-        | Twisted-pair B, differential signals           |

| 4     | TPB+        |                                                |

| 5     | TPA-        | Twisted-pair A, differential signals           |

| 6     | TPA+        |                                                |

| Shell | _           | Outer cable shield                             |

Input and Output Devices

The power pin provides up to 15 W total power on both connectors. The voltage on the power pin is unregulated, ranging from 20 V under a typical load to 30 V under no load. The power pin also accepts external power at 8 to 33 V, in conformity with the P1394a draft standard, to keep the FireWire bus connected when the computer is turned off.

Pin 2 of the 6-pin FireWire connector is ground return for both power and the inner cable shield. If a 4-pin connector is used on the other end of the FireWire cable, its shell should be connected to the wire from pin 2.

The signal pairs are crossed in the cable itself so that pins 5 and 6 at one end of the cable connect with pins 3 and 4 at the other end. When transmitting, pins 3 and 4 carry data and pins 5 and 6 carry clock; when receiving, the reverse is true.

For additional information about the FireWire interface and the Apple APIs for FireWire device control, refer to the resources available on the Apple FireWire website at

http://developer.apple.com/hardware/FireWire/index.html

or send electronic mail to

firewire@apple.com

# **Ethernet Port**

The Power Mac G4 computer has a built-in 10/100 Mbps Ethernet port. The actual speed of the link is auto-negotiated between the computer's PHY device and the network bridge or router to which it is connected.

The connector for the Ethernet port is an RJ-45 connector on the back of the computer. Table 3-3 shows the signals and pins on the connector. The computer does not have a connector for a fiber-optic cable.

Table 3-3

Signals on the Ethernet connector

| Pin | Signal name | Signal definition        |

|-----|-------------|--------------------------|

| 1   | ТХР         | Transmit (positive lead) |

| 2   | TXN         | Transmit (negative lead) |

| 3   | RXP         | Receive (positive lead)  |

| 4   | -           | Not used                 |

| 5   | -           | Not used                 |

| 6   | RXN         | Receive (negative lead)  |

| 7   | -           | Not used                 |

| 8   | -           | Not used                 |

|     |             |                          |

The Ethernet interface in the Power Mac G4 computer conforms to the ISO/IEC 802.3 specification, where applicable, and complies with IEEE specifications 802.3i (10Base-T) and 802.3u-1995 (100Base-T).

# **Disk Drives**

The Power Mac G4 computer has an Ultra DMA/66 (ATA-5) interface and an ATA-3 interface for internal mass storage and removable media devices. The enclosure includes data and power connectors for the boot drive and a second internal drive on the Ultra DMA/66 interface. It also has a power connector for a third internal drive. The enclosure has data and power connectors for the internal ATAPI DVD-ROM or DVD-RAM drive and an internal ATAPI Zip drive. Those drives are connected to the ATA-3 interface.

The enclosure includes three drive bays for mass storage devices. One bay is occupied by the boot drive. A drive in one of the other bays can be connected to the second drive connector on the Ultra DMA/66 cable assembly or to an

#### Input and Output Devices

optional or user installed third-party PCI controller card. None of the drive bays can be modified to support removable drive bay kits.

The Ultra DMA/66 bus supports PIO Mode 4, DMA Mode 2, and Ultra DMA Mode 2 data transfers. The ATA-3 bus supports PIO Mode 4 and DMA Mode 2 data transfers.

The ATA-3 channel supports two ATA devices. The devices are configured in a ATA Device 0/1 configuration. The ATAPI DVD-ROM and Zip drive, when installed, occupy both device locations on the ATA-3 channel. The ATAPI DVD-ROM is Device 0 (master), and the Zip drive is Device 1 (slave). If the Zip drive is not factory installed in the system, a power and data cable is available for adding a Zip drive to the ATA-3 bus in the Zip drive bay. The device must be device-select jumpered as Device 1 (slave).

The Power Mac G4 computer does not include a 1.44 MB floppy drive.

# Ultra DMA/66 Hard Disk

The logic board supports an internal hard disk that uses the standard Ultra DMA/66 (ATA-5) interface. The Power Mac G4 computer comes with an Ultra DMA/66 hard disk or a Wide Ultra 2 hard disk installed in the third drive bay.

The internal hard disk has a 40-pin connector and a separate 4-pin power connector. An 80-conductor high-density cable with a 40-pin connector is attached to the main logic board. To provide improved signal quality, the 80-conductor cable has ground lines separating the signals on the 40-pin connector. The power cable is attached directly to the power supply.

### **DVD-ROM Drive**

The Power Mac G4 computer has an internal 6x-speed DVD-ROM drive. The DVD-ROM drive supports the following disc formats:

- DVD-ROM (One- or two-layer, one- or two-sided)

- CD-ROM (Modes 1 and 2), CD-ROM XA (Mode 2, Forms 1 and 2)

- CD-Audio, Photo CD, CD-RW, CD-R, CD-Extra

- CD-I (Mode 2, Forms 1 and 2), CD-I Ready, CD-I Bridge

- Video CD

The DVD-ROM drive is an ATAPI drive and is connected as device 0 in an ATA Device 0/1 configuration on the ATA-3 channel of the main logic board. To provide improved signal quality, the ATA bus has an 80-conductor cable with ground lines separating the signals.

# **Optional DVD-RAM Drive**

As an option, the Power Mac G4 computer has an internal 2x-speed DVD-RAM drive in place of the DVD-ROM drive. The DVD-RAM drive supports the following disc formats.

- Reading and writing:

- DVD-RAM media in Type 1 cartridge, one- or two-sided

- □ DVD-RAM media in Type 2 catridge, one sided

- Reading only:

- □ DVD-RAM bare one-sided disc, reading only

- DVD-R (3.9 GB, disc-at-once only)

- □ DVD-ROM (One- or two-layer, one- or two-sided)

- □ CD-ROM (Modes 1 and 2)

- □ CD-ROM XA (Mode 2, Forms 1 and 2)

- □ CD-Audio (CD-DA data through IDE bus)

- □ Photo CD (single and multiple sessions)

- $\Box$  CD-RW

- □ CD-R (fixed and variable packets)

- □ CD-I (Mode 2, Forms 1 and 2), CD-I Ready, CD-I Bridge

- □ Video CD (White Book disc)

- □ CD-EXTRA CD (Blue Book disc)

The DVD-RAM drive takes the place of the DVD-ROM drive and is connected in the same way: as device 0 in an ATA Device 0/1 configuration on the ATA-3 channel of the main logic board. To provide improved signal quality, the ATA bus has an 80-conductor cable with ground lines separating the signals.

# ATAPI Zip Drive

The internal Iomega Zip drive is an ATAPI drive. It is connected as device 1 in an ATA Device 0/1 configuration on the EIDE channel of the main logic board.

Input and Output Devices

If the Zip drive option is not installed at the time of purchase, data and power connectors are provided to add an ATAPI Zip drive to the system. The device should be device-select jumpered as device 1 (slave).

# Optional Ultra2 SCSI (LVD) Drive

An optional Ultra2 SCSI low-voltage differential (LVD) drive and Ultra2 SCSI (LVD) PCI controller card are available as a configuration option. The Ultra2 SCSI (LVD) interface provides data transfer rates of up to 80 MB per second. Additional information about the Ultra2 SCSI (LVD) interface can be found at

http://www.quantum.com/src/whitepapers/

# **Internal Modem**

The Power Mac G4 computer has a dedicated slot for an internal modem module. The module is available as a build-to-order option or as a user-installable upgrade. The external I/O connector for the modem is an RJ-11 connector installed on the rear of the computer. The modem has the following features:

- modem bit rates up to 56 Kbps (supports K56flex and V.90 modem standards)

- fax modem bit rates up to 14.4 Kbps

The modem appears to the system as a serial port that responds to the typical AT commands. The modem provides a sound output for monitoring the progress of the modem connection.

#### Note

This developer note does not provide electrical or mechanical specifications for the modem slot.

# AirPort Card Wireless LAN Module

The Power Mac G4 computer supports the AirPort Card, an internal wireless LAN module. The AirPort Card is available as a build-to-order option or as a user-installable upgrade.

The AirPort Card can be used for local printer sharing, file exchange, internet access, and e-mail access.

The AirPort Card transmits and receives data at up to 11 Mbps. It is also interoperable with some older wireless LANs, as specified in "Hardware Components" (page 50).

Wireless connection to the internet or a wired LAN requires a base station as the connection to the internet or a bridge between the wireless signals and a wired LAN. Software included with the AirPort Card enables a Macintosh computer that has an AirPort Card installed to act as a base station. The user also has the option of purchasing an AirPort Base Station that can be connected to the wired LAN or to a 56 Kbps hardware modem.

### **Data Security**

Three features of the AirPort Card help to maintain the security of data transmissions:

- The system uses direct-sequence spread-spectrum (DSSS) technology that uses a multi-bit spreading code that effectively scrambles the data for any receiver that lacks the corresponding code.

- The system can use a table of authentic network client ID values to verify each client's identity before granting access to the network.

- When communicating with a base station, the system encrypts the data using Wired Equivalent Privacy (WEP) with a 40-bit security key.

# Hardware Components

The AirPort Card is a wireless LAN module based on the IEEE 802.11 standard and using direct-sequence spread-spectrum (DSSS) technology. It is

Input and Output Devices

interoperable with PC-compatible wireless LANs that conform to the 802.11 standard and use DSSS.

The AirPort Card contains a media access controller (MAC), a digital signal processor (DSP), and a radio-frequency (RF) section. The antennas are built into the computer's case.

The MAC provides the data communication protocols and the controls for the physical layer.

The DSP provides the core physical layer functionality and controls the RF section. The DSP communicates with the MAC for data exchange, physical layer control, and parameter settings.

The RF section provides modulation and transmission of outgoing signals and reception and demodulation of incoming signals. Its power output when transmitting is nominally 31 mW.

When transmitting data, the DSP converts the outgoing data stream into a DSSS signal and sends it to the RF section. When receiving data, the DSP accepts incoming DSSS data from the RF section and converts it to a normal data stream.

Two antennas are connected to the AirPort Card. One antenna is always used for transmitting. Either of the two antennas may be used for receiving. Using a diversity technique, the DSP selects the antenna that gives the best reception.

### Software Components

Software that is provided with the AirPort Card includes

- AirPort Setup Assistant, a standalone assistant that takes users through the steps necessary to set up the AirPort Card, set up an AirPort Base Station, or set up a software base station.

- AirPort Application, an application that allows users to switch between wireless networks and to create and join peer-to-peer networks.

- AirPort Control Strip module, which provides a signal strength indication and most of the functions of the AirPort Application.

- AirPort Utility, a utility for the advanced user. With it the user can edit the administrative and advanced settings for a hardware or software base station. It can also be used to determine the location for the base station that gives the best reception.

# Keyboard

The Power Mac G4 computer comes with an Apple USB keyboard. The keyboard has an attached 2-meter cable for installations where the computer is located on the floor or away from the immediate desktop area.

# Keyboard Layout

The Apple USB keyboard has a total of 82 keys, including 12 function keys, a numeric keypad and a set of 4 cursor-control keys. The cursor-control keys are in the inverted-T arrangement.

There are versions of the Apple USB keyboard with different key layouts for three standards used in different parts of the world: ANSI (US and North America), JIS (Japan), and ISO (Europe). Figure 3-3 shows the keyboard layout for the ANSI keyboard. Applications can determine which keyboard is connected by calling the Gestalt Manager and checking for the corresponding value of the gestaltKeyboardType selector:

- gestaltUSBCosmoANSIKbd (value = 198)

- gestaltUSBCosmoJISKbd (value = 200)

- gestaltUSBCosmoISOKbd (value = 199)

### Keyboard and USB

The Apple USB keyboard is designed to work with the computer by way of the USB ports. The keyboard has a captive cable with a USB Type A connector. The keyboard is a bus-powered USB hub with two USB Type A ports.

#### WARNING

A bus-powered hub as defined in the USB specification does not provide enough power to support a second bus-powered hub. A second bus-powered hub must be connected to the second USB port on the computer, not to a port on the Apple USB keyboard. ▲

The standard NMI and reset key combinations are available, but the keys are decoded in software and may not be available under some crashed conditions. Therefore, NMI and reset switches are also available on the front of the computer.

Apple provides a HID class driver for the Apple USB keyboard, which supports the USB boot protocol. Other keyboards intended for use on the Macintosh platform must support the HID boot protocol, as defined in the USB Device Class Definition for Human Interface Devices (HIDs).

# Mouse

The Power Mac G4 computer comes with an Apple USB mouse.

The mechanism inside the Apple USB mouse is similar to that in the Apple Desktop Bus Mouse II. The mouse ball is removeable for cleaning; the ring that allows access to the ball can be locked by inserting an unfolded paper clip into a small hole and turning the ring clockwise.

# Sound System

The sound system for the Power Mac G4 computer supports 44.1 kHz 16-bit stereo sound output and input, available simultaneously.

Input and Output Devices

Like other Macintosh computers, the sound circuitry and system software can create sounds digitally and either play the sounds through speaker inside the enclosure or send the sound signals out through the sound output jack. The Power Mac G4 computer also records sound from several sources: a stereo sound source connected to the line-level sound input jack, single-channel sound from the modem card in the internal modem slot, or sound from a PlainTalk microphone. With each sound input source, sound playthrough can be enabled or disabled.

# Sound Output

The Power Mac G4 computer has one built-in speaker and a 3.5 mm mini jack for stereo sound output on the back of the enclosure.

The output jack is suitable for connecting a pair of headphones or amplified external speakers. Inserting a plug into the sound output jack disconnects the internal speaker.

The sound output jack has the following electrical characteristics:

- output sound signal-to-noise ratio (SNR) <90 dB unweighted (typical) when sound playback is from system hard disk drive or main memory

- output sound SNR <80 dB unweighted (nominal) when playback is from CD

- overall output sound SNR <90 dB unweighted (typical)

# Sound Input

The Power Mac G4 computer provides a stereo sound input jack on the back of the enclosure for connecting an external PlainTalk microphone or a line-level sound source. The sound input jack accepts a standard 3.5 mm stereophonic phone plug (two signals plus ground).

The sound input jack has the following electrical characteristics:

- input impedance: 20 k $\Omega$

- maximum input level without distortion: 2.5 V peak to peak (Vpp) maximum

- line-level microphone voltage range of 0.28 V to 2.1 V peak to peak

- input SNR <90 dB unweighted (typical) for recording to system hard disk drive or system main memory

# **Digitizing Sound**

The sound circuitry digitizes and records sound as 44.1 kHz 16-bit samples. If a sound sampled at a lower rate on another computer is played as output, the Sound Manager transparently upsamples the sound to 44.1 kHz prior to outputting the audio to the Screamer sound IC.

The preferred sound sampling rate for output is specified in the Sound control panel when the sound input is not in use. The preferred output sampling rate is overridden by the setting of the input sampling rate, because the input and output sampling rates are physically locked together. The sound output sampling rate is always 44.1 kHz.

When recording sound from a microphone, applications that are concerned about feedback should disable sound playthrough by calling the Sound Manager APIs.

# Video Monitor Ports

The Power Mac G4 computer comes with an accelerated graphics card installed. The card provides an analog port for an external video monitor and a digital port for a digital flat-panel monitor.

### **Digital Monitor Connector**

The connector for the digital video monitor is a standard digital-only DVI connector. Figure 3-4 shows the contact configuration and Table 3-4 lists the signal assignments.

#### Figure 3-4 Digital monitor connector

| 1  | 2  | 3  | 4  | 5  | 6  | 1  | 8  |  |

|----|----|----|----|----|----|----|----|--|

| 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |  |

| 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |  |

Table 3-4

Signals on the digital monitor connector

| Pin | Signal name         | Pin | Signal name          |

|-----|---------------------|-----|----------------------|

| 1   | TMDS Data2-         | 13  | TMDS Data3+          |

| 2   | TMDS Data2+         | 14  | +5V Power            |

| 3   | TMDS Data2/4 Shield | 15  | Ground for +5V Power |

| 4   | TMDS Data4-         | 16  | Hot Plug Detect      |

| 5   | TMDS Data4+         | 17  | TMDS Data0-          |

| 6   | DDC Clock           | 18  | TMDS Data0+          |

| 7   | DDC Data            | 19  | TMDS Data0/5 Shield  |

| 8   | n. c.               | 20  | TMDS Data5-          |

| 9   | TMDS Data1-         | 21  | TMDS Data5+          |

| 10  | TMDS Data1+         | 22  | TMDS Clock Shield    |

| 11  | TMDS Data1/3 Shield | 23  | TMDS Clock+          |

| 12  | TMDS Data3-         | 24  | TMDS Clock-          |

The graphics data sent to the digital monitor use transition minimized differential signaling (TMDS). TMDS uses an encoding algorithm to convert bytes of graphics data into characters that are transition-minimized to reduce EMI with copper cables and DC-balanced for transmission over fiber optic cables. The TMDS algorithm also provides robust clock recovery for greater skew tolerance with longer cables or low cost short cables.

For information about TMDS, see the specification, Digital Visual Interface DVI Revision 1.0, available on the web site of the Digital Display Working Group (DDWG) at

Input and Output Devices

http://www.ddwg.org/index.html

# **Digital Display Resolutions**

Table 3-5 shows the resolutions supported on flat-panel (digital) displays. The 16 MB of video RAM on the accelerated graphics card supports pixel depths up to 32 bits per pixel at all resolutions.

| Table 3-5  | Digital display resolutions |              |

|------------|-----------------------------|--------------|

| 640 by 480 | 800 by 600                  | 1280 by 800  |

| 800 by 500 | 1024 by 640                 | 1280 by 1024 |

| 800 by 512 | 1024 by 768                 | 1600 by 1024 |

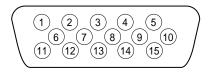

# Analog Monitor Connector

The connector for the video monitor is a three-row DB-9/15 (also called mini sub D15) connector for use with a VGA, SVGA, or XGA monitor. Figure 3-5 shows the pin configuration and Table 3-6 lists the signal pin assignments.

| Table 3-6 | Signals on the analog monitor connector |

|-----------|-----------------------------------------|

|-----------|-----------------------------------------|

| Pin | Signal name | Description        |

|-----|-------------|--------------------|

| 1   | RED         | Red video signal   |

| 2   | GREEN       | Green video signal |

| 3   | BLUE        | Blue video signal  |

#### Input and Output Devices

| Table 5-0 | Signals of the analog monitor connector (continued) |                                   |  |  |

|-----------|-----------------------------------------------------|-----------------------------------|--|--|

|           |                                                     |                                   |  |  |

| Pin       | Signal name                                         | Description                       |  |  |

| 4         | MONID(0)                                            | Monitor ID signal 0               |  |  |

| 5         | GND                                                 | DDC return                        |  |  |