# 64-Bit Extension Technology Software Developer's Guide Volume 1 of 2

Revision 1.00

**NOTE**: The *64-bit extension technology software developer's guide* consists of volumes 1 and 2. Refer to both volumes when evaluating your design needs.

Order Number: 300834-001

64-Bit Extension Technology Software Developer's Guide, Volume 1 of 2

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice.

Developers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Improper use of reserved or undefined features or instructions may cause unpredictable behavior or failure in developer's software code when running on an Intel processor. Intel reserves these features or instructions for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from their unauthorized use.

The Intel<sup>®</sup> IA-32 architecture processors (e.g., Pentium<sup>®</sup> 4, Intel<sup>®</sup> Xeon<sup>TM</sup>, and Pentium III processors) may contain design defects or errors known as errata. Current characterized errata are available on request.

Intel, Intel386, Intel486, Pentium, Intel Xeon are trademarks or registered trademarks of Intel Corporation and its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

COPYRIGHT © 1997-2004 INTEL CORPORATION

**NOTE:** This content listing reflects Volume 1 and Volume 2. Volume 1 houses the TOC, Chapters 1 and 2. Volume 2 houses the rest of the specification.

#### CHAPTER 1

| INTRODUCTION       |                                               |       |  |  |

|--------------------|-----------------------------------------------|-------|--|--|

| 1.1.               | 64-BIT EXTENSION TECHNOLOGY.                  | . 1-1 |  |  |

| 1.2.               | OPERATING MODES                               |       |  |  |

| 1.2.1.             | IA-32e Mode                                   |       |  |  |

| 1.2.2.             | 64-Bit Mode                                   |       |  |  |

| 1.2.3.             | Compatibility Mode                            |       |  |  |

| 1.2.4.             | Legacy Modes                                  |       |  |  |

| 1.2.5.             | System Management Mode                        | . 1-3 |  |  |

| 1.3.               | REGISTER-SET CHANGES                          |       |  |  |

| 1.3.1.             | General-Purpose Registers (GPRs)              |       |  |  |

| 1.3.2.             | Streaming SIMD Extension (SSE) Registers      | . 1-5 |  |  |

| 1.3.3.             | System Registers                              | . 1-5 |  |  |

| 1.3.3.1.           | Extended Feature Enable Register (IA32_EFER)  | . 1-5 |  |  |

| 1.3.3.2.           | Control Registers                             | . 1-5 |  |  |

| 1.3.3.3.           | Descriptor Table Registers                    | . 1-6 |  |  |

| 1.3.3.4.           | Debug Registers                               | . 1-6 |  |  |

| 1.4.               | INSTRUCTION-SET CHANGES                       | . 1-7 |  |  |

| 1.4.1.             | Address-Size and Operand-Size Prefixes        | . 1-7 |  |  |

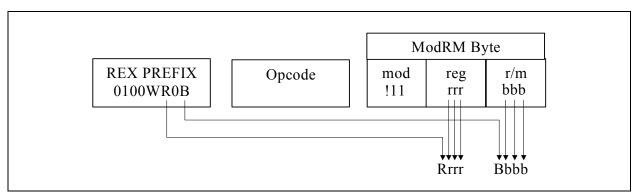

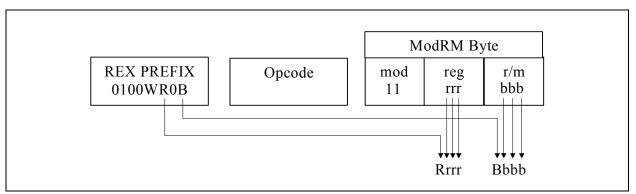

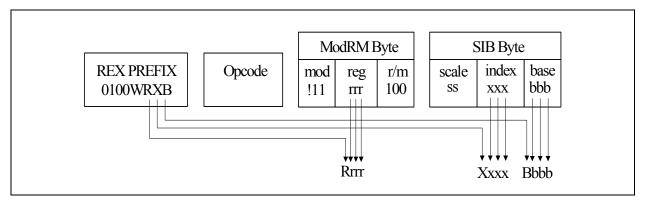

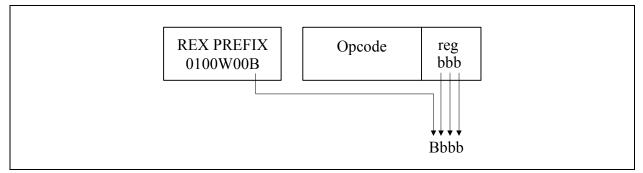

| 1.4.2.             | REX Prefixes                                  | . 1-8 |  |  |

| 1.4.2.1.           | Encoding.                                     |       |  |  |

| 1.4.2.2.           | REX Prefix Fields                             | . 1-9 |  |  |

| 1.4.2.3.           | Displacement                                  | 1-11  |  |  |

| 1.4.2.4.           | Direct Memory-Offset MOVs                     |       |  |  |

| 1.4.2.5.           | Immediates                                    |       |  |  |

| 1.4.2.6.           | RIP-Relative Addressing                       |       |  |  |

| 1.4.2.7.           | Default 64-Bit Operand Size                   |       |  |  |

| 1.4.3.             | New Encodings for Control and Debug Registers |       |  |  |

| 1.4.4.             | New Instructions                              | 1-13  |  |  |

| 1.4.5.             | Stack Pointer                                 |       |  |  |

| 1.4.6.             | Branches                                      |       |  |  |

| 1.5.               | MEMORY ORGANIZATION.                          |       |  |  |

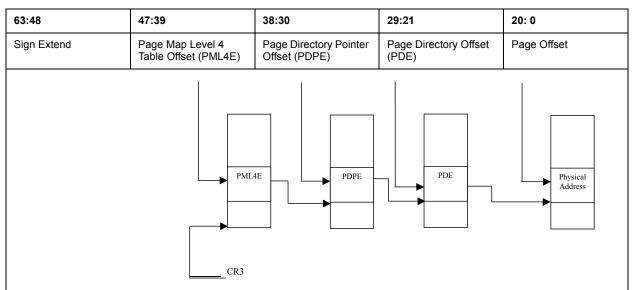

| 1.5.1.             | Address Calculations in 64-Bit Mode           | 1-14  |  |  |

| 1.5.2.             |                                               | 1-15  |  |  |

| 1.6.               |                                               | 1-15  |  |  |

| 1.6.1.             | CPUID.                                        | 1-15  |  |  |

| 1.6.2.             | Register Settings and IA-32e Mode             |       |  |  |

| 1.6.3.<br>1.6.3.1. | Processor Modes                               |       |  |  |

| 1.6.3.2.           | Activating IA-32e mode                        |       |  |  |

| 1.6.3.3.           | Virtual-8086 Mode                             |       |  |  |

| 1.6.3.4.           | Compatibility Mode                            |       |  |  |

| 1.6.4.             | Segmentation                                  |       |  |  |

| 1.6.4.1.           | Code Segments                                 |       |  |  |

| 1.6.4.2.           | Segment LOAD Instructions                     | 1-19  |  |  |

| 1.6.4.3.           | System Descriptors                            |       |  |  |

| 1.6.5.             | Linear Addressing and Paging                  |       |  |  |

| 1.6.5.1.           | Software Address Translations in 64-Bit Mode  |       |  |  |

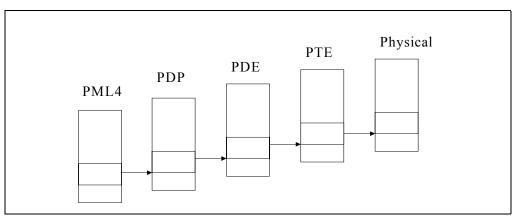

| 1.6.5.2.           | Paging Data Structures                        |       |  |  |

| 1.6.5.3.           | Overall Page Protection                       |       |  |  |

| 1.6.5.4.           | Reserved Bit Checking                         |       |  |  |

| 1.6.6.             | Enhanced Legacy-Mode Paging                   |       |  |  |

| 1.6.7.             | CR2 and CR3                                   |       |  |  |

| 1.6.8.             | Address Translation                           |       |  |  |

| 1.6.9.             | Privilege-Level Transitions and Far Transfers | 1-28  |  |  |

| 1.6.9.1. | Call Gates                                                                      |      |

|----------|---------------------------------------------------------------------------------|------|

| 1.6.9.2. | Privilege-Level Changes and Stack Switching                                     |      |

| 1.6.9.3. | Fast System Calls.                                                              |      |

| 1.6.9.4. | Task State Segments                                                             |      |

| 1.6.10.  | Interrupts                                                                      |      |

| 1.6.10.1 |                                                                                 |      |

| 1.6.10.2 |                                                                                 |      |

| 1.6.10.3 |                                                                                 |      |

| 1.6.10.5 |                                                                                 | 1-35 |

| 1.6.10.6 |                                                                                 | 1-36 |

| 1.6.10.7 |                                                                                 |      |

| 1.7.     | GENERAL RULES FOR 64-BIT MODE                                                   |      |

|          |                                                                                 |      |

| CHAPTE   |                                                                                 |      |

|          |                                                                                 | ~ 1  |

| 2.1.     | INTERPRETING THE INSTRUCTION REFERENCE PAGES                                    |      |

| 2.1.1.   | The Instruction Summary Table Opcode Column in the Instruction Summary Table    | 2-1  |

| 2.1.1.1. | Instruction Column in the Instruction Summary Table                             |      |

| 2.1.1.2. | 64-bit Mode Column in the Instruction Summary Table                             | 2-2  |

| 2.1.1.3. | Compatibility/Legacy Mode Column in the Instruction Summary Table               | 2-4  |

| 2.1.1.5. | Description Column in the Instruction Summary Table.                            | 2-5  |

| 2.1.2.   | Description Section                                                             | 2-5  |

| 2.1.3.   | Operation Section                                                               |      |

| 2.1.3.1. | IA-32e Mode Operation                                                           |      |

| 2.1.4.   | Flags Affected                                                                  |      |

| 2.1.5.   | FPU Flags Affected                                                              |      |

| 2.1.6.   | Protected Mode Exceptions                                                       |      |

| 2.1.7.   | Real-Address Mode Exceptions                                                    |      |

| 2.1.8.   | Virtual-8086 Mode Exceptions                                                    |      |

| 2.1.9.   | Floating-Point Exceptions                                                       |      |

| 2.1.10.  | SIMD Floating-Point Exceptions                                                  |      |

| 2.2.     |                                                                                 |      |

|          | AAA—ASCII Adjust After Addition.                                                |      |

|          | AAD—ASCII Adjust AX Before Division                                             |      |

|          | AAM—ASCII Adjust AX After Multiply                                              |      |

|          | AAS—ASCII Adjust AL After Subtraction                                           |      |

|          | ADC—Add with Carry                                                              |      |

|          | ADD—Add                                                                         |      |

|          | ADDPD—Add Packed Double-Precision Floating-Point Values                         |      |

|          | ADDPS—Add Packed Single-Precision Floating-Point Values                         |      |

|          | ADDSD—Add Scalar Double-Precision Floating-Point Values                         |      |

|          | ADDSD—Add Scalar Double-recision Floating-Point Values.                         |      |

|          | ADDSUBPD—Packed Double-Precision Floating-Point Values.                         | -    |

|          |                                                                                 |      |

|          | ADDSUBPS—Packed Single-Precision Floating-Point Add/Subtract                    |      |

|          |                                                                                 |      |

|          | ANDPD—Bitwise Logical AND of Packed Double-Precision Floating-Point Values      |      |

|          | ANDPS—Bitwise Logical AND of Packed Single-Precision Floating-Point Values      |      |

|          | ANDNPD—Bitwise Logical AND NOT of Packed Double-Precision Floating-Point Values |      |

|          | ANDNPS—Bitwise Logical AND NOT of Packed Single-Precision Floating-Point Values |      |

|          | ARPL—Adjust RPL Field of Segment Selector                                       |      |

|          | BOUND—Check Array Index Against Bounds                                          | 2-42 |

|          | BSF—Bit Scan Forward                                                            | 2-44 |

|          | BSR—Bit Scan Reverse                                                            | 2-45 |

|          | BSWAP—Byte Swap                                                                 |      |

|          | BT—Bit Test                                                                     |      |

|          | BTC—Bit Test and Complement.                                                    |      |

|          | BTR—Bit Test and Reset                                                          |      |

|          | BTS—Bit Test and Set                                                            |      |

|          | CALL—Call Procedure                                                             |      |

|          |                                                                                 | ∠-00 |

| CBW/CWDE/CDQE—Convert Byte to Word/Convert Word to Doubleword/Convert               |        |

|-------------------------------------------------------------------------------------|--------|

| Doubleword to Quadword                                                              | . 2-58 |

| CDQ—Convert Double to Quad                                                          | . 2-59 |

| CLC—Clear Carry Flag                                                                | . 2-60 |

| CLD—Clear Direction Flag                                                            |        |

| CLFLUSH—Flush Cache Line.                                                           |        |

| CLI—Clear Interrupt Flag                                                            |        |

| CLTS—Clear Task-Switched Flag in CR0.                                               |        |

| CMC—Complement Carry Flag.                                                          |        |

| CMOVcc—Conditional Move.                                                            |        |

| CMP—Compare Two Operands                                                            |        |

| CMPPD—Compare Packed Double-Precision Floating-Point Values.                        |        |

| CMPPS—Compare Packed Single-Precision Floating-Point Values                         |        |

| CMPS/CMPSB/CMPSD/CMPSD/CMPSQ—Compare String Operands                                |        |

| CMPSD—Compare Scalar Double-Precision Floating-Point Values                         |        |

| CMPSS—Compare Scalar Single-Precision Floating-Point Values                         |        |

| CMPXCHG—Compare and Exchange                                                        |        |

| CMPXCHG8B/CMPXCHG16B—Compare and Exchange 8 Bytes.                                  |        |

| COMISD—Compare Scalar Ordered Double-Precision Floating-Point Values and Set EFLAGS |        |

| COMISS—Compare Scalar Ordered Double-Frecision Floating-Point Values and Set EFLAGS |        |

|                                                                                     |        |

| CPUID—CPU Identification                                                            | . 2-09 |

| CVTDQ2PD—Convert Packed Doubleword Integers to Packed Double-Precision              | 2 00   |

| Floating-Point Values.                                                              | . 2-99 |

| CVTDQ2PS—Convert Packed Doubleword Integers to Packed Single-Precision              | 0.404  |

| Floating-Point Values.                                                              | 2-101  |

| CVTPD2DQ—Convert Packed Double-Precision Floating-Point Values to Packed            |        |

| Doubleword Integers                                                                 | 2-103  |

| CVTPD2PI—Convert Packed Double-Precision Floating-Point Values to Packed            |        |

| Doubleword Integers                                                                 | 2-105  |

| CVTPD2PS—Covert Packed Double-Precision Floating-Point Values to Packed             |        |

| Single-Precision Floating-Point Values                                              | 2-107  |

| CVTPI2PD—Convert Packed Doubleword Integers to Packed Double-Precision              |        |

| Floating-Point Values                                                               | 2-109  |

| CVTPI2PS—Convert Packed Doubleword Integers to Packed Single-Precision              |        |

| Floating-Point Values                                                               | 2-111  |

| CVTPS2DQ—Convert Packed Single-Precision Floating-Point Values to Packed            |        |

| Doubleword Integers                                                                 | 2-113  |

| CVTPS2PD—Covert Packed Single-Precision Floating-Point Values to Packed             |        |

| Double-Precision Floating-Point Values                                              | 2-115  |

| CVTPS2PI—Convert Packed Single-Precision Floating-Point Values to Packed            |        |

| Doubleword Integers                                                                 | 2-117  |

| CVTSD2SI—Convert Scalar Double-Precision Floating-Point Value to Doubleword Integer | 2-119  |

| CVTSD2SS—Convert Scalar Double-Precision Floating-Point Value to Scalar             |        |

| Single-Precision Floating-Point Value                                               | 2-121  |

| CVTSI2SD—Convert Doubleword Integer to Scalar Double-Precision Floating-Point Value |        |

| CVTSI2SS—Convert Doubleword Integer to Scalar Single-Precision Floating-Point Value |        |

| CVTSS2SD—Convert Scalar Single-Precision Floating-Point Value to Scalar             |        |

| Double-Precision Floating-Point Value                                               | 2-127  |

| CVTSS2SI—Convert Scalar Single-Precision Floating-Point Value to Doubleword Integer | 2-129  |

| CVTTPD2PI—Convert with Truncation Packed Double-Precision Floating-Point Values to  |        |

| Packed Doubleword Integers.                                                         | 2-131  |

| CVTTPD2DQ—Convert with Truncation Packed Double-Precision Floating-Point Values to  | 2-101  |

| Packed Doubleword Integers.                                                         | 2-133  |

| CVTTPS2DQ—Convert with Truncation Packed Single-Precision Floating-Point Values to  | 2-100  |

|                                                                                     | 2-125  |

| Packed Doubleword Integers                                                          | 2-130  |

|                                                                                     | 0 107  |

| Packed Doubleword Integers                                                          | 2-13/  |

| CVTTSD2SI—Convert with Truncation Scalar Double-Precision Floating-Point Value to |         |

|-----------------------------------------------------------------------------------|---------|

| Signed Doubleword Integer                                                         | 2-139   |

| CVTTSS2SI—Convert with Truncation Scalar Single-Precision Floating-Point Value to |         |

|                                                                                   | 2-141   |

| CWD/CDQ/CQQ—Convert Word to Doubleword/Convert Doubleword                         | 0 4 4 0 |

| to Quadword/Convert Quadword to Double Quadword                                   |         |

| DAA—Decimal Adjust AL after Addition                                              |         |

| DEC—Decrement by 1                                                                |         |

| DIV—Unsigned Divide                                                               |         |

| DIVPD—Divide Packed Double-Precision Floating-Point Values                        |         |

| DIVPS—Divide Packed Single-Precision Floating-Point Values                        |         |

| DIVSD—Divide Scalar Double-Precision Floating-Point Values                        |         |

| DIVSS—Divide Scalar Single-Precision Floating-Point Values.                       |         |

| EMMS—Empty MMX State                                                              |         |

| ENTER—Make Stack Frame for Procedure Parameters                                   |         |

| F2XM1—Compute 2x–1                                                                | 2-160   |

| FABS—Absolute Value                                                               |         |

| FADD/FADDP/FIADD—Add                                                              |         |

| FBLD—Load Binary Coded Decimal                                                    |         |

| FBSTP—Store BCD Integer and Pop                                                   |         |

| FCHS—Change Sign                                                                  |         |

| FCLEX/FNCLEX—Clear Exceptions.                                                    |         |

| FCMOVcc—Floating-Point Conditional Move                                           |         |

| FCOM/FCOMP/FCOMPP—Compare Floating Point Values                                   |         |

| FCOMI/FCOMIP/ FUCOMI/FUCOMIP—Compare Floating Point Values and Set EFLAGS         |         |

| FCOS—Cosine                                                                       |         |

| FDIC/FDIVP/FIDIV—Divide                                                           |         |

| FDIV/FDIVF/FIDIV—Divide                                                           |         |

| FFREE—Free Floating-Point Register                                                |         |

| FICOM/FICOMP—Compare Integer                                                      |         |

| FILD—Load Integer                                                                 |         |

| FINCSTP—Increment Stack-Top Pointer                                               |         |

| FINIT/FNINIT—Initialize Floating-Point Unit                                       |         |

| FIST/FISTP—Store Integer                                                          |         |

| FISTTP—Store Integer with Truncation                                              | 2-189   |

| FLD—Load Floating Point Value                                                     | 2-191   |

| FLD1/FLDL2T/FLDL2E/FLDPI/FLDLG2/FLDLN2/FLDZ—Load Constant                         |         |

| FLDCW—Load x87 FPU Control Word                                                   |         |

| FLDENV—Load x87 FPU Environment.                                                  |         |

| FMUL/FMULP/FIMUL—Multiply                                                         |         |

| FNOP—No Operation                                                                 |         |

| FPATAN—Partial Arctangent                                                         |         |

| FPREM—Partial Remainder                                                           |         |

| FPREM1—Partial Remainder                                                          |         |

| FPTAN—Partial Tangent.                                                            |         |

| FRNDINT—Round to Integer                                                          |         |

| FSAVE/FNSAVE—Store x87 FPU State                                                  |         |

| FSCALE—Scale                                                                      |         |

| FSIN—Sine                                                                         |         |

| FSINCOS—Sine and Cosine.                                                          |         |

| FSQRT—Square Root.                                                                |         |

| FST/FSTP—Store Floating Point Value                                               |         |

| FSTCW/FNSTCW—Store x87 FPU Control Word                                           |         |

| FSTENV/FNSTENV—Store x87 FPU Environment                                          | 2-218   |

| FSTSW/FNSTSW—Store x87 FPU Status Word                                            | 2-220   |

|                                                                                   |         |

| FSUB/FSUBP/FISUB—Subtract                                                                             | <b>っ</b> |

|-------------------------------------------------------------------------------------------------------|----------|

| FSUBR/FSUBRP/FISUBR—Reverse Subtract                                                                  |          |

| FTST—TEST                                                                                             |          |

| FUCOM/FUCOMPFUCOMPP—Unordered Compare Floating Point Values                                           | 2-220    |

|                                                                                                       |          |

| FWAIL—Wait                                                                                            |          |

|                                                                                                       |          |

| FXCH—Exchange Register Contents                                                                       |          |

| FXRSTOR—Restore x87 FPU, MMX, SSE, and SSE2 State.                                                    |          |

| FXSAVE—Save x87 FPU, MMX, SSE, and SSE2 State                                                         |          |

| FXTRACT—Extract Exponent and Significand                                                              | 2-241    |

| FYL2X—Compute y * log2x.                                                                              |          |

| FYL2XP1—Compute y * log2(x +1)<br>HADDPD—Horizontal Add Packed Double-Precision Floating-Point Values |          |

|                                                                                                       |          |

| HADDPS—Horizontal Add Packed Single-Precision Floating-Point Values                                   |          |

| HLT—Halt                                                                                              |          |

| HSUBPS—Horizontal Subtract Packed Single-Precision Floating-Point Values                              |          |

|                                                                                                       |          |

| IDIV—Signed Divide                                                                                    |          |

| IMUL—Signed Multiply                                                                                  |          |

| IN—Input from Port                                                                                    |          |

| INC—Increment by 1.                                                                                   |          |

| INS/INSB/INSD—Input from Port to String                                                               |          |

| INT n/INTO/INT 3—Call to Interrupt Procedure.                                                         |          |

|                                                                                                       |          |

| INVLPG—Invalidate TLB Entry                                                                           |          |

| IRET/IRETD—Interrupt Return                                                                           |          |

| Jcc—Jump if Condition Is Met.                                                                         |          |

| JMP—Jump<br>LAHF—Load Status Flags into AH Register                                                   |          |

| LAR—Load Access Rights Byte                                                                           |          |

|                                                                                                       |          |

| LDDQU—Load Unaligned Double Quadword                                                                  |          |

| LDMXCSR—Load MXCSR Register                                                                           | 2-219    |

| LDS/LES/LFS/LGS/LSS—Load Fair Pointer                                                                 |          |

| LEAVE—High Level Procedure Exit                                                                       |          |

| LES—Load Full Pointer                                                                                 |          |

|                                                                                                       |          |

| LFENCE—Load Fence                                                                                     |          |

| LGDT/LIDT—Load Global/Interrupt Descriptor Table Register                                             |          |

| LGS—Load Full Pointer                                                                                 |          |

|                                                                                                       |          |

| LIDT—Load Interrupt Descriptor Table Register                                                         | 2-290    |

| LMSW—Load Machine Status Word.                                                                        |          |

| LOCK—Assert LOCK# Signal Prefix                                                                       |          |

| LODS/LODSB/LODSW/LODSD/LODSQ—Load String                                                              |          |

|                                                                                                       |          |

| LOOP/LOOPcc—Loop According to ECX Counter                                                             |          |

| LSS—Load Full Pointer.                                                                                |          |

| LTR—Load Task Register.                                                                               |          |

|                                                                                                       | 2-233    |

|                                                                                                       |          |

#### CHAPTER 3

#### INSTRUCTION SET REFERENCE (M-Z)

| ION SET REFERENCE (M-2)                                            |      |

|--------------------------------------------------------------------|------|

| MASKMOVDQU—Store Selected Bytes of Double Quadword                 | 3-1  |

| MASKMOVQ—Store Selected Bytes of Quadword.                         | 3-3  |

| MAXPD—Return Maximum Packed Double-Precision Floating-Point Values | 3-5  |

| MAXPS—Return Maximum Packed Single-Precision Floating-Point Values | 3-7  |

| MAXSD—Return Maximum Scalar Double-Precision Floating-Point Value  | 3-9  |

| MAXSS—Return Maximum Scalar Single-Precision Floating-Point Value  | 3-11 |

|                                                                    |      |

| MFENCE—Memory Fence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-13                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| MINPD—Return Minimum Packed Double-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

| MINPS—Return Minimum Packed Single-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

| MINSD—Return Minimum Scalar Double-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                            |

| MINSS—Return Minimum Scalar Single-Precision Floating-Point Value                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |

| MONITOR—Setup Monitor Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                            |

| MOV—Move                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                            |

| MOV—Move to/from Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

| MOV—Move to/from Debug Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                            |

| MOVAPD—Move Aligned Packed Double-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |

| MOVAPS—Move Aligned Packed Single-Precision Floating-Point Values.                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

| MOVD/MOVQ—Move Doubleword                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                            |

| MOVDDUP—Move One Double-Precision Floating-Point Value and Duplicate                                                                                                                                                                                                                                                                                                                                                                                                                                | . 3-35                                                                                                                                     |

| MOVDQA—Move Aligned Double Quadword                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 3-37                                                                                                                                     |

| MOVDQU—Move Unaligned Double Quadword                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                            |

| MOVDQ2Q—Move Quadword from XMM to MMX Register                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 3-41                                                                                                                                     |

| MOVHLPS— Move Packed Single-Precision Floating-Point Values High to Low                                                                                                                                                                                                                                                                                                                                                                                                                             | . 3-42                                                                                                                                     |

| MOVHPD—Move High Packed Double-Precision Floating-Point Value                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                            |

| MOVHPS—Move High Packed Single-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                            |

| MOVLHPS—Move Packed Single-Precision Floating-Point Values Low to High                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                            |

| MOVLPD—Move Low Packed Double-Precision Floating-Point Value                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                            |

| MOVLPS—Move Low Packed Single-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                            |

| MOVMSKPD—Extract Packed Double-Precision Floating-Point Sign Mask                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |

| MOVMSKPS—Extract Packed Single-Precision Floating-Point Sign Mask                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |

| MOVNTDQ—Store Double Quadword Using Non-Temporal Hint                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                            |

| MOVNTI-Store Doubleword/Quadword Using Non-Temporal Hint                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                            |

| MOVNTPD—Store Packed Double-Precision Floating-Point Values Using Non-Temporal Hint                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                            |

| MOVNTPS—Store Packed Single-Precision Floating-Point Values Using Non-Temporal Hint                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                            |

| MOVNTQ—Store of Quadword Using Non-Temporal Hint                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                            |

| MOVQ—Move Quadword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

| MOVQ2DQ—Move Quadword from MMX to XMM Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                            |

| MOVS/MOVSB/MOVSW/MOVSD/MOVSQ—Move Data from String to String                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                            |

| MOVSD—Move Scalar Double-Precision Floating-Point Value                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                            |

| MOVSHDUP—Move Packed Single-Precision FP Values High and Duplicate                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                            |

| MOVSLDUP—Move Packed Single-Precision FP Values Low and Duplicate                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                            |

| MOVSS—Move Scalar SinglePrecision Floating-Point Values.                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                            |

| MOVSX/MOVSXD—Move with Sign-Extension                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                            |

| MOVUPD—Move Unaligned Packed Double-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                            |

| MOVUPS—Move Unaligned Packed Single-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                            |

| MOVZX—Move with Zero-Extend                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                            |

| MUL—Unsigned Multiply                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 3-84                                                                                                                                     |

| MULPD—Multiply Packed Double-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                            |

| MULPS—Multiply Packed Single-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                            |

| MULSD—Multiply Scalar Double-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 3-88                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 3-88<br>. 3-90                                                                                                                           |

| MULSS—Multiply Scalar Single-Precision Floating-Point Values                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 3-88<br>. 3-90<br>. 3-92                                                                                                                 |

| MWAIT—Monitor Wait.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94                                                                                                       |

| MWAIT—Monitor Wait                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95                                                                                             |

| MWAIT—Monitor Wait<br>NEG—Two's Complement Negation<br>NOP—No Operation                                                                                                                                                                                                                                                                                                                                                                                                                             | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97                                                                                   |

| MWAIT—Monitor Wait                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97                                                                                   |

| MWAIT—Monitor Wait.<br>NEG—Two's Complement Negation.<br>NOP—No Operation .<br>NOT—One's Complement Negation .<br>OR—Logical Inclusive OR.                                                                                                                                                                                                                                                                                                                                                          | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100                                                                |

| MWAIT—Monitor Wait.<br>NEG—Two's Complement Negation<br>NOP—No Operation<br>NOT—One's Complement Negation                                                                                                                                                                                                                                                                                                                                                                                           | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100                                                                |

| MWAIT—Monitor Wait.<br>NEG—Two's Complement Negation.<br>NOP—No Operation .<br>NOT—One's Complement Negation .<br>OR—Logical Inclusive OR.                                                                                                                                                                                                                                                                                                                                                          | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100<br>3-102                                                       |

| MWAIT—Monitor Wait.         NEG—Two's Complement Negation         NOP—No Operation         NOT—One's Complement Negation         OR—Logical Inclusive OR         ORPD—Bitwise Logical OR of Double-Precision Floating-Point Values         ORPS—Bitwise Logical OR of Single-Precision Floating-Point Values         OUT—Output to Port                                                                                                                                                             | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100<br>3-102<br>3-104<br>3-106                                     |

| MWAIT—Monitor Wait.         NEG—Two's Complement Negation         NOP—No Operation         NOT—One's Complement Negation         OR—Logical Inclusive OR         ORPD—Bitwise Logical OR of Double-Precision Floating-Point Values         ORPS—Bitwise Logical OR of Single-Precision Floating-Point Values                                                                                                                                                                                        | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100<br>3-102<br>3-104<br>3-106                                     |

| MWAIT—Monitor Wait.         NEG—Two's Complement Negation         NOP—No Operation         NOT—One's Complement Negation         OR—Logical Inclusive OR         ORPD—Bitwise Logical OR of Double-Precision Floating-Point Values         ORPS—Bitwise Logical OR of Single-Precision Floating-Point Values         OUT—Output to Port                                                                                                                                                             | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100<br>3-102<br>3-104<br>3-106<br>3-107                            |

| MWAIT—Monitor Wait.         NEG—Two's Complement Negation         NOP—No Operation         NOT—One's Complement Negation         OR—Logical Inclusive OR         ORPD—Bitwise Logical OR of Double-Precision Floating-Point Values         ORPS—Bitwise Logical OR of Single-Precision Floating-Point Values         OUT—Output to Port.         OUTS/OUTSB/OUTSW/OUTSD—Output String to Port.                                                                                                      | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100<br>3-102<br>3-104<br>3-106<br>3-107<br>3-109                   |

| MWAIT—Monitor Wait.         NEG—Two's Complement Negation         NOP—No Operation         NOT—One's Complement Negation         OR—Logical Inclusive OR         ORPD—Bitwise Logical OR of Double-Precision Floating-Point Values         ORPS—Bitwise Logical OR of Single-Precision Floating-Point Values         OUT—Output to Port.         OUTS/OUTSB/OUTSW/OUTSD—Output String to Port.         PACKSSWB/PACKSSDW—Pack with Signed Saturation                                                | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100<br>3-102<br>3-104<br>3-106<br>3-107<br>3-109<br>3-111          |

| MWAIT—Monitor Wait.         NEG—Two's Complement Negation         NOP—No Operation         NOT—One's Complement Negation         OR—Logical Inclusive OR         ORPD—Bitwise Logical OR of Double-Precision Floating-Point Values         ORPS—Bitwise Logical OR of Single-Precision Floating-Point Values         OUT—Output to Port.         OUTS/OUTSB/OUTSW/OUTSD—Output String to Port.         PACKSSWB/PACKSSDW—Pack with Signed Saturation         PACKUSWB—Pack with Unsigned Saturation | . 3-88<br>. 3-90<br>. 3-92<br>. 3-94<br>. 3-95<br>. 3-97<br>. 3-98<br>3-100<br>3-102<br>3-104<br>3-106<br>3-107<br>3-109<br>3-111<br>3-113 |

| PADDSB/PADDSW—Add Packed Signed Integers with Signed Saturation.           |       |

|----------------------------------------------------------------------------|-------|

| PADDUSB/PADDUSW—Add Packed Unsigned Integers with Unsigned Saturation      |       |

| PAND—Logical AND                                                           |       |

| PAUSE—Spin Loop Hint                                                       |       |

| PAVGB/PAVGW—Average Packed Integers                                        |       |

| PCMPEQB/PCMPEQW/PCMPEQD— Compare Packed Data for Equal.                    |       |

| PCMPGTB/PCMPGTW/PCMPGTD—Compare Packed Signed Integers for Greater Than    |       |

| PEXTRW—Extract Word.                                                       |       |

| PINSRW—Insert Word                                                         |       |

| PMADDWD—Multiply and Add Packed Integers                                   |       |

| PMAXSW—Maximum of Packed Signed Word Integers                              |       |

| PMAXUB—Maximum of Packed Unsigned Byte Integers.                           |       |

| PMINSW—Minimum of Packed Signed Word Integers.                             |       |

| PMINUB—Minimum of Packed Unsigned Byte Integers                            |       |

| PMOVMSKB—Move Byte Mask                                                    |       |

| PMULHUW—Multiply Packed Unsigned Integers and Store High Result            | 3-147 |

| PMULHW—Multiply Packed Signed Integers and Store High Result               |       |

| PMULLW—Multiply Packed Signed Integers and Store Low Result.               | 3-151 |

| PMULUDQ—Multiply Packed Unsigned Doubleword Integers                       | 3-153 |

| POP—Pop a Value from the Stack                                             | 3-155 |

| POPA/POPAD—Pop All General-Purpose Registers                               |       |

| POPF/POPFD—Pop Stack into EFLAGS Register                                  |       |

| POR—Bitwise Logical OR                                                     |       |

| PREFETCHh—Prefetch Data Into Caches                                        |       |

| PSADBW—Compute Sum of Absolute Differences                                 |       |

| PSHUFD—Shuffle Packed Doublewords                                          |       |

| PSHUFHW—Shuffle Packed High Words                                          |       |

| PSHUFLW—Shuffle Packed Low Words                                           |       |

| PSHUFW—Shuffle Packed Words                                                |       |

| PSLLDQ—Shift Double Quadword Left Logical                                  |       |

| PSLLW/PSLLD/PSLLQ—Shift Packed Data Left Logical                           |       |

| PSRAW/PSRAD—Shift Packed Data Right Arithmetic                             |       |

| PSRLDQ—Shift Double Quadword Right Logical                                 |       |

| PSRLW/PSRLD/PSRLQ—Shift Packed Data Right Logical                          |       |

| PSUBB/PSUBW/PSUBD—Subtract Packed Integers.                                |       |

| PSUBQ—Subtract Packed Quadword Integers                                    |       |

| PSUBSB/PSUBSW—Subtract Packed Signed Integers with Signed Saturation       |       |

| PSUBUSB/PSUBUSW—Subtract Packed Unsigned Integers with Unsigned Saturation | 3-186 |

| PUNPCKHBW/PUNPCKHWD/PUNPCKHDQ/PUNPCKHQDQ— Unpack High Data                 | 3-188 |

| PUNPCKLBW/PUNPCKLWD/PUNPCKLDQ/PUNPCKLQDQ—                                  | 5-100 |

|                                                                            | 3-100 |

| PUSH—Push Word or Doubleword Onto the Stack                                |       |

| PUSHA/PUSHAD—Push All General-Purpose Registers.                           |       |

| PUSHF/PUSHFD—Push EFLAGS Register onto the Stack                           |       |

| PXOR—Logical Exclusive OR.                                                 |       |

| RCL/RCR/ROL/ROR-—Rotate                                                    |       |

| RCPPS—Compute Reciprocals of Packed Single-Precision Floating-Point Values |       |

| RCPSS—Compute Reciprocal of Scalar Single-Precision Floating-Point Values  |       |

| RDMSR—Read from Model Specific Register                                    |       |

| RDPMC—Read Performance-Monitoring Counters                                 |       |

| RDTSC—Read Time-Stamp Counter                                              |       |

| REP/REPE/REPZ/REPNE /REPNZ—Repeat String Operation Prefix                  |       |

| RET—Return from Procedure                                                  |       |

| ROL/ROR—Rotate                                                             |       |

| RSM—Resume from System Management Mode                                     |       |

| RSQRTPS—Compute Reciprocals of Square Roots of Packed Single-Precision            |       |

|-----------------------------------------------------------------------------------|-------|

| Floating-Point Values.                                                            | 3-214 |

| RSQRTSS—Compute Reciprocal of Square Root of Scalar Single-Precision              | 0.040 |

| Floating-Point Value                                                              |       |

| SAHF—Store AH into Flags                                                          |       |

| SAL/SAR/SHL/SHR—Shift                                                             |       |

| SCAS/SCASB/SCASW/SCASD—Scan String                                                |       |

| SETcc—Set Byte on Condition                                                       |       |

| SFENCE—Store Fence.                                                               | 3-220 |

| SGDT/SIDT—Store Global/Interrupt Descriptor Table Register                        |       |

| SHL/SHR—Shift Instructions.                                                       |       |

| SHLD—Double Precision Shift Left                                                  | 3-233 |

| SHRD—Double Precision Shift Right                                                 |       |

| SHUFPD—Shuffle Packed Double-Precision Floating-Point Values                      |       |

| SHUFPS—Shuffle Packed Single-Precision Floating-Point Values                      |       |

| SIDT—Store Interrupt Descriptor Table Register                                    |       |

| SLDT—Store Local Descriptor Table Register                                        |       |

| SMSW—Store Machine Status Word                                                    |       |

| SQRTPD—Compute Square Roots of Packed Double-Precision Floating-Point Values      | 3-245 |

| SQRTPS—Compute Square Roots of Packed Single-Precision Floating-Point Values      |       |

| SQRTSD—Compute Square Root of Scalar Double-Precision Floating-Point Value        |       |

| SQRTSS—Compute Square Root of Scalar Single-Precision Floating-Point Value        |       |