# SysKonnect

SysKonnect a business unit of Schneider & Koch & Co. Datensysteme GmbH Siemensstraße 23 D-76275 Ettlingen Tel. 0 72 43 / 50 2100 Fax 0 72 43 / 50 29 89

> October 16, 1995 Version 1.0

# SK-NET FDDI-<x>P Technical Manual

## SK internal documentation

## **Revision History**

| Revision | Released at      | Changes from Previous Release | Remarks                                                            |

|----------|------------------|-------------------------------|--------------------------------------------------------------------|

| 1.0      | October 16, 1995 | n.a.                          | First Release after design closing.<br>No prototype available yet. |

### **Related Documentation**

"AM79C850 Supernet 3" Preliminary documentation, Issue Date March 1995, Publication # 19574 Rev. Afrom Advanced Micro Devices (AMD)

"Flash Memory Products : 1992/1993 Data Book/Handbook" from Advanced Micro Devices (AMD)

"PCI Local Bus Specification" Revision 2.1, June 1, 1995 from PCI Special Interest Group

"PCI Bios Specification" Revision 2.1, August 26, 1994 from PCI Special Interest Group

"FDDI Station Management : Draft Proposed American National Standard" Rev 7.2, June 25, 1992, X3T9/92-067 and editorial changes -> Rev. 7.3, X3T9.5/93-085

"Fibre Distributed Data Interface (FDDI) - Part1: Token Ring Physical Layer Protocol" ISO 9314-1 :1989

"Fibre Distributed Data Interface (FDDI) - Part2: Token Ring Media Access Control (MAC)" ISO 9314-2: 1989

"Fibre Distributed Data Interface (FDDI) - Part 3: Token Ring Physical Layer Medium Dependent (PMD)" ISO/IEC 9314 -3 : 1990

"FDDI Twisted Pair Physical Layer Medium Dependent (TP-PMD) : Proposed American National Standard" Rev. 2.1 03/01/94

"FDDI Low-Cost Fibre Physical Layer Medium Dependent (LCF-PMD) : Draft Proposed American National Standard for Information Systems" Rev. 2.0, 03/01//94

### **Current Release**

|                                         | Approved by |  |

|-----------------------------------------|-------------|--|

| Hardware Engineer                       | CF. Ruf     |  |

| Software<br>Engineer<br>(if applicable) |             |  |

| Technical Writer                        | W. Frank    |  |

## **Table of Contents**

|               | n                              |      |

|---------------|--------------------------------|------|

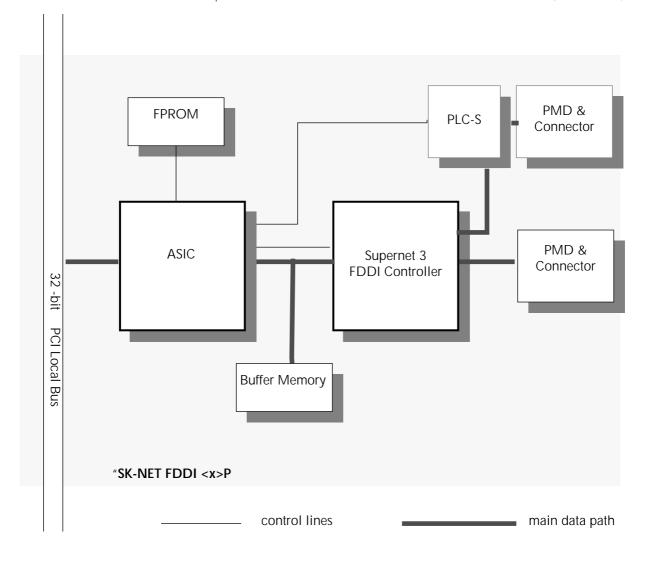

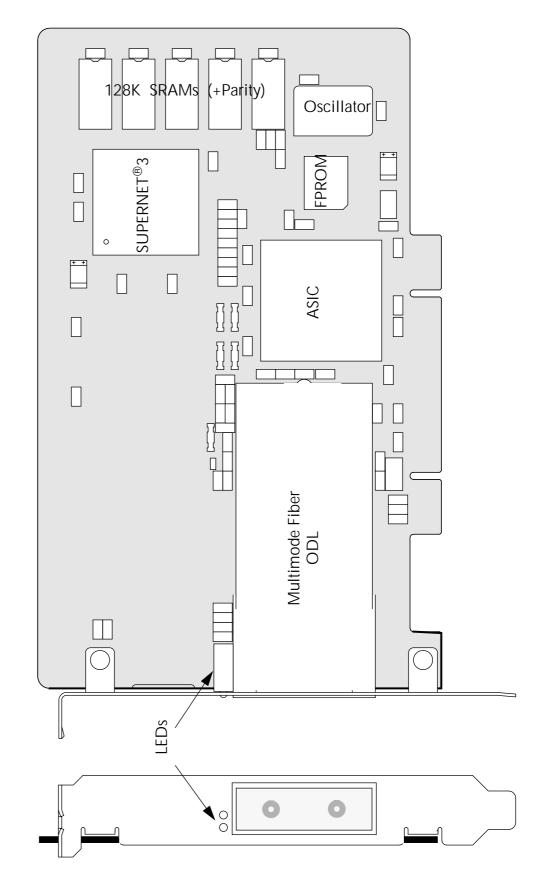

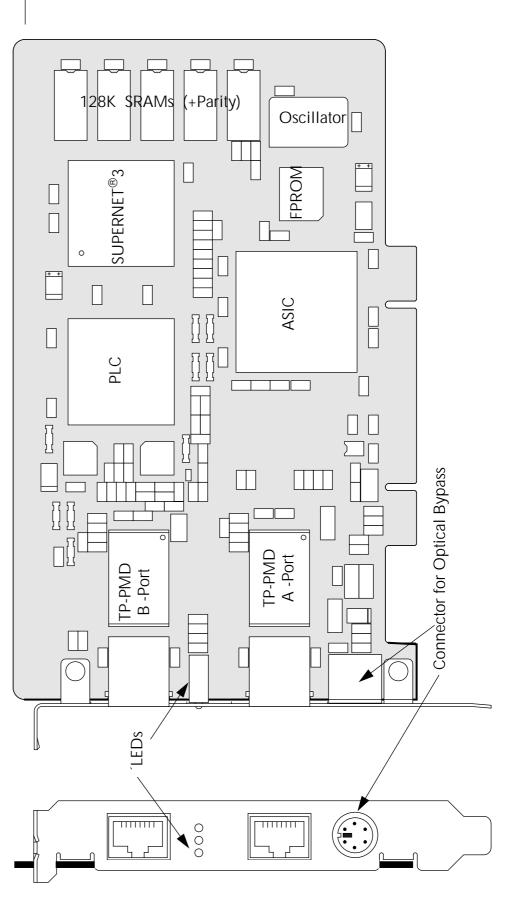

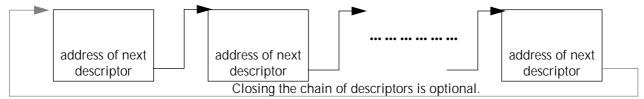

| Physical Blo  | ocks                           | 4    |

| 2.1           | Functional Description         | 7    |

| 2.1.1         | ASIC                           |      |

| 2.1.2         | Buffer Memory                  |      |

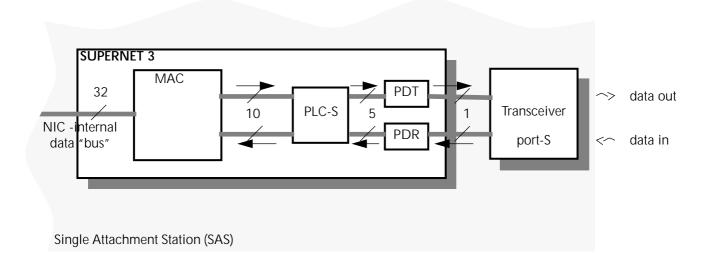

| 2.1.3         | SUPERNET 3                     |      |

| 2.1.4         | PLC-S                          |      |

| 2.1.5         | Transceivers                   |      |

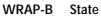

| 2.1.5         | Data Path in the NIC's         | 0    |

| 2.1.0         | FDDI Domain                    | 8    |

|               |                                |      |

| -             | ble Resources Overview         |      |

| 3.1           | Document Conventions           | 13   |

| 3.2           | Configuration Space            |      |

|               | Basics                         | 13   |

| 3.3           | I/O Space and                  |      |

|               | Memory Space                   |      |

|               | Basics                         | 15   |

| 3.3.1         | I/O Access                     | 16   |

| 3.3.2         | Memory Access                  | 16   |

| 3.4           | Principles of Operation        | 17   |

| 3.5           | Buffer Management Unit         |      |

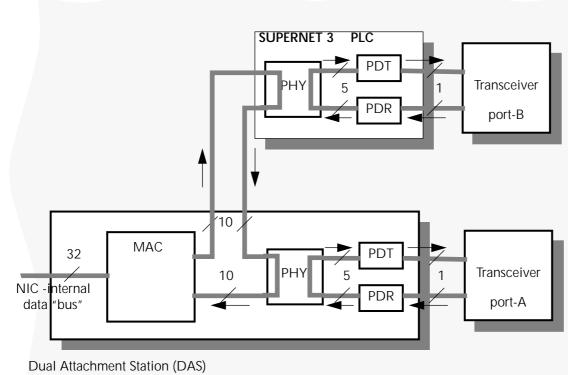

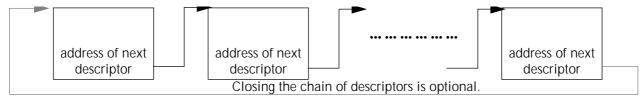

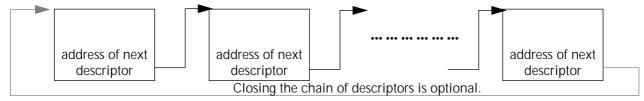

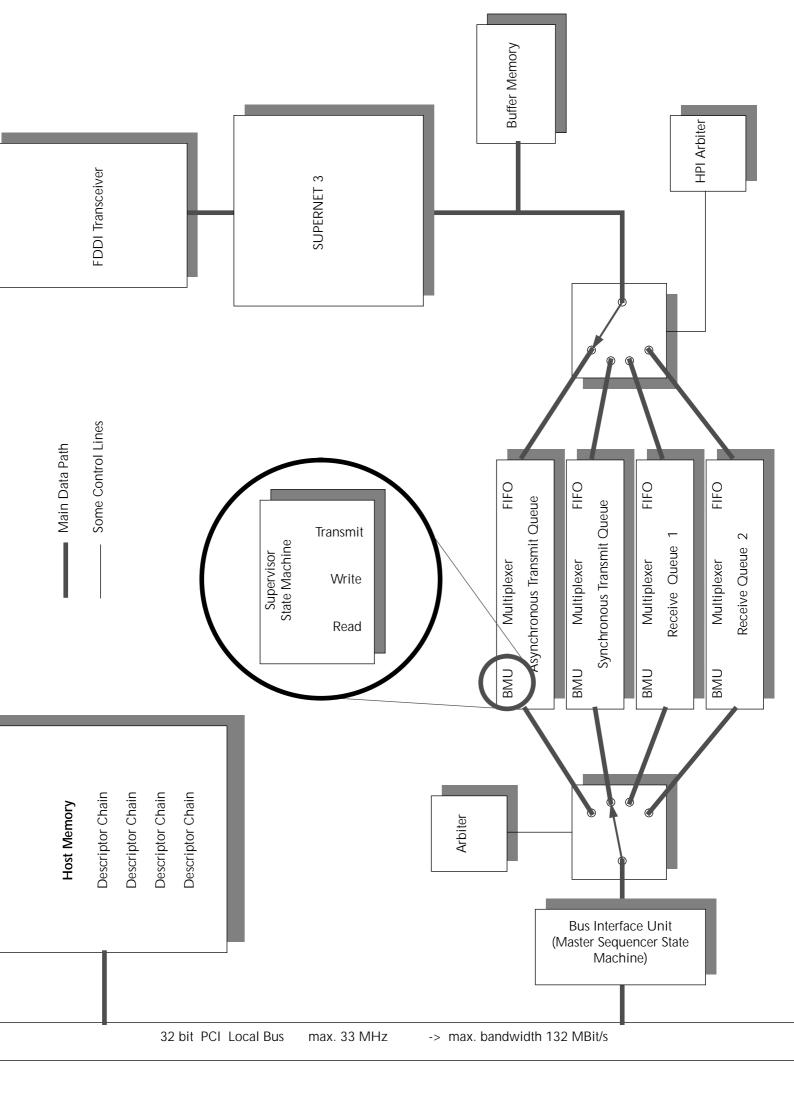

| 3.6           | Descriptor Chains              | 18   |

| 3.6.1         | Descriptor Entries in Detail   |      |

| 3.6.2         | BMU Operation                  |      |

| 3.6.3         | BMU Related Registers          |      |

| 3.6.4         | Subsequent BMU Operations      |      |

| 3.6.5         | Bus Master Operation           |      |

| 3.6.6         | Arbiter                        |      |

| 3.7           | Data Transfer                  |      |

| 011           | Block Diagram                  | 33   |

| 3.7.1         | Multiplexers                   |      |

| 3.7.2         | FIFOs                          |      |

| 3.7.3         | Host Processor Interface (HPI) |      |

| 3.8           | SUPERNET 3                     |      |

| 3.8.1         | PLC-S,                         | 50   |

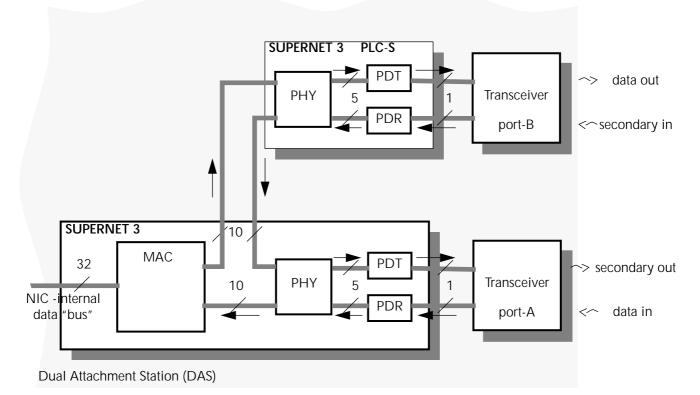

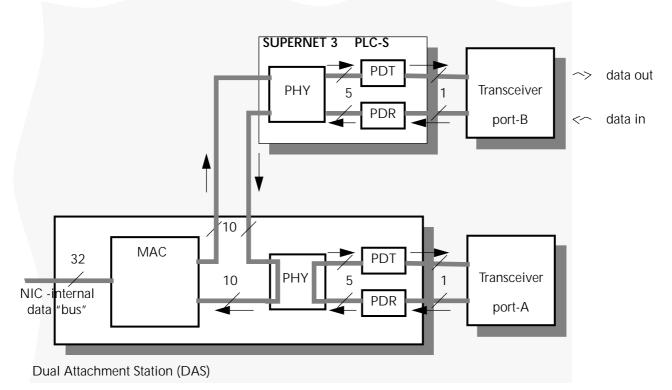

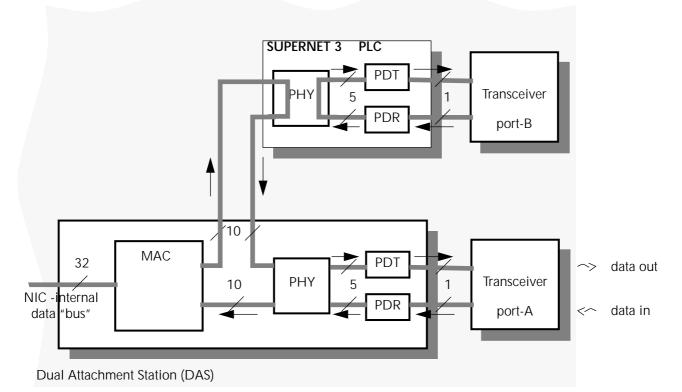

| 5.0.1         | DAS NIC                        | 26   |

| 3.9           |                                |      |

| 3.9           | Hardwired Values               |      |

| 3.9.1         |                                |      |

|               | Flash EPROM (FPROM)            |      |

| 3.9.3         | FPROM Loader                   |      |

| 3.9.4         | FPROM Loader                   |      |

| 3.9.5         | Initialization by Software     |      |

| 3.10          | Reset Behavior                 |      |

| 3.11          | Parity Generation/Control      | 42   |

| Configuration | on Space                       | . 44 |

| 5.1       Addressing the<br>Control Register File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 48<br>49<br>50 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.0.2       Command Register       4         4.0.3       Status Register       4         4.0.4       Cache Line Size, Latency,       4         4.0.5       Interrupt, Min_Gnt, Max_Latency       5         4.0.6       Base Address Register       5         4.0.7       Expansion ROM Base Address       5         4.0.8       Our_Register       5         4.0.8       Our_Register       6         5.1       Addressing the<br>Control Register File       6         5.1       Addressing the<br>Control Register Stack-       6         5.1.1       Register Address Port (RAP)       6         5.2       Various Registers       6         5.2.1       Control Register (DAS)       6         5.2.2       Control Register (DAS)       6         5.2.3       LED Register       6         5.2.4       Interrupt Source Register       6         5.2.5       Interrupt Mask Register       6         5.2.6       MAC-Address Registers       6 | 48<br>49<br>50 |

| 4.0.3       Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49<br>50       |

| 4.0.4       Cache Line Size, Latency,<br>Header Type, and BIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50             |

| Header Type, and BIST.       5         4.0.5       Interrupt, Min_Gnt, Max_Latency       5         4.0.6       Base Address Register       5         4.0.7       Expansion ROM Base Address       5         4.0.8       Our_Register       5 <b>Control Register File</b> 6         5.1       Addressing the<br>Control Register File.       6         5.1       Addressing the<br>Control Register File.       6         5.1.1       Register Address Port (RAP).       6         5.2       Various Registers.       6         5.2.1       Control Register (DAS)       6         5.2.3       LED Register       6         5.2.4       Interrupt Source Register       6         5.2.5       Interrupt Mask Register       6         5.2.6       MAC-Address Registers.       6                                                                                                                                                                   |                |

| 4.0.5       Interrupt, Min_Gnt, Max_Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| 4.0.6       Base Address Register       5         4.0.7       Expansion ROM Base Address       5         4.0.8       Our_Register       5         Control Register File         - The Entire Register Stack-       6         5.1       Addressing the<br>Control Register File.       6         5.1       Addressing the<br>Control Register Address Port (RAP).       6         5.2       Various Registers.       6         5.2.1       Control Register (DAS)       6         5.2.3       LED Register       6         5.2.4       Interrupt Source Register       6         5.2.5       Interrupt Mask Register       6         5.2.6       MAC-Address Registers.       6                                                                                                                                                                                                                                                                     | 52             |

| 4.0.7       Expansion ROM Base Address       5         4.0.8       Our_Register       6         Control Register File         - The Entire Register Stack-       6         5.1       Addressing the<br>Control Register File.       6         5.1       Addressing the<br>Control Register File.       6         5.1.1       Register Address Port (RAP).       6         5.2       Various Registers.       6         5.2.1       Control Register (DAS)       6         5.2.3       LED Register       6         5.2.4       Interrupt Source Register       6         5.2.5       Interrupt Mask Register       6         5.2.6       MAC-Address Registers.       6                                                                                                                                                                                                                                                                            |                |

| 4.0.8       Our_Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

| - The Entire Register Stack-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| 5.1       Addressing the<br>Control Register File         5.1.1       Register Address Port (RAP)         5.2       Various Registers         5.2.1       Control Register         5.2.2       Control Register (DAS)         5.2.3       LED Register         5.2.4       Interrupt Source Register         5.2.5       Interrupt Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| Control Register File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0              |

| 5.1.1       Register Address Port (RAP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| 5.2       Various Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| 5.2.1       Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| 5.2.2       Control Register (DAS) <t< td=""><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| 5.2.3         LED Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| 5.2.4         Interrupt Source Register                                                                                                     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| 5.2.5         Interrupt Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| 5.2.6 MAC-Address Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

| 5.2.7 Interface Type Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| 5.2.8 SUPERNET 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| 5.2.9 DAS Extension PLC-S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

| 5.2.10 Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59             |

| 5.2.11 Watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

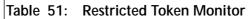

| 5.2.12 Restricted Token Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

| Electrical Interfaces 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '3             |

| 6.1 PCI Bus Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73             |

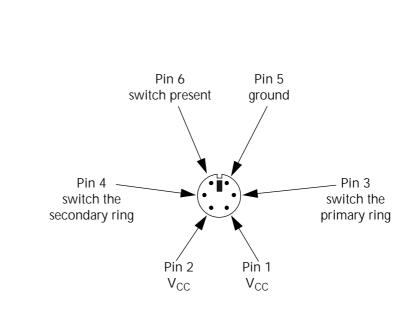

| 6.2 Mini DIN 6 Receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73             |

| 6.3 Copper Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74             |

| Technical Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6'             |

| 7.1 Standards Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76             |

| Appendix A:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| Control Register File 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8              |

| Appendix B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

| Testing the NIC 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84             |

| 9.0.1 Test Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34             |

| 9.0.2 Test FPROM Loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| 9.0.3 Test Downcounters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| (Timer, Watchdog, RTM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| 9.0.4 Test BMU Data Tranfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

## List of Tables

|                                                                                                          |                                                                                                                                                                                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                          |                                                                                                                                                                                                                                                      | Physical Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                                                                                 |

|                                                                                                          |                                                                                                                                                                                                                                                      | Programmable Resources Overview 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                                                                                                                                                 |

| Table                                                                                                    | 1:                                                                                                                                                                                                                                                   | Notations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   |

| Table                                                                                                    | 2:                                                                                                                                                                                                                                                   | Descriptor: Own_Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                                                |

| Table                                                                                                    | 3:                                                                                                                                                                                                                                                   | Transmit Descriptors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21                                                                                                                                                |

| Table                                                                                                    | 4:                                                                                                                                                                                                                                                   | Receive Descriptor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                                                                                                                                                |

| Table                                                                                                    | 5:                                                                                                                                                                                                                                                   | Receive /Transmit Queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                   |

|                                                                                                          |                                                                                                                                                                                                                                                      | Register Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27                                                                                                                                                |

| Table                                                                                                    | 6:                                                                                                                                                                                                                                                   | BMU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                   |

|                                                                                                          |                                                                                                                                                                                                                                                      | Control/Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                                                                                |

| Table                                                                                                    | 7:                                                                                                                                                                                                                                                   | <xxx></xxx>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                   |

|                                                                                                          |                                                                                                                                                                                                                                                      | Queue Flag Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29                                                                                                                                                |

| Table                                                                                                    | 8:                                                                                                                                                                                                                                                   | Data Structure of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

|                                                                                                          |                                                                                                                                                                                                                                                      | Initialization Values in the FPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88                                                                                                                                                |

| Table                                                                                                    | 9:                                                                                                                                                                                                                                                   | FPROM Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                   |

|                                                                                                          |                                                                                                                                                                                                                                                      | Register/Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 39                                                                                                                                                |

| Table                                                                                                    | 10:                                                                                                                                                                                                                                                  | Initialization Mode Register 1 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |

| Table                                                                                                    |                                                                                                                                                                                                                                                      | Initialization Mode Register 2 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                |

| Table                                                                                                    |                                                                                                                                                                                                                                                      | Initialization Mode Register 3 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11                                                                                                                                                |

| Table                                                                                                    |                                                                                                                                                                                                                                                      | Frame Threshold Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                   |

| Table                                                                                                    | 10.                                                                                                                                                                                                                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                   |

|                                                                                                          |                                                                                                                                                                                                                                                      | CONNOUS ANOT SUACE 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4                                                                                                                                                 |

|                                                                                                          |                                                                                                                                                                                                                                                      | Configuration Space 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                   |

| Table                                                                                                    |                                                                                                                                                                                                                                                      | Configuration Registers 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                                                                                                 |

| Table                                                                                                    | 15:                                                                                                                                                                                                                                                  | Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4<br> 5                                                                                                                                           |

| Table<br>Table                                                                                           | 15:<br>16:                                                                                                                                                                                                                                           | Configuration Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4<br>15<br>15                                                                                                                                     |

| Table<br>Table<br>Table                                                                                  | 15:<br>16:<br>17:                                                                                                                                                                                                                                    | Configuration Registers.         4           Vendor ID         4           Device ID.         4           Subsystem Vendor ID         4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4<br>15<br>15                                                                                                                                     |