# Short Papers\_

## Interconnect Coupling-Aware Driver Modeling in Static Noise Analysis for Nanometer Circuits

Xiaoliang Bai, Rajit Chandra, Sujit Dey, and Prasanna V. Srinivas

Abstract-With geometries shrinking in nanometer technologies, crosstalk noise becomes a critical issue. Modern designs like system-on-chips have millions of noise-prone nodes, mandating fast yet accurate crosstalk noise analysis techniques. Using linear circuit model, static noise analysis can efficiently estimate crosstalk noise. Traditionally in static noise analysis, drivers' holding resistances are precharacterized without considering the potential impact of crosstalk noise. However, crosstalk induced voltage fluctuation strongly affects the behavior of nonlinear drivers. When facing different coupling interconnects and hence crosstalk noise, a driver's holding resistance can change dramatically. In nanometer circuits, this substantial variation of nonlinear drivers cannot be totally ignored. To achieve high-quality in noise estimation yet maintain the efficiency of linear circuit model, we propose a novel interconnect coupling-aware driver modeling method. Based on layout-extracted interconnect parameters and precharacterized driver models, an effective holding resistance is calculated to capture the impact of the nonlinear driver. Multiple aggressors with synchronous and asynchronous switching activities are also considered. The proposed method is simple, efficient, and enables on-the-fly calculation of the effective holding resistance. Experiments show that with negligible computation overhead, the coupling-aware driver modeling methodology can significantly improve the quality of static noise analysis.

Index Terms—Driver, interconnect, noise analysis, signal integrity.

#### I. INTRODUCTION

Crosstalk is becoming an increasingly significant noise source in nanometer circuits, especially for low-power, high-performance designs. Due to high density interconnect, fast signal transition and small noise margin, crosstalk noise is one of the crucial issues that need to be addressed accurately and efficiently. Transistor-level simulation like SPICE is accurate but surfers from capacity limitation and time-consuming performance. For a modern design with millions of wires, transistor-level simulation becomes infeasible. Fast and accurate crosstalk estimation technique is needed to quickly identify nets that violate noise margins. In contrast to transistor-level simulation, static noise analysis can significantly speedup the noise analysis process by using linear circuit models with precharacterized gate models.

Various analytical noise-estimation models were proposed [1]–[3]. Much of the research effort was invested in modeling the intercon-

Manuscript received February 19, 2003; revised July 30, 2003. This work was supported in part by the MARCO/DARPA Gigascale Systems Research Center. This paper was recommended by Associate Editor F. N. Najm.

- X. Bai was with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093 USA. He is now with Magma Design Automation Inc., Santa Clara, CA 95054 USA (e-mail: xibai@magma-da.com).

- R. Chandra was with Magma Design Automation Inc., Santa Clara, CA 95054 USA. He is now with Gradient Design Automation Inc., Santa Clara, CA 95054 USA (e-mail: rajit@gradient-da.com).

- S. Dey is with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093 USA (e-mail: dey@ece.ucsd.edu).

- P. V. Srinivas was with Magma Design Automation Inc., Santa Clara, CA 95054 USA. He is now with Sierra Design Automation, Santa Clara, CA 95054 USA (e-mail: pvs@sierra-da.com).

Digital Object Identifier 10.1109/TCAD.2004.831568

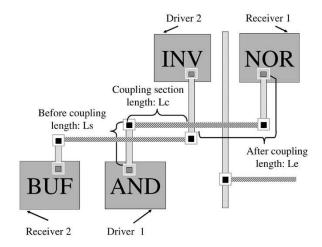

Fig. 1. Cross-coupling wires in layout.

nect and noise propagation property of receivers. Drivers were simply precharacterized with quiet (noiseless) inputs and outputs. However, with the interconnect voltage disturbed by crosstalk noise, the nonlinear driver behaves considerably different from the noiseless situation. The ability to accurately and efficiently model drivers under crosstalk noise perturbation will help to improve the quality of static noise analysis.

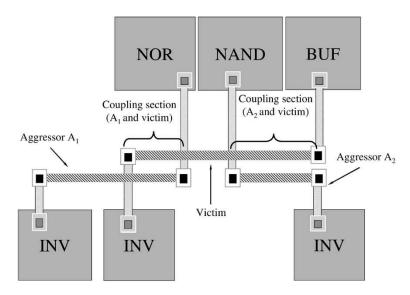

Fig. 1 shows an example of coupling wires in layout. The wire-under-concern is normally referred to as the victim, and wires coupling to the victim though capacitances are aggressors. In Fig. 1, there are two wires coupling to each other: one wire is from an AND gate to an NOR gate, another wire is from an INV gate to a BUF gate. If we consider the wire from INV to BUF as the victim, then the wire from AND to NOR is the aggressor. To model the distributed nature of interconnect, coupling wires can be divided into different sections [2]. The parallel sections are coupling sections. From drivers to coupling sections are before coupling sections, and from the coupling sections to receivers are after coupling sections. Different sections of the victim wire are illustrated explicitly in Fig. 1.

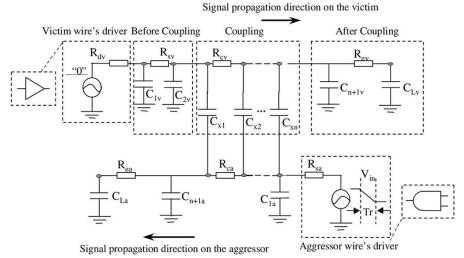

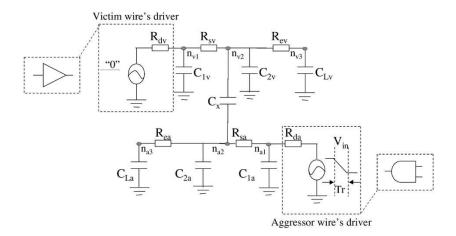

Linear circuit model is normally used in static noise analysis. Each section of the wire can be modeled by single or multiple lumped *RC* segments, as shown in Fig. 2. Different sections of the victim are labeled corresponding to the physical sections in the layout. Based on technology parameters, the number of *RC* segments needed to sufficiently model the distributed effect for each section of coupling interconnects, can be determined [4]. The aggressor driver is modeled by a Thevenin equivalent circuit [5], which consists of a saturated ramp voltage source and a resistance. The victim driver is simply modeled by a precharacterized holding resistance [6].

The victim driver's holding resistance is normally precharacterized using quiet inputs and outputs, without considering crosstalk noise perturbation. For a given standard cell, this single holding resistance value is used for all instantiations of the standard cell. However, the voltage of the victim driver's output is modulated by interconnect noise. Different wires will have different crosstalk noise sources. Even though the drivers are the same, the behavior can be totally dissimilar.

As a result of the changing voltage, a driver's holding resistance varies under noise interference and becomes a function of the output voltage  $V_{\rm driver\_out}$ . The voltage change induced by noise acts as a

Fig. 2. Linear circuit model (with multiple PI segments).

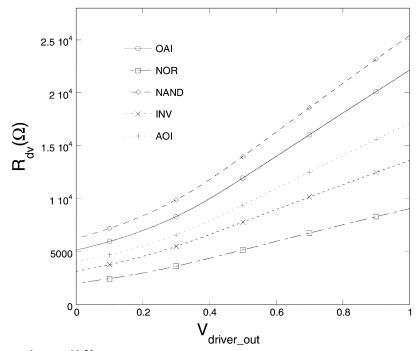

Fig. 3. Driver's holding resistance changes with  $V_{\rm \bf driver\_out}.$

voltage source. Therefore, instead of a constant Thevenin resistance, the driver's holding resistance is indeed a voltage-controlled resistance.

Using small signal analysis, the voltage-controlled holding resistance can be precharacterized with the dc value of the output voltage sweeping from GND to VDD. The characterization results of INV, NAND, NOR, AOI, and OAI gates are shown in Fig. 3. The x axis is the voltage source  $V_{\rm driver\_out}$  and the y axis is the driver's holding resistance. With the voltage source sweeping from 0 to VDD (1 v in these experiments), the holding resistance of INV gate changes from 3 to 14 k.

Closed-form formulas using different RC models such as L-type RC circuit [7], PI model [3], [8], 2-PI model [2], and 4-PI model [11] were developed based on different linear circuit models. One factor that affects the quality of static noise analysis is how good the linear model approximates the nonlinear circuit. Since driver's holding resistance can change dramatically, this potential variation has to be considered. However, most of the current noise estimation methods do not consider the driver's nonlinear property. Instead, a simple steady holding resistance  $R_{\rm steady}$  is used.

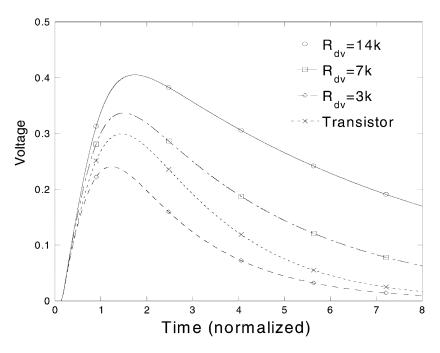

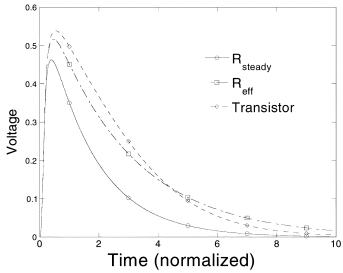

Fig. 4 shows SPICE simulation waveforms of crosstalk noise using different models for the INV gate: a nonlinear transistor model, the largest driver holding resistance value (14 k), the medium driver holding resistance value (7 k), and the smallest holding resistance value (3 k), respectively. The model with the largest possible holding resistance value overestimates the noise, whereas the model with the smallest holding resistance value underestimates the noise. In this example, the model with the medium resistance value overestimates the noise, but it may also underestimate the crosstalk noise for some other coupling situations. Using a single steady holding resistance ( $R_{\rm steady}$ ) for all instantiations of the gate may lead to large, unacceptable errors in noise estimation. Hence, a simple yet accurate modeling method is needed to efficiently capture the driver's nonlinear property.

A simulation-based method has been proposed to model *switching* drivers in noise-induced delay variation analysis [9]. A linear simulation waveform is firstly recorded and a noise-induced current is calculated. Then, nonlinear simulations with and without the injected noise current are performed and compared against each other. Finally,

Fig. 4. Simulation results with different  $R_{dy}$ 's and transistors.

a transient holding resistance is calculated. Comparing with the simple Thevenin resistance driver model [5], the simulation-based method greatly improves the accuracy. However, nonlinear circuit-level simulations and large lookup tables are needed, rendering it an accurate but expensive solution. In [10], driver is modeled by solving nonlinear differential equations separately and iteratively to achieve a better balance of accuracy and efficiency. Noise propagation is also considered in the method proposed in [10].

In this paper, we propose a simple yet accurate method to characterize and calculate effective holding resistances for the quiet victim drivers (aggressor is switching but the victim is intended to be stable) in static noise analysis. This method is interconnect coupling noise aware, captures the distributed nature of interconnects and is flexible to be used with different advanced interconnect noise estimation models. The remaining of this paper is organized as follows. Section II describes the proposed method of calculating effective holding resistances for quiet victim drivers based on physical information extracted from layout. In order to capture the distributed property of cross-coupling wires, an extended 2-PI model is also developed. Section III extends the method to handle synchronous and asynchronous multiple aggressors. In Section IV, we report experiments on different gates, demonstrating the accuracy of the coupling-aware driver modeling method. Section V concludes this paper.

## II. EFFECTIVE HOLDING RESISTANCE

To accurately model the nonlinear driver in static-noise analysis, the relationships among the holding resistance, the noise waveform and the coupling interconnects need to be carefully studied. In this section, we will use the INV gate as an example to develop the coupling-aware driver modeling method. In later sections, the proposed method will be validated on various gates and extended to handle situations with multiple aggressors.

### A. Voltage-Controlled Resistance

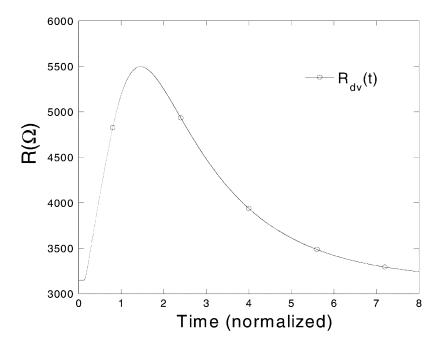

Crosstalk noise on the victim wire modulates the nonlinear driver's holding resistance. Based on the holding resistance characterization data  $R_{\rm dv}(v)$  in Fig. 3 and the noise waveform v(t) using nonlinear

model in Fig. 4, we can get the function of the changing holding resistance over time  $R_{\rm dv}(t)$ . The function for the gate INV is shown in Fig. 5.

The same driver that drives different interconnect parameters will have totally different holding resistances because of the impact of coupling noise. In order to efficiently estimate the noise's impact on a driver, a simple relationship between the holding resistance and the output voltage source is preferred.

From Fig. 3 we notice that the relationship of the holding resistance with respect to the output voltage can be approximated by a linear function

$$R_{\rm dy}(v) = kv + R_0 \tag{1}$$

where  $R_0$  is the smallest steady holding resistance and k is the gradient with respect to the voltage at driver's output node.

Similarly, other gates, like AND, NOR, AOI, and OAI, can also be characterized and the R–V relations can be approximated by (1). Although this simplified linear relation ignores some detailed nonlinear factors in the R–V curves, later our experiments will show that it provides a sufficiently accurate and efficient solution for static noise analysis.

As shown in Fig. 5, the holding resistance is modulated by interconnect noise. If the noise waveform v(t) is known, we will be able to get the "holding resistance" value at any given time

$$R_{\rm dv}(t) = kv(t) + R_0. \tag{2}$$

Next, we present a scalable and flexible noise-estimation technique that will be used to provide driver-end noise waveform v(t) in the coupling-aware driver-modeling method.

## B. Extended 2-PI Model

To facilitate fast and accurate noise estimation, we extended the 2-PI model [2] to consider interconnect distributed property, not only for the victim, but also for the aggressor. Unlike the 4-PI model [11], the extended 2-PI model does not need to decouple the aggressor and the victim. The extended 2-PI model can handle various coupling situations: the signal propagation directions of coupling wires can be same

Fig. 5. Drive holding resistance changes over time.

Fig. 6. Simple example of linear circuit (single RC segment for each section).

or reversed; the victim can have single/multiple aggressors and the coupling can happen at different locations with multiple coupling noise sources.

The extended 2-PI model can have an arbitrary number of *RC* segments for each sections (coupling, before coupling, and after coupling), as shown by the example in Fig. 2. It models the aggressor-slew degradation and can provide moments for any node of interest on the coupling interconnects. Next, we will use a simple linear circuit as an example. As shown in Fig. 6, we use one *RC* segment for each section (before coupling, coupling, and after coupling) in this example. Note that the extended 2-PI model can handle linear circuits with arbitrary number of *RC* segments.

In the example shown in Fig. 6, the coupling nodes are set to be the center of the coupling sections for the victim and aggressor, respectively. Suppose the length of the victim's coupling section is  $L_c$ , the length of before coupling section is  $L_s$ , and the length of after coupling section is  $L_e$  (as shown in Fig. 1). The coupling node is set to  $L_s + L_c/2$  from the driver.  $R_{\rm sa}$  and  $R_{\rm sv}$  are the total wire resistances from drivers to the coupling nodes for the aggressor and victim, respectively.  $R_{\rm ea}$

and  $R_{\rm ev}$  are the total wire resistances from the coupling nodes to the receivers of the aggressor and victim wires, respectively. The capacitances  $(C_{\rm La}, C_{\rm 1a}, C_{\rm 2a})$  and  $(C_{\rm Lv}, C_{\rm 1v}, C_{\rm 2v})$  are the load and ground capacitances of the aggressor and victim.  $C_x$  is the cross-coupling capacitance of the coupling sections. The parameters of the linear circuit are calculated based on the corresponding physical information [2].

Similar to asymptotic waveform evaluation in [12] and [13], the moment-matching technique is adapted and used to analyze the coupling *RC* network: coupling capacitance is replaced with voltage-controlled current source. Using impulse as input stimulus, the transfer function's moments can be calculated recursively by simple dc analysis. In this example, the zeroth moments for the aggressor and victim are

$$m_0^{a1} = m_0^{a2} = m_0^{a3} = 1$$

$m_0^{v1} = m_0^{v2} = m_0^{v3} = 0.$  (3)

Here,  $m_0^{\rm a\, 1}$  stands for the zeroth voltage moment of node  $n_{\rm a\, 1}$  of the aggressor in Fig. 6.

Replacing capacitances with current sources, we can calculate the first moments

$$m_{1}^{a1} = -R_{da}(C_{1a} + C_{2a} + C_{La} + C_{x})$$

$$m_{1}^{a2} = -R_{da}(C_{1a} + C_{2a} + C_{La} + C_{x})$$

$$-R_{sa}(C_{2a} + C_{La} + C_{x})$$

$$m_{1}^{a3} = -R_{da}(C_{1a} + C_{2a} + C_{La} + C_{x})$$

$$-R_{sa}(C_{2a} + C_{La} + C_{x}) - R_{ea}C_{La}$$

$$m_{1}^{v1} = R_{dv}C_{x}$$

$$m_{1}^{v2} = (R_{dv} + R_{sv})C_{x}$$

$$m_{1}^{v3} = (R_{dv} + R_{sv})C_{x} = m_{1}^{v2}$$

(4)

and the second moments can be calculated by using the first moments

$$\begin{split} m_{2}^{\text{a1}} &= -R_{\text{da}} \left( m_{1}^{\text{a1}} C_{1\text{a}} + m_{1}^{\text{a2}} C_{2\text{a}} \right. \\ &+ m_{1}^{\text{a3}} C_{\text{La}} + \left( m_{1}^{\text{a2}} - m_{1}^{\text{v2}} \right) C_{\text{x}} \right) \\ m_{2}^{\text{a2}} &= -R_{\text{da}} \left( m_{1}^{\text{a1}} C_{1\text{a}} + m_{1}^{\text{a2}} C_{2\text{a}} \right. \\ &+ m_{1}^{\text{a3}} C_{\text{La}} + \left( m_{1}^{\text{a2}} - m_{1}^{\text{a2}} \right) C_{\text{x}} \right) \\ m_{2}^{\text{a3}} &= m_{2}^{\text{a2}} - R_{\text{ea}} m_{1}^{\text{a3}} C_{\text{La}} \\ &- R_{\text{sa}} \left( m_{1}^{\text{a2}} C_{2\text{a}} + m_{1}^{\text{a3}} C_{\text{La}} + \left( m_{1}^{\text{a2}} - m_{1}^{\text{v2}} \right) C_{\text{x}} \right) \\ m_{2}^{\text{v1}} &= -R_{\text{dv}} \left( m_{1}^{\text{v1}} C_{1\text{v}} + m_{1}^{\text{v2}} C_{2\text{v}} + m_{1}^{\text{v3}} C_{\text{Lv}} \right. \\ &+ \left. \left( m_{1}^{\text{v2}} - m_{1}^{\text{a2}} \right) C_{\text{x}} \right). \end{split} \tag{5}$$

Using one pole model to approximate the transfer function for victim driver-end node  $n_{v1}$ , we have

$$H(s) = \frac{a_1 s}{b_1 s + 1} = m_1^{v \, 1} + m_a^{v \, 1} s + m_2^{v \, 1} s^2. \tag{6}$$

From (6), we can get

$$a_1 = m_1^{v_1} \text{ and } b_1 = \frac{m_2^{v_1}}{m_1^{v_1}}.$$

(7)

Suppose the aggressor's voltage source is modeled by a saturated ramp with a rising time  $T_r$ , then the noise voltage at node  $n_{v1}$  is

$$V_{v1}(s) = H(s) \cdot V_{agg}(s) = \frac{a_1 s}{b_1 s + 1} \cdot \frac{1 - e^{-sT_r}}{s^2 T_r}$$

(8)

By translating formula (8) back to time domain, we have the noise waveform function for driver-end node  $n_{v1}$ :

$$v_{\text{driver\_out}}(t) = v_{v1}(t) = \begin{cases} \frac{a_1}{T_r} \left( 1 - e^{\frac{1}{b_1}} \right), & 0 \le t \le T_r \\ \frac{a_1}{T_r} \left( e^{\frac{1 - T_r}{b_1}} - e^{\frac{1}{b_1}} \right), & t \le T_r. \end{cases}$$

In a first order approximation, the maximum value of the noise occurs at time  $T_r$ . Thus, the noise magnitude  $v_{\rm mag}$  is

$$v_{\text{mag}} = \frac{a_1}{T_r} \left( 1 - e^{\frac{T_r}{b_1}} \right). \tag{10}$$

With the knowledge of voltage-controlled holding resistance and the noise waveform at the victim's driver-end node, we will be able to estimate the noise-induced variations on the driver's holding resistance in the next section.

#### C. Effective Holding-Resistance Approximation

To capture the nonlinear behavior of the driver over a specified time span, an effective holding resistance can be calculated for the linear circuit, such that the estimated noise magnitude and area (under noise waveform) will be close to the nonlinear circuit model. From Section II-A, we know that the victim driver's holding resistance is a function of the driver-end node voltage. If a noise occurs, the holding resistance will be different from the  $R_0$ . Using a positive glitch (noise generated on signal "0" toward "1") as an example, the aggressor switches at time 0 and a positive glitch will be generated on the victim. At time  $T_1$ , the noise voltage drops to a voltage level  $V_{\rm zero\_th}$ , such that the perturbation on the holding resistance can be safely neglected. To model the overall effect of the changing resistance, we use an average holding resistance value for the period of noise  $(0 \sim T_1)$ . Therefore, the time constant of the linear circuit will be the same as the average value of the time constant of the nonlinear circuit. The average holding resistance value,  $R_{\rm dv\_eff}$ , is an effective holding resistance. Selection of the  $V_{\rm zero\_th}$  and, hence, the noise settle down time  $T_1$  plays an important role here. The larger the voltage  $V_{

m zero\_th}$  is, the more important for the higher section of the noise's waveform will be, and a larger effective holding resistance will be calculated. Since different circuits will have different noise magnitudes, we choose  $V_{\text{zero\_th}}$  to be proportional to noise magnitudes, e.g., 1/n of the magnitudes

$$v(T_1) = v_{\text{zero\_th}} = \frac{1}{n} v_{\text{mag}}.$$

(11)

Here, the "n" is a user controllable parameter. It can be tuned for different designs/technologies to achieve optimal results.

From (9)–(11), we have

$$T_1 = T_r + b_1 \ln n. (12)$$

Then, the driver's effective holding resistance, which is the average holding resistance from time 0 to  $T_1$ , can be calculated as

$$R_{\text{dv\_eff}} = \frac{\int_{0}^{T_{1}} R_{\text{dv}}(t)dt}{T_{1}} = k \frac{\int_{0}^{T_{1}} v_{1}(t)dt}{T_{1}} + R_{0}.$$

(13)

Thus, from (9) and (13) we have

$$R_{\text{dv\_eff}} = \frac{k}{T_1} \left( a_1 + \frac{a_1 b_1}{T_r} \left( e^{\frac{T_1}{b_1}} - \frac{1}{n} \right) \right) + R_0.$$

(14)

The calculation of the effective holding resistance is a "chicken and egg" problem:  $R_{\rm dv\_eff}$  is a function of the noise, whereas the noise estimation is strongly affected by the holding resistance, which is not known *a priori*. Hence, we use an iterative procedure to solve the problem.

- Step 1) Set initial  $R_{\text{eff}}$  value using  $R_{\text{steady}}$ .

- Step 2) Calculate the moments for all nodes.

- Step 3) Calculate the noise settle down time  $T_1$  using (12).

- Step 4) Calculate a temp-effective holding resistance  $R_{\rm eff}$  using (14).

Step 5) If the change of  $R_{\rm eff}$  is larger than stop criterion, use  $R_{\rm eff}$  as initial value and go to Step 2.

Since this method only involves closed-form formulas and simple dc analysis for moment calculations, the iteration requires little computation effort. After the iteration procedure converges, we will have an effective holding resistance. Moments calculated in this procedure can also be used to estimate the induced noise at the receiver-end node.

#### III. MULTIPLE AGGRESSORS

In real designs, a wire normally faces noise sources consisting of multiple aggressors. In this section, we address the driver's modeling problem for multiple-aggressors. An example circuit with multiple aggressors is shown in Fig. 7. For the purpose of illustration, we assume that two aggressors  $A_1$  and  $A_2$  are attacking the victim. Traditionally,

Fig. 7. Victim wire facing multiple aggressors.

Fig. 8. Multiple aggressors and corresponding noise waveforms. (a) Aggressors' signals. (b) Noise cause by aggressor  $A_1$ . (c) Noise cause by aggressor  $A_2$ .

each aggressor/victim pair is analyzed separately. Then, superposition of two noise waveforms is performed with a steady holding resistance as the victim's driver model. However, the direct use of superposition will introduce large error, and the victim driver's nonlinear property cannot be safely neglected.

In the coupling-aware driver-modeling method, a corresponding linear *RC* circuit is constructed for each aggressor-victim pair. Taking advantage of the simplified linear relationship between the holding resistance and the output voltage, (13) can be extended to calculate the effective holding resistance for a victim that faces multiple aggressors

$$R_{dv\_eff} = \frac{\int\limits_{0}^{T} R_{dv}(t)dt}{T} = k \sum_{i \in \text{aggressors}} \frac{\int\limits_{0}^{T_{i}} v_{i}(t)dt}{T_{i}} + R_{0}.$$

(15)

Next, we will illustrate the noise estimation process under situations with synchronous and asynchronous aggressors.

TABLE I ACCURACY OF LINEAR CIRCUIT MODELS USING  $R_{\rm eff}$  AND  $R_{\rm steady}$  DRIVER MODELS

|      |                              | Error (area) |         | Error (magnitude) |         |

|------|------------------------------|--------------|---------|-------------------|---------|

| Gate | Method                       | Maximum      | Average | Maximum           | Average |

| INV  | R <sub>steady</sub> (small)  | 52.9%        | 35.2%   | 25.3%             | 15.5%   |

|      | R <sub>Steady</sub> (medium) | 117.6%       | 44.6%   | 73.2%             | 8.5%    |

|      | R <sub>steady</sub> (high)   | 317.2%       | 176.4%  | 184.2%            | 23.4%   |

|      | R <sub>eff</sub>             | 5.9%         | 2.1%    | 7.2%              | 3.2%    |

| NAND | R <sub>steady</sub> (small)  | 50.0%        | 33.7%   | 17.9%             | 10.1%   |

|      | R <sub>Steady</sub> (medium) | 123.0%       | 52.1%   | 41.2%             | 5.9%    |

|      | R <sub>steady</sub> (high)   | 284.8%       | 151.2%  | 68.3%             | 12.8%   |

|      | R <sub>eff</sub>             | 9.1%         | 4.0%    | 4.3%              | 1.9%    |

| AOI  | R <sub>steady</sub> (small)  | 49.0%        | 33.1%   | 23.7%             | 12.4%   |

|      | R <sub>Steady</sub> (medium) | 128.9%       | 60.1%   | 54.4%             | 9.3%    |

|      | R <sub>steady</sub> (high)   | 301.9%       | 175.6%  | 192.3%            | 20.1%   |

|      | R <sub>eff</sub>             | 10.1%        | 4.9%    | 5.6%              | 2.2%    |

#### A. Synchronous Switching Aggressors

For synchronous aggressors, the effective holding resistance should consider the noise perturbations from all the aggressors. Even though separate linear-circuit models are constructed for each aggressor-victim pair, they actually share the same driver. The procedure of calculating the effective holding resistance is similar to the one for single aggressor. The only difference is that this iteration procedure involves noise estimations for the all the aggressor-victim pairs. Impacts from all the aggressors are considered in order to calculate the effective holding resistance, as shown in (15). After the iteration procedure converges, superposition can be applied to estimate the overall noise effect using the effective holding resistance.

## B. Overlapping Asynchronous Switching Aggressors

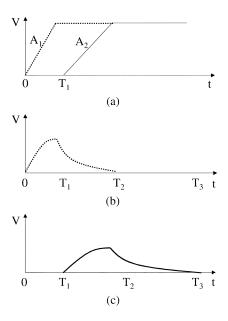

For situations in which multiple aggressors are asynchronous and the noise waveforms overlap each other, noise analysis can be performed in a multisegment fashion. Suppose aggressor  $A_1$  switches at time 0, and the noise settles down at time  $T_2$ . Aggressor  $A_2$  switches at time  $T_1$  and the noise settles down at time  $T_3$ . Without loss of generality, we can assume  $0 < T_1 < T_2 < T_3$  as an example. Fig. 8(a) shows the signals of two aggressors in such a situation. The switching signal of aggressor  $A_1$  is shown by a dotted line, and the switching signal of aggressor  $A_2$  is shown by a solid line. The corresponding noise waveforms, which are generated by only one active aggressor (assume another is quiet)

Fig. 9. Comparison: linear model (using effective holding resistance) versus nonlinear model. (a) Noise magnitude. (b) Noise area.

are shown in Fig. 8(b) and (c) for aggressor  $A_1$  and  $A_2$ , respectively. Note that in the steady holding resistance method, the overall noise effect is calculated by simply superposing these two noise waveforms.

In the coupling-aware driver-modeling method, the noise waveforms are first estimated and examined for timing information. According to the switching time of aggressors and the estimated noise waveforms, the combined crosstalk noise will be analyzed in three time periods for this example:  $0 \sim T_1, T_1 \sim T_2$ , and  $T_2 \sim T_3$ . There are three effective holding resistances  $R_{\rm eff1}$ ,  $R_{\rm eff2}$ , and  $R_{\rm eff3}$ , corresponding to the three time periods. Using (15) with the corresponding active aggressor(s) in each period, we have

$$R_{\text{eff 1}} = k \frac{\int_{0}^{T_1} v_1(t)dt}{T_1} + R_0$$

$$R_{\text{eff 2}} = k \frac{\int_{0}^{T_2} (v_1(t) + v_2(t))dt}{T_2 - T_1} + R_0$$

(16)

$$R_{\text{eff2}} = k \frac{\int_{T_1}^{T_2} (v_1(t) + v_2(t)) dt}{T_2 - T_1} + R_0$$

(17)

Fig. 10. Simulation waveforms using  $R_{\rm steady}$ ,  $R_{\rm eff}$  and nonlinear model.

Fig. 11. Noise waveforms using steady, effective holding resistance and nonlinear model.

$$R_{\text{eff3}} = k \frac{\int_{T_2}^{T_3} v_2(t) dt}{T_3 - T_2} + R_0.$$

(18)

Linear circuits with  $R_{\text{eff}1}$ ,  $R_{\text{eff}2}$ , and  $R_{\text{eff}3}$  will be used in static noise analysis for the corresponding time periods.

## IV. EXPERIMENTAL RESULTS

Experiments were conducted to validate the proposed method. Using parameters of a 0.18- $\mu$ m technology extracted from the ITRS roadmap [14], we construct test cases by randomly generating coupling interconnects. The length of the before coupling, after coupling, and coupling sections varies from 1 to 3000  $\mu$ m. The aggressor's driver slew changes from 10 to 300 ps and the load capacitances are in the range of 4 to 50 pF. For each randomly generated test case, an effective holding resistance is calculated using the proposed method. Linear circuits with the effective holding resistance and different steady holding resistances (the smallest value, the medium value, and the largest value) are simulated and compared with circuits using nonlinear driver model. Experiments were conducted for INV, NAND, and AOI gates.

ACCURACY OF STATIC NOISE ESTIMATION (NOISE MAGNITUDE) USING DIFFERENT MODELS

Gate Average Error (R<sub>steady</sub>) Average Error (R<sub>eff</sub>)

| Gate | Average Error (R <sub>steady</sub> ) | Average Error (R <sub>eff</sub> ) |

|------|--------------------------------------|-----------------------------------|

| INV  | 9.6%                                 | 3.7%                              |

| NAND | 12.4%                                | 3.3%                              |

| AOI  | 11.2%                                | 4.1%                              |

TABLE II

Whether a noise can cause an error depends on not only the noise magnitude but also the area of the noise waveform (the *energy* of the noise). Therefore, for all the test cases we compare both the magnitude and the area of the noise waveforms. The simulations are conducted with nonlinear transistors, effective holding resistance, and different steady holding resistances as the driver models, respectively. The nonlinear model acts as a golden reference and errors are calculated by comparing with the nonlinear model's simulation results.

Table I shows errors in noise area and magnitude estimations, using different linear circuit models. For 2000 randomly generated test cases, the model using effective holding resistance shows significant advantage in accuracy. The computation overhead of the effective holding resistance method is small: on average, each test case takes 0.027 s on a Sun Ultra 10 workstation, using Perl scripts. The execution time includes reading and parsing parameter files, creating and changing directories and noise estimations. The iteration procedure also converges very fast: for a stop criterion of 0.001  $\Omega$ , the largest number of iterations is 8 and the average number of iterations is 6.05. In all these experiments, we set the controllable parameter "n" to 10.

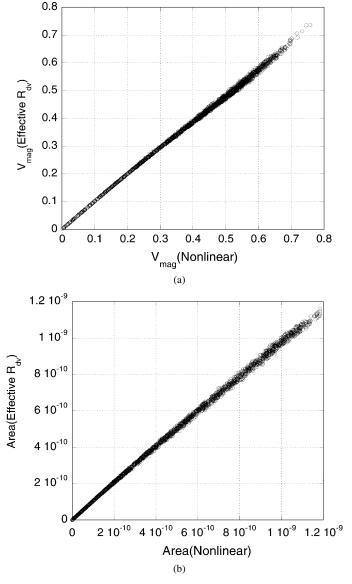

Fig. 9 shows scatter diagrams that compare the effective holding resistance method (y axis) with the nonlinear model (x axis). Fig. 9(a) is for noise magnitudes and Fig. 9(b) is for noise areas (energy). It shows that over a large range of noise magnitude and energy, the effective holding resistance method is consistently accurate.

The proposed method on multiple aggressors was also validated. Test cases were randomly generated for the example described in Section III. Fig. 10 shows the noise waveforms in one of the test cases, generated by using different driver modeling methods with synchronous aggressors. Comparing with the steady holding resistance model, the effective holding resistance method is much better in emulating the behavior of the nonlinear circuit.

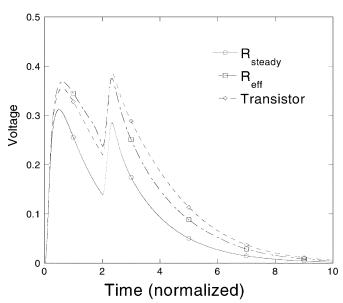

For asynchronous aggressors, the effective holding resistance method also shows significant improvement. In one randomly generated test case, aggressor  $A_1$  switches at time 0 with  $T_{\rm r1}=129$  ps and another aggressor  $A_2$  switches at time  $T_1=2$  ns with  $T_{\rm r2}=259$  ps. Fig. 11 shows simulation results of circuits using different driver models. The waveform of the effective holding resistance consistently approximates the waveform of the nonlinear circuit much better than using the steady holding resistance in all of our experiments.

The improvement of using the effective holding resistance model in static noise analysis was examined on test cases with synchronous multiple aggressors. Using the effective holding resistance driver model and an  $R_{\rm steady}$  model (the smallest value), static-noise analysis is performed on 1000 randomly generated test cases, with randomly selected transition directions of the aggressors' signals. The estimated noise magnitudes are compared with HSPICE simulation results. Table II shows the average errors of using  $R_{\rm eff}$  and  $R_{\rm steady}$  methods for different drivers (INV, NAND, and AOI). Comparing with the steady holding resistance method, the effective holding resistance method provides an accurate yet efficient linear model for static crosstalk noise analysis.

#### V. CONCLUSION

In this paper, we present a simple yet efficient coupling-aware driver modeling method for static noise analysis. Drivers are precharacterized and an effective holding resistance is calculated based on layoutextracted physical information of the coupling interconnects. Comparing with traditional steady holding resistance method, the couplingaware driver model is capable of capturing the behavior of the nonlinear victim driver. It helps to enhance the quality of the static noise estimation. Synchronous and asynchronous multiple aggressors are also considered. The proposed method enables fast and accurate noise estimation with negligible computation overhead.

#### REFERENCES

- A. Devgan, "Efficient coupled noise estimation for on-chip interconnects," in *Proc. Int. Conf. Computer-Aided Design*, 1997, pp. 147–153.

- [2] J. Cong, D. Pan, and P. V. Srinivas, "Improved crosstalk modeling for noise constrained interconnect optimization," in *Proc. Asia South Pacific Design Automation Conf.*, 2001, pp. 373–378.

- [3] A. B. Kahng, S. Muddu, and D. Vidhani, "Noise and delay uncertainty studies for coupled RC interconnects," in Proc. IEEE Int. ASIC/SOC Conf., 1999, pp. 3–8.

- [4] S. H. Hall, High-Speed Digital System Design: A Handbook of Interconnect Theory and Practices. New York: Wiley, 2000.

- [5] F. Dartu and L. T. Pileggi, "Calculating worst-case delays due to dominant capacitance coupling," in *Proc. Design Automation Conf.*, 1997, pp. 46–51.

- [6] W. Roethig et al., "Signal integrity methodology on 300 MHz SoC design using ALF libraries and tools," in Proc. Design, Automation, Test Eur., 2003.

- [7] A. Vittal and M. Marek-Sadowska, "Crosstalk reduction for VLSI," IEEE Trans. Computer-Aided Design, vol. 16, pp. 290–98, Mar. 1997.

- [8] A. Vittal, L. Chen, M. Marek-Sadowska, K.-P. Wang, and S. Yang, "Crosstalk in VLSI interconnections," *IEEE Trans. Computer-Aided Design*, vol. 18, pp. 1817–24, Feb. 1999.

- [9] S. Sirichotiyakul, D. Blaauw, C. Oh, R. Levy, V. Zolotov, and J. Zuo, "Driver modeling and alignment for worst-case delay noise," in *Proc. Design Automation Conf.*, 2001, pp. 720–725.

- [10] V. Zolotov, D. Blaauw, R. Panda, and C. Oh, "Noise injection and propagation in high performance designs," in *Proc. Int. Symp. Quality Electron. Design*, 2002, pp. 425–430.

- [11] M. R. Becer, D. Blaauw, V. Zolotov, R. Panda, and I. N. Hajj, "Analysis of noise avoidance techniques in DSM interconnects using a complete crosstalk noise model," in *Proc. Design, Automation, Test Eur.*, 2002, pp. 456–463.

- [12] L. T. Pillage and R. A. Rohrer, "Asymptotic waveform evaluation for timing analysis," *IEEE Trans. Computer-Aided Design*, vol. 9, pp. 352–366, Apr. 1990.

- [13] Q. Yu and E. S. Kuh, "New efficient and accurate moment matching based model for crosstalk estimation in coupled RC trees," in Proc. Int. Symp. Quality Electron. Design, 2001, pp. 151–157.

- [14] Semiconductor Industry Association (SIA). International Technology Roadmap for Semiconductors. [Online] Available: http://public.itrs.net/