#

# 2006 Technology Analyst Day

Daryl Ostrander Senior Vice President, Logic Technology and Manufacturing

June 1, 2006

# Leadership in Process Technology and Manufacturing

# **Process Technology**

- SOI Technology

- Power-efficient building blocks for our industry leading architectures and designs

- Optimum technology development model

- Partnering to leverage resources and knowledge

# Manufacturing

- Capacity to equal customer demand

- Leading Manufacturing Capability

- Industry leading manufacturing metrics

- Taking it to the next level with Lean Manufacturing

Better Customer Experience Better Products Dependable Quality and Delivery

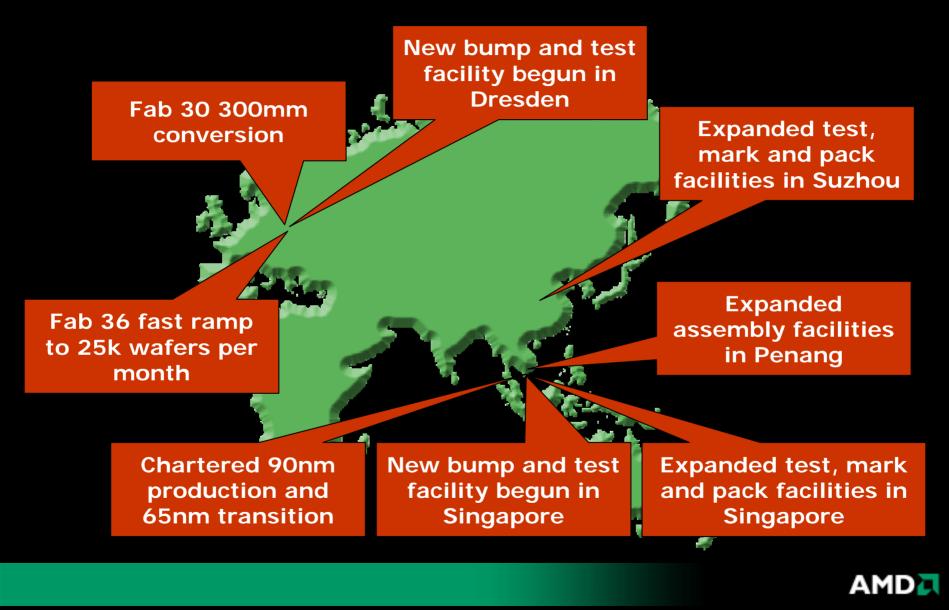

## **Comprehensive Global Capacity Expansion**

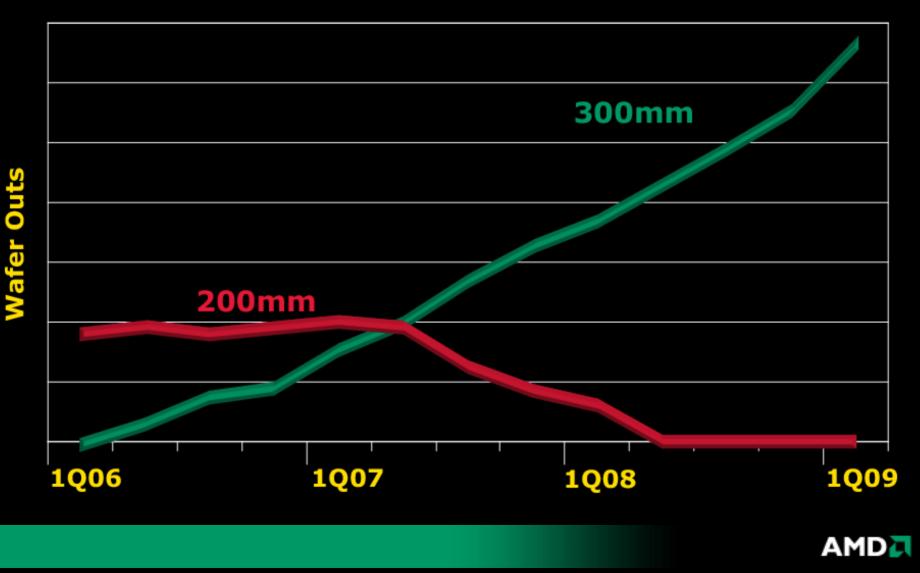

# Dresden Capacity Expansion to Meet the Anticipated Increase in Customer Demand

#### Conversion of Fab 30 to 300mm Fab 38

First wafer outs planned for first Q1 2008 20K wafers/month expected by Q4 2008 ~\$2 billion investment

# Fab 36 expanded to 25K wafers per month capability

25K wafers/month expected by Q4 2007 ~\$500M investment

# New onsite dedicated bump and test facility

#### Up to 4x Capacity Increase Potential

#### 2005 2009 Dresden Yearly Wafer Output

## Fab 38 Drives Total 300mm Production Increase in Dresden

5

# Fab 36: Highly Successful Ramp and 65nm Conversion On-Track

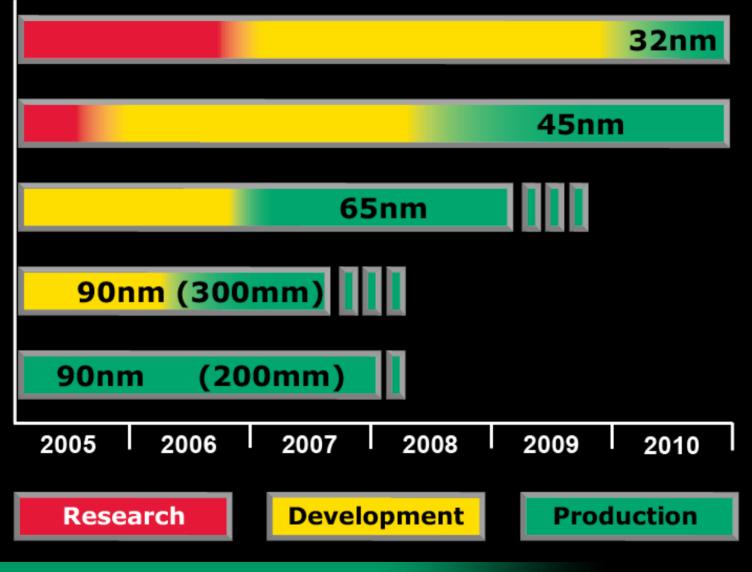

- First 90nm revenue shipments started 2Q 2006, on plan

- Fastest new fab ramp, started production at mature yields

- 65nm production shipments scheduled for 4Q 2006

- 65nm crossover expected in 1Q 2007, full conversion expected to be achieved in July 2007

- On track for volume 45nm production by mid-2008 1.5 years after 65nm

# Increased Chartered Capacity and 65nm Conversion

90nm production underway at Chartered six weeks ahead of schedule

Work with IBM and implementation of selected advanced process control capabilities at Fab 7 delivering excellent results

Plan to transition to 65nm in mid-2007

Foundry volumes a function of demand and pricing

# **Technology Roadmap**

# Technology Agreement with IBM Continues to Be Highly Beneficial to AMD

- **Consistent achievement of development objectives**

- Announced extension through 2011\*, expanded to include early exploratory research

- AMD expanding its R&D staff significantly

- 65nm development complete

- Currently working on 45nm, 32nm and 22nm technology generations

\*Capital purchases by IBM necessary for the continued development of process development projects past December 31, 2008 are conditioned upon the approval of IBM's board of directors

2006 Technology Analyst Day

June 1, 2006

# 65nm Volume Production On Track for Second Half 2006

Technology transfer to Fab 36 has been completed

Jointly developed by IBM and AMD in East Fishkill, NY and Dresden, Germany

SRAM yields at mature defect densities

Internal Revision G samples generated and production ready

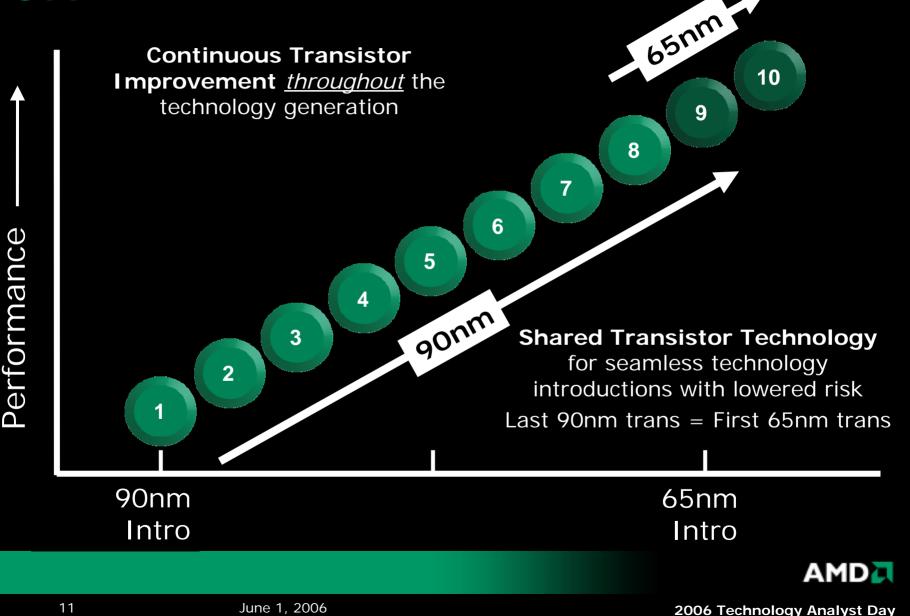

**Seamless production transition**

Use of 90nm-proven, high-performance SOI transistor Next generation transistor in 3 months

High-performance, power-efficient 65nm AMD64 processors on 300mm production wafer

# Smooth Transition to 65nm Using CTI and STT

# Using CTI to Maximize Transistor Performance and Power Efficiency

AMD makes relatively small, yet high-value changes to transistors on a regular basis for non-stop improvement with lowered risk

# **Great Progress on 45nm!**

Continuing to take full advantage of Silicon-on-Insulator for high-performance and increased power efficiency

#### Excellent progress on all development milestones working with IBM

Transistor performance milestones tracking to plan Working SRAMs achieved in January 2006 Excellent progress on Immersion Lithography

13

#### Aggressive schedule for first 45nm product introduction

AMD

# Leading the Industry to a New and Better Manufacturing Model

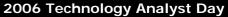

# AMD's Manufacturing Advantage

For over a decade, AMD has been creating a new and differentiated model focused on increasing operational speed, accuracy, agility and efficiency to maximize customer value

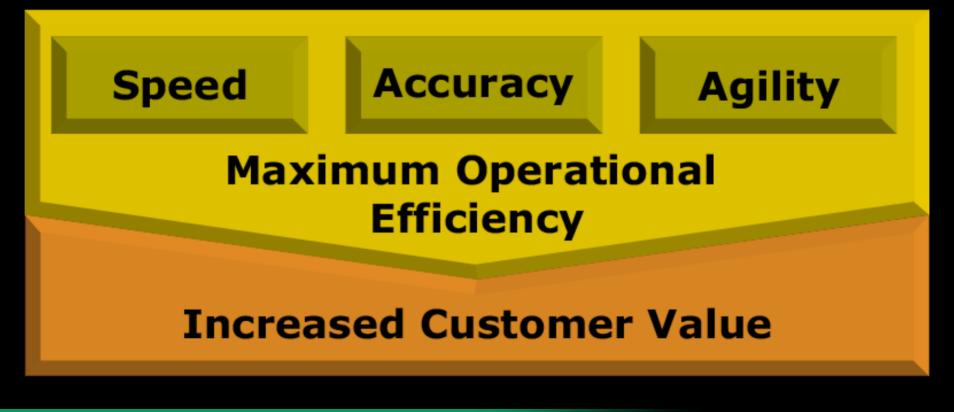

# APM: Unique Technology Framework Bridging Front- and Back-End Operations

Highly automated and synchronized *decision* <u>making</u>

Five integrated algorithmic analysis systems — much more than just APC

Includes proprietary technologies, logic and business processes

Introduction of lean methodologies for increased efficiency and agility

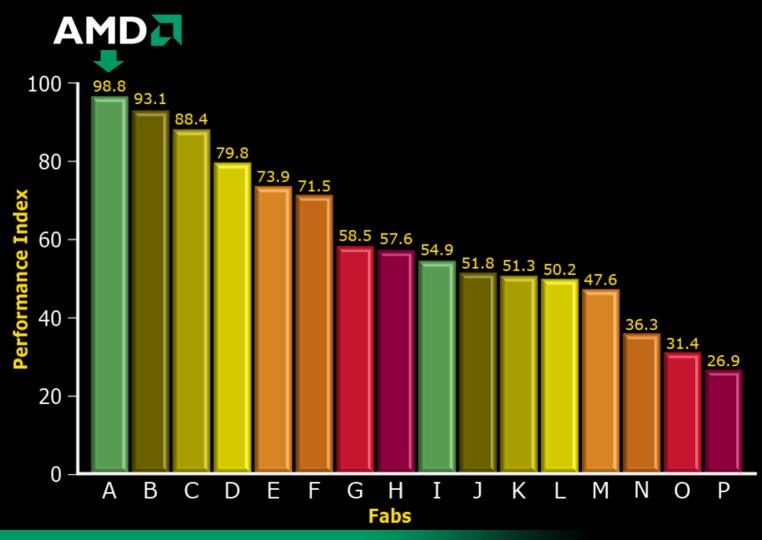

## Fab 30: Highest Performing Fab Six Years Running (1Q 1999 - 1Q 2005)

Source: Sematech

17

# **Best-in-Class Production Cycle Times**

Industry Worst

Industry Average

Industry Best

AMD Fab 30

Lower is better

Fab 30 is bestin-industry two years straight

#### 2004 - 2005

####

Sources: AMD & Sematech

# **Accelerated Yield Ramps**

Mature yield achieved ~40 percent faster than **Began** production Mature yield previous generation at mature yields in achieved ~66 Fab 36 percent faster than previous generation Mature Yield **Nafer Yiel** 90nm SOI Technology Fab 36 90nm SOI Technology Fab 30 130nm SOI Technology Fab 30 130nm Bulk Technology Fab 30

#### **Production Volume**

# **Extending the Reach and Benefits of APM**

#### Vision:

Maximizing operational efficiency and customer value-add, both within and outside of AMD owned facilities, using APM as the enabler for true end-to-end synchronization

# Our Industry Needs to Think Differently About the Role of Manufacturing

Manufacturing must play a concrete role in increasing value for customers and improving the customer experience

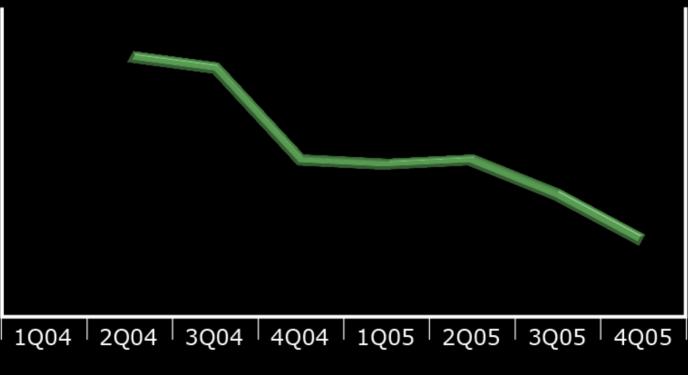

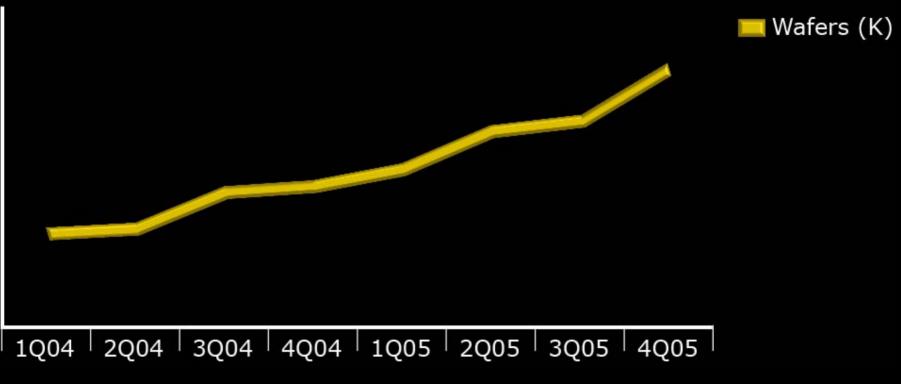

# Improved Cycle Time and Productivity Operational Improvements Achieved in Fab Wafer Output and Cycle Time Concurrently

Fab30 - Continuous Cycle Time Improvement

Cycle Time Improved 20%

# Improved Cycle Time and Productivity Operational Improvements Achieved in Fab Wafer Output and Cycle Time Concurrently

Fab30 - Continuous Productivity Improvement

Wafer Output Improved 47%

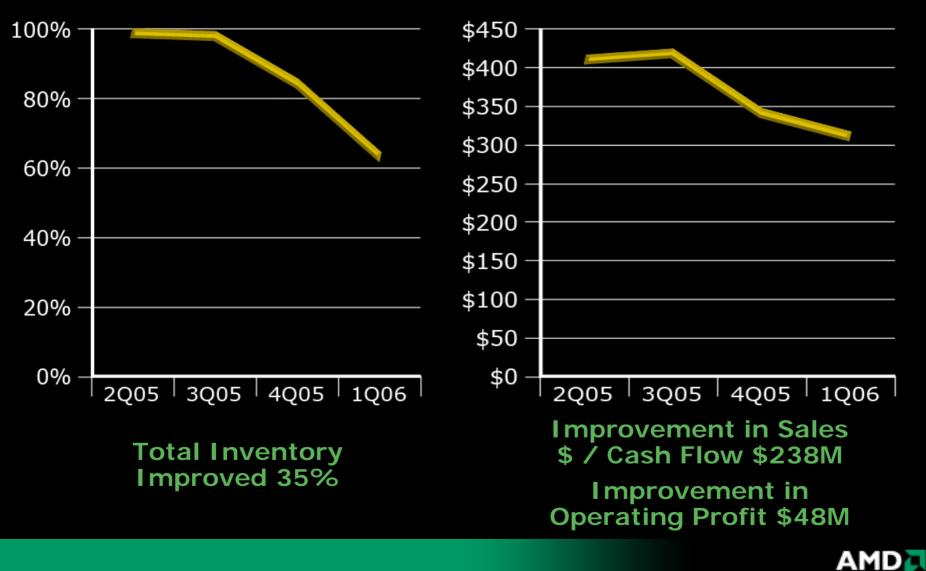

# **Opportunity meets Lean Preparedness**

**Total Inventory**

**MP \$ Gross Inventory**

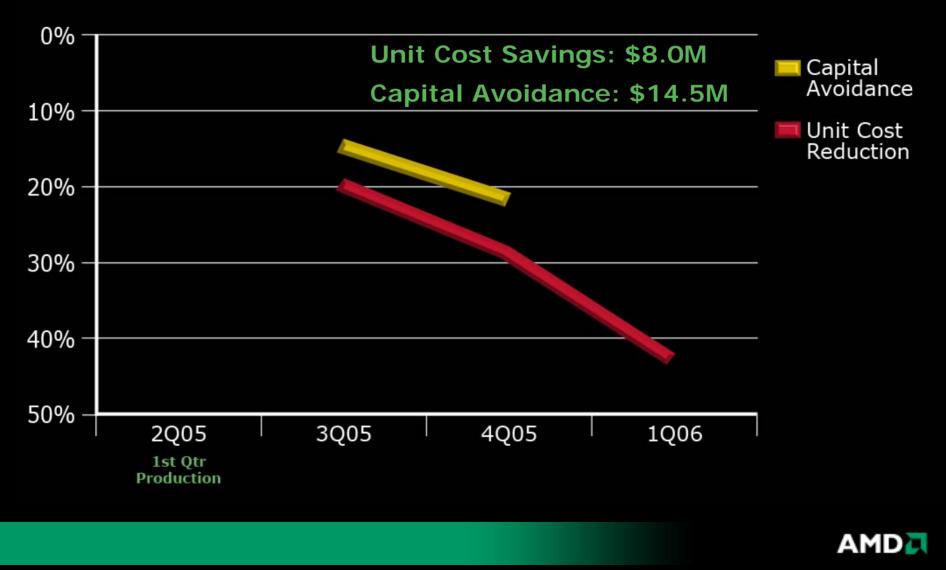

### Desktop Capital Avoidance and Unit Cost Reduction For Assembly and Test Operations

# AMD's Manufacturing Strategy -Flawless Execution Continues

Solid plans for increasing Dresden capacity by up to 4x in next three years

Highly Successful R&D relationships

65nm technology qualification on track

Expect mid-2008 45nm introduction

Taking our unique manufacturing advantage to the next level - Lean Manufacturing

Fully positioned to service 1/3 of the market by 2008

#### **Trademark Attribution**

AMD, the AMD Arrow logo and combinations thereof are trademarks of Advanced Micro Devices, Inc. in the United States and/or other jurisdictions. Other names used in this presentation are for identification purposes only and may be trademarks of their respective owners.

© 2006 Advanced Micro Devices, Inc. All rights reserved.