# **Summary**

Core Reference CR0116 (v1.5) December 12, 2005 The TSK52x is a fully functional, 8-bit microcontroller, incorporating the Harvard architecture. This core reference includes architectural and hardware descriptions, instruction sets and on-chip debugging functionality for the TSK52x family.

The TSK52x is an 8-bit embedded controller that executes all ASM51 instructions and is instruction set compatible with the 80C31.

#### **Features**

- Control Unit

- 8-bit Instruction decoder

- Reduced instruction cycle time up to 12 times.

- Arithmetic-Logic Unit

- 8 bit arithmetic and logical operations

- Boolean manipulations

- 8 x 8 bit multiplication and 8 / 8 bit division.

- 32-bit Input/Output ports

- Four 8-bit I/O ports

- Alternate port functions such as external interrupts and serial interface are separated, providing extra port pins when compared with the standard 8051.

- Interrupt Controller

- Four Priority Levels

- 7 external interrupts

- Internal Data Memory interface

- Can address up to 256 Bytes of Data memory Space.

- External Memory interface

- Can address up to 64 KB of external Program memory space

- Can address up to 64 KB of external Data memory space

- De-multiplexed Address/Data Bus to allow easy connection to memories

- Variable length code fetch and MOVC to access fast/slow Program memory

- Variable length MOVX to access fast/slow RAM or peripherals

- Wishbone-compliant (TSK52B\_W and TSK52B\_WD only)

#### **Performance**

The architecture eliminates redundant bus states and implements parallel execution of fetch and execution phases. Since a cycle is aligned with memory fetch when possible, most of the 1-byte instructions are performed in a single cycle. The TSK52x uses 1 clock cycle per machine (instruction) cycle. This leads to a more enhanced and efficient performance with respect to the industry standard 8051 processor working with the same clock frequency (in fact, the execution of instructions is an average eight times faster on the TSK52x).

The standard 8051 has a 12-clock architecture. A machine (instruction) cycle needs 12 clock cycles to execute to completion and most instructions require either one or two machine cycles. Therefore, with the exception of MUL and DIV, the 8051 uses either 12 or 24 clock cycles for each instruction. Furthermore, each cycle in the 8051 uses two memory fetches. In many cases the second fetch is a dummy and extra clock cycles are wasted.

Table 1 below shows the speed advantage of the TSK52x over the standard 8051. A speed advantage of 12 means that the TSK52x performs the same instruction twelve times faster that the 8051.

| Table 1 | Sneed | advantage | summanı |

|---------|-------|-----------|---------|

|         |       |           |         |

| Speed advantage | Number of instructions | Number of opcodes |

|-----------------|------------------------|-------------------|

| 24              | 1                      | 1                 |

| 12              | 27                     | 83                |

| 9.6             | 2                      | 2                 |

| 8               | 16                     | 38                |

| 6               | 44                     | 89                |

| 4.8             | 1                      | 2                 |

| 4               | 18                     | 31                |

| 3               | 2                      | 9                 |

| Average: 8.0    | Sum: 111               | Sum: 255          |

The average speed advantage is 8.0. However, the real speed improvement seen in any system will depend on the mixture of instructions used.

#### **Available Devices**

The following two variants of the microcontroller are available:

TSK52A - Standard version of the core

TSK52B\_W - Wishbone-compliant version of the core

In addition, a corresponding debug-enabled (OCD) version of each variant is also available (TSK52A\_D and TSK52B\_WD respectively).

**Note**: Throughout this document, differences between core variants are listed in terms of the standard core devices (TSK52A and TSK52B\_W). Unless specified otherwise, the feature/description applies to the debug-enabled version of the variant (TSK52A\_D and TSK52B\_WD) in exactly the same way.

These devices can be found in the FPGA Processors integrated library (\Program Files\Altium Designer 6\Library\Fpga\FPGA Processors.IntLib).

## **Architectural overview**

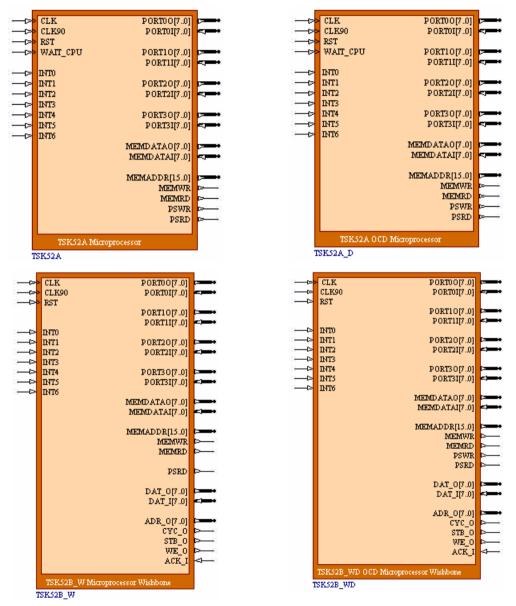

## **Symbols**

Figure 1. TSK52x family symbols

## **Pin description**

The pinout of the TSK52x has not been fixed to any specific device I/O, thereby allowing flexibility with user application. The TSK52x contains only unidirectional pins - inputs or outputs. To simplify using the bidirectional ports (PORT0-3), the schematic symbol includes a bus pin for each direction, allowing them to be wired independently. Configuration of bus direction is performed under program control.

Table 2. TSK52x Pin description

| Name                  | Туре | Polarity/Bus<br>size | Description                                                                                                  |

|-----------------------|------|----------------------|--------------------------------------------------------------------------------------------------------------|

|                       | •    | Co                   | ontrol Signals                                                                                               |

| CLK                   | I    | Rise                 | External system clock (used for internal clock counters and all other synchronous circuitry)                 |

| CLK90                 | I    | Rise                 | Second external clock with a phase lag of 90 Degrees in relation to CLK.                                     |

| RST                   | I    | High                 | External system reset. A high on this pin while the external system clock (CLK) is running resets the device |

| WAIT_CPU <sup>1</sup> | I    | High                 | When this signal is active, operation of the CPU is halted.                                                  |

|                       |      | Int                  | errupt Signals                                                                                               |

| INT0                  | I    | High/Rise            | External interrupt 0                                                                                         |

| INT1                  | I    | High/Rise            | External interrupt 1                                                                                         |

| INT2                  | I    | Fall/Rise            | External interrupt 2                                                                                         |

| INT3                  | I    | Fall/Rise            | External interrupt 3                                                                                         |

| INT4                  | I    | Rise                 | External interrupt 4                                                                                         |

| INT5                  | I    | Rise                 | External interrupt 5                                                                                         |

| INT6                  | I    | Rise                 | External interrupt 6                                                                                         |

|                       |      | I/O Por              | t Interface Signals                                                                                          |

| PORT0I                | I    | 8                    | Port 0 is an 8-bit bi-directional I/O port with separated                                                    |

| PORT0O                | 0    | 8                    | inputs and outputs                                                                                           |

| PORT1I                | I    | 8                    | Port 1 is an 8-bit bi-directional I/O port with separated                                                    |

| PORT10                | 0    | 8                    | inputs and outputs                                                                                           |

| PORT2I                | I    | 8                    | Port 2 is an 8-bit bi-directional I/O port with separated                                                    |

| PORT2O                | 0    | 8                    | inputs and outputs                                                                                           |

\_

<sup>&</sup>lt;sup>1</sup> TSK52A and TSK52A\_D only.

| Name                                                     | Туре | Polarity/Bus<br>size | Description                                                                                                                                                                                        |  |  |

|----------------------------------------------------------|------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PORT3I                                                   | I    | 8                    | Port 3 is an 8-bit bi-directional I/O port with separated                                                                                                                                          |  |  |

| PORT3O                                                   | 0    | 8                    | inputs and outputs                                                                                                                                                                                 |  |  |

|                                                          |      | External Me          | mory Interface Signals                                                                                                                                                                             |  |  |

| MEMDATAO                                                 | 0    | 8                    | External memory output                                                                                                                                                                             |  |  |

| MEMDATAI                                                 | I    | 8                    | External memory input                                                                                                                                                                              |  |  |

| MEMADDR                                                  | 0    | 16                   | External address bus                                                                                                                                                                               |  |  |

| MEMWR                                                    | 0    | High                 | External Data memory write enable                                                                                                                                                                  |  |  |

| MEMRD                                                    | 0    | High                 | External Data memory output enable                                                                                                                                                                 |  |  |

| PSRD                                                     | 0    | High                 | External Program memory output enable                                                                                                                                                              |  |  |

| PSWR <sup>2</sup>                                        | 0    | High                 | External Program memory write enable                                                                                                                                                               |  |  |

| Wishbone Interface Signals (TSK52B_W and TSK52B_WD only) |      |                      |                                                                                                                                                                                                    |  |  |

| DAT_O                                                    | 0    | 8                    | Data to be sent to an external Wishbone slave device                                                                                                                                               |  |  |

| DAT_I                                                    | I    | 8                    | Data received from an external Wishbone slave device                                                                                                                                               |  |  |

| ADR_O                                                    | 0    | 8                    | Standard Wishbone address bus, used to select an internal register of a connected Wishbone slave device for writing to/reading from                                                                |  |  |

| CYC_O                                                    | 0    | High                 | Cycle signal. When asserted, indicates the start of a valid Wishbone cycle                                                                                                                         |  |  |

| STB_O                                                    | 0    | High                 | Strobe signal. When asserted, indicates the start of a valid Wishbone data transfer cycle                                                                                                          |  |  |

| WE_O                                                     | 0    | Level                | Write enable signal. Used to indicate whether the current local bus cycle is a Read or Write cycle.  0 = Read  1 = Write                                                                           |  |  |

| ACK_I                                                    | I    | High                 | Standard Wishbone device acknowledgement signal. When this signal goes High, external Wishbone slave device has finished execution of the requested action and the current bus cycle is terminated |  |  |

\_

<sup>&</sup>lt;sup>2</sup> This signal is not available in the TSK52B\_W.

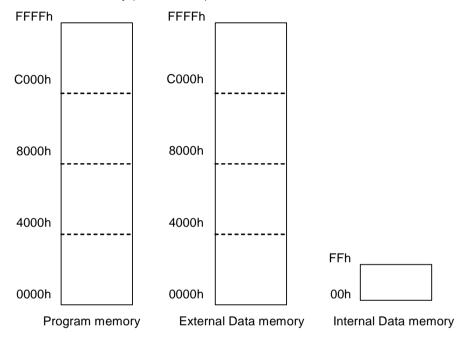

## **Memory organization**

Memory in the TSK52x is organized into three distinct areas:

- Program memory (external ROM)

- External Data memory (external RAM)

- Internal Data memory (internal RAM).

Figure 2. Memory map

## **Program memory**

The TSK52x can address up to 64 kB of Program memory space, from 0000h to FFFFh.

The External Bus Interface services Program memory when the PSRD signal is active. Program memory is read when the CPU performs fetching instructions or MOVC.

After a reset has been issued, the CPU starts program execution from location 0000h.

The lower part of the Program memory includes the interrupt and reset vectors. The interrupt vectors are spaced at 8-byte intervals, starting from 0003h, for External Interrupt 0.

Variable length code fetching and MOVC instructions enable access to fast or slow ROM. Three highorder bits of the CKCON register (in the Clock Control Unit) control wait state memory cycles. Setting these wait state bits to '1' allows access to very slow ROM.

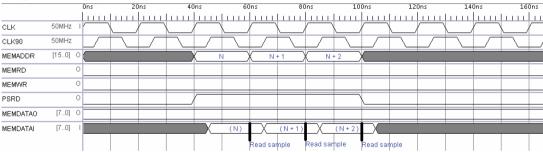

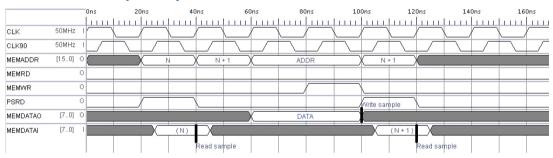

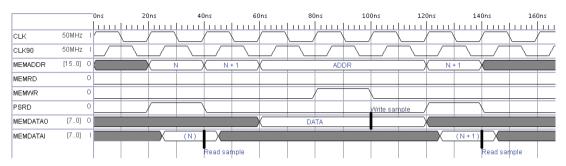

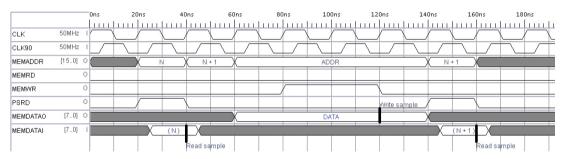

Table 3 shows how the signals of the External Memory Interface change when wait values are set from 0 to 7. The widths of the signals are counted in CLK cycles. The post-reset state of the CKCON register, which is in bold in the table, performs the fetching cycles or MOVC instructions without wait states.

Table 3. Wait state memory cycle width

| С       | KCON registe | er      | Wait value | Read signals | width |

|---------|--------------|---------|------------|--------------|-------|

| CKCON.6 | CKCON.5      | CKCON.4 |            | MEMADDR      | PSRD  |

| 0       | 0            | 0       | 0          | 1            | 1     |

| 0       | 0            | 1       | 1          | 2            | 2     |

| 0       | 1            | 0       | 2          | 3            | 3     |

| 0       | 1            | 1       | 3          | 4            | 4     |

| 1       | 0            | 0       | 4          | 5            | 5     |

| 1       | 0            | 1       | 5          | 6            | 6     |

| 1       | 1            | 0       | 6          | 7            | 7     |

| 1       | 1            | 1       | 7          | 8            | 8     |

### **Data memory**

#### **External Data memory**

The TSK52x can address up to 64 KB of external Data memory space, from 0000h to FFFFh.

The External Bus Interface services Data memory when the MEMRD or MEMWR signals are active. The TSK52x writes into external Data memory when the CPU executes MOVX @Ri,A or MOVX @DPTR,A instructions. The external Data memory is read when the CPU executes MOVX A,@Ri or MOVX A,@DPTR instructions.

The variable length MOVX instructions enable access to fast or slow external RAM and external peripherals. Three low-order bits of the CKCON register (in the Clock Control Unit) control stretch memory cycles. Setting these stretch bits to '1' allows access to very slow external RAM or external peripherals.

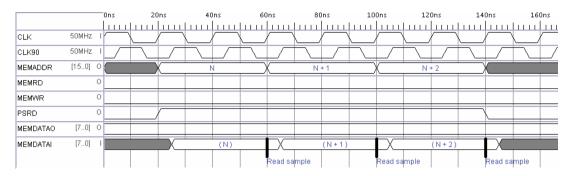

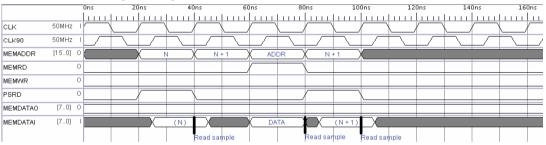

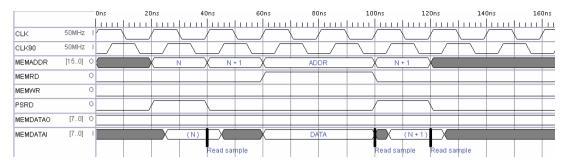

Table 4 shows how the signals of the External Memory Interface change when stretch values are set from 0 to 7. The widths of the signals are counted in CLK cycles. The post-reset state of the CKCON register, which is in bold in the table, performs the MOVX instructions with a value of stretch equal to 1.

Table 4. Stretch memory cycle width

| CKCON register |         | CKCON register Stretch Read signals wide |   | als width | Write sigr | nal width |       |

|----------------|---------|------------------------------------------|---|-----------|------------|-----------|-------|

| CKCON.2        | CKCON.1 | CKCON.0                                  |   | MEMADDR   | MEMRD      | MEMADDR   | MEMWR |

| 0              | 0       | 0                                        | 0 | 1         | 1          | 2         | 1     |

| 0              | 0       | 1                                        | 1 | 2         | 2          | 3         | 1     |

| 0              | 1       | 0                                        | 2 | 3         | 3          | 4         | 2     |

| 0              | 1       | 1                                        | 3 | 4         | 4          | 5         | 3     |

| C | CKCON register |   | Stretch value | Read signals width |   | Write signal width |   |

|---|----------------|---|---------------|--------------------|---|--------------------|---|

| 1 | 0              | 0 | 4             | 5                  | 5 | 6                  | 4 |

| 1 | 0              | 1 | 5             | 6                  | 6 | 7                  | 5 |

| 1 | 1              | 0 | 6             | 7                  | 7 | 8                  | 6 |

| 1 | 1              | 1 | 7             | 8                  | 8 | 9                  | 7 |

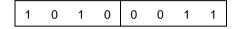

There are two types of MOVX instruction, differing in whether they provide an 8-bit or 16-bit indirect address to the external Data RAM.

In the first type, the contents of R0 or R1 in the current register bank provide an 8-bit address.

Eight bits are sufficient for external I/O expansion decoding or a relatively small RAM array. For somewhat larger arrays there are two methods to extend the 8-bit address to 16 bits:

- The first method is to use any output port pins to output higher-order address bits. These pins

would be controlled by an output instruction preceding the MOVX instruction

- The second method is to use the external Data memory paging register, XP. Using the XP register

makes accessing data within a page more efficient, since the page is held in the XP register and

only R0 or R1 needs to be changed. With this method, output ports are left free to serve any other

purpose.

In the second type of MOVX instruction, the data pointer generates a 16-bit address.

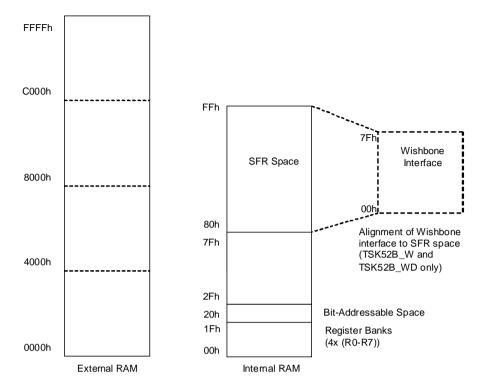

#### **Internal Data memory**

The TSK52x has a 512 byte block of RAM dedicated for use as internal Data memory. It should be noted, however, that although the physical size of the block is 512 bytes, only 256 bytes can be used for internal Data memory. This RAM cannot be upgraded in size. The internal Data memory interface is therefore not exposed to the user through the schematic symbol.

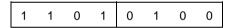

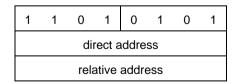

The 256 bytes of memory space (00h to FFh) can be accessed by either direct or indirect addressing (where supported). An internal Data memory address is always 1 byte in width.

The upper 128 bytes contain the Special Function Registers (SFRs). This area of internal Data memory is accessible only by direct addressing.

The lower 128 bytes contain work registers and bit-addressable memory. The lower 48 bytes of this area of memory space are further divided as follows:

- The lower 32 bytes (00h 1Fh) form four banks of eight registers (R0-R7). The RS0 and RS1 bits in the Program Status Word register (PSW) select which bank is currently in use.

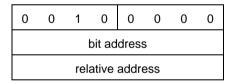

- The next 16 bytes (20h 2Fh) form a block of bit-addressable memory space, covering the bit address range 00h-7Fh.

All of the bytes in this lower half of the internal Data memory space are accessible through direct or indirect addressing.

Figure 3. Data memory map showing partitioning of internal RAM space

With respect to the Wishbone-compliant versions of the microcontroller (TSK52B\_W and TSK52B\_WD), all Wishbone peripheral devices map into the SFR address range of the Internal RAM space – overlapping the existing SFRs. Therefore, the only addresses available for accessing Wishbone devices are those in the SFR space that do not have any predefined function. The predefined SFR addresses are disabled on the Wishbone interface.

The SFR address 80h corresponds to the address 00h on the Wishbone interface. For example, a Wishbone peripheral device at address 08h on the Wishbone interface would be accessed in software at address 88h of the SFR space.

## **Special Function Registers**

### **Special Function Registers location**

As illustrated in the previous section, Special Function Registers (SFRs) reside in the top 128 bytes of the internal RAM space. A map of the Special Function Registers is shown in Table 5.

Table 5. Special Function Registers location

| Hex\Bin | X000              | X001              | X010 | X011 | X100 | X101 | X110  | X111 | Bin/Hex    |

|---------|-------------------|-------------------|------|------|------|------|-------|------|------------|

| F8      | WBT0 <sup>3</sup> | WBT1 <sup>3</sup> |      |      |      |      |       |      | FF         |

| F0      | В                 |                   |      |      |      |      |       |      | F7         |

| E8      |                   |                   |      |      |      |      |       |      | EF         |

| E0      | ACC               |                   |      |      |      |      |       |      | E7         |

| D8      |                   |                   |      |      |      |      |       |      | DF         |

| D0      | PSW               |                   |      |      |      |      |       |      | D7         |

| C8      |                   |                   |      |      |      |      |       |      | CF         |

| C0      | IRCON             |                   |      |      |      |      |       |      | <b>C</b> 7 |

| В8      | IEN1              | IP1               |      |      |      |      |       |      | BF         |

| В0      | P3                |                   |      |      |      |      |       |      | В7         |

| A8      | IEN0              | IP0               |      |      |      |      |       |      | AF         |

| Α0      | P2                |                   |      |      |      |      |       |      | A7         |

| 98      |                   |                   |      |      |      |      |       | XP   | 9F         |

| 90      | P1                |                   |      |      |      |      |       |      | 97         |

| 88      |                   |                   |      |      |      |      | CKCON |      | 8F         |

| 80      | P0                | SP                | DPL  | DPH  |      |      |       | PCON | 87         |

For the non-Wishbone versions of the microcontroller (TSK52A and TSK52A\_D), only 18 addresses are occupied, the others are not implemented. Read access to unimplemented addresses will return undefined data, while writes will have no effect.

For the Wishbone-compliant versions (TSK52B\_W and TSK52B\_WD), an additional 2 addresses are occupied by two dedicated timing registers – WBT0 and WBT1. The remaining 108 addresses in the SFR space can be used to access any 8-bit compatible Wishbone slave devices.

<sup>&</sup>lt;sup>3</sup> Wishbone-compliant versions only (TSK52B\_W, TSK52B\_WD).

## **Special Function Registers reset values**

Table 6. Special Function Registers reset values

| Register          | Location | Reset value | Description                          |

|-------------------|----------|-------------|--------------------------------------|

| P0                | 80h      | FFh         | Port 0                               |

| SP                | 81h      | 07h         | Stack Pointer                        |

| DPL               | 82h      | 00h         | Data Pointer Low 0                   |

| DPH               | 83h      | 00h         | Data Pointer High 0                  |

| PCON              | 87h      | 00h         | Power Control register               |

| CKCON             | 8Eh      | 01h         | Clock Control register (Stretch=1)   |

| P1                | 90h      | FFh         | Port 1                               |

| XP                | 9Fh      | 00h         | External Data memory Paging register |

| P2                | A0h      | 00h         | Port 2                               |

| IEN0              | A8h      | 00h         | Interrupt Enable register 0          |

| IP0               | A9h      | 00h         | Interrupt Priority register 0        |

| P3                | B0h      | FFh         | Port 3                               |

| IEN1              | B8h      | 00h         | Interrupt Enable register 1          |

| IP1               | B9h      | 00h         | Interrupt Priority register 1        |

| IRCON             | C0h      | 00h         | Interrupt Request Control register   |

| PSW               | D0h      | 00h         | Program Status Word register         |

| ACC               | E0h      | 00h         | Accumulator                          |

| В                 | F0h      | 00h         | B register                           |

| WBT0 <sup>4</sup> | F8h      | 00h         | Wishbone Timing register 0           |

| WBT1 <sup>4</sup> | F9h      | 00h         | Wishbone Timing register 1           |

# **Accumulator (ACC)**

Most instructions use the Accumulator to hold the operand. Note that the mnemonics for Accumulator-specific instructions refer to the Accumulator as A, not ACC.

<sup>&</sup>lt;sup>4</sup> Wishbone-compliant versions only (TSK52B\_W, TSK52B\_WD).

### **B** Register

The B register is used during multiply and divide instructions. It can also be used as a scratch-pad register to hold temporary data.

### **External Data memory Paging register (XP)**

The content of the XP register is loaded onto the high order byte of the memory address bus during external Data memory access using the MOVX @Ri, A and MOVX A, @Ri instructions. The XP register is used to implement paging and can provide access to up to 256 pages in external Data memory. Each page can contain up to 256 bytes of data – dependent on the contents of the register Ri. Therefore the maximum addressable external Data memory space is 64KB.

When the XP register is not used, its default reset value of 00h ensures the processor will act as its TSK51x counterpart for these two MOVX instructions, with the upper 8-bits of the memory address bus stuck at zeros.

## **Program Status Word register (PSW)**

Table 7. PSW register flags

| MSB |    |    |     | _   |    |    | LSB |

|-----|----|----|-----|-----|----|----|-----|

| CY  | AC | F0 | RS1 | RS0 | OV | F1 | Р   |

Table 8. PSW register bit functions

| Bit   | Symbol | Function                                                                 |  |

|-------|--------|--------------------------------------------------------------------------|--|

| PSW.7 | CY     | Carry flag                                                               |  |

| PSW.6 | AC     | Auxiliary Carry flag for BCD operations                                  |  |

| PSW.5 | F0     | General purpose Flag 0 available for user                                |  |

| PSW.4 | RS1    | Register bank select control bit 1, used to select working register bank |  |

| PSW.3 | RS0    | Register bank select control bit 0, used to select working register bank |  |

| PSW.2 | OV     | Overflow flag                                                            |  |

| PSW.1 | F1     | General purpose Flag 1 available for user                                |  |

| PSW.0 | Р      | Parity flag                                                              |  |

Bits RS1 and RS0 are used to select the working register bank as follows.

Table 9. Register Bank selection

| RS1:RS0 | Bank selected | Location    |

|---------|---------------|-------------|

| 00      | Bank 0        | (00h – 07h) |

| 01      | Bank 1        | (08h – 0Fh) |

| 10      | Bank 2        | (10h – 17h) |

| 11      | Bank 3        | (18h – 1Fh) |

### Stack Pointer (SP)

The Stack Pointer is a 1-byte register initialized to 07h after reset. This register is incremented before PUSH and CALL instructions, causing the stack to begin at location 08h.

### **Data Pointer register (DPL and DPH)**

The Data Pointer (DPTR) is 2 bytes wide. The lower byte is DPL and the higher DPH. It can be loaded as either a single 2 byte register:

MOV DPTR,#data16)

or as two individual, single byte registers:

MOV DPL,#data8

MOV DPH.#data8.

It is generally used to access external code or data space, for example:

MOVC A.@A+DPTR or

MOVX A,@DPTR.

## **Program Counter (PC)**

The Program Counter (PC) is 2 bytes wide and is initialized to 0000h after reset. This register is incremented during a fetch of operation code or operation data from Program memory.

## **Additional Wishbone Interface Special Function Registers**

The Wishbone-compliant versions of the microcontroller – the TSK52B\_W and TSK52B\_WD respectively – contain two additional special function registers as part of the Wishbone Interface. These two timing registers – WBT0 and WBT1 – are used to provide a 14-bit value to the built-in Wishbone Cycle Counter, which determines how many clock cycles the processor will wait for an acknowledge signal from an addressed Wishbone slave device to appear at its ACK\_I input, before the current data transfer cycle is forcibly terminated.

## Wishbone Timing register 0 (WBT0)

Table 10. The WBT0 register

MSB LSB

| CNT5 CNT4 CNT3 CNT2 CNT1 CNT0 ACK WCCEN |

|-----------------------------------------|

|-----------------------------------------|

Table 11. The WBT0 register bit functions

| Bit    | Symbol | Function                                                                                                                        |  |  |

|--------|--------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| WBT0.7 | CNT5   | Counter bit 5                                                                                                                   |  |  |

| WBT0.6 | CNT4   | Counter bit 4                                                                                                                   |  |  |

| WBT0.5 | CNT3   | Counter bit 3                                                                                                                   |  |  |

| WBT0.4 | CNT2   | Counter bit 2                                                                                                                   |  |  |

| WBT0.3 | CNT1   | Counter bit 1                                                                                                                   |  |  |

| WBT0.2 | CNT0   | Counter bit 0                                                                                                                   |  |  |

| WBT0.1 | ACK    | Acknowledge flag. Updated when the Wishbone Cycle Counter reaches zero, it is used to flag how the Wishbone transmission ended: |  |  |

|        |        | 0 = Wishbone transfer cycle terminated normally, with an acknowledge signal received from the slave Wishbone device             |  |  |

|        |        | 1 = Wishbone transfer cycle has been forcibly terminated by the processor due to no acknowledgement from slave Wishbone device. |  |  |

| WBT0.0 | WCCEN  | Wishbone Cycle Counter Enable.                                                                                                  |  |  |

|        |        | 0 = Wishbone interface will wait until an acknowledge is received from an external Wishbone device                              |  |  |

|        |        | 1 = Wishbone interface will wait for an acknowledge for CNT13-0 clock cycles, before forcibly terminating the transfer.         |  |  |

### Wishbone Timing register 1 (WBT1)

Table 12. The WBT1 register

MSB LSB

| CNT13 CNT12 CN | T11 CNT10 CNT | 9 CNT8 CNT7 | CNT6 |

|----------------|---------------|-------------|------|

|----------------|---------------|-------------|------|

Table 13. The WBT1 register bit functions

| Bit    | Symbol | Function       |  |

|--------|--------|----------------|--|

| WBT1.7 | CNT13  | Counter bit 13 |  |

| WBT1.6 | CNT12  | Counter bit 12 |  |

| WBT1.5 | CNT11  | Counter bit 11 |  |

| WBT1.4 | CNT10  | Counter bit 10 |  |

| WBT1.3 | CNT9   | Counter bit 9  |  |

| WBT1.2 | CNT8   | Counter bit 8  |  |

| WBT1.1 | CNT7   | Counter bit 7  |  |

| WBT1.0 | CNT6   | Counter bit 6  |  |

**Note**: Bits 7-0 of the WBT1 register and bits 7-2 of the WBT0 register are concatenated to form the 14-bit value, CNT13-0. This value is automatically re-loaded into the Wishbone Cycle Counter each time the processor initiates a Wishbone data transfer. The counter starts counting down automatically when a transfer is initiated and the initial value of the counter is greater than zero.

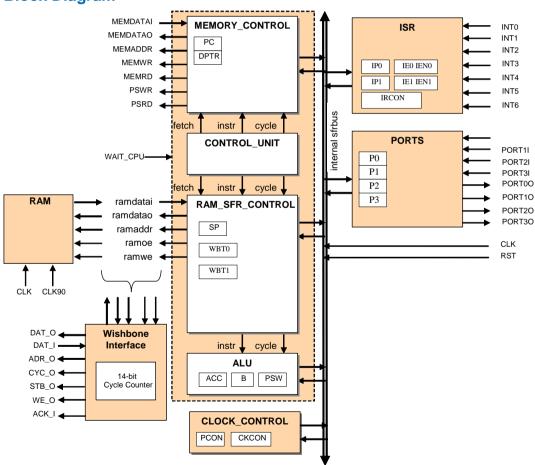

# **Hardware description**

The structure of the TSK52x consists of:

- Control Processor Unit

- Arithmetic Logic Unit

- Clock Control Unit

- Memory Control Unit

- · RAM and SFR Control Unit

- Ports Registers Unit

- Interrupt Service Routine Unit

- Wishbone Interface (TSK52B\_W and TSK52B\_WD only)

## **Block Diagram**

Figure 4. TSK52x Block Diagram

## **TSK52x Engine**

The core engine of the TSK52x is composed of four components:

- Control Unit

- Arithmetic Logic Unit

- Memory Control Unit

- RAM and SFR Control Unit.

The TSK52x engine allows instructions to be fetched from Program memory and to execute using either RAM or SFR.

#### **Ports**

Ports P0, P1, P2 and P3 are Special Function Registers. The contents of the SFR can be observed on the corresponding component symbol interface pins. Writing a '1' to any of the ports causes the corresponding pin to be at the high level and writing a '0' causes the corresponding pin to be held at the low level.

All four ports on the chip are bi-directional. Each of them consists of a Latch (SFR P0 to P3), an output drive and an input buffer, so the CPU can output or read data through any of these ports if they are not used for alternate purposes.

### Reset control

All registers and flip-flops are synchronously reset by the (active high) internal reset (rst) signal. An external hardware reset (RST) can activate the internal reset state. A high on the RST pin while the external clock is running, resets the device.

## **Interrupt Service Routine Unit**

The TSK52x provides seven external interrupts with four priority levels. Each interrupt has its own request flag located in the special function register IRCON or IEN1. Each interrupt requested by the corresponding flag could individually be enabled or disabled by the enable bits in the special function register IEN0.

## Interrupt overview

When the interrupt occurs, the engine will vector to a predetermined address (see Table 26). Once interrupt service has begun, it can be interrupted only by a higher priority interrupt. The interrupt service is terminated by a return from instruction RETI. When a RETI instruction is performed, the processor will return to the instruction that would have been next when the interrupt occurred.

When the interrupt condition occurs, the processor will also indicate this by setting a flag bit. This bit is set regardless of whether the interrupt is enabled or disabled. Each interrupt flag is sampled once per machine cycle, then samples are polled by hardware. If the sample indicates a pending interrupt when the interrupt is enabled, then the interrupt request flag is set. On the next multi-cycle instruction the interrupt will be acknowledged by hardware, forcing an LCALL to the appropriate vector address.

Interrupt response will require a varying amount of time depending on the state of the microcontroller when the interrupt occurs. If the microcontroller is performing an interrupt service with equal or greater

priority, the new interrupt will not be invoked. In other cases, the response time depends on the current instruction. The fastest possible response to an interrupt is 7 machine cycles. This includes one machine cycle for detecting the interrupt and six cycles for performing the LCALL.

### **Interrupt-based Special Function Registers**

### Interrupt Enable register 0 (IEN0)

Table 14. The IEN0 register

MSB

LSB

EAL

EX6

EX5

EX4

EX3

EX2

EX1

EX0

Table 15. The IEN0 register bit functions

| Bit    | Symbol | Function                         |  |

|--------|--------|----------------------------------|--|

| IEN0.7 | EAL    | 0 – disable all interrupts       |  |

|        |        | 1 – enable all interrupts        |  |

| IEN0.6 | EX6    | 0 – disable external interrupt 6 |  |

|        |        | 1 – enable external interrupt 6  |  |

| IEN0.5 | EX5    | 0 – disable external interrupt 5 |  |

|        |        | 1 – enable external interrupt 5  |  |

| IEN0.4 | EX4    | 0 – disable external interrupt 4 |  |

|        |        | - enable external interrupt 4    |  |

| IEN0.3 | EX3    | 0 – disable external interrupt 3 |  |

|        |        | 1 – enable external interrupt 3  |  |

| IEN0.2 | EX2    | 0 – disable external interrupt 2 |  |

|        |        | 1 – enable external interrupt 2  |  |

| IEN0.1 | EX1    | 0 – disable external interrupt 1 |  |

|        |        | 1 – enable external interrupt 1  |  |

| IEN0.0 | EX0    | 0 – disable external interrupt 0 |  |

|        |        | 1 – enable external interrupt 0  |  |

### **Interrupt Enable register 1 (IEN1)**

Table 16. The IEN1 register

MSB

LSB

F3

F2

I3FR

I2FR

IE1

IT1

IE0

IT0

Table 17. The IEN1 register bit functions

| Bit    | Symbol | Function                                                                                                                                             |  |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IEN1.7 | F3     | General purpose Flag 3 available for user                                                                                                            |  |

| IEN1.6 | F2     | General purpose Flag 2 available for user                                                                                                            |  |

| IEN1.5 | I3FR   | External interrupt 3 falling/rising edge flag.  0 – external interrupt negative transition active  1 – external interrupt positive transition active |  |

| IEN1.4 | I2FR   | External interrupt 2 falling/rising edge flag.  0 – external interrupt negative transition active  1 – external interrupt positive transition active |  |

| IEN1.3 | IE1    | External interrupt 1 flag                                                                                                                            |  |

| IEN1.2 | IT1    | External interrupt 1 type control bit.  0 – external interrupt high level active  1 – external interrupt positive transition active                  |  |

| IEN1.1 | IE0    | External interrupt 0 flag                                                                                                                            |  |

| IEN1.0 | IT0    | External interrupt 0 type control bit.  0 – external interrupt high level active  1 – external interrupt positive transition active                  |  |

### **Interrupt Request register (IRCON)**

Table 18. The IRCON register

MSB

LSB

F6

F5

IEX2

IEX3

IEX4

IEX5

IEX6

F4

Table 19. The IRCON register bit functions

| Bit     | Symbol | Function                                  |  |

|---------|--------|-------------------------------------------|--|

| IRCON.7 | F6     | General purpose Flag 6 available for user |  |

| IRCON.6 | F5     | General purpose Flag 5 available for user |  |

| IRCON.5 | IEX2   | External interrupt 2 edge flag            |  |

| IRCON.4 | IEX3   | External interrupt 3 edge flag            |  |

| IRCON.3 | IEX4   | External interrupt 4 edge flag            |  |

| IRCON.2 | IEX5   | External interrupt 5 edge flag            |  |

| Bit     | Symbol | Function                                  |  |  |

|---------|--------|-------------------------------------------|--|--|

| IRCON.1 | IEX6   | External interrupt 6 edge flag            |  |  |

| IRCON.0 | F4     | General purpose Flag 4 available for user |  |  |

### **Priority level structure**

All interrupt sources have predefined priority level.

Table 20. Priority level

| External interrupt 0 |  |

|----------------------|--|

| External interrupt 2 |  |

| External interrupt 1 |  |

| External interrupt 3 |  |

| External interrupt 4 |  |

| External interrupt 5 |  |

| External interrupt 6 |  |

Each interrupt source can be programmed individually to one of four priority levels by setting or clearing the appropriate bit in the special function registers IP0 and IP1. If requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced first.

### **Interrupt Priority register 0 (IP0)**

Table 21. The IP0 register

| MSB |       |       |       |       |       |       | LSB   |

|-----|-------|-------|-------|-------|-------|-------|-------|

| F7  | IP0.6 | IP0.5 | IP0.4 | IP0.3 | IP0.2 | IP0.1 | IP0.0 |

### **Interrupt Priority register 1 (IP1)**

Table 22. The IP1 register

| MSB |       |       |       |       |       |       | LSB   |  |

|-----|-------|-------|-------|-------|-------|-------|-------|--|

| F8  | IP1.6 | IP1.5 | IP1.4 | IP1.3 | IP1.2 | IP1.1 | IP1.0 |  |

Note: Bit 7 of register IP0 (F7) and bit 7 of register IP1 (F8) are general purpose flags available for the user.

Table 23. Priority levels

| IP1.x | IP0.x | Priority Level   |

|-------|-------|------------------|

| 0     | 0     | Level0 (lowest)  |

| 0     | 1     | Level1           |

| 1     | 0     | Level2           |

| 1     | 1     | Level3 (highest) |

Table 24. Priority level control bits

| Bit          | Interrupt Source     |

|--------------|----------------------|

| IP1.0, IP0.0 | External interrupt 0 |

| IP1.1, IP0.1 | External interrupt 1 |

| IP1.2, IP0.2 | External interrupt 2 |

| IP1.3, IP0.3 | External interrupt 3 |

| IP1.4, IP0.4 | External interrupt 4 |

| IP1.5, IP0.5 | External interrupt 5 |

| IP1.6, IP0.6 | External interrupt 6 |

Table 25. Polling sequence

| External interrupt 0 |                  |

|----------------------|------------------|

| External interrupt 2 | ф                |

| External interrupt 1 | Polling sequence |

| External interrupt 3 | l sed            |

| External interrupt 4 | olling           |

| External interrupt 5 | Δ.               |

| External interrupt 6 |                  |

# **Interrupt sources and vectors**

Table 26. Interrupt vectors

| Interrupt Request Flags     | Interrupt Vector Address |

|-----------------------------|--------------------------|

| IE0 – External interrupt 0  | 0003h                    |

| IE1 – External interrupt 1  | 0013h                    |

| IEX2 – External interrupt 2 | 004Bh                    |

| Interrupt Request Flags     | Interrupt Vector Address |

|-----------------------------|--------------------------|

| IEX3 – External interrupt 3 | 0053h                    |

| IEX4 – External interrupt 4 | 005Bh                    |

| IEX5 – External interrupt 5 | 0063h                    |

| IEX6 – External interrupt 6 | 006Bh                    |

### **External interrupt edge detect**

The external interrupts 2 and 3 can be programmed to be negative or positive transition-activated by setting or clearing bit I2FR or I3FR respectively, in register IEN1. The external interrupts 4, 5 and 6 are activated by a positive transition. The external source has to hold the request pin low (high for INT2 and INT3, if it is programmed to be negative transition-active) for at least one period of CLK. After this period, it must then be held high (low) for at least one period of CLK to ensure that the transition is recognized and that the corresponding interrupt request flag will be set.

### Wishbone Interface (TSK52B\_W and TSK52B\_WD)

The same internal RAM interface signals are used to connect the Wishbone Interface to the RAM and SFR Unit. On the other side of this interface, standard Wishbone interface signals are used to connect the processor to any 8-bit compatible Wishbone slave device.

When accessing a Wishbone slave device through the Wishbone Interface, an 8-bit address is put on the ADR\_O bus. Since a maximum of 108 addresses in SFR space can be used to address external Wishbone slave devices, bit 8 of ADR\_O is always zero.

#### Writing to a Wishbone Slave Device

Data is written from the host microcontroller (Wishbone Master) to a Wishbone-compliant peripheral device (Wishbone Slave) in accordance with the standard Wishbone data transfer handshaking protocol. This data transfer cycle can be summarized as follows:

- The host presents an address on its ADR\_O output for the register it wants to write to and a valid byte of data on its DAT\_O output. It then asserts its WE\_O output to specify a Write cycle

- The slave device receives the address at its ADR\_I input and prepares to receive the data

- The host asserts its STB\_O and CYC\_O outputs, indicating that the transfer is to begin. The slave

device, monitoring its STB\_I and CYC\_I inputs, reacts to this assertion by latching the byte of data

appearing at its DAT\_I input and asserting its ACK\_O signal to indicate to the host that the data

has been received

- The host, monitoring its ACK\_I input, responds by negating the STB\_O and CYC\_O signals. At the same time, the slave device negates the ACK\_O signal and the data transfer cycle is naturally terminated.

#### Reading from a Wishbone Slave Device

Data is read by the host microcontroller (Wishbone Master) from a Wishbone-compliant peripheral device (Wishbone Slave) in accordance with the standard Wishbone data transfer handshaking protocol. This data transfer cycle can be summarized as follows:

- The host presents an address on its ADR\_O output for the register it wishes to read. It then negates

its WE\_O output to specify a Read cycle

- The slave device receives the address at its ADR\_I input and prepares to transmit the data from the selected register

- The host asserts its STB\_O and CYC\_O outputs, indicating that the transfer is to begin. The slave

device, monitoring its STB\_I and CYC\_I inputs, reacts to this assertion by presenting the valid byte

of data at its DAT\_O output and asserting its ACK\_O signal to indicate to the host that valid data

is present

- The host, monitoring its ACK\_I input, responds by latching the byte of data appearing at its DAT\_I input and negating the STB\_O and CYC\_O signals. At the same time, the slave device negates the ACK\_O signal and the data transfer cycle is naturally terminated.

During Wishbone transmission the processor is stopped until an acknowledgement is received from a slave device. This can be a problem when a slave device disconnects from the Wishbone bus due to failure, leaving the processor waiting indefinitely for an acknowledge signal that will never come. To prevent this situation from happening, the Wishbone-compliant versions of the TSK52 have a built-in timer, that will automatically cancel a pending transmission after a given number of clock cycles. By default, this timer is inactive when the processor starts and the processor waits until there is an acknowledge from a slave device.

#### **Communicating with Multiple Wishbone Slave Devices**

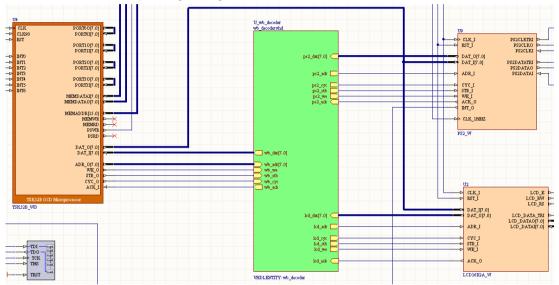

Typically in a design, the microcontroller will need to interface to multiple Wishbone-compliant peripherals (slave devices). Each of these peripherals may contain any number of internal registers with which to write to/read from. It is not possible to communicate directly, and simultaneously, with each of these slave devices. A means of multiplexing must be used, allowing the microcontroller to talk to any number of slaves over the one interface. Typically, this involves the use of a Wishbone Decoder, as illustrated in the example image of Figure 5.

Figure 5. Multiplexing the Wishbone interface using a Wishbone Decoder

In the example circuit above, the Wishbone Decoder enables a single microcontroller device (TSK52B\_WD) to communicate with two Wishbone-compliant peripheral devices (a PS/2 Controller and an LCD Controller). These two peripheral Controllers, in turn, each have two internal Wishbone registers that can be accessed by the microcontroller.

The Decoder itself is defined in an underlying VHDL file, which is used to decode the 8-bit address supplied by the microcontroller and enable communications with the relevant slave device and register therein, accordingly (Figure 6)

```

architecture rtl of wb decoder is

constant LCD DAT REG : std logic vector(7 downto 0) := "01110111" ;

constant LCD CTRL REG : std logic vector(7 downto 0) := "01111111" ;

constant PS2 DAT REG : std logic vector(7 downto 0) := "01100111" ;

constant PS2 CTRL REG : std logic vector(7 downto 0) := "01101111" ;

begin

process(lcd dat, lcd ack, wb adr, wb we, wb stb, wb cyc, ps2 dat, ps2 ack)

begin

case wb adr is

when LCD DAT REG =>

lcd adr <= '0';

led eve <= wb eve ;

lcd stb <= wb stb;

lcd we <= wb_we;

ps2 adr <= '0';

ps2 cyc <= '0';

ps2 stb <= '0';

ps2 we <= '0';

wb dat <= lcd dat ;

wb ack <= lcd ack;

when PS2 DAT REG =>

lcd adr <= '0';

lcd cyc <= '0';

lcd stb <= '0';

lcd we <= '0';

ps2_adr <= '1';

ps2_cyc <= wb_cyc ;

ps2 stb <= wb stb;

ps2 we <= wb we;

wb dat <= ps2 dat;

wb_ack <= ps2_ack;

```

Figure 6. Wishbone Decoder – under-the-bonnet code snippet

The exact configuration of a Wishbone Decoder and its underlying VHDL code, will vary depending on individual design requirements – the number of slave devices to be addressed, the number of accessible registers within each slave, etc – but the basic principle remains the same.

# **On-Chip Debugging**

The debug-enabled versions of the microcontroller (TSK52A\_D and TSK52B\_WD) provide the following set of additional functional features that facilitate real-time debugging of the microcontroller:

- · Reset, Go, Halt processor control

- Single or multi-step debugging

- Read-write access for internal processor registers including SFRs and PC

- Read-write access for Program memory and Data memory

- Unlimited software breakpoints

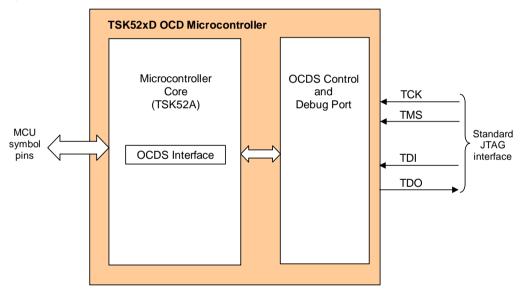

## Adding debug functionality to a standard core variant

For the TSK52A\_D and TSK52BW\_D (henceforth referred to as TSK52xD) debug functionality is provided through the use of an On-Chip Debug System unit (OCDS). The simplified block diagram of Figure 7 shows the connection between this unit and the standard TSK52A core.

Figure 7. Simplified TSK52xD block diagram

The host computer is connected to the target core using the IEEE 1149.1 (JTAG) standard interface. This is the physical interface, providing connection to physical pins of the FPGA device in which the core has been embedded.

The Nexus 5001 standard is used as the protocol for communications between the host and all devices that are debug-enabled with respect to this protocol. This includes all OCD-version microcontrollers, as well as other Nexus-compliant devices such as frequency generators, logic analyzers, counters, etc.

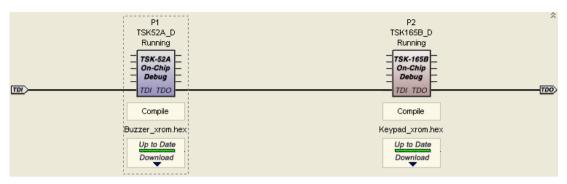

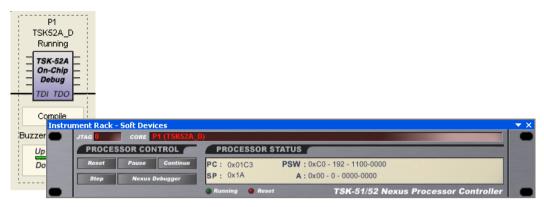

All such devices are connected in a chain – the Soft Devices chain – which is determined when the design has been implemented within the target FPGA device and presents in the **Devices** view (Figure 8). It is not a physical chain, in the sense that you can see no external wiring – the connections required between the Nexus-enabled devices are made internal to the FPGA itself.

Figure 8. Nexus-enabled microcontrollers appearing in the Soft Devices chain

For microcontrollers such as the TSK52xD, the Nexus protocol enables you to debug the core through communication with the OCDS Unit.

## Accessing the debug environment

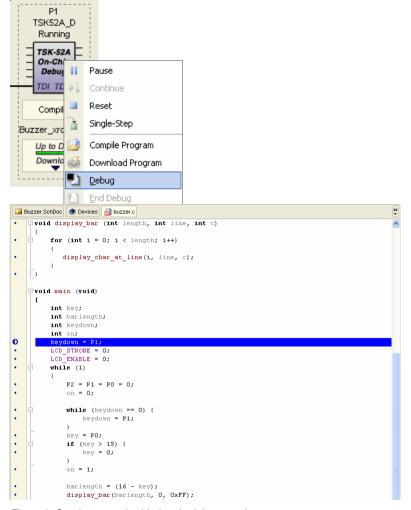

Debugging of the embedded code within an OCD-version microcontroller is carried out by starting a debug session. Prior to starting the session, you must ensure that the design, including one or more OCD-version microcontrollers and their respective embedded code, has been downloaded to the target physical FPGA device.

To start a debug session for the embedded code of a specific microcontroller in the design, simply right-click on the icon for that microcontroller, in the Soft Devices region of the view, and choose the **Debug** command from the pop-up menu that appears. Alternatively, click on the icon for the microcontroller (to focus it) and choose **Processors » Pn » Debug** from the main menus, where n corresponds to the number for the processor in the Soft Devices chain.

The embedded project for the software running in the processor will initially be recompiled and the debug session will commence. The relevant source code document (either Assembly or C) will be opened and the current execution point will be set to the first line of executable code (see Figure 9).

**Note**: You can have multiple debug sessions running simultaneously – one per embedded software project associated with a microcontroller in the Soft Devices chain.

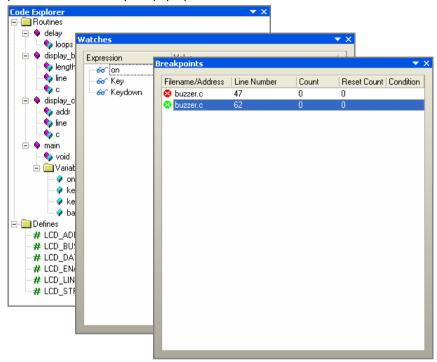

Figure 9. Starting an embedded code debug session.

The debug environment offers the full suite of tools you would expect to see in order to efficiently debug the embedded code. These features include:

- Setting Breakpoints

- Adding Watches

- Stepping into and over at both the source (\* . C) and instruction (\* .asm) level

- Reset. Run and Halt code execution

- Run to cursor

All of these and other feature commands can be accessed from the **Debug** menu or the associated **Debug** toolbar.

Various workspace panels are accessible in the debug environment, allowing you to view/control codespecific features, such as Breakpoints, Watches and Local variables, as well as information specific to the microcontroller in which the code is running, such as memory spaces and registers.

These panels can be accessed from the **View** » **Workspace Panels** » **Embedded** sub menu, or by clicking on the **Embedded** button at the bottom of the application window and choosing the required panel from the subsequent pop-up menu.

Figure 10. Workspace panels offering code-specific information and controls

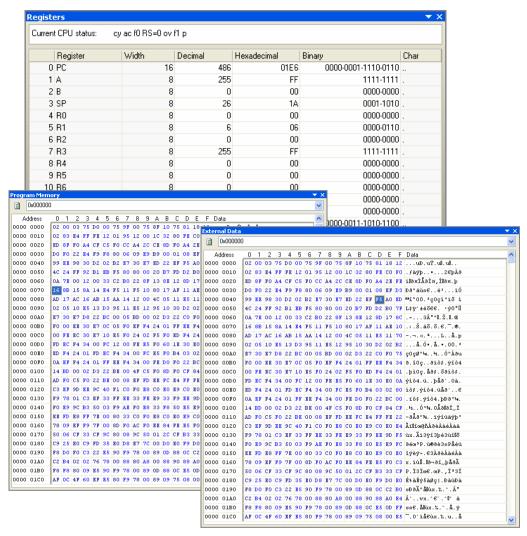

Figure 11. Workspace panels offering information specific to the parent processor.

Full-feature debugging is of course enjoyed at the source code level – from within the source code file itself. To a lesser extent, debugging can also be carried out from a dedicated debug panel for the processor. To access<sup>5</sup> this panel, first double-click on the icon representing the microcontroller to be debugged, in the **Soft Devices** region of the view. The *Instrument Rack* – *Soft Devices* panel will appear, with the chosen processor instrument added to the rack (Figure 12).

31

<sup>&</sup>lt;sup>5</sup> The debug panels for each of the debug-enabled microcontrollers are standard panels and, as such, can be readily accessed from the **View** » **Workspace Panels** » **Instruments** sub-menu, or by clicking on the **Instruments** button at the bottom of the application window and choosing the required panel – for the processor you wish to debug – from the subsequent pop-up menu.

Figure 12. Accessing debug features from the microcontroller's instrument panel

**Note**: Each core microcontroller that you have included in the design will appear, when double-clicked, as an Instrument in the rack (along with any other Nexus-enabled devices).

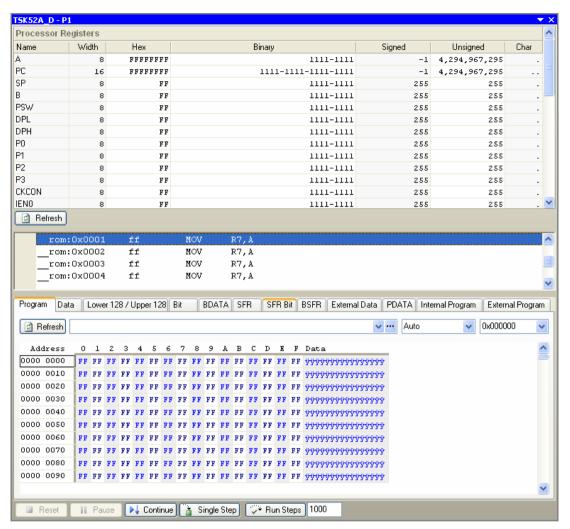

The **Nexus Debugger** button provides access to the associated debug panel (Figure 13), which in turn allows you to interrogate and to a lighter extent control, debugging of the processor and its embedded code, notably with respect to the microcontroller registers and memory.

One key feature of the debug panel is that it enables you to specify (and therefore change) the embedded code (HEX file) that is downloaded to the microcontroller, quickly and efficiently.

For more information on the content and use of processor debug panels, press **F1** when the cursor is over one of these panels.

For further information regarding the use of the embedded tools for the TSK52x, see the *Using the TSK51x/TSK52x Embedded Tools* guide.

For comprehensive information with respect to the embedded tools available for the TSK52x, see the TSK51x/TSK52x Embedded Tools Reference.

Figure 13. Processor debugging using an associated processor debug panel.

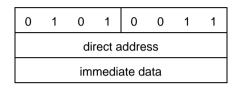

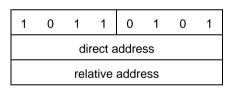

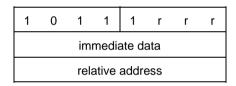

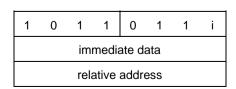

# **Instruction set**

All TSK52x instructions are binary code compatible with the TSK51 processor.

Table 27. Notes on data addressing modes

| Rn      | Working register R0-R7                                                    |

|---------|---------------------------------------------------------------------------|

| direct  | 256 internal RAM locations, any Special Function Registers                |

| @Ri     | Indirect internal or external RAM location addressed by register R0 or R1 |

| #data   | 8-bit constant included in instruction                                    |

| #data16 | 16-bit constant included as bytes 2 and 3 of instruction                  |

| bit     | any bit-addressable I/O pin, control or status bit                        |

| Α       | Accumulator                                                               |

Table 28. Notes on program addressing modes

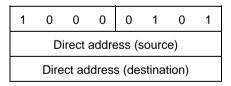

| addr16 | Destination address for LCALL and LJMP may be anywhere within the 64KB of Program memory address space.                                       |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| addr11 | Destination address for ACALL and AJMP will be within the same 2KB page of Program memory as the first byte of the following instruction.     |

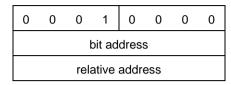

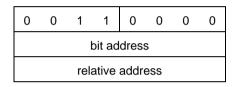

| rel    | SJMP and all conditional jumps include an 8-bit offset byte. Range is +127/-128 bytes relative to the first byte of the following instruction |

# Instruction set – functional groupings

Table 29. Arithmetic operations

| Mnemonic      | Description                                       | Hex<br>Opcode | Width<br>(in<br>bytes) | No. of Instruction<br>Cycles for<br>execution |

|---------------|---------------------------------------------------|---------------|------------------------|-----------------------------------------------|

| ADD A,#data   | Add immediate data to Accumulator                 | 24            | 2                      | 2                                             |

| ADD A,@Ri     | Add indirect RAM to Accumulator                   | 26-27         | 1                      | 2                                             |

| ADD A,direct  | Add direct byte to Accumulator                    | 25            | 2                      | 2                                             |

| ADD A,Rn      | Add register to Accumulator                       | 28-2F         | 1                      | 1                                             |

| ADDC A,#data  | Add immediate data to Accumulator with carry flag | 34            | 2                      | 2                                             |

| ADDC A,@Ri    | Add indirect RAM to Accumulator with carry flag   | 36-37         | 1                      | 2                                             |

| ADDC A,direct | Add direct byte to Accumulator with carry flag    | 35            | 2                      | 2                                             |

| Mnemonic      | Description                                          | Hex<br>Opcode | Width<br>(in<br>bytes) | No. of Instruction<br>Cycles for<br>execution |

|---------------|------------------------------------------------------|---------------|------------------------|-----------------------------------------------|

| ADDC A,Rn     | Add register to Accumulator with carry flag          | 38-3F         | 1                      | 1                                             |

| DEC @Ri       | Decrement indirect RAM                               | 16-17         | 1                      | 3                                             |

| DEC A         | Decrement Accumulator                                | 14            | 1                      | 1                                             |

| DEC direct    | Decrement direct byte                                | 15            | 2                      | 3                                             |

| DEC Rn        | Decrement register                                   | 18-1F         | 1                      | 2                                             |

| DIV AB        | Divide A by B                                        | 84            | 1                      | 6                                             |

| INC @Ri       | Increment indirect RAM                               | 06-07         | 1                      | 3                                             |

| INC A         | Increment Accumulator                                | 04            | 1                      | 1                                             |

| INC direct    | Increment direct byte                                | 05            | 2                      | 3                                             |

| INC DPTR      | Increment data pointer                               | А3            | 1                      | 1                                             |

| INC Rn        | Increment register                                   | 08-0F         | 1                      | 2                                             |

| MUL AB        | Multiply A and B                                     | A4            | 1                      | 2                                             |

| SUBB A,#data  | Subtract immediate data from Accumulator with borrow | 94            | 2                      | 2                                             |

| SUBB A,@Ri    | Subtract indirect RAM from Accumulator with borrow   | 96-97         | 1                      | 2                                             |

| SUBB A,direct | Subtract direct byte from Accumulator with borrow    | 95            | 2                      | 2                                             |

| SUBB A,Rn     | Subtract register from Accumulator with borrow       | 98-9F         | 1                      | 1                                             |

| DA A          | Decimal adjust Accumulator                           | D4            | 1                      | 1                                             |

Table 30. Logic operations

| Mnemonic         | Description                                | Hex<br>Opcode | Width<br>(in<br>bytes) | No. of Instruction<br>Cycles for<br>execution |

|------------------|--------------------------------------------|---------------|------------------------|-----------------------------------------------|

| ANL A,#data      | AND immediate data to Accumulator          | 54            | 2                      | 2                                             |

| ANL A,@Ri        | AND indirect RAM to Accumulator            | 56-57         | 1                      | 2                                             |

| ANL A,direct     | AND direct byte to Accumulator             | 55            | 2                      | 2                                             |

| ANL A,Rn         | AND register to Accumulator                | 58-5F         | 1                      | 1                                             |

| ANL direct,#data | AND immediate data to direct byte          | 53            | 3                      | 3                                             |

| ANL direct,A     | AND Accumulator to direct byte             | 52            | 2                      | 3                                             |

| CLR A            | Clear Accumulator                          | E4            | 1                      | 1                                             |

| CPL A            | Complement Accumulator                     | F4            | 1                      | 1                                             |

| ORL A,#data      | OR immediate data to Accumulator           | 44            | 2                      | 2                                             |

| ORL A,@Ri        | OR indirect RAM to Accumulator             | 46-47         | 1                      | 2                                             |

| ORL A,direct     | OR direct byte to Accumulator              | 45            | 2                      | 2                                             |

| ORL A,Rn         | OR register to Accumulator                 | 48-4F         | 1                      | 1                                             |

| ORL direct,#data | OR immediate data to direct byte           | 43            | 3                      | 3                                             |

| ORL direct,A     | OR A to direct byte                        | 42            | 2                      | 3                                             |

| RL A             | Rotate Accumulator left                    | 23            | 1                      | 1                                             |

| RLC A            | Rotate Accumulator left through carry      | 33            | 1                      | 1                                             |

| RR A             | Rotate Accumulator right                   | 03            | 1                      | 1                                             |

| RRC A            | Rotate Accumulator right through carry     | 13            | 1                      | 1                                             |

| SWAP A           | Swap nibbles within Accumulator            | C4            | 1                      | 1                                             |

| XRL A,#data      | Exclusive OR immediate data to Accumulator | 64            | 2                      | 2                                             |

| XRL A,@Ri        | Exclusive OR indirect RAM to Accumulator   | 66-67         | 1                      | 2                                             |

| XRL A,direct     | Exclusive OR direct byte to Accumulator    | 65            | 2                      | 2                                             |

| XRL A,Rn         | Exclusive OR register to Accumulator       | 68-6F         | 1                      | 1                                             |

| XRL direct,#data | Exclusive OR immediate data to direct byte | 63            | 3                      | 3                                             |

| Mnemonic     | Description                             | Hex<br>Opcode | Width<br>(in<br>bytes) | No. of Instruction<br>Cycles for<br>execution |

|--------------|-----------------------------------------|---------------|------------------------|-----------------------------------------------|

| XRL direct,A | Exclusive OR Accumulator to direct byte | 62            | 2                      | 3                                             |

Table 31. Data transfer

| Mnemonic               | Description                                    | Hex<br>Opcode | Width<br>(in<br>bytes) | No. of Instruction<br>Cycles for<br>execution |

|------------------------|------------------------------------------------|---------------|------------------------|-----------------------------------------------|

| MOV @Ri,#data          | Move immediate data to indirect RAM            | 76-77         | 2                      | 3                                             |

| MOV @Ri,A              | Move Accumulator to indirect RAM               | F6-F7         | 1                      | 3                                             |

| MOV @Ri,direct         | Move direct byte to indirect RAM               | A6-A7         | 2                      | 5                                             |

| MOV A,#data            | Move immediate data to Accumulator             | 74            | 2                      | 2                                             |

| MOV A,@Ri              | Move indirect RAM to Accumulator               | E6-E7         | 1                      | 2                                             |

| MOV A,direct           | Move direct byte to Accumulator                | E5            | 2                      | 2                                             |

| MOV A,Rn               | Move register to Accumulator                   | E8-EF         | 1                      | 1                                             |

| MOV direct,#data       | Move immediate data to direct byte             | 75            | 3                      | 3                                             |

| MOV direct,@Ri         | Move indirect RAM to direct byte               | 86-87         | 2                      | 4                                             |

| MOV direct,A           | Move Accumulator to direct byte                | F5            | 2                      | 3                                             |

| MOV direct,Rn          | Move register to direct byte                   | 88-8F         | 2                      | 3                                             |

| MOV<br>direct1,direct2 | Move direct byte to direct byte                | 85            | 3                      | 4                                             |

| MOV<br>DPTR,#data16    | Load data pointer with a 16-bit constant       | 90            | 3                      | 3                                             |

| MOV Rn,#data           | Move immediate data to register                | 78-7F         | 2                      | 2                                             |

| MOV Rn,A               | Move Accumulator to register                   | F8-FF         | 1                      | 2                                             |

| MOV Rn,direct          | Move direct byte to register                   | A8-AF         | 2                      | 4                                             |

| MOVC<br>A,@A+DPTR      | Move code byte relative to DPTR to Accumulator | 93            | 1                      | 3                                             |

| MOVC A,@A+PC           | Move code byte relative to PC to Accumulator   | 83            | 1                      | 3                                             |

| Mnemonic     | Description                                                | Hex<br>Opcode | Width<br>(in<br>bytes) | No. of Instruction<br>Cycles for<br>execution |

|--------------|------------------------------------------------------------|---------------|------------------------|-----------------------------------------------|

| MOVX @DPTR,A | Move Accumulator to external RAM (16-bit addr.)            | F0            | 1                      | 4-11                                          |

| MOVX @Ri,A   | Move Accumulator to external RAM (8-bit addr.)             | F2-F3         | 1                      | 4-11                                          |

| MOVX A,@DPTR | Move external RAM (16-bit addr.) to Accumulator            | E0            | 1                      | 3-10                                          |

| MOVX A,@Ri   | Move external RAM (8-bit addr.) to Accumulator             | E2-E3         | 1                      | 3-10                                          |

| POP direct   | Pop direct byte from stack                                 | D0            | 2                      | 3                                             |

| PUSH direct  | Push direct byte onto stack                                | C0            | 2                      | 4                                             |

| XCH A,@Ri    | Exchange indirect RAM with Accumulator                     |               | 1                      | 3                                             |

| XCH A,direct | Exchange direct byte with Accumulator                      | C5            | 2                      | 3                                             |

| XCH A,Rn     | Exchange register with Accumulator                         | C8-CF         | 1                      | 2                                             |

| XCHD A,@Ri   | Exchange low-order nibble of indirect RAM with Accumulator | D6-D7         | 1                      | 3                                             |

Table 32. Program branches

| Mnemonic              | Description                                              | Hex<br>Opcode | Width<br>(in<br>bytes) | No. of Instruction<br>Cycles for<br>execution |

|-----------------------|----------------------------------------------------------|---------------|------------------------|-----------------------------------------------|

| ACALL addr11          | Absolute subroutine call                                 | D1            | 2                      | 6                                             |

| AJMP addr11           | Absolute jump                                            | E1            | 2                      | 3                                             |

| CJNE<br>@Ri,#data,rel | Compare immed. to ind. and jump if not equal             | B6-B7         | 3                      | 4                                             |

| CJNE A,#data, rel     | Compare immediate to Accumulator and jump if not equal   | B4            | 3                      | 4                                             |

| CJNE A,direct,rel     | Compare direct byte to Accumulator and jump if not equal | B5            | 3                      | 4                                             |

| CJNE Rn,#data rel     | Compare immed. to reg. and jump if not equal             | B8-BF         | 3                      | 4                                             |

| Mnemonic     | Description                                | Hex<br>Opcode | Width<br>(in<br>bytes) | No. of Instruction<br>Cycles for<br>execution |

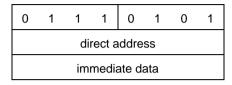

|--------------|--------------------------------------------|---------------|------------------------|-----------------------------------------------|