# Design, Automation and Test for Asynchronous Circuits and Systems

Information Society Technologies (IST) Programme Concerted Action Thematic Network Contract IST-1999-29119

D. A. Edwards W. B. Toms

3<sup>rd</sup> Edition June 2004

# Contents of Report

| Introduction                                           | 1   |

|--------------------------------------------------------|-----|

| 3D                                                     | . 3 |

| ACK                                                    | . 6 |

| ATACS (Automated Timed Asynchronous Circuit Synthesis) | . 8 |

| Balsa                                                  | 10  |

| Butler                                                 | 14  |

| CADP                                                   | 17  |

| CASCADE                                                | 20  |

| CAST (Caltech Asynchronous Synthesis Tools)            | 24  |

| CCS-based specification                                | 29  |

| Clp                                                    | 31  |

| ConfRes                                                | 33  |

| DESI (DEcomposer SIgnal Transition Graph)              | 36  |

| di2pn, syndi and diana                                 | 40  |

| DGC (Digital Gate Compiler)                            | 43  |

| FIREMAPS/Process Spaces                                | 45  |

| Handshake Technology Design Flow                       | 50  |

| LARD                                                   | 53  |

| MINIMALIST                                             | 56  |

| Oolong                                                 | 59  |

| OptiMist                                               | 61  |

| Petrify                                                | 64  |

| Phased Logic                                           | 66  |

| PipeFitter                                             | 69  |

| Punf                                                   | 71  |

| SIS                                                    | 73  |

| TAST                                                   | 75  |

| Theseus NCL Synthesis Flow                             | 78  |

| Transyt                                                | 83  |

| Veraci                                                 | 85  |

| VeriMap                                                | 87  |

| VerySAT                                                | 91  |

| VSTGL                                                  | 93  |

| Weaver/Gate Transfer Level (GTL) synthesis             | 94  |

| XDI                                                    | 97  |

| Testing Asynchronous Circuits                          | 99  |

| Identified Tools & Methodologies 1                     | 03  |

| Original Questionnaire 1                               | 119 |

# Introduction

This report forms part of the deliverable for workpackage 3 of contract IST-1999-29119. It is intended to describe the state-of-the-art in methods and tools for the design of asynchronous digital VLSI systems. This report is intended to be primarily of use to companies, both members and non-members of the Working Group on Asynchronous Circuit Design (*http://www.bcim.lsbu.ac.uk/ccsv/ACiD-WG/*), who are aware of the potential benefits of asynchronous circuit technology, but who need to know more about available asynchronous design methods and tools before committing resources. The report aims to highlight deficiencies in existing approaches and so provide the impetus for further tools development.

# Notes on the 3<sup>rd</sup> Edition:

Nine new tools have been described: CAST, DGC, Oolong, Phased Logic, Verimap, VerySAT and Weaver are described in their own right; syndi and diana are included under the di2pn tool description. Tangram has been replaced by Haste and is now commerically available. Updated submissions were received about the tools ATACS, Balsa, Cascade, Clp, ConfRes, Desi, di2pn, Optimist, Pipefitter, Punf and Theseus NCL Synthesis Flow. No further information has been received about the tools 3D, ACK, CADP, FIREMAPS, SIS, Transyt, Veraci, VSTGL. It is assumed they are in the same state as last year and so their previous submissions have been kept. New references have been added to the Test section.

# Notes on the 2<sup>nd</sup> Edition:

Several organisations have updated their descriptions with new features, FIREMAPS, CADP and di2pn all have new descriptions, ATACS now has a wider availability. It is expected that there are changes to entries for Minimalist and Tangram, but no information is available as yet. There are no notable changes for most of the other tools in the first report. No further information has been received about the tools 3D, ACK, Theseus NCL Flow, Transyt and XDI. It is assumed that these tools are in the same state as last year, and so their previous submissions have been kept. The tool VHDL++ has been removed as it is no longer being maintained. Professor Graham Birtwhistle, who pioneered CCS verification of asynchronous circuits, has retired from his post at the University of Leeds, UK, but currently has a temporary post at the Dept of Computer Science, University of Sheffield, UK. Six new tools have been added: CASCADE, ConfRes, Clp, DESI, Optimist, Punf. New references have been added to the Test section.

# **Introduction to the 1<sup>st</sup> Edition:**

# Scope of the Report

The tools in this report have not been assessed by the authors. Rather, they are a self-evaluation by the creators of the tools in response to an email questionnaire. A search of the published literature has been used to identify tool developers in areas relevant to asynchronous circuits.

#### **Structure of the Report**

The main body of the report contains the self evaluations received from various tools developers. Test methodologies for asynchronous circuits are still in their infancy. The section "Testing Asynchronous Circuits" details some of the more important papers in this area. Appendix A, "Identified Tools & Methodologies," on page 102 of the report identifies tool and methodology developers who were contacted, The original questionnaire is reproduced in Appendix B, "Original Questionnaire," on page 118.

In total, twenty two tools/methodologies are listed in alphabetical order. Four of these, (ACK, Balsa, Tangram and TAST) are primarily concerned with silicon compilation, and two (LARD and VHDL++) with simulation. Two (BUTLER and NCL technologies) exploit libraries of special-purpose components. Five (3D, ATACS, MINIMALIST, Petrify and SIS) perform logic synthesis, with three more (di2pn, Pipefitter and VSTGL) usable as front ends to Petrify. Finally, six (CADP, CCS, Firemaps, Transyst, Veraci and XDI) support formal verification.

# Tool/Methodology: 3D

Developer: Ken Yun Organisation: University of California, San Diego

#### Summary

Today's system components typically employ the synchronous paradigm primarily because of the availability of the rich set of design tools and algorithms and, perhaps, because of the designers' perception of "ease of design" and the lack of alternatives. Even so, the interfaces among the system components do not strictly adhere to the synchronous paradigm because of the cost benefit of mixing modules operating at different clock rates and modules with asynchronous interfaces.

In order to tackle this problem, the synthesis system called 3D has been developed. The 3D system uses a design style called extended burst-mode (XBM). The XBM design style covers a wide spectrum of sequential circuits ranging from delay-insensitive to synchronous. It can synthesize multiple-input change asynchronous finite state machines, and many circuits that fall in the gray area between synchronous and asynchronous which are difficult or impossible to synthesize automatically using existing methods. This implementation of XBM machines uses standard combinational logic, generates low-latency outputs and guarantees freedom from hazards at the gate level.

#### **Strengths and Weaknesses**

Not stated.

#### **Application domain**

Controllers operating in heterogeneous systems – systems with components employing different synchronization mechanisms.

#### **Use of Existing HDLs**

Currently, the 3D system is integrated with HFMIN, an exact two-level logic minimizer, implemented by Robert Fuhrer and Steve Nowick at Columbia University. The integrated technology mapper is adaptable to most commercial CMOS standard cell and mask programmable gate array libraries. Inputs to the 3D tool are textual descriptions of XBM controllers, and outputs are technology-independent logic equations and technology- mapped netlists.

#### **Extent of Automation**

The 3D synthesis system is an implementation of a complete set of automated sequential synthesis algorithms: hazard-free state assignment, hazard-free state minimization, and critical-race-free state encoding.

# Category

Synthesis – Extended Burst Mode asynchronous controllers.

# **Design Flow and Commercial EDA Tool Requirement**

Not stated.

#### **Test Strategy**

Not stated

# **Current Status of Tool**

#### **Current Activities**

The 3D synthesis system is completely functional now. It synthesizes XBM controllers in twolevel AND-OR logic and maps them to a generic CMOS standard cell library or in generalized C-elements. All known bugs have been fixed. It has been used to synthesize the above mentioned chips and is actively used by several research groups, including Intel, IBM, and University of Utah VLSI group.

#### Maintainer

Ken Yun, kyy@ucsd.edu

#### Availability

Available from: *http://paradise.ucsd.edu/3D/*

#### **Future plans**

There is an on-going research efforts to generate multi-level logic and generalized C-element based implementations.

#### Demonstrators

The effectiveness of the XBM design style and the synthesis tool has been demonstrated by designing several chips or modules, some of which are are listed below:

- a low-control-overhead differential equation solver in 0.5um HP CMOS14TB process; http://paradise.ucsd.edu/3D/examples/diffeq

- a commercial-scale SCSI controller, which is functionally compatible with an existing high performance commercial chip and meets the ANSI SCSI-2 standard; *http://paradise.ucsd.edu/3D/examples/scsi*

- an infrared communications chip (in collaboration with HP Labs) capable of transferring data at 800Kbps only dissipating 200mW at peak data rate.

# References

See http://paradise.ucsd.edu/controller.html for hyptext links to the following publications:

[1] W.-C. Chou, P. A. Beerel, and K. Y. Yun, "Average-case technology mapping of asynchronous burst-mode circuits," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 18, no. 10, pp. 1418-1434, Oct. 1999.

- [2] S. Chakraborty, K. Y. Yun, and D. L. Dill, "Timing analysis of asynchronous systems using time separation of events," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 18, no. 8, pp. 1061-1076, Aug. 1999.

- [3] K. Y. Yun and D. L. Dill, "Automatic synthesis of extended burst-mode circuits: part I (specification and hazard-free implementations)," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 18, no. 2, pp. 101-117, Feb. 1999.

- [4] K. Y. Yun and D. L. Dill, "Automatic synthesis of extended burst-mode circuits: part II (automatic synthesis)," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 18, no. 2, pp. 118-132, Feb. 1999.

- [5] S. Chakraborty, D. L. Dill, and K. Y. Yun, "Min-max timing analysis and an applications to asynchronous circuits," *Proceedings of the IEEE*, vol. 87, no. 2, pp. 332-346, Feb. 1999.

- [6] K. Y. Yun, B. Lin, D. L. Dill, and S. Devadas, "BDD-based synthesis of extended burstmode controllers," *IEEE Transactions on Computer-Aided Design of Integrated Circuits* and Systems, vol. 17, no. 9, pp. 782-792, Sept. 1998.

- [7] S. Chakraborty, K. Y. Yun, and D. L. Dill, "Practical timing analysis of asynchronous systems using time separation of events," in *Proceedings of the IEEE 1998 Custom Integrated Circuits Conference*, Santa Clara, California, May 1998, pp. 455-458.

- [8] K. W. James and K. Y. Yun, "Average-case optimized transistor-level technology mapping of extended burst-mode circuits," *in Proceedings of the 1998 International Symposium on Advanced Research in Asynchronous Circuits and Systems*, San Diego, California, Mar. 1998, pp. 70-79.

- [9] W. Chou, P. A. Beerel, R. Ginosar, R. Kol, C. J. Myers, S. Rotem, K. Stevens, and K. Y. Yun, "Average-case optimized technology mapping of one-hot domino circuits," in *Proceedings of the 1998 International Symposium on Advanced Research in Asynchronous Circuits and Systems*, San Diego, California, Mar. 1998, pp. 80-91.

- [10] S. Chakraborty, D. L. Dill, K. Y. Yun, and K-Y. Chang, "Timing analysis for extended burst-mode circuits," in *Proceedings of the 1997 International Symposium on Advanced Research in Asynchronous Circuits and Systems*, Eindhoven, The Netherlands, Apr. 1997, pp. 101-111.

- [11] K. Y. Yun, "Automatic synthesis of extended burst-mode circuits using generalized Celements," in *Proceedings of the 1996 European Design Automation Conference*, Geneva, Switzerland, Sept. 1996, pp. 290-295.

- [12] P. A. Beerel, K. Y. Yun, and W. Chou, "A heuristic covering technique for optimizing average-case delay in the technology mapping of asynchronous burst-mode circuits," in *Proceedings of the 1996 European Design Automation Conference*, Geneva, Switzerland, Sept. 1996, pp. 284-289.

# **Tool/Methodology: ACK**

Developers: Hans Jacobson, Prabhakar Kudva, Ganesh Gopalakrishnan, Erik Brunvand Organisation: University of Utah

#### **Summary**

We define asynchronous systems to be medium to large digital systems whose descriptions include both datapath and control, that may involve non-trivial interface requirements, and whose control is too large to be synthesized in one large controller. ACK is a framework for designing high-performance asynchronous systems of this type. In ACK we advocate an approach that begins with procedural level descriptions of control and datapath and results in a hybrid system that mixes a variety of hardware implementation styles including burst-mode AFSMs, macromodule circuits, and programmable control. Specifically, ACK is a high level synthesis tool that describes the desired system at a procedural level (including datapath specification), and automatically compiles that specification into interconnected control and datapath circuits.

Apart from creating an automated path from high-level specification all the way down to layout, our work on ACK so far has concentrated on providing what we consider to be three of the most important features of a successful asynchronous high-level synthesis tool. While many additional features are needed to form a complete tool these are what we consider to be the most important basic building blocks of the type of framework for asynchronous system synthesis we have outlined.

- New efficient control structures for asynchronous hardwired as well as programmable control. These structures also support thread-level concurrency and sequential chaining of system tasks.

- Provide high-level design optimisation with comprehensible feedback.

- Partitioning and fast and exact synthesis of ASFMs to enable exploration of large design spaces.

#### **Strengths and Weaknesses**

See previous bulleted list. Enables high level design by allowing system level descriptions that include both control and datapath. Weaknesses are that the tools backend isn't currently working as we switch back-end tool support from Cascade to Cadence, no fancy interface so the tool is difficult to drive, some parts of the flow are integrated, others are separate point tools at the moment.

# **Application domain**

Medium to large asynchronous digital systems whose descriptions include both datapath and control, that may involve non-trivial interface requirements, and whose control is too large to be synthesized in one large controller.

# **Use of Existing HDLs**

Front end uses standard Verilog simulation tools (Veriwell, Verilog-XL, etc.), Datapath synthesis uses Synopsys, complex gate synthesis uses Cadence, back-end assembly worked using Cascade, which is no longer available. We are switching to Cadence.

# Category

Synthesis – Partitioned Burst Mode or timed async controllers, standard synchronous datapath synthesis.

# **Design Flow and Commercial EDA Tool Requirement**

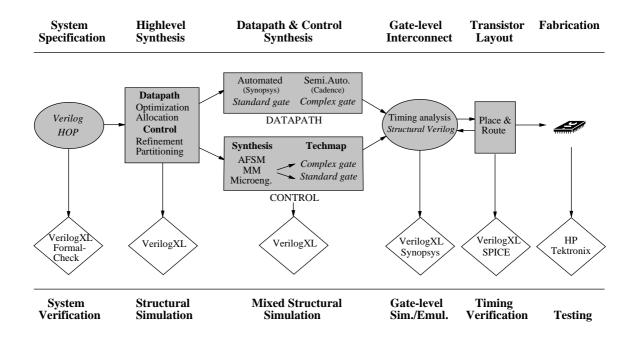

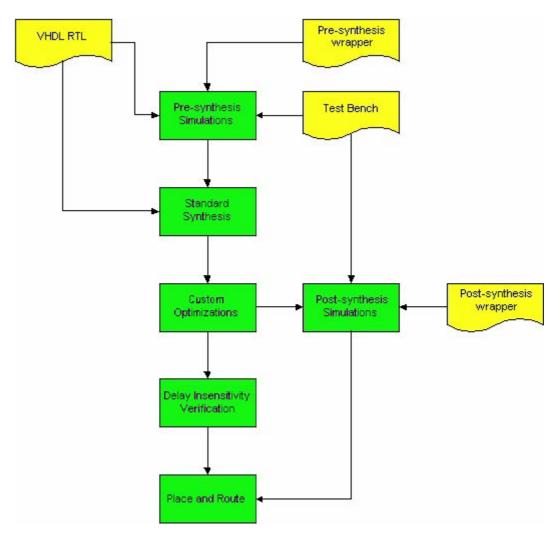

see figure.

# **Current Status of Tool**

In current development. Entire tool is not ready for wide release.

#### Maintainer

Hans Jacobson, hans@cs.utah.edu

#### **Future plans**

Integrate into more usable interface, add back-end support from Cadence, add microengine controller support, firm up Verilog front end.

Figure 1: ACK Tool Flow

# Tool/Methodology: ATACS (Automated Timed Asynchronous Circuit Synthesis)

Developers: Chris Myers, Wendy Belluomini, Hans Jacobson, Sung-Tae Jung, Chris Kreiger, Scott Little, Eric Mercer, Eric Peskin, Nick Seegmiller, Robert Thacker, David Walter, Hao Zheng

# Organisation: University of Utah, USA

#### Summary

ATACS is a synthesis, analysis, and verification tool for timed circuits. Timed circuits are defined to be any circuits that are optimised using explicit timing information. One example is the self-resetting and delayed-reset domino circuits used in IBM's gigahertz research microprocessor. Much of the improvement in speed in this processor can be attributed to these aggressive circuit styles. Another example is the asynchronous circuits utilized by Intel's RAPPID instruction length decoder. This design was 3 times faster while using only half the power of the comparable synchronous design. These results were obtained using aggressive timing assumptions.

The ATACS tool accepts designs given VHDL, handshaking expansions, Petri-nets, burst-mode state machines, timed event/level structures, and state graphs. VHDL descriptions can model a system either at a communication channel level or a signal transition level. Simulation at both levels is supported by VHDL packages developed in our group, and the VHDL code using these packages can be simulated using any commercial VHDL simulator. In most of the specification methods, timing annotations can be made to indicate knowledge about the delays of any given signal transition in the design. This delay information is utilized throughout the design process to optimise the design which is produced. Each of these input forms is compiled into an internal graphical representation. At this point, one of numerous timing analysis methods can be selected to find only those states which are reachable given the provided timing information. Automatic abstraction and partial order methods are provided to improve the efficiency of timed state space exploration.

After finding the reachable state space, a timed circuit implementation can be synthesized. ATACS supports several synthesis algorithms including efficient explicit state methods, BDD implicit methods, and a direct synthesis method which avoids state space exploration and simply generates the circuit from a free-choice Petri net representation. Each synthesis method generates circuits which are hazard-free under a particular technology model. The choices of technology model are: atomic gate, generalized C-elements, standard C-elements, and burstmode.

ATACS also supports analysis and verification. For analysis, a stochastic simulation is performed utilizing provided delay distributions. The result is a reported average-case performance as well as detailed information about areas of the design which contribute the most to the cycle time. For verification, a designer can provide timing constraints that should be checked during timed state space exploration. If a circuit is provided, the circuit will be also be checked for hazard-freedom. Finally, several other properties are checked during state space

exploration including net safety and deadlock. When errors are found a graphical error trace is provided.

### **Strengths and Weaknesses**

Allows for the systematic design of extremely efficient and aggressive circuits. Application is limited to moderate size blocks of a design.

# **Application Domain**

High performance circuits.

#### **Use of Existing HDLs**

Utilizes VHDL as both a front end and back end allowing simulation and integration with commercial tools.

# **Extent of Automation**

Fully automated approach.

#### Category

Synthesis => timing driven

# **Design Flow and Commercial EDA Tool Requirement**

A VHDL simulator is useful. Physical design tools are needed to realize the synthesized logic.

# **Test Strategy**

ATACS supports performance analysis and formal verification. Functional simulation is performed using a VHDL simulator. There is no support for test generation.

# **Current Status**

#### **Current Activities**

ATACS is in continuous development.

#### Maintainer

Chris Myers (myers@ee.utah.edu)

#### Availability

ATACS is available to download for free for academic institutions, SRC member companies, and government agencies for non-commercial research purposes from:

http://www.async.ece.utah.edu.

Others may license ATACS from the University of Utah Technology Transfer Office.

#### **Future Plans**

Improve integration with existing design flows.

#### **Demonstrators**

ATACS was used during the Intel RAPPID project (see JSSC 36(2): 217-228). It was also used to verify several circuits from GUTS (see TCAD 20(1):129-146).

# **Tool/Methodology: Balsa**

# Developers: Andrew Bardsley, Doug Edwards, Lilian Janin Organisation: University of Manchester, UK

#### **Summary**

The Balsa System is a Handshake Circuit based, macromodule synthesis tool-set. Design descriptions are written in the proprietary language Balsa and synthesised into networks of handshake components in a similar manner to the Philips Tangram compiler. These handshake circuits are expressed in a format called Breeze. Breeze is used by all the Balsa tools as a design repository format making the backend tools independent of the frontend Balsa language. Breeze descriptions can be realised as standard-cell VLSI layout using a combination of Balsa tools and commercial CAD. The Balsa language is based on the synchronous channel communicating, fine grain parallel descriptive style of CSP and shares many features with Tangram and OCCAM. The Balsa system can currently generate circuits for several backend technologies: Xilinx FPGAs, ARM generic design rules and cell library (as used to implement AMULET3), two ASIC cell libraries: a 0.35um from Austria Mikro Systems and the 0.18um HCMOS8D STMicroelectronics. A custom-built cell library using the ST process is also available. Adding technologies is relatively simple and tools are available to allow users to target their own cell-libraries. Three choices of data encodings are possible for each of these technologies: single-rail - based in part on our previous work on the EXACT project; dual-rail and 1-of-4 - for easier timing validation. Two further backends are also currently in development: early-single-rail - to allow overlapping of return-to-zero phases of handshakes, and m-of-n encoded - allowing each channel to adopt arbitrary encodings.

The most recent release (3.4) has greatly improved simulation within the Balsa framework Lard has been replaced with the much more efficient *breeze-sim* which allows source-level debugging of Balsa code. The Lard viewer has been replaced by *gtkwave* a signal-viewer maintained by the University of Manchester - which has been enhanced to display channel communications. An animated Handshake Circuit visulisation tool allows circuit allows circuit behaviour to be examined at the Breeze level. The Balsa language has also been updated with new unsynthesisable constructs, such as printing, that aid the construction of test-benches within the Balsa language itself. The balsa-verilog-sim package provides a VPI/PLI interface to several commercially and freely available simulators, allowing complete verilog simulation within the balsa environment.

The Balsa System comprises:

- balsa-c: the Balsa to Breeze compiler.

- balsa-netlist: Breeze to CAD system netlist expansion. Balsa-netlist processes descriptions of the backend technology to produce technology specific netlists.

- breeze-cost: circuit cost estimation for Breeze.

- breeze2ps: Breeze handshake circuit pretty printer.

- balsa-mgr, balsa-md: design management tools. Balsa-mgr is a friendly GUI frontend for the Balsa system allowing design descriptions to be compiled and simulated more easily.

- balsa-make-test: automatically generates test harness for a Balsa description.

- breeze-sim: the preferred simultor working at the handshake component level.

- breeze-sim-control: a graphical front-end to the simulation and visualisation environment

- balsa-verilog-sim: a package which makes Verilog simulation of Balsa descriptions easier by providing wrapper scripts for common simulators and by supporting user-written builtin functions which can be called from Balsa

# **Strengths and Weaknesses**

Rapid development time, transparent design approach. The design of the Balsa System allows new backend technologies and data encodings/handshake protocols to be easily added allowing the designer to choose a point in the speed/area/power design space.

Possibly not optimally efficient.

# **Application Domain**

High complexity, medium performance circuits.

# **Use of Existing HDLs**

Compass, Cadence, Xilinx and Mentor-Graphics commercial tools are used to implement Balsa designs. Balsa-mgr specifically targets several verilog simulators - Icarus, Cver, Cadence's NCVerilog and VerilogXL, Synopsys VCS.

# **Extent of Automation**

Push-button approach from description to layout. Balsa-mgr supports generation and simulation of within the framework, from Breeze to Verilog. A complete flow to layout exists for the custom-built Amust018 cell library using the ST process.

# Category

Synthesis - Silicon compilers

# **Design Flow and Commercial EDA Tool Requirement**

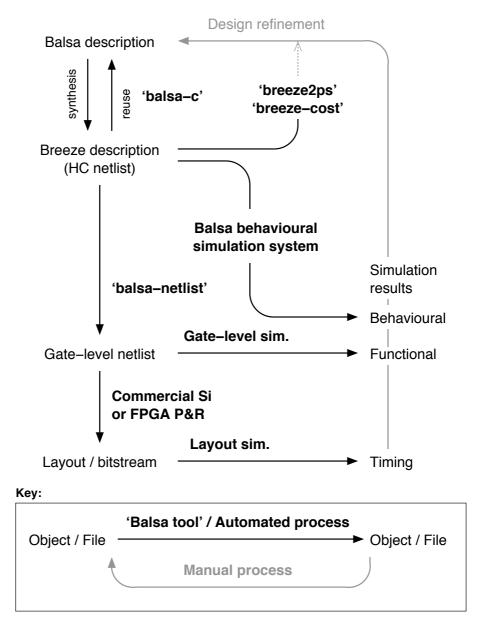

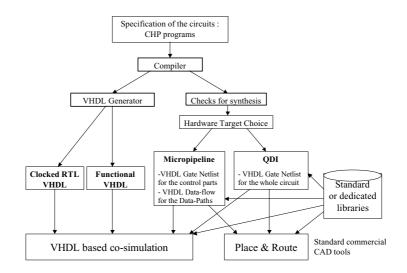

The current Balsa design flows are shown in Figure 1

# **Test Strategy**

Balsa provides an interface to the Breeze-SIM and several commercial verilog simulators for functional simulation. There are no test vector generation tools.

# **Current Status of Tool**

#### **Current Activities**

In current development.

**Figure 1: Balsa Design Flows**

#### Maintainer

Contact: balsa@cs.man.ac.uk

#### Availability

#### GNU GPL

available from: http://www.cs.man.ac.uk/apt/projects/balsa

#### **Future plans**

Better simulation support, Datapath compilation, More target technologies, Data encoding choices

# **Demonstrators**

AMULET3i DMA controller described in "Synthesising an asynchronous DMA controller with Balsa" Andrew Bardsley, Doug Edwards Journal of Systems Engineering 46 (2000) pp 1309-1319

# **Tool/Methodology: Butler**

Developer: Eric Campbell

Organisation: MBDA

#### **Summary**

The Butler Technology provides a general solution to the problem of managing processing and communication resources in an embedded real-time multiple processor system. It includes generic designs for special hardware components that work in conjunction with minimal executive software to provide an efficient execution environment for application functions. The generic designs are parameterised to obtain project specific versions which are then incorporated with conventional processing and communications hardware designs to produce robust, high performance, computing modules.

The generic designs have a modular design structure, being constructed from an assembly of design tiles. Each tile is a design building block that comprises both logic and structure. The logic in each tile is expressed in terms of a few interconnected simple gates. Tiles are butted together to form a two dimensional array that realises overall functionality and in some implementations can directly form part of an integrated circuit layout.

A clock-free, event driven, design approach has been used within the generic designs. This reflects the nature of the reactive computational model being supported. Each design is analysed for correctness by formal mathematical methods. The designs can be easily integrated with other circuitry and implemented in different fabrication technologies because they are not dependent on critical timing parameters. The circuitry has non-demanding power supply requirements.

One of the generic designs is called the butler, a device that can be used with any microprocessor. It provides efficient support for multi-tasking in a single or multiple processor system. It holds control variables for each task assigned to run on the microprocessor and at execution time identifies the next task that should run. The logic for selecting the next task is programmable. Priority levels can be allocated to individual tasks or groups of tasks. Tasks that are given the same priority are selected on a round robin basis within their group. Asynchronous stimuli (e.g. interrupt lines from local peripherals) are handled directly by the butler, scheduling the relevant task when its turn arrives according to the programmed priority level selection. Cooperative and pre-emptive scheduling schemes are supported.

Another of the generic designs is called the route-table, a device that can be used with any physical communication medium. It enables many software routes, each with a range of different interaction characteristics, to be multiplexed onto the same physical communication medium. The butler and route-table operate together to manage the communication and processing resources in a system in a defined way with a minimum of software overhead.

#### **Strengths and Weaknesses**

A major advantage of the approach, especially for products with a long in-service life, is that it does not require the use of any special languages or tools. Designs can be re-implemented,

when hardware obsolescence becomes a problem, using the technology and tools in use at the time.

# **Application Domain**

Our problem domain is the development of dependable, small, harsh-environment, high-performance, low-power, embedded computing in guided weapon systems.

# **Use of Existing HDLs**

# **Extent of Automation**

# Category

# **Design Flow and Commercial EDA Tool requirement**

The butler technology generic designs are integrated with conventional clocked circuitry, often on the same silicon. We use a conventional synchronous design flow overall but inhibit some stages on the asynchronous parts. E.g. We do not use synthesis and optimization because the generic design is already expressed at simple gate level. We do not need to run timing analysers and insert scan paths because we have no clocked latches.

# **Test Strategy**

We analyse the generic design for correctness by formal mathematical methods (this covers all aspects for all versions). This confirms both that the generic design satisfies its specification and that its specification provides for correct system operation.

Knowing that the design for any version is correct means that our production testing need only confirm that each manufactured item conforms to its design. I.e. that every transistor is present and correct. The test pattern developed for each tile type is simply repeated for each tile instance in the array. The clock-free ripple-through design style allows internal states to be observed externally and we are able to achieve full manufacturing fault coverage

# **Current Status of Tool**

#### **Current Activities**

We are applying the butler technology in the design process for a 'next generation' computing module for use in a new missile system

#### Maintainer

Eric Campbell MSc., CEng., M.I.E.E., Technologist Computing Architectures, PB 77, MBDA UK, Six Hills Way, Stevenage SG1 2DA.

eric.campbell@mbda.co.uk

Tel:+44(0)1438 755268 Fax:+44(0)1438 756293

#### Availability

#### **Future Plans**

The butler technology does not require the use of any special asynchronous design tool. The butler technology generic designs are being developed further to include additional features

# **Demonstrators**

The Butler Technology is currently used in two of our missile systems: an advanced short range air-to-air missile called ASRAAM; a ship based anti-missile missile called Seawolf

# **Tool/Methodology: CADP**

# Developer: VASY Team Organisation: INRIA Rhone-Alpes

#### **Summary**

CADP (CAESAR/ALDEBARAN Development Package) is a toolbox for protocol engineering. It offers a wide range of functionalities, from interactive simulation to the most recent formal verification techniques. CADP is maintained by the VASY project at INRIA Rhone-Alpes. It is dedicated to the efficient compilation, simulation, formal verification, and testing of descriptions written in the ISO language LOTOS [ISO standard 8807]. In particular, the toolbox include state-of-the-art tools to perform (enumerative, on the fly, compositional) verification using either bisimulation or mu-calculus methodologies.

#### **Strengths and Weaknesses**

Clearly, the asynchronous concurrency model of LOTOS, which is based upon interleaving semantics, is appropriate for describing networks of processes that execute in parallel and communicate by message passing. This approach is especially suitable for multiprocessor architectures which are difficult to describe accurately using a synchronous approach. Examples can be found at the following URLs:

http://www.inrialpes.fr/vasy/cadp/case-studies/00-f-circuits.html

http://www.inrialpes.fr/vasy/cadp/case-studies/98-f-async-circuits.html

On the other hand, languages based on automata communicating by FIFO queues are not well adapted to hardware systems, as they do not allow to model instantaneous communications (using electric signals) between hardware components. For instance, the request of a processor wanting to access a bus is better expressed using a LOTOS rendez-vous than by putting a message in an infinite FIFO queue.

Compared to other asynchronous process algebras, LOTOS has the merit of being an established international standard, for which many textbooks and tutorials are available (even on the Internet).

Finally, the CADP tools are robust and widely disseminated in more than 274 sites around the world (data: November 2002). They are also available for several platforms including Sun Solaris, Linux PCs and Windows PCs.

#### **Application Domain**

The semantic model of process algebras is general enough not to be tied to a particular kind of hardware systems. For instance, the LOTOS language and CADP tools have also been used to model software and telecommunication systems. So far, in the VASY team of INRIA, we have used LOTOS and the CADP tools to verify bus arbitration and cache coherency protocols for high-end server multiprocessor architectures developed by Bull, the link layer of the IEEE 1394 bus, the bus arbitration protocol of SCSI-2, etc. See:

http://www.inrialpes.fr/vasy/dyade/vasy.html

http://www.inrialpes.fr/vasy/dyade/formalfame.html http://www.inrialpes.fr/vasy/Press/firewire.html http://www.inrialpes.fr/vasy/verdon.

# **Use of Existing HDLs**

We operate at system level. At this level, there is no well-established HDL yet, so our industrial partners are ready to adopt process algebraic formalisms provided that they are supported by robust tools that bring concrete results

# **Extent of Automation**

The enumerative approach used in the CADP allows a large degree of automation. However, to make the best use of the tools, it is suitable to use trained professionals with a background in formal methods and verification tools.

# Category

Formal verifiers/Theorem provers

# **Design Flow and Commercial EDA Tool Requirement**

As far as hardware design is concerned, our methodology consists in establishing a reference specification of the system under design using a formal description technique such as LOTOS. We usually start from an informal description of the system, which we turn into a formal one. So doing, inconsistencies and uncovered issues are often detected. Then, we use the CADP tools to simulate, validate and verify the formal description. This work allows the informal description to be refined and corrected. Then, the informal and formal specifications are used by code writers as a basis to develop Verilog or VHDL code. Additionally, we can use the formal description to generate or validate test suites (see below).

# **Test Strategy**

The CADP toolbox can be used for generating test suites automatically using the TGV tool contained in the CADP distribution. The test suites are derived from a reference specification of the system using a formal description technique (such as LOTOS). They are used to assess the correctness of the actual implementation.

The CADP toolbox can also be used in conjunction with the TorX architecture, developed jointly by the University of Twente, the University of Eindhoven, and Philips Research. TorX is a flexible and open architecture that allows on-the-fly testing, batch test derivation and batch test execution for different specification formalisms.

The CADP toolbox can also be used to check the correctness of execution traces obtained from the real system (or from an execution of Verilog or VHDL code). These traces can be produced using either random testing or "focused" testing. More often, such traces are tedious to verify by a human. The CADP tools allow to check automatically if these traces are accepted by the formal specification.

# **Current Status of Tool**

#### **Current activities**

The CADP toolbox is distributed, maintained and improved by the VASY team of INRIA. Other research groups contribute actively to the development of CADP, and especially the Verimag laboratory, the PAMPA team of INRIA/IRISA, and the TIOS team at the University of Twente.

#### Maintainer

See above.

#### Availability

Information regarding the CADP toolbox, its availability, its recent changes and improvements is available from the following URL:

http://www.inrialpes.fr/vasy/cadp.

This Web page contains centralized up to date information regarding CADP

#### **Future Plans**

#### **Significant Demonstrators**

Two published papers regarding the application of CADP to system-level design of multiprocessor architectures:

http://www.inrialpes.fr/vasy/Publications/Chehaibar-Garavel-et-al-96.html http://www.inrialpes.fr/vasy/Publications/Garavel-Viho-Zendri-00.html

# References

A list of published case-studies involving CADP is available from

http://www.inrialpes.fr/vasy/cadp/case-studies

A list of third-party software developed using CADP is available from

http://www.inrialpes.fr/vasy/cadp/software

# **Tool/Methodology: CASCADE**

Developer: CASCADE-Team (Chair of Digital Technic) Organisation: Kaiserslautern University of Technology

#### **Summary**

CASCADE (Communicating Asynchronous Sequential Circuits: Architecture Development Environment) is a hardware design tool that supports a comprehensive Petri net based design method for asynchronous controllers. Currently, a designer wishing to synthesize a controller consisting of one or several communicating asynchronous circuits is faced with the problem of first having to choose an appropriate design style and then formulating the design problem in that style's particular specification scheme (which in general is not a Petri net). A better approach would be to

- 1. start from a unified design entry using a specification scheme capable of expressing every known kind of asynchronous controller behaviour, and

- 2. then decide upon the appropriate synthesis method.

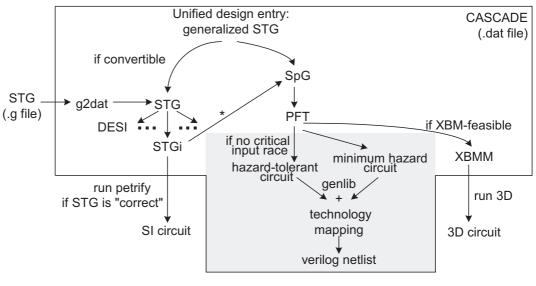

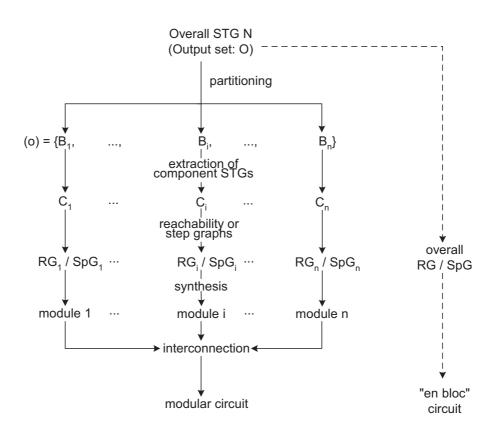

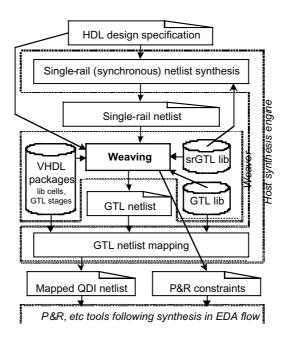

Asynchronous circuits are event-driven. It would be adequate, therefore, to specify the required input-output behaviour from a causal point of view. A causal specification scheme already in use is the signal transition graph (STG) [8]. STGs are interpreted place-transition Petri nets where the firing of a transition represents the occurrence of a rising(+) or falling(-) edge of the binary signal with which it is labelled. Black transitions are used for input signals, white ones for output signals. STGs express causal dependence, independence and exclusion (choice, conflict) between signal edges. However, conventional STGs are unable to express certain kinds of asynchronous behaviour such as pseudo-causalities, causal linkage, biased concurrency, and race causality. These shortcomings have been overcome by the introduction of the generalized STG (gSTG) [5]. CASCADE supports the full modelling power of the gSTG. The additional net elements needed, such as unlabelled and tc-labelled read and inhibitor arcs, have been incorporated into the Petri net editor PED [6] that outputs net data for further processing by CASCADE. This meets our first demand. To meet the second demand (choice of design style), the net data can be preprocessed and handed over to existing synthesis tools (Fig. 1). CASCADE supports speed-independent (SI) synthesis with petrify [3] and extended-burst-mode (XBM) synthesis with 3D. Support of hazard-tolerant synthesis [7] is currently being incorporated (shaded in fig 1).

STG data can be directly handed over to petrify (which includes a feasibility checker) using a format converter. Interfacing to 3D is not possible directly because 3D starts from an XBM machine (XBMM), an FSM-like specification which, if it exists, guarantees implementability [2]. However, CASCADE can derive a primitive flow table (PFT) from the gSTG, check it for XBM feasibility, and, if positive, transform it into an XBMM. Certain forms of output concurrency, not implementable by a single XBMM [2], are treated by a parallel decomposition algorithm for PFTs [4] as part of CASCADE's transformation procedure. Multiple-output-change (MOC) behaviour (in the sense of [1], where a single change of the input state causes a sequence of output-state changes), which is forbidden in a single XBMM, but may realized by a set of interacting 3D circuits, can also be handled using CASCADE, as

shown in Sect. 3.1. This enables designers to implement systematically a larger class of behaviour than ever berfore.

: still under development

#### Figure 1: Comprehensive Design Method

# **Strengths and Weaknesses**

As a standalone tool, CASCADE is very useful in synthesizing asynchronous controllers with STG as specification. Users can derive either minimum hazard equations or XBMMs from STG. CASCADE has been used internally until now. We would be very grateful for any feedback that can improve this tool.

# **Application domain**

High-speed asynchronous controllers.

# **Use of Existing HDLs**

The initial STG can be read from g-files (petrify). The Netlist can be generated in Verilog (early development ...). Gate libraries are read in genlib format (from SIS).

# **Extent of Automation**

The graphical user interface provides a 'single button sythesis', as well as access to all synthesis parameters.

# Category

Synthesis - gSTG/Petri net.

# **Design Flow and Commercial EDA Tool Requirement**

CASCADE is a standalone synthesis tool. Within CASCADE the graphical Petri net editor "PED" is used to create a (g)STG which specifies the system's behavior. CASCADE will

derive either a single two level AND-OR-circuit, or a combination of two level circuits. If a gate library is provided, the circuits will be transformed into netlists.

# **Test Strategy**

We are still working on netlist generation that will enable simulation of the circuit with other tools.

# **Current Status of Tool**

The minimum hazard and XBM synthesis branch have been used internally for quite a time and are judged to be reliable. The hazard-tolerating synthesis is hardly tested and still being worked on.

# **Current Activities**

We are currently testing the hazard-tolerating synthesis and also the technology mapping part of the tool. We have done some improvements to CASCADE's graphical user interface. The STG decomposer tool (DESI) is also being improved. Interfacing with HDL is under development.

#### Maintainer

Karsten Laux: laux@eit.uni-kl.de

Benedictus Kangsah: kangsah@rhrk.uni-kl.de

#### **Tool Availability**

Available from *http://www.eit.uni-kl.de/beister/eng/projects/download.html*

#### **Future plans**

We will continue to improve CASCADE as described above in current activities.

# **Significant Demonstrators**

CASCADE has been tested with some controller specification, e.g. Fifo, VMEbus Interrupt, etc. All of the examples have been included in the CASCADE package in PED format.

# References

- [1] Unger, S.H. "Asynchronous Sequential Switching Circuits". R.E. Krieger, reprint 1983 (original edition 1969).

- [2] Yun, K.Y. "Synthesis of Asynchronous Controllers for Heterogeneous Systems". PhD thesis, Stanford University (1994).

- [3] Cortadella, J. "*Petrify: A tutorial for the designer of asynchronous circuits*". Available as part of the petrify tool package from: *http://www.lsi.upc.es/jordic/ petrify*.

- [4] Beister, J., Eckstein, G., Wollowski, R.. "From STG to Extended-Burst-Mode Machines". In: Proc. of the 5th Int. Symp. on Advanced Research in Asynchronous Circuits and Systems, Barcelona (April 1999). IEEE Computer Society Press.

- [5] Wollowski, R., Beister, J. "Comprehensive Causal Specification of Asynchronous Controller and Arbiter Behaviour". In: Yakovlev, A., Gomes, L., Lavagno, L. (eds.): Hardware Design and Petri Nets. Kluwer Academic Publishers, Boston (2000) 3-32.

- [6] Tiedemann, R.: Dokumentation PED Version 4.3 (Benutzerleitfaden). Technical Report, Cottbus Technical University (June 1997).

- [7] Eckstein, G. "Logischer Entwurf hasardtoleranter asynchroner Schaltwerksverbünde (Logical design of hazard-tolerant communicating asynchronous circuits)". Doctoral dissertation, University of Kaiserslautern. Fortschritt-Berichte VDI, Reihe 20, Nr.324. VDI-Verlag, Düsseldorf (2000).

- [8] Kondratyev, A., Kishinevsky, M., Yakovlev, A. "*Hazard-free implementation of speed-independent circuits*". IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Volume 17 (September 1998).

# **Tool/Methodology: CAST (Caltech Asynchronous Synthesis Tools)**

# Developers: Alain J. Martin, Mika Nyström Organisation: California Institute of Technology

# **General Summary**

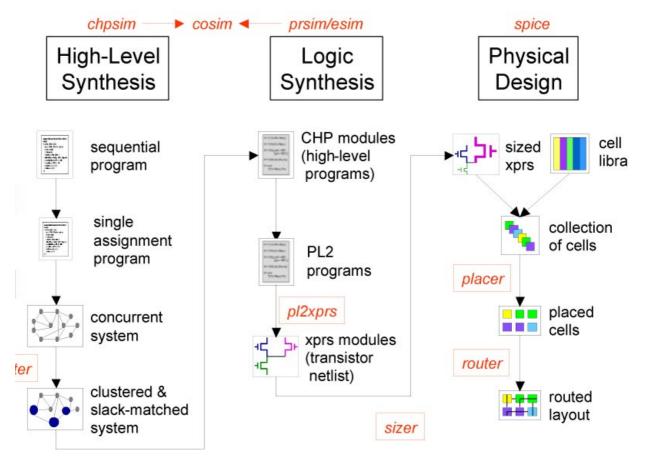

CAST is the name of the suite of design tools developed to support the Caltech synthesis method for asynchronous QDI (*quasi delay-insensitive*) circuits. The method is based on synthesis by program transformations. The system to be designed is first described in the high-level language CHP. This description is refined, manually or automatically, into a more concurrent version. Once the desired degree of concurrency among the CHP components and the desired granularity for each CHP process are achieved, the CHP processes are translated into the HSE (*handshaking expansion*) notation, in which all communications are replaced with handshake protocols, and all variables are implemented in terms of booleans. The HSE representation can also be modified. HSE processes can be decomposed further, but the most important transformation at this level is what is called "reshuffling": handshake protocols on different channels are made to overlap to some degree in order to improve efficiency or simplify the implementation. Finally, all explicit sequencing is removed by translating the HSE representation as a traditional SPICE netlist, and it is therefore considered the target of the logic synthesis. The CAST toolset consists of:

- high-level synthesis tools including both source-to-source (CHP) decomposition tools and logic-synthesis tool. (2)

- simulation tools at various levels of representation - both logic and performance simulation including energy and timing, and electrical simulation, and tools for cosimulation of a design mixing different levels of representation

- low-level tools for translation of production-rule sets into layout, as well as placement and routing, and tools for checking electrical properties of layout (charge sharing, slew rate, etc).

The CAST toolset provides several alternative paths for designers: the standard CAST solution (described in more detail below and shown in the figure) is a specialization of the general method targeting a specific building block called PCHB. Other paths are also possible starting from any HSE representation.

The different programs of the suite are structured so as to make it possible for the designers to tailor the tools to their styles, needs, and experiences, by carefully designing the interfaces in such a way that replacing one tool with another should be easy. The current design procedure embodied in the CAST tools represent a specialization of the asynchronous design techniques pioneered at Caltech in the 1980s and used to design the world's first asynchronous microprocessor rather than a departure from those techniques. The traditional technique consisted of a series of stepwise refinements starting at the CHP level and ending in finished PRS, proceeding through the HSE level of description. The HSE level was important in this

Figure 1: The CAST Toolset

design style because this is the level at which all abstract channels are replaced with booleans and all inter-process sequencing decisions (e.g., channel handshakes) are specified. The HSE level has lost of its importance in the current generation of the tools because the current generation uses very few unique HSE reshufflings, and therefore it is unnecessary to repeat the work of compiling from HSE to PRS for each and every process that is designed. Large systems, such as the MiniMIPS processor and the Lutonium microcontroller, have been designed using as few as three different HSE "templates" for the vast majority of circuits. A small fraction of the circuits still present special design problems, however (in the Lutonium, six-transistor SRAM memories were an example), and in these cases, hand design using HSE is still the norm. A tool for synthesizing those designs automatically from HSE to PRS (aptly named *hse2prs*) is included in CAST.

# **Strengths & Weaknesses**

CAST does not yet integrate a testing procedure.

# **Application Domain**

CAST is a general tool suite with emphasis on high-performance microprocessor design.

# **Use of Existing HDLs**

For high-level description, the CAST tools use the language CHP, which was developed and refined at Caltech over the last decade, rather than VHDL or Verilog. However, an alternative is provided in the form of a subset of VHDL that exactly implements the constructs of CHP. This language is called CHDL. A user designing in CHDL will be in the familiar environment of VHDL. The resulting code is translated into CHP at little cost. From then on, the design flow is the same.

# **Extent of Automation**

Our goal is to make the CAST tools entirely automatic, from high-level representation to the final layout. Currently, there are only some small gaps in the tool flow that are in the process of being filled in. More important than the extent of the automation, however, is the way in which the automation has been achieved. The CAST tools are designed in accordance with the idea of "designer-assisted compilation": the idea is that the designer can affect any step of the compilation procedure and insert his own design. This goes for all levels from the highest decompositions to the lowest-level layout descriptions. The CAST tools thus make it easy to mix high-level automatically decomposed circuits with hand-designed SRAM cells and other special circuits. All the different levels of description are presented in one unified representation to make this easy.

# Category

QDI-Synthesis

# **Design Flow and Commercial EDA Requirement**

The CAST toolset is built around a way of designing circuits that consists of a sequence of systematic, provably correct transformations that take the designer from an initial specification to a final layout geometry. As we have seen, this sequence of transformations passes through a number of representations, e.g., CHP, HSE, PRS, transistor netlists, and various representations of layout geometries. The tools support several transformation paths, and users are free to add their own, using their own tools or standard commercial tools from other commercial CAD vendors.

**High-Level Synthesis.** The first step in the CAST design flow is process decomposition, which transforms sequential high-level descriptions of circuit behavior into a system of communicating modules. Each module is still expressed in a high-level language and they are normally each synthesized individually at lower levels. The goals of process decomposition are to expose concurrency and facilitate low-level synthesis while producing a system with an acceptable throughput but not a surfeit of communications. (In most QDI systems, the computation of values consumes significantly less energy than the communication of these values.) Previous approaches to automated process decomposition have been syntax-directed and unable to produce modules suited for implementation as the fine-grain pipeline stages (*precharge half-buffers*, or *PCHB*) used in the high-performance MiniMIPS and Lutonium asynchronous microprocessors. The CAST tool flow features *data-driven decomposition* (DDD), the first decomposition method to target the fast PCHB asynchronous circuit family. The CAST tool chain gives users the freedom to choose between DDD, syntax-directed decomposition, and performing the process decomposition by hand. DDD creates a working concurrent system where every module can be implemented by a PCHB circuit. DDD starts by

ACiD-WG

converting the original specification into DSA *dynamic single-assignment* form and maintaining it in that form; it then proceeds by process decomposition through *projection*.. The last stage of DDD is to cluster the DSA modules into larger modules to improve energy (reducing the number of communications in the system) and performance (cutting forward latency while still running at the desired throughput). The final output is a concurrent system where communicating modules may implement the computations of one or multiple variables, or may be simple buffers inserted to improve system performance. All modules fit the PCHB circuit template. CAST contains tools that convert deterministic CHP programs into DSA form, analyze the data dependencies in a DSA program and output a system of CHP modules equivalent to the original sequential specification. A tool that implements the final clustering stage of DDD is currently under development.

Production Rules to Layout. The CAST toolset takes the Production Rule Set (PRS) as the boundary between logical and physical design; production rules are the target of the logical design and the specification for the physical design. However, a production-rule set is a purely logical specification, and it is not sufficient for driving the physical design tools. In order to provide a specific enough (but not over-specific) description of the system, the CAST toolset uses a new representation called the Extended-Production-Rule Set (XPRS). This representation specifies transistor-gate ordering and transistor-gate widths, but it does not specify the complete circuit topology, nor does it specify any other geometry information. The XPRS notation is ideal for transistor sizing and it is also ideal for human-produced low-level descriptions: using XPRS, a designer can specify all relevant details about an asynchronous circuit implementation without having to edit actual chip layout directly. The introduction of XPRS subdivides what was formerly one task (sizing, gate ordering, and specification of the netlist) into two tasks (sizing and gate ordering on the one hand and specification of the netlist on the other). The CAST tools convert the standard PRS into XPRS as the first step in the physical-design flow. This conversion is done in one of three ways: *i*) Automatically through gate matching. (ii) Automatically through XPRS generation from PRS. (iii) Manually or by logical-design tools. The three ways are used as follows: the automatic methods are used when a PRS is given. First of all, gate matching is performed: the CAST system is able to match a given PRS against a gate library whose cells are described in XPRS - in this case, the presence of a cell in the gate library is taken to mean that the transistor-gate ordering is arbitrary, and logically equivalent cells are matched against the given PRS. Secondly, remaining PRs are converted by a special XPRS generator: this generator makes the decisions regarding transistor-gate ordering and gate sharing; this is the least preferred approach because the XPRS generator has to be conservative about its designs in order to guarantee that they function properly. The final method of generating XPRS is the simplest: the user simply specifies the gate ordering. Normally, however, the "user" is a higher-level tool in the CAST logical-design suite; this tool will have the necessary information to pick a reasonable gate ordering and sharing. In the current system, automatic gate matching has not yet been implemented; this is not a major drawback because most circuits are compiler-generated anyhow, and the compiler is aware of the structure of the standard-cell library.

**Placement and Routing.** The CAST toolchain is extremely flexible with regard to cell placement. Cells can either be placed manually by the designer by leaving the appropriate directives in the CAST code, or the placement can be done automatically. If it is done automatically, special directives can still be used in order to perform datapath placement – the regularity of a datapath means that extra information is available in order to optimize the

routes. The CAST03 system makes it easy for the designer to specify this extra information. Routing is performed by a proprietary CAST router. The CAST router routes nets one at a time, it supports rip-up-and-reroute for batch mode "hands-off" routing, and it works with all standard ASIC processes. The router makes it very easy to combine standard cells with handdrawn layout, in keeping with the CAST philosophy of designer-assisted compilation.

**Commercial EDA Requirement.** Currently, the CAST tools do not require the use of any commercial tools. It is our intention to keep the use of commercial tools as small and as optional as possible in order to enable the entire system to be used for a very small start-up cost.

# **Test Strategy**

Currently, CAST does not have any special features devoted to testing.

# **Current Status**

The status of the CAST tools project can be summarized as follows. At the logic-synthesis level, an automatic procedure exists for decomposing any given CHP or CHDL program into a network of small components. Also, the core of the logic synthesis – the transformation from CHP to PRS – has been formalized. At the simulation level, the framework of the CAST toolset has been defined and the interfaces have been delineated. A CHP simulator now exists, and a new method for mixed-level simulation or cosimulation has been defined. At the physical-design level, a standard-cell library has been defined and built. The front-end of a cell generator (*stackgen*) has been developed, as well as two placers (one constraint-based and one based on simulated annealing) and a router. An extended version of the PRS language, called XPRS, has been defined that contains information about transistor ordering and sizing. XPRS makes it possible to layout a chip without need to edit the layout manually.

# **Current Activities**

#### Maintainer

The CAST tools are maintained by the Asynchronous VLSI Group of the Computer Science Department at the California Institute of Technology, Pasadena, California, U.S.A., and by Situs Logic, Pasadena, California, U.S.A.

#### **Tool Availability**

The CAST tools are currently only available internally at Caltech and Situs Logic, although earlier versions have slightly wider circulation. Situs Logic is in the process of commercializing the tools for a wider range of users.

#### **Future Plans**

N/A

# Significant demonstrators

Previous versions of the CAST tools have been used to design the Caltech Asynchronous Microprocessor (the world's first asynchronous microprocessor), the MiniMIPS processor (a two-million-transistor quasi delay-insensitive clone of the MIPS R3000), and various other chips. The current version of the CAST tools is being used to design the Lutonium microcontroller, an Intel-8051 compatible microcontroller.

# **Tool/Methodology: CCS-based specification**

Developer: Graham Birtwistle Organisation: School of Computing, Leeds University, UK

#### **Summary**

The work of the Leeds based group is methodological not tool building. We are interested in finding ways to specify the control signals in large realistic circuits. We specify in the CCS notation and use its CONCURRENCY WORKBENCH support tool to minimise, equivalence and property check.

The Leeds work was preceded by work at Calgary, Canada, where we used CCS to specify cell libraries and then design three variations of a (very) small microprocessor (4-phase (RTZ), 4-phase with exception handing, and 2-phase pipelined). The last machine was laid out by Tom Borsodi from our CCS specification in Actel FPGA technology using Erik Brunvand's thesis as guideline. One chip was required for the 8-deep register bank; the rest fitted onto another.

With Ying Liu (also at Calgary), we worked with the Amulet group at Manchester University formalising the design of AMULET1, their 2-phase asynchronous version of ARM6. We put a lot of work into picking an appropriate notation for extracting the specification from the Manchester architects in a manner that made them feel comfortable and from which we could derive the CCS specifications mechanically. We also put a lot of time into coming up with the right levels of abstraction. We formalised and checked the 5 main floor plan elements. We also have an instruction level specification which clarifies the links amongst the floorplan elements. We are now looking at facts and figures on 2- and 4-phase pipelines and working round the problems encountered with Ying. The latest (Harvard-style) architecture is temporarily called TK (short for trinket - a cheap amulet, according to Websters). Once this is sorted, then a 4-phase version will be studied.

#### **Strengths and Weaknesses**

CCS is a small language with a fully defined syntax and semantics; with well defined equivalence rules; and a match with the powerful modal mu calculus for property checking. CCS is a suitable notation for specifying and reasoning about control signals in 2-phase or 4-phase asynchronous systems. It has been used to reason about control in circuits from the gate level and above. Its support tool, the CWB, is public domain. It has been found to be robust and reliable and has been used to minimise and property check pipelined circuits with 10<sup>50</sup> or more states.

Its weaknesses include:

- it does not handle data values well being best suited to the study of control signals only;

- it is however not a programming language and CCS descriptions cannot be run as simulations;

- its notion of time is "before" rather than numerical so it cannot be used for performance estimations.

# **Application Domain**

Modelling of asynchronous 2- and 4-phase pipelines and proving theorems about their state spaces; the specification and property checking of AMULET like (but simpler) microprocessor designs.

# Use of existing HDLs

CCS is not a HDL

# **Extent of Automation**

CCS specifications are entered into the CWB and syntactically checked. They may then be minimised to the least equivalent state machine; property checked (deadlock etc.) and checked for equivalence against other definitions (e.g. an implementation) by built-in procedures.

# Categories

Verifier

# **Design Flow and Commercial EDA Tool Requirement**

Stand alone.

# **Test Strategy**

Property checking and equivalence checking.

# **Current Status of Tool**

See Concurrency Workbench, Edinburgh University.

#### **Current Activities**

- proving facts about 2- and 4-phase pipelines.

- extending a basic RTL model to include exception handling, register forwarding, etc.

#### Maintainer

Professor Graham Birtwhistle has now retired from his post at the University of Leeds.

#### Availability

CCS was designed by Robin Milner while at Edinburgh University. Its public domain CWB support tool is freely available from CS at Edinburgh.

#### **Future Plans**

Continuation of the current program

#### Demonstrators

Published papers and theses available via: www.comp.leeds.ac.uk/research/asynch.html

# **Tool/Methodology: Clp**

#### Victor Khomenko

# School of Computing Science, University of Newcastle upon Tyne

#### **Summary**

Clp-- a Model Checking Engine Based on Petri Net Unfoldings is an integer programming based model checker. It can formally verify various safety properties (e.g. deadlock-freeness and mutex), and detect of coding (CSC and USC) conflicts in STGs. Clp employs finite complete prefixes of Petri net unfoldings (e.g. those produced by the Punf tool [3].

#### **Strengths and Weaknesses**

Memory efficient and quite fast, though the performance on large benchmarks might be not entirely satisfactory; we deal with this problem in the VerySAT tool (see current status below).

# **Application domain**

verification and synthesis of self-timed circuits.

# Use of existing HDLs

none (works on finite prefixes in the `.mci' format).

### **Extent of automation**

fully automatic.

# Category

synthesis=>STG/Petri net

#### **Design flow**

Clp is intended as a powerful model checking engine to be used by other applications. Currently, prefixes produced by Punf [3] can be used by Clp for detection of coding (CSC and USC) conflicts and normalcy violations. Clp, together with Punf and ConfRes tools, comprise a framework for detection and resolution of coding conflicts in STGs [6,7].

#### **Test strategy**

Clp can formally verify many safety properties (e.g. deadlock-freeness and mutex).

#### **Current status of the Tool**

Clp is fully operational. It is integrated into the PEP tool [1]. We work on a tool VerySAT offering similar functionality but employing a SAT solver rather than a specialized integerprogramming one, which is often faster [8].

#### Maintainer

Victor Khomenko (Victor.Khomenko@ncl.ac.uk).

#### Availability

Available for research purposes from

http://www.cs.ncl.ac.uk/people/victor.khomenko/home.formal/tools/tools.html

#### **Future plans**

We plan to create a full design cycle for self-timed circuits based on Petri net unfoldings and not involving building the state space at any stage. VerySAT is to replace Clp in near future as its performance is much better.

#### References

- [1] E.Best and B.Grahlmann: "*PEP: Documentation and User Guide, Version 1.4. Manual*" (1995).

- [2] V.Khomenko: "*Model Checking Based on Prefixes of Petri Net Unfoldings*". PhD Thesis, Department of Computing Science, University of Newcastle (2002).

- [3] V.Khomenko: "Punf: Documentation and User Guide", Version 6.01. Manual (2002).

- [4] V.Khomenko: "Clp: Documentation and User Guide". Version 3.01beta. Manual (2002).

- [5] V.Khomenko and M.Koutny: "LP Deadlock Checking Using Partial Order Dependencies". CONCUR'2000, LNCS 1877 (2000) 410-425.

- [6] V.Khomenko, M.Koutny, and A.Yakovlev: "*Detecting State Coding Conflicts in STGs Using Integer Programming*". DATE'2002, IEEE Comp. Soc. Press (2002) 338-345.

- [7] A.Madalinski, A.Bystrov, V.Khomenko, and A.Yakovlev: "Visualization and Resolution of Coding Conflicts in Asynchronous Circuit Design". DATE'2003, IEEE Comp. Soc. Press (2003) to appear.

- [8] V.Khomenko, M.Koutny, and A.Yakovlev: "Detecting State Coding Conflicts in STG Unfoldings Using SAT. ICACSD'2003", IEEE Comp. Soc. Press (2003) submitted paper.

# **Tool/Methodology: ConfRes**

#### Developer: A.Madalinski

#### Organisation: University of Newcastle upon Tyne, UK

#### **Summary**

The tool supports semi-automated resolution of Complete State Coding (CSC) conflicts in asynchronous circuit specification given as Signal Transition Graphs (STGs) and display them as partial orders (finite and complete prefixes of STG unfoldings). Being more efficient than the automated methods the manual approach requires a significant effort from the designer. The tool ConfRes assists the designer by visualising the conflicts cores, their superposition and the constraints on signal insertion.

Cores extend the known concept of complementary sets. Only those complementary sets are used which are not combinations of others . The advantage of using cores is that only those parts of STGs are considered, which cause coding conflicts, rather than the complete set of conflicts. Since the number of cores is usually much smaller than the number of coding conflicts, this approach saves the designer from analysing large amounts of information. Moreover, cores are represented at the level of the STG unfolding prefix, which is a convenient model for understanding the behaviour of the system due to its simple branching structure and acyclicity.

Cores are important for resolving coding conflicts. They can be eliminatedby adding auxiliary signals and by concurrency reduction, respectively. The former introduces additional internal signals to disambiguate encoding conflicts and the latter reduces the state space in the STG's reachability graph and thus potential encoding conflicts. The resolution process uses the partial order model and employs the visualisation concept as follows: (a) shows the superposition of cores by meansof a 'height map' (b) only those cores are displayed which are relevant to selected part of the specification, i.e. cores which are extracted from the height map and (c) the constraints on insertion identify a small part of the specification rather than the entire design. In addition, heuristics are used to pre-compute solutions, which are suggested to the designer. These can be used as guidelines, however, the designer is free to intervene at any stage and choose an alternative solution in order to account the design constraints.

ConfRes takes an STG in the '.g' format supported by Petrify, an STG-based synthesis tool. It uses Punf, a Petri net unfolder, to produce a finite and complete prefix of the STG, and either Clp[2], a linear programming model checker or VerySAT [4], a SAT based model checker, to detect coding conflicts in the STG. Both of these tools are described elsewhere in this report. After the detection of conflicts, cores are computed and the resolution process is applied. The tool guides the designer through all the stages. During this process the cores and the corresponding height map are visualised using Dot [5], a graph drawing software by AT&T, and the designer can interactively insert new signals to obtain a customised solution.

#### **Strengths and Weaknesses**

Manual approach requires human participation. For this reason the designer should be familiar with STG-based design. The tool, however, minimises the efforts of the designer by using a

compact model, the concept of cores and constraints on insertion. In addition, it suggests solutions, which can be used as a guideline.

# **Application Domain**

High-speed asynchronous controllers, e.g. interface logic, pipeline controllers

# **Use of Existing HDLs**

none

#### **Extent of Automation**

The tool is aimed at facilitating a manual refinement of an STG with coding conflicts. Its guides the designer through the steps of the resolution process, where the designer is free to choose a location for the signal insertion.

# Category

Synthesis STG/Petri net

# **Design Flow and Commercial EDA Tool Requirement**

Any STG-based synthesis, where next-state functions are computed, needs solving coding conflicts. In particular, ConfRes can be employed in combination with STG unfolding based model checker and synthesis tool VerySAT [4] to solve the CSC problem. Alternatively, ConfRes can be used in combination with the state-based synthesis tool Petrify [1] to enforce the CSC condition, and thus to obtain a tailor made solution.

# **Test Strategy**

N/A

# **Current Status of Tool**

ConfRes is at the alpha-stage

#### **Current activities**

Extensive testing

Maintainer A. Madalinski (a.a.madalinski@ncl.ac.uk)

**Tool Availability** http://async.org.uk/movie/

**Future Plans** Greater extension of automation.

**Demonstrators** none

# References

- [1] J. Cortadella, M. Kishinevsky, A. Kondratyev, L. Lavagno, and A. Yakovlev: "*Petrify: a tool for manipulating concurrent specifications and synthesis of asynchronous controllers*". In XI Conference on Design of Integrated Circuits and Systems, (1996).

- [2] V. Khomenko: "*Clp Documentation and User Guide*". Department of Computing Science, University of Newcastle (2002).

- [3] V. Khomenko: "*Punf Documentation and User Guide*". Department of Computing Science, University of Newcastle (2002).

- [4] V. Khomenko, M. Koutny, and A. Yakovlev: "Logic synthesis avoiding state space explosion". In Int. Conf. on Application of Concurrency to System Design. IEEE Computer Society Press, (2004 - to appear).

- [5] E. Koutsofios, and S. North: "Dot User's Manual", AT&T Labs-Research (2002).

- [6] A. Madalinski: "ConfRes: Interactive coding conflict resolver based on core visualisation". In Int. Conf. on Application of Concurrency to System Design. IEEE Computer Society Press, (2003).

- [7] A. Madalinski, V. Khomenko, A. Bystrov, and A. Yakovlev: "Visualisation and Resolution of Coding Conflicts in Asynchronous Circuit Design". IEE Proceedings, Computers and Digital Techniques, Special Issue on Best Papers from DATE03, (2003).

# Tool/Methodology: DESI<sup>1</sup> (DEcomposer SIgnal Transition Graph)

Developer: B. Kangsah, R.Wollowski, W. Vogler, and J. Beister Organisation: Kaiserslautern University of Technology

### **Summary**

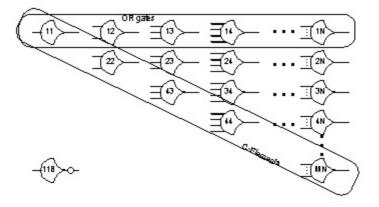

Signal Transition Graphs (STGs) are a version of Petri nets for the specification of asynchronous circuit behaviour. As a first step in the indirect synthesis of a circuit corresponding to a given STG N, one usually constructs the reachability graph (e.g. when using the tool petrify) or the step graph (e.g. using CASCADE [2]). A serious problem - state explosion - may occur when constructing such a graph: the number r of reachable states (markings) may become too large to be handled due to insufficient storage space or too long CPU times. To avoid state explosion, one could try to decompose the STG N into components Ci (and thus, the circuit into modules). The reachability graphs of the Ci, taken together, can be much smaller than r since r might be the product of their sizes. Even if this is not achieved, decomposition can reduce design effort and save circuit area. Where N may have to be synthesized by heuristic methods, its components Ci may even be handled by exact methods yielding optimal results. Decomposition can also be useful aside from size considerations: there are examples where N cannot be handled by a certain synthesis method, while its Ci can (e.g. deriving a set of XBM machines from an STG [1]). It may also be possible to extract library elements; this is particularly valuable for arbiters, which are difficult to design.

We have presented a decomposition algorithm [5] that is based on that of Chu [3] but is much more generally applicable. In particular, there is no restriction to live and safe free-choice nets or to marked graphs, and labels are not required to occur only once. A formal proof based on a formal correctness criterion has been given. The algorithm starts with a given partition of the set of output variables: each Ci is responsible for one block of the partition. The Cis are then extracted from the STG by transition contraction, care being taken to keep only the relevant input signals, which may be global inputs or outputs of other components. The kernel of the algorithm has been implemented in DESI (DEcomposer SIgnal Transition Graph). DESI is originally design as part of CASCADE, which can also forward results to other synthesis tools such as petrify and 3D.

## Strengths & Weaknesses

With STG decomposition one may be able to:

- avoid state explosion

- reduce design effort

- save circuit area

- derive a set of XBM machines from an STG

<sup>1.</sup> This work was partially supported by the DFG-project ` STG-Dekomposition' Vo615/7-1 / Wo814/1-1.

• extract library elements.

The STGs to be decomposed has to fulfill the following requirements:

- no internal transitions

- no auto-concurrency

- no structural auto-conflicts

- no i/o conflicts.

For more detail, please refer to [5].