# AMD Alchemy<sup>™</sup>Au1500<sup>™</sup> Processor Data Book

March 2006 Publication ID: 30361D

#### © 2006 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD Arrow logo, and combinations thereof, and AMD Alchemy and Au1550 are trademarks of Advanced Micro Devices, Inc.

MIPS32 is a trademark of MIPS Technologies, Inc.

Microsoft and Windows are registered trademarks of Microsoft Corporation in the United States and/or other jurisdictions.

SafeNet and CGX are trademarks of SafeNet, Inc.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# Contents

| List | of Figure                                                                     | es                                                                                                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List | of Table                                                                      | s 9                                                                                                                                                                                                                                                               |

| 1.0  | 1.1 Pr                                                                        | ew         13           oduct Description         13           vatures         14                                                                                                                                                                                 |

| 2.0  | 2.1 Cc<br>2.2 Ca<br>2.3 Wi<br>2.4 Vir<br>2.5 Ex<br>2.6 MI<br>2.7 Cc<br>2.8 Sy | 15         ore       15         aches       17         rite Buffer       23         rtual Memory       26         acceptions       27         PS32™ Instruction Set       28         oprocessor 0       30         rstem Bus (SBUS)       41         TAG       42 |

| 3.0  | 3.1 SE                                                                        | y Controllers43DRAM Memory Controller44atic Bus Controller53                                                                                                                                                                                                      |

| 4.0  | 4.1 PC<br>4.2 PC                                                              | Bus Controller         73           CI Memory Map         73           CI Arbiter         81           plementation Specifics         81                                                                                                                          |

| 5.0  | 5.1 DN<br>5.2 Us                                                              | ontroller87MA Configuration Registers87sing GPIO as External DMA Requests (DMA_REQn)92ogramming Considerations93                                                                                                                                                  |

| 6.0  | 6.1 Int<br>6.2 Re<br>6.3 Ha                                                   | pt Controller95verrupt Controller Sources95egister Definitions97ardware Considerations100ogramming Considerations100                                                                                                                                              |

| Α | M | D | Л |

|---|---|---|---|

|---|---|---|---|

| 7.0  | Peripheral Devices                                                                | 101 |

|------|-----------------------------------------------------------------------------------|-----|

|      | 7.1 AC97 Controller                                                               | 102 |

|      | 7.2 USB Host Controller                                                           | 107 |

|      | 7.3 USB Device Controller                                                         | 109 |

|      | 7.4 Ethernet MAC Controller                                                       | 119 |

|      | 7.5 UART Interfaces                                                               | 140 |

|      | 7.6 Secondary General Purpose I/O                                                 | 149 |

| 8.0  | System Control                                                                    | 153 |

|      | 8.1 Clocks                                                                        |     |

|      | 8.2 Time of Year Clock and Real Time Clock                                        |     |

|      | 8.3 Primary General Purpose I/O and Pin Functionality                             |     |

|      | 8.4 Power Management                                                              |     |

| 9.0  | Power-up, Reset and Boot                                                          | 180 |

| 5.0  | •                                                                                 |     |

|      | 9.1 Power-up Sequence                                                             |     |

|      | 9.2 Reset                                                                         |     |

|      | 9.3 Boot                                                                          |     |

| 10.0 | EJTAG Implementation                                                              | 184 |

|      | 10.1 EJTAG Instructions                                                           |     |

|      | 10.2 Debug Exceptions                                                             |     |

|      | 10.3 Coprocessor 0 Registers                                                      |     |

|      | 10.4 EJTAG Memory Range                                                           | 188 |

| 11.0 | Signal Descriptions                                                               | 200 |

| 12 0 | Electrical and Thermal Specifications                                             | 216 |

| 12.0 | 12.1 Absolute Maximum Ratings                                                     |     |

|      | 12.1 Absolute Maximum Haungs                                                      |     |

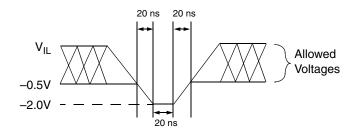

|      | 12.2 Ondershoot                                                                   |     |

|      | 12.4 Thermal Characteristics                                                      |     |

|      | 12.5 DC Parameters                                                                |     |

|      | 12.6 AC Parameters                                                                |     |

|      | 12.7 Power-up and Reset Timing                                                    |     |

|      | 12.8 Asynchronous Signals                                                         |     |

|      | 12.9 External Clock Specifications                                                |     |

|      | 12.10 Crystal Specifications                                                      |     |

|      | 12.11 System Design Considerations                                                |     |

| 12 0 | , ,                                                                               |     |

| 13.0 | Packaging, Pin Assignments, and Ordering Information         13.1       Packaging |     |

|      | 13.1 Packaging                                                                    |     |

|      | •                                                                                 |     |

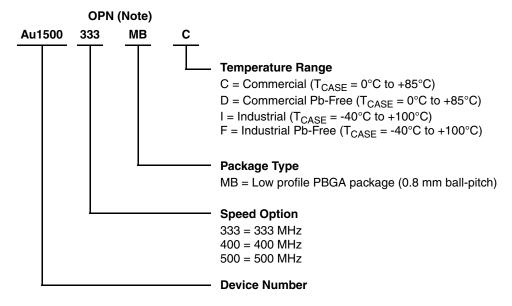

|      | 13.3 Ordering Information                                                         |     |

# List of Figures

| Figure 1-1.  | Block Diagram                                                  |      |

|--------------|----------------------------------------------------------------|------|

| Figure 2-1.  | Au1 Core Diagram                                               |      |

| Figure 2-2.  | Cache Organization                                             |      |

| Figure 2-3.  | Au1 Write Buffer                                               |      |

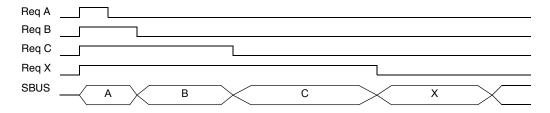

| Figure 2-4.  | SBUS Arbitration                                               |      |

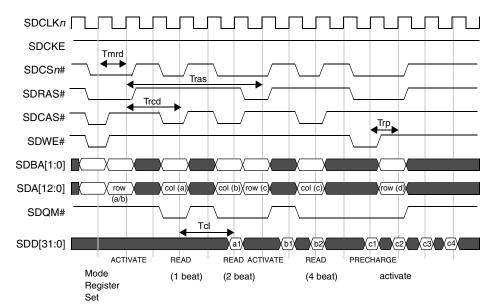

| Figure 3-1.  | SDRAM Typical Read Timing                                      |      |

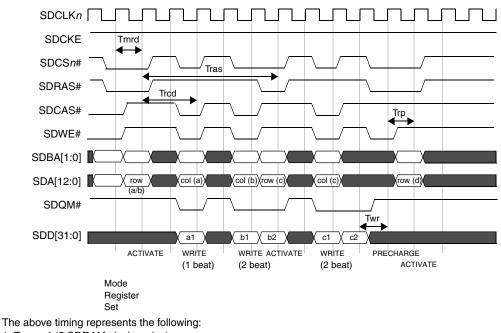

| Figure 3-2.  | SDRAM Typical Write Timing                                     |      |

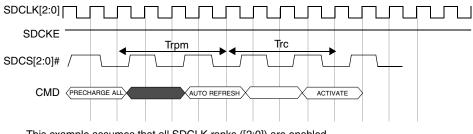

| Figure 3-3.  | SDRAM Refresh Timing                                           |      |

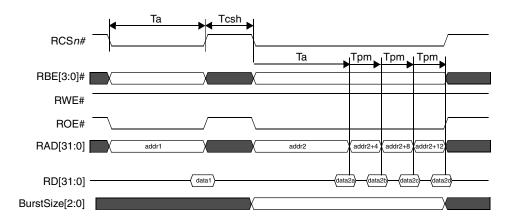

| Figure 3-4.  | Static Memory Read Timing (Single Read Followed by Burst)      |      |

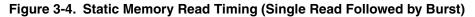

| Figure 3-5.  | Static Memory Read EWAIT# Timing                               |      |

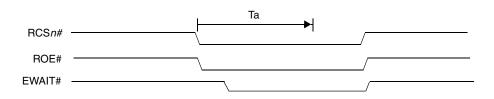

| Figure 3-6.  | Static Memory Write Timing                                     |      |

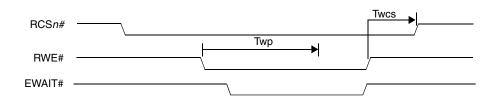

| Figure 3-7.  | Static Memory Write EWAIT# Timing                              |      |

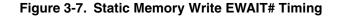

| Figure 3-8.  | One Card PCMCIA Interface                                      |      |

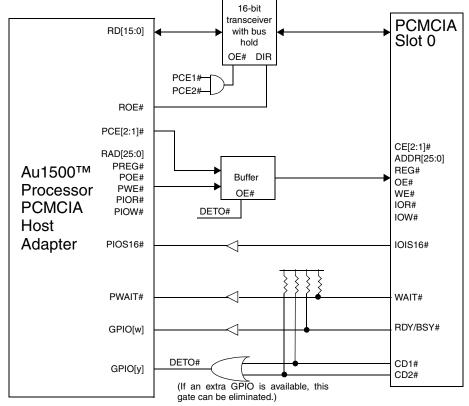

| Figure 3-9.  | Two Card PCMCIA Interface                                      |      |

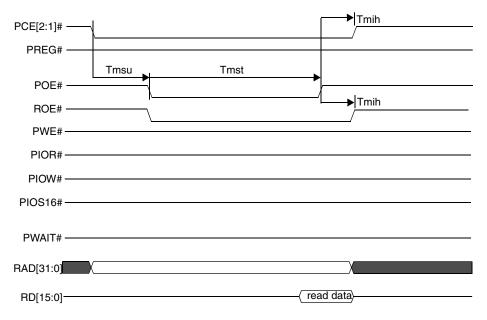

| Figure 3-10. | PCMCIA Memory Read Timing                                      |      |

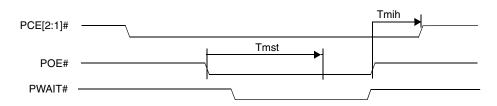

| Figure 3-11. | PCMCIA Memory Read PWAIT# Timing                               | . 65 |

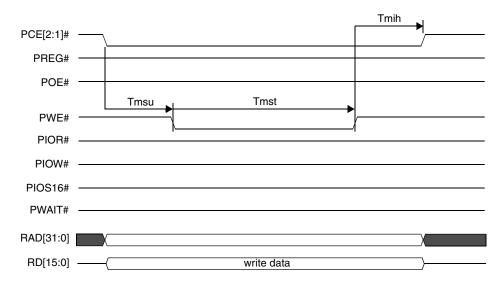

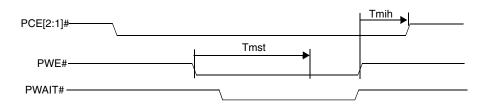

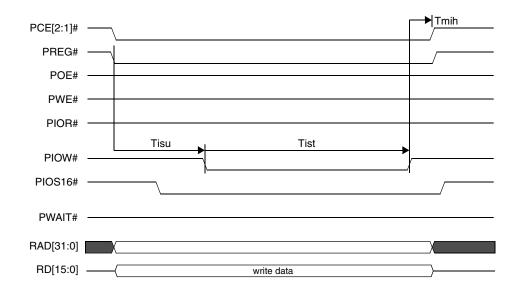

| Figure 3-12. | PCMCIA Memory Write Timing                                     |      |

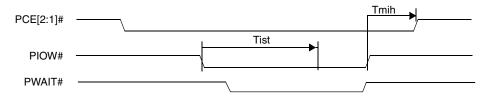

| Figure 3-13. | PCMCIA Memory Write PWAIT# Timing                              |      |

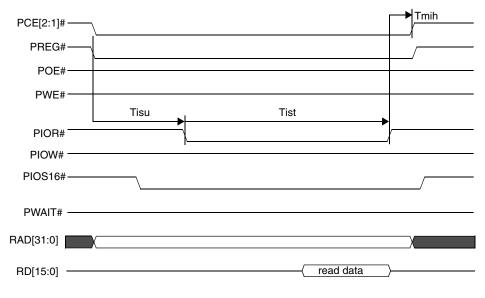

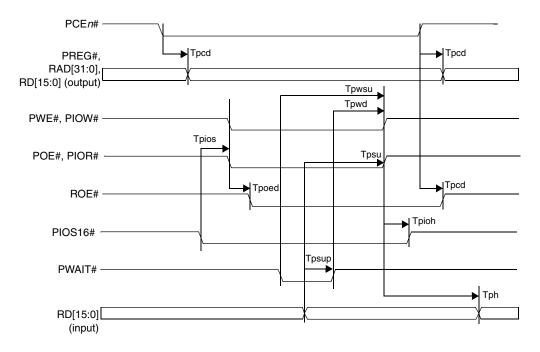

| Figure 3-14. | PCMCIA I/O Read Timing                                         |      |

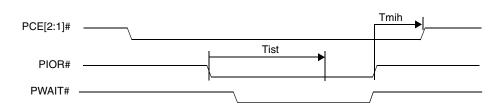

| Figure 3-15. | PCMCIA I/O Read PWAIT# Timing                                  | . 67 |

| Figure 3-16. | PCMCIA I/O Write Timing                                        |      |

| Figure 3-17. | PCMCIA I/O Write PWAIT# Timing                                 | . 67 |

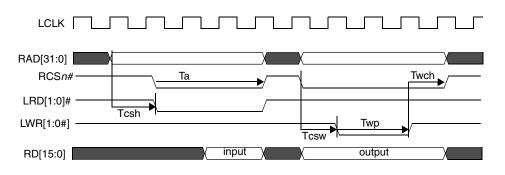

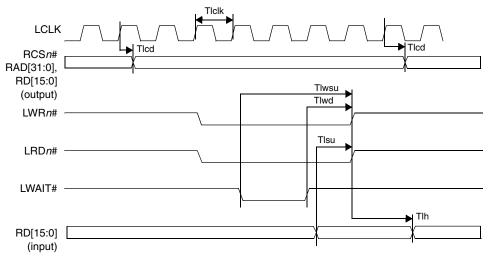

| Figure 3-18. | LCD Controller Timing                                          | . 69 |

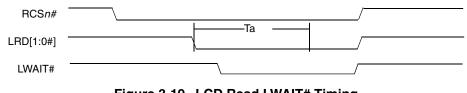

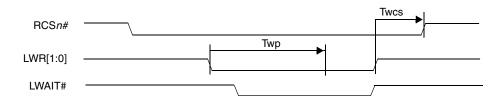

| Figure 3-19. | LCD Read LWAIT# Timing                                         | . 69 |

| Figure 3-20. | LCD Write LWAIT# Timing                                        | . 69 |

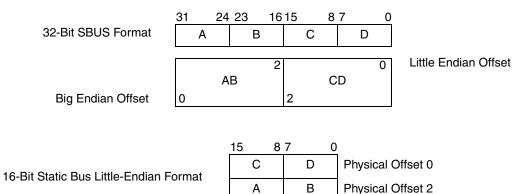

| Figure 3-21. | 16-Bit Chip Select Little-Endian Data Format (Default)         | . 70 |

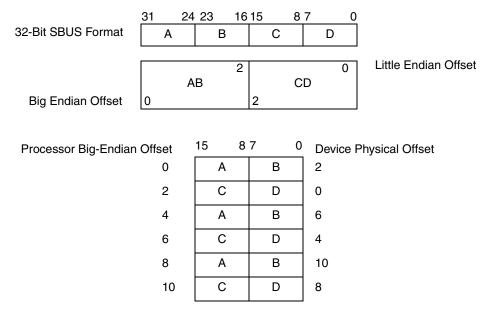

| Figure 3-22. | Big-Endian Au1 Core and Little-Endian 16-Bit Chip Select       | .71  |

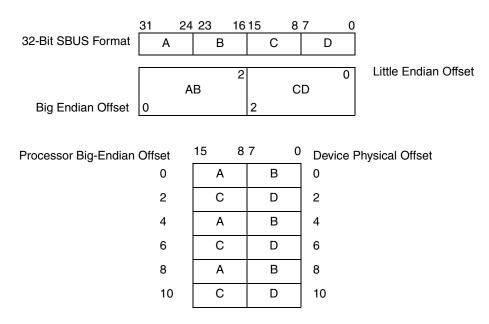

| Figure 3-23. | Big-Endian Au1 Core and Big-Endian 16-Bit Chip Select          | . 72 |

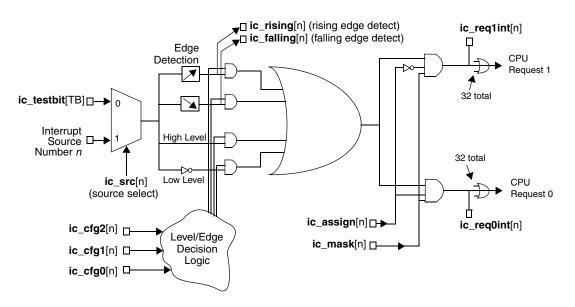

| Figure 6-1.  | Interrupt Controller Logic                                     | . 97 |

| Figure 7-1.  | Endpoint Configuration Data Structure                          | 111  |

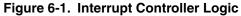

| Figure 7-2.  | Logic for Interrupt Source Number 31 on Interrupt Controller 1 | 151  |

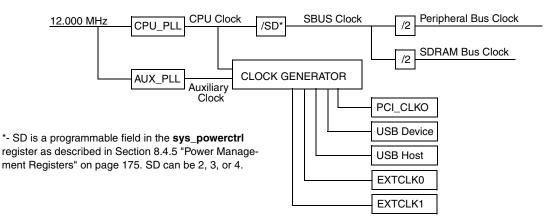

| Figure 8-1.  | Clocking Topology                                              |      |

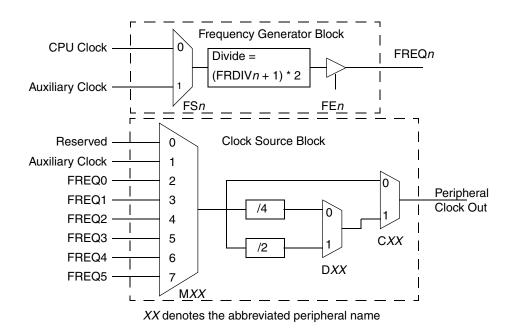

| Figure 8-2.  | Frequency Generator and Clock Source Block Diagram             | 156  |

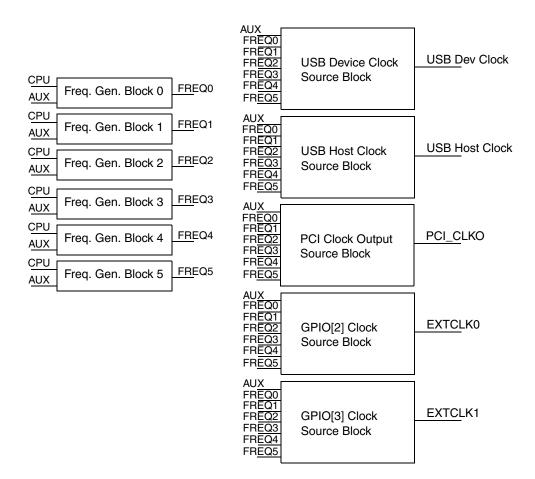

| Figure 8-3.  | Frequency Generator and Clock Source Mapping                   | 156  |

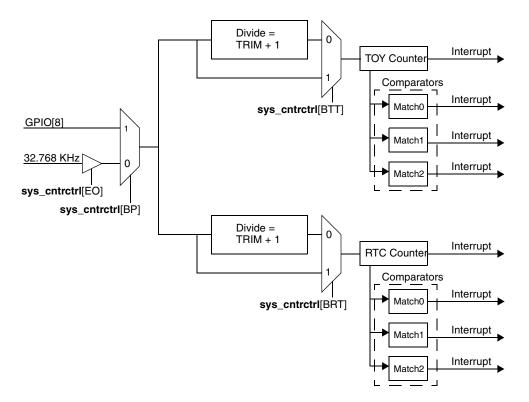

| Figure 8-4.  | TOY and RTC Block Diagram                                      | 163  |

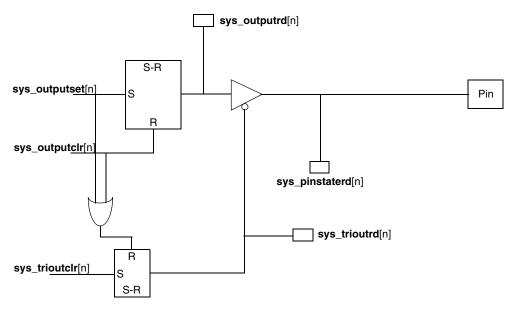

| Figure 8-5.  | GPIO Logic Diagram                                             | 169  |

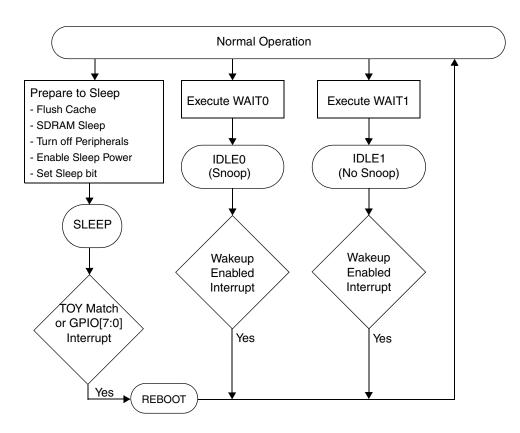

| Figure 8-6.  | Sleep and Idle Flow Diagram                                    | 172  |

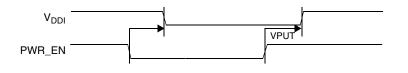

| Figure 8-7.  | Sleep Sequence                                                 | 174  |

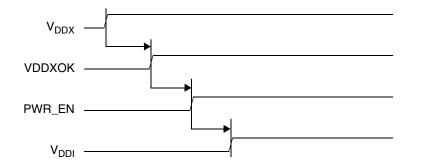

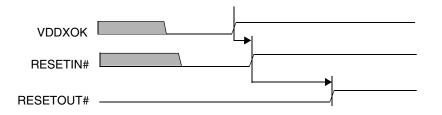

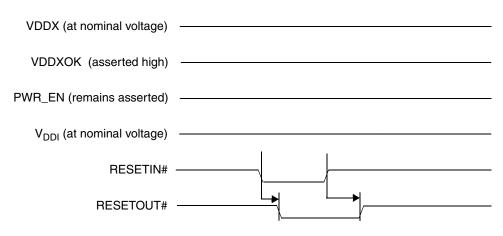

| Figure 9-1.  | Power-up Sequence                                              | 180  |

| Figure 9-2.  | Hardware Reset Sequence                                        |      |

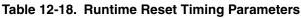

| Figure 9-3.  | Runtime Reset Sequence                                         |      |

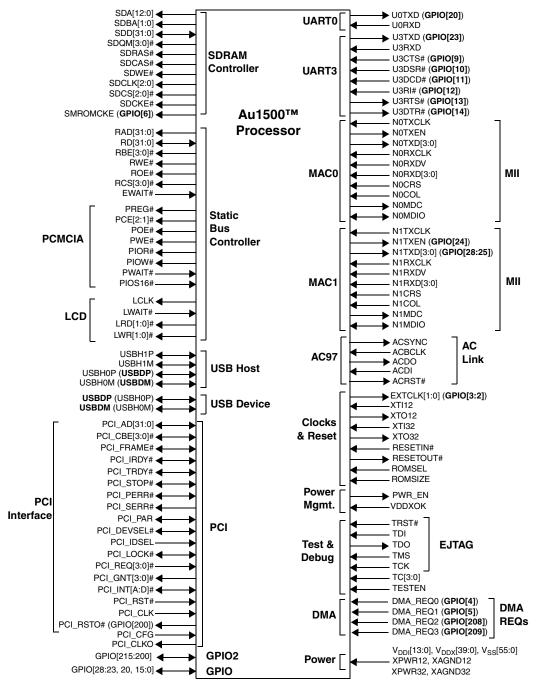

| Figure 11-1. | External Signals                                               |      |

| Figure 12-1. | Voltage Undershoot Tolerances for Input and I/O Pins           |      |

| Figure 12-2. | Voltage Overshoot Tolerances for Input and I/O Pins            |      |

| Figure 12-3. | SDRĂM Timing                                                   |      |

| -            | -                                                              |      |

| Figure 12-4.  | Static RAM, I/O Device and Flash Timing | 222   |

|---------------|-----------------------------------------|-------|

| Figure 12-5.  | PCMCIA Host Adapter Timing              |       |

| •             |                                         |       |

| Figure 12-6.  | LCD Interface Timing                    | . 224 |

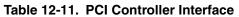

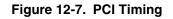

| Figure 12-7.  | PCI Timing                              | . 225 |

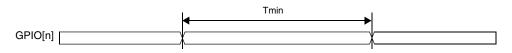

| Figure 12-8.  | GPIO Interrupt Timing                   | . 226 |

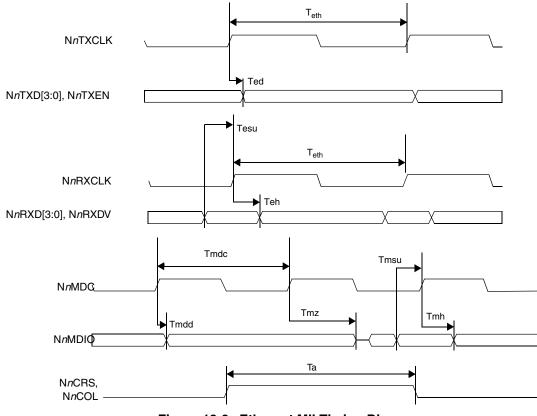

| Figure 12-9.  | Ethernet MII Timing Diagram             | . 227 |

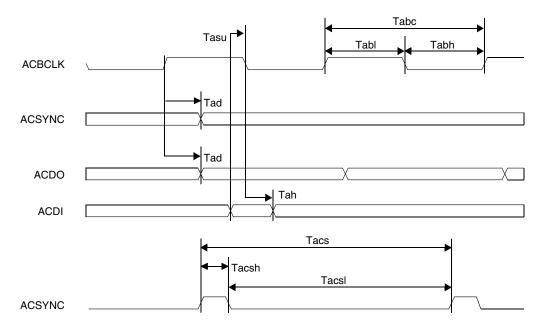

| Figure 12-10. | AC-Link Timing Diagram                  | . 228 |

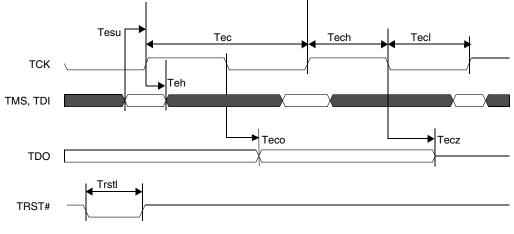

| Figure 12-11. | EJTAG Timing Diagram                    | . 229 |

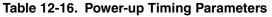

| Figure 12-12. | Power-up Sequence                       | . 230 |

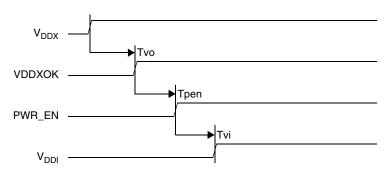

| Figure 12-13. | Hardware Reset Sequence                 | . 231 |

| Figure 12-14. | Runtime Reset Sequence                  | . 232 |

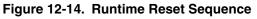

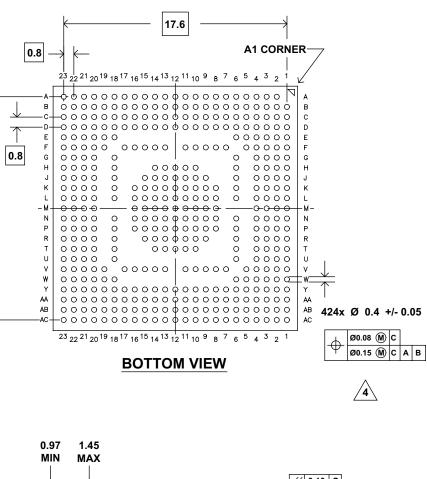

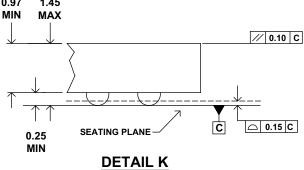

| Figure 13-1.  | Package Dimensions                      | . 238 |

| Figure 13-2.  | Connection Diagram—Top View             |       |

| Figure 13-3.  | OPN Example                             | . 254 |

# List of Tables

| Table 2-1.  | Cache Line Allocation Behavior                              | . 18 |

|-------------|-------------------------------------------------------------|------|

| Table 2-2.  | Cache Operations                                            |      |

| Table 2-3.  | Cache Coherency Attributes (CCA)                            |      |

| Table 2-4.  | Values for Page Size and PageMask Register                  |      |

| Table 2-5.  | Cause[ExcCode] Encodings                                    |      |

| Table 2-6.  | CPU Interrupt Sources                                       |      |

| Table 2-7.  | Coprocessor 0 Register Definitions                          |      |

| Table 3-1.  | Memory Controller Block Base Address                        |      |

| Table 3-2.  | SDRAM Configuration Registers                               |      |

| Table 3-3.  | SDRAM Signals                                               |      |

| Table 3-4.  | Static Bus Controller Configuration Registers               |      |

| Table 3-5.  | Device Type Encoding                                        |      |

| Table 3-6.  | Burst Size Mapping                                          |      |

| Table 3-7.  | Actual Number of Clocks for Timing Parameters (Except Tcsh) |      |

| Table 3-8.  | Actual Number of Clocks for Tcsh                            |      |

| Table 3-9.  | Static RAM, I/O Device and Flash Control Signals            | . 60 |

| Table 3-10. | PCMCIA Memory Mapping                                       | . 62 |

| Table 3-11. | PCMCIA Interface Signals                                    | . 62 |

| Table 3-12. | LCD Controller Interface Signals                            | . 68 |

| Table 4-1.  | PCI Memory Map                                              |      |

| Table 4-2.  | PCI Bus Controller Configuration Registers                  | .74  |

| Table 4-3.  | PCI Arbiter Priority Configuration                          |      |

| Table 4-4.  | PCI Error Conditions on pci_config[27:24]                   | . 83 |

| Table 4-5.  | Data Bus Swapping                                           | . 84 |

| Table 4-6.  | Swapping Configurations                                     | . 84 |

| Table 4-7.  | Supported Endian/Swapping Modes                             | . 85 |

| Table 4-8.  | PCI Bus Support Signals                                     |      |

| Table 5-1.  | DMA Channel Base Addresses                                  | . 87 |

| Table 5-2.  | DMA Channel Configuration Registers                         |      |

| Table 5-3.  | Peripheral Addresses and Selectors                          |      |

| Table 6-1.  | Interrupt Controller Connections to the CPU                 | . 95 |

| Table 6-2.  | Interrupt Sources                                           |      |

| Table 6-3.  | Interrupt Controller Base Addresses                         | . 97 |

| Table 6-4.  | Interrupt Controller Registers                              |      |

| Table 6-5.  | Interrupt Configuration Register Function                   |      |

| Table 7-1.  | AC97 Base Address                                           | 102  |

| Table 7-2.  | AC97 Registers                                              | 102  |

| Table 7-3.  | AC-Link Signals                                             |      |

| Table 7-4.  | USB Host Base Address                                       | 107  |

| Table 7-5.  | USB Host Signals                                            |      |

| Table 7-6.  | USB Device Base Address                                     | 109  |

| Table 7-7.  | USB Device Register Block                                   |      |

| Table 7-8.  | Endpoint Configuration Field Descriptions                   |      |

| Table 7-9.  | Example Endpoint Configuration Data Block                   |      |

| Table 7-10. | USB Device Signals                                          | 118  |

| Table 7-11.                | Ethernet Base Addresses                                                                   | 120 |

|----------------------------|-------------------------------------------------------------------------------------------|-----|

| Table 7-12.                | MAC Register Descriptions                                                                 |     |

| Table 7-13.                | MAC DMA Entries                                                                           |     |

| Table 7-14.                | MAC DMA Receive Entry Registers                                                           |     |

| Table 7-15.                | MAC DMA Transmit Entry Registers                                                          |     |

| Table 7-16.                | MAC DMA Block Indexed Address Bit Definitions                                             |     |

| Table 7-17.                | Ethernet Signals                                                                          |     |

| Table 7-18.                | UART Register Base Addresses                                                              |     |

| Table 7-19.                | UART Registers                                                                            |     |

| Table 7-20.                | Interrupt Cause Encoding                                                                  |     |

| Table 7-21.                |                                                                                           |     |

| Table 7-22.                | GPIO2 Register Base Addresses                                                             |     |

| Table 7-23.                | GPIO2 Registers                                                                           |     |

| Table 8-1.                 | System Control Block Base Address                                                         |     |

| Table 8-2.                 | Clock Generation Registers                                                                |     |

| Table 8-3.                 | Clock Mux Input Select Values                                                             |     |

| Table 8-4.                 | Programmable Counter Registers                                                            |     |

| Table 8-5.                 | GPIO Control Registers                                                                    |     |

| Table 8-6.                 | Peripheral Power Management                                                               |     |

| Table 8-7.                 | Power Management Registers                                                                |     |

| Table 9-1.                 | ROMSEL and ROMSIZE Boot Device                                                            |     |

| Table 10-1.                | Coprocessor 0 Registers for EJTAG                                                         |     |

| Table 10-2.                | EJTAG Memory Mapped Registers at 0xFF300000                                               |     |

| Table 10-3.                | EJTAG Instruction Register Values                                                         |     |

| Table 10-4.                | EJTAG Signals                                                                             |     |

| Table 11-1.                | Signal Type Abbreviations for Table 11-3                                                  |     |

| Table 11-2.                | Signal State Abbreviations for Table 11-3                                                 |     |

| Table 11-3.                | Signal Description                                                                        |     |

| Table 12-1.                | Absolute Maximum Ratings                                                                  |     |

| Table 12-2.                | Thermal Characteristics with Changing Air Flow Conditions                                 |     |

| Table 12-3.                | DC Parameters                                                                             |     |

| Table 12-4.                | Voltage and Power Parameters for 333 MHz Part                                             |     |

| Table 12-5.                | Voltage and Power Parameters for 400 MHz Part                                             |     |

| Table 12-6.                | Voltage and Power Parameters for 500 MHz Part                                             |     |

| Table 12-7.                | SDRAM Controller Interface                                                                |     |

| Table 12-8.                | Static RAM, I/O Device and Flash Timing                                                   |     |

| Table 12-9.                | PCMCIA Timing                                                                             |     |

| Table 12-10.               | LCD Timing                                                                                |     |

| Table 12-11.               | PCI Controller Interface                                                                  |     |

| Table 12-12.               | GPIO Timing for Interrupts                                                                |     |

| Table 12-13.               | Ethernet MII Timing                                                                       |     |

| Table 12-14.               | AC-Link Interface Timing                                                                  |     |

| Table 12-15.               | EJTAG Interface Timing                                                                    |     |

| Table 12-16.               | Power-up Timing Parameters                                                                |     |

| Table 12-17.               | Hardware Reset Timing Parameters                                                          |     |

| Table 12-18.               | Runtime Reset Timing Parameters                                                           |     |

| Table 12-19.               | External Clock EXTCLK[1:0] Specifications                                                 |     |

| Table 12-20.               | 12 MHz Crystal Specification                                                              |     |

| Table 12-21.               | 32.768 KHz Crystal Specification                                                          |     |

| Table 13-1.<br>Table 13-2. | Pin Assignment — Sorted by Pin Number                                                     |     |

| Table 13-2.<br>Table 13-3. | Pin Assignment — Sorted Alphabetically by Default Signal                                  |     |

| Table 13-3.<br>Table 13-4. | Pin Assignment — Alternate Signals Sorted Alphabetically                                  |     |

| Table 13-4.<br>Table A-1.  | Valid OPN Combinations<br>Basic Au1500 <sup>™</sup> Processor Physical Address Memory Map |     |

| Table A-1.<br>Table A-2.   | System Bus Devices Physical Address Memory Map                                            |     |

|                            | Cystem Dus Devices i hysical Address Memory Map                                           | 200 |

| List of Tables | 30361D                                             |  |

|----------------|----------------------------------------------------|--|

| Table A-3.     | Peripheral Bus Devices Physical Address Memory Map |  |

| Table A-4.     | Device Memory Map                                  |  |

| Table A-5.     | Revision History                                   |  |

| Table A-6.     | Edits to Current Revision                          |  |

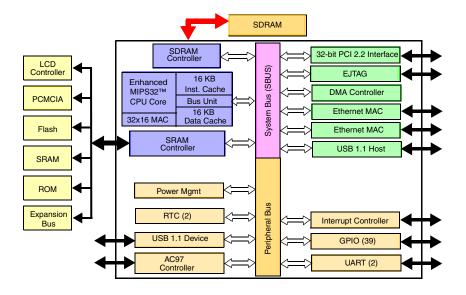

The AMD Alchemy<sup>™</sup> Au1500<sup>™</sup> processor is a high-performance, low-power, high integration system-on-a-chip (SOC) designed for use in the Internet edge device market. These devices are customer premise equipment products, including both wireless and wired Internet access devices and portable compute devices, as well as Internet infrastructure products such as routers and line cards. Devices based on the Au1500 are capable of processing high performance digital video and data streams in either battery or line-powered environments. The Au1500 processor contains a PCI controller, providing a flexible interface to external peripherals.

## 1.1 Product Description

The Au1500 processor is a complete SOC based on the MIPS32<sup>™</sup> instruction set. Designed for maximum performance at low power, the processor runs up to 500 MHz. Power dissipation is less than 700 mW for the 400 MHz version. Highly integrated with on-chip memory controllers and Internet access peripherals, the Au1500 processor runs a variety of operating systems, including Windows® CE, Linux, and VxWorks. Moreover, the integration of peripherals with the unique, high performance, MIPS-compatible core provides low system cost, small form factor, low system power requirement, simple designs at multiple performance points and thus, short design cycles.

Figure 1-1. Block Diagram

# 1.2 Features

#### High Speed MIPS CPU Core

- 333, 400, or 500 MHz

- MIPS32 instruction set 32-bit architecture

- 16 KB instruction and 16 KB data caches

- High speed multiply-accumulate (MAC) and divide unit

- 1.5V core @ 333 MHz and 400 MHz, 1.8V core @ 500 MHz

- 3.3V I/O

- Pipeline:

- Scalar 5-stage pipeline

- Load/store adder in I-stage (instr decode)

- Scalar branch techniques optimized: Pipelined register file access in fetch stage

- Zero penalty branch

- Multiply-Accumulate (MAC) and Divide Unit:

- Max issue rate of one 32x16 MAC per clock

- Max issue rate of one 32x32 MAC per every other clock

- Operates in parallel to CPU pipeline

- Executes all integer multiply and divide instructions

- 32 x 16-bit MAC hardware

#### **Highly-Integrated System Peripherals**

- GPIOs (39 total, 22 dedicated for system use)

- Two 10/100 Ethernet MAC controllers

- USB 1.1 device and host controllers

- Two UARTs

- AC97 controller

- PCI interface

- PCMCIA interface

#### High-Bandwidth Memory Buses

- 100 MHz SDRAM controller (@400 MHz)

- SRAM/Flash EPROM controller

#### Caches

- 16 KB non-blocking data cache

- 16 KB instruction cache

- Instruction and data caches are 4-way set associative

- Write-back with read-allocate

- Cache Management Features:

- Programmable allocation policy

- Line locking

- Prefetch instructions (instruction and data)

- High speed access to on-chip buses

#### MMU

- Instruction and data watch registers for software breakpoints

- Separate interrupt exception vector

- TLB Features:

- 32 dual-entry fully-associative

- Variable page sizes: 4 KB to 16 MB

- 4-entry ITB

#### Low System Power

- Core / Power:

- 333 MHz / 400 mW

- 400 MHz/ 700 mW

- 500 MHz/ 1.2 W

- Power-Saving Modes:

- Idle

- Sleep

- Pseudo-static design to 0 Hz

#### Package

■ 424 BGA (Ball Grid Array), 19x19 mm

#### **Operating System Support**

- Microsoft<sup>®</sup> Windows<sup>®</sup> CE

- Linux

- VxWorks

#### **Development Tool Support**

- Complete MIPS32<sup>TM</sup> Compatible Tool Set

- Numerous 3rd-Party Compilers, Assemblers and Debuggers

30361D

The Au1500 CPU core is a unique implementation of the MIPS32 instruction set architecture (ISA) designed for high frequency and low power. This chapter provides information on the implementation details of this MIPS32 compliant core.

The full description of the MIPS32 architecture is provided in the "MIPS32<sup>TM</sup> Architecture For Programmers" documentation, available from MIPS Technologies, Inc. The information contained in this chapter supplements the MIPS32 architecture documentation.

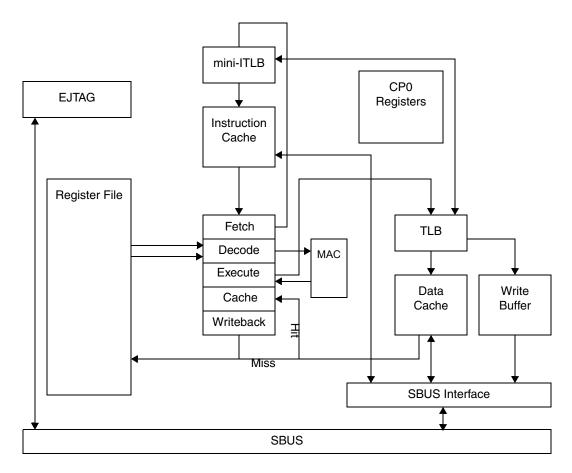

# 2.1 Core

The Au1500 CPU core (Au1) is a high performance, low power implementation of the MIPS32 architecture. Figure 2-1 shows a block diagram of the core.

Figure 2-1. Au1 Core Diagram

The Au1 core contains a five-stage pipeline. All stages complete in a single cycle when data is present. All pipeline hazards and dependencies are enforced by hardware interlocks so that any sequence of instructions is guaranteed to execute correctly. Therefore, it is not necessary to pad legacy MIPS hazards (such as load delay slots and coprocessor accesses) with NOPs.

The general purpose register file has two read ports and one write port. The write port is shared with data cache loads and the pipeline Writeback stage.

#### 2.1.1 Fetch Stage

The Fetch stage retrieves the next instruction from the instruction cache, where it is passed to the Decode stage. If the instruction is not present in the instruction cache, then the fetch address is forwarded to the virtual memory unit in order to fulfill the request. Instruction fetch stalls until the next instruction is available.

#### 2.1.2 Decode Stage

The Decode stage prepares the pipeline for executing the instruction. In the Decode stage, the following occur in parallel:

- The instruction is decoded.

- Control for the instruction is generated.

- Register data is read.

- The branch target address is generated.

- The load/store address is generated.

Instructions stall in the Decode stage if dependent data or resources are not yet available. At the end of the Decode stage a new program counter value is sent to the Fetch stage for the next instruction fetch cycle.

#### 2.1.3 Execute Stage

In the Execute stage, instructions that do not access memory are processed in hardware (shifters, adders, logical, comparators, etc.). Most instructions complete in a single cycle, but a few require multiple cycles (CLO, CLZ, MUL).

The virtual address calculation begins in the Decode stage so that physical address calculation can complete in the Execute stage, in time to initiate the access to the data cache in the Execute stage. If the physical address misses in the TLB, a TLB exception is posted.

Multiplies and divides are forwarded to the Multiply Accumulate unit. These instructions require multiple cycles to execute and operate mostly independent of the main five-stage pipeline.

All exception conditions (arithmetic, TLB, interrupt, etc.) are posted by the end of the Execute stage so that exceptions can be signalled in the Cache stage.

## 2.1.4 Cache Stage

In the Cache stage, load and store accesses complete.

Loads that hit in the data cache obtain the data in the Cache stage. If a load misses in the data cache, or is to a non-cacheable location, then the request is sent to the System Bus (SBUS) to be fulfilled. Load data is forwarded to dependent instructions in the pipeline.

Stores that hit in the data cache are written into the cache array. If a store misses in the data cache, or is to a non-cacheable location, then the store is sent to the write buffer.

If any exceptions are posted, an exception is signaled and the Au1 core is directed to fetch instructions at the appropriate exception vector address.

#### 2.1.5 Writeback Stage

In the Writeback stage, results are posted to the general purpose register file, and forwarded to other stages as needed.

#### 2.1.6 Multiply Accumulate Unit

The Multiply Accumulate unit (MAC) executes all multiply and divide instructions. The MAC is composed of a 32x16 bit pipelined array multiplier that supports early out detection, divide block, and the HI and LO registers used in calculations.

The MAC operates in parallel with the main five-stage pipeline. Instructions in the main pipeline that do not have dependencies on the MAC calculations execute simultaneously with instructions in the MAC unit.

A multiply calculation of 16x16 or 32x16 bits can complete in one cycle. The 32x16 bit multiply must have the signextended 16-bit value in register operand rt of the instruction.

32x32 bit multiplies may be started every other CPU cycle. The 32x32 multiplies will complete in two cycles if the results are written to the general purpose registers.

If the results are written to the HI/LO registers then three cycles are required for 16x16 and 32x16 bit multiplies. 32x32 bit multiplies that use HI/LO will complete in four cycles.

Divide instructions complete in a maximum of 35 cycles.

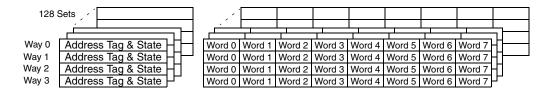

## 2.2 Caches

The Au1 core contains independent, on-chip 16KB instruction and data caches. As shown in Figure 2-2, each cache contains 128 sets and is four-way set associative with 32 bytes per way (cache line).

#### Figure 2-2. Cache Organization

A cache line is tagged with a 20-bit physical address, a lock bit, and a valid bit. Data cache lines also include coherency and dirty status bits. The physical address tag contains bits 31:12 of the physical address; as such, physical addresses in which bits 35:32 are non-zero must be mapped non-cacheable.

#### Cache Line State

| Bit | 31 3                 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|----------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|     | Physical Address Tag |    |    |    |    |    |    |    |    |    |    |    |    |    | D  | S  | L  | V  |    |    |    |   |   |   |   |   |   |   |   |   |   |

A cache line address is always 32-byte aligned. The cache is indexed with the lower, untranslated bits (bits 11:5) of the virtual address, allowing the virtual-to-physical address translation and the cache access to occur in parallel.

#### Cache Address Decode

| Bit 31 30 29 28 27 26 25 24 23 | 22 21 20 19 18 17 | 16 15 14 13 1 | 2 11 | 10 9 | 87      | 6 | 5 | 4 | 3    | 2    | 1    | 0 |

|--------------------------------|-------------------|---------------|------|------|---------|---|---|---|------|------|------|---|

| Virtual/Physical Address       |                   |               |      |      | t Selec | t |   |   | Byte | e Se | lect |   |

#### 2.2.1 Cache Line Replacement Policy

In general, the caches implement a least recently used (LRU) replacement policy. Each cache set maintains true LRU status bits (MRU, nMRU and LRU) to determine which cache line is selected for replacement. However, software can influence which cache line is replaced by marking memory pages as *streaming*, or by *locking* lines in the cache.

#### 2.2.2 Cache Line Locking Support

The **CACHE** instruction is used to lock individual lines in the cache. A locked line is not subject to replacement. All four lines in a set can not be locked at once; at least one line is always available for replacement. To *unlock* individual cache lines use the **CACHE** instruction with a 'hit invalidate' command opcode. See Section 2.2.5 "Cache Management" on page 19 for further discussion of the **CACHE** instruction.

### 2.2.3 Cache Streaming Support

Streaming is typically characterized as the processing of a large amount of transient instructions and/or data. In traditional cache implementations (without explicit support for streaming), transient instructions and/or data quickly displace useful, recently used items in the cache. This yields poor utilization of the cache and results in poor system performance.

The Au1 caches explicitly support streaming by placing instructions and/or data marked as streaming into way 0 of the cache. This method ensures that streaming does not purge the cache(s) of useful, recently used items, while permitting transient instructions and/or data to be cached. The CCA bits in the TLB entry indicate if a page contains streaming instructions and/or data. In addition, the **PREF** instruction is available to software to allow data to be placed in the data cache in advance of its use.

#### 2.2.4 Cache Line Allocation Behavior

When an instruction fetch misses in the instruction cache, or a data load misses in the data cache, a burst fill operation is performed to fill the cache line from memory. The cache line is selected by the following algorithm:

```

MRU is most recently used

nMRU is next most recently used

nLRU is next least recently used

LRU is least recently used

Cache Miss:

if (Streaming CCA=6) then Replacement = 0,

else if (LRU is !Valid or !Locked) then Replacement = LRU

else if (nLRU is !Valid or !Locked) then Replacement = nLRU

else if (nMRU is !Valid or !Locked) then Replacement = nMRU

else Replacement = MRU

Cache Hit:

new MRU = Hit Way

```

In short, the LRU selection is true LRU but with the following priorities:

- 1) Streaming: cache misses are forced to way 0.

- 2) Locking: cache misses follow policy above and set Lock bit.

- 3) Normal: true LRU replacement.

Table 2-1 summarizes cache line allocation for misses, as well as cache hit behavior. The table also shows how prefetching and cache locking affect the cache for hits and misses.

| Operation                                                            | Hit                                                        | Miss                                                                           |  |  |  |  |  |

|----------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| NORMAL                                                               |                                                            |                                                                                |  |  |  |  |  |

| Data load, Instruction fetch                                         | Read data from whichever cache line contains the address.  | Allocate and fill cache line; clear Lock bit; return read data.                |  |  |  |  |  |

| Data store                                                           | Write data to whichever cache line contains the address.   | Send to the write buffer.                                                      |  |  |  |  |  |

| STREAMING (CCA=6)                                                    |                                                            |                                                                                |  |  |  |  |  |

| Data load, Instruction fetch                                         | Read data from whichever cache line contains the address.  | Allocate and fill cache line in Way 0;<br>maintain Lock bit; return read data. |  |  |  |  |  |

| Data store                                                           | Write data to whichever cache line contains the address.   | Send to the write buffer.                                                      |  |  |  |  |  |

| PREF (data prefetch instruction with 0x4 hint)                       | No action taken—data remains in cur-<br>rent cache line.   | Allocate and fill cache line in Way 0; maintain Lock bit.                      |  |  |  |  |  |

| LOCKING                                                              |                                                            |                                                                                |  |  |  |  |  |

| CACHE 0x1D/0x1C (cache manage-<br>ment instruction with Lock opcode) | Set Lock bit in whichever cache line contains the address. | Allocate and fill cache line; set Lock bit.                                    |  |  |  |  |  |

| Table 2-1. Ca | ache Line Allocatio | n Behavior |

|---------------|---------------------|------------|

|---------------|---------------------|------------|

#### 2.2.5 Cache Management

The caches are managed with the **CACHE** instruction. The effect of the **CACHE** instruction is immediately visible to subsequent data accesses. Table 2-2 shows the cache operations, including the opcode to direct the operation to either the instruction cache or data cache. (An "n/a" indicates that the operation is not applicable.)

| Operation                    | CACHE[2018]<br>Encoding | Opcode for<br>Instruction Cache | Opcode for<br>Data Cache |

|------------------------------|-------------------------|---------------------------------|--------------------------|

| Index Invalidate             | 000                     | 0x00                            | 0x01 (with writeback)    |

| Index Load Tag               | 001                     | 0x04                            | 0x05                     |

| Index Store Tag              | 010                     | 0x08                            | 0x09                     |

| Hit Invalidate               | 100                     | 0x10                            | 0x11                     |

| Fill                         | 101                     | 0x14                            | N/A                      |

| Hit Writeback and Invalidate | 101                     | N/A                             | 0x15                     |

| Hit Writeback                | 110                     | N/A                             | 0x19                     |

| Fetch and Lock               | 111                     | 0x1C                            | 0x1D                     |

| Table 2-2. Cache Operations | Table 2 | 2-2. Ca | che Op | perations |

|-----------------------------|---------|---------|--------|-----------|

|-----------------------------|---------|---------|--------|-----------|

These cache operations permit initialization, locking/unlocking and management of the caches.

#### 2.2.6 Cache Coherency Attributes (CCA)

The cache coherency attributes (CCA) field in Config0[K0] and in the TLB determine the cache-ability of accesses to memory. Cached accesses (except CCA = 4) are performed critical-word-first to improve performance. The Au1 implements the following:

| CCA  | CCA<br>(3 Bits) | Description                                                                                                                                                               |

|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0, 1 | 00x             | Reserved (undefined).                                                                                                                                                     |

| 2    | 010             | Uncached, non-mergeable, non-gatherable. Required by the MIPS32 architecture. In addition, data is not merged within the write buffer to achieve a truly uncached effect. |

| 3    | 011             | Cached, mergeable, gatherable.                                                                                                                                            |

| 4    | 100             | Cached, mergeable, gatherable (word 0 first). Word 0 is always accessed first; that is, the cache line is accessed in word order (word 0, 17).                            |

| 5    | 101             | Cached, mergeable, gatherable.                                                                                                                                            |

| 6    | 110             | Cached, mergeable, gatherable, streaming. Instructions and/or data are placed into way 0.                                                                                 |

| 7    | 111             | Uncached, mergeable, gatherable. Even though data is not cached, data stores sent to the write buffer are subject to merging and gathering in the write buffer.           |

Table 2-3. Cache Coherency Attributes (CCA)

#### 2.2.7 Instruction Cache

The instruction cache is a 16 KB, four-way set associative cache. The instruction cache services instruction fetch requests from the Fetch stage of the pipeline.

An instruction cache line state consists of a 20-bit physical address tag, a lock bit (L) and a valid bit (V).

#### Instruction Cache line state

| Bit 31 30 29 28 27 26 2 | 5 24 23 22 21   | 20 19  | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------------|-----------------|--------|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|                         | Physical Addres | ss Tag |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   | L | V |

#### 2.2.7.1 Instruction Cache Initialization and Invalidation

Out of reset, all instruction cache lines are invalidated; thus the instruction cache is ready for use.

To invalidate the instruction cache in software, a loop of index invalidate **CACHE** instructions for each of the lines in the cache invalidates the cache.

```

li t0,(16*1024) # Cache size

li t1,32 # Line size

li t2,0x80000000 # First KSEG0 address

addu t3,t0,t2 # terminate address of loop

loop:

cache 0,0(t2) # Icache indexed invalidate tag

addu t2,t1 # compute next address

bne t2,t3,loop

nop

```

#### 2.2.7.2 Instruction Cache Line Fills

If an instruction fetch address hits in the instruction cache, the instruction word is returned to the Fetch stage. If the fetch address misses in the cache, and the address is cacheable, then the instruction cache performs a burst transfer from the memory subsystem to fill a cache line, and returns the instruction word to the Fetch stage.

The instruction cache line is selected by the replacement policy described in Section 2.2.1 "Cache Line Replacement Policy" on page 17.

#### 2.2.7.3 Instruction Cache Coherency

The instruction cache does not maintain coherency with the data cache. Coherency between the instruction cache and the data cache is the responsibility of software. However, the data cache snoops during instruction cache line fills.

Maintaining coherency is important when loading programs into memory, creating exception vector tables, or for self-modifying code. In these circumstances, memory is updated with new instructions using store instructions which places the new instructions in the data cache, but not in the instruction cache (thus the instruction cache may contain old instructions).

To maintain coherency, software must use the **CACHE** instruction to invalidate the modified range of program addresses in the instruction cache. Because the data cache snoops during instruction cache line fills, it is not necessary to writeback the data cache prior to invalidating the instruction cache. An instruction fetch to the newly loaded/modified program correctly fetches the new instructions.

#### 2.2.7.4 Instruction Cache Control

The cache-ability of instructions is controlled by three mechanisms:

- · Config0[K0] field

- The CCA bits in the TLB

- The CACHE instruction

The Config0[K0] field contains a cache coherency attribute (CCA) setting to control the cache-ability of KSEG0 region. At reset, this field defaults to CCA=3 (cacheable).

The CCA bits in the TLB entry control the cache-ability of the KUSEG, KSEG2, and KSEG3 regions. Each TLB entry specifies a CCA setting for the pages mapped by the TLB.

The **CACHE** instruction manages the caches, including the ability to lock lines in the cache. Valid instruction cache operations are the following:

- Index Invalidate

- Index Load Tag

- Index Store Tag

- Hit Invalidate

- Fill

- · Fetch and Lock

The effect of the **CACHE** instruction is visible to subsequent instructions not already in the pipeline. Instructions already in the fetch and decode stages of the pipeline are not affected by a cache operation on the instruction cache.

#### 2.2.8 Data Cache

The data cache is a 16 KB four-way set associative write-back cache. Data cache accesses are distributed across the Execute and Cache pipeline stages.

A data cache line state consists the 20-bit physical address tag, a dirty bit (D), a coherency bit (S), a lock bit (L) and a valid bit (V).

#### Data cache line state

| Bit 31 30 29 28 27 26 25 | 24 23 22 21 20 19 18 17 16 15 | 5 14 13 12 1 <sup>-</sup> | 1 10 9 | 87 | 65 | 4 | 3 2 | 1 | 0 |

|--------------------------|-------------------------------|---------------------------|--------|----|----|---|-----|---|---|

|                          | Physical Address Tag          |                           |        |    |    |   | DS  | L | V |

The data cache employs a read-allocate policy. Cache lines can be replaced on loads, but not on stores. Stores that miss in the data cache are forwarded to the write buffer.

The data cache supports hit-under-miss for one outstanding miss. If an access misses in the data cache, the data cache services the next access while the memory subsystem provides the data for the missed access. If the next access hits in the data cache, the data is available immediately; otherwise the cache stalls the access until the first access completes.

#### 2.2.8.1 Data Cache Initialization and Invalidation

Out of reset, all data cache lines are invalidated; thus the data cache is ready for use.

To invalidate the data cache in software, a loop of indexed writeback invalidate **CACHE** instructions for each of the lines in the cache invalidates the cache.

```

li t0,(16*1024) # Cache size

li t1,32 # Line size

li t2,0x80000000 # First KSEG0 address

addu t3,t0,t2 # terminate address of loop

loop:

cache 1,0(t2) # Dcache indexed invalidate tag

addu t2,t1 # compute next address

bne t2,t3,loop

nop

```

#### 2.2.8.2 Data Cache Line Fills

A data cache access is initiated in the Execute stage which allows a cache hit or miss indication and all exceptions to be signaled early in the Cache stage. If the data address hits in the data cache, the data is available in the Cache stage. If the data address misses in the data cache, and the address is cacheable, the data cache performs a burst fill to a cache line, forwarding the critical word to the Cache stage.

The data cache line is selected by the replacement policy described in Section 2.2.1 "Cache Line Replacement Policy" on page 17. If the line selected contains modified data (cache line is valid and has its dirty bit set by a store hit), then the cache line is moved to a cast-out buffer, the cache line is filled from memory and the load request fulfilled, and then the cast-out buffer is written to memory.

#### 2.2.8.3 Data Cache Coherency

The data cache snoops coherent SBUS transactions to maintain data coherency with other SBUS masters (i.e. DMA). If a coherent read transaction on the SBUS hits in the data cache, the data cache provides the data. If a coherent write transaction on the SBUS hits in the data cache, the data cache updates its internal array with the data. If a coherent transaction (read or write) misses in the data cache, the data cache array is unchanged by the transaction.

Loads and stores which hit in the data cache can bypass previous stores in cacheable regions. The read-allocate data cache policy forwards store-misses to the write buffer. Subsequent loads and stores which hit in the data cache, and to a different cache line address than store-misses, are fulfilled immediately (while store-misses may still be in the write buffer). However, if a load address hits in a cache-line address of an item in the write buffer, the load is stalled until the write buffer commits the corresponding store.

The data cache also maintains coherency with other caching masters. When a load is serviced from another caching master, both caching masters set the shared bit for the affected cache line. Then if a store occurs to a data cache line with the

shared bit set, the cache line address is broadcast on the SBUS to invalidate cache lines in other caching masters that contain the same address.

The data cache is single-ported; therefore transactions on the SBUS are prioritized over accesses by the core. However, the data cache design prevents the SBUS from saturating the data cache indefinitely, which ensures that the core can make forward progress.

When changing the CCA encoding in Config0[K0] or the TLB to a different CCA encoding, software must ensure that data integrity is not compromised by first pushing modified (dirty) data to memory within the page. This is especially important when changing from a coherent CCA encoding to a non-coherent CCA encoding.

#### 2.2.8.4 Data Cache Control

The cache-ability of data accesses is controlled by four mechanisms:

- Config0[K0] field

- The CCA bits in the TLB

- The CACHE instruction

- The PREF instruction

The Config0[K0] field contains a cache coherency attribute (CCA) setting to control the cache-ability of KSEG0 region. At reset, this field defaults to 011b, cacheable.

The CCA bits in the TLB entry control the cache-ability of the KUSEG, KSEG2, and KSEG3 regions. Each TLB entry specifies a CCA setting for the pages mapped by the TLB.

The **CACHE** instruction manages the caches; including the ability to lock lines in the cache. Valid data cache operations are:

- Index Writeback Invalidate

- Index Load Tag

- Index Store Tag

- Hit Invalidate (unlocks)

- Hit Writeback and Invalidate

- Hit Writeback

- Fetch and Lock

The effect of the CACHE instruction is immediately visible to subsequent data accesses.

The **PREF** instruction places data into the data cache. The following prefetch hints are implemented:

- 0x00 Normal load

- 0x04 Streaming load

The streaming load hint directs the data be placed into way 0 of the data cache (even if the line is locked), thus permitting transient data to be cached and non-transient data to remain in the cache for improved performance. Data cache streaming support combined with the **PREF** instruction enhances multimedia processing.

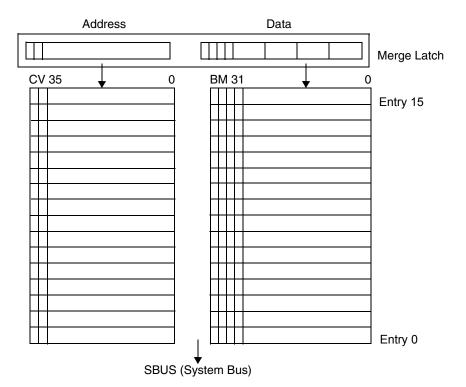

#### 2.3 Write Buffer

The Au1 write buffer is depicted in Figure 2-3. All non-cacheable processor stores and data cache store-misses (the data cache is a read-allocate policy) are routed through the write buffer.

Figure 2-3. Au1 Write Buffer

The write buffer is a 16-word deep first-in-first-out (FIFO) queue. All processor stores arrive first at the merge latch, where merging and gathering decisions are performed, and then travel through the queue. The write buffer arbitrates for the SBUS to perform consolidated transfers to the main memory.

A write buffer FIFO entry contains the address (word address), the data and associated byte masks (BM), and two control bits. The four BM bits indicate which bytes within the word contain valid data. The two control bits are the Valid bit which indicates if the entry is valid, and the Closed (C) bit. When a C bit is set, the write buffer initiates a request to the SBUS so that it can transfer data to memory. The circumstances for which the C bit is set are described below.

The write buffer is capable of variable-length burst writes to memory. The length can vary from one word to eight words, and is determined by the C bits in the write buffer. During each beat of the burst, the appropriate bytes to write are selected from the corresponding byte masks. As each entry is written to memory, it is popped from the FIFO, advancing each entry in the FIFO by one. In other words, entry 0 is always presented to the SBUS for writing.

When the write buffer has at least one empty entry, processor stores do not stall, thus improving processor performance.

The write buffer is disabled by setting Config0[WD] to 1. In this instance, all non-cacheable and data cache store-misses stall until the write completes. The remaining description of the write buffer operation assumes Config0[WD] is 0. Out of reset, Config0[WD] is 0.

#### 2.3.1 Merge Latch

All processor stores first arrive at the merge latch. Logic within the merge latch decides what action to take with the incoming data.

- 1) The incoming address is the *same word address* as the merge latch address. This case is for Merging, which occurs within the merge latch itself.

- 2) The incoming word address is *sequentially adjacent* to the merge latch word address (incoming address is merge latch address + 4). This case is for Gathering. The merge latch contents are propagated to the FIFO with the C bit cleared for this entry.

- 3) Neither 1 nor 2 is true. The merge latch contents are propagated to the FIFO with the C bit set for this entry.

If the merge latch contents are propagated to the FIFO, the incoming address and data are placed in the merge latch for future comparisons. Furthermore, if the incoming address is the last word address of the maximum burst line size (the least significant 5 bits are 0x1C), then the C bit is set.

#### 2.3.2 Write Buffer Merging

Write buffer merging combines stores destined for the *same word address*. Merging places the incoming data into the appropriate data byte(s) within the merge latch.

Write buffer merging is particularly useful for sequential, incremental address write operations, such as string operations. With write buffer merging, the writes are merged into 32-bit writes which reduces the number of accesses to the memory and increases the effective throughput to main memory.

This example demonstrates merging: these five byte writes occur in sequence:

0x00001000 = 0xAB 0x00001001 = 0xCD 0x00001002 = 0xDE 0x00001003 = 0xEF 0x00001002 = 0xBE

After the first four writes, the data in the merge latch contains 0xABCDDEEF. However, after the fifth write, the merge latch data now contains 0xABCDBEEF.

So long as the incoming word address is the same as the merge latch word address, the data can change without a processor stall or access to memory.

Write buffer merging is controlled by the Config[NM] bit and the TLB[CCA] setting. When Config0[NM] is 1 or TLB[CCA] is 2, the merge latch does not perform merging. Conversely, Config0[NM] is 0 or TLB[CCA] is not 2 enables merging. Out of reset, Config0[NM] is 0.

- **Note:** Merging takes place *only* in the merge latch. As such, writes to an address which are in the FIFO (but not in the merge latch) do not merge. In the example below, writes to 0x0001000 and 0x0001002 do not merge because the intervening write to address 0x00001005 is not in the same word address which caused 0x00001000 to leave the merge latch.

- 000 = 0xAB 005 = 0xCD 002 = 0xDE

AMDZ

#### 2.3.3 Write Buffer Gathering

Write buffer gathering combines *sequentially adjacent* word addresses for burst transfers to the main memory. When a C bit is set, all queue entries from zero (0) up to and including the entry with its C bit set (N) are written to main memory in a single burst.

Write buffer gathering is particularly useful for sequential, incremental address store operations, such as string operations. With write buffer gathering, the stores are combined into bursts up to 32-bytes (eight words) in length which reduces the number of accesses to the memory and increases effective throughput.

Here is an example of an eight-word burst. The burst could result from code which sequentially writes words (optimized memcpy(), for example). These eight word writes occur in sequence:

0x00001000 0x00001004 0x00001008 0x0000100C 0x00001010 0x00001014 0x00001018 0x0000101C

The entries corresponding to word addresses 0x00001000 through 0x00001018 have C bit set to zero. When address 0x0000101C arrives, its C bit is set. When the write buffer is granted the SBUS, it bursts all eight entries to main memory.

Here is an example of two-word burst. This burst may be typical of application software. These four word writes occur in sequence:

0x00001000 0x00001004 0x0000100C 0x00001008

The C bit is cleared for the 0x00001000 entry and is set for the 0x00001004 entry. These two words are then burst to main memory. The 0x0000100C entry also has its C bit set, and is written to memory. The 0x00001008 will reside in the merge latch until displaced by a subsequent store.

#### 2.3.4 Write Buffer Reads

When a read from memory is initiated, the read cache-line address (A35..A5) is compared against all cache-line addresses in the write buffer. If the read cache-line address matches a write buffer cache-line address, the read is stalled. The write buffer then flushes entries to memory until the read address no longer matches a write buffer cache-line address. The read is then allowed to complete. The write buffer ensures data integrity by not allowing reads to bypass writes.

#### 2.3.5 Write Buffer Coherency

Non-cacheable stores and/or data cache store-misses reside in the write buffer, possibly indefinitely. Furthermore, the write buffer does not snoop SBUS transactions (e.g. integrated peripheral DMA engines). To ensure the write buffer contents are committed to memory, a **SYNC** instruction must be issued.

Issuing a **SYNC** instruction prior to enabling each DMA transfer from memory buffers and/or structures is necessary. Without the **SYNC**, the DMA engine may retrieve incomplete buffers and/or structures (the remainder of which may be in the write buffer).

Issuing a **SYNC** instruction after a store to an I/O region where stores have side effects is necessary. Without the **SYNC** instruction, the store may not leave the write buffer to achieve the side effects (e.g. clearing an interrupt acknowledge bit).

Note that a read access does not guarantee a complete write buffer flush since the write buffer flushes as few entries as necessary until the read address no longer matches an address in the write buffer.

# 2.4 Virtual Memory

The Au1 implements a TLB-based virtual address translation unit which is compliant with the MIPS32 specification. This scheme is similar to the R4000 TLB and CP0 implementation. The "MIPS32 Architecture For Programmers Volume III" contains all the information relevant to a TLB-based virtual address translation unit.

The virtual address translation architecture is composed of a main 32-entry fully associative TLB array. To improve instruction fetch performance, a 4-entry fully associative instruction TLB is implemented. This miniature instruction TLB is fully coherent with the main TLB array and is completely transparent to software.

Each TLB entry maps a 32-bit virtual address to a pair of 36-bit physical addresses. The page size of a TLB entry is variable under software control, from 4 KB to 16 MB.

A TLB entry is described below.

#### **TLB Entry**

| ·,         |    |    |    |    |    |    |    |    |     |     |     |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |    |     |    |    |   |

|------------|----|----|----|----|----|----|----|----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|----|-----|----|----|---|

| Bit 31     | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22  | 21  | 20  | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4  | 3   | 2  | 1  | 0 |

| PageMask   | 0  |    |    |    |    |    |    |    | Pa  | age | Mas | sk |    |    |    |    |    |    |    |    |    |   |   |   | 0 |   |    |     |    |    |   |

|            |    |    |    |    |    |    |    |    |     |     |     |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |    |     |    |    |   |

| EntryHi    |    |    |    |    |    |    |    | V  | PN2 | 2   |     |    |    |    |    |    |    |    |    |    | 0  |   |   |   |   |   | AS | SID |    |    |   |

| EntryLo0 0 | 0  |    |    |    |    |    |    |    |     |     |     |    | PF | N0 |    |    |    |    |    |    |    |   |   |   |   |   | C0 |     | D0 | V0 | G |

| EntryLo1 0 | 0  |    |    |    |    |    |    |    |     |     |     |    | PF | N1 |    |    |    |    |    |    |    |   |   |   |   |   | C1 |     | D1 | V1 | G |

The size of the page(s) that the TLB entry translates is determined by PageMask. The valid values for PageMask range from 4 KB to 16 MB, according to Table 2-4.

|           | •                 | • •                                     |                |

|-----------|-------------------|-----------------------------------------|----------------|

| Page Size | PageMask Register | Bits [28:13]                            | PFN Select Bit |

| 4 KB      | 0x0000000         | 000000000000000000000000000000000000000 | 12             |

| 16 KB     | 0x00006000        | 00000000000011                          | 14             |

| 64 KB     | 0x0001E000        | 000000000001111                         | 16             |

| 256 KB    | 0x0007E000        | 000000000111111                         | 18             |

| 1 MB      | 0x001FE000        | 000000011111111                         | 20             |

| 4 MB      | 0x007FE000        | 0000001111111111                        | 22             |

| 16 MB     | 0x01FFE000        | 0000111111111111                        | 24             |

#### Table 2-4. Values for Page Size and PageMask Register

The PageMask determines the number of significant bits in the 32-bit address generated by the program (either as a load/ store address or an instruction fetch address). The upper, significant bits of the program address are compared against the upper, significant bits of VPN2. When an address match occurs, the even/odd PFN select bit of the program address selects either PFN0 (even) or PFN1 (odd) as the upper bits of the resulting 36-bit physical address.

The TLB mechanism permits mapping a larger, 36-bit physical address space into the smaller 32-bit program address space. The Au1 implements an internal 36-bit physical address SBUS which is then decoded by integrated peripherals, and by chip-selects for external memories and peripherals.

The cache coherency attributes (CCA) of the physical page are controlled by the TLB entry. The valid values are described in Table 2-3 on page 19. In general, I/O spaces require a non-cacheable setting, whereas memory can utilize a cacheable setting.

Note: Physical addresses in which address bits [35:32] are non-zero must be mapped non-cached (CCA = 2).

The TLB array is managed completely by software. Software can implement a TLB replacement algorithm that is either random (via the **TLBWR** instruction) or deterministic (via the **TLBWI** instruction). Hardware is available to segment the TLB via the Wired register so different replacement strategies can be used for different areas of the TLB.

# 2.5 Exceptions

The Au1 core implements a MIPS32 compliant exception scheme. The scheme consists of the exception vector entry points in both KSEG0 and KSEG1, and the exception code (ExcCode) encodings to determine the nature of the exception.

## 2.5.1 Exception Causes

The nature of an exception is reported in the Cause[ExcCode] field. The Au1 core can generate the following exceptions:

| ExcCode | Mnemonic | Description                                         |

|---------|----------|-----------------------------------------------------|

| 0       | Int      | Interrupt                                           |

| 1       | Mod      | TLB modification exception                          |

| 2       | TLBL     | TLB exception (load or instruction fetch)           |

| 3       | TLBS     | TLB exception (store)                               |

| 4       | AdEL     | Address error exception (load or instruction fetch) |

| 5       | AdES     | Address error exception (store)                     |

| 6       | IBE      | Bus error exception (instruction fetch)             |

| 7       | DBE      | Bus error exception (data reference: load or store) |

| 8       | Sys      | Syscall exception                                   |

| 9       | Вр       | Breakpoint exception                                |

| 10      | RI       | Reserved instruction exception                      |

| 11      | CpU      | Coprocessor Unusable exception                      |

| 12      | Ov       | Arithmetic Overflow exception                       |

| 13      | Tr       | Trap exception                                      |

| 23      | WATCH    | Reference to Watchpoint address                     |

| 24      | MCheck   | Machine Check (duplicate TLB entry)                 |

Table 2-5. Cause[ExcCode] Encodings

The Au1 core does not implement hardware floating-point. As a result, all floating-point instructions generate the Reserved Instruction (RI) exception, which permits floating-point operations to be emulated in software.

In addition, the Au1 core does not recognize Soft Reset, Non-Maskable Interrupt (NMI), or Cache Error exception conditions. 2.5.2

# Interrupt Architecture

The Au1 core implements a MIPS32 compliant interrupt mechanism in which eight interrupt sources are presented to the core. Each interrupt source is individually maskable to either enable or disable the core from detecting the interrupt. Interrupts are generated by software, integrated interrupt controllers, performance counters and timers, as noted in Table 2-6.

| Interrupt Source                                  | CP0 Cause Register Bit | CP0 Status Register Bit |

|---------------------------------------------------|------------------------|-------------------------|

| Software Interrupt 0                              | 8                      | 8                       |

| Software Interrupt 1                              | 9                      | 9                       |

| Interrupt Controller 0:<br>Request 0<br>Request 1 | 10<br>11               | 10<br>11                |

| Interrupt Controller 1:<br>Request 0<br>Request 1 | 12<br>13               | 12<br>13                |

| Performance Counters                              | 14                     | 14                      |

| Count/Compare                                     | 15                     | 15                      |

| Table 2-6. | <b>CPU Interrupt Sources</b> |  |

|------------|------------------------------|--|

|------------|------------------------------|--|

All interrupt sources are equal in priority; that is, the interrupt sources are not prioritized in hardware. As a result, software determines the relative priority of the interrupt sources. When Cause[ExcCode]=0, software must examine the Cause[IP] bits to determine which interrupt source is requesting the interrupt.

For more information on Interrupt Controller 0 and 1 see Section 6.0 "Interrupt Controller" on page 95.

# 2.6 MIPS32<sup>™</sup> Instruction Set

The Au1 core implements the instruction set defined in "MIPS32 Architecture For Programmers Volume II: The MIPS32 Instruction Set". The floating-point instructions are not implemented in the Au1 core, but may be emulated in software.

The MIPS32 ISA is characterized as a combination of the R3000 user level instructions (MIPSII) and the R4000 memory management and kernel mode instructions (32-bit MIPSIII).

#### 2.6.1 CACHE Instruction

The **CACHE** instruction permits management of the Au1 instruction and data caches. The valid operations are listed in Table 2-2 "Cache Operations" on page 19.

For *data* cache operations, the effect of the **CACHE** instruction is immediately visible to subsequent data accesses. However, for *instruction* cache operations, the effect of the **CACHE** instruction is not visible to subsequent instructions already in the Au1 core pipeline. Therefore, care should be exercised if modifying instruction cache lines containing the **CACHE** and subsequent instructions.

When issuing the **CACHE** instruction with indexed operations (Index Invalidate, Index Load Tag and Index Store Tag) the format of the effective address is as follows:

#### **CACHE Index Operation Address Decode**

| Bit | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22  | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8     | 7   | 6 | 5 | 4 | 3   | 2    | 1    | 0 |

|-----|----|----|----|----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|-----|---|---|---|-----|------|------|---|

|     |    |    |    |    |    |    |    |    | 0x8 | 000 |    |    |    |    |    |    |    |    | W  | ay |    |    | Se | t/Inc | lex |   |   |   | Byt | e Se | lect |   |

The effective address base should be 0x80000000 (KSEG0) to avoid possible TLB exceptions, and place zeros in the remainder of the effective address. The format correlates to a 16KB cache that is 4-way set associative with 128 sets and 32-byte line size.

Software must not use the Index Store Tag **CACHE** operation to change the Dirty, Lock and Shared state bits. To set the Lock bit, software must use the Fetch and Lock **CACHE** operation.

The Index Load Tag and Index Store Tag **CACHE** operations utilize CP0 registers DTag, DData, ITag and IData. The format of data for Index Tag operations is depicted in the description of these registers.

**CACHE** operations that require an effective address (i.e., not the Index operations) do not generate the Address Error Exception or trigger data watchpoint exceptions.

#### 2.6.2 PREF Instruction

The **PREF** instruction prefetches data into the data cache. Data is prefetched to improve algorithm performance by placing the data in the cache in advance of its use, thus minimizing stalls due to data cache load misses. See also Section 2.2.8.4 "Data Cache Control" on page 22 for more on how to use **PREF**.

If the effective address computed by the **PREF** instruction does not translate in the TLB (i.e. the address would cause a TLBL exception), no exception is generated and the cache is unchanged.

The Au1 core implements the following **PREF** instruction hints:

- 0x00 Normal load

- 0x04 Streaming load

A PREF instruction using any other hint value becomes a NOP for the Au1 core.

#### 2.6.3 WAIT Instruction

The **WAIT** instruction places the Au1 core in one of two low power modes: IDLE0 and IDLE1. The low power mode is encoded in the **WAIT** instruction bits 24:6 (implementation-dependent code). A value of 0 selects IDLE0, and the value 1 selects IDLE1. Other values are not supported and must not be used.

In the IDLE0 low power mode, the Au1 core stops clocks to all possible core units but continues to snoop the SBUS to maintain data coherency.

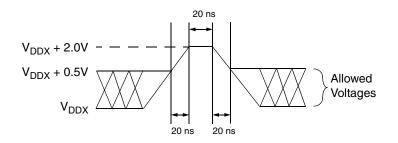

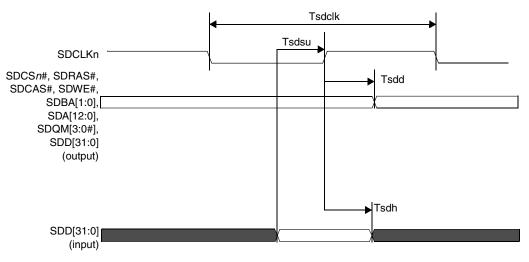

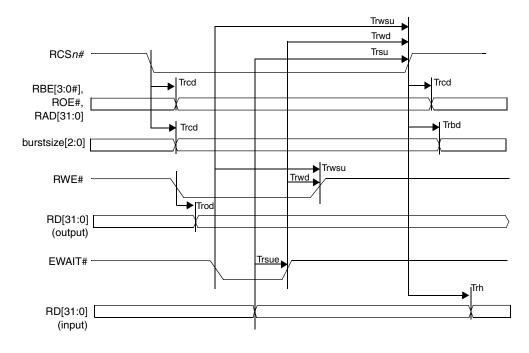

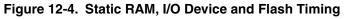

In the IDLE1 low power mode, the Au1 core stops clocks to all possible core units, including the data cache, so data coherency is no longer maintained.