User Guide

# **AMD Stream Computing**

August 2008

**PRELIMINARY**

© 2007, 2008 Advanced Micro Devices, Inc. All rights reserved. AMD, the AMD Arrow logo, ATI, the ATI logo, Radeon, FireStream, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other names are for informational purposes only and may be trademarks of their respective owners.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. The information contained herein may be of a preliminary or advance nature and is subject to change without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

Advanced Micro Devices, Inc.

One AMD Place

P.O. Box 3453

Sunnyvale, CA 94088-3453

www.amd.com

## **Preface**

## **About This Document**

This document provides a basic description of the AMD Stream Computing environment and components. It describes the basic architecture of stream processors and provides useful performance tips. This document also provides a guide for programmers who want to use the AMD Stream SDK to accelerate their applications.

## **Audience**

This document is intended for programmers. Programming guides for Brook+ and CAL are provided. It assumes prior experience in writing code for CPUs and basic understanding of threads. While a basic understanding of GPU architectures is useful, this document does not assume prior graphics knowledge.

## Contact Information

To submit questions or comments concerning this document, contact our technical documentation staff at: streamcomputing@amd.com.

For questions concerning AMD Stream products, please email: streamcomputing@amd.com.

For questions about developing with AMD Stream, please email: streamdeveloper@amd.com.

You can learn more about AMD Stream at: http://ati.amd.com/technology/streamcomputing.

We also have a growing community of AMD Stream users! Come visit us at the AMD Stream Developer Forum to find out what applications other users are trying on their AMD Stream products!

http://forums.amd.com/devforum/categories.cfm?catid=328

## Organization

This document begins with an overview of the AMD Stream Computing programming models, the stream processor hardware description, and a discussion of performance and optimization when programming for stream

Preface iii

processors. Chapters 2 and 3 are programming guides for the Brook+ language and CAL platform, respectively. Chapters 4 and 5 are the specifications for the Brook+ language and the CAL platform, respectively. The last section of this book is a glossary of acronyms and terms.

## Conventions

The following conventions are used in this document.

| mono-spaced font          | A filename, file path, or code.                                                                                  |

|---------------------------|------------------------------------------------------------------------------------------------------------------|

| *                         | Any number of alphanumeric characters in the name of a code format, parameter, or instruction.                   |

| < >                       | Angle brackets denote streams.                                                                                   |

| [1,2)                     | A range that includes the left-most value (in this case, 1) but excludes the right-most value (in this case, 2). |

| [1,2]                     | A range that includes both the left-most and right-most values (in this case, 1 and 2).                          |

| {x   y}                   | One of the multiple options listed. In this case, x or y.                                                        |

| 0.0                       | A single-precision (32-bit) floating-point value.                                                                |

| 1011b                     | A binary value, in this example a 4-bit value.                                                                   |

| 7:4                       | A bit range, from bit 7 to 4, inclusive. The high-order bit is shown first.                                      |

| italicized word or phrase | The first use of a term or concept basic to the understanding of stream computing.                               |

## **Related Documents**

- AMD, R600 Technology, R600 Instruction Set Architecture, Sunnyvale, CA, est. pub. date 2007. This document includes the RV670 GPU instruction details.

- ISO/IEC 9899:TC2 International Standard Programming Languages C

- Kernighan Brian W., and Ritchie, Dennis M., *The C Programming Language*, Prentice-Hall, Inc., Upper Saddle River, NJ, 1978.

- I. Buck, T. Foley, D. Horn, J. Sugerman, K. Fatahalian, M. Houston, and P. Hanrahan, "Brook for GPUs: stream computing on graphics hardware," ACM Trans. Graph., vol. 23, no. 3, pp. 777–786, 2004.

- AMD Intermediate Language (IL) Compiler Reference Manual. Published by AMD.

- CAL Image. AMD's Compute Abstraction Layer Program Binary Format Specification. Published by AMD.

- Buck, Ian; Foley, Tim; Horn, Daniel; Sugerman, Jeremy; Hanrahan, Pat; Houston, Mike; Fatahalian, Kayvon. "BrookGPU" http://graphics.stanford.edu/projects/brookgpu/

- Buck, Ian. "Brook Spec v0.2". October 31, 2003. http://merrimac.stanford.edu/brook/brookspec-05-20-03.pdf

- OpenGL Programming Guide, at http://www.glprogramming.com/red/

- Microsoft DirectX Reference Website, at http://msdn.microsoft.com/archive/default.asp?

url=/archive/enus/directx9\_c\_Summer\_04/directx/graphics/reference/reference.asp

- GPGPU: http://www.gpgpu.org, and Stanford BrookGPU discussion forum http://www.gpgpu.org/forums/

Preface v

## **Contents**

| Chapter 1 | AMD Stream Computing Overview |                          |                                                 |      |

|-----------|-------------------------------|--------------------------|-------------------------------------------------|------|

|           | 1.1                           | The Al                   | The AMD Stream Computing Programming Model      |      |

|           |                               | 1.1.1                    | Pseudo Code Explanation of AMD Stream Computing | 1-3  |

|           |                               | 1.1.2                    | Brook+ Open-Source Data-Parallel C Compiler     | 1-8  |

|           |                               | 1.1.3                    | AMD Compute Abstraction Layer (CAL)             | 1-9  |

|           |                               | 1.1.4                    | GPU ShaderAnalyzer                              | 1-10 |

|           |                               | 1.1.5                    | AMD Core Math Library (ACML)                    | 1-11 |

|           | 1.2                           | Stream                   | n Processor Hardware Functionality              | 1-12 |

|           |                               | 1.2.1                    | The Stream Processor                            | 1-12 |

|           |                               | 1.2.2                    | Thread Processing                               | 1-14 |

|           |                               | 1.2.3                    | Flow Control                                    | 1-14 |

|           |                               | 1.2.4                    | Thread Creation                                 | 1-15 |

|           |                               | 1.2.5                    | Accessing Memory                                | 1-16 |

|           |                               | 1.2.6                    | Host-to-Stream Processor Communication          | 1-18 |

|           |                               | 1.2.7                    | Stream Processor Scheduling                     | 1-19 |

|           | 1.3                           | Perfori                  | mance                                           | 1-2  |

|           |                               | 1.3.1                    | Analyzing Stream Processor Kernels              | 1-21 |

|           |                               | 1.3.2                    | Estimating Performance                          | 1-22 |

|           |                               | 1.3.3                    | Additional Performance Factors                  | 1-23 |

| Chapter 2 | Brook+ Programming            |                          |                                                 |      |

|           | 2.1                           | Prereq                   | juisites                                        | 2-1  |

|           |                               | 2.1.1                    | System Requirements                             | 2-1  |

|           |                               | 2.1.2                    | Installation                                    | 2-1  |

|           |                               | 2.1.3                    | Syntax Highlighting in Visual Studio            | 2-3  |

|           | 2.2                           | 2.2 A Sample Application |                                                 | 2-3  |

|           |                               | 2.2.1                    | Writing                                         | 2-3  |

|           |                               | 2.2.2                    | Building                                        | 2-6  |

|           |                               | 2.2.3                    | Executing                                       | 2-7  |

|           |                               | 2.2.4                    | Debugging                                       | 2-7  |

|           |                               | 2.2.5                    | Logging                                         | 2-7  |

|           | 2.3                           | Include                  | ed Samples                                      | 2-8  |

|           |                               | 2.3.1                    | Simple Matrix Multiply Example                  | 2-8  |

|           |                               | 2.3.2                    | Optimized Matrix Multiply Example               | 2-10 |

|           | 24                            | Fxamn                    | ole of Generated C++ Code for sum, br           | 2-13 |

|           | 2.5         | Buildir                               | ng Brook+                                       | 2-14 |

|-----------|-------------|---------------------------------------|-------------------------------------------------|------|

|           |             | 2.5.1                                 | Visual Studio                                   | 2-14 |

|           |             | 2.5.2                                 | Command Line                                    | 2-15 |

| Chapter 3 | 3 Al        | MD Cor                                | mpute Abstraction Layer (CAL) Programming Guide |      |

|           | 3.1         | Introdu                               | uction                                          | 3-1  |

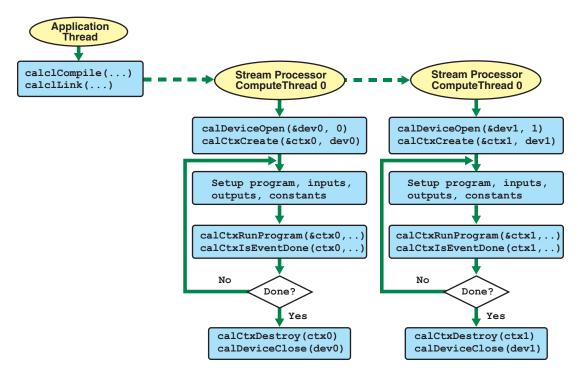

|           |             | 3.1.1                                 | CAL System Architecture                         | 3-1  |

|           |             | 3.1.2                                 | CAL Programming Model                           | 3-5  |

|           |             | 3.1.3                                 | CAL Software Distribution                       | 3-6  |

|           | 3.2         | CAL Application Programming Interface |                                                 | 3-7  |

|           |             | 3.2.1                                 | CAL Runtime                                     | 3-8  |

|           |             | 3.2.2                                 | CAL Compiler                                    | 3-14 |

|           |             | 3.2.3                                 | Kernel Execution                                | 3-16 |

|           | 3.3         | HelloC                                | CAL Application                                 | 3-18 |

|           |             | 3.3.1                                 | Code Walkthrough                                | 3-19 |

|           | 3.4         | Perfor                                | mance Optimizations                             | 3-24 |

|           |             | 3.4.1                                 | Arithmetic Computations                         | 3-24 |

|           |             | 3.4.2                                 | Memory Considerations                           | 3-25 |

|           |             | 3.4.3                                 | Asynchronous Operations                         | 3-27 |

|           | 3.5         | Tutoria                               | al Application                                  | 3-28 |

|           |             | 3.5.1                                 | Problem Description                             | 3-29 |

|           |             | 3.5.2                                 | Basic Implementation                            | 3-29 |

|           |             | 3.5.3                                 | Optimized Implementation                        | 3-30 |

|           | 3.6         | CAL/D                                 | 3-33                                            |      |

| 3.7       |             | Advanced Topics                       |                                                 | 3-33 |

|           |             | 3.7.1                                 | Thread-Safety                                   | 3-33 |

|           |             | 3.7.2                                 | Multiple Stream Processors                      |      |

|           |             | 3.7.3                                 | Using the Global Buffer in CAL                  | 3-35 |

|           |             | 3.7.4                                 | Double Precision Arithmetic                     | 3-37 |

| Appendix  | A B         | rook+ S                               | Specification                                   |      |

|           | <b>A</b> .1 | The St                                | tructure of a Brook+ Program                    | A-1  |

|           | <b>A.2</b>  | Primiti                               | ive Data Types                                  | A-2  |

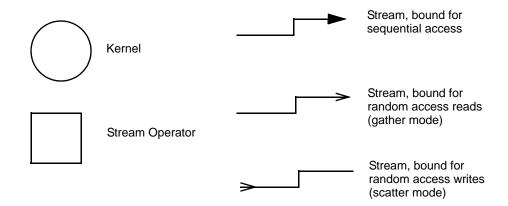

|           | A.3         | Strean                                | ns and Stream Operators                         | A-3  |

|           |             | A.3.1                                 | Streams                                         | A-3  |

|           |             | A.3.2                                 | Stream Declarations                             | A-4  |

|           |             | A.3.3                                 | Stream Operators                                | A-4  |

|           | <b>A</b> .4 | Kernel                                | ls                                              | A-7  |

|           |             | A.4.1                                 | Kernel Types                                    | A-7  |

|           |             | A.4.2                                 | Kernel-Specified Communication Patterns         | A-9  |

|           |             | A.4.3                                 | Calling Other Code from Kernel Code             | A-10 |

|           |             | A.4.4                                 | Restrictions on Kernel Code                     | A-10 |

|           | A.5         | Standa                                | ard Library Functions and Intrinsics            | A-11 |

| Appendix B TI | ne AMD Compute Abstraction Layer (CAL) API Specification |      |

|---------------|----------------------------------------------------------|------|

| B.1           | Programming Model                                        | B-1  |

| B.2           | Runtime                                                  | B-3  |

|               | B.2.1 System                                             | B-3  |

|               | B.2.2 Device Management                                  | B-3  |

|               | B.2.3 Memory Management                                  | B-3  |

|               | B.2.4 Context Management                                 | B-4  |

|               | B.2.5 Program Loader                                     | B-4  |

|               | B.2.6 Computation                                        | B-4  |

| B.3           | Platform API                                             | B-4  |

|               | B.3.1 System Component                                   | B-4  |

|               | B.3.2 Device Management                                  | B-5  |

|               | B.3.3 Memory Management                                  | B-8  |

|               | B.3.4 Context Management                                 | B-13 |

|               | B.3.5 Loader                                             | B-15 |

|               | B.3.6 Computation                                        | B-17 |

|               | B.3.7 Error Reporting                                    | B-19 |

| B.4           | Extensions                                               | B-19 |

|               | B.4.1 Extension Functions                                | B-19 |

|               | B.4.2 Interoperability Extensions                        | B-20 |

|               | B.4.3 Counters                                           | B-22 |

| B.5           | CAL API Types                                            | B-25 |

|               | B.5.1 Enums                                              | B-25 |

|               | B.5.2 Structures                                         | B-25 |

| B.6           | Function Calls in Alphabetic Order                       | B-25 |

| Appendix C S  | upported Devices                                         |      |

| Appendix D In | troduction to 3D Graphics and Shader Terminology         |      |

| D.1           | Shaders                                                  | D-1  |

| D.2           | Domain of Execution                                      | D-1  |

| D 3           | Geometry and Vertices                                    | D-1  |

## **Figures**

| 1.1  | AMD Stream Software Ecosystem                                | 1-1  |

|------|--------------------------------------------------------------|------|

| 1.2  | Simplified AMD Stream Computing Programming Model            | 1-2  |

| 1.3  | Stream Processor Execution                                   | 1-4  |

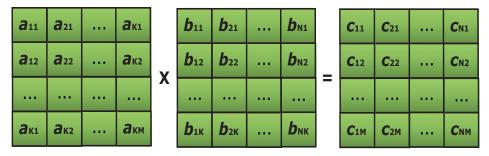

| 1.4  | Matrix Multiply (nxk) X (kxm)                                | 1-5  |

| 1.5  | Brook+ Language Elements                                     | 1-9  |

| 1.6  | CAL Functionality                                            | 1-10 |

| 1.7  | GSA User Interface Example                                   | 1-11 |

| 1.8  | Generalized Stream Processor Structure                       | 1-12 |

| 1.9  | Simplified Block Diagram of the Stream Processor             | 1-13 |

| 1.10 | Rasterization of Threads to SIMD Engines                     | 1-15 |

| 1.11 | One Example of a Tiled Layout Format                         | 1-18 |

| 1.12 | Simplified Execution Of Threads On A Single Thread Processor | 1-20 |

| 1.13 | Thread Processor Stall Due to Data Dependency                | 1-21 |

| 1.14 | AMD GPU ShaderAnalyzer Output                                | 1-22 |

| 2.1  | Compiling a Brook+ File and Generating a C++ File            | 2-6  |

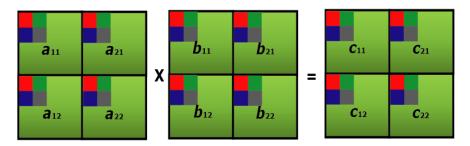

| 2.2  | Optimized Matrix Multiplication                              | 2-12 |

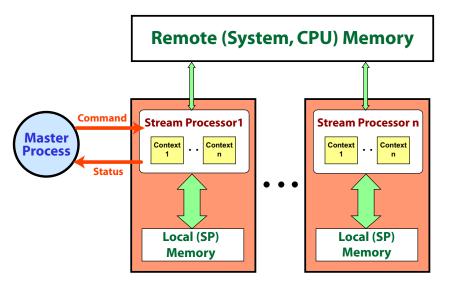

| 3.1  | CAL System Architecture                                      | 3-2  |

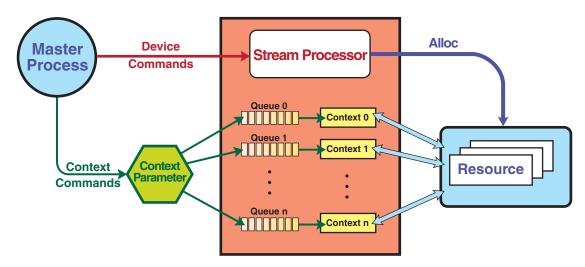

| 3.2  | CAL Device and Memory                                        | 3-3  |

| 3.3  | AMD Stream Processor Architecture                            | 3-4  |

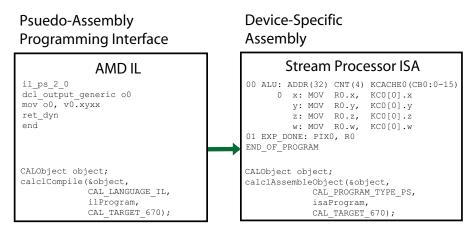

| 3.4  | CAL Code Generation                                          | 3-6  |

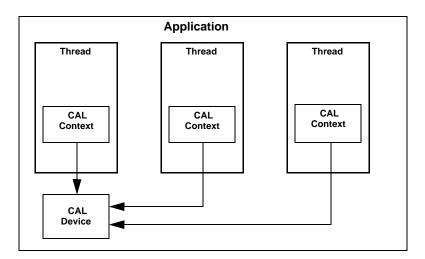

| 3.5  | Context Management for Multi-Threaded Applications           | 3-10 |

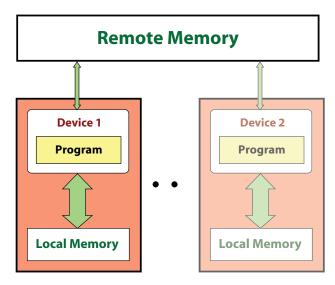

| 3.6  | Local and Remote Memory                                      | 3-11 |

| 3.7  | Kernel Compilation Sequence                                  | 3-16 |

| 3.8  | Multiplication of Two Matrices                               | 3-29 |

| 3.9  | Blocked Matrix Multiplication                                | 3-31 |

| 3.10 | Micro-Tiled Blocked Matrix Multiplication                    | 3-32 |

| 3.11 | CAL Application using Multiple Stream Processors             | 3-35 |

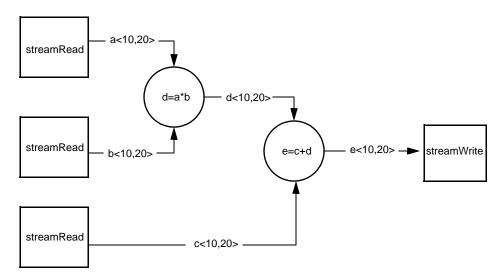

| A.1  | Symbols for Brook+ Building Blocks                           | A-2  |

| A.2  | Simple Streamed Multiply-Add                                 | A-2  |

| B.1  | CAL System                                                   | B-2  |

| B.2  | Context Queues                                               | B-3  |

# **Chapter 1 AMD Stream Computing Overview**

AMD Stream Computing harnesses the tremendous processing power of GPUs (stream processors) for high-performance, data-parallel computing in a wide range of applications. The following is an overview of the AMD Stream Computing programming model, hardware, and performance.

## 1.1 The AMD Stream Computing Programming Model

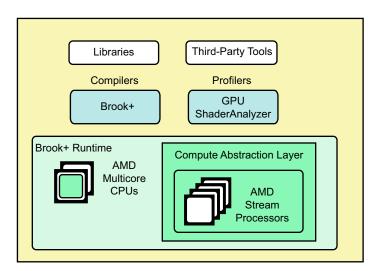

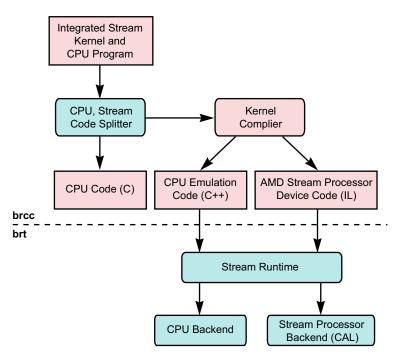

The AMD Stream Computing Model includes a software stack and the AMD stream processors. Figure 1.1 illustrates the relationship of the AMD Stream Computing components.

Figure 1.1 AMD Stream Software Ecosystem

The AMD Stream Computing software stack provides end-users and developers with a complete, flexible suite of tools to leverage the processing power in AMD stream processors. AMD software embraces open-systems, open-platform standards. The AMD open platform strategy enables AMD technology partners to develop and provide third-party development tools.

The software includes the following components:

• Compilers – like the Brook+ compiler with extensions for AMD devices.<sup>2</sup>

<sup>1.</sup> A stream is a collection of data elements of the same type that can be operated on in parallel.

<sup>2.</sup> See Chapter 2, "Brook+ Programming," for using Brook+.

- Device Driver for stream processors AMD Compute Abstraction Layer (CAL).<sup>1</sup>

- Performance Profiling Tools GPU ShaderAnalyzer.

- Performance Libraries ACML for optimized domain-specific algorithms.

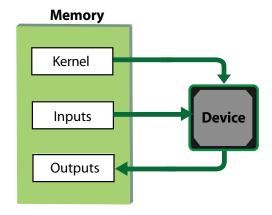

The latest generation of AMD stream processors are programmed using the unified shader programming model. Programmable stream cores execute various user-developed programs, called *stream kernels* (or simply: kernels). These stream cores can execute non-graphics functions using a virtualized SIMD programming model operating on streams of data. In this programming model, known as *stream computing*, arrays of input data elements stored in memory are mapped onto a number of SIMD engines, which execute kernels to generate one or more outputs that are written back to output arrays in memory.

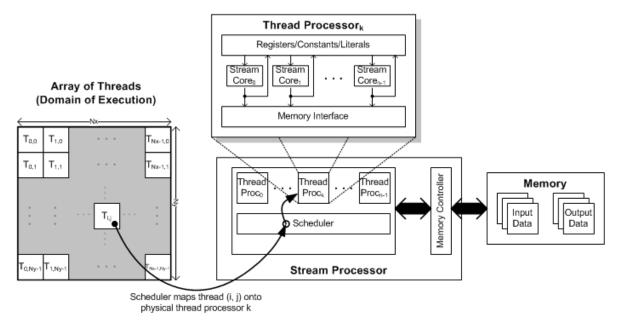

Each instance of a kernel running on a SIMD engine's thread processor is called a *thread*. A specified rectangular region of the output buffer to which threads are mapped is known as the *domain of execution*.

The stream processor schedules the array of threads onto a group of *thread processors*, until all threads have been processed. Subsequent kernels can then be executed, until the application completes. A simplified view of the AMD Stream Computing programming model and the mapping of threads to thread processors is shown in Figure 1.2 (also see Figure 1.9).

Figure 1.2 Simplified AMD Stream Computing Programming Model

<sup>1.</sup> When using CAL, it might not be necessary to use Brook+; instead, it is possible to use AMD IL. See Chapter 3, "AMD Compute Abstraction Layer (CAL) Programming Guide."

## 1.1.1 Pseudo Code Explanation of AMD Stream Computing

Another way to explain the AMD Stream Computing programming model is through pseudo code.

Matrix Sum - The following example sums two matrices.

The CPU code is:

```

void sum(float A[], float B[], float C[])

{

for(int i=0; i<n; i++)

{

for(int j=0; j<m; j++)

{

float a0 = A[i][j];

float b0 = B[i][j];

C[i][j] = a0 + b0;

}

}

}</pre>

```

This code can be rewritten as to emphasize the data parallel operations:

```

float sum_kernel(int y, int x, float M0[], float M1[])

{

float a0 = M0[y][x];

float b0 = M1[y][x];

return a0 + b0;

}

void sum(float A[], float B[], float C[])

{

for(int i=0; i<n; i++)

{

for(int j=0; j<m; j++)

{

C[i][j] = sum_kernel(i, j, A, B);

}

}

}</pre>

```

The CPU executes the code serially such that C[0][0] is calculated before C[0][1]. However, the elements of C can be calculated independently of each other in any order. On a multi-CPU-core processor, they can also be calculated in parallel.

A multi-threaded version of the code might look like this:

```

void sum(float A[], float B[], float C[])

{

for(int i=0; i<n; i++)

{

for(int j=0; j<m; j++)

{

launch_thread{ C[i][j] = sum_kernel(i, j, A, B); }

}

}

sync_threads{}

}</pre>

```

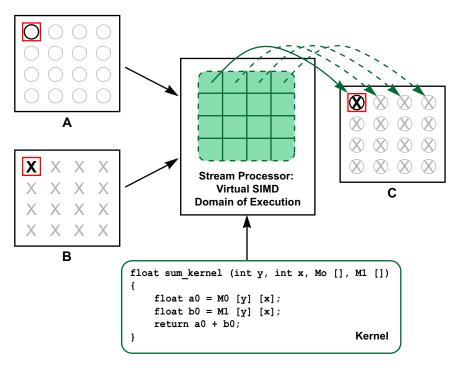

Effectively, this is the AMD Stream Computing programming model. The function  $sum\_kernel$  is the kernel written by the developer. The array C is the output stream and defines the domain of execution  $(n \times m)$ . Independent threads that run  $sum\_kernel$  execute and write at every location in C. The hardware takes the place of the nested for-loop.

Figure 1.3 illustrates the process of a matrix sum execution in a stream processor. Since the stream processor can operate in parallel with the CPU, sync\_threads is used to wait for the threads to complete before continuing. The CPU can perform other tasks while the stream processor is processing.

High-level languages for AMD Stream Computing, such as Brook+, abstract the hardware details; no additional knowledge of stream processor hardware is required. The developer writes kernels to be executed on the stream processor, provides inputs and outputs, and defines the domains of execution.

Figure 1.3 Stream Processor Execution

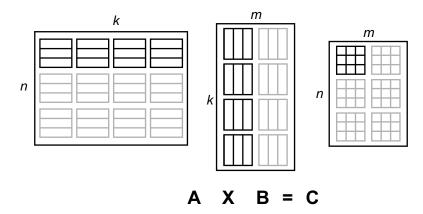

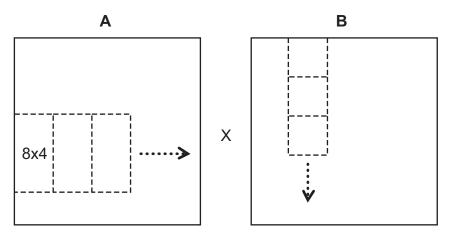

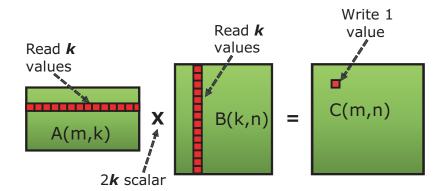

Matrix Multiply – This example multiplies two matrices (see Figure 1.4). This shows how some understanding of the hardware can improve performance.

Figure 1.4 Matrix Multiply (nxk) X (kxm)

The CPU code is:

```

void matmult(float A[], float B[], float C[])

{

for(int i=0; i<n; i++)

{

for(int j=0; j<m; j++)

{

float total = 0;

for(int c=0; c<k; c++)

total += A[i][c] * B[c][j];

C[i][j] = total;

}

}</pre>

```

The kernel that can be executed on the stream processor is shown in bold. The outer two for-loops represent the stream processor executing the kernel on the domain of execution of array C.

Again, this code can be rewritten as to emphasize the data parallel operations:

One feature of stream processors is that each thread processor can perform parallel operations. So far, the examples indicate scalar operations in the kernel. If the compiler detects parallelization within a kernel, it tries to optimize it. For example, a thread processor can execute multiple multiplies and adds simultaneously. To take advantage of the stream processor's ability to perform multiple operations at the same time, the user can explicitly code in vector operations.

The following implementation uses the float4 data type. This causes the thread processors to execute four operations at the same time:

Several key changes in this code maximize performance. Since inputs and outputs are now float4 instead of float, the domain of execution dimensions decrease to  $(n \times (m/4))$ ; fewer threads are executed by the stream processor.

Also, the addressing for one of the arrays in the kernel has changed. To support maximum usage of float4 operations, the second matrix, B, must be transposed to B'. The inner loop also decreases by a factor of four. The developer must decide if the extra step of transposing the input data is worth the cost.

If the input matrices are small, the transposition cost might not be offset by the performance gain in the kernel. If the matrices are large, the time to perform the transpose might be offset by the optimized kernel and yield a performance gain. If the input matrix sizes are variable, two separate code paths might be required for optimal performance.

The following sections explain how the stream processor executes kernels. It also teaches the developer how to optimize code for execution on the stream processor.

## 1.1.2 Brook+ Open-Source Data-Parallel C Compiler

Brook+ provides an explicit data-parallel C compiler using extensions to the standard ANSI C programming language. The Brook+ computational model, called *streaming*, goes beyond traditional, sequential programming languages by providing:

- Data Parallelism Brook+ provides an intuitive mechanism for specifying single-instruction multiple-data (SIMD) operations.

- Arithmetic Intensity the Brook+ interface encourages development of efficient algorithms by minimizing global communication and maximizing localized computation on stream processors.

The two key elements in the Brook+ language are:

- Stream A collection of data elements of the same type that can be operated on in parallel. Streams are notated in angle brackets.

- Kernel A parallel function that operates on every element of a domain of execution. Kernels are specified using the kernel keyword.

The following code shows a Brook+ kernel that adds two input streams and stores the results in an output stream. The kernel performs an implicit loop over each element in the output stream.

```

kernel

void sum(float a<>, float b<>, out float c<>)

{

c = a + b;

}

```

As shown in Figure 1.5, the Brook+ software consists of:

- brcc a source-to-source meta-compiler that translates Brook+ programs (.br files) into device-dependent kernels embedded in valid C++ source code. The generated C++ source includes the CPU code and the stream processor device code, both of which are later linked into the executable.

- brt a runtime library that executes a kernel invoked from the CPU code in the application. Brook+ includes various runtimes for CPUs and stream processors; you can select the execution model at application run-time. The CPU runtime serves as a good debugging tool when developing stream kernels.

Figure 1.5 Brook+ Language Elements

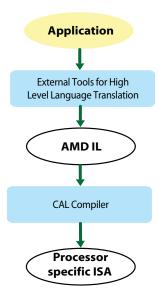

AMD has enhanced brcc to produce the virtual ISA, called the AMD IL (for intermediate language). AMD also has enhanced the brt with a backend optimized for AMD stream processors using the CAL driver (see Section 1.1.3, "AMD Compute Abstraction Layer (CAL)," page 1-9).

## 1.1.3 AMD Compute Abstraction Layer (CAL)

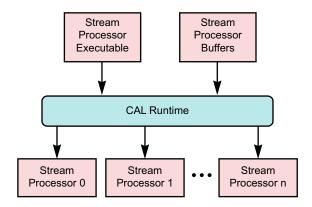

The AMD Compute Abstraction Layer (CAL) is a device driver library that provides a forward-compatible interface to AMD stream processors (see Figure 1.6). CAL lets software developers interact with the stream processor cores at the lowest-level for optimized performance, while maintaining forward compatibility. CAL provides:

- Device Specific Code Generation

- Device Management

- Resource Management

- Kernel Loading and Execution

- Multi-device support

- Interoperability with 3D Graphics APIs

Figure 1.6 CAL Functionality

CAL includes a set of C routines and data types that allow higher-level software tools to control hardware memory buffers (device-level streams) and stream processor programs (device-level kernels). The CAL runtime accepts kernels written in AMD IL and generates optimized code for the target architecture. It also provides access to device-specific features.

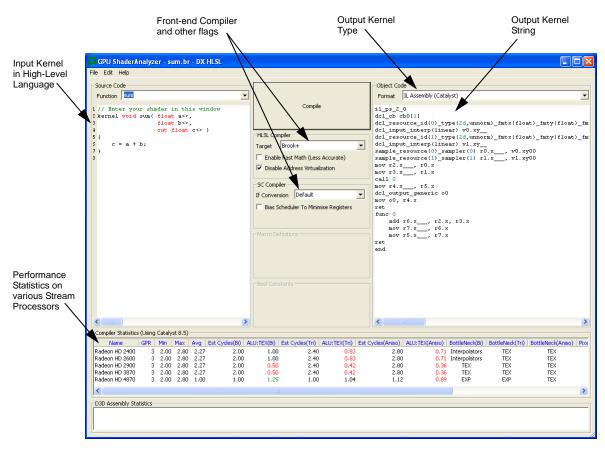

## 1.1.4 GPU ShaderAnalyzer

The GPU ShaderAnalyzer is a performance-profiling tool developers can use to develop and profile stream kernels. It can be downloaded for free from the AMD developer web pages,

http://ati.amd.com/technology/streamcomputing/sdkdownload.html.

Features provided by the GPU ShaderAnalyzer include:

- Quick syntax checking of programs written in Brook+.

- Online kernel compilation to generate the equivalent AMD IL and the processor-specific ISA assembly. The generated assembly can be modified manually and used in a CAL application.

- Performance characterization of arithmetic, memory, and flow-control instructions.

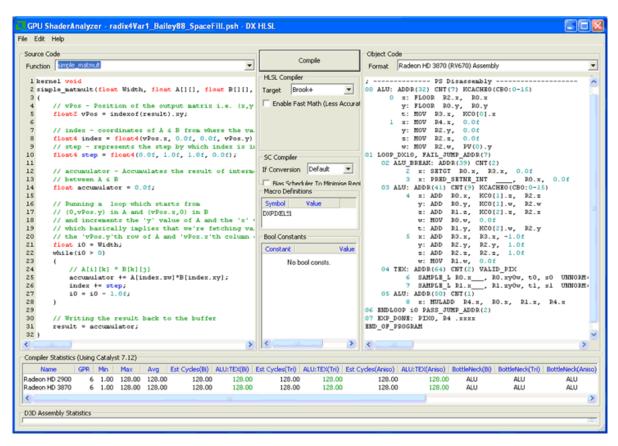

The GPU ShaderAnalyzer has a simple graphical user interface. Figure 1.7 shows an example kernel, that was written in Brook+ and is converted to AMD IL. The generated AMD IL can be sent to the CAL runtime compiler for object code generation and subsequent execution.

Figure 1.7 GSA User Interface Example

#### Note that:

- The input program can be edited directly in the Source Code window on the top-left.

- The function name must be the name of the Brook+ kernel.

- The target compiler must be set to Brook+ in the HLSL Compiler section.

- The output program type can be set using the Format selection tab in the Object Code section.

## 1.1.5 AMD Core Math Library (ACML)

The ACML includes a collection of commonly used mathematical software routines. It is optimized for AMD platforms and provides a quick path to high-performance development.

The ACML includes implementations of:

- Full Basic Linear Algebra Subroutines (BLAS)

- Linear Algebra Package (LAPACK) routines

- Fast Fourier Transform (FFT) routines

- Math transcendental routines

- Random Number Generator routines

The ACML includes a stream processing backend for load balancing of computations between the CPU and stream processor depending upon the suitability of the task for a particular architecture. This is done at runtime.

## 1.2 Stream Processor Hardware Functionality

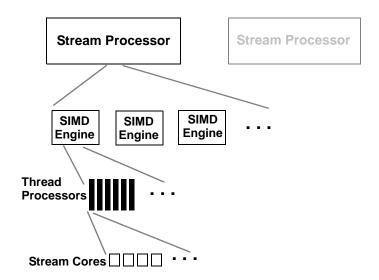

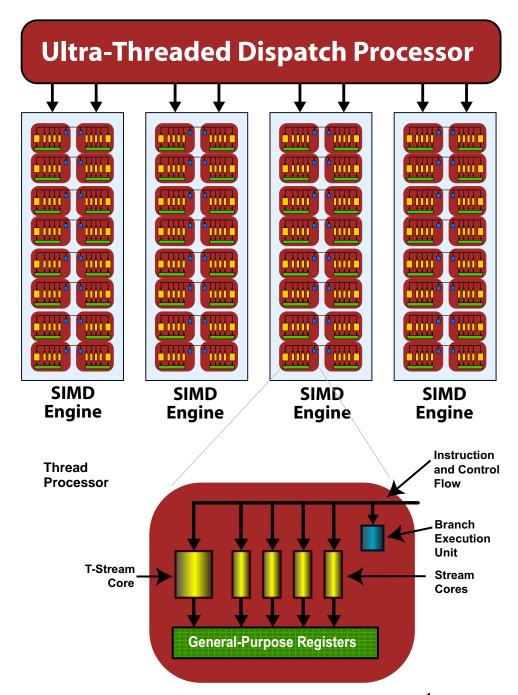

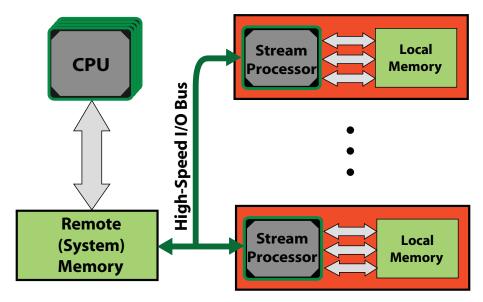

Figure 1.8 shows a simplified block diagram of a generalized stream processor.

Figure 1.8 Generalized Stream Processor Structure

#### 1.2.1 The Stream Processor

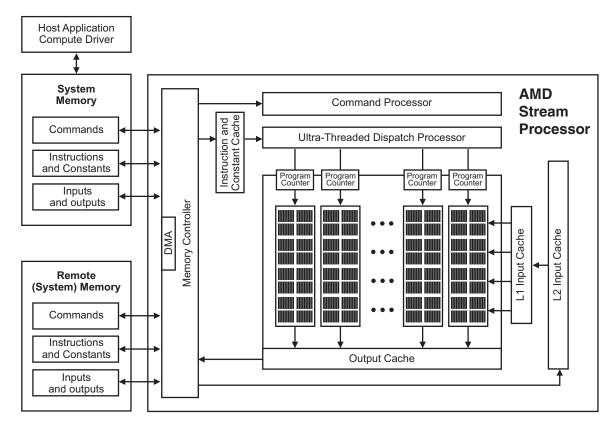

Figure 1.9 is a simplified diagram of an AMD stream processor. Different stream processors have different characteristics (such as the number of SIMD engines), but follow a similar design pattern.

Stream processors comprise groups of SIMD engines (see Figure 1.2). Each SIMD engine contains numerous thread processors, which are responsible for executing kernels, each operating on an independent data stream. Thread processors, in turn, contain numerous stream cores, which are the fundamental, programmable computational units, responsible for performing integer, single, precision floating point, double precision floating point, and transcendental operations. All thread processors within a SIMD engine execute the same instruction sequence; different SIMD engines can execute different instructions.

The stream-accelerated version of the ACML is called ACML-GPU. The ACML-GPU uses the stream

processor to accelerate ACML routines that can benefit from stream acceleration. The ACML-GPU

currently provides stream-accelerated implementations of SGEMM and DGEMM.

Figure 1.9 Simplified Block Diagram of the Stream Processor<sup>1</sup>

A thread processor is arranged as a five-way VLIW processor (see bottom of Figure 1.9). Up to five scalar operations can be co-issued in a very long instruction word (VLIW) instruction. Stream cores can execute single-precision floating point or integer operations. One of the five stream cores also can handle transcendental operations (sine, cosine, logarithm, etc.)<sup>2</sup>. Double-precision floating point operations are processed by connecting four of the stream cores

<sup>1.</sup> As described later, much of this is transparent to the programmer.

(excluding the transcendental core) to perform a single double-precision operation. The thread processor also contains one branch execution unit to handle branch instructions.

Different stream processors have different numbers of stream cores. For example, the ATI Radeon™ 3870 GPU (RV670) stream processor has four SIMD engines, each with 16 thread processors, and each thread processor contains five stream cores; this yields 320 physical stream cores.

## 1.2.2 Thread Processing

All thread processors within a SIMD engine execute the same instruction for each cycle. To hide latencies due to memory accesses and stream core operations, multiple threads are interleaved; thus, in a thread processor, up to four threads can issue four VLIW instructions over four cycles. For example, on the ATI Radeon™ 3870 GPU (RV670) stream processor, the 16 thread processors execute the same instructions, with each thread processor processing four threads at a time; effectively, this appears as a 64-wide SIMD engine. The group of threads that are executed together is called a *wavefront*.

The size of wavefronts can differ on different stream processors. For example, the ATI Radeon™ HD 2600 and the ATI Radeon™ HD 2400 graphics cards each have fewer thread processors in each SIMD engine on their stream processors compared to the ATI Radeon™ 3870 GPU (RV670) stream processor; therefore, the wavefront sizes are 32 and 16 threads, respectively. The AMD FireStream™ 9170 stream processor, which uses the RV670 stream processor, has a wavefront size of 64 threads.

SIMD engines operate independently of each other, so it is possible for each array to execute different instructions.

## 1.2.3 Flow Control

Flow control, such as branching, is done by combining all necessary paths as a wavefront. If threads within a wavefront diverge, all paths are executed serially. For example, if a thread contains a branch with two paths, the wavefront first executes one path, then the second path. The total time to execute the branch is the sum of each path time. An important point is that even if only one thread in a wavefront diverges, the rest of the threads in the wavefront execute the branch. The number of threads that must be executed during a branch is called the *branch granularity*. On AMD hardware, the branch granularity is the same as the wavefront granularity.

**Example 1:** If two branches, A and B, take the same amount of time *t* to execute over a wavefront, the total time of execution, if any thread diverges, is 2*t*.

Loops execute in a similar fashion, where the wavefront occupies a SIMD engine as long as there is at least one thread in the wavefront still being processed.

<sup>2.</sup> For the actual operations, see the AMD Compute Abstraction Layer (CAL) Technology Intermediate Language (IL) Reference Manual.

Thus, the total execution time for the wavefront is determined by the thread with the longest execution time.

**Example 2:** If *t* is the time it takes to execute a single iteration of a loop; and within a wavefront all threads execute the loop one time, except for a single thread that executes the loop 100 times, the time it takes to execute that entire wavefront is *100t*.

## 1.2.4 Thread Creation

Wavefronts are composed of *quads*, which are groups of 2x2 threads in the domain. Quads are processed together. If there are non-active threads within a quad, the thread processors that would have been mapped to those threads are idle. The simplest example is a domain of execution of height or width one. In this case, since quads are not fully covered, the hardware is only half used because half the quad is empty.

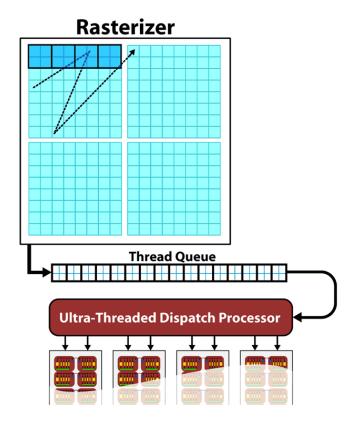

Wavefront construction and order of thread execution are determined by the *rasterization order* of the domain of execution (see Figure 1.10). *Rasterization* is the process of mapping threads from the domain of execution to SIMD engines<sup>1</sup>.

Figure 1.10 Rasterization of Threads to SIMD Engines

<sup>1.</sup> Rasterization is a carryover from graphics terminology, where it refers to the process of turning geometry, such as triangles, into pixels.

#### 1.2.4.1 Rasterization

Rasterization follows a pre-set zig-zag-like pattern across the domain of execution. The exact pattern normally is not disclosed because it might change in subsequent stream processor generations. The pattern is based on multiples of 8x8 blocks (16 quads) within the domain, matching the size of a wavefront. For example, if the domain of execution is 16x16, the first 8x8 block maps to one wavefront and is executed in one SIMD engine. A second 8x8 block maps to another wavefront and is executed in another SIMD engine. This continues until all 8x8 blocks in the domain are mapped to SIMD engines.

#### 1.2.4.2 Thread Optimization

AMD hardware is designed to maximize the number of active threads in a wavefront. So, if there are partial 8x8 blocks, the stream processor tries to fill the rest of the wavefront from other blocks, but within the quad limitation. For example, if the domain is of height 2, the wavefront is constructed using blocks of height 2 and width 32. Thus, having domains that are a multiple of 8x8 is not necessary, but might be more efficient.

This rasterization process is transparent to the user, but can affect memory access performance, as described in Section 1.2.5, "Accessing Memory," page 1-16.

## 1.2.5 Accessing Memory

Accessing stream processor local memory typically is an order of magnitude faster than accessing remote (system or CPU) memory. However, stream cores (see Figure 1.8) do not directly access memory; instead, they issue memory requests through dedicated hardware units. When a thread tries to access memory, the thread is transferred to the appropriate fetch unit. The thread is then deactivated until the access unit finishes accessing memory. Meanwhile, other threads can be active within the SIMD engine, contributing to better performance. The data fetch units handle three basic types of memory operations: loads, stores, and streaming stores. Stream processors now can store writes to random memory locations using global buffers.

#### 1.2.5.1 Global Buffer

The global buffer lets applications read from, and write to, arbitrary locations in input buffers and output buffers, respectively. When using a global buffer, memory-read and memory-write operations from the stream kernel are done using regular stream processor instructions with the global buffer used as the source or destination for the instruction. The programming interface is similar to load/store operations used with CPU programs, where the relative address in the read/write buffer is specified.

#### 1.2.5.2 Memory Loads

Memory loads are done by addressing the desired location in the input memory using the fetch unit. The fetch units can process either 1D or 2D addresses.

These addresses can be *normalized* or *un-normalized*. Normalized coordinates are between 0.0 and 1.0 (inclusive). For the fetch units to handle 2D addresses and normalized coordinates, pre-allocated memory segments must be bound to the fetch unit so that the correct memory address can be computed. For a single kernel invocation, up to 128 memory segments can be bound at once. The maximum number of 2D addresses is 8192x8192. When accessing a global buffer, of which only one can be bound at a time, addresses must be unnormalized, 1D coordinates. Memory loads are usually cached, except for loads from a global buffer, which are not cached.

#### 1.2.5.3 Memory Stores

When using a global buffer, each thread can write to an arbitrary location within the global buffer. Only one global buffer is allowed to be bound at a time for a particular kernel invocation. The same global buffer must be used for loads and stores. Global buffers use a linear memory layout. If consecutive addresses are written, the SIMD engine issues a burst write for more efficient memory access.

#### 1.2.5.4 Streaming Stores

Kernels can perform streaming writes in up to eight separate memory segments. The streaming writes occur only once per kernel invocation: only one write is allowed per segment, and the write location is implicitly computed based on each thread's location in the domain of execution. For example, the thread at location <1,1> in the domain would write to location <1,1> in each bound memory segment. For these addresses to computed implicitly, the sizes of the bound memory segments must be the same and specified beforehand.

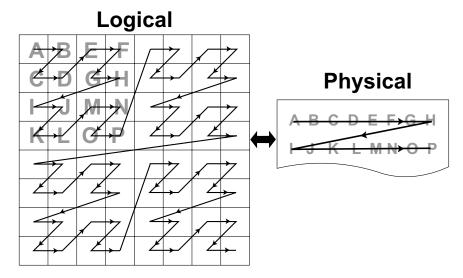

## 1.2.5.5 Memory Tiling

There are many possible physical memory layouts for data streams. AMD stream processors can access memory in a tiled or in a linear arrangement.

- Linear A linear layout format arranges the data linearly in memory such that element addresses are sequential. This is the layout that is familiar to CPU programmers. This format must be used for global buffers.

- Tiled A tiled layout format has a pre-defined sequence of element blocks arranged in sequential memory addresses (see Figure 1.11). Translating from user address space to the tiled arrangement is transparent to the user. Tiled memory layouts provide an optimized memory access pattern to make more efficient use of the RAM attached to the stream processor. This contributes to lower latency.

Figure 1.11 One Example of a Tiled Layout Format

## 1.2.6 Host-to-Stream Processor Communication

The following subsections discuss the communication between the host (CPU) and the stream processor. This includes an overview of the PCI Express<sup>®</sup> bus, processing API calls, and DMA transfers.

#### 1.2.6.1 PCI Express Bus

Communication and data transfers between the system and the stream processor occur on the PCI Express® (PCIe®) channel. AMD Stream Computing cards use PCIe 2.0 x16 (second generation, 16 lanes). Generation 1 x16 has a theoretical maximum throughput of 4 GBps in each direction. Generation 2 x16 doubles the throughput to 8 GBps in each direction. Actual transfer performance is CPU and chipset dependent.

Transfers from the system to the stream processor are done either by the *command processor* or by the *DMA engine*. The stream processor also can read and write system memory directly from the SIMD engine through kernel instructions over the PCIe<sup>®</sup> bus.

## 1.2.6.2 Processing API Calls: The Command Processor

The host application does not interact with the stream processor directly. A driver layer translates and issues commands to the hardware on behalf of the application.

Most commands to the stream processor are buffered in a command queue on the host side. The command queue is flushed to the stream processor, and the commands are processed by it, only when a kernel program is executed. Flushing sends the current state of the command queue to the stream processor. There is no guarantee as to when commands from the command queue are

executed, only that they are executed in order. Unless the stream processor is busy, commands are executed immediately.

Command queue elements include:

- Kernel execution calls

- Kernels

- Constants

#### 1.2.6.3 DMA Transfers

Direct Memory Access (DMA) memory transfers can be executed separately from the command queue using the DMA engine on the stream processor. DMA calls are executed immediately; and the order of DMA calls and command queue flushes is guaranteed.

DMA transfers can occur asynchronously. This means that a DMA transfer is executed concurrently with other system or stream processor operations. However, data is not guaranteed to be ready until the DMA engine signals that the event or transfer is completed. The application can query the hardware for DMA event completion. If used carefully, DMA transfers are another source of parallelization.

The thread processors handle non-DMA memory transfers.

## 1.2.7 Stream Processor Scheduling

Stream processors are very efficient at running large numbers of threads in a manner transparent to the application. Each stream processor uses the large number of threads to hide memory access latencies by having the resource scheduler switch the active thread in a given thread processor whenever the current thread is waiting for a memory access to complete. This time multiplexing is also used to hide the latency of stream core operations resulting from pipelining. Hiding memory access latencies requires that each thread contain a large number of calculations.

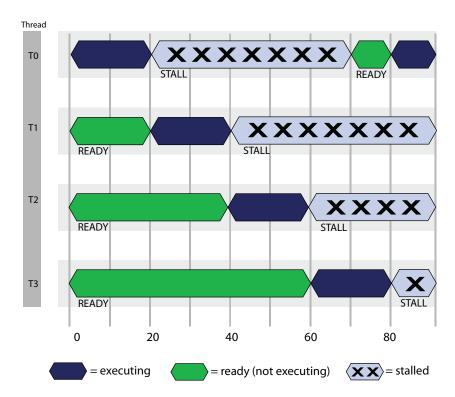

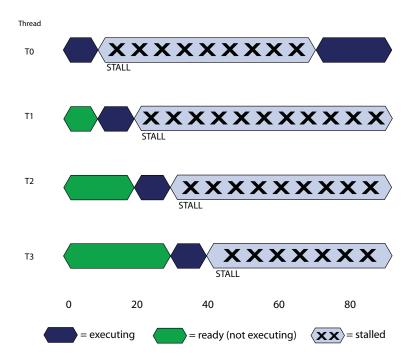

Figure 1.12 shows the timing of a simplified execution of threads in a single thread processor. At time 0, the threads are queued and waiting for execution. In this example, only four threads (T0...T3) are scheduled for the processor. The hardware limit for the number of active threads is dependent on the resource usage (such as the number of active registers used) of the program being executed. An optimally programmed stream processor typically has thousands of active threads.

Figure 1.12 Simplified Execution Of Threads On A Single Thread Processor

At runtime, thread T0 executes until cycle 20; at this time a stall occurs due to a memory fetch request. The scheduler then begins execution of the next thread, T1. Thread T1 executes until it stalls or completes. New threads execute, and the process continues until the available number of active threads is reached. The scheduler then returns to the first thread, T0.

If the data thread T0 is waiting for has returned from memory, T0 continues execution. In the example in Figure 1.12, the data is ready, so T0 continues. Since there were enough threads and stream core operations to cover the long memory latencies, the thread processor does not idle. This method of memory latency hiding helps the stream processor achieve maximum performance.

If the data for thread T0 is not ready, the thread processor waits until thread T0 is ready to execute, even if there are other threads ready to execute, as demonstrated in Figure 1.13.

Figure 1.13 Thread Processor Stall Due to Data Dependency

The causes for this situation are discussed in the following sections.

## 1.3 Performance

This section discusses performance and optimization when programming for stream processors.

## 1.3.1 Analyzing Stream Processor Kernels

Kernels must be compiled to native hardware instructions. The AMD GPU ShaderAnalyzer (Figure 1.14) can provide the instruction set architecture (ISA) disassembly. This tool can show the instructions executed on the hardware, as well as the number of active registers used.

Looking at the ISA of an example program (see Figure 1.14), instructions are grouped into *clauses*. A clause is a set of sequential instructions that executes without *pre-emption*. There are three types of instructions: stream core, local memory fetch, and memory read/write. Clauses can only contain one type of instruction. Only one clause is loaded onto a SIMD engine or the local memory fetch units at a time; however, multiple clauses can be executed in parallel because each SIMD can run a different clause.

Figure 1.14 shows an implementation of matrix multiply using Brook+. The resulting ISA code contains eight clauses (00...07). Of these, 00, 02, 03, and 05 are stream core clauses; 01 and 06 are branch clauses; 04 is a fetch clause; and 07 is a memory write clause. There are seven stream core instructions and two fetch instructions.

Performance 1-21

Figure 1.14 AMD GPU ShaderAnalyzer Output

## 1.3.2 Estimating Performance

Estimating the theoretical performance of a kernel running on a stream processor is important because it helps developers identify and remove performance bottlenecks.

The last section shows the components of the instructions of a kernel. This is needed for the theoretical estimates. The other information needed consists of:

- Number of stream cores

- Number of local memory fetch units

- Memory bus size

- Engine clock frequency

- Memory clock frequency

For the ATI Radeon™ 3870 GPU (RV670) stream processor, the number of thread processors that execute the VLIW instructions is 64. The memory bus size is 256 bits. The engine and memory clocks are dependent on the stream processor (see the technical specifications for a specific stream processor for the rates). A typical ATI Radeon™ HD 3870 graphics card, which uses the RV670

stream processor, has an engine clock of 775 MHz and a memory clock of 1125 MHz.

A kernel with only stream core instructions has a theoretical performance of:

The number of threads is the size of the domain of execution. Taking the ATI Radeon™ 3870 GPU (RV670) stream processor as an example, a one stream core instruction kernel with a domain of two million threads theoretically executes in:

$$\frac{\text{(2M threads)} \times \text{(1 stream core instruction/thread)}}{\text{(64 stream core instructions / clk)}} = 0.04 \text{ ms}$$

A kernel with only a single fetch instruction has a theoretical performance of:

$$\frac{\text{(\# threads) x (\# fetch instructions/thread)}}{\text{(fetches / clk) x (3D engine clock)}} = \frac{2M \times 1}{16 \times 775 \text{ MHz}}$$

$$= 0.16 \text{ ms}$$

Local memory fetch units operate on the engine clock; thus, the 3D engine speed was used in the calculation above.

Memory performance estimation is based on the total amount of data being read from, and written to, memory per thread:

A simple copy kernel (one byte in and one byte out) with a domain of two million threads has a theoretical memory performance of:

$$\frac{\text{(2M threads) x (16 bits)}}{\text{(256 bits) x (1125 MHz x 2DDR)}} = 0.056 \text{ ms}$$

All hardware units run in parallel. Thus, the theoretical performance is the worst case of the three estimates. In the example of a kernel with one stream core instruction, one fetch instruction, and one byte input and output, the theoretical runtime would be 0.16 ms. This kernel is considered fetch-bound because the local memory fetch units are the bottleneck.

Note that the theoretical performance serves only as a guide. As kernel complexity increases, the ability to model the hardware becomes more difficult. Also, the above memory performance model is based on ideal (sequential) memory access patterns. Section 1.3.3, "Additional Performance Factors" explores additional factors which affect performance.

## 1.3.3 Additional Performance Factors

This section describes potential factors that can impact kernel performance on the stream processor.

Performance 1-23

## 1.3.3.1 Register Usage

The number of active wavefronts depends on the active register usage of a kernel. This can be determined from the ISA disassembly provided by the GPU ShaderAnalyzer or other tools. Compilers try to optimize for the best register use; however, manual optimizations often can yield better results. Optimizing register counts yields performance gains through better memory latency hiding. However, a stream-core-bound kernel is bound by the peak stream core performance, even if many threads are active simultaneously.

When too many active registers are used, the stream processor places excess registers into memory. If this happens, performance is significantly impacted.

#### 1.3.3.2 Domain Size

Stream processors have deep pipelines and many parallel execution units. Thus, stream processors require a large number of threads to be executed for maximum efficiency. This, however, is highly application workload dependent.

As mentioned in Section 1.2.2, "Thread Processing," page 1-14, and Section 1.2.4, "Thread Creation," page 1-15, threads are executed on the hardware in wavefronts and quads. It is recommended that, at a minimum, domains have a height or width of a multiple of two.

#### 1.3.3.3 Stream Core to Fetch Instruction Ratio

One often-cited kernel statistic is the stream core-to-fetch (instructions) ratio. As shown in Section 1.3.2, "Estimating Performance," page 1-22, there must be enough stream core instructions to hide the fetch latencies. This consideration is not intended for initially developing kernel programs, but rather for cases where the performance of the kernel program is not as expected. This ratio is device-specific.

## 1.3.3.4 Memory Fetch Instructions

Since there are normally significantly more stream core resources than memory fetch resources, it is important that the developer keep memory fetch instructions to a minimum. Every memory fetch instruction takes at least one cycle. If the kernel is designed to fetch from consecutive data locations, then vector fetches can make more efficient use of the fetch resources. For example, a kernel can issue a fetch for a float4 type in one cycle versus four separate float fetches in four cycles. Sometimes, the compiler consolidates fetches; however, if there is math involved in calculating addresses, the compiler might not be able to perform the optimization for the developer. One solution is to explicitly load data into registers as a first step (prefetching), rather than calling for fetches in the code as needed.

#### 1.3.3.5 Thread Processor Use

Most developers are used to programming with scalar operations. The compiler attempts to parallelize kernels into VLIW instructions for the developer. However,

if instructions are highly dependent on each other, the VLIW might have low occupancy; then, the thread processors are under-used. One optimization is to vectorize not just fetches, but also threads. This is done by combining multiple threads into a single thread and writing out multiple results with a vector data type, such as float4.

Since threads can write out up to eight vector types, it is possible to do much more work per thread by vectorizing them. This not only minimizes the number of stream core operations, but also might reduce the number of memory fetches.

Further optimization is achieved by having data ready in registers, since reading from registers is faster than fetching data from the cache.

#### 1.3.3.6 Memory Access Patterns

The hardware is optimized for sequential memory access within, and between, threads. This is due to the way the DRAM and the cache are set up. On a memory fetch, an entire cache line is returned, which accelerates the next fetch in the sequence. Also, tiled memory works with thread rasterization (discussed in Section 1.2.4, "Thread Creation," page 1-15) to accelerate memory fetches and increase performance. This is because consecutively created threads are likely to have their fetches in the cache already, leading to less stalling in the thread processor.

When a stream is formatted with a linear layout, performance can be negatively affected. More cache lines might be fetched to service the reads than from a tiled format.

Random accesses into memory, and fetch patterns that consistently access the same memory bank and channel (all fetches going to the same physical memory chip), cause the greatest degradation in memory performance.

Since memory access patterns can throw off performance estimates, it is possible to isolate the stream core and fetch performance by reducing input stream sizes to just one element. This determines if a kernel is memory bound or not, since by reducing the input stream size, the input stream data remains in the cache. This technique only works on fetches that do not depend on a value written from the kernel.

#### 1.3.3.7 Command Processor

Since the command queue is flushed on every execution of a stream processor program, short kernels and small domains can cause many gaps to be inserted in the execution pipeline.

Having too large of a command queue also can affect performance. The buffer in the command processor has a finite size. Thus, very large command queues must be repackaged into smaller queues. As a result, extra overhead can occur when handling very large command queues.

Performance 1-25

#### 1.3.3.8 Bus Transfers

Ideally, total stream processor time measures not only the kernel compute time, but also the transfer of data over the system bus between the host and the stream processor, or between multiple stream processors. Bus transfers are highly platform dependent, so running the application on another system sometimes can be the quickest attempt at optimization.

Another method for improving performance is to hide the data transfer time with other work. Since the stream processor can read and write data directly from host memory, for some applications it might be better to leave the input or output streams in host memory and avoid any explicit bus transfer steps.

Since DMA transfers are asynchronous, they can be hidden through other CPU or stream processor computations. This can be achieved by subdividing a large domain and transferring data for subsequent kernels during prior kernel executions. However, it is important to ensure that asynchronous transfers have completed before a kernel tries to use transferred data for computation.

# Chapter 2 Brook+ Programming

This chapter is for developers using the Brook+ language to develop applications for AMD stream processors. See *Brook+ Language Specification* for a complete development guide and language specification. Also, see Section 3.1, "Introduction," page 3-1, for an introduction to the stream processor architecture.

# 2.1 Prerequisites

The following subsections detail the system requirements, the installation procedure, and the steps for enabling syntax highlighting in Visual Studio.

# 2.1.1 System Requirements

Installing Brook+ SDK (compiler, runtime, and sample applications) on your system requires:

- Windows XP 32-bit, XP 64-bit (both SP2).

- Vista 32-bit, Vista 64-bit (both SP1).

- All ATI Radeon HD 2000+ series, ATI Radeon HD 3870, ATI Radeon HD 4850, ATI Radeon HD 4870, ATI FireGL V7700, and AMD FireStream 9170 graphics cards.

- Visual Studio 2005 (VS8) and 2008 (VS9) Brook+ platform and samples are in VS8.

- Linux (both 32-bit and 64-bit): Red Hat Enterprise Linux 5.1, SUSE Linux Enterprise Server (SLES) 10 SP1.

# 2.1.2 Installation

Access http://ati.amd.com/technology/streamcomputing/sdkdwnld.html, and download the following files:

- ATI Catalyst<sup>™</sup> Driver Brook+ and CAL require ATI Catalyst version 8.1 or above. Choose the version of ATI Catalyst that matches your operating system.

- AMD Stream SDK v1.2-beta (Win XP 32) or AMD Stream SDK v1.2-beta (Win XP 64) - Choose the one that matches your operating system. The executable file installs the Brook+ compiler and runtime, as well as the AMD CAL software.

- GPU ShaderAnalyzer (optional) This is a tool for analyzing the performance

of pixel and vertex shaders on ATI Radeon graphics cards. It gives you

accurate performance estimates for shaders and lets you view disassembly

of the generated hardware shader. It can be used as a GUI tool for

interactive tuning of shaders, or, in command line mode, to generate detailed

reports. It supports DirectX9, DirectX10 & OpenGL.

- ACML (optional) The AMD Core Math Library.

The AMD Stream SDK compressed file contains a setup executable that installs the Brook+ SDK and the CAL SDK. This package contains the following files:

| File and location        | Description                                 |

|--------------------------|---------------------------------------------|

| <brookroot>\</brookroot> | Install directory                           |

| doc\                     | Documentation                               |

| platform\                |                                             |

| brook.sln                | Visual Studio solution                      |

| brcc\src\                | Brook+ Compiler source                      |

| include\                 | Brook+ include files                        |

| runtime\src\             | Runtime source                              |

| utils\                   | Misc. make files and tools                  |

| samples\                 | Brook+ sample apps                          |

| sdk\                     | SDK tree                                    |

| bin\                     |                                             |

| brcc.exe                 | Release build of the Brook+ compiler        |

| brcc_d.exe               | Debug build of the Brook+ compiler          |

| include\                 | Brook+ include files                        |

| lib\                     |                                             |

| brook.lib                | Release build of the Brook+ runtime library |

| brook_d.lib              | Debug build of the Brook+ runtime library   |

| utils\                   |                                             |

| vs8_syntaxHighlighting\  | Brook+ syntax highlighting files            |

#### To install the files:

- 1. Install AMD CAL (Compute Abstraction Layer) using the CAL installer, and follow the prompts.

- a. The installer adds the location of the CAL  $\tt dlls$  to the path. The default location is:

```

C:\Program Files\AMD\<CAL SDK>\lib\xp32

```

b. The installer adds the environment variable CALROOT and sets it to the CAL install path. The default value is:

```

CALROOT = C:\Program Files\AMD\<CAL SDK>

```

- 2. Install Brook+ using the provided installer, and follow the prompts.

- a. The installer adds the environment variable BROOKROOT and sets it to the Brook+ install path. The default value is:

```

BROOKROOT = C:\Program Files\AMD\<BROOK+ SDK>\

```

# 2.1.3 Syntax Highlighting in Visual Studio

To enable syntax highlighting for .br files in Visual Studio:

- If not already present, copy usertype.dat in <BROOKROOT>\utils\vs8\_syntaxHighlighting\ to <Visual Studio 8>\Common7\IDE\.

Otherwise, append the contents of usertype.dat onto <Visual Studio 8>\Common7\IDE\usertype.dat.

- Open Visual Studio 8, and select Tools→Options. Expand Text Editor and select File Extension. Enter br in the Extension box, choose your favorite editor, and click Add then OK to close window.

- 3. Close Visual Studio 8; then, restart this program.

See the associated readme file (located in vs8\_syntaxHighlighting\) for more information.

# 2.2 A Sample Application

Brook+ comes in two components: the compiler (brcc.exe) and the Brook+runtime libraries. Building an application consists of

- 1. Using the Brook+ compiler to compile the Brook+ source code into a C++ file. This contains the CPU and stream processor code.

- 2. Compiling the C++ file with the rest of the application and link it with the Brook+ runtime libraries.

The following subsections detail writing, building, executing, debugging, and logging a sample application.

## 2.2.1 Writing

The following is an example Brook+ source code for sum.br that adds two streams and outputs to a third. Brook+ source files normally are given a .br extension.

```

Sum.br

#include <stdio.h>

kernel void sum(float a<>, float b<>, out float c<>)

{

c = a + b;

}

```

```

int main(int argc, char** argv)

int i, j;

float a<10, 10>;

float b<10, 10>;

float c<10, 10>;

float input_a[10][10];

float input_b[10][10];

float input_c[10][10];

for(i=0; i<10; i++)

for(j=0; j<10; j++)

input_a[i][j] = (float) i;

input_b[i][j] = (float) j;

}

streamRead(a, input_a);

streamRead(b, input_b);

sum(a, b, c);

streamWrite(c, input_c);

for(i=0; i<10; i++)

for(j=0; j<10; j++)

printf("%6.2f ", input_c[i][j]);

printf("\n");

return 0;

}

```

Brook+ code is very similar to C/C++. Note the following limitations.

First, brcc functions like a C compiler; thus, programs must adhere to standard C constructions (for example: variables are declared at the beginning of code blocks). The Brook+ compiler has no built-in preprocessor. If the kernel code uses preprocessor directives, the Brook+ file must be processed by a preprocessor before it is passed to the Brook+ compiler. The Brook+ compiler reports a problem when there is a preprocessor directive inside the kernel code, but passes preprocessor directives in non-kernel code to the C++ compiler invoked in the second step of the compilation.

For more complex applications, carefully partition the C code and the Brook+code into manageable, easily maintainable sections. So, instead of using main, a function can be declared there and called from a C/C++ source file.

#### 2.2.1.1 Kernels

From the example on page 2-3:

```

kernel void sum(float a<>, float b<>, out float c<>)

{

c = a + b;

}

...

sum(a, b, c);

```

Kernels are functions that run on the stream processor. The kernel is invoked on every element of the stream. Kernels are executed by calling them, just as in C with the actual parameters.

Kernels are written like C, but with some extensions and limitations (see the *Brook+ Language Specification* for a complete listing). In the following example, a and b are input streams, and c is the output stream. Streams use angle brackets. In this situation, the API automatically handles stream addressing.

#### 2.2.1.2 Streams

From the example on page 2-3:

```

float a<10, 10>;

float b<10, 10>;

float c<10, 10>;

```

Streams are created using angle brackets (rather than square brackets used for arrays in C/C++). The hardware natively supports only 1D arrays up to 8192 elements, and 2D arrays up to 8192·8192 elements, where an element is the stream data type (for example: float4). Higher dimensions and larger sizes have limited support through address virtualization at compile time (possibly affecting the performance). For example, a 1D array can be virtualized to 64M (8192x8192) elements. See Section 2.2.2, "Building," page 2-6, for enabling address virtualization; also see Section 4.1 of the *Brook+ Language Specification* for more details.

#### 2.2.1.3 Handling Streams

From the example on page 2-3:

```

streamRead(a, input_a);

streamRead(b, input_b);

...

streamWrite(c, input_c);

```

Streams cannot be accessed directly by the application. Data must be copied between streams and memory using streamRead() and streamWrite().

# 2.2.2 Building

Use the following steps to build:

Step 1. Compile with brcc.exe, which can be found in <BROOKROOT>\sdk\bin\

In the example on page 2-3, use:

brcc.exe -o sum sum.br

This compiles the Brook+ file sum.br and generates a C++ file, sum.cpp. (see Figure 2.1)

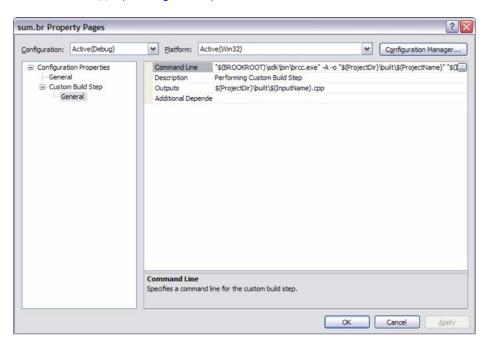

Figure 2.1 Compiling a Brook+ File and Generating a C++ File

In Visual Studio, you can add the Brook+ compilation step as a custom build event for the Brook+ file. Right-click on the Brook+ file in the project, and select Properties.

In *Command Line*, add the compiler command. For *Outputs*, add the location of the generated C++ file. You then can add the generated C++ file to the project. Subsequent Brook+ compiles overwrite the existing C++ file.

Brook+ header files are located in <BROOKROOT>\sdk\include.

- 4. Compile the application with the generated C++ files.

To use a makefile, see <BROOKROOT>\samples\util\build for examples.

# 2.2.3 Executing

If the installation was followed correctly and the build was successful, run the executable. If the application does not run, then at least one path has not been set.

# 2.2.4 Debugging

When debugging an application, debugging happens on the generated C++ source, not on the original Brook+ source. For a complete example, see Section 2.4, "Example of Generated C++ Code for sum.br," page 2-12.

There is no hardware debugging of stream kernels (for example: \_\_sum\_cal\_desc); it is not possible to step through the kernel code. The kernel inputs and outputs can be inspected (before a streamRead and after a streamWrite). Kernels can be written so that intermediate data can be output to streams and inspected.

Alternatively, kernels can be stepped through and debugged as usual using the CPU emulation mode (for example: \_\_sum\_cpu and \_\_sum\_cpu\_inner). To enable CPU emulation, create and set the environment variable:

```

BRT RUNTIME = cpu

```

To return to the CAL backend, either delete the environment variable or set it to:

```

BRT_RUNTIME = cal

```

# 2.2.5 Logging

Brook+ can log various internal states to a log file. Use the following steps to enable this feature:

- Step 1. Invoke the preprocessor macro #define BROOK\_LOGGER\_ENABLED = 1 (currently, this is the default, set in logger.hpp).

- Step 2. Add an environment variable BRT\_LOG\_FILE with the log file name.

Optionally, set the environment variable BRT\_LOG\_MASK to a decimal integer representing a bitmask of the types of information to log. The values

corresponding to each log type are listed in logger.hpp. For example, to enable logging of function entries and warning messages, set BRT LOG MASK to 5.

Similarly, the compiler execution can be logged by setting the corresponding environment variables BRCC\_LOG\_FILE and BRCC\_LOG\_MASK. Note, however, that compiler logging coverage is incomplete.

Logging is enabled only in the debug versions of the tools. It is disabled in the release versions for performance reasons.

# 2.3 Included Samples

The Brook+ folder contains sample applications that can be built using the included makefiles or the included Visual Studio solution file <BROOKROOT>\samples\samples.sln.

Release builds of the samples are pre-built and located in: <BROOKROOT>\samples\bin\.

# 2.3.1 Simple Matrix Multiply Example

This example is a standard matrix multiply. The code presented here is excerpted from the simple matmult example found in the samples directory.

```

//! C = A * B

//! \param Width The value for which the loop runs over the matrices

//! \param A Input matrix A(MxK)

//! \param B Input matrix B(KxN)

//! \param result Output matrix(MxN)

//!

kernel void

simple_matmult(float Width, float A[][], float B[][], out float result<>)

// vPos - Position of the output matrix i.e. (x,y)

float2 vPos = indexof(result).xy;

// index - coordinates of A & B from where the values are fetched

float4 index = float4(vPos.x, 0.0f, 0.0f, vPos.y);

// step - represents the step by which index is incremented

float4 step = float4(0.0f, 1.0f, 1.0f, 0.0f);

// accumulator - Accumulates the result of intermediate calculation

// between A & B

float accumulator = 0.0f;

// Running a loop which starts from

// (0, vPos.y) in A and (vPos.x,0) in B

// and increments the 'y' value of A and the 'x' value of B

// which basically implies that we're fetching values from

// the 'vPos.y'th row of A and 'vPox.x'th column of B

float i0 = Width;

while(i0 > 0)

// A[i][k] * B[k][j]

accumulator += A[index.zw]*B[index.xy];

index += step;

i0 = i0 - 1.0f;

}

```

```

// Writing the result back to the buffer

result = accumulator;

}

int main(int argc, char** argv)

{

float A<Height, Width>;

float B<Width, Height>;

float C<Height, Height>;

float* inputA;

float* inputB;

float* output;

...

streamRead(A, inputA);

streamRead(B, inputB);

...

simple_matmult((float)Width, A, B, C);

...

streamWrite(C, output);

...

}

```

Starting at main, three streams are created representing the input (A and B) matrices and the output matrix (streams are used to represent a matrix). Then, three corresponding memory buffers are declared (inputA, inputB, and inputC).

Next, streamRead() copies data from inputA to stream A, and data from inputB to stream B.

The line simple\_matmult((float)Width, A, B, C); binds the kernel to the size parameter Width, the input streams A and B, and the output stream C; this also triggers execution of the kernel by the stream processor. In a simple matrix multiply operation, the kernel reads in one row vector from one matrix and a column vector from another matrix; it applies a dot product to the two vectors, and writes out the result. In the example above, the kernel is invoked at each data location in the output stream. The kernel:

- 1. loops over the row of matrix A,

- 2. loops over the column of matrix B,

- 3. fetches a value from each matrix, and

- 4. accumulates the values.

A feature used by this kernel is vector data types (float2 and float4). Brook+ can support data types of up to four elements. Elements can also be accessed in any combination. This is also known as *swizzling*.