# AN-971

# LVDS 技術の概要

Application Note 971 Syed B. Hug John Goldie 1998年7月

# はじめに

現在成長しているハイエンド・プロセッサ、マルチメディア、バーチャル・リアリティ、ネットワーキングなどの分野では、以前より広い帯域幅が求められています。しかし一対一フィジカル・レイヤ・インタフェースでは、画像情報を必要なデータレートで扱うことができませんでした。速い伝送能力、現在入手できる製品よ注低消費電力、フィジカル・レイヤ・ボトルネックを解消する経済的な解決法など、いくつかの大きな問題が存在するからです。RS-422、RS-485、SCSIなどのようなデータ伝送の規格のすべてが、媒体に生データを伝送するのに最も著しい自己制限を持っています。でも、もう大丈夫。LVDS(小振幅差動信号)はボトルネックを解決し、一方で広いアプリケーションで使用できる高速

( > 155.5Mbps) かつ、低消費電力の汎用インタフェース標準です。

本アプリケーション・ノートは LVDS 技術の主要な利点について 説明します。ここでは、DS90C031 (LVDS 5V 4 回路入り差動出 カライン・ドライバ ) と DS90C032 (LVDS 5V 4 回路入り差動入力 ライン・レシーバ ) がキーポイントを説明するために使われています。 ナショナル セミコンダクター社は本アプリケーション・ノートの 発行時点 (1998 年) で 50 を超える LVDS デバイスを製品化して います。 詳細な仕様は LVDS の各データシートを参照してください。

### 規格の概要

LVDS を定義する二つの主要産業規格があります。そのうち広く使われている規格は TIA によって規定されている電気レイヤの汎用的な規格です。この規格は ANSI/TIA/EIA-644 として知られています。一方、スケーラブル・コヒーレント・インターコネクトと名付けられた IEEE (電気電子技術者協会)規格は、個別のアプリケーションを規定した規格です。

# ANSI/TIA/EIA-644

Data Transmission Interface Committee TR30.2 に属する規格です。ドライバ出力とレシーバ入力の特性を定義しています。機能の使用と、またはプロトコルは TIA 規格の範囲には含まれていません。それは推奨される 665 Mbps の最大データレートと、損失の少ない媒体における1.923Gbpsの理論上の最大データレートを明記しています。ただし、最大データレートはアプリケーション(求められる信号インテグリティ)とデバイスによって決まります。 LVDSを使用したインタフェースは、近い将来、500Mbps から 1.5Gbpsの範囲で動作すると見込まれます。 この規格は伝送媒体に関して最低限の仕様も規定しています。また、故障状態でのレシーバのフェイル・セーフ動作や、マルチ・レシーバ動作などの回路構成についても論じています。ナショナル セミコンダクター社はこの規格に関する委員会の書記をつとめています。

## **IEEE 1596.3 SCI-LVDS**

SCI は IEEE 規格 SCI (Scalable Coherent Interface) 1596-1992 の中で、通常差動 ECL インタフェースとされています。しかしこれは、高速データレートの要求を扱うだけで、低消費電力については着目していません。したがって、SCI-LVDS は SCI の一種として定義され、IEEE1596.3 規格で記載されています。SCI-LVDS

は高速、低消費電力フィジカル・レイヤ・インタフェースのための信号レベルを記述しています。また SCI データ伝送に使われるパケット・スイッチングに対するエンコードを定義しています。 パケットは 2 バイト (doublet) シンボルで構成されます。 これは基本的な 16 ビット・シンボルサイズです。 明記されている媒体はありませんが、そのデータレートは 1, 4, 8, 16, 32, 64, ....bits シリアルまたはパラレル伝送に基づいて 500MT/s のオーダにできます。

SCI-LVDSは制限された環境での超低消費電力データ伝送に対するラムリンクもサポートします。IEEE 1596.3 規格は 1994 年 3 月に承認されました。 ナショナル セミコンダクター社はこの規格委員会の議長をつとめています。

SCI-LVDS は TIA バージョンに類似していますが、電気的要件と 負荷条件の一部が異なっています。 両規格ともに、ドライバの出 カレベル、レシーバのスレッショルド、データレーHはほぼ同じです。 ただし、TIA バージョンのほうが汎用的で、多様なアプリケーショ ンへの適用を意図したものとなっています。

### LVDS(小振幅差動信号)

National Semiconductor

LVDS 技術は差動データ伝送方式を使用しています。この差動 伝送方式は、コモンモード・ノイズに対する感度を少なくするシグナルエンド方式を超えたかなりの利点を持っています。 内部接続 に関連したノイズはレシーバが同相変調とみなし取り除かれます。このレシーバは差動電圧だけに応答します。

LVDS 技術は+5V のような電源電圧の仕様に依存しません。これは+3.3V、さらには+2.5V のような低電源電圧へ容易に移行する方法があることを意味していますが、扱える信号レベルと性能はかわりません。ECL や PECL のような技術は電源電圧にかなり依存しています。 大掛かりな再設計なしでまたシステム基盤上での混合電圧操作(+5V/+3.3V)の心配なく、低電源電圧での動作を要求されるアプリケーションにとって、LVDS の持つ特徴はとても好ましいものといえます。

高データレート、低消費電力を達成し、EMIの影響を減少させるためには、信号レベルを減少させなければなりません。DS90C031/C032 チップセットのデータレート上の制限は主にLVDSドライバを駆動させる技術に依存しています。LVDS技術が駆動できる帯域幅は、損失の少ない媒体でGbpsの範囲で持っています。500~1000Mbpsのデータレートが可能であり、データレートに対する制限は主に駆動された媒体に依存します。

### 信号レベル

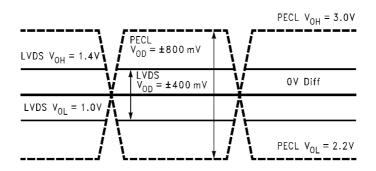

名前が示すとおり、他の産業用データ伝送規格と比較して、LVDS の特徴は低電圧振幅にあります。信号レベルは Figure 1 に示してあり、PECL レベルとの比較としても、Figure 1を参照できます。低いスイング幅の利点によって、一対一のアプリケーションで LVDS は高帯域幅を達成します。ナショナル セミコンダクター社は Bus LVDS と呼ぶ新しいデバイス・ファミリを製品化しました。このファミリは、従来一対一アプリケーションを前提とした LVDS をマルチポイント・アプリケーションにまで拡大するもので、詳細は別のアプリケーション・ノートで説明しています。 Bus LVDS は、電圧振幅は LVDS と同じですが、マルチポイント・アプリケーションで必要となる二重終端をサポートするために電流駆動能力が高められています。

TRI-STATE® はナショナル セミコンダクター社の登録商標です。

FIGURE 1. PECL vs LVDS Signal Swing

低いスイング電圧を利用することなしに、高データレートでかつ低消費電力は供給できません。LVDS の信号振幅は、Figure 1 に示すように、PECL レベルに比べて 50%も小さくなっています。従来の CMOS、TTL、PECL に比べて信号振幅が大幅に小さいため、EMI の大幅な抑制が実現されています。電流モード・ドライバ、緩やかな信号遷移、小さなスイッチング電流、真の差動データ伝送の採用も寄与しています。

### LVDS の終端

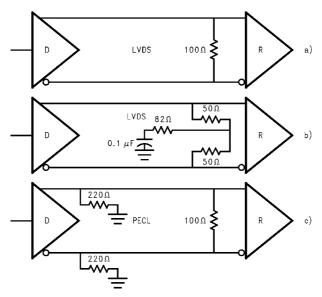

LVDS はその多くの特長をいかすために、定電流モード・ドライバを使用しています。DS90C031のための電流源の値は最大4.5mAです。この伝送媒体は反射を防ぐためにその媒体にあったインピーダンスで終端されなければなません。一般的に特性インピーダンスは100~120 であり、現行のケーブルにマッチしています。レシーバ入力で差動出力電圧(V<sub>OD</sub>)を発生させるために終端抵抗がレシーバの入力間に必要となます(Figure 2a 参照)。終端なしでのドライバからレシーバへのデータ伝送は推奨されません。LVDS の終端の簡素化は、多くのアプリケーションへの導入を容易にします。その場合、ドライバの出力間に1個の100 の終端をつけることとともに、寄生容量の影響を減少させるために表面実装用部品の使用が推奨されます。LVDS の終端では、その単純さゆえに、単一抵抗方式がもっとも広く用いられています。適切な終端は反射の問題を避けるだけでなく、好ましくない電界の放射を減少できます。

Figure 2B に示すように、ケーブル・ダンピング抵抗をコンデンサを介してグラウンドに接続する方法もあります。この方法は付加的な

コモンモード終端を与えます。 ただし回路が複雑となるためあまり 採用されていません。

ECL と PECL ではより複雑な終端を必要としますが、LVDS では 1 つの抵抗で解決できます。 Figure 2c に示すように PECL ドライバはドライバ出力間に 100 終端抵抗と各々のドライバ出力からグラウンドの間に 220 のプルダウン抵抗を必要とします。この終端方法は、単一抵抗による LVDS 終端に比べて、余分なプリント基板面積を必要としシステム・コストも高くなります。

### 同相電圧範囲

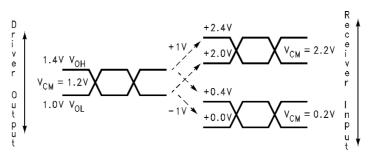

LVDS レシーバは、ドライバのグラウンドとレシーバのグラウンド間の グラウンド・シフトを最小± 1V 許容できます。 LVDS のドライバ・ オフセット電圧の代表値は+ 1.2V です。またグラウンド・シフト、 ドライバ・オフセット電圧、縦結合ノイズの合計は、レシーバ入力 端子から見て、レシーバ・グラウンドに対して同相電圧となる点に 留意してください。レシーバの同相電圧範囲は+0.2Vから+2.2V です。また推奨するレシーバの入力電圧範囲はグラウンドから + 2.4V までです。 たとえば、ドライバの  $V_{OH}$  が 1.4V、 $V_{OL}$  が 1.0V(ドライバ・グラウンドに対して)とし、 + 1V のグラウンド・シ フト(ドライバ・グラウンドがレシーバ・グラウンドから+ 1V 高い状 態)が存在する場合、レシーバ入力は、レシーバ・グラウンドを基 準として ( +  $2.2 \text{V V}_{\text{CM}}$ )、  $\text{V}_{\text{IH}}$  は+ 2.4 V (1.4 + 1.0)、  $\text{V}_{\text{IL}}$  は + 2.0V (1.0 + 1.0) となります。 同様に - 1V のグラウンド・シフト と同じドライバ・レベルのときは、レシーバ入力  $(+0.2V V_{CM})$  で、  $V_{IH}$  = 0.4V (1.4 - 1.0) と  $V_{IL}$  = 0.0V (1.0 - 1.0) の結果になぼ す。これは Figure 3 に図解しています。

FIGURE 2. a, b, c. Termination Schemes

FIGURE 3. Common Mode Voltage Range

### フェイル・セーフ

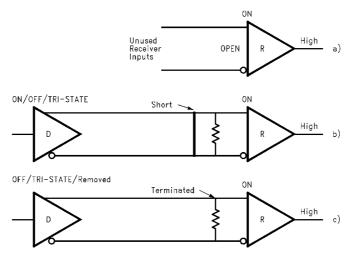

フェイル・セーフは、明らかな故障の際に、既知の論理状態 (HIGH) に出力をすることを保証するレシーバの機能です。フェイル・セーフはレシーバの入力がオープン、ショート、または終端されている場合に発生します。

DS90C032の4回路すべてのレシーバがアプリケーションによっては使用されないときがあります。この場合、使用しないレシーバ入力は開放に保ちます。フェイル・セーフ機能をサポートしていないレシーバを入力を開放のままで使用した場合 (Figure 4参照)、レシーバ・スレッショルドを超える外部ノイズが混入すると、出力がトリガされ伝送ラインで誤差が発生します。 DS90C032 はフェイル・セーフをサポートしているため、入力を開放にしてもレシーバ出力は HIGH の状態になります。

また、入力が短絡した場合も故障状態となります (Figure 4 参照)。 この状態では、レシーバ出力はロジック HIGH になりますが、不定 になることはありません。

もう一つ故障を引き起こす状態は、レシーバが100 の終端抵抗で終端された入力をパワーオンに保ったままドライバがTRI-STATE®、パワーオフまたは、ラインから取りはずした場合です。

レシーバ出力は上記に記載されたすべての状況下で論理 HIGH になります。 フェイル・セーフのサポートはレシーバに依存するので、使用する LVDS レシーバのデータシートを参照し、どのレベルのフェイル・セーフがサポートされているか確認してください。 レシーバの機能は、単純に、小信号 (mV) で短時間 (ps ~ ns) のパルスを、フルスイングの CMOS レベルへと増幅するだけで、そ

のほかの機能は持ち得ません。システム設計では、インターコネクトが拾うノイズが差動モードではなくコモンモードとなるように保証してください。平衡ケーブル、ノイズ源からのシールド、あるいはプリント基板上で密結合の差動トレースの採用などが対応策となります。

# パワーオン/オフ要件とハイ・インピーダンス・バス端子

アプリケーションによってはハイ・インピーダンス端子が必要となります。 ハイ・インピーダンス端子が必要となる理由は、 回路上に電源オフのデバイスが存在する場合に、ドライバ出力またはレシーバ入力の負荷が問題となるからです。 第1世代の LVDS デバイスは一対一アプリケーションでの使用を前提としていました。 この構成では、ドライバの電源がオフ、あるいはドライバがディスエーブルまたは未実装の場合に、リンクの動作は停止しコミュニケーション(伝送)は行われません。 つまり、デバイスのバス負荷は大きな問題ではありませんでした。 なお、 DS90C031/DS90C032 ファミリ・デバイスは、 バス端子に直接 ESD 保護回路が実装されています。ドライバがアクティブでレシーバがオフであっても、 出力電流は厳格に制限され、レシーバ入力でラッチアップ状態は起こりません。

ナショナル セミコンダクター社が提供する第二世代のデバイス (DS90LV031A/DS90LV032A) は、ハイ・インピーダンス・バス端子が必要な場合を含めて、より広範囲なアプリケーションへの適用を意図しています。このデバイス・ファミリの ESD 保護回路は、デバイスの電源がオフの場合に、ラインに対して負荷となりません。

デバイスがハイ・インピーダンス・バス端子をサポートしていることを確認するには、デバイスのデータシートの特徴リストや、レシーバ入力電流パラメータ、ドライバの出力リーク電流パラメータを参照してください。ナショナルの Bus LVDS ファミリ・デバイスは、マ

ルチドロップ・アプリケーションとマルチポイント・アプリケーションを サポートするために、ハイ・インピーダンス・バス端子を備えていま す。

FIGURE 4. a, b, c. Failsafe Operation

### 一対一構成

ドライバのトランジション・タイムが媒体の遅れ時間より生十分短いインタフェースにとって、内部コネクションに一点の負荷があると考えず負荷の分布を考えなければなりません。 伝送線路の分配要素は信号の質に大きな影響を与えます。

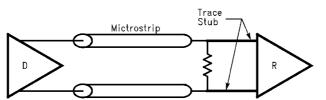

具体的には、伝送線路理論はドライバの遷移(立ち上が)または 立ち下がり)時間が信号遅延の4倍よりた短い場合は伝送媒体 を集中定数ではなく分布定数として取り扱わなければならないと しており、合わせて、インピーダンスの不連続とスタプに充分な注 意が必要です。 与えられたドライバに対し、 $t_r$  < 4  $t_d$  ( $t_r$  =ドライ バのライズ・タイム、 $t_d$  = 伝搬遅延時間 )または  $t_d$  <  $1/4t_r$  ならば、 このラインは損失のあるラインとして検討します。ドライバの t, がサ ブナノセコンドの範囲であれば、正確です。簡単な計算方法に ついてはこの規則で説明されます。 例えば DS90C031 ドライバは 代表値で t<sub>r</sub> = 350ps を持ち、FR-material の microstrip built は プリント基板のトレース 1 インチに対して t<sub>d</sub> = 147ps を持ちます。こ の値を使って計算した結果から(350 < 4\*147)、DS90C031ドラ イバで駆動した場合に、1 インチ長の FR-4 マイクロストリップは伝 送線路として振る舞うことがわかります。Figure 5 は終端抵抗とレ シーバ入力の間にスタブを含んでいます。この長さは1インチより 長くしてはなりません。またできる限り短く保つようにします。1 イン チまたはそれ以上にスタブが長いと、伝搬信号にスタブの末端の ハイ・インピーダンスが加えられ、信号の質を低下させます。 複 数の反射がノイズマージンを減らすリンギング、オーバーシュート、 アンダーシュートを引き起こしながらラインを伝わります。

DS90C031 の速い t, はドライバにより高い帯域幅を与えますが、それらのエッジ・レートで適切に扱われなければ、伝送線路の特徴がシステム基板上に突然現れます。 デバイスを最大限の能力で働かせるために、LVDS DS90C031 と LVDS DS90C032 は伝送ライン上で絶間なく伝送できる一対一構成で動作させます。 こうすれば、ライン上でのスタブの問題はなくなります。 媒体は遠いほ

うの末端でライン間を100 の終端抵抗で終端しなければなりません。100 の終端抵抗は特性インピーダンスをもつ 2 つの差動伝送ラインを終端し、また電流出力ドライバに対して差動電圧 (V<sub>OD</sub>)を与えます。 上記の状況下でドライバは 155.5Mbps (77.7MHz)以上の伝送速度で 10m のツイスト・ペア・ケーブルを駆動できます。 なお、ナショナルのそのほかの LVDS デバイスは、より高いデータレートでの動作に対応しています。 たとえば FAST LVDS ファミリ・デバイスは 400Mbps 動作をサポートしており、LVDS のチャネルリンク・ファミリ・デバイスは LVDS ライン上でさらに高速なデータレートで動作します。

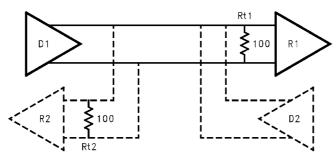

# 1 本のツイストペア・ケーブルによる双方向アプリケー ション

並列の二重終端負荷がドライバの出力振幅を大きく減衰させてしまうため、標準 LVDS を用いて 1 本のツイストペア・ケーブルで双方向伝送を行う方法は推奨されません。二重終端を採用するアプリケーションには Bus LVDS デバイスを使用してください (アプリケーション・ノート AN-1115 を参照)。

FIGURE 5. A Point-to-Point Configuration Using LVDS

FIGURE 6. Bi-Directional Application over One Pair of Twp

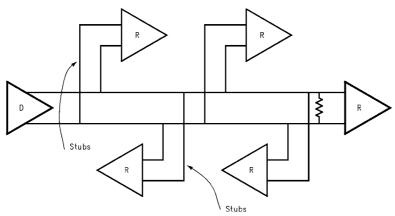

# マルチドロップ構成

マルチドロップ構成は (Figure 7を参照)、10個のレシーバまたはそれ以上をバスに接続することが可能です。各デバイスに電源が個別に与えられて、電源が与えられているレシーバへドライバからデータを伝送中に、他のレシーバの電源がオフになる可能性のあるアプリケーションでは、ハイ・インピーダンス・バス端子をサポートする LVDS レシーバを選択してください。また、ラインからレシーバまでのスタブが長いと反射あるいはインピーダンス不整合が起こる可能性があります。終端抵抗は1つのみ使用することと、終端抵抗はケーブル遠端に配置しなければならないことを確認してください。

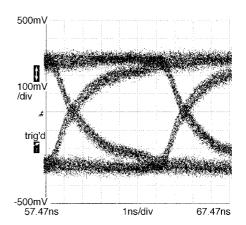

# ケーブルを通る信号の品質

伝送媒体の信号の品質を決定するための方法はたくさんあります。ビット・エラー・レート(BER)、ジッタ、アイパターン、ライズ・タイムとユニット・インターバルの比率は、設計者が信号の質を決めるときに用いられるそれぞれ異なった測定方法です。この記載の中でアイパターンがLVDSのレシーバとドライバの信号の品質を説明するために使用します。

アイパターンを作るために、 $511 (2^9 - 1)$  ビットの疑似ランダム・パルス (PRBS: Pseudo Random Bit Sequence) の NRZ データが LVDS のドライバ入力を駆動させるのに使用されます。 LVDS の

ドライバは LVDS レシーバと 10m、25 ペア、28AWG のツイストペア・ケーブル (SCSI グレード・ケーブル) でつなぎます。 アイパターンは 155.5Mbps で差動ドライバ出力を、またケーブルの未端でレシーバ入力をプロットします (Figure 8、9を参照)。

ランダム・データパターンはシンボル間干渉となる傾向があります。 パルス幅がだんだん短くなっていくにしたがってシンボル間干渉 から誤差が発生する高い可能性があります。 レシーバ入力への ビットの着信が次のビットが着信する前に、スレッショルドを横切る ための時間が十分でないため、その結果としてデータロスとなってしまいます。

511 ビット、または 2047 ビット (2<sup>11</sup>-1)、または 32767 ビット (2<sup>15</sup>-1) のパターン深さを持った PRBS をアイパターンの作成に使用しています。 アイパターンはシンボル間干渉の問題点を特徴づけるために使われます。アイパターンを使用して信号の品質を決定し、ジッタはクロスポイントを測定できます。 他の工業 規格、例えば SONET/SDH は信号の品質解析のためにアイパターンを明記しています。 LVDS 技術は 10m のケーブル 155.5Mbps のデータレートで広いアイパターン (目)表示ができます。 信号の品質のより詳しい説明については、アプリケーション・ノート AN-808 の "Long Transmission Line and Data Signal Quality"の項を参照してください。

FIGURE 7. Multi-Drop Configuration for LVDS

FIGURE 8. Eye Pattern at Driver Output

FIGURE 9. Eye Pattern at Receiver Inputs with 10m Cable

### まとめ

LVDS 技術は増加しつづけるデータレートの問題を解決し、一方で消費電力を減らす問題を解決します。またその技術は広く、テレコム、ルータ、インテリジェント・ハブ、LCD ディスプレイ、コピー、その他さまざまなアプリケーションに使用できます。 LVDS テクノロジーは、今日の回路が必要とする電力の配分要件を満たす最適なソリューションです。 複雑な終端を必要とせずに、一対一アプリケーションの高速インタフェースを簡単に実現できます。 消費電力が低くコア・プロセスとして独立した LVDS は、PLL やデジタル回路プロックとの集積によって、最適なインタフェース・シングルチップ・ソリューションを実現します。「ミリワットでメガビット」が求められる場合に、LVDS テクノロジーは最適なソリューションです。

# 参考文献

TIA 規格の問合せ先: Global Engineering Documents、http://global.ihs.com/

# 生命維持装置への使用について

弊社の製品はナショナル セミコンダクター社の書面による許可なくしては、生命維持用の装置またはシステム内の重要な部品として使用することはできません。

- 1. 生命維持用の装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与えると予想されるものをいいます。

- 2. 重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいいます。

# ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

フリーダイヤル

www.national.com/jpn/

0120-666-116

その他のお問い合わせはフリーダイヤルをご利用下さい。