# CHECK OT POSTcard

# POSTcard and PCI POSTcard

**Diagnostic Cards**

Version 2.0

User's Manual

SS

Unicore Software, Inc. 1538 Turnpike St. North Andover, MA 01845 Sales: 800/800-2467

Tech Support: 978/686-2204

# **Unicore Software, Inc**

#### **CheckIt POSTcard**

# POSTcard mini and PCI POSTcard

Power On Self Test (POST) System

Diagnostic Board

Version 2.0

User's Manual

Copyright 1994-1999 UNICORE Software, Inc. All rights reserved.

Unauthorized reproduction of this manual is strictly prohibited.

Unicore Software, Inc. does not make any claims as to the accuracy of the information contained in this manual and reserves the right to make changes to this information without prior notice.

Modular BIOS is a trademark of Award Software, Inc.

286, 386, and 386SX are trademarks of Intel Corporation.

Dysan is a registered trademark and AAD and DDD are trademarks of Xidex Corporation.

Hercules is a trademark of Hercules Computer Technology.

IBM, IBM PC, and IBM AT are registered trademarks and IBM PC/XT is a trademark of International Business Machines Corporation.

#### Warranty

The Unicore Software, Inc. CheckIt POSTcards<sup>™</sup> are warranted to be free from failures due to defects in material and workmanship for a period of 90 days following purchase. During this period, Unicore will, at its sole option, repair or replace at no charge a CheckIt POSTcard which in its opinion is defective.

This warranty applies only if the CheckIt POSTcard fails to function properly under normal use and within Unicore's specifications. If the failed CheckIt POSTcard has been modified without Unicore's consent or if the failure is a result of misuse, abuse, or misapplication, Unicore is under no obligation to repair or replace the failed CheckIt POSTcard.

You are responsible for properly packing the failed card for shipment and for the charges to ship the failed CheckIt POSTcard to Unicore and Unicore is responsible for charges to ship the repaired or replacement CheckIt POSTcard back to you.

Except as expressly provided for above, the CheckIt POSTcard and accompanying written material are provided as is without warranty of any kind, including the implied warranties of merchantability and fitness for a particular purpose. In no even will Unicore be liable for any direct, indirect, consequential or incidental damages arising from the use or inability to use such product even if Unicore has been advised of the possibility of such damages. Some states do not allow the exclusion or limitation of implied warranties or liabilities or consequential damages, so the above limitation or exclusion may not apply.

For information on obtaining service under this warranty, contact the Dealer from which the CheckIt POSTcard was purchased or contact Unicore directly.

Unicore Software, Inc. 1538 Turnpike Street North Andover, MA 01845 Tel: 978/686-6468

Fax: 978/ 683-1630

Technical Support: 978/686-2204

## **Table of Contents**

| Table of Contents          | 4                                     |

|----------------------------|---------------------------------------|

| Overview                   | 5                                     |

| POST Sequence              | 6                                     |

| Installation               | 7                                     |

| Troubleshooting            | 8                                     |

| Lights on the Card         | 9                                     |

| Frequently Asked Questions | 10                                    |

| System Motherboard         | 11                                    |

| BIOS-Specific POST Codes   | 12                                    |

| Shutdown or Reset Commands | 12                                    |

| Manufacturing Loop Jumper  | 13                                    |

| ACER                       | 13                                    |

| ALR                        |                                       |

| Ambra                      | 14                                    |

| AMI                        |                                       |

| Arche Technologies         |                                       |

| AST                        |                                       |

| AT&T                       |                                       |

| Award                      |                                       |

| Chips and Technologies     |                                       |

| Compaq                     |                                       |

| Dell                       |                                       |

| DTK                        |                                       |

| EurosoftFaraday A-Tease    |                                       |

| Headstart                  |                                       |

| HP                         |                                       |

| IBM                        |                                       |

| Landmark                   |                                       |

| Magnavox                   |                                       |

| MR BIOS.                   |                                       |

| Mylex/Eurosoft             |                                       |

| NCR                        | · · · · · · · · · · · · · · · · · · · |

| Olivetti                   |                                       |

| Packard Bell               |                                       |

| Philips/Magnavox/Headstart | 105 |

|----------------------------|-----|

| Phoenix                    |     |

| Quadtel                    |     |

| SuperSoft                  |     |

| Tandon                     |     |

| Tandy                      |     |

| Wyse                       |     |

| Zenith                     | 127 |

## **Overview**

The Unicore Software, Inc. CheckIt POSTcard is an 8-bit card that fits into a PCI or ISA slot on your computer. The CheckIt PCI POSTcard and POSTcard Mini will work on any computer (XT all the way to Pentium class machines) that support BIOS POST codes.

The two CheckIt POSTcards are ideal tools for troubleshooting PCs down to the component level, saving you hundreds of dollars along the way. These POSTcards use hexadecimal LED displays to indicate possible error codes.

## **POST Sequence**

The Power on System Test (POST) routines in the BIOS perform tests and initialize the circuitry on the motherboard peripheral adapter boards. The POST is reached by powering on the system or by using the Ctrl-Alt-Del reboot keystrokes.

The degree and path of the test/initialization will vary among different versions of the BIOS. The usual sequence is:

- CPU register checks.

- Setup the 8253/8254 timer for RAM refresh timing.

- Setup the DMA in RAM refresh on channel 0.

- Verify refresh is operating.

- Test low RAM 16-64k.

- Load interrupt vectors and assign a stack in the low RAM area.

- Initialize video and keyboard devices.

- Size and test remaining RAM.

- Initialize all COM, LPT and game ports.

- Initialize floppy disk system.

- Initialize hard disk system (AT class systems).

- Scan user ROM area.

- Call boot strap interrupt.

- Most ISA machines output their POST codes to port 80h with the exception of COMPAQ, which outputs all codes to I/O port 84h.

#### Installation

**WARNING!** The CheckIt POSTcard must always be installed with the arrow on the sticker on the back of the card facing the back of the computer. If you insert the card the wrong way, you will burn out its power cells and it will not function.

**Note:** The back of the computer is the end where all the cables for the monitor, keyboard, mouse, etc. are plugged in.

#### What slot to insert the cards into:

There are two different kinds of cards.

1. One is an ISA-style card that has an arrow. When you insert the card, make sure the arrow is pointing toward the back of the computer.

This is the **CheckIt ISA POSTcard** goes into an ISA slot. ISA slots are usually black and about 5.5" long. Insert the card so that the arrow on the sticker on the card is pointing toward the back of the computer. Put the card into the slot so that it is as close to the back of the computer as possible. See the picture below of this card and its notch in the bottom.

2. The other card has a notch in the bottom. This card is the CheckIt PCI POSTcard and it goes in a PCI slot. PCI slots are usually white and about 3.25" long. A PCI card has a notch in it that allows it to go into a PCI slot in only one direction. If your card does not have a notch, it should go into an ISA slot. See below.

Note: Shut your computer's power OFF when installing the CheckIt POSTcard.

#### To install:

- 1. Turn off your CPU, monitor, printer, and all other peripherals attached to the computer.

- 2. Disconnect all cables and power cords from the rear of your computer.

- 3. Remove the cover of your computer very carefully.

- 4. Carefully take the CheckIt POSTcard mini from its protective wrapping, making sure to handle the card by its edges.

- 5. To determine which slot to insert the card into, see the two choices listed above.

- 6. Position the card so that the arrow on the sticker on it points to the back of your computer. The back of the computer is where all the cables are plugged in.

**Note:** If your card does not have an arrow with a sticker on it, insert the card with the CheckIt label on the same side as the back of the computer.

- 7. Press the card firmly into the slot.

- 8. To run the card, turn on your computer.

The card's displays your computer's ROM BIOS POST codes as the computer boots up.

If the LED display stops on a particular code, look this code up under the appropriate BIOS manufacturer's table in the appendix to determine what the problem is.

For example, if you have a Award BIOS, go to that table's codes and look up the one on the card. For instance, 09 for a Award BIOS means the keyboard is not working, perhaps because it is not plugged in.

## **Troubleshooting**

If you are having problems installing the POSTcard, review this checklist:

- Is everything in your computer plugged in and turned on?

- Are all cables and cords connected properly?

- Are all necessary jumper or DIP switches set correctly?

- Is the proper diskette in the proper floppy drive?

- Is the electric wall socket the computer is plugged into working?

- Is the power on?

- Do any LED lights light up? If the LED lights are not on and your computer is

plugged in and turned on, then the power supply may not work on your

computer.

- Does the hard drive light come on? Do any of the floppy disk drive lights come

on? Do any of the disk drives make noises? If the power light is on, but the disk

drive lights do not come on or you do not hear the disk drives turning, the

problem may be with the floppy disk drives or the hard disk drives.

Does the computer beep when you turn it on? One beep means your computer is okay. More than one beep means there is an error code. Write down the error code on the LED display and the number of beeps and whether they are long or short.

## **Lights on the Card**

When you boot up your computer with a CheckIt POSTcard installed, there are a series of lights on the cards that give you information.

**Reset:** When lit, this means the computer was successfully reset or rebooted.

**CLK:** This tells you that the data and command lines were synchronized correctly.

+12V, -12V, +5V, +3.3V: These lights tell you what kind of voltage is going into your computer. If +3.3V is not lit, then that kind of voltage is not going to your computer. This is for informational purposes only.

## **Frequently Asked Questions**

#### Q: Will the CheckIt POSTcard work in my XT computer?

**A:** Yes, the POSTcard works on any PC as long as that computer's ROM BIOS supports POST error codes.

#### Q: What are ROM BIOS POST error codes?

A: When your system is first turned on, the ROM BIOS initializes various components on your system and determines what is and is not working. While running this sequence of tests, the ROM BIOS outputs certain numerical codes to a particular I/O port on your computer. This code is called a POST code and signifies what particular test the BIOS is executing at that time.

#### Q: What do I do with the POST code?

**A:** If your computer fails one of the POST tests, that POST code will be displayed on the POSTcard's LED displays. You can then look up the POST code in the appendix of this manual to determine which test the ROM BIOS actually failed on.

#### Q: How do I determine which ROM BIOS is on my machine?

A: To determine which BIOS you have:

- When your computer first boots up, you may see a message indicating a

particular brand of ROM BIOS and version number.

- When your system first boots up, you may see a message display with the particular brand of BIOS and its version number on your screen.

- If your system will not boot, look on the motherboard for the ROM BIOS chips. These chips are marked with the brand name on a sticker (see Figure 2).

- If you cannot find this information on the chips, look in the manual that came

with your system for the brand name of the BIOS that came with your computer

or call the computer manufacturer for this information.

#### Q: What are the most popular brand names for ROM BIOS?

A: The most popular are AMI, AWARD, IBM, MR BIOS, PHOENIX, and QUADTEL.

#### Q: What happens if my ROM BIOS does not support POST codes?

A: Most BIOS versions support POST codes, but if your system does not, you can always replace your existing ROM BIOS with a new BIOS which does support POST codes.

## **System Motherboard**

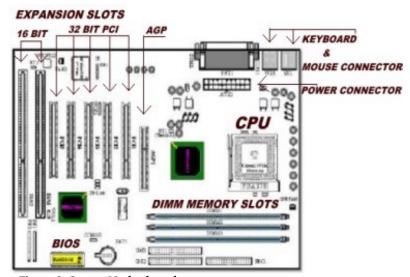

Figure 2. System Motherboard

Figure 2 is a diagram of a typical motherboard layout. Some computers have what is called a passive backplane. On these systems, most of the electronics would be on a plug-in card. The POSTcard will work the same as on a standard motherboard.

## **BIOS-Specific POST Codes**

**Note:** These POST Codes are extracted from a book called The BIOS Companion. You can order this book from this website: <a href="http://www.electrocution.com">http://www.electrocution.com</a>. The BIOS Companion explains all those settings in your BIOS in plain English, as well as containing stacks of other technical information

The POST code that the CheckIt POSTcard displays points to the general area of a failure. The codes change with each test that is performed. If the code stays on at 00h or FFh, then the BIOS is not emitting POST codes. Check to make sure the BIOS that came with your computer supports BIOS POST codes and determine which I/O port it uses.

**Note**: Remember to always check the area indicated by the POST code. The failure indicated by the POST code should be fixed. If this does not solve the problem, you need to perform more testing. Test the chip or chips that the POST code indicated had failed.

During the POST on AT-compatibles and above, special signals are output to I/O port 80H at the beginning of each test (genuine PCs and XTs don't issue POST codes, although some machines with compatible BIOSes do). Some computers may use a different port, such as 84 for the Compaq or 378 (LPT1) for Olivetti. IBM PS/2s use 90, while some EISA machines send them to 300H as well. Those at 50h are chipset or custom platform specific.

Having obtained a POST code, identify the manufacturer of the chipset on the motherboard, then refer to the *Chipsets* section to find the chip(s) that control whatever is not working.

The POST checks three levels, *Early*, *Late* and *System Initialization*. Early POST failures are generally fatal and will produce a beep code, because the video will not be active; in fact, the last diagnostic during Early POST is usually on the video, so that Late failures can actually be seen. System Initialization involves loading configuration from the CMOS, and failures will generate a text message. Consistent failures indicate a bad battery backup system.

#### Shutdown or Reset Commands

The Reset command stops the current operation and begins fetching instructions from the BIOS, as if the power has just been switched on. The Shutdown command, on the other hand, just forces the CPU to leave protected mode for real mode, so the system behaves differently after each one. Before issuing the shutdown command, the BIOS sets a value into the *shutdown byte* in the CMOS, which is checked after a reset, so the BIOS can branch to the relevant code and continue where it left off.

One of the problems with shutdown handling is that the POST must do some handling before anything else, immediately after power-on or system reset. The path between the CPU and the BIOS ROM, as well as basic control signals, has to be working before the POST gets to its first diagnostic test (usually the CPU register test), so some of the

circuitry that the CPU test is supposed to check will be checked by the shutdown handling instead, and you will get no POST indication if a critical failure occurs.

#### **Manufacturing Loop Jumper**

The phrase *Check for Manufacturing Jumper* in the tables refers to one on the motherboard that makes the POST run in a continuous loop, so you can burn in a system, or use repetitive cycling to monitor a failing area with an oscilloscope or logic analyzer. It usually forces a reset, so the POST has to start from the beginning every time. Compaq used to have the shorted jumper cause the POST to jump to another ROM at E000 just after power-on, which could have diagnostic code in it. IBM and NCR used a germanium or silicon diode to short together the keyboard connector pins 1 (cathode, bar) and 2 (5-pin DIN) or 1 (anode, arrow) and 5 (6-pin mini-DIN), so the POST checks the keyboard controller to see whether the jumper is installed.

**Note:** To get the latest updates to the Post Codes, you may have to go to the manufacturer's specific web site and download their last post codes.

#### **ACER**

Based on Award BIOS 3.03, but not exactly the same.

| Code | Meaning                                    |

|------|--------------------------------------------|

| 04   | Start                                      |

| 08   | Shutdown                                   |

| 0C   | Test BIOS ROM checksum                     |

| 10   | Test CMOS RAM shutdown byte                |

| 14   | Test DMA controller                        |

| 18   | Initialize system timer                    |

| 1C   | Test memory refresh                        |

| 1E   | Determine memory type                      |

| 20   | Test 128K memory                           |

| 24   | Test 8042 keyboard controller              |

| 28   | Test CPU descriptor instruction            |

| 2C   | Set up and test 8259 interrupt controller  |

| 30   | Set up memory interrupts                   |

| 34   | Set up BIOS interrupt vectors and routines |

| 38   | Test CMOS RAM                              |

| 3C   | Determine memory size                      |

| XX   | Shut down 8 (system halt C0h + checkpoint) |

| 40   | Shutdown 1                                 |

| 44   | Initialize Video BIOS ROM                  |

| 45   | Set up and test RAM BIOS                   |

| 46   | Test cache memory and controller           |

| 48   | Test memory                                |

| 4C   | Shutdown 3                                 |

| 50   | Shutdown 2                                 |

| 54   | Shutdown 7                                 |

| 55   | Shutdown 6                                 |

| 5C   | Test keyboard and auxiliary I/O            |

| Code | Meaning                                |

|------|----------------------------------------|

| 60   | Set up BIOS interrupt routines         |

| 64   | Test real time clock                   |

| 68   | Test diskette                          |

| 6C   | Test hard disk                         |

| 70   | Test parallel port                     |

| 74   | Test serial port                       |

| 78   | Set time of day                        |

| 7C   | Scan for and invoke option ROMs        |

| 80   | Determine presence of math coprocessor |

| 84   | initialize keyboard                    |

| 88   | Initialize system 1                    |

| 8C   | Initialize system 2                    |

| 90   | Invoke INT 19 to boot operating system |

| 94   | Shutdown 5                             |

| 98   | Shutdown A                             |

| 9C   | Shutdown B                             |

## **ALR**

See *Phoenix*.

## **Ambra**

See Phoenix.

#### AMI

Not all tests are performed by all AMI BIOSes. Those below refer to the 2 Feb 91 BIOS.

## **POST Procedures**

| Procedure              | Explanation                                                                                                                                                                                                                                                                                                            |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI Disable            | NMI interrupt line to the CPU is disabled by setting bit 7 I/O port 70h (CMOS).                                                                                                                                                                                                                                        |

| Power On Delay         | Once the keyboard controller gets power, it sets the hard and soft reset bits. Check the keyboard controller or clock generator.                                                                                                                                                                                       |

| Initialize Chipsets    | Check the BIOS, CLOCK or chipsets.                                                                                                                                                                                                                                                                                     |

| Reset<br>Determination | The BIOS reads the bits in the keyboard controller to see if a hard or soft reset is required (a soft reset will not test memory above 64K). Failure could be the BIOS or keyboard controller.                                                                                                                         |

| ROM BIOS<br>Checksum   | The BIOS performs a checksum on itself and adds a preset factory value that should make it equal 00. Failure is due to the BIOS chips.                                                                                                                                                                                 |

| Keyboard Test          | A command is sent to the 8042 (keyboard controller) which performs a test and sets a buffer space for commands. After the buffer is defined the BIOS sends a command byte, writes data to the buffer, checks the high order bits (Pin 23) of the internal keyboard controller and issues a No Operation (NOP) command. |

| CMOS                   | Shutdown byte in CMOS RAM offset 0F is tested, the BIOS                                                                                                                                                                                                                                                                |

14

| Procedure             | Explanation                                                                                          |

|-----------------------|------------------------------------------------------------------------------------------------------|

|                       | checksum calculated and diagnostic byte (0E) updated                                                 |

|                       | before the CMOS RAM area is initialized and updated for                                              |

|                       | date and time. Check RTC/CMOS chip or battery.                                                       |

| 8237/8259             | The DMA and Interrupt Controller are disabled before the                                             |

| Disable               | POST proceeds any further. Check the 8237 or 8259 chips.                                             |

| Video Disable         | The video controller is disabled and Port B initialized. Check                                       |

| Ohimaat               | the video adapter if you get problems here.                                                          |

| Chipset               | Memory addressed in 64K blocks; failure would be in the                                              |

| Init/Memory<br>Detect | chipset. If all memory is not seen, failure could be in a chip in the block after the last one seen. |

| PIT test              | The timing functions of the 8254 interrupt timer are tested.                                         |

| Pirtest               | The PIT or RTC chips normally cause problems here.                                                   |

| Memory Refresh        | PIT's ability to refresh memory tested (if an XT, DMA                                                |

|                       | controller #1 handles this). Failure is normally the PIT                                             |

|                       | (8254) in ATs or the 8237 (DMA #1) in XTs.                                                           |

| Address Lines         | Test the address lines to the first 64K of RAM. An address                                           |

|                       | line failure.                                                                                        |

| Base 64K              | Data patterns are written to the first 64K, unless there is a                                        |

|                       | bad RAM chip in which case you will get a failure.                                                   |

| Chipset               | The PIT, PIC and DMA controllers are enabled.                                                        |

| Initialization        |                                                                                                      |

| Set Interrupt         | Interrupt vector table used by PIC is installed in low                                               |

| Table                 | memory, the first 2K.                                                                                |

| 8042 check            | The BIOS reads the buffer area of the keyboard controller                                            |

|                       | I/O port 60. Failure here is normally the keyboard controller.                                       |

| Video Tests           | The type of video adapter is checked for then a series of                                            |

| D100 D                | tests is performed on the adapter and monitor.                                                       |

| BIOS Data Area        | The vector table is checked for proper operation and video                                           |

|                       | memory verified before protected mode tests are entered                                              |

|                       | into. This is done so that any errors found are displayed on the monitor.                            |

| Protected Mode        | Perform reads and writes to all memory below 1 Mb.                                                   |

| Tests                 | Failures at this point indicate a bad RAM chip, the 8042 chip                                        |

| 1.0010                | or a data line.                                                                                      |

| DMA Chips             | The DMA registers are tested using a data pattern.                                                   |

| Final Initialization  | These differ with each version. Typically, the floppy and                                            |

|                       | hard drives are tested and initialized, and a check made for                                         |

|                       | serial and parallel devices. The information gathered is then                                        |

|                       | compared against the contents of the CMOS, and you will                                              |

|                       | see the results of any failures on the monitor.                                                      |

| Boot                  | The BIOS hands over control to the Int 19 bootloader; this is                                        |

|                       | where you would see error messages such as non-system                                                |

|                       | disk.                                                                                                |

#### AMI BIOS 2.2x

| Code | Meaning                        |

|------|--------------------------------|

| 00   | Flag test                      |

| 03   | Register test                  |

| 06   | System hardware initialization |

| 09   | BIOS ROM checksum              |

| 0C   | Page register test             |

| Code | Meaning                                  |

|------|------------------------------------------|

| 0F   | 8254 timer test                          |

| 12   | Memory refresh initialization            |

| 15   | 8237 DMA controller test                 |

| 18   | 8237 DMA initialization                  |

| 1B   | 8259 interrupt controller initialization |

| 1E   | 8259 interrupt controller test           |

| 21   | Memory refresh test                      |

| 24   | Base 64K address test                    |

| 27   | Base 64K memory test                     |

| 2A   | 8742 keyboard self test                  |

| 2D   | MC 146818 CMOS test                      |

| 30   | Start first protected mode test          |

| 33   | Memory sizing test                       |

| 36   | First protected mode test                |

| 39   | First protected mode test failed         |

| 3C   | CPU speed calculation                    |

| 3F   | Read 8742 hardware switches              |

| 42   | Initialize interrupt vector area         |

| 45   | Verify CMOS configuration                |

| 48   | Test and initialize video system         |

| 4B   | Unexpected interrupt test                |

| 4E   | Start second protected mode test         |

| 51   | Verify LDT instruction                   |

| 54   | Verify TR instruction                    |

| 57   | Verify LSL instruction                   |

| 5A   | Verify LAR instruction                   |

| 5D   | Verify VERR instruction                  |

| 60   | Address line 20 test                     |

| 63   | Unexpected exception test                |

| 66   | Start third protected mode test          |

| 69   | Address line test                        |

| 6C   | System memory test                       |

| 6F   | Shadow memory test                       |

| 72   | Extended memory test                     |

| 75   | Verify memory configuration              |

| 78   | Display configuration error messages     |

| 7B   | Copy system BIOS to shadow memory        |

| 7E   | 8254 clock test                          |

| 81   | MC 146818 real time clock test           |

| 84   | Keyboard test                            |

| 87   | Determine keyboard type                  |

| 8A   | Stuck key test                           |

| 8D   | Initialize hardware interrupt vector     |

| 90   | Math coprocessor test                    |

| 93   | Determine COM ports available            |

| 96   | Determine LPT ports available            |

| 99   | Initialize BIOS data area                |

| 9C   | Fixed/Floppy controller test             |

| 9F   | Floppy disk test                         |

| A2   | Fixed disk test                          |

| A5   | External ROM scan                        |

| Code | Meaning                    |

|------|----------------------------|

| A8   | System key lock test       |

| ΑE   | F1 error message test      |

| AF   | System boot initialization |

| B1   | Interrupt 19 boot loader   |

## AMI Old BIOS (AMI Plus BIOS); 08/15/88-04/08/90

| Code | Meaning                                           |

|------|---------------------------------------------------|

| 01   | NMI disabled & 286 reg. test about to start       |

| 02   | 286 register test over                            |

| 03   | ROM checksum OK                                   |

| 04   | 8259 initialization OK                            |

| 05   | CMOS pending interrupt disabled                   |

| 06   | Video disabled & system timer counting OK         |

| 07   | CH-2 of 8253 test OK                              |

| 08   | CH-2 delta count test OK                          |

| 09   | CH-1 delta count test OK                          |

| 0A   | CH-0 delta count test OK                          |

| 0B   | Parity status cleared                             |

| 0C   | Refresh & system timer OK                         |

| 0D   | Refresh link toggling OK                          |

| 0E   | Refresh period ON/OFF 50% OK                      |

| 10   | Confirmed refresh ON & about to start 64K memory  |

| 11   | Address line test OK                              |

| 12   | 64K base memory test OK                           |

| 13   | Interrupt vectors initialized                     |

| 14   | 8042 keyboard controller test OK                  |

| 15   | CMOS read/write test OK                           |

| 16   | CMOS checksum/battery check OK                    |

| 17   | Monochrome mode set OK                            |

| 18   | Color mode set OK                                 |

| 19   | About to look for optional video ROM              |

| 1A   | Optional video ROM control OK                     |

| 1B   | Display memory read/write test OK                 |

| 1C   | Display memory read/write test for alt display OK |

| 1D   | Video retrace check OK                            |

| 1E   | Global equipment byte set for video OK            |

| 1F   | Mode set call for Mono/Color OK                   |

| 20   | Video test OK                                     |

| 21   | Video display OK                                  |

| 22   | Power on message display OK                       |

| 30   | Virtual mode memory test about to begin           |

| 31   | Virtual mode memory test started                  |

| 32   | Processor in virtual mode                         |

| 33   | Memory address line test in progress              |

| 34   | Memory address line test in progress              |

| 35   | Memory below 1MB calculated                       |

| 36   | Memory size computation OK                        |

| 37   | Memory test in progress                           |

| 38   | Memory initialization over below 1MB              |

| Code     | Mooning                                             |

|----------|-----------------------------------------------------|

|          | Meaning Meany initialization over shows 1MP         |

| 39<br>3A | Memory initialization over above 1MB                |

|          | Display memory size                                 |

| 3B       | About to start below 1MB memory test                |

| 3C       | Memory test below 1MB OK                            |

| 3D       | Memory test above 1MB OK                            |

| 3E       | About to go to real mode (shutdown)                 |

| 3F       | Shutdown successful and entered in real mode        |

| 40       | About to disable gate A-20 address line             |

| 41       | Gate A-20 line disabled successfully                |

| 42       | About to start DMA controller test                  |

| 4E       | Address line test OK                                |

| 4F       | Processor in real mode after shutdown               |

| 50       | DMA page register test OK                           |

| 51       | DMA unit-1 base register test about to start        |

| 52       | DMA unit-1 channel OK; about to begin CH-2          |

| 53       | DMA CH-2 base register test OK                      |

| 54       | About to test f/f latch for unit-1                  |

| 55       | f/f latch test both unit OK                         |

| 56       | DMA unit 1 & 2 programmed OK                        |

| 57       | 8259 initialization over                            |

| 58       | 8259 mask register check OK                         |

| 59       | Master 8259 mask register OK; about to start slave  |

| 5A       | About to check timer and keyboard interrupt level   |

| 5B       | Timer interrupt OK                                  |

| 5C       | About to test keyboard interrupt                    |

| 5D       | ERROR! timer/keyboard interrupt not in proper level |

| 5E       | 8259 interrupt controller error                     |

| 5F       | 8259 interrupt controller test OK                   |

| 70       | Start of keyboard test                              |

| 71       | Keyboard BAT test OK                                |

| 72       | Keyboard test OK                                    |

| 73       | Keyboard global data initialization OK              |

| 74       | Floppy setup about to start                         |

| 75       | Floppy setup OK                                     |

| 76       | Hard disk setup about to start                      |

| 77       | Hard disk setup OK                                  |

| 79       | About to initialize timer data area                 |

| 7A       | Verify CMOS battery power                           |

| 7B       | CMOS battery verification done                      |

| 7D       | About to analyze diagnostic test results for memory |

| 7E       | CMOS memory size update OK                          |

| 7F       | About to check optional ROM C000:0                  |

| 80       | Keyboard sensed to enable setup                     |

| 81       | Optional ROM control OK                             |

| 82       | Printer global data initialization OK               |

| 83       | RS-232 global data initialization OK                |

| 84       | 80287 check/test OK                                 |

| 85       | About to display soft error message                 |

| 86       | About to give control to system ROM E000:0          |

| 87       | System ROM E000:0 check over                        |

| 00       | Control given to Int-19; boot loader                |

|          |                                                     |

#### AMI BIOS 04/09/90-02/01/91

| Code | Meaning                                                               |

|------|-----------------------------------------------------------------------|

| 01   | NMI disabled and 286 register test about to start.                    |

| 02   | 286 register test passed.                                             |

| 03   | ROM BIOS checksum (32K at F800:0) passed.                             |

| 04   | Keyboard controller test with and without mouse passed.               |

| 05   | Chipset initialization over; DMA and Interrupt controller disabled.   |

| 06   | Video disabled and system timer test begin.                           |

| 07   | CH-2 of 8254 initialization half way.                                 |

| 08   | CH-2 of timer initialization over.                                    |

| 09   | CH-1 of timer initialization over.                                    |

| 0A   | CH-0 of timer initialization over.                                    |

| 0B   | Refresh started.                                                      |

| 0C   | System timer started.                                                 |

| 0D   | Refresh link toggling passed.                                         |

| 10   | Refresh on and about to start 64K base memory test.                   |

| 11   | Address line test passed.                                             |

| 12   | 64K base memory test passed.                                          |

| 15   | Interrupt vectors initialized.                                        |

| 17   | Monochrome mode set.                                                  |

| 18   | Color mode set.                                                       |

| 19   | About to look for optional video ROM at C000 and give control to      |

| 13   | ROM if present.                                                       |

| 1A   | Return from optional video ROM.                                       |

| 1B   | Shadow RAM enable/disable completed.                                  |

| 1C   | Display memory read/write test for main display type as set in the    |

| . •  | CMOS setup program over.                                              |

| 1D   | Display memory read/write test for alternate display type complete if |

|      | main display memory read/write test returns error.                    |

| 1E   | Global equipment byte set for proper display type.                    |

| 1F   | Video mode set call for mono/color begins.                            |

| 20   | Video mode set completed.                                             |

| 21   | ROM type 27256 verified.                                              |

| 23   | Power on message displayed.                                           |

| 30   | Virtual mode memory test about to begin.                              |

| 31   | Virtual mode memory test started.                                     |

| 32   | Processor executing in virtual mode.                                  |

| 33   | Memory address line test in progress.                                 |

| 34   | Memory address line test in progress.                                 |

| 35   | Memory below 1MB calculated.                                          |

| 36   | Memory above 1MB calculated.                                          |

| 37   | Memory test about to start.                                           |

| 38   | Memory below 1MB initialized.                                         |

| 39   | Memory above 1MB initialized.                                         |

| 3A   | Memory size display initiated. Will be updated when BIOS goes         |

|      | through memory test.                                                  |

| 3B   | About to start below 1MB memory test.                                 |

| 3C   | Memory test below 1MB completed; about to start above 1MB test.       |

| 3D   | Memory test above 1MB completed.                                      |

| 3E   | About to go to real mode (shutdown).                                  |

| Code | Meaning                                                                           |

|------|-----------------------------------------------------------------------------------|

| 3F   | Shutdown successful and processor in real mode.                                   |

| 40   | Cache memory on and about to disable A20 address line.                            |

| 41   | A20 address line disable successful.                                              |

| 42   | 486 internal cache turned on.                                                     |

| 43   | About to start DMA controller test.                                               |

| 50   | DMA page register test complete.                                                  |

| 51   | DMA unit-1 base register test about to start.                                     |

| 52   | DMA unit-1 base register test complete.                                           |

| 53   | DMA unit-2 base register test complete.                                           |

| 54   | About to check F/F latch for unit-1 and unit-2.                                   |

| 55   | F/F latch for both units checked.                                                 |

| 56   | DMA unit 1 and 2 programming over; about to initialize 8259 interrupt controller. |

| 57   | 8259 initialization over.                                                         |

| 70   | About to start keyboard test.                                                     |

| 71   | Keyboard controller BAT test over.                                                |

| 72   | Keyboard interface test over; mouse interface test started.                       |

| 73   | Global data initialization for keyboard/mouse over.                               |

| 74   | Display 'SETUP' prompt and about to start floppy setup.                           |

| 75   | Floppy setup over.                                                                |

| 76   | Hard disk setup about to start.                                                   |

| 77   | Hard disk setup over.                                                             |

| 79   | About to initialize timer data area.                                              |

| 7A   | Timer data initialized and about to verify CMOS battery power.                    |

| 7B   | CMOS battery verification over.                                                   |

| 7D   | About to analyze POST results.                                                    |

| 7E   | CMOS memory size updated.                                                         |

| 7F   | Look for <del> key and get into CMOS setup if found.</del>                        |

| 80   | About to give control to optional ROM in segment C800 to DE00.                    |

| 81   | Optional ROM control over.                                                        |

| 82   | Check for printer ports and put the addresses in global data area.                |

| 83   | Check for RS232 ports and put the addresses in global data area.                  |

| 84   | Coprocessor detection over.                                                       |

| 85   | About to display soft error messages.                                             |

| 86   | About to give control to system ROM at segment E000.                              |

| 00   | System ROM control at E000 over now give control to Int 19h boot loader.          |

## AMI New BIOS; 02/02/91—12/12/91

| Code | Meaning                                                                                        |

|------|------------------------------------------------------------------------------------------------|

| 01   | Processor register test about to start and NMI to be disabled.                                 |

| 02   | NMI is Disabled. Power on delay starting.                                                      |

| 03   | Power on delay complete. Any initialization before keyboard BAT is in progress.                |

| 04   | Init before keyboard BAT complete. Reading keyboard SYS bit to check soft reset/ power-on.     |

| 05   | Soft reset/ power-on determined. Going to enable ROM. i. e. disable shadow RAM/Cache.          |

| 06   | ROM enabled. Calculating ROM BIOS checksum, waiting for KB controller input buffer to be free. |

| Code     | Meaning                                                                                                        |

|----------|----------------------------------------------------------------------------------------------------------------|

| 07       | ROM BIOS Checksum passed. KB controller I/B free. Going to                                                     |

|          | issue BAT comd to kboard controller.                                                                           |

| 80       | BAT command to keyboard controller issued. Going to verify BAT                                                 |

|          | command.                                                                                                       |

| 09       | Keyboard controller BAT result verified. Keyboard command byte to                                              |

|          | be written next.                                                                                               |

| 0A       | Keyboard command byte code issued. Going to write command                                                      |

|          | byte data.                                                                                                     |

| 0B       | Keyboard controller command byte written. Going to issue Pin-23 &                                              |

| 00       | 24 blocking/unblocking command                                                                                 |

| 0C       | Pin 23 & 24 of keyboard controller is blocked/unblocked. NOP command of keyboard controller to be issued next. |

| 0D       | NOP command processing done. CMOS shutdown register test to                                                    |

| OD       | be done next.                                                                                                  |

| 0E       | CMOS shutdown register R/W test passed. Going to calculate                                                     |

| -        | CMOS checksum, update DIAG byte.                                                                               |

| 0F       | CMOS checksum calculation is done DIAG byte written. CMOS init.                                                |

|          | to begin (If INIT CMOS IN EVERY BOOT is set).                                                                  |

| 10       | CMOS initialization done (if any). CMOS status register about to init                                          |

|          | for Date and Time.                                                                                             |

| 11       | CMOS Status register initialized. Going to disable DMA and                                                     |

|          | Interrupt controllers.                                                                                         |

| 12       | DMA Controller #1 & #2, interrupt controller #1 & #2 disabled. About                                           |

|          | to disable Video display and init port-B.                                                                      |

| 13       | Video display disabled and port-B initialized. Chipset init/auto mem                                           |

| 4.4      | detection about to begin.                                                                                      |

| 14       | Chipset initialization/auto memory detection over. 8254 timer test about to start.                             |

| 15       | CH-2 timer test halfway. 8254 CH-2 timer test to be complete.                                                  |

| 16       | Ch-2 timer test over. 8254 CH-1 timer test to be complete.                                                     |

| 17       | CH-1 timer test over. 8254 CH-0 timer test to be complete.                                                     |

| 18       | CH-0 timer test over. About to start memory refresh.                                                           |

| 19       | Memory Refresh started. Memory Refresh test to be done next.                                                   |

| 1A       | Memory Refresh line is toggling. Going to check 15 microsecond                                                 |

|          | ON/OFF time.                                                                                                   |

| 1B       | Memory Refresh period 30 microsec test complete. Base 64K                                                      |

|          | memory test about to start.                                                                                    |

| 20       | Base 64k memory test started. Address line test to be done next.                                               |

| 21       | Address line test passed. Going to do toggle parity.                                                           |

| 22       | Toggle parity over. Going for sequential data R/W test.                                                        |

| 23       | Base 64k sequential data R/W test passed. Setup before Interrupt                                               |

|          | vector init about to start.                                                                                    |

| 24       | Setup before vector initialization complete. Interrupt vector                                                  |

|          | initialization about to begin.                                                                                 |

| 25       | Interrupt vector initialization done. Going to read I/O port of 8042 for                                       |

| 26       | turbo switch (if any).  I/O port of 8042 is read. Going to initialize global data for turbo                    |

| 26       | switch.                                                                                                        |

| 27       | Global data initialization is over. Any initialization after interrupt                                         |

| <u> </u> | vector to be done next.                                                                                        |

| 28       | Initialization after interrupt vector is complete. Going for                                                   |

| _~       | monochrome mode setting.                                                                                       |

| 29       | Monochrome mode setting is done. Going for Color mode setting.                                                 |

| •        | G                                                                                                              |

| Code | Meaning                                                                        |

|------|--------------------------------------------------------------------------------|

| 2A   | Color mode setting is done. About to go for toggle parity before               |

|      | optional ROM test.                                                             |

| 2B   | Toggle parity over. About to give control for any setup before                 |

|      | optional video ROM check.                                                      |

| 2C   | Processing before video ROM control is done. About to look for                 |

|      | optional video ROM and give control.                                           |

| 2D   | Optional video ROM control done. About to give control to do any               |

|      | processing after video ROM returns control.                                    |

| 2E   | Return from processing after the video ROM control. If EGA/VGA                 |

|      | not found then do display memory R/W test.                                     |

| 2F   | EGA/VGA not found. Display memory R/W test about to begin.                     |

| 30   | Display mem R/W test passed. About to look for retrace checking.               |

| 31   | Display mem R/W test/ retrace check failed. About to do alternate              |

|      | Display memory R/W test.                                                       |

| 32   | Alternate Display memory R/W test passed. About to look for                    |

|      | alternate display retrace checking.                                            |

| 33   | Video display checking over. Verification of display with switch               |

|      | setting and card to begin.                                                     |

| 34   | Verification of display adapter done. Display mode to be set next.             |

| 35   | Display mode set complete. BIOS ROM data area about to be                      |

|      | checked.                                                                       |

| 36   | BIOS ROM data area check over. Going to set cursor for power on                |

|      | message.                                                                       |

| 37   | Cursor setting for power on message id complete. Going to display              |

|      | the power on message.                                                          |

| 38   | Power on message display complete. Going to read new cursor                    |

| 00   | position.                                                                      |

| 39   | New cursor position read and saved. Going to display the reference             |

| 2.4  | String.                                                                        |

| 3A   | Reference string display is over. Going to display the Hit <esc></esc>         |

| 3B   | message.  Hit <esc> message displayed. Virtual mode memory test about to</esc> |

| SD   | start.                                                                         |

| 40   | Preparation for virtual mode test started. Going to verify from video          |

| 40   | memory.                                                                        |

| 41   | Returned after verifying from display memory. Going to prepare the             |

| ~ '  | descriptor tables.                                                             |

| 42   | Descriptor tables prepared. Going to enter in virtual mode for                 |

| l '- | memory test.                                                                   |

| 43   | Entered in the virtual mode. Going to enable interrupts for                    |

| l    | diagnostics mode.                                                              |

| 44   | Interrupts enabled (if diagnostics switch is on). Going to initialize          |

|      | data to check memory wrap around at 0:0.                                       |

| 45   | Data initialized. Going to check for memory wrap around at 0:0and              |

|      | finding the total system memory size.                                          |

| 46   | Memory wrap around test done. Memory size calculation over.                    |

|      | About to go for writing patterns to test memory.                               |

| 47   | Pattern to be tested written in extended memory. Going to write                |

|      | patterns in base 640k.                                                         |

| 48   | Patterns written in base memory. Going to find out amount of                   |

|      | memory below 1Mb.                                                              |

| 49   | Amount of memory below 1Mb found and verified. Going to find out               |

|      | amount of memory above 1M memory.                                              |

| Amount of memory above 1Mb found and verified. Going for BIOS ROM data area check.  BIOS ROM data area check over. Going to check <esc> and clear mem below 1Mb for soft reset.  C Memory below 1Mb cleared. (SOFT RESET). Going to clear memory above 1M. Cleared. (SOFT RESET). Going to clear memory above 1M cleared. (SOFT RESET). About to display the first 64k memory size.  Memory test started. (NO SOFT RESET). About to display the first 64k memory size display started. This will be updated during memory test. Going for sequential and random memory test.  Memory size display started. This will be updated during memory test. Going for sequential and random memory test.  Memory test below 1Mb complete. Going to adjust memory size for relocation/ shadow.  Memory size adjusted due to relocation/shadow. Memory test above 1Mb to follow.  CPU registers are saved including memory size. Going to enter in real mode.  SOPU registers are saved including memory size. Going to enter in real mode.  Shutdown successful. CPU in real mode. Going to restore registers saved during preparation for shutdown.  Registers restored. Going to disable gate A20 address line.  A20 address line disable successful. BIOS ROM data area about to be checked.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check over. Going to clear Hit <esc> message.  Hit <esc> message cleared. WAIT message displayed. About to start DMA and interrupt controller test.  DMA page register test passed. About to go for DMA #2 base register test.  DMA #2 base register test passed. About to go for DMA #2 base register test.  DMA #2 base register test passed. About to program DMA unit 1 and 2.  BIOS ROM data area check over. About to program DMA unit 1 and 2.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check over. About to</esc></esc></esc> | Code | Meaning                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------|

| mem below 1Mb for soft reset.  4C Memory below 1M cleared. (SOFT RESET). Going to clear memory above 1M.  4D Memory above 1M cleared. (SOFT RESET). Going to save the memory size.  4E Memory test started. (NO SOFT RESET). About to display the first 64k memory test.  4F Memory size display started. This will be updated during memory test. Going for sequential and random memory test.  50 Memory test below 1Mb complete. Going to adjust memory size for relocation/shadow.  51 Memory size adjusted due to relocation/shadow. Memory test above 1Mb to follow.  52 Memory test above 1Mb complete. Going to prepare to go back to real mode.  53 CPU registers are saved including memory size. Going to enter in real mode.  54 Shutdown successful. CPU in real mode. Going to restore registers saved during preparation for shutdown.  55 Registers restored. Going to disable gate A20 address line.  56 A20 address line disable successful. BIOS ROM data area about to be checked.  57 BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  58 BIOS ROM data area check over. Going to clear Hit <=sc=message.  59 Hit <=sc=message.  59 Hit <=sc=message.  60 DMA page register test passed. About to yerify from display memory.  61 Display memory verification over. About to go for DMA #1 base register test.  62 DMA #1 base register test passed. About to go for BIOS ROM data area check to be complete.  63 BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  64 BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  65 BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  66 DMA #1 base register test passed. About to program DMA unit 1 and 2.  66 DMA wit 1 and 2 programming over. About to initialize 8259 interrupt controller  67 8259 initialization over. About to start keyboard test.  68 Keyboard test started. Clearing output buffer, checking for stuck key. About to issue keyboard reset  80 Keyboard controller interface test over. About to write command byte and init              | 4A   | ROM data area check.                                              |

| above 1M. Memory above 1M cleared.(SOFT RESET). Going to save the memory size.  4E Memory test started. (NO SOFT RESET). About to display the first 64k memory test.  4F Memory size display started. This will be updated during memory test. Going for sequential and random memory test.  50 Memory test below 1Mb complete. Going to adjust memory size for relocation/ shadow.  51 Memory size adjusted due to relocation/shadow. Memory test above 1Mb to follow.  52 Memory test above 1Mb complete. Going to prepare to go back to real mode.  53 CPU registers are saved including memory size. Going to enter in real mode.  54 Shutdown successful. CPU in real mode. Going to restore registers saved during preparation for shutdown.  55 Registers restored. Going to disable gate A20 address line.  56 A20 address line disable successful. BIOS ROM data area about to be checked.  57 BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  58 BIOS ROM data area check over. Going to clear Hit <a essage"="" href="Esc&gt;">Esc&gt;"message</a> .  59 Hit <a essage"="" href="Esc&gt;">Esc="esc&gt;"essage</a> cleared. WAIT message displayed. About to start DMA and interrupt controller test.  60 DMA page register test passed. About to go for DMA #1 base register test.  61 Display memory verification over. About to go for DMA #2 base register test.  62 DMA #1 base register test passed. About to go for BIOS ROM data area check.  63 DMA #2 base register test passed. About to program DMA unit 1 and 2.  66 DMA unit 1 and 2 programming over. About to initialize 8259 interrupt controller  67 8259 initialization over. About to start keyboard test.  68 Keyboard test started. Clearing output buffer, checking for stuck key. About to issue keyboard controller if test command.  68 Keyboard controller interface test over. About to write command byte and init circular buffer.                                                                                                                                                                                      | 4B   | mem below 1Mb for soft reset.                                     |

| memory size.  Memory test started. (NO SOFT RESET). About to display the first 64k memory test.  Memory size display started. This will be updated during memory test. Going for sequential and random memory test.  Memory test below 1Mb complete. Going to adjust memory size for relocation/ shadow.  Memory size adjusted due to relocation/shadow. Memory test above 1Mb to follow.  Memory test above 1Mb complete. Going to prepare to go back to real mode.  Memory test above 1Mb complete. Going to prepare to go back to real mode.  CPU registers are saved including memory size. Going to enter in real mode.  Shutdown successful. CPU in real mode. Going to restore registers saved during preparation for shutdown.  Registers restored. Going to disable gate A20 address line.  A20 address line disable successful. BIOS ROM data area about to be checked.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check over. Going to clear Hit <=Esc>message.  Hit <esc>message cleared. WAIT message displayed. About to start DMA and interrupt controller test.  DMA page register test passed. About to verify from display memory.  Display memory verification over. About to go for DMA #1 base register test.  DMA #1 base register test passed. About to go for BIOS ROM data area check.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check halfway. BIOS ROM data area check.  BIOS ROM data area check over. About to go for DMA #2 base register test.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check over. About to program DMA unit 1 and 2.  BIOS ROM data area check over. About to initialize 8259 interrupt controller  EBIOS ROM data area check over. About to initialize 8259 interrupt controller over. About to start keyboard test.  Keyboard test started. Clearing output buffer, checking for stuck key. About to issue keyboard reset  Keyboard controller interface test over. About to write command byte and in</esc>           | 4C   | above 1M.                                                         |

| 4F Memory test.  4F Memory size display started. This will be updated during memory test. Going for sequential and random memory test.  50 Memory test below 1Mb complete. Going to adjust memory size for relocation/ shadow.  51 Memory size adjusted due to relocation/shadow. Memory test above 1Mb to follow.  52 Memory test above 1Mb complete. Going to prepare to go back to real mode.  53 CPU registers are saved including memory size. Going to enter in real mode.  54 Shutdown successful. CPU in real mode. Going to restore registers saved during preparation for shutdown.  55 Registers restored. Going to disable gate A20 address line.  56 A20 address line disable successful. BIOS ROM data area about to be checked.  57 BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  58 BIOS ROM data area check over. Going to clear Hit <esc>message.  59 Hit <esc> message cleared. WAIT message displayed. About to start DMA and interrupt controller test.  60 DMA page register test passed. About to verify from display memory.  61 Display memory verification over. About to go for DMA #1 base register test.  62 DMA #1 base register test passed. About to go for BIOS ROM data area check.  63 DMA #2 base register test passed. About to go for BIOS ROM data area check.  64 BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  65 BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  66 BIOS ROM data area check over. About to program DMA unit 1 and 2.  66 DMA unit 1 and 2 programming over. About to initialize 8259 interrupt controller  67 8259 initialization over. About to start keyboard test.  68 Keyboard test started. Clearing output buffer, checking for stuck key. About to issue keyboard reset  80 Keyboard controller interface test over. About to write command byte and init circular buffer.</esc></esc>                                                                                                                                                                                            | 4D   | memory size.                                                      |

| test. Going for sequential and random memory test.  Memory test below 1Mb complete. Going to adjust memory size for relocation/shadow.  Memory size adjusted due to relocation/shadow. Memory test above 1Mb to follow.  Memory test above 1Mb complete. Going to prepare to go back to real mode.  CPU registers are saved including memory size. Going to enter in real mode.  Shutdown successful. CPU in real mode. Going to restore registers saved during preparation for shutdown.  Registers restored. Going to disable gate A20 address line.  A20 address line disable successful. BIOS ROM data area about to be checked.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check over. Going to clear Hit <=Esc>message.  Hit <esc> message cleared. WAIT message displayed. About to start DMA and interrupt controller test.  DMA page register test passed. About to verify from display memory.  Display memory verification over. About to go for DMA #1 base register test.  DMA #1 base register test passed. About to go for BIOS ROM data area check.  BIOS ROM data area check halfway. BIOS ROM data area check.  BIOS ROM data area check halfway. BIOS ROM data area check.  BIOS ROM data area check halfway. BIOS ROM data area check.  BIOS ROM data area check halfway. BIOS ROM data area check.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check over. About to program DMA unit 1 and 2.  CHANGE ADD THE ADD</esc>           |      | 64k memory test.                                                  |

| relocation/ shadow.  Memory size adjusted due to relocation/shadow. Memory test above 1Mb to follow.  Memory test above 1Mb complete. Going to prepare to go back to real mode.  CPU registers are saved including memory size. Going to enter in real mode.  Shutdown successful. CPU in real mode. Going to restore registers saved during preparation for shutdown.  Registers restored. Going to disable gate A20 address line.  A20 address line disable successful. BIOS ROM data area about to be checked.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check over. Going to clear Hit <esc>message.  Hit <esc> message cleared. WAIT message displayed. About to start DMA and interrupt controller test.  DMA page register test passed. About to verify from display memory.  Display memory verification over. About to go for DMA #1 base register test.  DMA #1 base register test passed. About to go for BIOS ROM data area check.  DMA #2 base register test passed. About to go for BIOS ROM data area check.  BIOS ROM data area check halfway. BIOS ROM data area check to be complete.  BIOS ROM data area check over. About to program DMA unit 1 and 2.  BIOS ROM data area check over. About to initialize 8259 interrupt controller  BIOS ROM data area check over. About to initialize 8259 interrupt controller  BIOS ROM data area check over. About to initialize 8259 interrupt controller  Reyboard reset error/stuck key found. About to issue keyboard controller if test command.  Keyboard controller interface test over. About to write command byte and init circular buffer.</esc></esc>                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4F   |                                                                   |