# Revolutionary Architecture for the Next Generation Platform FPGAs

Embargoed News:

December 8, 2003

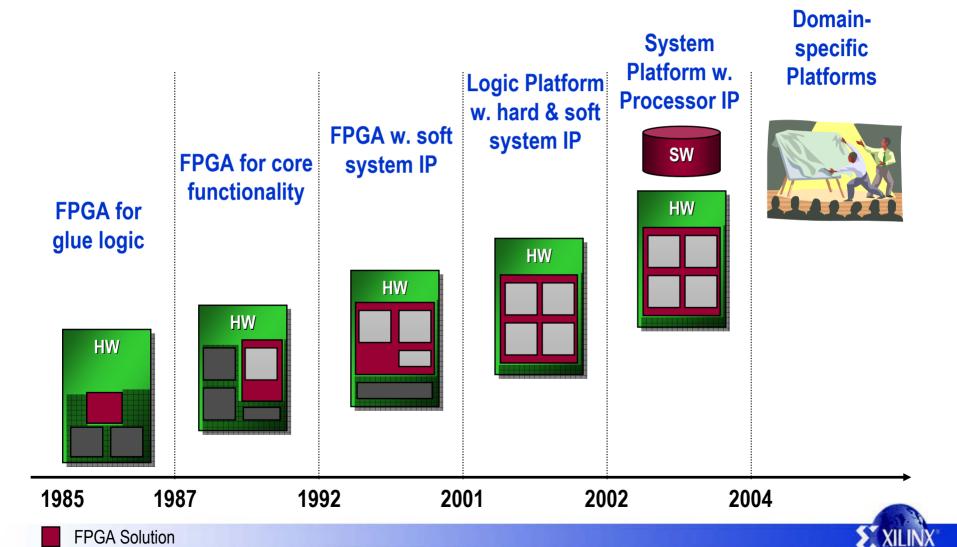

### The Evolution of FPGA Architectures

Meta Architecture 2

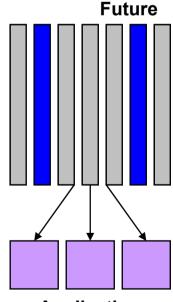

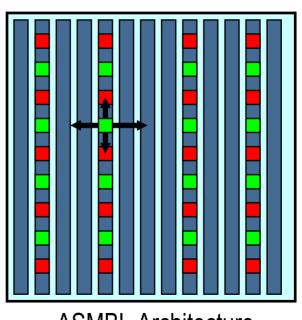

### The ASMBL<sup>(TM)</sup> Architecture <u>Application Specific Modular Block Architecture</u>

Column

Based

ASMBL

Architecture

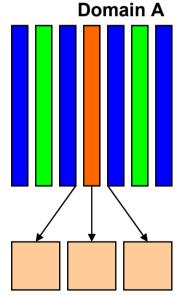

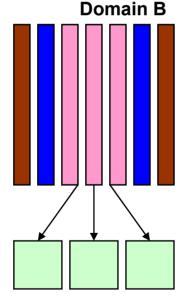

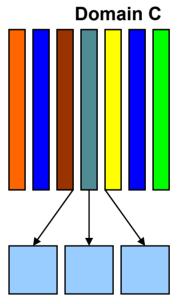

#### **Feature Options**

- Logic

- DSP

- Memory

- Processing

- High-speed I/O

- Hard IP

- Mixed Signal

- □ Future...

**Applications**

**Applications**

**Applications**

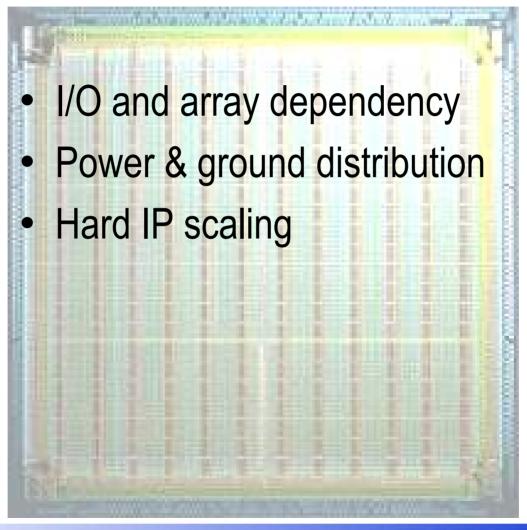

# Addressing Geometric Constraints

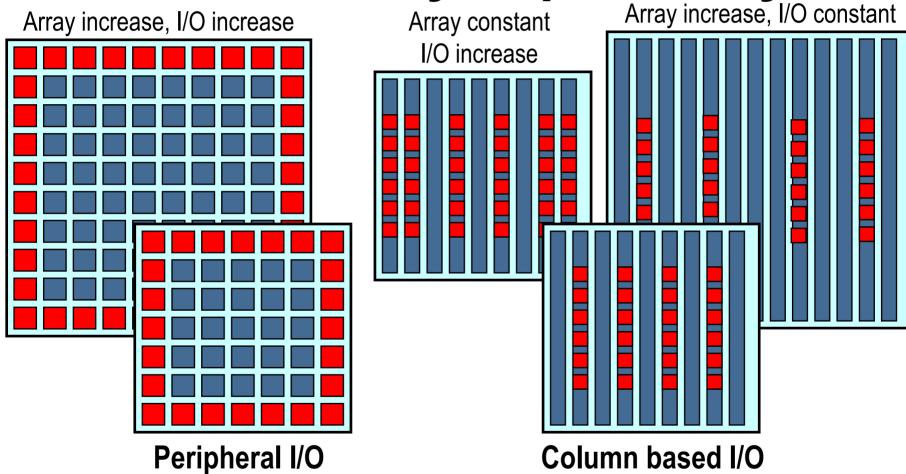

# ASMBL Addresses I/O and Array Dependency

independent of array size

dependent on array size

### ASMBL Addresses PWR & GND Distribution

- New Pwr & Gnd distribution reduces voltage drop

- Switching reliability increase via higher thresholds

**ASMBL** Architecture

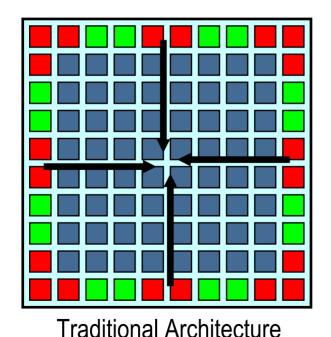

### ASMBL Addresses Hard IP Scaling

Array size increase to accommodate feature scaling **Traditional Architecture**

Array size constant as features scale independently

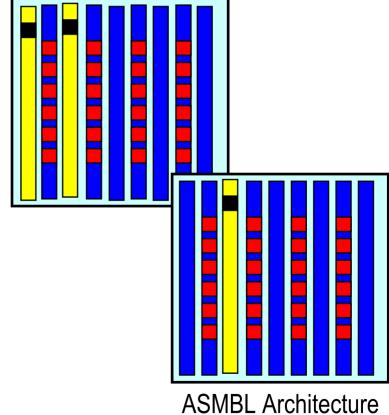

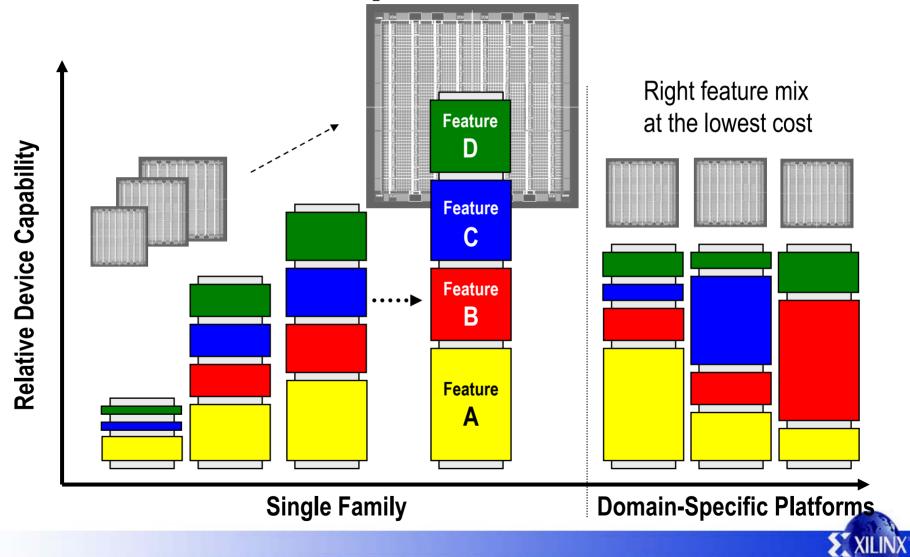

#### **ASMBL Advantages**

#### Xilinx Benefits

- Reduces time & risk for FPGA platform development

- Enables cost-effective assembly of multiple platforms

- Allows rapid response to new market demands

#### Customer Benefits

- Highest value solution at a given price point

- Right feature mix for a given domain

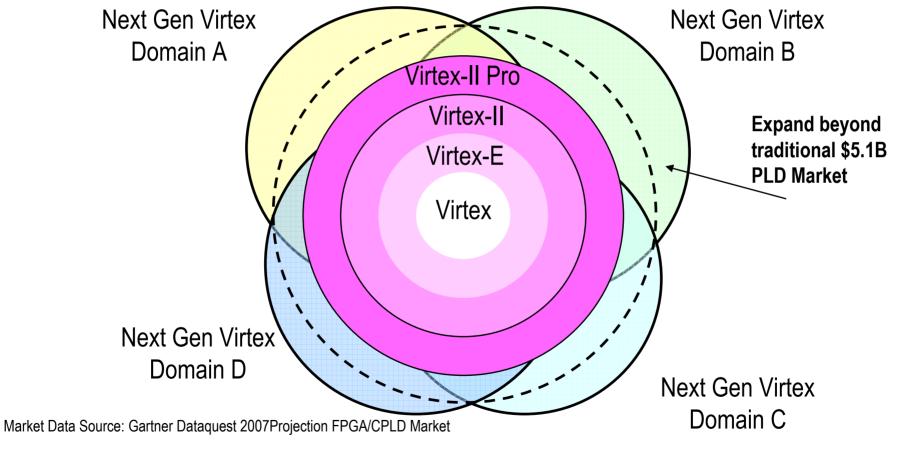

### ASMBL Enables Domain-Specific Platforms

# Cost Effectively Expanding Xilinx FPGA Application Domains

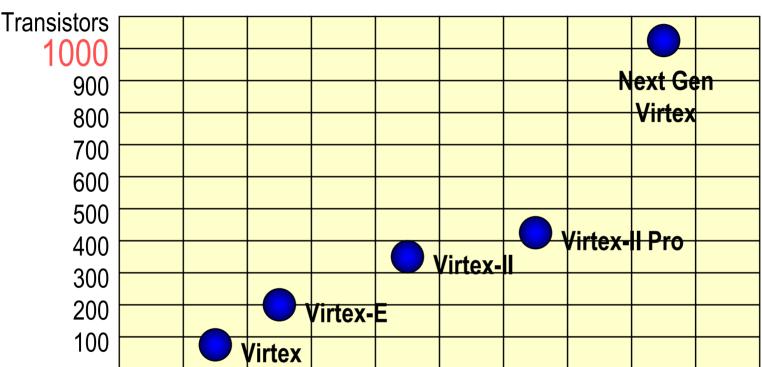

### Taking Advantage of Moore's Law

Millions of

1996 1997 1998 1999 2000 2001 2002 2003 2004 2005

Transistor count increases, cost decreases

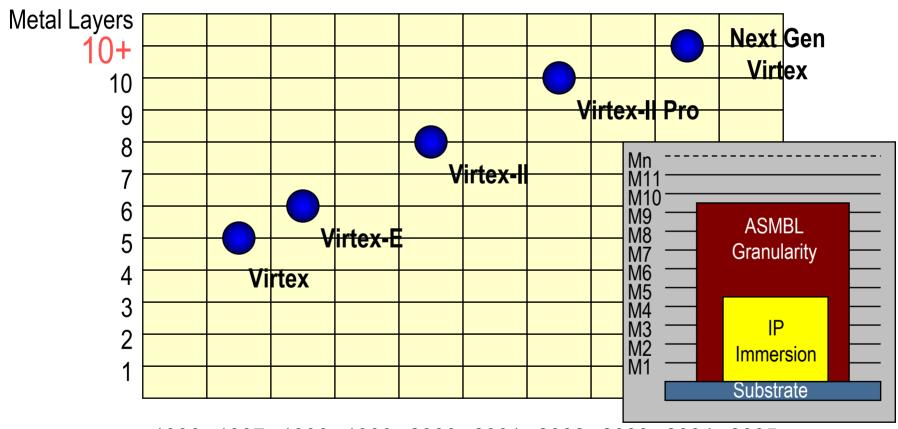

# Taking Advantage of 10+ Layers of Metal

1996 1997 1998 1999 2000 2001 2002 2003 2004 2005

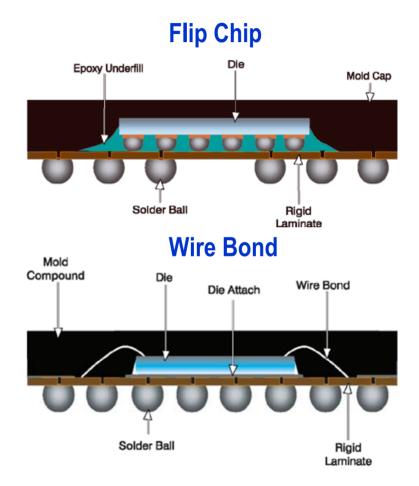

# Taking Advantage of Advanced Packaging

- Flip Chip enables column based architecture

- Allows connecting to I/Os anywhere on the die

- Enhanced thermal dissipation

Package source: Amkor Technology

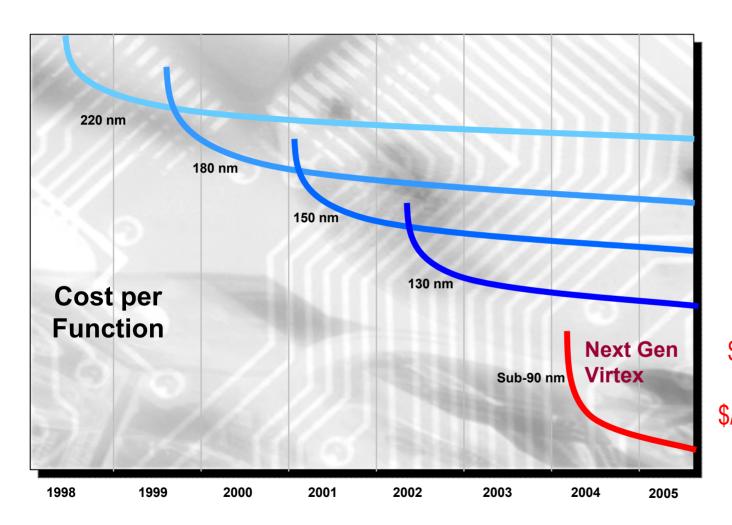

#### **Next Generation Cost Metrics**

Old density based metrics

\$/LC and \$/Gate

New capability

based metrics

\$/MAC/s or \$/BOPS

\$/Mbit of storage

\$/Gbps bandwidth

\$/Gbyte/s bandwidth

\$/DMIPS

\$/system functionality

\$/mixed signal

#### Conclusion

- ASMBL enables domain-specific Platform FPGAs

- Addresses traditional architectural limitations

- Highest value solution at a given price point