# "Advancing Traffic Efficiency and Safety through Software Technology, Phase 2 (ATESST2)"

### **Tooling**

### ATESST2 Final Workshop June 21 2010

### **Outline**

Overall tool development

Quick demo preview

Parallel sidetracks with DSL tools

Conclusion and plans ahead

### Overall tool development

- WT4.2

- √ (CEA) workbench based on a customized version of UML2 modeler Papyrus

- WT3.1

- √ (CAR) RIF gateway

- WT3.2

- √ (KTH,HULL) safety analysis with gateway to HipHops

- WT3.3

- √ (TUB) feature/variability plugin

- WT3.4

- ✓ (CEA) Autosar gateway

- √ (KTH) Simulink gateway

- WT3.5

- ✓ (CEA): Timing analysis

- √ (CEA,KTH,HULL): Combined analysis (time & safety)

- √ (CEA,KTH,HULL,TUB): Analysis-driven optimization

- ✓ Available, included in the USB stick

- Experiments only

- ✓ Results from collaboration with EDONA (French System@tic cluster), not included in USB stick

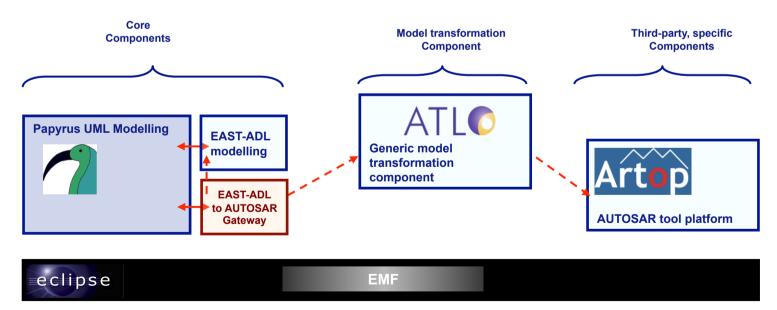

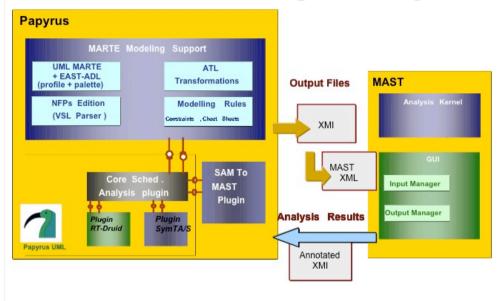

### WT4.2 Workbench architecture explained

- The component is an extension plug-in for Papyrus

- It uses features from the following components:

- Papyrus and its EAST-ADL customization plug-in (<u>www.papyrusuml.org</u>)

- Based on EMF based implementations of UML2 and EAST-ADL

- ATL (<u>www.eclipse.org/m2m/atl</u>)

- Provides a generic EMF compliant model transformation engine

- ARTOP (www.artop.org)

- Provides an EMF implementation of the AUTOSAR metamodel

# WT3.1 RIF Plugin

#### Main Goal:

Provide an EAST-ADL Modeling User a UI based Eclipse Plugin Mechanism to Import or Export Requirements into/out of an EAST-ADL System Model

#### Architecture:

- ATL Transformation Rules: RIF XSD Schema → EAST-ADL UML Profile (Import Direction) +

EAST-ADL UML Profile → RIF XSD Schema (Export Direction)

- User Interface to choose EAST-ADL System Model File, RIF XML File, and possibly ATL Transformation rules to use

- Contextual Invoking by right clicking on the EAST-ADL System Model File (Import/Export)

- Contextual Invoking by right clicking on the RIF XML File (New EAST-ADL Model with Requirements Specification)

#### **Current status:**

- Domain language updates identified and agreed upon

- Use cases identified

- Import developed/Export being finalized

Leader: Carmeq GmbH

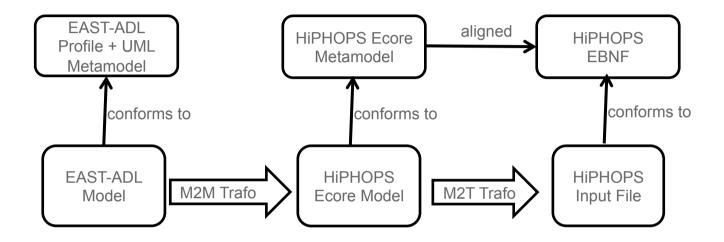

# WT3.2 Safety analysis plugin

Leader KTH, HULL

Goal: enable safety analysis with HipHOPS engine

Current status: HW/SW error propagation, involves HipHOPS extension provided by HULL

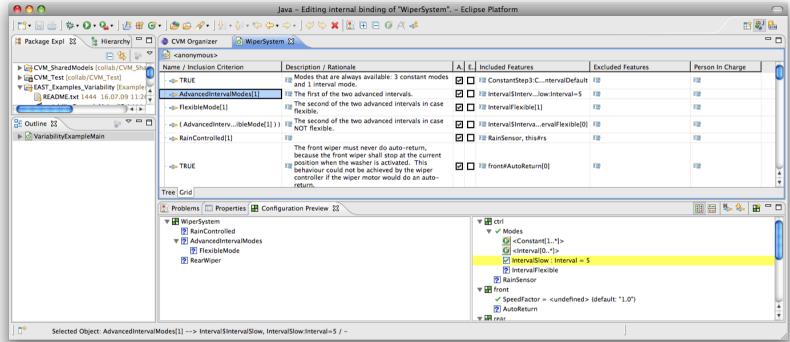

# WT3.3 Feature/Variability plugin

#### Leader TUB

Goal: to provide support for the management of feature-oriented modeling at vehicle level and vehicle configuration support on to the artifact level

#### Tool is twofolds:

- 1. CVM feature modeling editor

- 2. Bridge with EAST-ADL Papyrus

Evaluated by Continental on demonstrator models

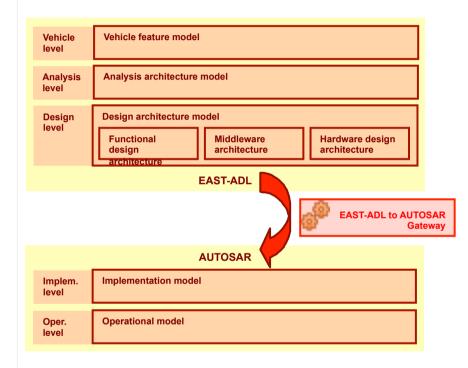

### WT3.4 Autosar gateway

Result from collaboration with EDONA (French System@tic cluster)

Leader CEA

The refinement activity between EAST-ADL and AUTOSAR is:

- Tedious and Repetitive

- Error prone

- Time consuming

- Uneasy as it is necessary to manage AUTOSAR consistency and to make mapping (function / software) choice at the same time

Automated mapping taking into account allocation constraints and hardware architecture.

**Evaluated by Continental (Toulouse)**

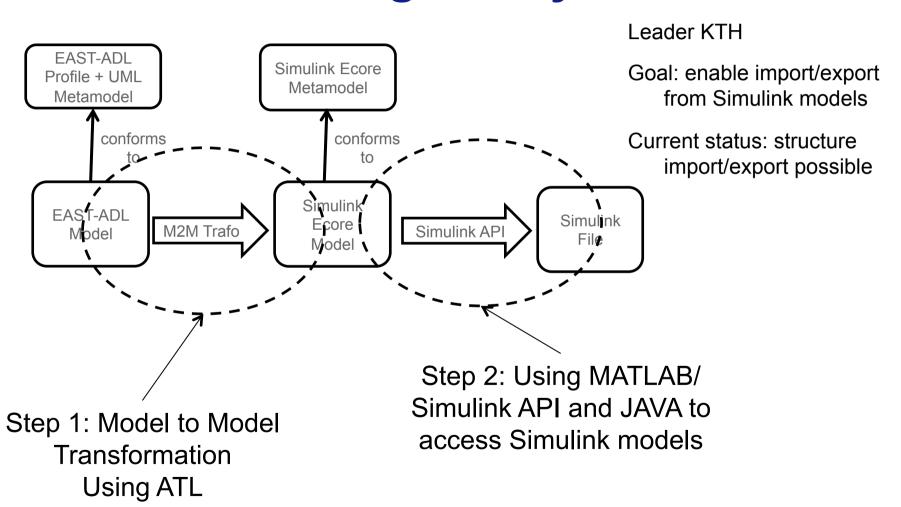

### WT3.4 Simulink gateway

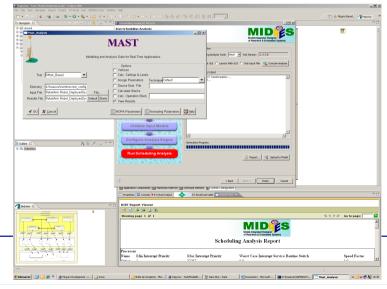

### WT3.5 Timing analysis

Result from collaboration with EDONA (French System@tic cluster)

Leader CEA

Goal: perform timing analysis at Design level based on timing assumptions captured through timing constructs annotations

Evaluated by Continental (Toulouse) and used in architecture optmization experiments in ATESST2

### Parallel side tracks

Beside the main UML2 implementation of the EAST-ADL2 language and tool support, there are DSL implementation under-development

- MetaEdit+ by KTH

- VSA by MGH

#### Benefits are:

- Verification of consistency between profile and metamodel

- Broaden community use

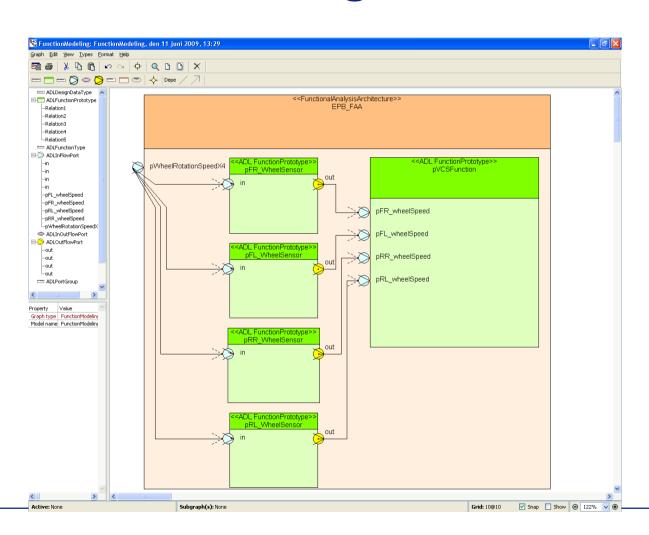

# **EAST-ADL** modeling in Metaedit+

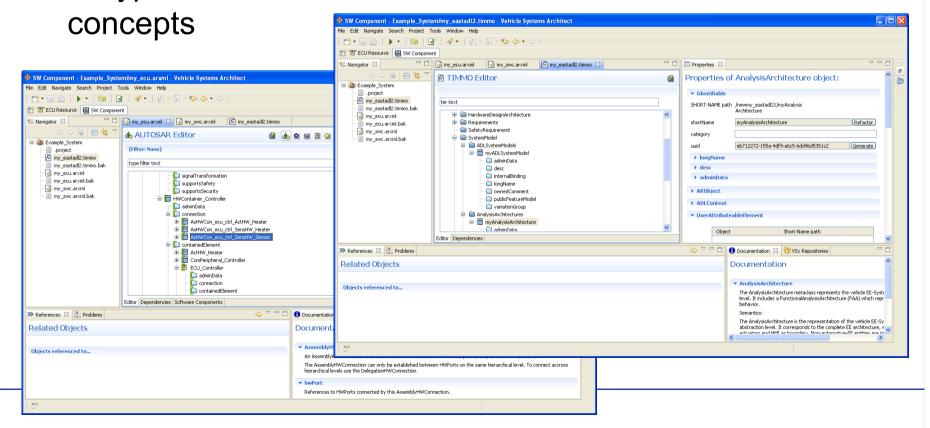

# **Vehicle Systems Architect**

**AUTOSAR** authoring tool

Prototype version extended with EAST-ADL2 and TIMMO

# Conclusion and plans ahead

- Workbench provides sound basis for EAST-ADL modeling and exchange with other tools and languages

- Analysis-driven tool specification with experimental case study

- Methodology and tool-support oriented investigation:

- Eclipse tool support system cheatsheets, hints, etc.

- Link from EPF to such tool support

- Planning for an integration as an Eclipse MDT subproject, along with Papyrus MDT