S 1/ 8

ション

いたいのかったり

ALC: NO

リたス

いためになっていたとうないであります。これではないとうというないでは、

5.1

Internal Transfer Rate

.

3' Ribbon Cable 900 ns / cycle

300"= 25' RibbonCable 2000ns/cycle

## DHZ80 Board

03M01 111 03 moz 1xz

03 115 GND 03 116 GND

### PROMS

Does checksum of its prom (800-FFF) and prints on terminal. Repeats. Should print 954B

### PROMØ

Does checksum of PROMØ (0-200) and prints on terminal. Repeats.

Check with PROM burner for varification.

#### RAM4

Does ramcheck of ram at 4000-7FFF. Writes incrementing 16 bit patterns and compares back. Starting 16 bit value is printed each iteration.

If fail is found program checks S1 to continue

S1 up => continue

S1 down = wait

PAME

Same as RAMA but for RAM 8000-BFFF

RAMX

Same as RAMA but for RAM 4000-BFFF

3-NOV-81

Outputs message. Then inputs from terminal and echos character <u>plus</u> one.

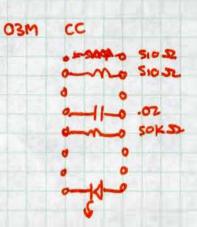

- I/O check: 510/0

- Ch A RXDA 12

- TxDA 15 Ch B RxDB 28

- TxDB 26

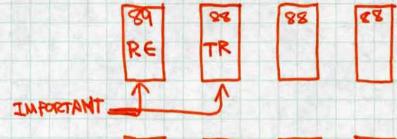

| 89 | - 1 | 89 | 89 | 89 |

|----|-----|----|----|----|

| 1  |     | -  |    |    |

### RAMALL

Checks all RAM (4000-BFFF). IF an envoris detected the syndrome is primbed. <u>S1 up => continue on error</u>, S1 down => stop on error.

## EMON for DH280

NMICHT 42FF

OUTBYT 4301

- IO78 <=> Reset fifes

4-NOV-81

B-NOV-81

#### MAIN BOARD

8288 -AEN should be GUD, Not SV -RAS should come from -A17 -PROM should come from A17 RAM addressed - Grann A17 TO word addressed - change decoders to A4, A2, A3 from AP-A1-A2

### 21 Jan 82

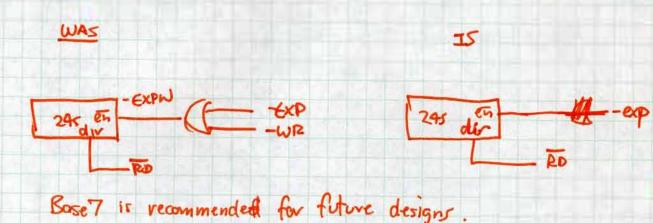

## BASE7 board/Wivelist

Discovered logic error on 245, prevented reading external I/o space.

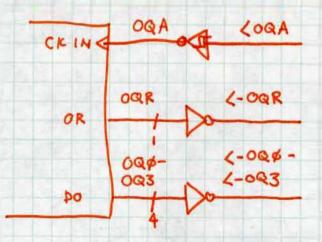

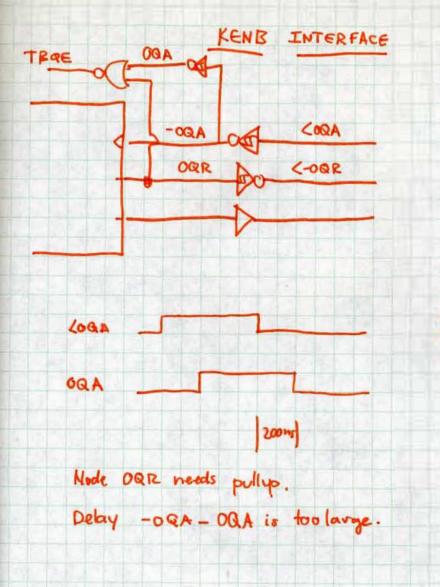

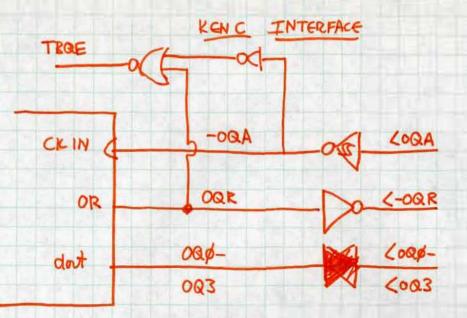

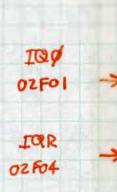

### Delay CKIN VE to OR VE 25 ns

10.9

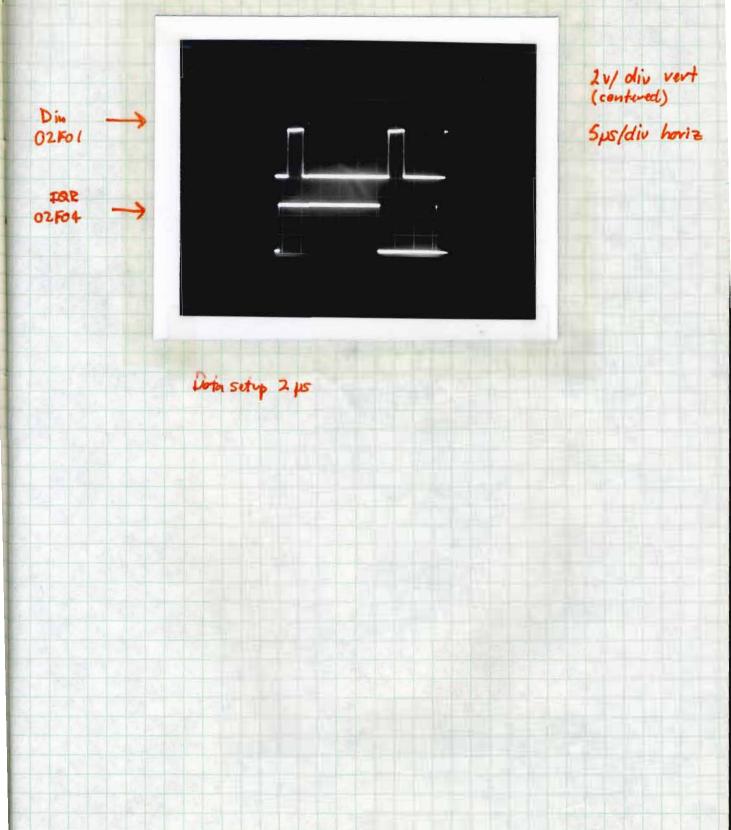

02FOI

DIA

IQR 02F04

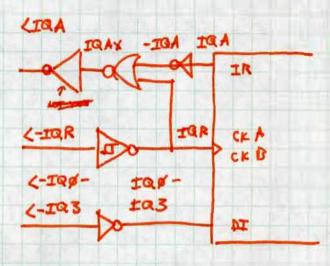

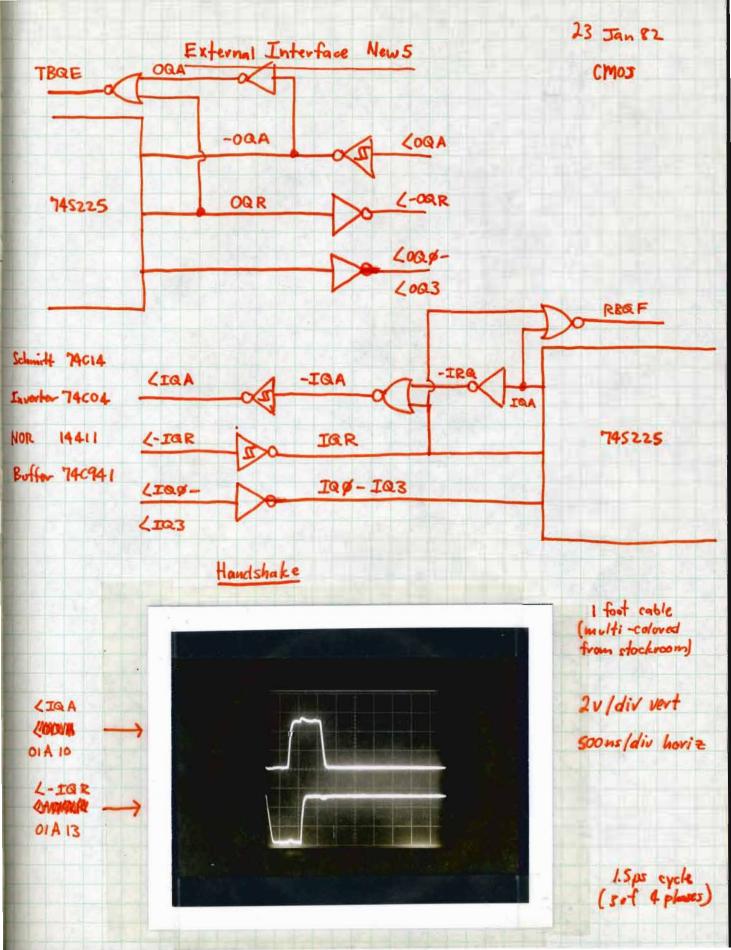

#### 23 Jan 82 Chos

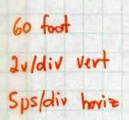

## 150 ns setup time

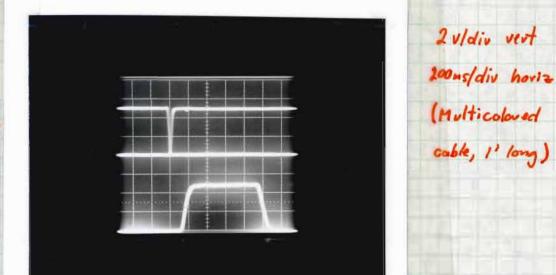

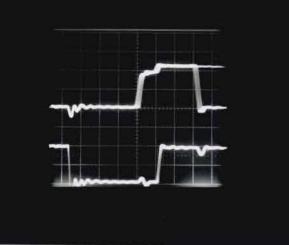

2 vidir sert

200ns/div hoviz

|          | LSTTL      | implementation |

|----------|------------|----------------|

| Schmitt  | 7414 (15)  |                |

| Inverter | 7404 (LS)  |                |

| Nor      | 14411      |                |

| Buffer   | 74244 (LS) |                |

IRP

IQR

## Botton Effect

## Only change 740941 for 7415244!

150-225 ns setup time change. Chos takes 75 ns longer than LSTTC.

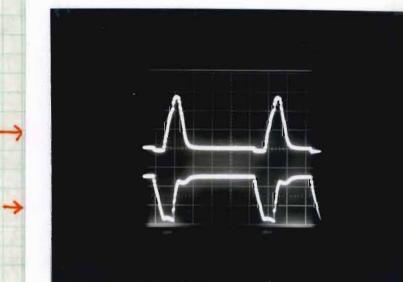

350ms cycle (3 of 4 phases)

## Data Setup

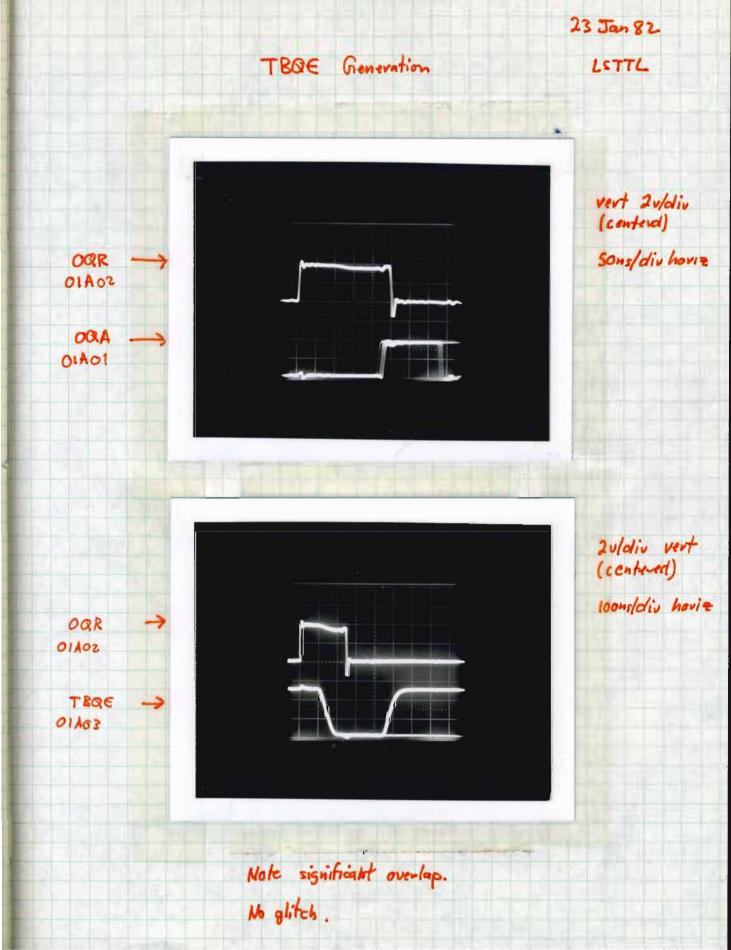

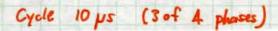

23 Jan 82 |STTL

2 v/div vert (centered) Sons/div hoviz

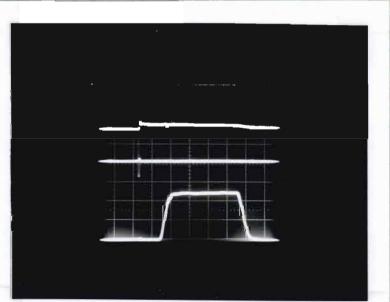

## Data Setup -30 hs

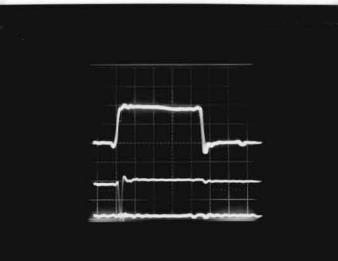

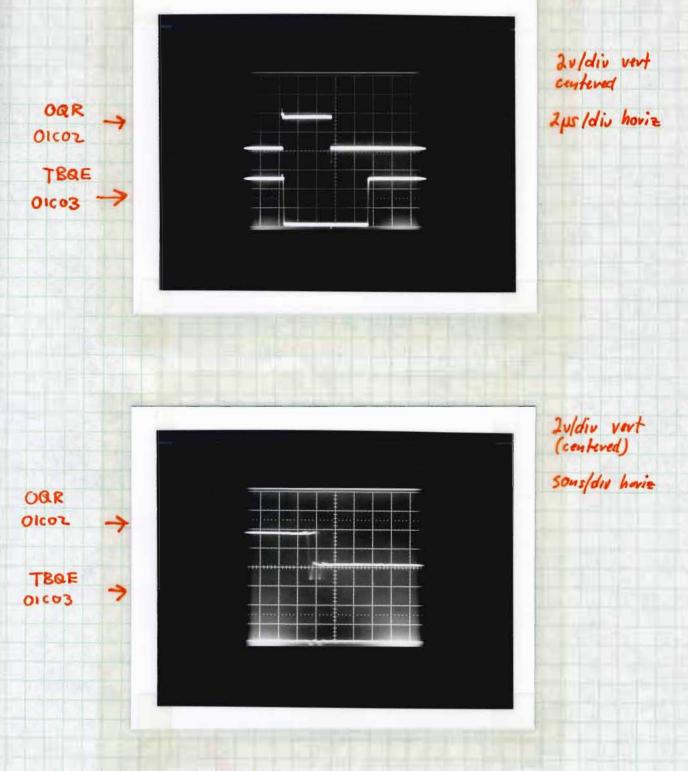

## Long Cable CMOS interface

ZIRA OIAIO

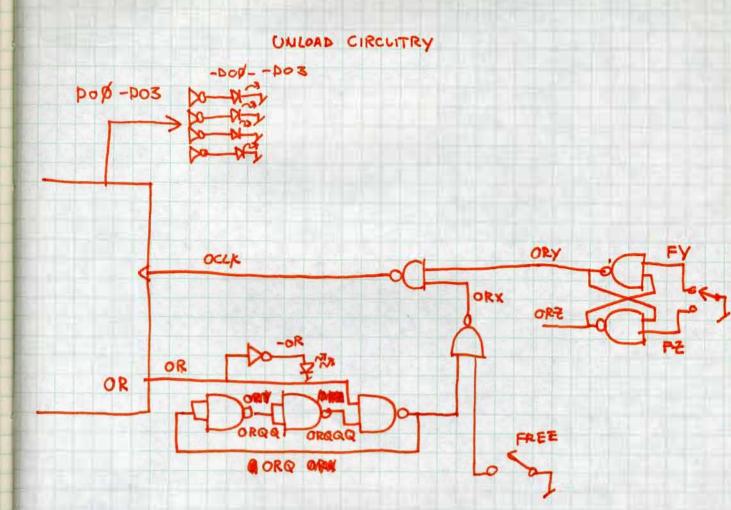

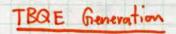

### TBRE Generation

### 23 Jan 82 CHOS Long

No glitch

23 Jan 82 Cros Long

# 86-12 a intempts

|   |                       | INT         | 594     |

|---|-----------------------|-------------|---------|

| ø | RX INTR               | 82          | 81      |

| 1 | TX INTR               | 90          | 88      |

| 2 | FIN W FARMAR THR      | IDATE T     | 91 79   |

| 3 | FANSY THE FUTOTOX CDC | 70          | 78      |

| 4 | BFI RK                | 69          | 714 77  |

| 5 | BFI TX                | 68          | 7111 76 |

| 6 | Prose TAX FIFD TX     | W4 66       | W 15    |

| 7 | FUER AN FIFORX        | <b>W 65</b> | 4 74    |

256

An interesting RAM characteristic might be obtained by examping an entire RM row.

CAS

Locations on each row are separated by 256 addresses / SIZ bytes. Adjacent rows should be in a known (constant) state to prevent coupling.

he actually examine every 256 the byte due to the funny 128 refresh stuff.

Test: Zero 16 rows and analyze only the middle one. Use feedback to adjust delay to exact threshold of one bit and observe other bits: The particular bit of interest is known to drift 0=1. Feedback model:

stoge 1 exponentially increasing times (2<sup>m</sup>) until 1 bit claeved

Stagez successive approx. until convergence Stagez algorithm:

> Init jump = 1 dir = p count from before If direction change from last time then jump = 1 else jump = jump + (jumpt!)\*2 \$ if viller if bit = 1 then count= count jump if bit = \$ then count= count jump dir = bit Output row meb tested:

Results particular unit

5F8E on scores 0578 820A080080208A heatgun 20" CPU fails, probably justhot! heatgun 15" Might be unveliable?? Can 4 tell. 4393 8A0A2800002888 438E 8AQA2800002888

# Other unit

| 1A9F  | 2A2A0222A2A880              |

|-------|-----------------------------|

| IAAD  | AA2A02ZZA2A880              |

| IAOF  | 2A 2A0202A 2A 800           |

| 1952  | A A 2 A 0 2 0 2 A 2 A 8 8 0 |

| 1986  | 2A 2A0222AZA880             |

| 145 B | 2A 2 A 0 2 0 2 A 2 A 8 8 0  |

|      | First wit                        |

|------|----------------------------------|

| 414A | 0 A 0 A 2 8 0 0 0 0 2 0 8 8      |

| 4488 | 8 A 0 A 2 800 0 0 2 8 8 8        |

| 4298 | 8A8A280080288A                   |

| 3FB3 | 0A0A2800002888                   |

| 3437 | 8 A 8 A 2800002888 - POWER CYCLE |

## Speed Check

65,000 packets in 6 sec 10 K packets/sec 10K.16 160K bytes/sec

### Failure :

- Channel 4, receiver, band &

- \* Cobles swapped no effect

- \* Transmit FIFO no effect

- \* 4.956 V original

- 4.817 V still happens

- SISO V Still happens

- Channel 4, A001 still happens 3 sorry, Channel 1, 74004 still happens 5 wrong board

- \* Channel 4 14001 replaced still happens

- + Channel 4 14c14 & 14c04 Still happens

- \* Software swizzle of 445 still happens

- \* Extra software guard still happens

## 18 October 82

| Reported van                   | problem,                | CPU # 1                                                                                                          |           |

|--------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------|-----------|

| Flakiness att                  | he following ad         | dresses:                                                                                                         |           |

| 55AB                           | 75eB                    | D320                                                                                                             | D126 D927 |

| 67A8                           | 7789                    | D32.D                                                                                                            | DB24      |

| 5789                           | 7987                    | DSZA                                                                                                             | DB2s      |

| 5044<br>5645                   | 7885 ??                 | D528                                                                                                             | DD23      |

| 5DA3                           |                         | D728                                                                                                             |           |

| Program                        | R, 5804                 | D729                                                                                                             |           |

| ion : Replace                  | 8288                    | - no et                                                                                                          | fect      |

|                                | 7400/74657<br>7400 only |                                                                                                                  |           |

|                                | nothing -               | and the second |           |

|                                | TALSOO with ano         | Her 7400                                                                                                         |           |

| D52 B D9                       | 27                      |                                                                                                                  |           |

|                                | 741500 with 74          | HOO                                                                                                              | -gone     |

| Ocd 7400.                      | saved 741               | 100 left                                                                                                         | in        |

| ot:<br>IIFF3                   | 3)                      |                                                                                                                  | 23 oct 82 |

| 11 FF4<br>1 1 FF 3<br>1 1 F F4 | 59<br>17<br>8F          |                                                                                                                  |           |

|                                | Con                     | + laber                                                                                                          |           |

#### 23 Oct 82

Problem reported with 74HØØ.

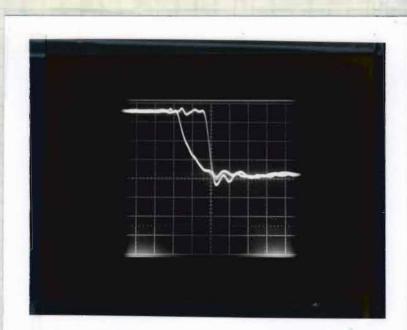

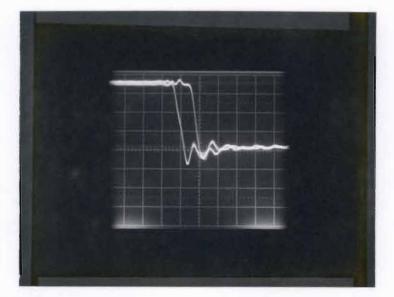

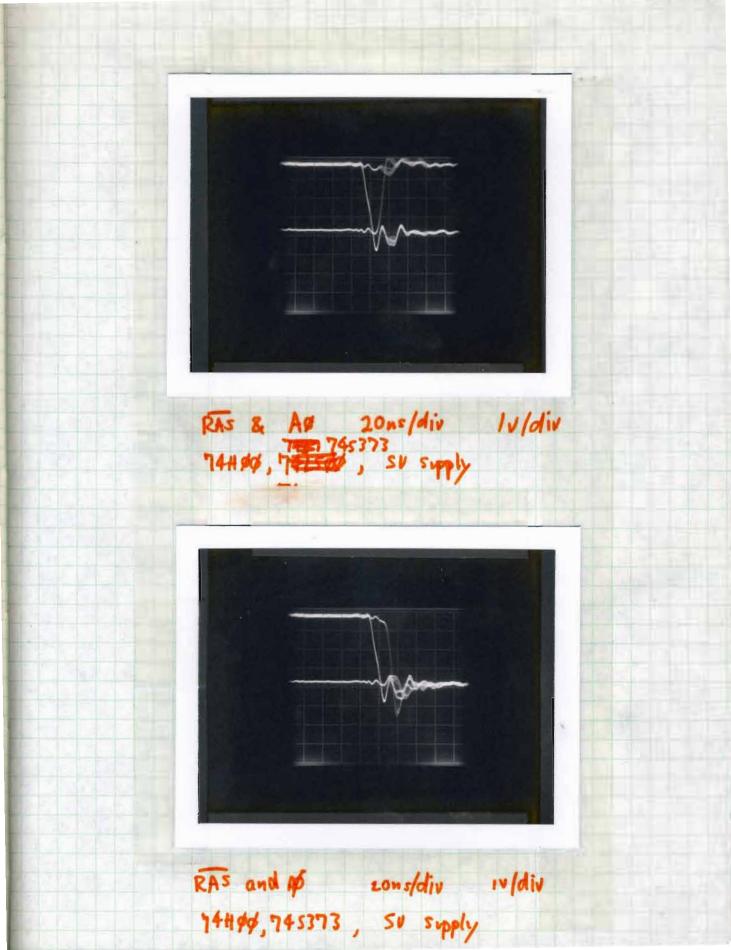

Analysis: With a 742500 the -RAS line is overloaded and the H=L transition is slow, inregular and delayed. With a 7400 it is better, 74400 better yet. 74500 rings alot, but probably due to scope.

Flokey board bas power supply voltage of 4. 5%.

Suggestions: Use 748373 for the RAS address driver. This improves timing under all circumstances.

quality can be verified). This fixes the H-2L -RAS transition.

If the RAM is slow, a 7404 instead of 74604 will give n3ns more RAS-CAS interval. The value of this is questionable

Use supply voltage = 5v.

Cuticisin: The overloaded 746500 is an engineering error. The source of the error was either sloppy debugging, or due to the prototype also using a 7400 (because 746500 is not available.

The 745373 17465373 is an either way, and the original engineering used all 65.

Supply voltage is not an engineering problem.

### 230482

Problem is definitely write related. Memory write fails and previous contents are still there. Where does it go??

- 1 FF3 31 1 FF4 57 1 FF4 6F 1 FF7 18

- Ram test program 123. Designed to allow detection of a mis-write. Checks until error then calculates syndrome of memory. Syndrome will reveal if and the address of an extraneous write. HOP -> no errors, no extra writes LSP\$ > STAY ervor 17A9 extra write STAT ENVI NO extra write STAY error 17 A9 extra write (2C) in MA9 of error STA9 Crivor NO extra write

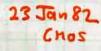

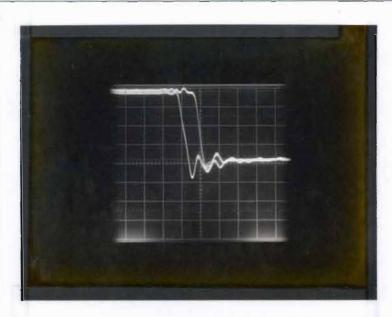

## 745373 - low address supply @5.0 V

RAS & CAS 20ms/dw Iv/div -RAS driver: 746500

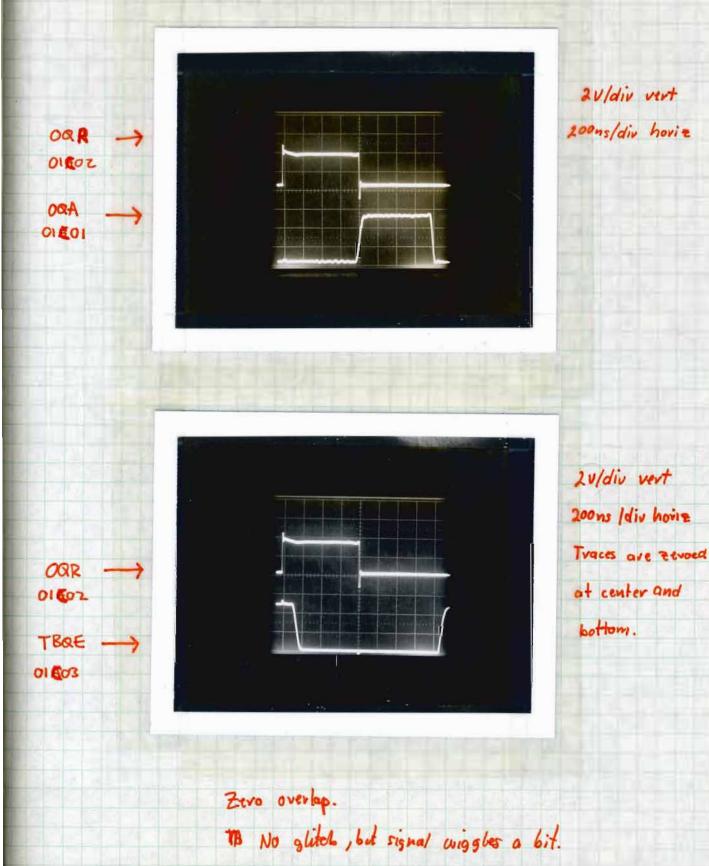

## RAG & CHE 20ns/ div 1v/div Using 74tlof, 745373, 4.74 V supply

RAS & CAS 20ns/dw W/dw Using 744#\$ ,745373 , 5.00 v supply

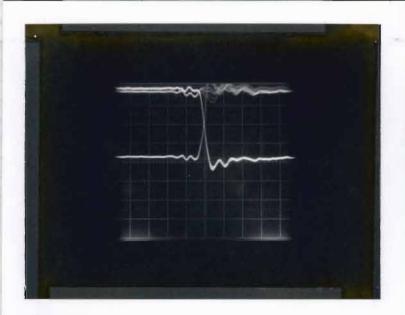

CAS & and Ad 20ns/div Iv/div 74H4, 745373, Sv supply

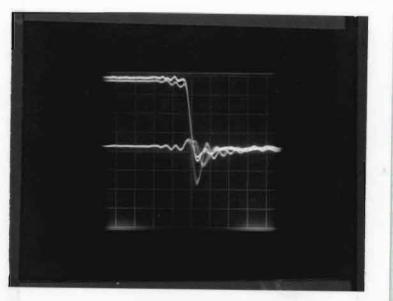

CAS 2 A\$ 20ns/div 10/div 74400 2745873, Sv supply

### 2300t82

## BFIB problem:

BFIB board screws up ram accesses to addresses XFFXX.

Problem: incorrect logic on BFIB board : opput drivers gated with I/o address without

Ilo occess:

Solution: -ACKEN 12 ACKEN DOINT POREN INTEN DO-BDEN

Added to BFIB to make BFIBZ. Board changed. Untested.