# **Marvell® PXA3xx Processors and Tavor P Processor**

**Boot ROM Reference Manual**

Doc. No. MV-S301208-00, Rev. -January 29, 2008

Document Classification: PUBLIC RELEASE

#### **Document Conventions**

#### Note

Provides related information or information of special importance.

#### Caution

Indicates potential damage to hardware or software, or loss of data.

#### Warning

Indicates a risk of personal injury.

#### **Document Status**

Doc Status: Preliminary Technical Publication: 2.3x

#### For more information, visit our website at: www.marvell.com

#### Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document.

Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;

2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for national security reasons by the EAR; and,

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such information.

Copyright © 2008. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon, Libertas, Link Street, NetGX, PHYAdvantage, Prestera, Raising The Technology Bar, The Technology Within, Virtual Cable Tester, and Yukon are registered trademarks of Marvell. Ants, AnyVoltage, Discovery, DSP Switcher, Feroceon, GalNet, GalTis, Horizon, Marvell Makes It All Possible, RADLAN, UniMAC, and VCT are trademarks of Marvell. All other trademarks are the property of their respective owners.

Intel XScale® is a trademark or registered trademark of Intel Corporation and its subsidiaries in the United States and other countries.

## **Table of Contents**

| 1   | Boot ROM Functional Overview                                                              | 11 |

|-----|-------------------------------------------------------------------------------------------|----|

| 1.1 | General Description                                                                       | 11 |

| 1.2 | Purpose Of This Document                                                                  | 11 |

| 1.3 | ROM Location, Size, and Mapping                                                           | 11 |

| 1.4 | Boot ROM Overview                                                                         | 12 |

|     | 1.4.1 Boot Process for Programmed Device                                                  | 13 |

| 2   | Boot ROM Differences                                                                      | 15 |

| 2.1 | Non-Trusted vs Trusted                                                                    | 17 |

| 2.2 | TIM/NTIM/OBM Support                                                                      | 17 |

|     | 2.2.1 Version 2.xx Platforms                                                              | 17 |

|     | 2.2.2 Version 3.xx Platforms                                                              | 18 |

| 2.3 | Boot ROM Address Maps                                                                     | 18 |

|     | 2.3.1 ISRAM Usage                                                                         | 18 |

|     | 2.3.2 OBM Usage                                                                           |    |

| 2.4 | PXA31x and Tavor Processor Auto-Boot                                                      |    |

|     | 2.4.1 Auto-Boot on Non-Trusted Platforms                                                  |    |

|     | 2.4.2 Auto-Boot on Trusted Platforms                                                      | 20 |

| 3   | Software Requirements                                                                     | 23 |

| 3.1 | Size Restrictions for the Device Keying Binary                                            | 23 |

| 3.2 | OEM Boot Module Requirements for NAND Platforms                                           | 23 |

|     | 3.2.1 NAND OEM Boot Module Size Restrictions                                              | 23 |

| 3.3 | NAND Bad/Relocation Block Table Definition                                                | 23 |

|     | 3.3.1 Bad Block Table Definition                                                          | 24 |

|     | 3.3.2 Bad Block Relocation Area                                                           | 25 |

| 3.4 | OEM Boot ROM Requirements for NOR Platforms                                               |    |

|     | 3.4.1 Traditional Boot Platforms                                                          |    |

|     | 3.4.2 Trusted Boot Platforms                                                              |    |

| 3.5 | Marvell® Wireless Trusted Module Driver Requirements                                      | 26 |

| 4   | Methods for Platform Provisioning                                                         | 27 |

| 4.1 | Non-Trusted Provisioning                                                                  | 27 |

|     | 4.1.1 Provisioning an Unprogrammed Non-Trusted Boot Platform Using a Device Keying Binary | 27 |

| 4.2 | Trusted Provisioning                                                                      | 28 |

|     | 4.2.1 Provisioning an Unprogrammed Trusted Boot Platform Using a Device Keying Binary     |    |

|     | 4.2.2 Device Keying Process                                                               | 30 |

| 5    | Boot ROM Implementation Details                                                                | 35   |

|------|------------------------------------------------------------------------------------------------|------|

| 5.1  | Non-Trusted Boot Address Map                                                                   | . 35 |

|      | 5.1.1 Trusted Boot Address Map                                                                 | . 36 |

|      | 5.1.2 NTIM/TIM Execution                                                                       | . 36 |

|      | 5.1.3 Requirements for the Wireless Trusted Module Save State                                  | . 37 |

|      | 5.1.4 Specific Requirements for NAND Platforms                                                 | . 38 |

| 5.2  | Boot ROM NAND Device Support                                                                   | . 39 |

|      | 5.2.1 Boot ROM NAND Device Recognition                                                         | . 39 |

| 5.3  | XIP Flash Support                                                                              | . 41 |

|      | 5.3.1 NOR Flash One-Time Programmable Register Usage                                           | . 42 |

| 5.4  | Managed NAND Memory Support                                                                    | . 42 |

| 5.5  | OneNAND Support                                                                                | . 43 |

|      | 5.5.1 Exiting Low Power Mode and Resets with OneNAND                                           | . 44 |

| 5.6  | mDOC Support                                                                                   | . 45 |

|      | 5.6.1 Exiting Low Power Mode and Resets with mDOC                                              | . 45 |

| 5.7  | Internal SRAM Usage                                                                            | . 46 |

| 5.8  | Handling Power Mode and Reset Transitions                                                      | . 46 |

|      | 5.8.1 Platform Boot Process for Watchdog Reset, Power on Reset, Low Power Exit, and GPIO Reset |      |

|      | 5.8.2 S2/D3/C4 Resume Requirements                                                             |      |

| 5.9  | Boot ROM: Processor-Specific Configurations                                                    | . 50 |

|      | 5.9.1 PXA32x Processor Register Settings                                                       | . 52 |

|      | 5.9.2 Other Registers                                                                          | . 54 |

| 5.10 | PXA31x Processor Register Settings                                                             | . 54 |

| 5.11 | PXA30x Processor Register Settings                                                             | . 56 |

| 5.12 | Tavor Processor Implementation Details                                                         | . 58 |

| 5.13 | Error Conditions                                                                               | . 60 |

| 5.14 | Hints And Tips                                                                                 |      |

|      |                                                                                                |      |

| 6    | Non-Trusted Image Module                                                                       | 63   |

| 6.1  | Non-Trusted Image Module Format                                                                | . 64 |

|      | 6.1.1 Version Information                                                                      | . 64 |

|      | 6.1.2 Flash Information                                                                        | . 65 |

|      | 6.1.3 NTIM Sizing Information                                                                  | . 65 |

|      | 6.1.4 Image Information Array                                                                  | . 65 |

|      | 6.1.5 Reserved[SizeOfReserved]                                                                 | . 66 |

| 6.2  | Reserved Area                                                                                  | . 66 |

|      | 6.2.1 Reserved Area Header                                                                     | . 66 |

|      | 6.2.2 Reserved Area Packages                                                                   | . 66 |

| 6.3  | Predefined Packages for Reserved Area                                                          | . 67 |

|      | 6.3.1 GPIO Packages                                                                            | . 67 |

|      | 6.3.2 UART/USB Protocol Packages                                                               | . 68 |

|      | 6.3.3 DDR Package                                                                              |      |

|      | 6.3.4 Resume Package                                                                           | . 68 |

|     | 6.3.5 USB Vendor Request Package                                   | 68 |

|-----|--------------------------------------------------------------------|----|

| 6.4 | Summary of Predefined Package IDs for the Non-Trusted Image Module | 69 |

| 7   | Trusted Image Module                                               | 71 |

| 7.1 | Trusted Image Module Format                                        | 72 |

|     | 7.1.1 Version Information                                          | 72 |

|     | 7.1.2 Flash Information                                            | 73 |

|     | 7.1.3 TIM Sizing Information                                       | 73 |

|     | 7.1.4 Image Information Array                                      | 73 |

|     | 7.1.5 Key Information Array                                        | 74 |

|     | 7.1.6 Reserved[SizeOfReserved]                                     | 74 |

|     | 7.1.7 Platform Digital Signature Information                       |    |

| 7.2 | Reserved Area                                                      |    |

|     | 7.2.1 Reserved Area Header                                         | 75 |

|     | 7.2.2 Reserved Area Packages                                       | 75 |

| 7.3 | Predefined Packages                                                | 75 |

|     | 7.3.1 GPIO Packages                                                | 76 |

|     | 7.3.2 UART/USB Protocol Packages                                   |    |

|     | 7.3.3 DDR Package                                                  | 77 |

|     | 7.3.4 Resume Package                                               |    |

|     | 7.3.5 Autobind Package                                             |    |

|     | 7.3.6 USB Vendor Request Package                                   |    |

| 7.4 | Hashing Methods                                                    | 78 |

| 7.5 | Summary of Predefined Package IDs for the Trusted Image Module     | 78 |

| 8   | Non-Trusted Operation                                              | 81 |

| 8.1 | Operation with a Non-Trusted Image Module                          | 81 |

|     | 8.1.1 NAND Flash                                                   |    |

|     | 8.1.2 XIP Flash on Chip Select 2                                   | 81 |

|     | 8.1.3 XIP Flash on Chip Select 0                                   |    |

|     | 8.1.4 Samsung OneNAND* Flash                                       | 82 |

|     | 8.1.5 SanDisk <sup>*</sup> Flash                                   | 83 |

|     | 8.1.6 Image Downloading                                            | 83 |

|     | 8.1.7 Preprogrammed Flash Requirements                             | 83 |

| 8.2 | Operation Without a Non-Trusted Image Module                       | 84 |

|     | 8.2.1 NAND Flash                                                   | 84 |

|     | 8.2.2 XIP Flash on Chip Select 2                                   | 84 |

|     | 8.2.3 XIP Flash on Chip Select 0                                   | 84 |

|     | 8.2.4 OneNAND Flash                                                | 85 |

|     | 8.2.5 MSystems Flash                                               |    |

|     | 8.2.6 Preprogrammed Flash Requirements                             | 85 |

| 9    | Trusted Boot Operation                    | 87  |  |  |

|------|-------------------------------------------|-----|--|--|

| 9.1  | Trusted Boot Usage Cases                  | 87  |  |  |

|      | 9.1.1 Trusted Image Module Validation     | 88  |  |  |

|      | 9.1.2 NAND Flash                          | 89  |  |  |

|      | 9.1.3 XIP Flash on Chip Select 2          | 89  |  |  |

|      | 9.1.4 XIP Flash on Chip Select 0          | 89  |  |  |

|      | 9.1.5 Samsung OneNAND™ Flash              |     |  |  |

|      | 9.1.6 SanDisk <sup>*</sup> Flash          |     |  |  |

|      | 9.1.7 Image Downloading                   |     |  |  |

| 9.2  | Preprogrammed Flash Requirements          |     |  |  |

| 9.3  | JTAG Re-enablement                        | 92  |  |  |

| 10   | TIM/NTIM Support For Memory Devices       | 93  |  |  |

| 10.1 | NAND Flash                                | 93  |  |  |

| 10.2 | XIP Flash on Chip Select 2                | 93  |  |  |

| 10.3 | OneNAND Flash                             | 94  |  |  |

| 10.4 | SanDisk Flash                             | 94  |  |  |

| 11   | Communication Protocol                    | 95  |  |  |

| 11.1 | Preamble                                  |     |  |  |

| 11.2 |                                           |     |  |  |

| 11.3 |                                           |     |  |  |

| 11.4 |                                           |     |  |  |

| 11.5 | Responses                                 |     |  |  |

| 11.6 | •                                         |     |  |  |

| 11.7 | <u> </u>                                  |     |  |  |

| 11.8 |                                           |     |  |  |

| 12   | Host Tools                                | 103 |  |  |

| 12.1 | Trusted Image Tools                       |     |  |  |

| 12.2 | -                                         |     |  |  |

| 12.3 |                                           |     |  |  |

| 13   | Other Boot ROM Features                   | 105 |  |  |

| 13.1 | Optional Settings in the TIM/NTIM Modules |     |  |  |

| 13.2 | Tamper Recovery Mechanisms                |     |  |  |

| Retu | urn Code Definitions 107                  |     |  |  |

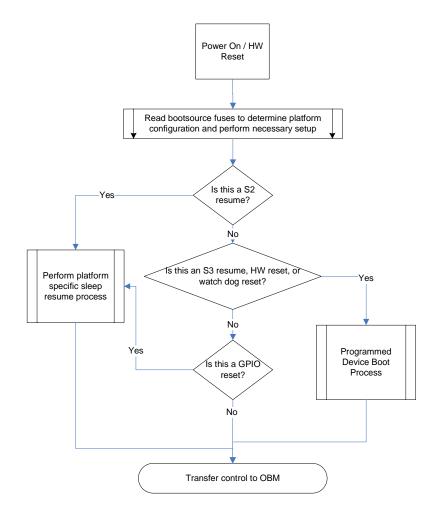

| Figure 1:  | PXA3xx Top Level Boot ROM Flow                                                                                               | 13 |

|------------|------------------------------------------------------------------------------------------------------------------------------|----|

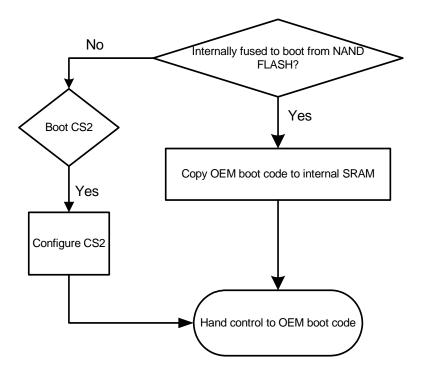

| Figure 2:  | Boot Process Flow Chart                                                                                                      | 14 |

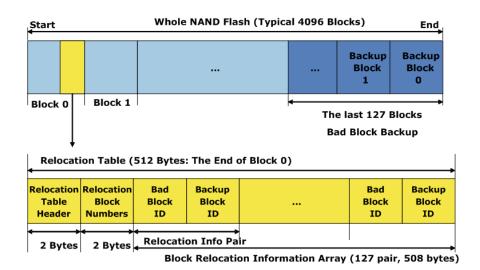

| Figure 3:  | Block 0 Layout on a Samsung K9K1216Q0C* with 16-KB Block Sizes and 512-Byte Pages24                                          |    |

| Figure 4:  | Example of Bad Block Table NAND Flash Mapping in Use — Small Block NAND Flash Type: Samsung K9K1216Q0C* (Device ID = 0x46)25 |    |

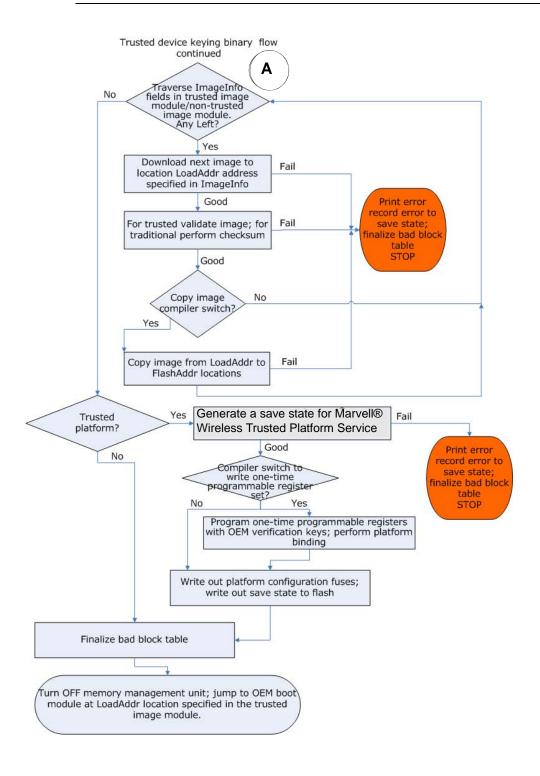

| Figure 5:  | Device Keying Binary Requirements Flow for an Unprogrammed System                                                            | 32 |

| Figure 6:  | Device Keying Binary Requirements Flow for an Unprogrammed System (cont)                                                     | 33 |

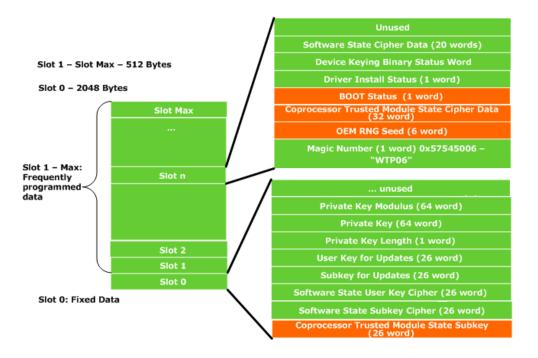

| Figure 7:  | Coprocessor Trusted Module Save State Implementation                                                                         | 38 |

| Figure 8:  | Electronic Signature Requirements                                                                                            | 41 |

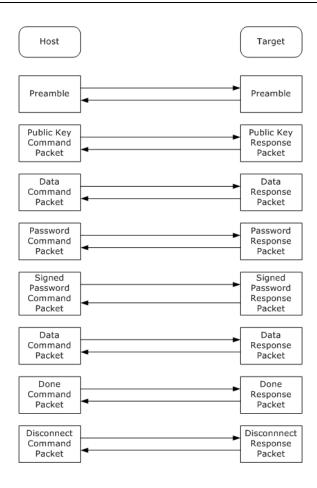

| Figure 9:  | JTAG Re-enable Flow Diagram                                                                                                  | 96 |

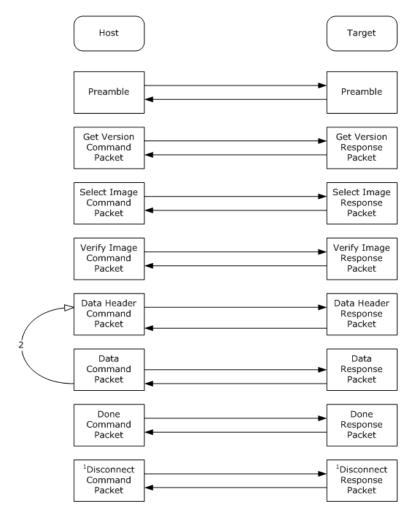

| Figure 10: | Download Flow Diagram                                                                                                        | 97 |

## List of Tables

| Table 1:  | Version 2.xx and Version 3.xx High Level Differences                | 15 |

|-----------|---------------------------------------------------------------------|----|

| Table 2:  | Version 2.xx ISRAM usage                                            | 18 |

| Table 3:  | Version 3.xx ISRAM Usage                                            | 18 |

| Table 4:  | Version 2.xx OBM Usage                                              | 19 |

| Table 5:  | Version 3.xx OBM usage                                              | 19 |

| Table 6:  | Relocation Table Addresses                                          | 24 |

| Table 7:  | Non-Trusted Image Module Locations                                  | 35 |

| Table 8:  | OEM Boot Module (OBM) locations when No NTIM is used                | 35 |

| Table 9:  | Trusted Image Module Locations for Trusted Boot                     | 36 |

| Table 10: | OEM Boot Module Sizes Without Marvell Bad Block Management          | 38 |

| Table 11: | Small Block Devices                                                 | 40 |

| Table 12: | NAND Flash Controller Initial Register Settings                     | 41 |

| Table 13: | NAND Command Set                                                    | 41 |

| Table 14: | Flash Commands Supported by the Boot ROM                            | 42 |

| Table 15: | OneNAND Device ID Support                                           | 44 |

| Table 16: | Overview of Resets and Power Modes                                  | 46 |

| Table 17: | PXA32x Processor Implementation Settings                            | 52 |

| Table 18: | Chip Select 2 Setup                                                 | 53 |

| Table 19: | Additional PXA32x Processor Ball Values Set for NAND Platforms Only | 53 |

| Table 20: | FFUART Pins                                                         | 53 |

| Table 21: | USB Single Ended Pins                                               | 53 |

| Table 22: | During Sleep (S3/D3/C4 mode) Resume                                 | 54 |

| Table 23: | PXA31x Processor Implementation Settings                            | 54 |

| Table 24: | Additional PXA31x Processor Ball Values Set for NAND Platforms Only | 55 |

| Table 25: | USB Port ULPI Pins                                                  | 55 |

| Table 26: | FFUART Pins                                                         | 55 |

| Table 27: | PXA30x Processor Implementation Settings                            | 56 |

| Table 28: | Chip Select 2 Setup                                                 | 57 |

| Table 29: | Additional PXA30x Processor Ball Values Set for NAND Platforms Only | 57 |

| Table 30: | FFUART Pins                                                         | 57 |

| Table 31: | USB Single Ended Pins                                               | 57 |

| Table 32: | Tavor Processor Register Settings                                   | 58 |

| Table 33: | Additional Tavor Processor Ball Values Set for NAND Platforms Only  | 59 |

| Table 34: | FFUART Pins (Primary Location)                                      | 59 |

| Table 35: | FFUART Pins (Secondary Location)                                    | 59 |

| Table 36: | USB 2.0 Pins                                                        | 59 |

| Table 37: | BootFlashSign Definitions                                           | 65 |

| Table 38: | Reserved Area Predefined Package ID's                               |    |

| Table 39: | BootFlashSign Definitions                                           |    |

| Table 40: | Reserved Area Predefined Package ID's                               |    |

| Table 41: | Preamble                                                            |    |

| Table 42: | Host Commands                | 99  |

|-----------|------------------------------|-----|

|           | Target Responses             |     |

|           | Status Codes                 |     |

| Table 45: | Return Codes and Definitions | 107 |

## 1 Boot ROM Functional Overview

### 1.1 General Description

The Boot ROM software is preloaded into the processors' internal ROM. The Boot ROM is an enabling component of the Marvell Trusted Boot solution. The Boot ROM provides support for the implementation of processors with Intel XScale<sup>®</sup> technology for the usage cases described in the following sections. When operating in a non-trusted mode, the Boot ROM supports loading software from various devices as part of the boot process. When operating in a trusted mode, the Boot ROM is considered the root of trust for the platform and it handles the initialization of the Marvell<sup>®</sup> Wireless Trusted Module (Marvell<sup>®</sup> WTM) subsystem.

Because the Boot ROM is configured at manufacture, no changes can be made to the boot configuration of the Boot ROM. The correct boot configuration must be ordered from Marvell for a given platform architecture however some processors support an "auto-boot feature and are not configured to one boot memory for the first boot. Refer to 2 "Boot ROM Differences" for details on auto-boot support.

The list of supported boot configurations and how to configure the PXA31x auto-boot feature are discussed in this document. The Boot ROM implements a common set of functionality across all implementations of the PXA3xx processor family and Tavor processor. Refer to the specific processor developers manual for details of the processor features.

### 1.2 Purpose Of This Document

This document covers the operational details of the Boot ROM for the PXA3xx processor family and Tavor processors. System- level dependencies are also covered such as:

- Booting the platform

- Choice of NAND memory and how the Boot ROM supports NAND

- Managed NAND support This is NAND memory with a NOR-like bus interface such as Samsung OneNAND and Sandisk mDOC.

- Software requirements for both trusted and non-trusted platforms

- Boot ROM versions and feature sets

- Exiting low power modes

- Host Tools

- JTAG Re-enablement

### 1.3 ROM Location, Size, and Mapping

The processor family has 48 KB of internal ROM, which is used for the Boot ROM. Anytime the processor goes through a power transition that causes a jump to the reset vector, the Boot ROM is mapped to two different address spaces, via hardware mechanisms:

- 0x0000 0000 0x0000 BFFF

- 0x5E00 0000 0x5E01 FFFF

The physical ROM is mapped to the  $0x5E00\_0000 - 0x5E01\_FFFF$  address space in the processor memory map. The  $0x0000\_0000 - 0x00000\_BFFF$  address space is a virtual memory mapping implemented by the hardware to locate the vector table at the correct address for the processor core. After any power transition which causes the processor core to jump to the reset vector, the Boot ROM is the first code to execute on the processor.

While the Boot ROM is running and is mapped to  $0x0000\_0000 - 0x00000\_BFFFF$ , external flash memory mapped to this region is not accessible. Before handing control to any image, the Boot ROM remaps the  $0x0000\_0000 - 0x0000\_BFFFF$  address space to external flash memory on chip select 0 to make access to this flash memory possible. Once this address space is remapped to the external flash, higher layers of software must accommodate the vector table by setting up a vector table in an appropriate location depending on the usage model chosen. Refer to the specific processor developers manual for more details on the requirements for setting up the vector table.

#### 1.4 Boot ROM Overview

After reset, the Boot ROM performs the essential initialization including programming the clocks, GPIO settings, and the interrupt controller. The Boot ROM verifies whether the reset reason was a return-from-hardware reset (HWR), Watchdog reset (WDR), or a resume-from-S3 power-state reset.

#### Note

After V3.20 Boot ROM, the Boot ROM does not perform verification to identify the last reset transition. All Version 2.xx Boot ROMs perform this task. Therefore, for the application processors, only the PXA320 and PXA30x A1 perform this procedure as indicated in Figure 1.

If the reset is not attributable to any of these reasons listed above, the Boot ROM uses the platform configuration data that is provided by the bootsource fuses to determine how to resume the platform from an S2/D3/C4 state or GPIO reset.

For more details, refer to Chapter 2 and Chapter 3 of this document.

Figure 1 shows the execution flow of the Boot ROM from reset. All processor resets are directed to the Boot ROM, from where the appropriate path to resume or boot is determined.

Figure 1: PXA3xx Top Level Boot ROM Flow

### 1.4.1 Boot Process for Programmed Device

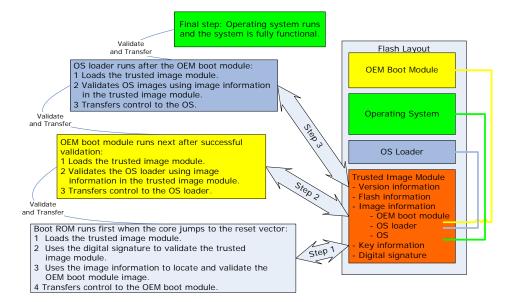

The Boot ROM identifies the platform configuration fuses and transitions to the external flash. For platforms using NAND flash, the OEM boot module (OBM) is copied from Block 0 of the NAND flash to internal SRAM at and control is transferred to the OBM. For platforms using NOR flash, control is transferred to the external flash on nCS2 of the DFI bus. See Figure 2 (Boot Process Flow Chart).

Figure 2: Boot Process Flow Chart

There are many more details that are noted in later chapters. This section is the introduction and there are differences between the Boot ROM revisions and the different processor silicon steppings; however the main flow of execution is the same.

## 2

## **Boot ROM Differences**

This section provides information on the differences between Boot ROM version 2.x and 3.x. The Boot ROM is implemented in all of the PXA3xx family processors and the Tavor processor. Table 1 describes which processor is implemented with the different versions of the Boot ROM.

Table 1: Version 2.xx and Version 3.xx High Level Differences

| Processor<br>Stepping                                                 | PXA32x B1/B2;<br>Tavor A0 | PXA32x C0       | PXA301 A1<br>and<br>PXA300 A1 | PXA31x A1;<br>Tavor B0.a                                                        | PXA31x A2;<br>PXA302;<br>PXA312 PoP<br>Tavor B0.b                                                                                                                 |

|-----------------------------------------------------------------------|---------------------------|-----------------|-------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Boot ROM<br>Version                                                   | Version<br>2.22           | Version<br>3.38 | Version<br>3.19               | Version<br>3.27                                                                 | All Version 3.32<br>except PXA31x A2<br>Version 3.33                                                                                                              |

|                                                                       |                           | Non-Ti          | rusted                        |                                                                                 | Trusted and<br>Non-Trusted                                                                                                                                        |

| JTAG<br>Re-enablement<br>(only for trusted<br>platforms) <sup>1</sup> | No                        | No              | No                            | No                                                                              | Yes                                                                                                                                                               |

| Download via<br>USB1.1<br>(differential/SE)                           | No                        | No              | No                            | Not applicable for PXA31x A1; Yes (default) for Tavor B0.a                      | Yes (default) except for PXA31x A2                                                                                                                                |

| Download via<br>USB2.0                                                | No                        | No              | No                            | Yes (default) for PXA31x; Yes with (TIM)/ (NTIM) override but only for Tavor B0 | Not applicable for PXA302; Yes with TIM/NTIM override but only for Tavor B0; Yes (default) for PXA310 A2                                                          |

| Download via<br>USB OTG                                               | No                        | No              | No                            | No                                                                              | No                                                                                                                                                                |

| Download via<br>UART                                                  | No                        | No              | No                            | Yes                                                                             | Yes                                                                                                                                                               |

| TIM/NTIM                                                              | No                        | No              | NTIM                          | NTIM                                                                            | TIM/NTIM                                                                                                                                                          |

| Support                                                               |                           |                 |                               |                                                                                 | 1. The BootFlashSign field as defined in the TIM/NTIM header must be included. Previous Boot ROM versions did not use this field.  2. ImageSizeToCRC must be 0x00 |

|                                                                       |                           |                 |                               | M can also operate withe V2.xx IVM/OBM m                                        |                                                                                                                                                                   |

#### Table 1: Version 2.xx and Version 3.xx High Level Differences (Continued)

| Processor<br>Stepping                                            | PXA32x B1/B2;<br>Tavor A0 | PXA32x C0           | PXA301 A1<br>and<br>PXA300 A1 | PXA31x A1;<br>Tavor B0.a                   | PXA31x A2;<br>PXA302;<br>PXA312 POP<br>Tavor B0.b                                                                                                                    |

|------------------------------------------------------------------|---------------------------|---------------------|-------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Boot ROM<br>Version                                              | Version<br>2.22           | Version<br>3.38     | Version<br>3.19               | Version<br>3.27                            | All Version 3.32<br>except PXA31x A2<br>Version 3.33                                                                                                                 |

|                                                                  |                           | Non-Ti              | usted                         |                                            | Trusted and<br>Non-Trusted                                                                                                                                           |

| Tamper<br>Recovery                                               | No                        | No                  | No                            | No                                         | Yes done in WTPSP                                                                                                                                                    |

| Sandisk M-DOC<br>H3 and Samsung<br>OneNAND                       | Yes, using XIP area       | Yes, using XIP area | Yes, using<br>XIP area        | Yes, using XIP area                        | Yes, with NTIM and<br>TIM support                                                                                                                                    |

| The drivers are not sees these devices from XIP area, then       |                           | as NOR memory.      | The OBM boot m                | orocessor initially<br>odule can be loaded | The drivers are integrated into the Boot ROM. At Boot time the processor can fully access the managed NAND memory. Refer to Section 5.5 and Section 5.6 for details. |

| NAND Interface Timing Configuration - Programmed in NDTR1CS0[tR] | 39.23uS                   | 39.23uS             | 38.76uS                       | Tavor - 39.23uS<br>PXA31x A1 -<br>38.76uS  | 52.4uS                                                                                                                                                               |

| MMC/SD Boot                                                      | No                        | No                  | No                            | No                                         | No                                                                                                                                                                   |

| Auto-Boot                                                        | No                        | Yes <sup>2</sup>    | No                            | Yes                                        | Yes                                                                                                                                                                  |

| Boot from nCS0 <sup>3</sup> (Static CS)                          | No                        | No                  | No                            | PXA31x only                                | PXA31x only                                                                                                                                                          |

| ONFI <sup>4</sup> Compliant<br>NAND Reset<br>Command 0xFF        | No                        | Yes                 | No                            | No                                         | Yes                                                                                                                                                                  |

- 1. The JTAG port is enabled on all non trusted platforms. Refer to JTAG re-enablement in Section 9.3, JTAG Re-enablement, on page 100.

- 2. Version 3.xx Auto-Boot mode is not backward compatible with Version 2.xx. See Note in Auto-Boot in Non-Trusted Platforms.

- 3. XIP NOR only, not managed NAND (OneNand + mDOC)

- 4. ONFI is the Open NAND Flash Interface specification www.onfi.org

### 2.1 Non-Trusted vs Trusted

Version 2.xx implements only the non-trusted boot process. A non-trusted platform is defined as a platform that does not use the Wireless Trusted Module (WTM) to validate the integrity of the OS image.

Version 3.xx supports both trusted and non-trusted boot process. A trusted platform does use the WTM for security encryption and validation of an uncompromised OS image.

#### 2.2 TIM/NTIM/OBM Support

#### 2.2.1 Version 2.xx Platforms

Version 2.xx platforms have-hard coded requirements for booting to the OEM boot module (OBM) image. These requirements impose several restrictions on the platform for NAND boot, specifically:

- A maximum size limit of two blocks can be used for OBM, restricting the size

- Two words of offset must be pre-pended to the OBM before programming to the NAND Flash

- For an OBM of one block in size:

- Set NAND Flash address 0x0 to 0x0000 0008.

- Set NAND Flash address 0x4 to 0x0000\_0000.

- Burn the OEM boot module image to NAND Flash address at 0x8.

- For an OBM of two blocks in size, follow the same as the steps above for OBM of one block in size: however, set NAND Flash address 0x4 to address of Block 2.

- All unused pages within Block 0, after the OBM image, must be programmed with 0x0.

- Runtime location is fixed in the ISRAM

- Use of an NTIM is not supported

If the first two words are not written as 0x0 and the unused pages in Block 0 are also not written as 0x0, then the system fails to boot. Not performing this action creates inconsistent Error-Correcting Code (ECC) information so the Boot ROM aborts the boot process.

#### 2.2.2 **Version 3.xx Platforms**

Version 3.xx trusted boot platforms use the TIM and NTIM. These headers store information about the flash layout and runtime locations for the platform software. The header format is compatible between trusted and non-trusted systems allowing reuse of images. The difference between a TIM and an NTIM is the type of information within the header. The TIM holds security information in addition to the flash layout and runtime information.

When a header (NTIM or TIM) is used, the requirement to program all unused pages as specified for V2 Boot ROM is no longer necessary. The header contains the size of the OBM image. If not using a header, Marvell recommends that the unused pages be programmed with 0x0.

V3.xx Boot ROM also has a backward compatibility mode such that the OBM/IVM from V2 may be used as an option.

#### 2.3 **Boot ROM Address Maps**

#### 2.3.1 ISRAM Usage

This section shows the internal SRAM address usage. Approximately 4 KB of internal SRAM was freed up in the data/stack area of the Boot ROM and made available for OBM downloading in V3.xx.

#### Table 2: Version 2.xx ISRAM Usage

| ISRAM Address | Size  | Usage |

|---------------|-------|-------|

| 0x5C00_0000   | 32 KB | Caddo |

#### Table 2: Version 2.xx ISRAM Usage (Continued)

| ISRAM Address | Size          | Usage               |

|---------------|---------------|---------------------|

| 0x5C00_8000   | 48 KB         | Boot ROM data/stack |

| 0x5C01_4000   | Rest of ISRAM | Image download      |

#### Table 3: Version 3.xx ISRAM Usage

| ISRAM Address | Size          | Usage               |

|---------------|---------------|---------------------|

| 0x5C00_0000   | 32 KB         | Caddo               |

| 0x5C00_8000   | 44 KB         | Boot ROM data/stack |

| 0x5C01_3000   | Rest of ISRAM | Image download      |

### 2.3.2 OBM Usage

Version 2.xx has fixed offsets for OBM images based on flash type used. The area in the Static Chip Select 0 (nCS0) from 0x0 to 0xBFFF is dual-mapped to either Boot ROM or external flash, which can make programming difficult. The Boot ROM also uses the first two words for its own operations so the OEM system boot module (OSBM) images had to be manually shifted when programming.

#### Table 4: Version 2.xx OBM Usage

| Boot Device            | OBM location in device | Runtime location of OBM |

|------------------------|------------------------|-------------------------|

| Chip Select 2 - nCS2   | Block 0 offset 0x0     | 0x1000_0000             |

| NAND device on ND_nCS0 | Block 0 offset 0x8     | 0x5C01_4000             |

Version 3.xx is backward compatible with version 2.xx. Certain requirements, such as the boot state fuses, must be programmed and the offsets in Table 5 must be adhered to. For NAND Flash, the OBM size is limited to one block.

Table 5: Version 3.xx OBM Usage

| Boot Device            | OBM location in device | Runtime location of OBM |

|------------------------|------------------------|-------------------------|

| Chip Select 0 - nCS0   | block 0 offset 0xC000  | 0x0000_C000             |

| Chip Select 2 - nCS2   | block 0 offset 0x0     | 0x1000_0000             |

| NAND device on ND_nCS0 | block 0 offset 0x0     | 0x5C01_3000             |

## 2.4 PXA31x and Tavor Processor Auto-Boot

All PXA3xx processors and Tavor processors have been pre-programmed prior to customer shipments, which requires customers to specify the required boot memory such as XIP NOR Flash boot from nCS2 and x8 or x16 NAND boot devices.

However, the PXA31x A1 and Tavor B0 stepping do not operate in this way. These processors are shipped without the boot type fuses configured, which allows flexibility in customer builds for using the same device in multiple platforms with different boot-memory configurations.

Auto-boot is a process whereby the Boot ROM probes all the valid boot devices for a valid header file (either a TIM or NTIM). Once this header is found, it is used to boot the system. The Boot ROM does not search for multiple headers. The first valid header that is found is used to boot the system.

The boot memories are probed in the following order:

- XIP on nCS2

- XIP on nCS0 (XIP NOR only; not Managed NAND + mDOC)

- x16 NAND on ND\_nCS0

- x8 NAND on ND\_nCS0

- Samsung OneNAND on nCS2

- Sandisk mDOC on nCS2

If a valid TIM or NTIM is not found, then the Boot ROM waits for a download operation over USB or UART. This operation would be downloading an image from a host over a USB or UART to the platform. If the TIM or NTIM is not found, this would indicate that the flash memory is not programmed.

If the Boot ROM does not find a valid header and the image download is successful, the subsequent boot probes each boot memory (as described above) but now the Boot ROM finds the valid TIM/NTIM and the boot process continues.

#### 2.4.1 Auto-Boot on Non-Trusted Platforms

The auto-boot process described in Section 2.4, PXA31x and Tavor Processor Auto-Boot occurs for every boot or reset exit on non-trusted platforms. Below is the list of resets and mode exits:

- SOD start of day

- Hardware reset

- Watchdog reset

- GPIO reset

- S2/D3 exit\*\*

- S3/D4 exit

\*\*Software may optionally configure a D3 resume to internal SRAM. If enabled, then the "probing" is bypassed. This option is enabled in the NTIM/TIM package.

Note

For PXA32x C0 processor, Auto-Boot feature does not allow for backward compatibity between Boot ROM version 2.xx and version 3.xx. In Auto-Boot mode, the PXA32x C0 processor requires the same memory addresses as the PXA31x processor. The PXA32x C0 is fully backward compatible with PXA32x B2 in fused mode only.

#### 2.4.2 Auto-Boot on Trusted Platforms

The auto-boot process described in Section 2.4, PXA31x and Tavor Processor Auto-Boot occurs only for the first boot if a valid TIM is found for a Trusted Boot. If the Boot ROM fails to find a valid header, then the Boot ROM waits for an image download to occur.

Once a TIM is found and has been successfully validated, the platform is bound, which means that the fuses have been configured permanently. All subsequent boots are fused boots and the probing (auto-boot feature) of each memory device does not occur.

The auto-boot feature has certain platform requirements that must be enabled. For fuses to be configured, VCC\_MVT must be raised to 1.9V through a sequence of PWR I2C commands sent to the PMIC over the PWR\_I2C bus.

A trusted platform must be architected such that the Services Power Management Unit sends I2C commands to the PMIC. The processor sends these command sequences automatically. There are internal handshaking and acknowledgement tokens passed between Caddo, the Boot ROM, and the Services unit to enable the correct sequencing of I2C commands and voltage changes to VCC\_MVT. This sequencing is isolated and cannot be reconfigured or changed in any way.

The basic steps of operation are as follows:

- 1. The Auto-Boot procedure selects the valid boot memory by the Boot ROM finding a valid TIM header.

- VCC\_MVT is currently at default value -> 1.8V

- 2. MDTV2 is loaded with the value 0x08 -> for 1.9V.

- The higher voltage is required to allow the fuses to be configured correctly.

- VCC\_MVT operating at 1.9V is only allowed while the fuses are been configured.

- 3. VCC1[MVS] and VCC1[MGO] are both set to 0b1.

- 4. Now VCC\_MVT voltage is raised by the PMIC to 1.9V.

- · Internal handshaking indicates the fuses have been configured.

- The Services Unit must now return VCC\_MVT to default value.

- 5. MDTV1 is loaded with 0x04 -> for 1.8V.

- 6. VCC1[MVS] is cleared 0b0 and VCC1[MGO] is set to 0b1.

- 7. Now VCC MVT is lowered to 1.8V.

Refer to the "Clock Controllers and Power Management" chapter of the PXA3xx Processor Family Developers Manual for more information on PWR\_I2C commands.

Not only must a PXA3xx-compliant PMIC be used in any PXA3xx-enabled platform but also for trusted platforms, the system design must be connected in such a way to enable the PMIC to raise VCC\_MVT for fuse configuring. This design may require detailed inspections of the PMIC datasheet to ensure that VCC\_MVT is connected to a dynamically programmable PMIC output regulator. This is known as "Boost Mode". Refer to the PXA3xx EMTS for more details.

## 3 Software Requirements

This chapter lists the requirements that must be performed by the OBM for the NAND and NOR platforms.

## 3.1 Size Restrictions for the Device Keying Binary

The Device Keying Binary should be restricted in size, based on the available internal SRAM on the processor used. Refer to the internal SRAM usage in Section 2.3.1, "ISRAM Usage". Marvell suggests that the Device Keying Binary size be restricted to less than 64 KB, based on the minimum internal SRAM that is used (128 KB). Of that 128 KB of internal SRAM, the Marvell<sup>®</sup> WTM locks 32 KB, which leaves 96 KB for software usage in a minimum internal SRAM scenario.

# 3.2 OEM Boot Module Requirements for NAND Platforms

The OEM boot module is responsible for performing all of the relevant tasks required for booting the platform. OEMs can choose between using their proprietary mechanism for identifying and loading the images from the NAND flash, or using the Marvell proposed bad block/relocation table located in Block 0 of the NAND flash in identifying and loading images from the flash. An example of an OEM boot module that uses the Marvell proposed bad block/relocation table is provided as a template. The requirements that must be completed by the OEM boot module include the following:

- Identifying the OS loader/image in the NAND flash

- Loading the content of the OS loader/image from the NAND flash into either internal SRAM or the DDR memory, as applicable

- Integrity checking the OS loader/image for trusted platforms

- Executing the loaded image.

The OEM boot loader must first initialize the DDR memory when loading to DDR memory. The OEM boot module must also relocate the contents of a block that goes bad in the process of accessing the block to a new block and update the bad block/relocation table of the platform.

The OEM boot module in Block 0 must also have all the basic OS startup capabilities, such as identifying reset reason and knowing when/how to identify and load the OS loader/image. For example, when returning from sleep resume, the OEM boot module simply performs the relevant requirements or workarounds, and transitions to the OS image in the DDR; when returning from hardware reset, the OEM boot module must perform a full DDR memory initialization and load the OS contents from the NAND flash to the DDR memory before transitioning to the DDR memory to continue execution.

#### 3.2.1 NAND OEM Boot Module Size Restrictions

If the Marvell bad-block management table is used and the Trusted Image Module or image module is used, then the OEM boot module is restricted by the size of the available internal SRAM. If the Marvell bad-block management table or the image module is not present, then the OEM boot module is restricted to Block 0 of the NAND.

## 3.3 NAND Bad/Relocation Block Table Definition

This section defines the bad-block relocation table that is used by the Boot ROM to load the OEM boot module and by the OEM boot module to identify and load the OS loader/image from the NAND

Copyright © 2010 Marvell PUBLIC RELEASE Doc. No. MV-S301208-00 Rev. -

flash to either the DDR memory or internal SRAM. The bad-block management scheme consists of two components: the bad-block table and the pool of reserved relocatable blocks. The relocation table always resides starting with the last page of Block 0. This offset in Block 0 for the initial table depends on the number of bytes per page and number of pages per block, as shown in Table 6.

Table 6: Relocation Table Addresses

| Block 0 Offset Of<br>Relocation Table<br>Base | Block Size | Number of<br>Bytes/Page and<br>Pages/Block | Comments                      |

|-----------------------------------------------|------------|--------------------------------------------|-------------------------------|

| 0x0000_F800                                   | 64 KB      | 2048/32                                    | _                             |

| 0x0001_F800                                   | 128 KB     | 2048/64                                    | Largest supported block size. |

The bad-block table requires exactly one page per block. If the bad-block table has to change at run time, each page is treated like a new slot for additional tables. Rather than erasing and creating a new table over the initial page each time, a new table is simply written to the page directly below the current table, which reduces wear and tear on the block by reducing the number of erase cycles. The maximum number of pages reserved for bad-block tables is 24. When 24 pages have been filled with bad-block tables, the next entity to create a new bad-block table then erases the block, reprograms any non-bad-block table-related information, and creates a new bad-block table at the initial page as defined in the addresses in Table 6.

#### Note

Note

This implementation requires a binary search algorithm to search for and find the most current table. Figure 3 is an example of a typical Block 0 layout at run time indicating how the slot-based mechanism works.

Figure 3: Block 0 Layout on a Samsung K9K1216Q0C\* with 16-KB Block Sizes and 512-Byte Pages

| Address | Blocks                            |  |

|---------|-----------------------------------|--|

| 0x3E00  | Page 31 – Initial Bad Block Table |  |

| 0x3C00  | Page 30 – Second Bad Block Table  |  |

| 0x3A00  | Page 29 – Third Bad Block Table   |  |

|         | Page 28 – Fourth Bad Block Table  |  |

| 0x3800  | Page 27                           |  |

| 0x3600  | Page 26                           |  |

|         |                                   |  |

| 0x1000  | Page 8                            |  |

|         | Trusted Image Module              |  |

| 0x0     |                                   |  |

#### 3.3.1 Bad Block Table Definition

Each bad-block table has a layout in flash, as defined with the following structure:

```

Typedef struct S_Reloc

{

USHORT Header;

USHORT NumReloc;

Rel_T Relo[NAND_RELOC_MAX];

}Reloc T;

```

The header is a fixed value of 0x524E to identify the presence of a bad-block table; that is, if the header is valid as defined above, the initial block scan has been completed. Otherwise, the block scan has not been completed. The NumReloc parameter identifies the number of blocks that has currently been relocated and is followed by up to 127 relocation pairs.

```

Typedef struct S_Rel

{

USHORT From;

USHORT To;

}Rel_T;

Const ULONG NAND RELOC MAX = 127;

```

Each "From" entry identifies the block that has been relocated and the entry "To" identifies the relocated block number.

#### 3.3.2 Bad Block Relocation Area

The last 127 blocks of the device are reserved for bad-block relocations. The first block that is relocated goes to the very last block of the device; the second block relocated goes to the second to the last block of the device, and so forth. This process effectively allows relocated blocks to grow from the highest address down. A block in the relocation pool itself may be relocated, so use caution when relocating to skip over these blocks. Figure 4 presents a typical flash part layout and a relocation table layout to tie the concepts together.

Figure 4: Example of Bad Block Table NAND Flash Mapping in Use —

Small Block NAND Flash Type: Samsung K9K1216Q0C\* (Device ID = 0x46)

Copyright © 2010 Marvell CONFIDENTIAL Doc. No. MV-S301208-00 Rev. -

### 3.4 OEM Boot ROM Requirements for NOR Platforms

#### 3.4.1 Traditional Boot Platforms

The OEM boot module on a traditional boot platform is responsible for loading the next layer of software and performing any platform initialization required to boot the operating system and/or communication layer.

#### 3.4.2 Trusted Boot Platforms

The following are the list of tasks that must be performed by the OEM boot module during normal trusted platform boot-up and resume operations.

- Use the OEM proprietary scheme to validate the security of all OEM supplementary binaries (OS/Application/Data, and so on).

- Use the OEM proprietary scheme to validate the security of the mobile operator's service provisioning module, if any.

- For the Tavor processor, the OEM boot module must integrity-check the communications content, initialize the DDR memory, copy the communications content to the DDR memory, and trigger the execution of the communications subsystem.

- Boot the platform.

# 3.5 Marvell<sup>®</sup> Wireless Trusted Module Driver Requirements

The Marvell<sup>®</sup> WTM driver is responsible for completing the following as part of the virgin boot requirements:

- Generate a new Random Number Generator (RNG) seed using the Marvell® WTM from the RNG seed programmed by the OEM boot module and program it to flash. This process must occur on every reset.

- Execute the CREATE\_SUBKEY\_PI to create a new subkey that is used for protecting the Marvell<sup>®</sup> WTM state and write the resulting subkey into flash.

- Execute the SAVE\_WTM\_STATE\_PI and write the resulting state data into flash memory at the designated address.

- Program the platform configuration fuses, if not done at manufacturing.

The Marvell<sup>®</sup> WTM driver must generate a new RNG seed using the Marvell<sup>®</sup> WTM for seeding into the Marvell<sup>®</sup> WTM on the next subsequent boot, and program the new seed to flash. The Marvell<sup>®</sup> WTM state in flash must also be updated before the platform is put to sleep.

# 4 Methods for Platform Provisioning

The requirements for platform provisioning depend on the usage model selected. This chapter provides some guidance on provisioning a platform for operation with the Boot ROM. "Provisioning a platform" means performing the required steps to turn an uninitialized system into an initialized system capable of booting to an operating system. Differences between a development system and a manufacturing system are highlighted whenever possible.

### 4.1 Non-Trusted Provisioning

The first step toward provisioning a non-trusted system is to review the use cases in Section 8.1, "Operation with a Non-Trusted Image Module" to determine the requirements. During this time, consider the following:

- 1. How the flash device is programmed. Several options are available:

- Programmed via the JTAG port using the JTAG software package

- · Preprogrammed by a flash programming vendor

- Programmed using a separate software image that is downloaded over one of the available ports

- 2. The flash device that is used for booting the system. The options are:

- X16 NAND device on data flash controller Chip Select 0

- X8 NAND device on data flash controller Chip Select 0

- XIP device on the static memory controller Chip Select 2

- The size of the first boot loader binary. Size implications must be reviewed when using a NAND flash device. For larger boot loaders, the use of a non-trusted image module and the bad-block management is required.

- 4. The level of verification that is required. The use of the Non-Trusted Image Module allows for a cyclic redundancy check (CRC) to be performed on the image.

- 5. Whether the same OEM boot module is used for both trusted and non-trusted systems. If both trusted and non-trusted platforms are supported, use the non-trusted image module. This selection allows one OEM boot module binary to be used on both platforms.

## 4.1.1 Provisioning an Unprogrammed Non-Trusted Boot Platform Using a Device Keying Binary

Complete these steps fully to provision an unprogrammed platform using a Device Keying Binary. Troubleshooting a secure enabled processor is more complicated because the JTAG port is disabled by default.

- Decide on the usage model for booting the system. See Section 8.2, "Operation Without a Non-Trusted Image Module".

- 2. Prepare a non-trusted image module binary and Device Keying Binary using the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package or a custom tool created by the OEM.

- 3. Prepare the non-trusted image module binary, OEM boot module, and associated operating system images using the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package or a custom tool created by the OEM.

- a) Boot the target platform and first download the non-trusted image module and associated Device Keying Binary created in Step 2 using the download tool available in the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package or a custom tool created by the OEM.

- b) The Device Keying Binary runs on the system and must perform all of the requirements documented in Section 4.1.1.1.

- c) The non-trusted image module, OEM boot module, and associated OS images created in Step 3 are downloaded by the Device Keying Binary using the download tool available in the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package or a custom tool created by the OEM.

- d) The Device Keying Binary must have the built-in capabilities to allow debug and testing of the non-trusted image module, OEM boot module, and associated OS images created in Step 3

- 4. As a last step, the non-trusted boot operation should be verified from a power-on reset.

The non-trusted boot process occurs on the platform upon every reset of an initialized platform. The non-trusted boot processes use the information stored in the non-trusted image module to load the images from flash memory before transferring control, if required.

## 4.1.1.1 Device Keying Binary Requirements for an Unprogrammed Non-Trusted System

The Device Keying Binary is responsible for provisioning and preparing an uninitialized system for initial boot. It must determine the flash used to boot, program the proper images to the flash, and if the platform is a NAND platform, validate or create the relocation table. In addition, an OEM may want to create multiple versions of the Device Keying Binary, one for use in manufacturing and one for use in development. The development Device Keying Binary could be used to aid in platform debugging.

Marvell provides the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package as an example for OEMs. This package contains all of the host tools and middleware required for both trusted and traditional boot. Contact your local Marvell field application engineer for more information.

The Device Keying Binary is responsible for completing the following on non-trusted boot platforms:

- Provide an interface through the UART or USB port to print messages and download binary images.

- Set up the DDR memory and all necessary flashes to store the downloaded images. At a minimum, this would include the OEM boot module.

- Create the initial bad-block table, if the flash signature in the Non-Trusted Image Module indicates a setup for NAND.

- Perform a checksum on the images against the values stored in the non-trusted image module to validate a correct download.

## 4.2 Trusted Provisioning

The first step towards provisioning a trusted system is to review the usage cases in Section 9.1, "Trusted Boot Usage Cases" and determine the requirements. When doing so, consider the following:

- 1. How the flash device is programmed. Several options are available:

- a) A separate software image that is downloaded over one of the available ports.

- b) A system that is preprogrammed by a flash programming vendor.

- 2. The flash device that is used for booting the system. The options are:

- a) X16 NAND device on data flash controller Chip Select 0.

- b) X8 NAND device on data flash controller Chip Select 0.

- c) XIP device on the static memory controller Chip Select 2.

- 3. The Device Keying Binary that is used. Marvell provides a sample Device Keying Binary that performs all of the necessary tasks required to provision a trusted system. If system-level debug is also required, modification of the Device Keying Binary may be necessary or a new Device Keying Binary can be developed by the OEM.

- 4. If the same OEM boot module is used for both trusted and non-trusted systems. If both trusted and non-trusted platforms are supported, use the Non-Trusted Image Module for the non-trusted system, which allows one OEM boot module binary to be used on both platforms. Review the requirements for the trusted OEM boot module in Chapter 9, "Trusted Boot Operation".

- The tools that are used to generate the Trusted Image Module. Marvell provides a sample tool

for generating the Trusted Image Module described in Chapter 7, "Trusted Image Module". An

OEM may also generate a separate tool.

- 6. How the system is debugged and how errors are diagnosed. The JTAG port on a trusted boot processor is disabled by default, which means different strategies must be deployed for troubleshooting. Refer to Table 1, Version 2.xx and Version 3.xx High Level Differences, on page 15 to identify processors enabled for trusted boot support.

## 4.2.1 Provisioning an Unprogrammed Trusted Boot Platform Using a Device Keying Binary

Complete the following steps to provision an unprogrammed platform using a Device Keying Binary. On a secure enabled processor, the JTAG port is disabled by default and makes troubleshooting more complicated.

- 1. Decide on the usage model for booting the system, according to those documented in Chapter 9, "Trusted Boot Operation".

- 2. Prepare a trusted image module binary and Device Keying Binary using the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package or a custom tool created by the OEM.

- Prepare the Trusted Image Module binary, the OEM boot module, and the associated operating system images using the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package or a custom tool created by the OEM.

- 4. Boot the target platform and first download the trusted image module and associated Device Keying Binary created in Step 2 using the download tool available in the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package or a custom tool created by the OEM.

- 5. The Device Keying Binary runs on the system and must perform all of the requirements documented in Section 4.2.2, "Device Keying Process".

- 6. The Trusted Image Module, OEM boot module, and associated operating system images created in Step 3 are downloaded by the Device Keying Binary using the download tool available in the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package or a custom tool created by the OEM.

- 7. The Device Keying Binary must have built-in capabilities to allow debug and testing of the Trusted Image Module, OEM boot module, and associated operating system images created in Step 3. This capability can be accomplished by allowing JTAG re-enabling or providing debug and test functionality over the download port.

- 8. As a last step, the trusted boot operation should be verified from a power-on reset.

#### Warning

Warning

Once the fuses are programmed on the processor, they cannot be changed. Verify correct boot operation before programming all of the fuses to avoid incorrect configuration.

The device keying process is initiated by the Boot ROM when the platform fuses indicate the platform is in the uninitialized state. A Device Keying Binary is used to load images into the boot flash and set other security-related information on the processor with XScale<sup>®</sup> technology. Once the provision is successful and the fuses are programmed, the platform becomes an initialized platform.

The trusted boot process occurs on the platform upon every reset of an initialized platform. The trusted boot processes use the security information stored in the trusted image module and the security information programmed by the Device Keying Binary to integrity check the images loaded from the flash before transferring control. If the validation process fails, the boot operation is halted.

The validation process is a series of checks on the Marvell<sup>®</sup> WTM and the images loaded into the flash. If the Marvell<sup>®</sup> WTM is successfully initialized, the Boot ROM starts the validation process on the images in the flash. Validation uses the RSA digital signature and the SHA-1 based digital signature verification of the trusted image module and OEM boot module in the validation process. Computed hashes are compared with hashes stored in the flash, which allows the Boot ROM to detect any changes that have occurred since the last boot attempt. If an error occurs at any point in the process, the boot process halts.

### 4.2.2 Device Keying Process

The device keying process occurs on an uninitialized platform, as defined by the Boot ROM fuses. Device keying is performed during platform manufacturing, when the platform configuration fuses can be programmed through the Marvell® WTM. The fuses can also be programmed during the manufacturing of the processors at the Marvell factory. The OEM must use the Marvell® Wireless Trusted Platform Tool Package to generate a trusted image module with all of the necessary security information for the trusted boot process. Optionally, an OEM could develop custom tools to generate the trusted image module according to Chapter 7, "Trusted Image Module".

- During the device keying process, the Boot ROM listens for a download request on either the UART, differential USB, or single-ended USB port to start the download process.

- If a request has been initiated, the Boot ROM begins by downloading a trusted image module to a reserved location in the internal SRAM. This trusted image module should cover the Device Keying Binary that is downloaded next.

- 3. After examining the load address for the Device Keying Binary from the trusted image module, the Boot ROM downloads the Device Keying Binary to this address and the Device Keying Binary should have been linked to execute from this location. Depending on the setting of the secure download enable fuse, the trusted image module and the Device Keying Binary may be integrity checked or control is transferred to the Device Keying Binary directly.

- 4. Once the downloaded Device Keying Binary is given control, it is responsible for completing the requirements listed in Section 4.2.2.1, "Device Keying Binary Requirements for an Unprogrammed System". The OEM should have its own proprietary secure scheme implemented in the downloaded OEM boot image. Execution of this scheme allows further download and future security checking of the OEM's supplementary binaries for its OS/application/data, as well as the mobile operator's service provisioning modules.

To allow an OEM to debug images, hooks have been provided in the Boot ROM to allow commands to be issued. Refer to the command protocol section in Chapter 11, "Communication Protocol" for details about the commands. The debug commands are allowed only on an uninitialized platform. Once the platform fuses are configured, debug commands are disabled. The Device Keying Binary must allow for the debug capabilities to be used by having an option to skip programming the fuses, which also implies that the Device Keying Binary should have a mode where it skips the download of images and only programs the fuses. The way this process is implemented as defined by the OEM. One suggestion is to support additional commands through the port protocol to allow for separating the steps of the platform provisioning.

#### 4.2.2.1 Device Keying Binary Requirements for an Unprogrammed System

The Device Keying Binary is responsible for provisioning and preparing an uninitialized system for initial boot. It must determine the flash that is used to boot, program the proper images to the flash, integrity check images if required (secure download enabled), program the platform configuration fuses, program the one-time programmable registers on NOR platforms, and if the platform is a NAND platform, validate or create the relocation table. In addition, an OEM may want to create

multiple versions of the Device Keying Binary, one for use in manufacturing and one for use in development. The development Device Keying Binary could be used to aid in debugging the platform.

Marvell provides the Marvell<sup>®</sup> Wireless Trusted Platform Tool Package as an example for OEMs. This package contains all of the host tools and middleware required for both trusted and traditional boot. Contact your local Marvell field applications engineer for more information.

The Device Keying Binary is responsible for completing the following on trusted boot platforms:

- Provide an interface through the UART or USB port to print messages, when run-time progress and error reporting are needed, and download binary images.

- Set up the DDR memory and all necessary flashes to store the downloaded images. At a minimum, this includes the OEM boot module.

- If the flash signature in the trusted image module indicates a setup for NAND, create the initial bad block table.

- Integrity check the images against the trusted image module.

- Find a good entropy source to generate/collect a five-word random number generator (RNG) seed and program it into flash where the Marvell<sup>®</sup> WTM save state is newly created, according to the trusted image module.

- Program the encrypted hash value of the OEM platform verification key into the flash one-time programmable Register 0 (64-bits) and the remaining 96 bits into the lower half of Register 1 (for platforms using XIP-based flashes only).

- Program the hash value of the JTAG re-enabling key, also referred to as the corrupted OEM boot module reverification key, into the upper half of Register 1 (32 bits) and the remaining 128 bits into Register 2 and lock Registers 0, 1, and 2 respectively (for platforms using XIP-based flashes only).

- Program the OEM wrapped verification keys (24 bits for A0, 48 bits for stepping B0 and forwards) into the Marvell<sup>®</sup> WTM fuses using the OEM Platform Bind PI via an ippCP call.

- Program the platform configuration fuses in the Marvell<sup>®</sup> Wireless Trusted Module.

Trusted device keying binary starts at internal Fail SRAM 0x5c013000 Print error Check boot flash STOP signature NAND XIP Initialize interrupts and stack Initialize static memory Initialize data controller CS0/CS2 flash controller Initialize DDR memory, optionally Does a bad Flash erase set up MFPR YES block table already compiler switch? exist? Fail, Device keying binary copies itself to DDR memory at Loop Try YES NO NO Again address 0x8000\_0000 physical, address 0 virtual Create a new bad block table For each Turn on memory block, management unit erase it For each block, Jump To C Code in Done read spare area DDR memory and and look for bad begin running block virtually Good Bad Initialize FFUART single ended and Record entry in differential USB ports bad block table Flash erase NO Fail, compiler switch? Loop Try Download trusted image Again module/non-trusted image module to internal SRAM Copy image YES compiler switch? YES NO Erase block Bad For trusted, validate trusted image module. Good For traditional boot, do a Fail Copy trusted rint error checksum on image module/non-Fail Print error trusted non-trusted image record error to image module module save state. to flash inalize bad block table Good STOP

Figure 5: Device Keying Binary Requirements Flow for an Unprogrammed System

Figure 6: Device Keying Binary Requirements Flow for an Unprogrammed System (cont)

### 4.2.2.2 Size Restrictions for the Device Keying Binary

The size of the Device Keying Binary should be restricted, based on the available internal SRAM on the processor. Refer to the internal SRAM usage in Section 5.7, "Internal SRAM Usage". Marvell suggests restricting the Device Keying Binary size to less than 64 KB, because a minimum of 128 KB of internal SRAM is used.

# 5 Boot ROM Implementation Details

The following sections detail the Boot ROM address maps.

### 5.1 Non-Trusted Boot Address Map

For non-trusted platforms, control is handed to the OEM boot module without security validation. For consistency with trusted platforms, the use of an image module is supported to provide image information in the same manner as a trusted platform. A Non-Trusted Image Module also allows for a CRC to be performed on an image before control is transferred. See Chapter 6, "Non-Trusted Image Module" for more details.

If a Non-Trusted Image Module is used, it must be loaded at the location shown in Table 7, "Non-Trusted Image Module Locations". NTIM headers are only supported in version 3.xx of the Boot ROM.