# VERY HIGH SPEED INTEGRATED CIRCUITS

# - VHSIC -

# VHSIC PROGRAM OFFICE

# OFFICE OF THE UNDER SECRETARY OF DEFENSE FOR ACQUISITION DEPUTY DIRECTOR, DEFENSE RESEARCH AND ENGINEERING FOR RESEARCH AND ADVANCED TECHNOLOGY

**SEPTEMBER 30, 1990**

APPROVED FOR PUBLIC RELEASE: DISTRIBUTION IS UNLIMITED

#### FOREWORD

This report presents a description and final account of the VHSIC program during its ten years of successfully developing advanced integrated circuit technologies and products for military systems. The new technologies and the products that VHSIC has produced have steadily found their way not only into defense systems but also into the commercial industrial base. They provide the reservoir from which new system capabilities are emerging and a foundation upon which continual further advances are being made.

. - --- --

<sup>1</sup>Over the course of the past decade, the VHSIC program has been active in the development of new materials, new circuit design concepts, advanced fabrication processes, new manufacturing equipment, higher levels of radiation hardening, new data interface standards and specifications, and improved techniques for built-in-test and maintainability. The VHSIC Hardware Description Language and other design automation tools have broken through major integrated circuit complexity barriers and will decrease the cost and the development time of modern electronic systems. The resulting achievements have helped to produce a new level of system design and tabrication --- one that approaches an integrated  $\bullet$ concept-to-system<sup>•</sup> capability.

The broad scope of technology that VHSIC activities included and the almost universal application of IC technology in military systems required an unusual structure and management strategy for the program. Although most of the technology work was in the "research and development" category, the identified goals and near term objectives were to insert the technology products into systems as soon as possible --- either as updates to thencutrent systems or as enhancements to systems in the design and development phase. In addition, the applicability of almost all of the technologi responsibility was required on the part of the program to commercial IC production meant a continuing high interest on the part of the entire semiconductor industry in the program managers to consult with the industry leaders and be aware of their concerns. Finally, since the technology was (and is) broadly applicable to the electronic system requirements of all the military Services, an integrated Department of Defense management was adopted which involved the participation of technical and contract managers at the Services' headquarters and technical specialists from many of the Service laboratories.

The results of the VHSIC program will continue to be absorbed into industrial practice and DoD procurement for many years as new IC production capabilities are achieved and new systems designs are placed into operation. Continuing developments in integrated system design techniques will allow a design, simulation, and re-design process that ensures optimum performance at low development costs. The evolution of the Qualified Manufacturing Line procedure will make it possible to produce highly complex ICs as military qualified parts without incurring excessive qualification costs.

# PAGES ARE MISSING IN ORIGINAL DOCUMENT

The legacy of the VHSIC program is a broad spectrum of technological advances, the enhanced military capabilities, and the maintenance of U.S. leadership in an area of technology that is vital to our national well being.

In carrying out its activities the VHSIC program involved a major portion of the U.S. semiconductor industry and a considerable number of technical managers and specialists in the Department of Defense. The success and achievements of the program would not have been possible without their leadership initiatives and dedicated, enthusiastic efforts.

John M. Mochallum

John M. MacCallum Director, VHSIC Program Office ODDDRE/R&AT

# CONTENTS

# **CHAPTER 1 - EXECUTIVE SUMMARY**

| Background and Program Objectives            |

|----------------------------------------------|

| Program Structure                            |

| Security                                     |

| Program Results                              |

| Design and Design Automation                 |

| Fabrication and Manufacturing Technology 10  |

| System Insertion                             |

| Technology Transfer 13                       |

| The Impact of VHSIC - Leonard R. Weisberg 14 |

# CHAPTER 2 - THE VHSIC PROGRAM HISTORY, STRUCTURE, AND POLICIES

| 2.1 Program Origins and Objectives                           | 24 |

|--------------------------------------------------------------|----|

| The Legacy of VHSIC - Larry W. Sumney                        | 26 |

| 2.2 Program Structure                                        | 30 |

| 2.2.1 Phase 0 Concept Definition                             | 30 |

| 2.2.2 Phase 1                                                | 32 |

| 2.2.3 Phase 1 Yield Enhancement                              | 34 |

| 2.2.4 Phase 1 Technology Insertion                           | 35 |

| 2.2.5 Phase 2 Submicrometer Technology Development           | 35 |

| 2.2.6 Phase 3 and Other Supporting Technologies              | 37 |

| 2.2.7 Design Automation                                      | 38 |

| 2.2.8 VHSIC Manufacturing Technology Program - Joseph A. Key | 39 |

| 2.3 Program Management                                       | 40 |

| 2.4 Funding                                                  | 42 |

| 2.5 Security - James J. Hower                                | 42 |

| 2.5.1 History of VHSIC Security Measures                     | 42 |

| 2.5.2 Additional Security Decisions                          | 47 |

# **CHAPTER 3 - DEVELOPMENT TASKS**

| 3.1 Design                                                       | 50  |

|------------------------------------------------------------------|-----|

| The Impact of VIISIC on System Level Design - Robert W. Rolfe    | 51  |

| 3.2 Test and Life Cycle Support                                  | 74  |

| 3.3 Chip Fabrication                                             | 88  |

| The Impact of VHSIC on Fabrication Technology - Charles S. Meyer | 88  |

| 3.4 Description of VHSIC Chips                                   | 120 |

# **CHAPTER 4 - BRASSBOARD DEMONSTRATIONS**

| 4.1 Phase  | 1 |  | <br>  |   |       | • |  |  | , |     |  |       |   |   |  |   |     | • |   |  |   |  | • • |       |     | <br>142 |

|------------|---|--|-------|---|-------|---|--|--|---|-----|--|-------|---|---|--|---|-----|---|---|--|---|--|-----|-------|-----|---------|

| 4.2. Phose | 2 |  | <br>• | • | <br>• | • |  |  |   | • • |  | <br>• | • | • |  | • | • • |   | • |  | • |  | •   | <br>• | • • | <br>145 |

# **CHAPTER 5 - TECHNOLOGY INSERTION**

| The Impact of VHSIC on the DoD System Life Cycle - Joel M. Schoen | 150 |

|-------------------------------------------------------------------|-----|

| 5.1 Army System Insertion Projects                                | 154 |

| 5.2 Navy System Insertion Projects                                | 160 |

| 5.3 Air Force System Insertion Projects                           | 164 |

| 5.4 Other System Insertion Projects (Name only)                   | 170 |

| 5.5 Logistics Retrofit Engineering                                | 172 |

| 5.6 Projects Involving VHDL Insertion                             | 173 |

| The Impact of VHSIC on DoD Weapon Systems: A Case Study           |     |

| - John E. Stuelphagel                                             | 177 |

# CHAPTER 6 - TECHNOLOGY TRANSFER

| 6.1 Training                            | 184 |

|-----------------------------------------|-----|

| 6.2 Conferences and Workshops           | 186 |

| 6.3 Technology Transfer of Design Tools | 190 |

| 6.4 Testability and Built-In-Self-Test  | 191 |

| 6.5 Commercial Applications             | 192 |

# CHAPTER 7 - VHSIC INDUSTRIAL BASE

| The Impact of VHSIC at IBM: A Case Study                   |     |

|------------------------------------------------------------|-----|

| - Robert H. Estrada and Harley A. Cloud                    | 197 |

| 7.1 Design and Manufacturing Capabilities                  | 200 |

| 7.2 Commercially Available VHSIC Design Tools              | 213 |

| The Impact of VHDL on Design Automation - Randolph E. Harr | 213 |

| ACKNOWLEDGEMENTS |  | 229 |

|------------------|--|-----|

|------------------|--|-----|

# APPENDICES

| Appendix A - References      | 231 |

|------------------------------|-----|

| Appendix B - VHSIC Contracte | 243 |

| Appendix C - Glossary        | 259 |

# Figures:

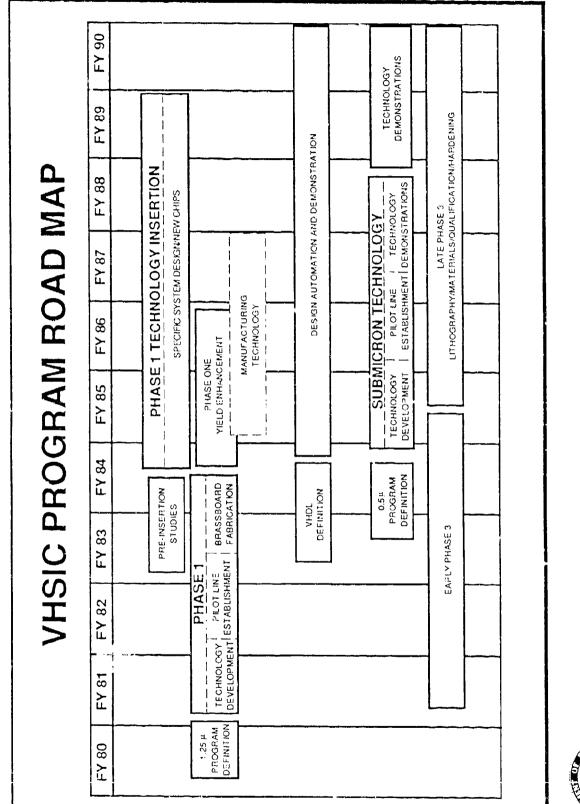

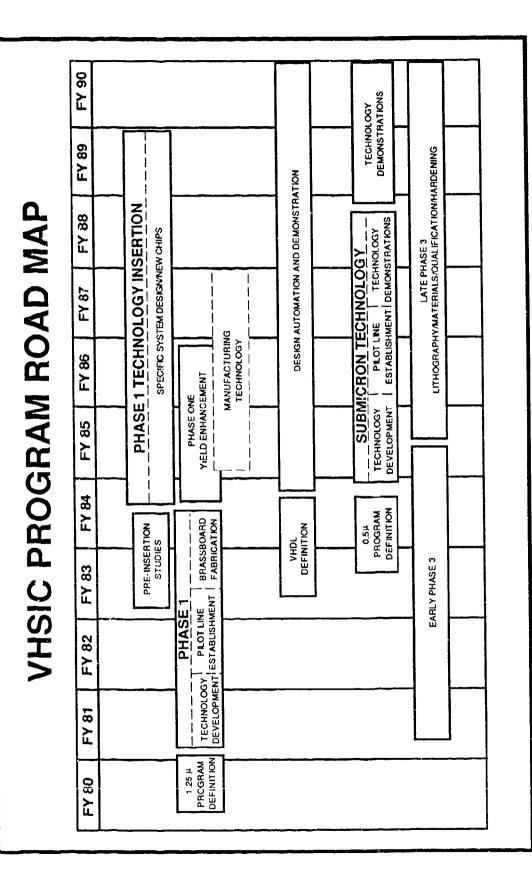

| 1.1  | VHSIC Program Roadmap                                | 5   |

|------|------------------------------------------------------|-----|

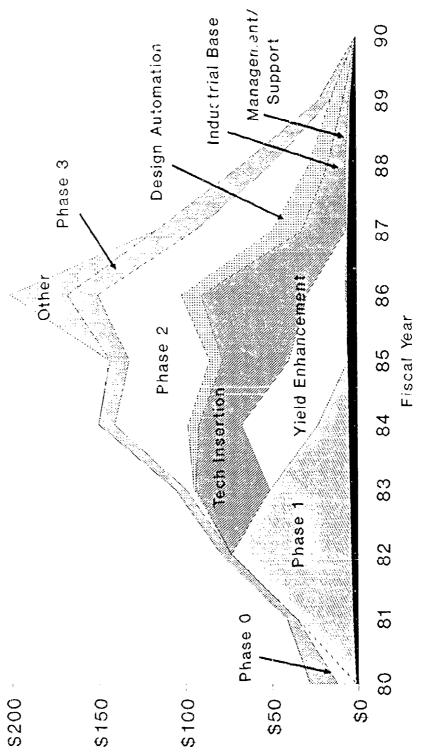

| 1.2  | VHSIC Funding Profile                                | 6   |

| 2.1  | VHSIC Program Roadmap                                | 43  |

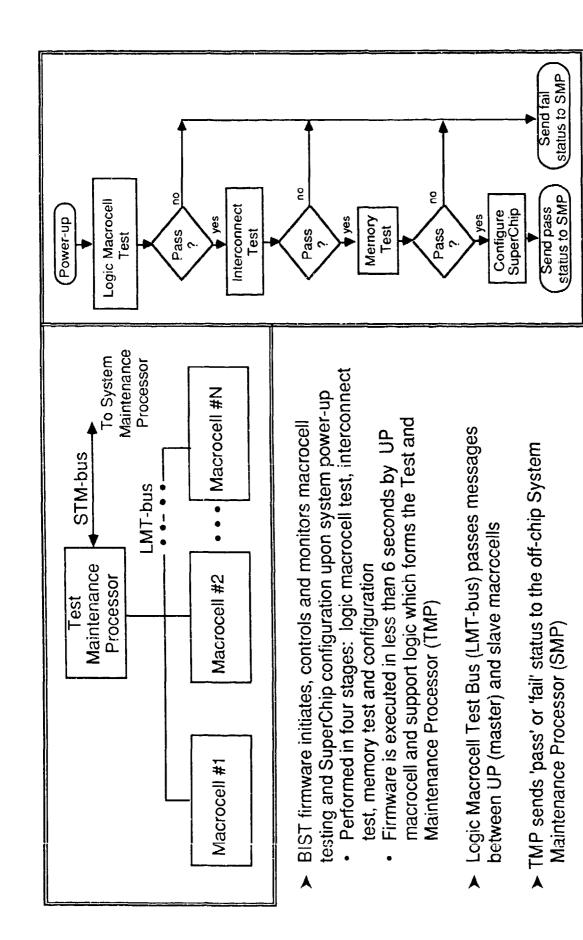

| 3.1  | Built-In Self-Test Features (TRW)                    | 59  |

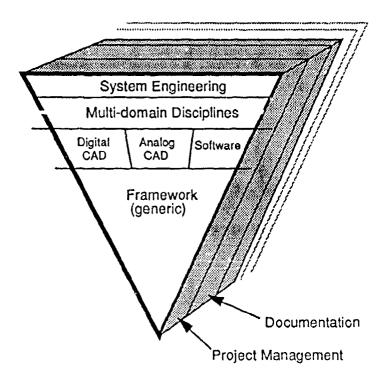

| 3.2  | Relationship of Frameworks To Application Domains    | 72  |

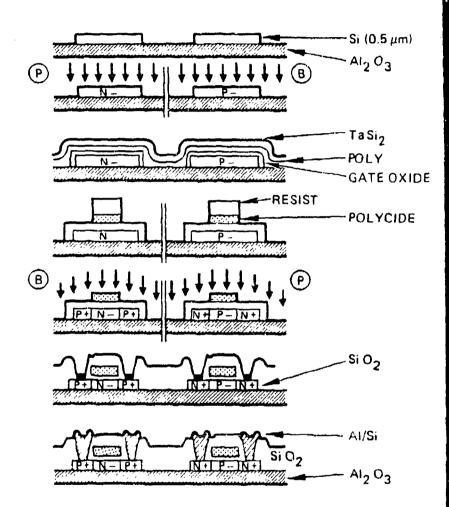

| 3.3  | SOS-III VHSIC Phase 1 Process (Hughes)               | 92  |

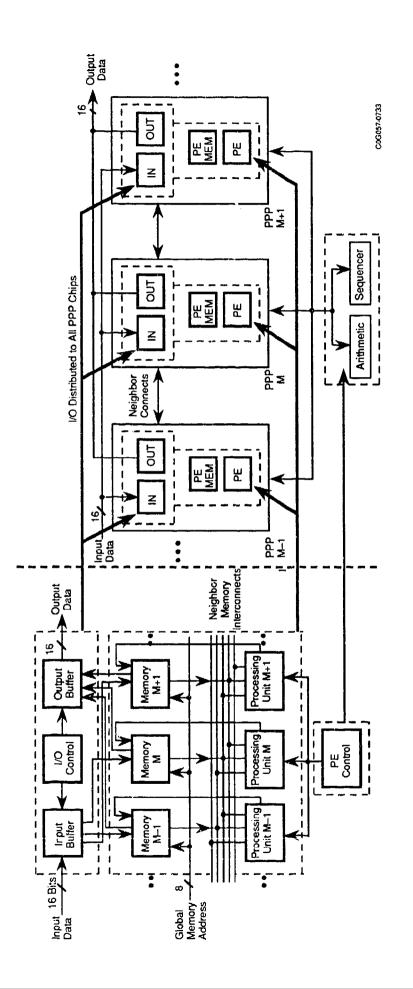

| 3.4  | PPP Architecture Partitioning Into Chips (Honeywell) | 123 |

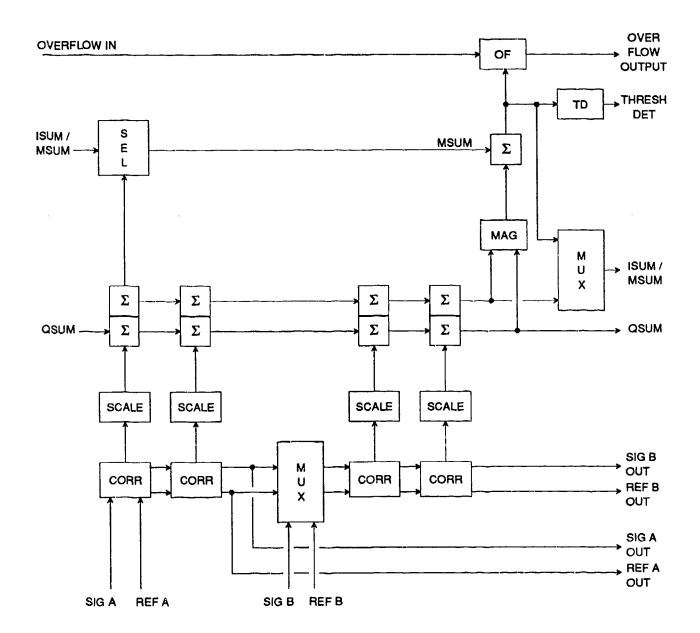

| 3.5  | Single Channel Digital Correlator (Hughes)           | 125 |

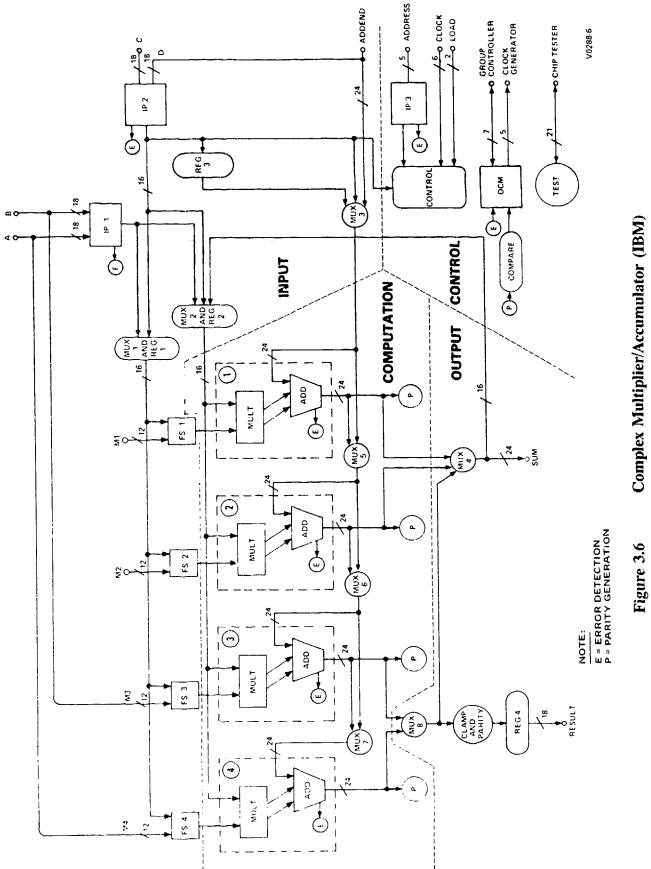

| 3.6  | Complex Multiplier/Accumulator (IBM)                 | 127 |

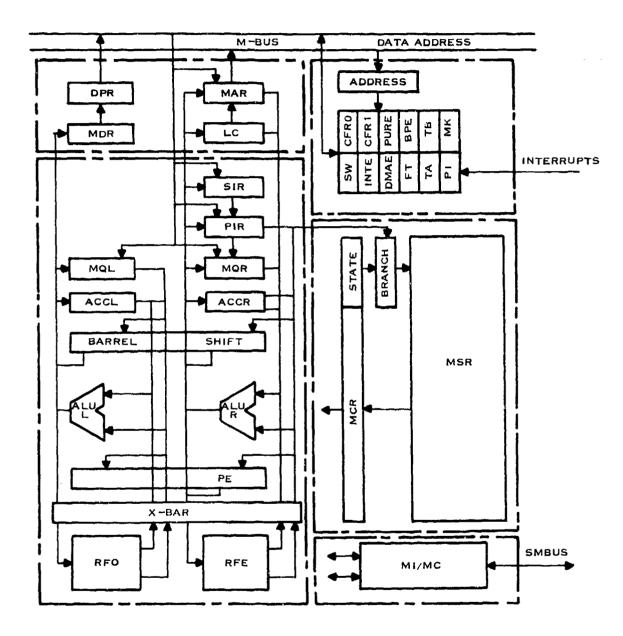

| 3.7  | Data Processor Unit (Texas Instruments)              | 128 |

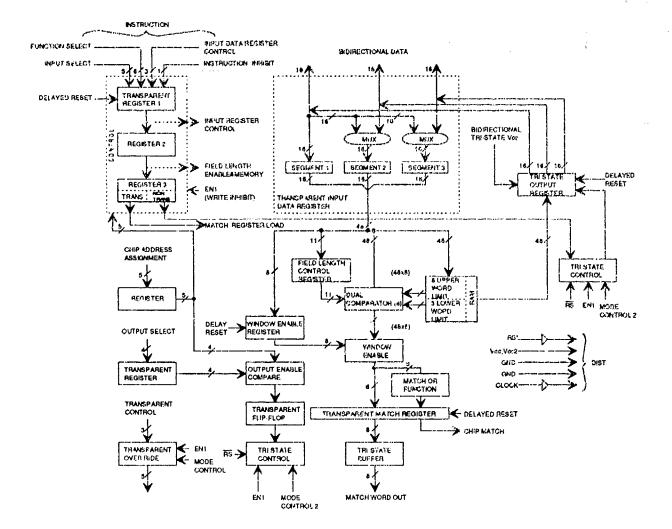

| 3.8  | Window Addressable Memory (TRW)                      | 131 |

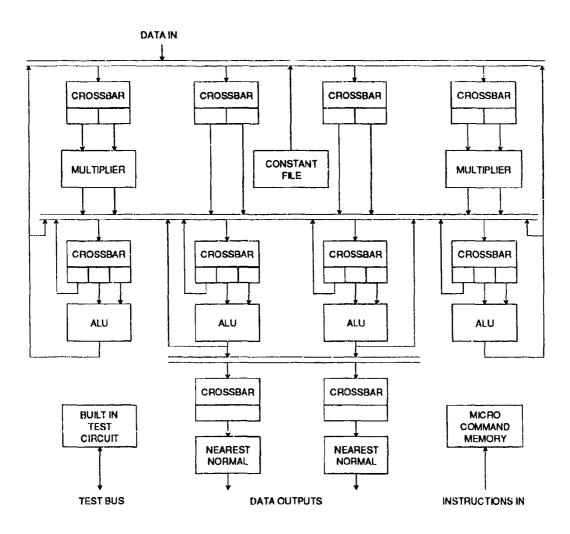

| 3.9  | Pipeline Arithmetic Unit (Westinghouse)              | 133 |

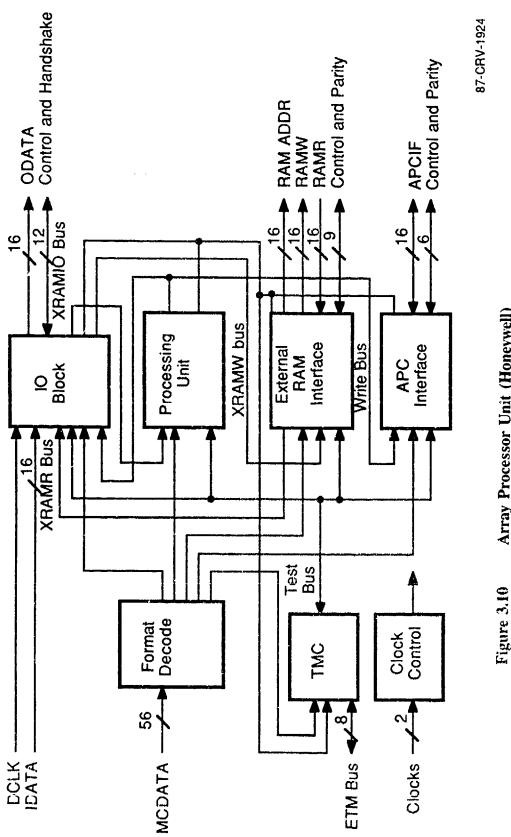

| 3.10 | Array Processor Unit (Honeywell)                     | 135 |

| 3.11 | Systolic Processor (IBM)                             | 136 |

| 3.12 | Central Processing Unit, Arithmetic Extended (TRW)   | 139 |

| 5.1  |                                                      | 178 |

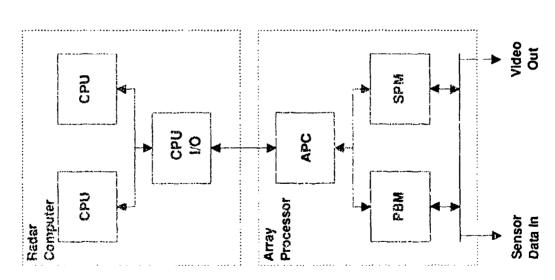

| 5.2  | Advanced PSP Architecture                            | 180 |

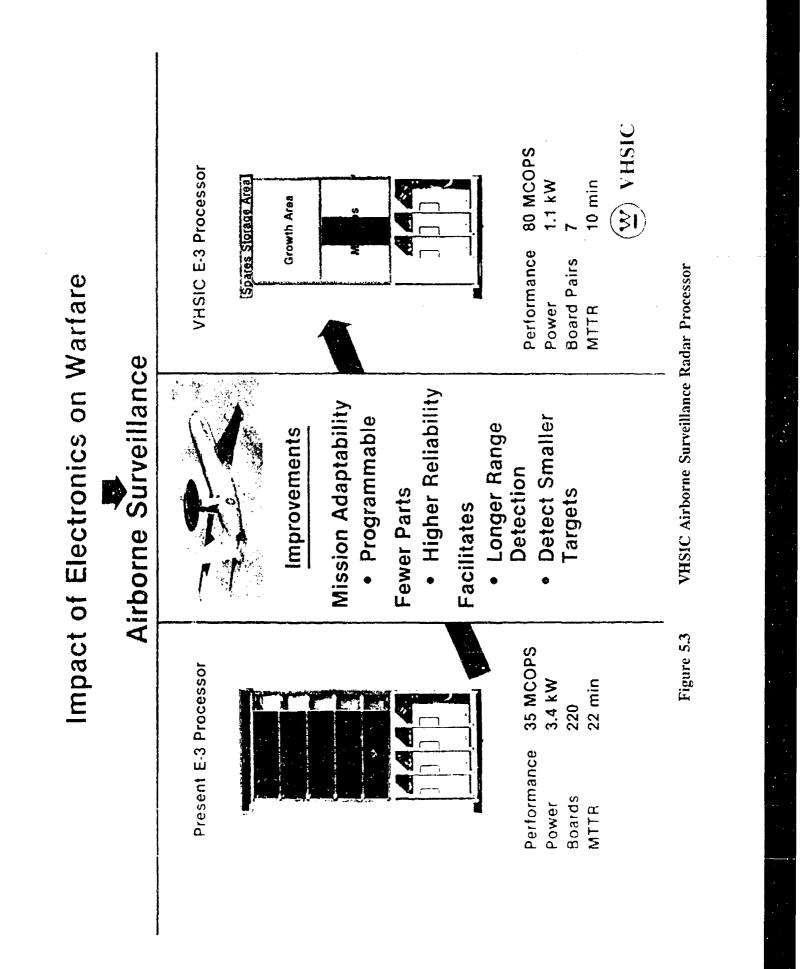

| 5.3  | Airborne Surveillance Radar Processor                | 181 |

|      |                                                      |     |

# Tables:

| 1.2 | VHSIC Chips Demonstrated in Phase 1 and Phase 2 | 8   |

|-----|-------------------------------------------------|-----|

| 1.1 | Major Events, Milestones, and Highlights        | 20  |

| 2.1 | VHSIC Funding History                           | 44  |

| 3.1 | IBM 0.5 Micron CMOS Technology Features         | 102 |

| 3.2 | VHSIC Phase 1 Chip Characteristics              | 121 |

| 3.3 | VIISIC Phase 2 Chip Characteristics             | 122 |

OTIC Inspector

وجواديا فيواقوا الهار

·.• .

$\pm 1$

....

....

NES CONS

Dark 12.2

. ....

.

î

vii

| Background And Program Objectives           | 2 |

|---------------------------------------------|---|

| Program Structure                           | 3 |

| Security                                    | 7 |

| Program Results                             | 7 |

| Design and Design Automation                | 9 |

| Fabrication and Manufacturing Technology    | 0 |

| System Insertion                            | 2 |

| Technology Transfer                         | 3 |

| The Impact of VHSIC - Leonard R. Weisberg 1 | 4 |

## **CHAPTER 1**

## EXECUTIVE SUMMARY

In March 1980, the Department of Defense began the Very High Speed Integrated Circuits (VHSIC) program to develop advanced silicon integrated circuits. In September 1990, the VHSIC program officially came to an end in terms of starting new activities. During the intervening decade, with funding of approximately \$918M, VHSIC organized the efforts of hundreds of engineers, scientists, and managers, and scores of companies in a highly technical and complex enterprise. For much of that time VHSIC was considered one of the highest priority technology programs in the DoD and of vital importance to sustaining the military superiority of the United States. This Final Report is an update to and summary of the Annual Reports for 1986, 1987, and 1988 (References 2.27-2.29). Together, these four reports provide an overall documentation of the VHSIC program.

This report presents the rationale and objectives of the program, the organization and structure through which it directed its efforts, the results that were achieved from its many activities, and independent assessments of the impact that it has had on integrated circuit technology and its use in military systems. Such an assessment by one of the primary initiators of the VHSIC Program is included at the end of this Executive Summary.

"VHSIC is our highest priority technology and we will continue to provide strong management emphasis in order to achieve the increased military capability expected from its results."

- Richard D. DeLauer, Under Secretary of Luffense for Research and Engineering. Statement to the 98th Congress, First Session, March 1983.

## Background And Program Objectives – (Chapter 2)

Prior to 1980, the DoD had spent several years carefully assessing its needs and deficiencies in integrated circuit technology. The major deficiency perceived was that the DoD deployment of military products incorporating state of the art microelectronic technology was running ten or more years behind the appearance of that technology in the commercial market. Worse still, the delay was increasing with time. However, the need for ready access to this technology had become increasingly vital to the U.S. defense posture as the weapon systems being deployed became more and more dependent on electronic subsystems for their effectiveness, for their speed of response, and for their adaptability in rapidly changing battle environments.

The goal of the VHSIC program was to correct that deficiency by giving system developers and acquisition managers a military qualified microelectronics technology that was on par with or better than the technology available commercially.

# **Program Structure** – (Chapter 2)

VHSIC presented the DoD with an unusual program concept to define and manage. The technology of integrated circuits was (and is) broadly applicable to a wide and rapidly growing variety of uses which were dominated by commercial activity. The application of integrated circuits in military equipment was also pervasive throughout the Services, on all platforms, and in most weapon systems. The program would therefore have to face the problems of developing new generations of complex integrated circuits in cooperation with the leaders of the semiconductor industry and then finding effective ways to make them readily available to the military systems community. The core of VHSIC was the development of a new level of "high tech" electronics design and manufacturing which, it was realized even then, would have strong implications for changes in other indispensable system acquisition activities such as military qualification procedures. The management and structure of the VHSIC program therefore had to integrate all of these elements into a compatible set of comprehensive and interactive activities.

To define and organize the tasks that would have to be carried out, a VHSIC Program Office (VPO) was established in the Office of the Under Secretary of Defense for Research and Engineering (later to become OUSD for Acquisition) for overall management and direction of the program. The Army, Navy, and Air Force each set up corresponding offices to award and administer the contracts. They also provided the detailed, day-to-day technical management of the program, the technical teams required for program reviews, and the inhouse skills and facilities for testing the VHSIC products.

Under the coordination of the VHSIC Program Office, a high degree of tri-Service cooperation and task sharing was achieved. The formulation of programs and the evaluation of proposals were carried out jointly. Representatives from all the Services and other DoD components attended the program reviews and provided technical evaluations to the program managers. This cooperative environment permitted the administrative tasks of letting and monitoring contracts to be distributed among the Services while the technical tasks were handled by the DoD VHSIC community as an organic whole, each Service contributing the expertise of its internal technical staffs and sharing the information gained as the contractors made progress.

The program was divided into the following distinct activities.

**Phase 0**: a one year concept definition effort to prepare a detailed development plan to accomplish the technical objectives set out by the VHSIC program office. Emphasis

was put on 1.25 micron minimum feature size and 25 megahertz clock speed. Nine companies participated in I na e 0, starting in March 1980.

**Phase 1**: a primary effort, based on the approaches defined in Phase 0, to develop and produce silicon chips with 1.25 micron minimum feature sizes and 25 MHz clock speed, and to demonstrate them in subsystem brassboards. Phase 1 contracts were awarded to Honeywell, Hughes, IBM, Texas Instruments, TRW, and Westinghouse in May 1981.

This phase was later expanded to include a yield enhancement program to increase the yield or producibility of the VHSIC chips.

<u>Manufacturing Technology:</u> the development of better manufacturing tools and techniques that were needed to make the VHSIC chips producible and affordable. These projects were defined and funded jointly with the manufacturing technology programs in the Services.

**Design Automation:** the development of the design tools, standards, software, and hardware needed to make the design of large, complex VHSIC chips more effective and affordable.

<u>Technology Insertion</u>: the demonstration of VHSIC Phase 1 chips and technology by inserting them into a broad variety of military systems, both existing systems and others still in development. In cooperation with the system program offices, VHSIC co-funded both feasibility studies and demonstrations of hardware in operating systems.

**Phase 2:** a primary effort to develop and produce (on a pilot line basis) silicon chips with 0.5 micron minimum feature size and 100 megahertz clock speed. This phase was started after it became clear that development of the 1.25 micron technology and its transition into manufacturable products could, in fact, be accomplished. The contractors selected to undertake the submicron development tasks were Honeywell, IBM, and TRW. Contracts were awarded and work began in November 1984.

**Phase 3**: a broadly based collection of separately funded contracts conducted concurrently with Phases 1 and 2. These supporting technologies were found necessary to meet the program objectives. Specific efforts were undertaken to deal with technology applications, materials requirements, lithography and fabrication tools, design software development, packaging, chip qualification, and radiation hardness.

A "roadmap" of these program activities and the overall program funding profile from 1980 to 1990 are shown in Figures 1.1 and 1.2.

VHSIC

VHSIC Program Ruadmap

Figure 1.1

Millions (Then year dollars) \$250 -

VHSIC Funding Profile Figure 1.2

## Security.

The House and Senate Conference Report for the 1980 Defense budget, which authorized the initial funding for the VHSIC program, included the following statement:

"The expert of the technology developed in this (VHSIC) program would be controlled where applicable by the ITAR until the state-of-the-art for such technology progresses to the point where national security permits its transfer to other controls for expert".

This statement represented a departure from the existing administrative controls on microelectronics. Only those devices specifically designed for military application had previously been constrolled by the HAR. All dual-use or general purpose devices, even those puin to military specifications, were controlled under the Export Administration Regulations (EAR) of the Department of Commerce.

As the Detense VHSIC Program officially came to an end, the VPO no longer considered it necessary or appropriate to single or t "VHSIC" devices for special control. The terms of the Congressional mandate for release from ITAR control were met by the diffusion of the technology throughout the industry and the subsequent availability of comparable technology in Europe and the western Pacific.

The VPO also supported authorizing the use of devices developed under this program in commercial applications. Such devices would be properly identified as "dual-use" and would then be subject to the same EAR control as other commercial integrated circuit devices.

#### **Program Results**

The results of the decade of work conducted by the VHSIC program are summarized in the remainder of this Executive Summary. A chronology of some of the more significant events that occurred during the course of the program are listed in Table 1.1 at the end of this chapter. More details are described in Chapters 2 through 7 of this report. The most complete technical accounts and the fullest documentation of results will be found in the references that are listed in Appendix A. Included at appropriate places throughout this report are individual assessments of the VHSIC program which have been contributed by people who have been mostly outside of the VHSIC program offices but who have participated in VHSIC activities in various positions. Each contribution provides an evaluation, from the author's personal perspective, of the impact that VHSIC has had either on a company position with respect to IC technology, on DoD applications of IC technology, or on particular areas of IC technology.

| Chip Name                                                                                                                                                                                                  | Equivalent Logic Gates<br>(x1000)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Size<br>(Mils)                                                                       | I/O<br>Pins                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Ī                                                                                                                                                                                                          | Phase 1 Chips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |                                                             |

| <u>Honeywell</u> : Pipeline Par Proc<br>Sequencer<br>Arithmetic Unit                                                                                                                                       | 28<br>27<br>18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 311x309<br>300x300<br>300x300                                                        | 180<br>180<br>180                                           |

| <u>Hughes</u> : Multiple Channel Correlator<br>Single Channel Correlator<br>Signal Tracking Subystem                                                                                                       | 18<br>20<br>14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 368x315<br>397x367<br>360x360                                                        | 148<br>148<br>148                                           |

| IBM: Complex Multiplier/Adder                                                                                                                                                                              | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 320x320                                                                              | 240                                                         |

| <u>T.I.</u> : Data Processing Unit<br>Vector Arithm Logic Unit<br>Vector Address Generator<br>Array Controller/Sequencer<br>Device Interface Unit<br>Multipath Switch<br>General Buffer Unit<br>Static RAM | $     \begin{array}{r}       16 \\       17 \\       12 \\       10 \\       16 \\       4 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\      10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\       10 \\  $ | 350x350<br>353x365<br>301x312<br>301x312<br>350x350<br>250x265<br>341x312<br>240x264 | 84<br>164<br>84<br>84<br>84<br>84<br>84<br>32               |

| <u>1RW</u> : Window Addressable Memory<br>Content Addressable Memory<br>Register Arithm Logic Unit<br>Multiply/Accumulate<br>Address Generator<br>Microcontroller<br>Matrix Switch<br>Four Port Memory     | $     \begin{array}{c}       11 \\       12 \\       6 \\       8 \\       10 \\       6 \\       2 \\       13 \\       13     \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 310x290<br>314x272<br>37x330<br>320x298<br>336x285<br>346x306<br>200x200<br>290x313  | 132<br>132<br>132<br>132<br>132<br>132<br>132<br>132<br>132 |

| Westinghouse: Static RAM<br>Pipeline Arithmetic Unit<br>Extended Arithmetic Unit<br>Extended Arithmetic Unit Mult<br>General Purpose Controller<br>10K Gate Array                                          | 30<br>33<br>26<br>23<br>20<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 190x310<br>340x350<br>340x350<br>340x350<br>340x350<br>280x304                       | 42<br>224<br>224<br>224<br>224<br>224<br>224                |

|                                                                                                                                                                                                            | <u>Phase 2 Chips</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                      |                                                             |

| Honeywell: Array Processor Unit *<br>Array Processor Controller *<br>Bus Interface Unit **                                                                                                                 | 32<br>27<br>19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 370x370<br>370x370<br>280x280                                                        | 270<br>270<br>180                                           |

| <u>IBM</u> : Systolic Processor<br>Configurable Static RAM<br>Address Generator<br>Bus Interface Unit<br>Signal Processing Element                                                                         | 33<br>9<br>24<br>15<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 215x215<br>215x215<br>215x215<br>215x215<br>215x215<br>151x151                       | 180<br>180<br>180<br>180<br>180                             |

| <u>TRW</u> : CPUAX Superchip ***                                                                                                                                                                           | 4100/1700                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1500x1600                                                                            | 275                                                         |

| Table 1.2 | VHSIC Chips | Demonstrated i | n Phase 1 | and Phase 2 |

|-----------|-------------|----------------|-----------|-------------|

|-----------|-------------|----------------|-----------|-------------|

<sup>4</sup> Personalization of a 70K configurable gate array

\*\* Personalization of a 35K configurable gate array

\*\*\* Total transistors on chip/number needed to operate fully

The direct activities of VHSIC were concentrated in four broad areas ---- design and design automation, fabrication and manufacturing technology for VHSIC chips, insertion of VHSIC products into systems, and the transfer of the technology into the broader industrial community involved in military system development.

# Design and Design Automation: (Chapter 3, Sections 3.1 and 3.2)

Twenty-nine chips for Phase 1 and nine chips for Phase 2 were designed, produced, and demonstrated during the VHSIC program. They constituted very complete and powerful chip sets which were capable of performing the wide variety of signal processing functions needed by military weapon systems and were used experimentally to explore specific system applications. These chips are listed in Table 1.2.

In order to design chips of such functional complexity and large physical size, the VHSIC program needed advanced design automation tools. Design standards were also needed to make sure that the resulting chips would operate successfully in real system environments. The VHSIC efforts in this very dynamic and rapidly growing field of technology have had a strong influence on many of the directions taken in design tool development. The most visible influence has been the development of the VHSIC Hardware Description Language (VHDL) which was adopted as a international commercial standard by the IEEE in December 1988.

The VHDL provides a powerful computer language by which both the hardware structure and the electrical behavior of any IC can be described. The VHDL description can be used in the design process to simulate the performance of the chip and make sure that it will operate as desired. It can also be used to generate the computer programs for testing the chip after manufacture, to transfer the design data from one company to another for second source production, and to provide archival documentation of the chip design in case it needs to be remanufactured in the future. As a result of its usefulness in the acquisition and maintenance of electronic systems, VHDL has been adopted as a DoD requirement for microcircuit documentation.

<sup>&</sup>quot;<u>ASIC documentation in VHDL</u>. Digital Application-Specific Integrated Circuits (ASICs) designed after 30 September 1988 shall be documented by means of structural and behavioral VHSIC Hardware Description Language (VHDL) descriptions in accordance with IEEE 1076. Behavioral VHDL descriptions shall describe the input/output behavior at a sufficiently detailed level to permit the behavioral description to be used within a larger VHDL model for test generation and fault grading of the containing model.

<u>Fault coverage</u>, Fault coverage shall be reported for the manufacturing-level logic tests for all digital microcircuits designed after 30 September 1988, Fault coverage shall be based on the equivalence classes of single, permanent, stuck-atzero and stuck-at-one faults on all lines of a TISSS-compatible structural VHDL model, where the structural model is expressed in terms of gate-level primitives or simple atomic functions (such as flip-flops)."

> DOD M1L-STD-454L, Requirement 64 (Microelectronic Devices) September 20, 1988

VHSIC also emphasized the need for system level design tools. The increasing functional complexity of VHSIC chips was bringing the concept of an "electronic system on a chip" much closer to realization and so the design of individual chips was no longer isolated from the design of the overall system. The Architectural Design and Assessment System which was developed under a Phase 3 contract has found widespread use in the design of optimal system architectures. The development efforts begun by VHSIC have been continued in many cases under separate Service sponsorship.

VHSIC required that testing capabilities be built into the chips so that they could provide self-generated data on their readiness to operate. This requirement resulted in the development of very sophisticated built-in test design methodologies that are now in use.

Four standards were developed to provide for the interoperability of VHSIC chips with each other and with the other system components. The standards include an electrical specification for direct interfacing of all VHSIC chips, a parallel interface bus for message and data communication on a system backplane, a serial test and maintenance bus for sending and receiving test data signals on the system backplane, and a serial element test and maintenance bus for test data communication with individual chips on the same circuit board. These standards are part of a group of data bus and interface standards that were developed and transferred to the larger industrial (and international) electronic community for use in the controlled exchange of data.

## Fabrication and Manufacturing Technology: (Chapter 3, Section 3.3)

The VHSIC contractors developed technologies for fabricating the complex, large area, signal processing chips first with 1.25 micron and then with 0.5 micron feature sizes. They accomplished this on time schedules which, in both cases, produced manufacturing prototype chips ahead of the time schedules for the production of equivalent commercial chips. Twenty

nine different 1.25 micron chips and nine 0.5 micron chips were designed, fabricated, and demonstrated. Many new and difficult fabrication problems had to be solved, especially in the areas of silicon substrate material, fine-line lithography, multi-layer metalization, and packaging.

"...most experts agree that without VHSIC, semiconductor development in the U.S. wouldn't have progressed so quickly toward submicron geometries, even in the commercial world."

"Among the technical breakthroughs spawned by VHSIC is the use of multiple layers of metal in advanced semiconductors, now a routine design feature in high-density ICs."

"What Did We Get From VHSIC", <u>Electronics</u>, June 1989, p. 97

The first VIISIC chip with 1.25 micron technology was produced in February 1983. Since that time, the technology has evolved into a full production capability at a large number of industrial manufacturing lines. A representative list of such companies with their VHSIC manufacturing capabilities is included in Chapter 7.

The culmination of the manufacturing technology developed in the VHSIC program was the successful fabrication and operation by the Phase 2 contractors of highly complex, capable, 100 megahertz, 0.5 micron chips. IBM demonstrated a set of four signal processing chips in an acoustic beamformer brassboard in December 1988, TRW demonstrated an operating VHSIC "superchip" in December 1989, and Honeywell is scheduled to demonstrate a set of three customized gate array chips in a cruise missile guidance application in September 1990. The TRW "superchip", for example, measures 1.5 inch by 1.6 inch and contains over 4 million transistors. More than one half of the transistors are used as redundant elements that are automatically switched into operation, if needed, to ensure that the chip is functioning properly before it leaves the manufacturing line. This design characteristic also guarantees that the chip will have an extraordinarily extended lifetime in satellite applications or other unattended operations.

After an intensive effort on manufacturing yield enhancement, the various Phase 1 chip types were produced on pilot production lines at yields that ranged from under 10%, which is marginal for production, to over 70% which is high enough to enter confidently into full scale production.

One of the major requirements of VHSIC was that the chips be operable in severe radiation environments. In coordination with the Defense Nuclear Agency, the VHSIC program developed fabrication technologies which could, by the end of Phase 2, produce chips that were fully capable of meeting military radiation hard specifications at very little, if any, extra cost.

## System Insertion: (Chapter 5)

A very substantial portion of the VHSIC management efforts and funding went into approximately twenty-seven system demonstration projects in which VHSIC chips and boards were integrated into system hardware so that the benefits and advantages could be realistically evaluated in a variety of applications. An even larger number of system insertion demonstrations were undertaken independently by system program offices, using the design and manufacturing capabilities developed by VHSIC program contractors. The technology insertion demonstrations, many of which continued beyond the formal close of the VHSIC program, have shown that VHSIC is highly effective in benefiting the performance, weight, space, power, and reliability of systems. Some platform systems in development, such as the LHX helicopter and the ATF fighter, are using electronic subsystems which would be impossible to design and build within the constraints of weight and space imposed by the platforms without the technology made available by the VHSIC program.

"When the helicopter-borne version of the AT&T-built AN/USY-2 enhanced modular signal processor enters fleet service in 1995, it will give anti-submarine forces 18 times the power of existing units at half the weight."

Defense Science, April 1990, p. 50

Two examples of the successful early insertion of VHSIC technology into systems that have passed the full scale development stage and are scheduled for production are the AN/APG-68 airborne radar signal processor by Westinghouse for the F-16 aircraft (scheduled for 1991 production) and the AN/AYK-14(V) airborne computer by Control Data Corporation (scheduled for 1990 production). These are described in Sections 5.3.4 and 5.2.2 respectively. In particular, the AN/AYK(V) insertion proved that the benefits expected of VHSIC could in fact be achieved in real systems, as the following table shows.

|                      | Previous Version | VHSIC Version |

|----------------------|------------------|---------------|

| Number of chips      | 13               | 5             |

| Complexity per chip  | 4000 gates       | 35,000 gates  |

| Chips fabricated     | 51               | 5             |

| Cost per chip        | \$50,000         | \$130,000     |

| Total chip cost      | \$2,550,000      | \$650,000     |

| PCB Iterations       | 4                | 1             |

| Check out time       | 15 months        | 4 months      |

| Design to brassboard | 42 months        | 30 months     |

Another important aspect of the technology insertion effort involved the use of VHSIC design and fabrication technology to alleviate the "obsolete parts" problem. Many of the integrated circuit chips used in military equipments go out of production as time progresses. This creates a difficult and expensive maintenance or resupply problem. The Air Logistics Command Center at Sacramento used the VHSIC technology to design circuit boards that were "form, fit, and function" replacements for equipment in the F-111 aircraft. The result was much less expensive than procurement of exact replacement parts, an improvement in reliability, and a much faster design cycle. Although the VHSIC program was neither designed nor expected to solve the broader aspects of system acquisition problems, it developed a technology that was available not only for designing and building new, advanced systems but also was very useful in solving some otherwise intractable problems of resupply and retrofit for older electronic subsystems.

## Technology Transfer: (Chapters 6 and 7)

VHSIC has carried out the task of transferring the technology developed in the contract programs to the people and organizations that could use it most effectively, in three direct ways.

First, the contract programs were conducted on a highly interactive, tri-Service basis, led by a Steering Committee composed of the DoD Program Director and the three Service Program Directors. The Steering Committee set policy, initiated programs, and evaluated progress. Formal, semi-annual (sometimes quarterly) technical reviews of each Phase 1 and Phase 2 contract were attended by technical evaluators from each of the Services. Technical committees in such areas as lithography, packaging, CAD, and qualification were formed, with representatives from each of the Services. These committees interacted closely with the contractors, helped to solve technical and programmatic difficulties, served as advisors to the Program Offices, and provided liaison with system program managers. The result of this management structure was a high level of communication, coordination, and cooperation within VHSIC and between VHSIC and potential system users.

Second, in order to increase the flow of information to potential users, the Program Office set up a series of VHSIC Application Workshops to describe the products being developed and the ways in which they could be applied in systems. Workshops for specialists in technical areas such as CAD, packaging, and qualification were organized and held at which information was exchanged, problems defined, and various approaches charted. More than forty such workshops were conducted in all sections of the U.S.

Third, a number of major conferences were organized, the most prominent of which were Annual VHSIC Conferences, held from 1982 to 1989. At these, the status of the total program was presented to a wide spectrum of technical and management attendees from Government and industry. Two VHSIC Tech Fairs were held at which the wares of most of the VHSIC contractors were displayed and demonstrated. Technical VHSIC sessions were organized at the Government Microelectronic Conference (GOMAC) for the years 1978 through 1989.

An important indirect mode of technology transfer activity also took place. The very existence of the VHSIC program and the visible results of its contract efforts spurred other companies to initiate independent IC technology development programs with the intention of remaining current and competitive. Several companies (including Raytheon in Phase 1 and Harris in Phase 2) even entered into no-cost contracts with the Government in order mutually to share information during their development activities. By the end of the VHSIC program the list of companies that had gained a VHSIC capability included most of the major IC fabrication and/or design houses in the United States.

There were other indirect processes, such as the wide distribution of technical reports and the development of DoD requirements documents, by which VHSIC technology diffused into the electronics industry and into the procedures for the procurement of military equipment.

## The Impact of VHSIC

VHSIC pursued certain specific goals in carrying out its program. ICs with fixed specifications and electronic brassboards configured for particular weapon systems were required to be demonstrated. On the other hand, because of the broad utility of IC technology, the impact of VHSIC activities and results could be equally broad and, therefore, difficult to measure. In order to assess the impact correctly one must, therefore, have a clear understanding of what VHSIC was expected to produce.

The fabrication goals of 1.25 and 0.5 micron feature sizes and the FTR goals of  $5x10^{11}$  and  $1x10^{13}$  gate-Hz/cm<sup>2</sup> were expected to be within the boundaries of the then-current development programs of the leading semiconductor companies. In fact, those were the

conditions under which the development contracts were let. The expectation was that these goals would accelerate the emergence of technology that was already under active commercial development and hasten its application to military designs. In many cases these VHSIC goals required the contractors to operate at the leading edge of their development efforts. For example, increased chip functionality required larger chip sizes which in turn required advances in optical lithography, multilevel chip interconnects, and packaging technology. The reduction in feature size to 0.5 micron in particular put a heavy emphasis on the development of high resolution lithography using both electron beams and light optics.

Therefore, the specific chips that were developed during Phases 1 and 2 and used in application brassboards were primarily intended to demonstrate that a comprehensive mastery of the technology which met the stringent VHSIC requirements could indeed be achieved. It was also hoped that derivatives of these chips would find wide spread system application and, therefore, be required in increasingly large numbers. They would also be quickly absorbed into the DoD acquisition process. This indeed did happen in some cases. In other cases the technology has evolved and diffused more indirectly so that the impact of VHSIC must be looked for beyond the bounds of the VHSIC hardware itself.

Chapters 2, 3, 5, and 7 of this report include articles on VHSIC that have been contributed by people who were participants in the program or who have closely followed the program activity in a particular field of technology. The papers they have written are their personal views of the impact VHSIC has had and include some descriptions of company-specific case histories by managers involved in VHSIC contracts. The contributed papers also emphasize that many of the applications of VHSIC, especially in the design automation area, are ongoing and even accelerating. Therefore the impact of VHSIC in some areas will increase in time.

This Executive Summary concludes with one such assessment by the initial architect of the VHSIC program in his role as a former Director for Electronic and Physical Sciences in the Office of the Under Secretary of Defense for Research and Engineering.

#### The Impact of VHSIC

Leonard R. Weisberg Vice President, Corporate Research and Engineering Honeywell, Inc.

The VHSIC program has had a profound impact on Honeywell's and other companies' technology and business strategies, and thus on the United States defense capabilities. Besides greatly accelerating the use of new technology ICs in

our military systems, VHSIC provided additional significant advantages including the VHDL language, high-speed multi-chip packaging, and interoperability standards. Furthermore, the VHSIC program established, at Honeywell, a source of highly advanced radiation hard ICs for critical space and strategic applications.

#### Impact on DoD Systems

In order to maintain the U.S. technology lead, the use of new technology ICs in military systems had to be accelerated. Highly advanced ICs had to be available for military use at the same time they became available for the commercial market, or even earlier. Even though the military portion of the IC market had shrunk to 7%, industry's attention had to be refocused onto military needs.

To accomplish this, a very different kind of program was needed. VHSIC was established with strong DoD policy support and unprecedented funding levels for a broad technology research and development program. VHSIC focused attention not only on advancing the IC technology, but also on special military system requirements including ultra—high speed processors for which the commercial demand is limited.

The VHSIC program galvanized the semiconductor IC industry into action. Several of the largest IC manufacturers became contractors or subcontractors in the VHSIC program including IBM, Motorola, TI, and National; it is noteworthy that the last three are presently among the top five producers of military ICs. Similarly, VHSIC became the focal point of attention among the top military contractors for electronic systems and subsystems, with Westinghouse, Hughes, TRW, and Honeywell as main contractors in VHSIC.

The VHSIC technology goals were symbolized by the numbers 1.25 micron ("near-micron") and 0.5 micron ("submicron"). These numbers set new, demanding goals for the production of military ICs at both merchant IC manufacturers and system developers. Achieving submicron dimensions was no longer a distant goal, oriented mostly to commercial memory requirements. Instead, it became a real target whose achievement would ensure a leading business position for those companies that reached it.

As a result, the VHSIC contractors built up their IC capabilities with investments estimated at double (or more) the VHSIC funding. For example, Honeywell invested about \$300 million, nearly triple its total VHSIC contract funding. Even companies that did not have VHSIC contracts felt that they had to remain competitive and therefore also significantly increased the investment in their military IC capabilities.

It is our estimate that near-micron and submicron military ICs have become available to the designers of military systems three to five years earlier than would have happened without the VHSIC program. Military systems and equipment are now in development with these advanced ICs, or their direct derivatives, which give unprecedented performance, size, weight, power and reliability that could not have been achieved without VHSIC.

There are now over 40 programs in which VHSIC has been or is being designed into future products. In Honeywell alone, these include the Enhanced

Modular Signal Processor (the new Navy standard processor), the MK-50 Advanced Lightweight Torpedo, the Advanced Spaceborne Computer Module, the Multipurpose Space Computer, and upgrades to Milstar.

#### Impact on Technology

Besides meeting the main VHSIC goal of accelerating military IC capabilities by three to five years, other important capabilities emerged from the VHSIC program of significant importance to industry.

## VHSIC Hardware Description Language (VHDL)

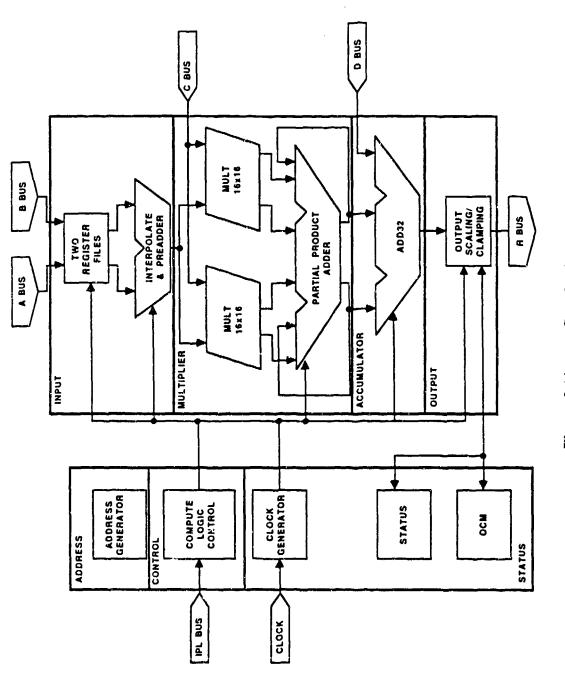

The development of VHDL is particularly notable. The VHDL portion of the VHSIC program was a far-sighted endeavor with an outstanding payoff. It is now possible to start an IC design at a functional system-level description, proceed into more and more detailed design levels and end up with a fully documented and well validated circuit layout ready for fabrication. This is all done under the control of a computer aided design (CAD) system. It significantly reduces the time and cost of the design by virtually eliminating the need for major redesign.