# Display Technologies for Intel<sup>®</sup> Graphics

Chak Sriprasad – Director, Display Software Engineering, Intel Corporation

**GVCS001**

# Agenda

**IDF**13

- Mobile Industry Processor Interface (MIPI\*) Based Displays

- Overview

- Enabling considerations

- Scalable model for fast time to market

- Display Power Savings

- Display power consumption

- Display power savings features

- Miracast<sup>\*</sup> Wireless Display Demo

#### Agenda

- MIPI\* DSI Based Displays

- Overview

- Enabling considerations

- Scalable model for fast time to market

- Display Power Savings

- Display power consumption

- Display power savings features

- Miracast<sup>\*</sup> Wireless Display Demo

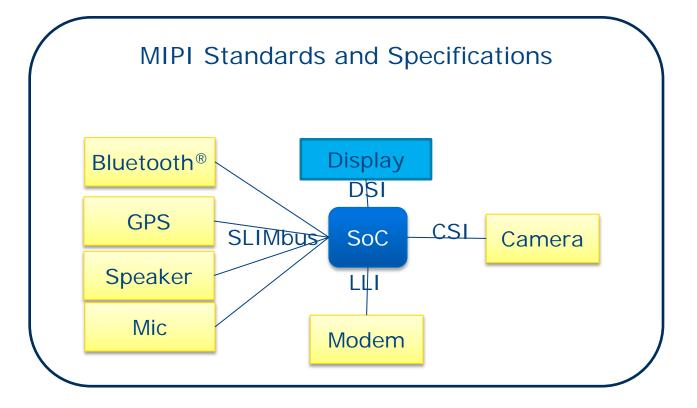

#### **MIPI\* Display Overview**

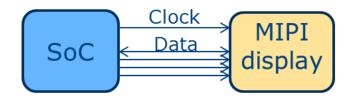

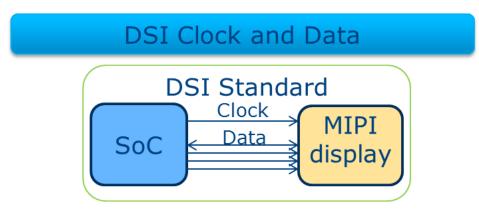

**DSI Clock and Data**

5

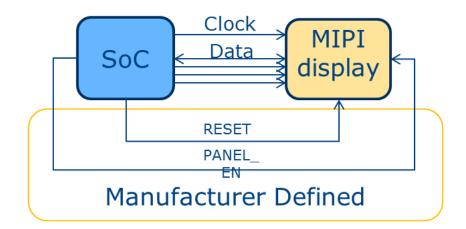

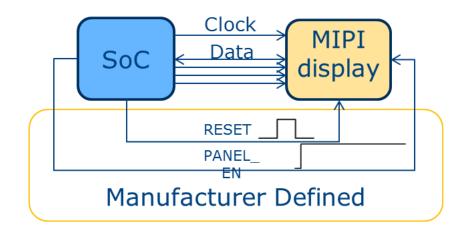

Manufacturer Defined Pins

5

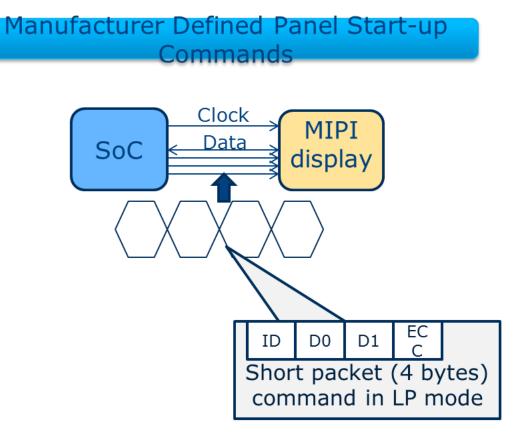

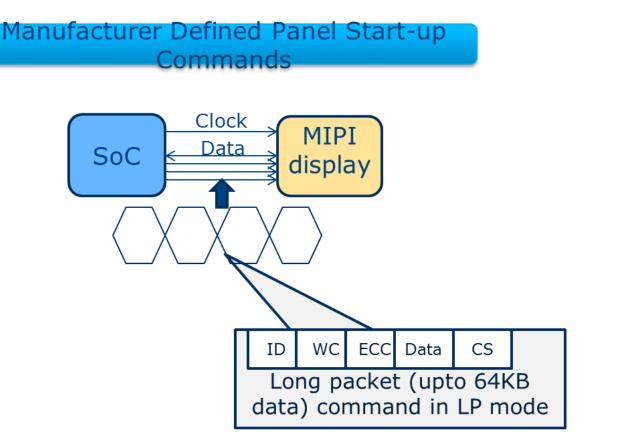

Panel Power-up Sequence

5

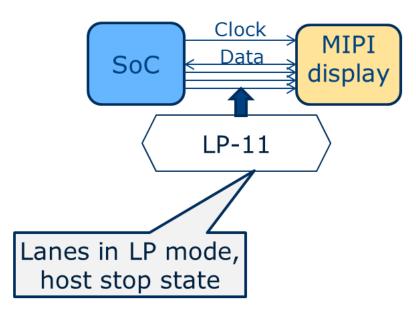

Lane State On Power-up

**IDF**13

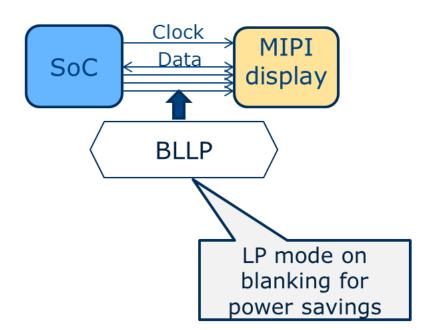

Video Mode: Blanking

#### **MIPI\*** Display Support on Intel Platforms

Intel Atom processor Z2760 MIPI DSI 1.01 4 lanes 1366x768

MIPI to LVDS 11" Native bridge + MIPI 11" LVDS Panels Intel<sup>®</sup> Atom<sup>™</sup> processor based Bay Trail platform

MIPI DSI 1.01 2x4 lanes (Dual-link) Single-link -1920x1200 Dual-link - 2560x1600

~10" native MIPI

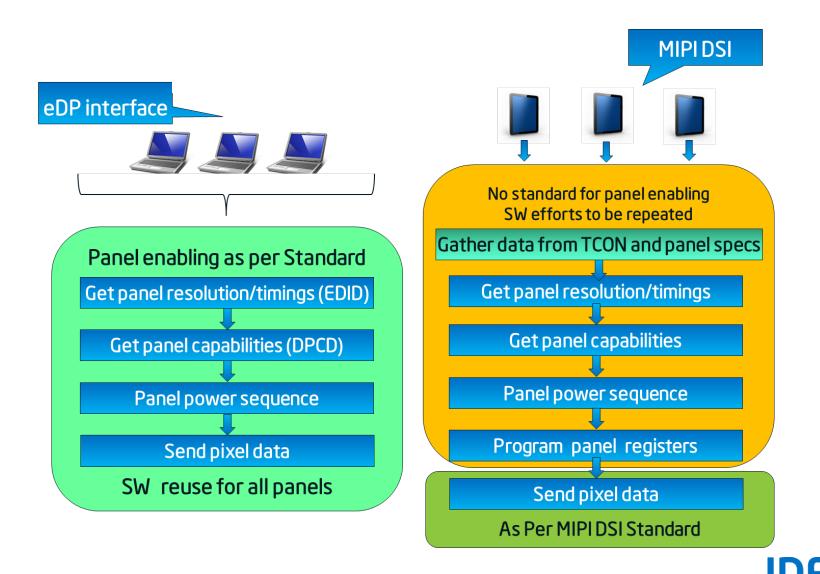

#### MIPI\* vs. eDP\* Panel Enabling

## MIPI\* -DSI Panel Interface considerations

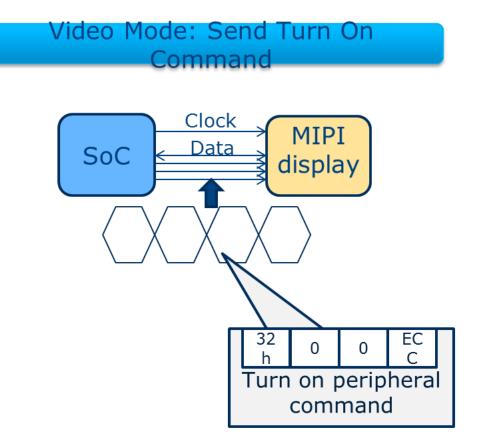

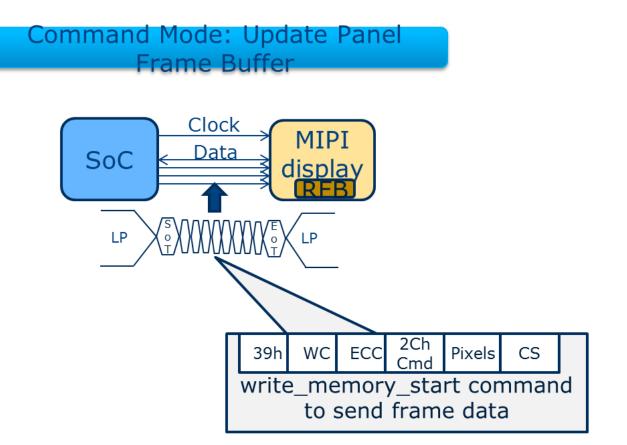

- Panel Variations: Command Mode / Video Mode: W & w/o burst mode; sync events or sync pulses; preferred operating mode

- EDID support is not uniform or consistent

- Panel resolution and timing parameters

- commended format

- Recommended data rate/D figuration for book

Panel power up seer Constant signals and delays

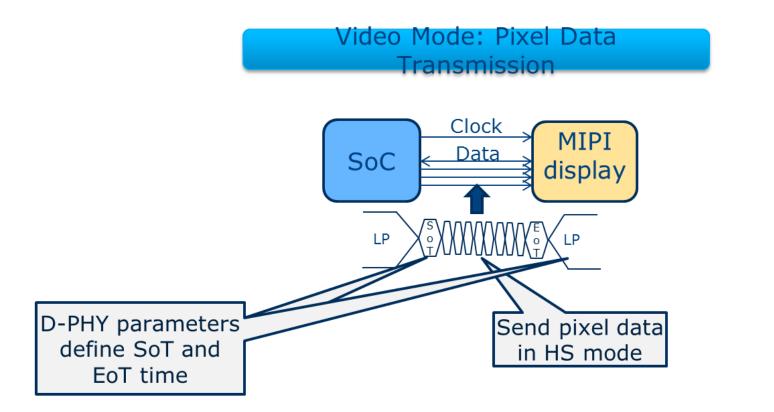

LP to HS and many witching time required Jues for DPHY parameters THS-PREPARE, , ICLK-TRAIL, THS-ZERO, EOT packet

- er programming (EPROM based or by host) during power up/down; programming sequence; default values

- Panel backlight control (external PWM?)

18

- CABC support and register programming sequence

- Other value-add features supported on the panel; its enabling

## **MIPI\*** Panel Enabling Implications

| Panel<br>Implementations                                                  | Hardware/Software Impact                                                                                      |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| No EDID                                                                   | Software: EDID should be configured in VBT                                                                    |

| Variance in panel capability<br>(lane count, command/video<br>mode, etc.) | Software: The panel parameters must be configured and read from VBT                                           |

| Panel power sequence (pin controls and delays)                            | Software: Driver code addition for panel power sequence                                                       |

| No internal EPROM for panel register initialization                       | Software: Driver code addition of command sequence for panel register initialization                          |

| Non-standard pin<br>assignment, cable,<br>connector                       | Hardware: Add-on card and cable design<br>according variance in panel pins for<br>Reference Hardware platform |

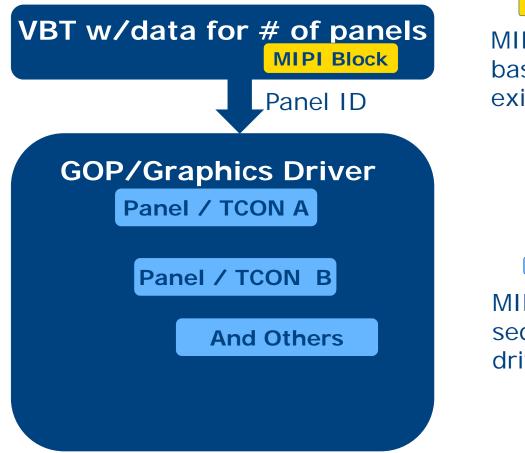

#### **Current Driver Model for MIPI\***

MIPI block in firmware with basic config data used in existing platforms

MIPI\* panel enabling sequence hard coded in driver for each panel

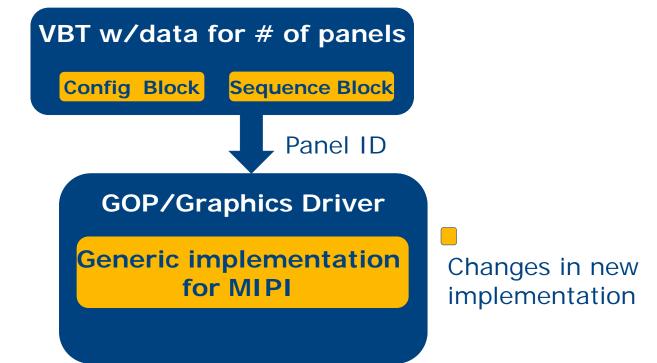

### **Towards a Generic Model**

- Goals:

- No driver code changes

- Support in both GOP and driver

- Extends to all types of MIPI\* panels/TCON:

- Scalable for future features / specs / platforms

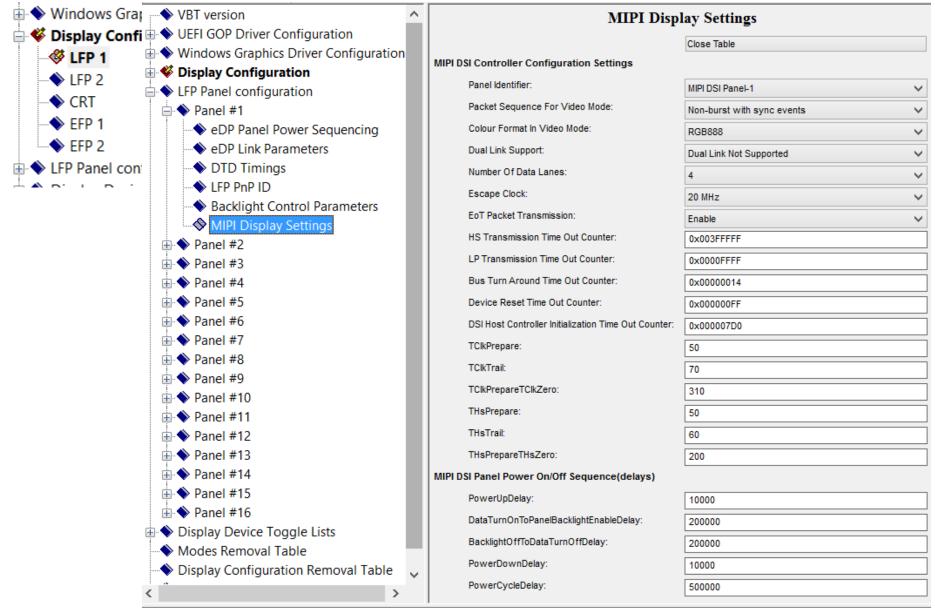

#### **BMP<sup>1</sup> Settings for Configuration Block**

<sup>1</sup> BMP – Binary Modification Program -- tool

22

## **MIPI\* Sequences Programming**

- MIPI\* Sequences

- Reset assert/de-assert sequence

- Programming panel OTP by sending DCS commands

- Display ON/OFF sequence

- Backlight ON/OFF sequence

- Sequence Operations

- Delay

- Send MIPI packets

- GPIO programming

- MMIO programming

| 4                                | MIPISeqTool 🗕 🗆               |                           |  |  |  |

|----------------------------------|-------------------------------|---------------------------|--|--|--|

| Options                          |                               |                           |  |  |  |

| Selection Block<br>Choose Action | Add New Sequence 🗸            | Input File (.bin or .xml) |  |  |  |

| Choose Sequence<br>Element       | MIPI SEQUENCE RESET V         | ]                         |  |  |  |

| Byte 0 0 0<br>(hex) Payload      | 0                             |                           |  |  |  |

| Data Type, Flags, Wor            | d Count                       |                           |  |  |  |

|                                  | Save Element<br>Save Sequence | Save Sequence To File     |  |  |  |

|                                  |                               | ^                         |  |  |  |

#### **Generic MIPI\* Design Advantages**

| Existing model for MIPI* in driver                                                | Generic MIPI support in driver                                                                       |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Updates and rebuild GOP/Gfx driver panel                                          | No panel specific GOP/Gfx driver changes                                                             |

| Panels, AIC needed w/driver<br>developers                                         | Easy panel enabling w/ just VBT<br>modification (more virtual<br>developers, i.e., AE, OEM)          |

| Requires more panel enabling time                                                 | Saves panel enabling effort                                                                          |

| Driver update for TCON issues<br>(post-launch issues will need driver<br>updates) | No driver updates fixing TCON<br>specific issues<br>(post-launch issues will need driver<br>updates) |

| Not scalable for newer features/<br>Panels/ platforms                             | Easily scalable for supporting newer features/ panels/ platforms                                     |

| Supports both Android* & Windows*                                                 | Supports both Android & Windows                                                                      |

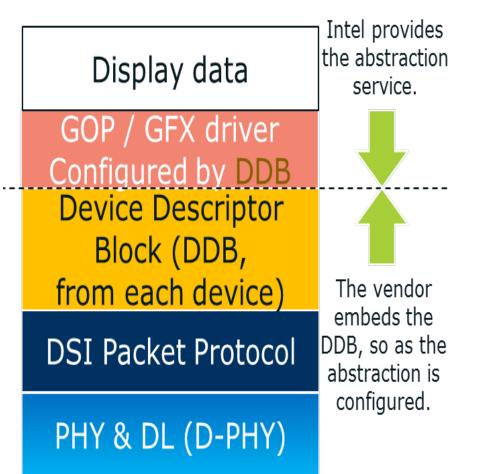

#### **Towards Further Standardization**

- Intel working to define a standard MIPI\* panel descriptor

- Goal is to implement the standard descriptor among panel TCONs

- Driver would read the panel descriptor from the panel and take the enabling actions

- Next steps / Call to action

- TCON vendor collaboration for common DDB format

#### Agenda

- MIPI\* DSI Based Displays

- Overview

- Enabling considerations

- Scalable model for fast time to market

- Display Power Savings

- Display power consumption

- Display power savings features

- Miracast<sup>\*</sup> Wireless Display Demo

### **Display Power Savings**

Agenda

- Display power consumption

- Display power saving features

- Backlight control

- Intel<sup>®</sup> Display Power Saving Technology (Intel<sup>®</sup> DPST)

- Content Adaptive Backlight Control (CABC)

- DPST vs. CABC backlight power comparison

- Windows<sup>\*</sup> 8 adaptive brightness control

- MIPI\* display self refresh

- Embedded DisplayPort\* (eDP) panel self refresh

- Other power saving options

- Co-existence of display power savings features

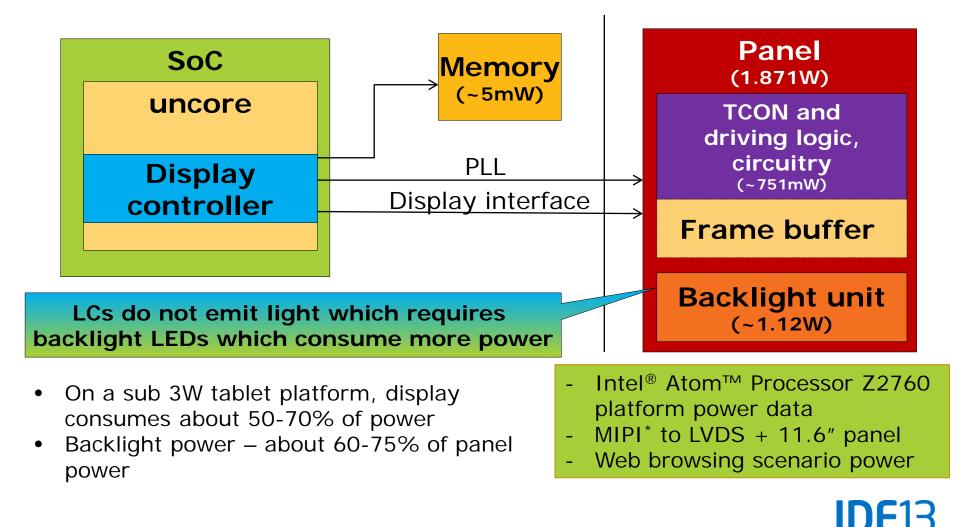

#### **Display Power Consumption**

Display sub-components that consume power

## **Display Power Saving Features**

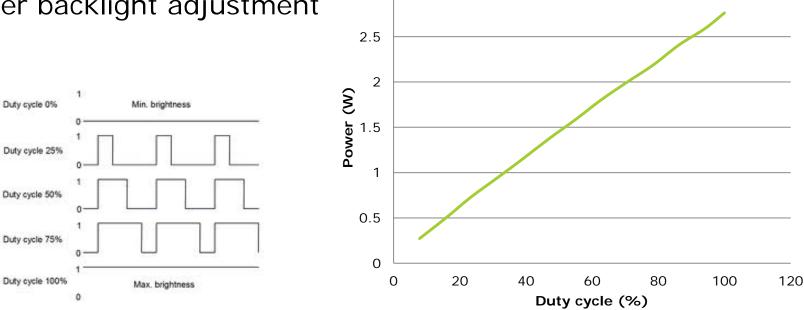

### **Backlight Control**

- PWM signals control backlight intensity and power

- OS reduces backlight on •

- User inactivity

- Ambient light change

- User backlight adjustment ۲

3

Controlling backlight intensity linearly impacts power

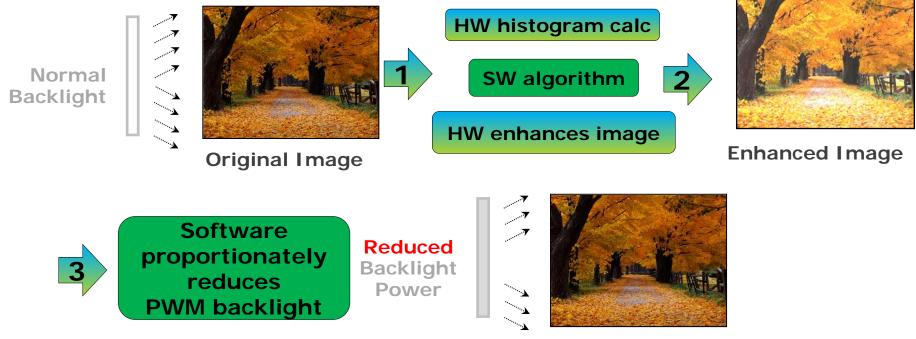

#### Intel<sup>®</sup> Display Power Saving Technology (Intel<sup>®</sup> DPST)

- A power savings technology that reduces backlight power

- Increases pixel luminance and reduces backlight with minimum visual impact

**Visually Equivalent**

For DVD workloads, Intel DPST 6.0 reduces backlight power by about 70%

#### **Content Adaptive Backlight Control (CABC)**

- Similar concept as Intel<sup>®</sup> Display Power Saving Technology (Intel<sup>®</sup> DPST), reduces backlight power

- Implementation is on the panel and proprietary to vendor

- Supported on MIPI\* panels/bridges

- Controlled through MCS packets on MIPI

- Intel DPST and CABC cannot be enabled together

CABC on Intel<sup>®</sup> Atom<sup>™</sup> Z2760 processor reduces backlight power by about 33% on video playback scenarios

In general for command mode MIPI panels CABC is preferred

#### Windows\* 8 Adaptive Brightness Control

- OS policy for backlight control algorithms

- Requires a balance between power and user experience

- OS controls DPST/CABC

- OS enables CABC based on scenario

- Enabled in battery power and disabled on AC power

- Lower aggressiveness with desktop, browsing, photos, static content

- Higher aggressiveness with dynamic content like video

### **MIPI\*** Display Self Refresh

- Supported on MIPI<sup>\*</sup> command mode panels

- Pixels are sent to panel only on demand

- Display engine is active only when pixels are fetched

- DSI PLL can be power gated when OS detects idleness

- Display memory bandwidth is not consumed when display is idle

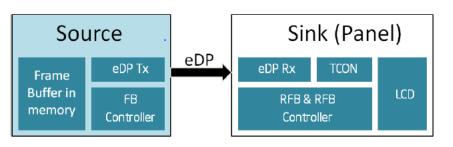

#### Embedded DisplayPort\* (eDP) Panel Self Refresh (PSR)

- Similar to MIPI\* DSR, utilizes panel frame buffer

- Supported on eDP 1.3 with PSR panels

- Hardware detects idle display and enters PSR active

- Display engine clock gated on PSR active

- Software needs to exit PSR on user activity

PSR and DSR save power on display engine, memory panel power on I/O, but panel frame buffer will consume power SoC+memory+panel savings could save ~17%

#### **Other Power Saving Options**

- Max FIFO

- Combine display FIFO in single display

- Reduces internal clock activity and memory I/O

- Saves power on display engine and memory I/O

- Dynamic Voltage Frequency Scaling

- Set Core Display clock according to the max resolution

- Display vnn scales according to CD clock

- Saves power on display engine

#### **Coexistence of Display Power Savings Features**

|                      | eDP<br>PSR | MI PI<br>DSR | DPST | CABC | DVFS | Max<br>FIFO | Backlight<br>control |

|----------------------|------------|--------------|------|------|------|-------------|----------------------|

| eDP PSR              |            | NA           | Yes  | NA   | Yes  | Yes         | Yes                  |

| MIPI* DSR            |            |              | Yes  | Yes  | Yes  | Yes         | Yes                  |

| DPST                 |            |              |      | NA   | Yes  | Yes         | Yes                  |

| CABC                 |            |              |      |      | Yes  | Yes         | Yes                  |

| DVFS                 |            |              |      |      |      | Yes         | Yes                  |

| Max FIFO             |            |              |      |      |      |             | Yes                  |

| Backlight<br>control |            |              |      |      |      |             |                      |

#### Agenda

- MIPI\* DSI Based Displays

- Overview

- Enabling considerations

- Scalable model for fast time to market

- Display Power Savings

- Display power consumption

- Display power savings features

- Miracast\* Wireless Display Demo

#### Miracast\* Wireless Display Demo

#### Summary

- MIPI\*-DSI Displays

- Intel scalable model is imperative for time to market

- Need OxM, Panel, TCON support for success

- Further standardization opportunities need industry support

- Display Power Management

- Several techniques exist to fine tune design for optimal power performance

- Screen size, resolution; Panel type, capability will drive right power optimization schemes

#### **Next Steps**

- MIPI\* DSI Displays

- Needs Industry Collaboration Panel, TCON, OxM, IHV to drive efficient design and robust enabling

## **Additional Sources of Information**

PDF of this presentation is available is available from our Technical Session Catalog: <u>www.intel.com/idfsessionsSF</u>. The URL is on top of Session Agenda Pages in Pocket Guide.

Additional info on the web – www.mipi.org

#### Legal Disclaimer

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: <u>http://www.intel.com/design/literature.htm</u>

Bay Trail and code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

Intel, Atom, Look Inside and the Intel logo are trademarks of Intel Corporation in the United States and other countries.

\*Other names and brands may be claimed as the property of others. Copyright ©2013 Intel Corporation.

## Legal Disclaimer

- Intel® WiDi Technology requires an Intel® Wireless Display enabled system, compatible adapter and TV. 1080p and Blu-Ray\* or other protected content playback only available on select Intel® Core™ processor-based systems with built-in visuals enabled, a compatible adapter and media player, and supporting Intel WiDi software and graphics driver installed. Consult your PC manufacturer. For more information, see <u>www.intel.com/go/widi</u>.

- Bluetooth is a trademark owned by its proprietor and used by Intel Corporation under license.

#### **Risk Factors**

The above statements and any others in this document that refer to plans and expectations for the third quarter, the year and the future are forward-looking statements that involve a number of risks and uncertainties. Words such as "anticipates," "expects," "intends," "plans," "believes," "seeks," "estimates," "may," "will," "should" and their variations identify forward-looking statements. Statements that refer to or are based on projections, uncertain events or assumptions also identify forward-looking statements. Many factors could affect Intel's actual results, and variances from Intel's current expectations regarding such factors could cause actual results to differ materially from those expressed in these forward-looking statements. Intel presently considers the following to be the important factors that could cause actual results to differ materially from the company's expectations. Demand could be different from Intel's expectations due to factors including changes in business and economic conditions; customer acceptance of Intel's and competitors' products; supply constraints and other disruptions affecting customers; changes in customer order patterns including order cancellations; and changes in the level of inventory at customers. Uncertainty in global economic and financial conditions poses a risk that consumers and businesses may defer purchases in response to negative financial events, which could negatively affect product demand and other related matters. Intel operates in intensely competitive industries that are characterized by a high percentage of costs that are fixed or difficult to reduce in the short term and product demand that is highly variable and difficult to forecast. Revenue and the gross margin percentage are affected by the timing of Intel product introductions and the demand for and market acceptance of Intel's products; actions taken by Intel's competitors, including product offerings and introductions, marketing programs and pricing pressures and Intel's response to such actions; and Intel's ability to respond quickly to technological developments and to incorporate new features into its products. The gross margin percentage could vary significantly from expectations based on capacity utilization; variations in inventory valuation, including variations related to the timing of qualifying products for sale; changes in revenue levels; segment product mix; the timing and execution of the manufacturing ramp and associated costs; start-up costs; excess or obsolete inventory; changes in unit costs; defects or disruptions in the supply of materials or resources; product manufacturing quality/yields; and impairments of long-lived assets, including manufacturing, assembly/test and intangible assets. Intel's results could be affected by adverse economic, social, political and physical/infrastructure conditions in countries where Intel, its customers or its suppliers operate, including military conflict and other security risks, natural disasters, infrastructure disruptions, health concerns and fluctuations in currency exchange rates. Expenses, particularly certain marketing and compensation expenses, as well as restructuring and asset impairment charges, vary depending on the level of demand for Intel's products and the level of revenue and profits. Intel's results could be affected by the timing of closing of acquisitions and divestitures. Intel's results could be affected by adverse effects associated with product defects and errata (deviations from published specifications), and by litigation or regulatory matters involving intellectual property, stockholder, consumer, antitrust, disclosure and other issues, such as the litigation and regulatory matters described in Intel's SEC reports. An unfavorable ruling could include monetary damages or an injunction prohibiting Intel from manufacturing or selling one or more products, precluding particular business practices, impacting Intel's ability to design its products, or requiring other remedies such as compulsory licensing of intellectual property. A detailed discussion of these and other factors that could affect Intel's results is included in Intel's SEC filings, including the company's most recent reports on Form 10-Q, Form 10-K and earnings release.

Rev. 7/17/13