FALL/WINTER 2010 VOLUME 11, NUMBER 1 WWW.TIIJ.ORG

**Technology Interface International Journal**

ISSN: 1523-9926

Philip D. Weinsier Editor-in-Chief

Jeff Beasley Founding Editor

Published by the

**International Association of Journals & Conferences**

# Time to change the way academics works? Try acamedics!

f you are not using the Internet, please skip this ad and enjoy the rest of the journal. The average burden of reading this ad is two minutes, which may add two months of productivity to your academic life. Seriously!

Whether you organize a conference, publish a journal, or serve on a committee to collect and review applications, you can use the Internet to make your life easier. We are not talking about emails. We are talking about state-of-the-art online systems to collect submissions, assign them to reviewers, and finally make a decision about each submission. We are talking about value-added services, such as payment and registration systems to collect registration fees online. We are talking about digital document services, such as proceedings CD/DVD development and duplication, or creating professional-looking digital documents.

Finally, we are talking about AFFORDABLE PRICE, QUALITY, and CUSTOMIZATION. And we are talking about each of them at the same time.

By the way, you don't have to be a computer geek to use our systems. We have a couple of them, and they will do all the technical mumbo jumbo for you. We also have a few select people from academics like you, and they know what you do. You just relax and enjoy our systems.

If you are still reading this ad, chances are you are interested in our systems or services. So, visit us at *www.acamedics.com*. While you are there, check the names of our clients as well. Most of them are quite familiar, but the list is too long to include here.

#### TECHNOLOGY INTERFACE INTERNATIONAL JOURNAL

The TECHNOLOGY INTERFACE INTERNATIONAL JOURNAL (TIIJ) is an independent, not-for-profit publication, which aims to provide the engineering technology community with a resource and forum for scholarly expression and reflection.

TIIJ is published twice annually (Fall/Winter and Spring/Summer issues) and includes peer-reviewed articles that contribute to our understanding of the issues, problems, and research associated with engineering technology and related fields. The journal encourages the submission of manuscripts from private, public, and academic sectors. The views expressed are those of the authors and do not necessarily reflect the opinions of TIIJ or its editors.

#### **EDITORIAL OFFICE:**

Philip Weinsier, Ed.D. Editor-in-Chief

Office: (419) 372-0628 Email: philipw@bgsu.edu Department of Applied Sciences Bowling Green State University-

Firelands

One University Dr. Huron, OH 44839

#### THE TECHNOLOGY INTERFACE INTERNATIONAL JOURNAL

Editor-in-Chief:

**Philip Weinsier**

Bowling Green State University-Firelands

Production Editor:

Li Tan

Purdue University North Central

Subscription Editor:

Morteza Sadat-Hossieny

Northern Kentucky University

Financial Editor:

Li Tan

Purdue University North Central

Manuscript Editor:

Haoyu Wang

Central Connecticut State University

Executive Editor:

Mark Rajai

California State University-Northridge

Copy Editor:

Li Tan

Purdue University North Central

Publishers:

Farrokh Attarzadeh

University of Houston

Hisham Alnajjar

University of Hartford

Web Administrator:

Saeed Namyar

Namyar Computer Solutions

### TABLE OF CONTENTS

| Editor's Note: The Technology Interface International Journal Joins IAJC                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The Evolution of Virtual Reality Environments and Implementation of New Technologies:                                                                               |

| Design and Development of a Durability Testing Machine                                                                                                              |

| Design Project Based Modules to Promote Engineering Learning and Retention                                                                                          |

| Finding the Exact Maximum Impedance Resonant Frequency of a Practical Parallel                                                                                      |

| Kenneth V. Cartwright, College of The Bahamas; Elton Joseph, College of The Bahamas; Edit J. Kaminsky, University of New Orleans                                    |

| Evaluation of Fatigue Criteria for Asphalt Pavements                                                                                                                |

| Developing a Digital Logic Design Curriculum in Electrical Engineering Technology:                                                                                  |

| Using an Industrial Advisory Council for Student Outcomes Assessment: A Work in Progress                                                                            |

| Meeting Student and Industry Needs Through Experiential Learning and Soft Skills Study in Computer Graphics                                                         |

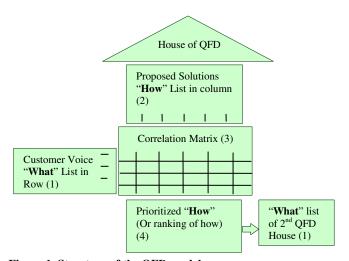

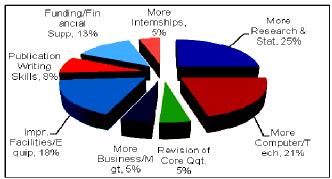

| Case Study: Applying QFD in a Graduate Curriculum Design for an Industrial Engineering Technology Program                                                           |

| Analysis of Metallurgical and Mechanical Failure of a Centrifugal Compressor                                                                                        |

| Built-in-self-test (BIST) for System-on-a-chip Using Output Voltage Difference Between Fault-free and Faulty Devices 78<br>Graham Thomas, Texas Southern University |

| Instructions for Authors                                                                                                                                            |

# EDITOR'S NOTE: THE TECHNOLOGY INTERFACE INTERNATIONAL JOURNAL JOINS IAJC

Philip Weinsier, TIIJ Editor-in-Chief

# TIIJ is the Newest Member of the IAJC-owned Journals

After many successful years of service to engineering technology, and special thanks to former editor Jeff Beasley, the Technology Interface Journal sports a new name and joins the International Association of Journals and Conferences (IAJC). For the first published issue of the *Technology Interface International Journal* (TIIJ) since joining IAJC, the acceptance rate was just under 50%. We expect that future rates will continue to be in a range similar to what they had been over the journal's previous years, roughly 50%. Information about TIIJ can be accessed via the IAJC web site (<a href="www.iajc.org">www.iajc.org</a>) or directly at <a href="www.tiij.org">www.tiij.org</a>. TIIJ, like the other IAJC journals, is published both online and in print.

### IAJC also Welcomes Three New Affiliate Journals

IAJC, the parent organization of TIIJ, the *International Journal of Modern Engineering* (IJME) and the *International Journal of Engineering Research and Innovation* (IJERI), is a first-of-its-kind, pioneering organization acting as a global, multilayered umbrella consortium of academic journals, conferences, organizations, and individuals committed to advancing excellence in all aspects of education related to engineering and technology. IAJC is fast becoming the association of choice for many researchers and faculty due to its high standards, personal attention, fast-track publishing, biennial IAJC conferences, and its diversity of journals.

IAJC would also like to welcome the following to its growing list of affiliate journals: The *International Journal of Engineering* (IJE), the *International Journal of Industrial Engineering Computations* (IJIEC) and the *International Transaction Journal of Engineering, Management, & Applied Sciences & Technologies* (ITJEMAST). With a total of 13 journals, authors now have a venue for publishing work across a broad range of topics.

### IAJC-ASEE 2011 Joint International Conference

The editors and staff at IAJC would like to thank you, our readers, for your continued support and look forward to seeing you at the upcoming IAJC conference. For this third biennial IAJC conference, we will be partnering with the American Society for Engineering Education (ASEE). This event will be held at the University of Hartford, CT, April 29-30, 2011, and is sponsored by IAJC, ASEE and IEEE (the Institute of Electrical and Electronic Engineers).

The IAJC-ASEE Conference Committee is pleased to invite faculty, students, researchers, engineers, and practitioners to present their latest accomplishments and innovations in all areas of engineering, engineering technology, math, science and related technologies. Presentation papers selected from the conference will be considered for publication in one of the three IAJC journals or other affiliate journals. Oftentimes, these papers, along with manuscripts submitted at-large, are reviewed and published in less than half the time of other journals. Please refer to the publishing details at the back of this journal, or visit us at <a href="www.iajc.org">www.iajc.org</a>, where you can also read any of our previously published journal issues, as well as obtain information on chapters, membership and benefits, and journals.

#### **International Review Board**

TIIJ is steered by IAJC's distinguished Board of Directors and is supported by an international review board consisting of prominent individuals representing many well-known universities, colleges, and corporations in the United States and abroad. To maintain this high-quality journal, manuscripts that appear in the *Articles* section have been subjected to a rigorous review process. This includes blind reviews by three or more members of the international editorial review board—with expertise in a directly related field—followed by a detailed review by the journal editors.

EDITOR'S NOTE: THE TECHNOLOGY INTERFACE INTERNATIONAL JOURNAL JOINS IAJC

| THE TECHNOLOGY INTERFACE INTERNATIONAL JOURNAL   VOLUME 11, NUMBER 1, FALL/WINTER 2010 |

|----------------------------------------------------------------------------------------|

|                                                                                        |

|                                                                                        |

# THE EVOLUTION OF VIRTUAL REALITY ENVIRONMENTS AND IMPLEMENTATION OF NEW TECHNOLOGIES: AN OVERVIEW OF THE CURRENT STATE OF RESEARCH

Kimberly James Nankivell, Purdue University Calumet

#### **Abstract**

The evolution and use of virtual reality environments (VREs) have coincided with the advancement in software and hardware technologies. These advancements in technologies have provided academia, business, and government new avenues for expansion with less expensive and more enhanced forms of VREs. This study sought to compile a review of available literature with respect to the implementation and usability of VREs, examining how the advances in these technologies have affected these environments. This review considers how these environments are being used and the nature of the institutions exploiting them. Further outlined is the newest research and the potentials this research is discovering. Subsequently, this study considered the legal, social, and political questions that the participants in VREs must address and concluded with what possible new technologies are being examined and opportunities for future research in these virtual reality environments.

#### Introduction

The use of virtual reality environments (VREs) in education, business, research, and government has increased substantially since the early introduction of the technology. Within the last decade the cost of the technologies to create VREs has become reasonable for many organizations and institutions. Prior to the advancement of these technologies, only those organizations and institutions which could afford the high-priced mainframe computers required to create these environments could implement them [1]. The original implementations of VREs were for simulations, engineering, and entertainment. The explosion in computer hardware and software technology over the past few decades brought with it an evolution in the functionality and availability of VREs.

The definition of VRE has matured with the evolution of the technologies such that a VRE is now defined as a computer-generated three-dimensional (3D) location, created by a virtual environment software package that can provide an interactive experience influenced by a user [2]. The user experience provided is one of interaction, immersion, and

imagination combining simulation, multimedia functionality and artificial intelligence, experiences which are delivered over network technologies. The navigational systems within these VREs can be classified into two types. The first type employs immersive VREs that require various types of devices such as head-mounted displays, projection-based setting (CAVE), stereoscopic headsets, etc. The desktop virtual navigation system is the alternative and is the least expensive VRE approach that employs the display screen of the system to engage the user [3].

The introduction of Web 2.0 has seen an increase in deploying these environments. Virtual Reality Modeling Language (VRML) is currently the open source standard of choice for creating internet based virtual environments [3]. Interactive environments such as Second Life, Cyworld, and Entropia Universe are increasing in their popularity and usability as social platforms on the World Wide Web. These interactive worlds employ avatars, which are digital representations of the user, to provide the virtual presence to interact with other participants.

The current research into the implementations of VREs is on many fronts. The evolution of virtual environments coincides with research into the devices and technologies to increase the functionality of these VREs. Motion-capture systems, projection systems, and headset displays are just some of the fields of research. These types of technologies will enhance the interactivity and usability of such environments to customize VREs for such endeavors as training and social interaction [4].

The next section will detail the methodology used to examine the validity of the articles reviewed, including the rationale for including those articles reviewed for this study. The following section provides an overview of the types of VREs being employed and the various institutions and organizations which use these technologies. A review of the quantitative and qualitative research being conducted is presented, along with results and discussion on the literature review and conclusions drawn from this review.

#### Research Methodology

An empirical methodology was carried out for this overview in order to examine the current research on the topic. This review was designed to assist in identifying the issues, uses and solutions research has undertaken to better understand virtual reality environments (VREs) and provide the best methodologies to increase and improve the use of these environments.

One of the core purposes of this review was to create a valid and robust reference list to add to the credibility of the research. Each reference was evaluated using the following criteria: (a) the integrity of the author(s) and/or institution(s) where the research was performed along with a robustness and methodology that conforms to best practices, (b) whether the article was subjected to a peer-review process, (c) timeliness and relevance of the article, and (d) the diversity of the subject matter to current academic research was also considered carefully. Some anecdotal articles were also included as a means of providing richness to the content of the article.

#### Virtual Reality Environments

#### Historical Perspective

Virtual reality environments were once considered to be available only to those institutions and organizations that had access to large sums of money and mainframe computers. The environments were rudimentary in nature, with limited modeling technologies available for creating realistic environments and characters. The initial implementations of these VREs were for simulation, training and educational endeavors. The cost of these technologies was considered prohibitive for all but a few institutions. It was estimated that a quarter of a million dollars (\$250,000 US) would be required to create a very limited set of networked virtual worlds Beyond the initial cost of the system to create a VRE, the usability of such systems was far from what would be required to facilitate the multiple methods of interaction required. The networking technologies inhibited the distribution of these VREs and limited the size and scope as well. The modeling software also was a hindrance to usability, providing only simple systems with counts under 10,000 polygons [5].

The research in the early 1990s recognized the need for advancements in technologies to overcome the impediments that hindered the use of VREs. It was suggested that lightweight, dynamic software programming would need to be developed to allow for fluid interaction of environments including advancements in collision detection, command

structure and the user interface. It was also suggested that this dynamic software be developed specifically for VRE creation and implementation. Along with software improvements, devices needed to be developed to allow for more functional participation in immersive environments such as head-mounted displays, hand-held devices and motion-capture tracking devices [5], [6]. These initial implementations and recommendations provided the needed foundations for the research and advancements that has progressed to today.

#### **Current VRE Implementation**

These technologies have improved to the point where current VRE implementations can provide a wide variety of interactions, environments and characters, thus providing greater diversity in uses. Currently, VREs are far less expensive to implement than they were fifteen years ago. Current research indicates that a well-conceived VRE can be deployed on a high-end desktop computer or created over the internet using reasonably priced server technology [6]. This availability of affordable VREs has spawned growing implementation and research into evolving the medium.

The business community is realizing the benefits that virtual environments can provide through their implementations in production, marketing and communication. The use of a virtual production line at Deere & Company provides an example of the advantages that virtualization can provide. The company used a 3D computer model to recreate a parts production line, which then enabled investigation into how modifications to the production line would translate into enhanced parts production. This VRE, named VRFactory, proved that creating an immersive virtual production line allows for "the exploration of design changes and their effects on the simulation" [2].

The VRFactory as defined by Rehn et al. [2] was developed by modifying off-the-shelf software and hardware technologies. The final product referred to as Assembly Line Solution Set (ALiSS) incorporated four components, which created the functionality that was essential for the requirements outlined by Deere & Company. These components included a Graphics module that provided the means of displaying the 3D objects in the VRE, including the production line and parts. It also generated the user interface. The second component was a Data Processing module that handled the interpretation of the results of the simulations. A third component, the Logical module, was incorporated into ALiSS to establish and monitor the behavior of the virtual objects in the simulations. The final Interaction module was employed to provide the controls of ALiSS functionality [2]. The system was then deployed using a six-screen projection system to provide for full immersion for its users.

Prior to this implementation, the manufacturing industry was quite hesitant to employ these types of simulations or virtual production processes due to (a) time constraints for simulation development, (b) the cost of deploying effective simulation models, and (c) a lack of accessible real-time data of current production. These limitations were overcome by the development of the ALiSS system with its realized goals of (a) reduction in development time of the model, (b) the ability for non-specialists in simulations to perform investigations, (c) the transfer of results from simulation to actual production, and (d) the consistency of design of the final production line. The system was extensively tested and found to be extremely useful in evaluating prototype design and production-line processes [1]. This VRE allows a designer to run through a wide range of designs virtually and provides the stakeholders the opportunity to collaborate on the most appropriate direction to explore.

The increasing successful use of VREs within the business community has also expanded into the realm of online virtual worlds. The introduction of Second Life in 2003 by Linden Research, Inc. [7] marked the emergence of one of the most successful online virtual communities. Second Life, along with many other virtual communities (Entropia Universe, Cyworld, Active Worlds etc.), can be defined as virtual worlds (VW) or metaverses, which allow for a user to view alternate worlds via a computer screen or specialized goggles. The interaction within these alternate worlds is achieved by means of a digital representation in the form of an avatar [8]. These virtual worlds are a collaborative environment where one is able to experience the feeling of being physically connected with other individuals [9]. Along with the feeling of a physical presence, one is able to experience all forms of reality as diverse as eighteenth century London to a galaxy far into the future.

The avatar is the digital representation of the user and can have a distinct look and wardrobe, own its own property and make friends and associates. The communication can be by text and voice along with non-verbal gestures and expressions. The avatar (user) can, in many virtual worlds, create virtual business which can earn virtual money and the user can actually make a real-life living in the VW. The virtual money in many instances can be converted into real currency. The VW phenomenon not only has opportunities for individuals, but corporations, academic institutions, governments and researchers as well.

#### The Second Life Experience

The research community has taken a close look at Second Life (SL), which presently asserts a membership of over 13 million distinctive membership accounts with an in-world presence of over 680,000 in April of 2008 [8]. It has been

reported that Second Life has claimed to have the first virtual millionaire with a convertible currency called the Linden dollar allowing for actual exchange of currency through the LindeX virtual stock exchange [10]. The SL community provides a foundation for making possible communication, entertainment and education, which has provided businesses and academia opportunities to provide virtual facilities and services that users are accustomed to in the real world.

Businesses have begun opening store fronts to provide virtual goods and services in a manner similar to real-world endeavors. Banks (Wells Fargo, for example) have established a presence in SL. Meta Bank is a totally virtual bank providing the same services that a real bank provides, such as loans for purchasing virtual property and saving accounts for accruing interest. The entertainment industry has also established a presence in SL with MTV building its own space or "island" called MTV's Virtual Laguna Beach. (Islands are virtual spaces that individuals or entities can purchase for development.) Advertisers are also moving into SL to take advantage of the media-rich environment of the VW [10]. These business activities have evolved to where many businesses are creating virtual space for training.

The nature of SL provides for free-form user-created content that can be manipulated to suit the needs of the creator. British Petroleum has embraced this functionality by recreating a gasoline storage and piping system representative of a typical gas station. This virtual gas station allows trainees to visually inspect the underground components of the station and observe the operation of the safety devices. This provides a unique perspective of an extremely complex system that could not be achieved in real life [9].

Galagan [9] also reports on IBM's incorporation of SL into its corporate structure with a variety of experimental ways of providing new experiences and training for its employees. It is reported that over 6,000 IBM employees log into SL each week to experience a wide variety of activities. These activities include training, conversations with customers and the holding of meetings worldwide. A unique aspect of using SL is the opening up of the IBM Island to retired IBM employees to chat and stay in contact with one another and current IBM employees. Advanced 3D voice capability has been incorporated into the IBM implementation to allow for a more natural and realistic means of communicating.

Customer feedback is another avenue that has been employed by businesses to better design and market its products, as suggested by Galagan [9]. Starwood Hotels prototyped versions of its new high-tech loft-like hotels, referred to as Aloft. As part of the design process, the company created various prototypes of the proposed hotel and requested feedback on the most desirable designs. The auto-

maker Pontiac has a space in SL where its engineers can chat with customers on design and engineering concerns. Many other institutions such as Cisco, the National Oceanic and Atmospheric Administration (NOAA), NASA and the Tech Museum of Innovation have incorporated SL into their organizational culture to further enrich and enhance the goals of their respective institutions.

Medical research and information technologists have embraced SL as an avenue for research, dissemination of knowledge and training. Delarge [8] researched a variety of opportunities available in the VW environment. He concluded that "the most compelling and unique applications were in the areas of education & training and research" [8]. Play2Train, Second Health London and Ann Myers Medical Center provided the best examples of virtual applications that mimic real-world environments within the medical community. Ann Myers Medical Center is a virtual medical center for experimentation in virtual training for First Life Medical and Nursing students in diagnostics and bedside manner. The National Health Service London has created Second Health Life as a means of distributing health-care information and medical-practice information in an efficient and innovative manner. It is suggested by Delarge [8] that these and other types of medical endeavors are ideally suited for the VW environments.

Educational institutions have established a presence in SL as extensions of their physical classrooms. Harvard Law School provides a portion of its CyberOne course on Second Life's Berkman Island. A combined political science and business course is offered by Emery University housed at SIMsim Island [10]. These universities, along with many others, are recognizing the value that a VW such as Second Life (SL) can provide in the educational process. Many institutions in fact have gone one step further and have provided facilities for researchers and staff to create their own virtual reality environments (VREs).

#### Institutionally-owned VREs

Young [11] examines several universities' innovative implementations of VREs as supplements to their traditional educational activities. Cornell University has created a virtual science museum called SciCenter where the laws of physics do not apply. This, as suggested by one its creators, Ms. Corbit, provides for an educational 3D world that acts like a video game and creates a rich environment for education. The University of North Carolina at Wilmington has begun using VREs as sites for virtual classrooms. The instructors using this technology have been impressed with the level of communication provided by the environments and the interactivity demonstrated by the learners. These virtual classrooms are housed in an expansive virtual three-story

building which boasts an atrium and balconies for students to gather and relax. Assistant Professor of Education Gill observed that the students did remain in close proximity to one another, but when their avatars got too close or collided, the students demonstrated a sense of being offended for trespassing into their virtual space. The overall experience was extremely positive with the students attending the virtual classes more regularly than was experienced in previous physical classroom attendance.

The VREs have always been an integral component of the modern military establishment. The traditional use of VREs, and their related simulations as discussed by Stackpole [1], has been for battle-plan strategies, pilot training and weapons training. These traditional VREs are now included in even more realistic training for increasing the effectiveness and efficiencies in deploying and designing the everincreasing complex military systems. The basic motivator for the increased use of these VRE technologies is to reduce cost and increase safety [11].

#### Virtual Reality Research

Virtual environments have been employed in the form of virtual laboratories for many years. The Virtual Laboratory (VL) has been used as an alternative to physical labs due to the lack of funds, physical space, and the threat of physical harm to the student [12], along with the lack of physical proximity of the student to the physical lab. These VLs have taken on many degrees of complexity from a simple simulation presented on a CD to a network-based VL providing remote access to a complete learning environment with user set-ups [13].

#### Virtual Laboratory

Some of the more notable projects using VL technologies are being done at Te´le´universite´in Toronto, Canada, and Drexel University in Philadelphia, PA. VPLab is the name given to the Teʾleʾuniversiteʾ project that provides a student with a virtual lab that is instinctive, enjoyable, and an interface that is interactive. This VPLab was designed to provide the learner with an appearance of a serious lab environment and not a video game. The interface offers eight sets of generic tools that can perform twelve physics experiments.

Once the prototype of the VPLab was finalized, the virtual lab was presented to 13 students to determine the perceptions and integrity of the system. The evaluation involved the collection of data in three phases: (a) a questionnaire gathering demographic information on the students familiarity with simulations and computer software; (b) a series

of lab exercises were required that were indicative of what a novice user would perform; and, (c) an exit interview with each learn to better comprehend the effectiveness of the VPLab.

The overall reaction by the students was quite favorable with many valuable elements mentioned. Though one of the many objectives of the project was to stay away from the appearance of the VPLab as a video game, many of the students stated otherwise. The positive reactions towards the VPLab outstripped the negative reactions. The availability of on-demand video clips of an actual experiment being performed was quite beneficial. The visual cues on the functionality of each virtual object were extremely helpful in conducting the experiments and added to the realism. The students emphasized the feeling of freedom and control within the VPLab [13]. Overall, the VPLab was considered a success with further refinements being proposed by the researchers.

A second deployment of a virtual laboratory was performed at Drexel University and the results of the deployment and research were reported by Leitner and Cane [14]. This virtual network lab (VNL) was conceived to provide online learners with the experience of an actual IT laboratory. The VNL was created to allow online learners the ability to carry out multiple IT experiments, including the configuration of a virtual network. The researcher augmented the VNL by employing the Blackboard system as a course management tool.

The VNL designers' approach was an open system which allowed the students to work within the environment and have input into the construction of the virtual network connections for access to the lab [14]. This approach allowed the students to choose the appropriate elements to build the laboratory environment from which to carry out the experiments. This open-format construction was closely watched by the instructor to coordinate the level of competency of each student, generating a greater degree of learning. The software packages chosen for the VNL were typical of real-world IT labs.

The VNL as reported by Leitner and Cane [14] was deployed on an existing server and was designed so that each course instructor could set up the components reflective of the course and experimental outcomes. This allowed for elements to be either open (those elements that the student could modify) or closed (those elements that the student had no control over). Once these components were established by the instructor, the student was instructed to perform the assignment. The addition of the Blackboard course management system provided the instructor with the capability of maintaining course control. The designers also incorpo-

rated a management system named DameWare, which enables the instructor to log in to the VNL systems and monitor the students' behavior.

The VNL system has been implemented and is in the early stages of its deployment but has not been evaluated with respect to learning outcomes. Leitner and Cane [14] are still working on more appropriate means of integrating the VNL into the IT curriculum. They are also contemplating utilizing this system in the classroom in addition to online learning.

#### **Usability Research**

Actual research into VREs has been somewhat sporadic, but the past few years have shown an increase which has stimulated the growth of these environments [6]. The usability of VREs is one area where research has had some impact, as demonstrated by the research performed by Schroeder, Heldal, and Tromp [15]. Their research article "The Usability of Collaborative Virtual Environments and Methods for the Analysis of Interaction" examined two methods of analyzing interaction within VREs. They suggest that problems do exist within these environments and these VREs are limited due to the available field of view, the interaction of objects, and the awkward tools for navigation and avatar gesturing.

Research in usability has been limited, as suggested by the Schroeder et al. [15] and is due to the immaturity and lack of VREs available for research. Thus, usability is one of the main issues directed at VREs and why many are reluctant to use them. To this end, the authors of "The Usability of Collaborative Virtual Environments and Methods for the Analysis of Interaction" took a comprehensive look at usability issues. The nature of this digital medium allowed for the capture of the interactions of the users, which provided for more reliable results. The major obstacles that were addressed in the research were (a) how to generalize the results to other VRE settings, (b) discovering patterns of the interaction that are common and unique, and (c) developing the proper method for analyzing and capturing the interaction [15]. The underlying goal of the research was to improve the usability of VREs. This was accomplished by focusing on the techniques for analyzing interaction within these environments.

#### **Evaluating Sequence of Behavior**

Categories of behavior. The research employed two methods for analyzing the interaction of participants within VREs. The first method was quantitative in nature, evaluating sequences of behavior within a group environment. The VREs were presented via the desktop technology. The first step in this approach was to establish a set of categories for

scoring the observed behaviors. Initially, twenty six categories were established that were reviewed by a panel of experts.

The review refined the categories to eight distinct variables to be analyzed. These eight categories were: (a) external events outside the VRE, (b) communication, (c) avatar gestures, (d) manipulation of the avatar, (e) navigation of the avatar, (f) positioning of the avatar, (g) viewing the environment, and (h) verify to activity. Within these categories there were between two and fifteen subcategories to better quantify the activities [15]. These categories were designed to focus the research on the behavior within a VRE during the acts of collaboration.

Analysis of interaction. This method analyzed a series of video recordings of participants interacting as they performed various tasks. The researchers then scored the interactions observed, based on the eight categories identified. This method permitted the researcher to follow a series of interactions in a very detailed manner. This, then, provided the opportunity to breakdown the types of actions that are performed during the interaction. An example of the data that this method generated was presented by the authors. The example detailed four trials involving three to nine participants and lasting a total of thirty two minutes. These observations generated 705 individual acts to be analyzed and categorized.

Conclusion on usability. Through this process a number of conclusions about how individuals interact within a VRE where developed. It was discovered that almost half (48.1%) of all acts were in the form of communication, with general communication accounting for 20.4 % and the balance, verifying the functionality of the VRE with fellow users. It was also determined that newer users communicate more often than experts and that experts scanned or viewed the environment more often. It was also observed that as a user navigates within the environment, there is less likelihood that he/she will communicate, as the focus is on navigation and not communication. The research was able to establish the time requirements for various acts performed within the VRE.

The actions that require the most time were communication, when they were done via text input. Navigation typically took between 1 and 2 seconds, except when the avatar was moving backwards and most other acts on average took about 1 second. Reaction times in communication were another area that demonstrated some interesting results. General, unfocused communication usually required about 5 seconds for a response. When the communication was a part of collaboration, the response time was much faster, within a range of 1 to 2 seconds.

Recommendations on usability. The results of the observed interactions produced a number of recommendations as advocated by Schroeder et al. [15]. The first of these recommendations was to fully or partially automate a regularly occurring task. A second recommendation was to develop a better instrument for providing feedback to other users and, finally, there needed to be an easier way to navigate to a particular position.

Benefits of method. The main benefit of this method is to provide other researchers a means of uniformly analyzing interactions within a VRE. The advantages of the methodology are (a) sequences can be categorized and inspected in detail, (b) correlation between activities can be identified and aligned, (c) length of specific activities can be established, and (d) the frequency of various activities can be established. There are, however, three main disadvantages that researchers must take into account when using this method of analysis. The time required to perform this type of analysis is quite extensive and should be considered when designing the research. There is also the problem of generalizability and whether the results from one VRE can be generalized to another. Finally, the qualitative elements of the users' experience are lost by reducing the data to its basic quantitative form. This loss of richness of the qualitative data can be problematic when the data is being reviewed by persons other than the ones that scored the activities.

Definition of collaboration. The second method explored in the research [15] expanded the model developed by Heldal in 2004, which attempted to identify those elements that support or disrupt the acts of collaboration by users. The elements that disrupt collaboration were identified as the lack of awareness of what others are doing, inadequate feedback from others on one's own actions, and the difficulty in seeing what others are actually seeing. The research was performed in an immersive projection environment (CAVE) and involved two sets of trials. The trials were distinct in that one paired strangers and the other paired friends to determine whether the disparate pairs would act differently in given collaborative situations.

Results of qualitative approach. The second method employed a qualitative approach to reviewing the actions of the paired participants. The research used video and audio recordings, questionnaires, interviews and real-time observation, which was quite similar to the first method. The results provided some insights into the collaborative nature of the paired participants along with observations related to those elements that disrupt collaboration. Perceptual issues were discovered when users were attempting to navigate within an environment where the horizon was indistinguishable. The user had difficulty recognizing various locations due to the bland horizon and often got lost. Interaction among the par-

ticipants was also quite revealing in that when collaborating the users respected each other's virtual space, but while navigating there tended to be a disregard for one another's space and at times participants would actually walk through the other's avatar.

The appearance of the avatars was only a concern when the participants were not actively involved in a specific task. The discussion about one another's appearance typically occurred early in a session or after a task had been completed. During the collaborative process, the focus was on the task with little concern about each other's avatar appearance. The treatment of the avatar was sometimes perceived as real, versus times when the avatar was ignored or was similar to the way objects were perceived. Depending on the objective of the task, participants would sometimes walk through an object as if it did not exist, while other times the object presented an obstacle to be dealt with.

The two methods were quite similar in their approach to analyzing the interactions of participants. The first method observed the actions of individuals as they navigated a VRE, while the second method focused on pairs of participants and how the pairs collaborated within a VRE. The research focused more on the methods employed, striving to established validity in this type of research. The research did generate a few recommendations for better usability within a virtual environment. The researchers provide additional suggestions for researchers as they investigate usability within a VRE. Schroeder et al. [15] suggest that one (a) think about what to study from the beginning, (b) plan the iterations of design, test, redesign and test considering the methods outlined in this current study, (c) focus on the specific aspects of behavior that are of interest, (d) use appropriate combinations of methods, and (e) evaluate the results to achieve logical suggestions for redesign [15].

#### **Authoring Tools**

The lack of virtual environments can be attributed to a combination of cost and the ability to program the interactivity into the environments. The cost for development of these environments has declined as the technology has increased, thus reducing one of the obstacles in creating VREs. The technical skills required to create a VRE are still one of the pervasive reasons why more VREs are not being developed [6]. The research conducted by Hendricks et al. [6] considers the conceptual creation of an authoring tool that will provide the novice with the ability to create and implement a VRE, which includes extensive interactivity. The proposed tool would expand on the Virtual Reality Meta Language (VRML), which is considered the 3D version of HTML. The authoring tool would provide "both novice and advanced users a single system on which to develop, with the opportu-

nity for novice users to smoothly migrate to creating more complex applications" [6]. The research defines the framework for such an authoring tool.

Implementing VREs. The behavior and interaction of VREs can be implemented in one of two general ways. The first is behavior-based where the interactions of the objects are considered attributes of the objects. For example, an avatar runs according to the way the object is programmed and is programmed to know what to do in response to other objects. The second way is event-based where the interactions occur in the environment. These events are produced by the users' activity or are produced by a change in the state of the objects. Currently, the main development tools use one or a combination of both of these methods but do not provide the user support required for the novice to work with them effectively.

Prototype authoring tool. The ideal authoring tool, as prescribed by Hendricks et al. [6], would be useful not only for the advanced programmer but the novice as well. The system would (a) allow for a smooth transition of user support so that users with various levels of skills are able to work with the system, (b) the system should be able to produce, regardless of the expertise of the user, as complex a VRE as required, (c) the system should be able to produce a viable VRE in a short period of time, similar to the time is takes to produce a GUI application, and (d) the system should allow for deployment on any hardware or software platform including new technologies [6].

Their system would have three main features or modules interacting with one another in varying ways. The first module would be a Graphics module consisting of a world component and an objects component that are stored in the database. The world component controls the rendering of the objects in the database. The second module would comprise a Scripting interface for implementation of the scripting language of choice rather than relying on one specific scripting language. The final Events module would be responsible for coordinating the interactions within the environment. It houses the structures for attribute variables, actions and conditions.

The proposed generic authoring tool allows both the novice and advanced user the ability to create interactivity by specifying pre-defined event-action pairs provided by the system. The support system will allow the novice user to migrate to more complex actions as his/her expertise increases. The development time will be greatly reduced as the use of scripting languages will reduce the time spent on compiling and employing API code. Since the system is modular, various implementations of a module can be used. The scripting module, for example, could simultaneously run

both a portion of Python and JavaScript. The authors conclude that VRE authoring tools have increased in number and usability, but few have targeted the novice developer. The implementation of their meta-authoring system would assist in overcoming this problem and rapidly generate more VREs with richer content.

#### Implications for the Future

The development and implementation has been an ongoing process in the area of virtual reality environments. The term "Virtual Reality Environments" has evolved to represent a computer-generated 3D collaborative environment, where the user can interact and manipulate the environment. These environments are limited only by one's imagination where physics and the natural world can be modified. The potential for VREs is unlimited, providing distinct advantages over existing communication and interactive technologies. These 3D virtual environments, as suggested by Pekkola [16], have these distinct advantages: (a) a mutual understanding and sense of space, (b) a mutual perception of the presence of others through their avatars, (c) a commonality of the sense of time, (d) the ability to negotiate and communicate with others, and (e) a means of sharing models and objects in virtual space and collectively achieve understanding of activities [16].

The recent exponential growth of virtual worlds (VWs) such as Second Life demonstrates the realization by individuals, the private sector, academia and government sectors of the power of VREs. Individuals have embraced the entertainment and collaborative nature of these environments to the point where some are now making a living in these VWs. The private sector is expanding its operations into these worlds as well, establishing store fronts, meeting areas, research endeavors and marketing campaigns to take advantage of these new opportunities. Academia has also moved into these new environments to take advantage of the inexpensive virtual space available and the ability to communicate, educate and research within these environments.

As these VWs evolve, new issues arise that must be addressed. The ability of users to create and own objects has spawned the existence of virtual businesses. This rise in business activities has prompted governments to take a look at avenues for taxing these types of activities. Along with business activities, the very nature of owning property has created new questions that must be addressed legally. There are increasing concerns about such concepts as the legal definitions of intellectual property as created within these VWs [17]. The owners of these VWs also have to consider how they word their "terms of service" as a recent court case ruled against Second Life and its restrictive "terms of service" (ToS). In that case, a federal district court found that

the Second Life's ToS was illegal in its strict ownership and participation requirements and awarded a substantial settlement to the plaintiff [18]. Virtual governments are now being created by the citizens of the VWs to establish laws by which the residence must abide.

Research in VREs has increased as the cost of creating, and expertise to develop, them has decreased. This research is delving into many arenas within the VREs, especially into the navigation, field of view, gesturing and mechanics of motion. There has been extensive research into the software applications that create these environments with an emphasis on ease of development. There has been widespread research into the hardware used in simulating, navigating and observing these environments.

#### Conclusion

There has been an ever-increasing amount of research into the VREs and the various ways that they can be used and exploited. The research efforts have mainly focused on the architecture, navigation and delivery of the VRE technology with minimal research into the social and legal aspects of these environments. Many institutions have become actively engaged in these VREs and many are exploring alternative uses for them. The potential of VREs has been recognized as a new source of research opportunities, which has prompted continued development in this area. There are justifiable arguments both for and against to the viability of these technologies, though it is imperative that research into the merits as a social, business, entertainment and educational tool be continued.

The continued growth in the software and hardware will also have a dramatic impact on the growth and acceptability of VREs in the future. As suggested by Bray and Konsynski [10], there are several interesting questions for researchers that include business theory, political systems and social interaction that provide a wealth of research opportunities. These new environments have demonstrated their current effectiveness, showing great promise, and should be explored with great vigor.

#### References

- [1] Stackpole, B. (2008, January). Virtual reality gets real [Electronic version]. *Design News*, 63(1), 85-88.

- [2] Rehn, G. D., Lemessi, M., Vance, J. M., & Dorozhkin, D. V. (2004, May). Integrating operations simulation results with an immersive virtual reality environment [Electronic version]. *Proceedings of the 36th Conference on Winter Simulation* (Washington, D.C.). 1713-1719.

- [3] Yan, L., Ji-zhou, S., & Ke, T. (2004, June). The design of desktop virtual reality environment based on VRML: Digital TJU navigation system [Electronic version]. Proceedings of the 2004 ACM SIGGRAPH international Conference on Virtual Reality Continuum and Its Applications in industry (Singapore). VRCAI '04. ACM, New York, NY, 480-483.

- [4] Huang, C., Hsu, H., Shih, T. K., & Chang, R. (2006,December). A VR-based hyper interaction platform [Electronic version]. *Proceedings of the 38th Conference on Winter Simulation* (Monterey, California, USA). 576-582.

- [5] Bricken, M. (1991, July). Virtual reality learning environments: Potentials and challenges [Electronic version]. SIGGRAPH Computer Graphics. 25, 3, 178-184.

- [6] Hendricks, Z., Marsden, G., & Blake, E. (2003, February). A meta-authoring tool for specifying interactions in virtual reality environments [Electronic version]. Proceedings of the 2nd international Conference on Computer Graphics, Virtual Reality, Visualisation and interaction in Africa (Cape Town, South Africa). AFRIGRAPH '03. ACM, New York, NY, 171-180.

- [7] Kenter, P., (2008, April). Training to make it real: What's on Second (Life)? [Electronic version]. *OH & S Canada*, 24(3), 17-18.

- [8] DeLarge, C., (2008, June). Second coming? [Electronic version]. *Medical Marketing and Media, 43*(6), 47-50, 4.

- [9] Galagan, P., (2008, February). Second that [Electronic version]. *Technology + Design*, 62(2), 34-37,4.

- [10] Bray, D. A. & Konsynski, B. R. (2007, October). Virtual worlds: Multi-disciplinary research opportunities [Electronic version]. *SIGMIS Database* 38, 4, 17-25.

- [11] Young, J. R., (2000, October). Virtual reality on a desktop hailed as new tool in distance education [Electronic version]. *The Chronicle of Higher Educa*tion, October 6, 2000, A43. Retrieved August 18, 2008 from: http://chronicle.com/free/v47/i06/06a04301.htm

- [12] Budhu, M., (2002, August). Virtual laboratories for engineering education [Electronic version]. *International Conference on Engineering Education*, Manchester, U.K.

- [13] Couture, M. (2004). Original article realism in the design process and credibility of a simulation-based virtual laboratory [Electronic version]. *Journal of Computer Assisted Learning*, 20(1), 40-49.

- [14] Leitner, L. J. & Cane, J. W. (2005, October). A virtual laboratory environment for online IT education [Electronic version]. Proceedings of the 6th Conference on

- information Technology Education. SIGITE '05. ACM, 283-289.

- [15] Schroeder, R., Heldal, I., & Tromp, J. (2006, December). The usability of collaborative virtual environments and methods for the analysis of interaction [Electronic version]. *Presence: Teleoperators & Virtual Environments*, 15(6), 655-667.

- [16] Pekkola, S. (2002, October). Critical approach to 3D virtual realities for group work [Electronic version]. Proceedings of the Second Nordic Conference on Human-Computer interaction (Aarhus, Denmark). NordiCHI '02, vol. 31. ACM, New York, NY, 129-138.

- [17] Davidson, S. J., (2008). An immersive perspective on the Second Life virtual world [Electronic version]. *Computer and Internet Lawyer*, 25(3), 1-16.

- [18] Christ, R. E., & Peele, C. A., (2008). Virtual worlds: Personal jurisdiction and click-wrap licenses [Electronic version]. *Intellectual Property & Technology Law Journal*, 20(1), 1-0\_1.

#### **Biographies**

KIMBERLY JAMES NANKIVELL received his B.S. degree in Marketing from the University of Arizona, Tucson, Arizona, in 1974, a Masters degree in Information Technology from American Intercontinental University, Hoffman Estates, Illinois, in 2003 and a Ph.D. degree in Information Technology from Capella University, Minneapolis, Minnesota, in 2011. Currently he is an assistant Professor of Computer Graphics Technology. He can be reached at nankivel@purduecal.edu.

# DESIGN AND DEVELOPMENT OF A DURABILITY TESTING MACHINE

Bhargav Shah, Arizona State University; Sangram Redkar, Arizona State University

#### **Abstract**

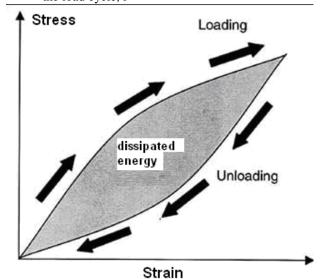

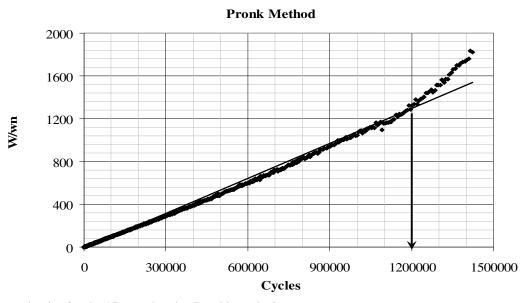

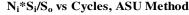

This work presents the process of design and development of a durability testing machine, development of a statistical testing methodology and subsequent reliability testing results of surge brake assemblies used in commercial trailers. The surge brake assembly is a critical component of the trailer braking system that is actuated by the relative deceleration of the towing vehicle and trailer. The durability-testing machine used to test surge brake assemblies was designed and developed using state-of-the-art analysis and design software-Autodesk Inventor for CAD, MSC-ADAMS for dynamic analysis and MSC-NASTRAN for Finite Element Analysis (FEA). This durability testing machine can be used for accelerated life testing where, due to high speeds of operation, dynamic effects play a significant role. This machine was designed in such a way that it can withstand the alternating inertial loadings and continue to perform optimally and consistently over a useful operating life. This paper presents the mechanical and electrical design methodology, development and commissioning of this machine. It also outlines the statistical testing procedure for surge brake assembly and reliability testing results. The durability testing results for the surge brake assemblies can be used for reliability analysis, vendor comparison and component selection. It can also be used to identify the probable causes of failure of surge brake assemblies in the field.

#### Introduction

Durability is an ability to sustain and endure. Product or component durability means that the products or components should perform their intended function for the designed lifespan without failure. Durability is a critical parameter in the design process. It is also important to validate the product durability and specifications provided by the Original Equipment Manufacturer (OEM) through standardized testing procedures before the component is put into use. Depending upon the application, intended use, environment and expected reliability, there are various standards for durability testing such as DO 160E, MIL 810E and SAE J1153 [1], to mention a few.

The objectives and original contributions of this work are:

1. Design and develop a durability testing machine to test surge brake assemblies used in trailers. Using a practical design methodology, the specifications for surge brake test-

ing were derived. The design parameters and constraints were finalized using preliminary testing. Various design alternatives were evaluated and the most appropriate design was finalized. This design was used to size various subcomponents using machine design principles [2], [3]. It should be noted that a twofold design approach was used: a) a strength-based design where the component is strong enough to withstand the load, and b) a deformation-based design where the component does not undergo deformation (either in static or dynamic conditions) that would affect the operation or performance of the machine. Finally, the durability testing machine was built and commissioned. Thus, the theoretical design was put into practice, refined and tested.

2. Establish a data analysis and test procedure for vendor comparison. The authors proposed a Weibull analysis for reliability studies and comparison. This provided a systematic practical approach to quantify and compare surge brake reliability.

The results of the durability testing can be used to conduct Failure Mode Effect Analysis (FMEA), reliability analysis, design validation, life-cycle analysis, and to study effects of varying operating conditions on the component performance [4]. The durability machine designed and developed in this work is versatile and can be used to test a variety of products/components such as trailer surge brakes, trailer suspension systems, hitch-ball and hitch-receiver assemblies.

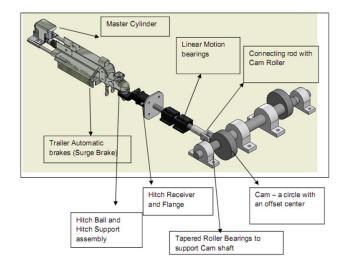

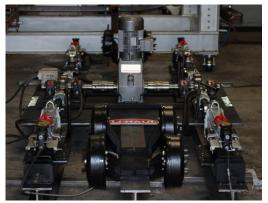

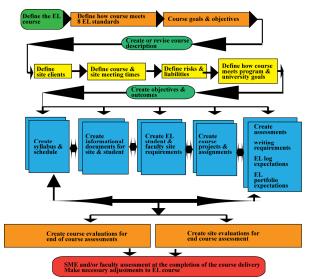

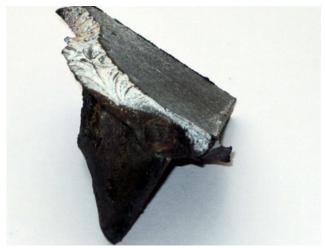

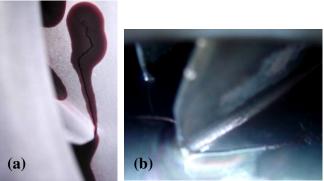

Figure 1. The surge brake

The surge brake (as shown in Figure 1) is a critical component of the trailer braking system that is actuated by the relative deceleration of the towing vehicle and trailer. The Society of Automotive Engineers (SAE) sets standards for all components in automobiles. SAE J1153 is the standard used for master cylinders in the braking system [1]. All of the surge brake OEMs are required to adhere to this stan-

dard. The SAE J1153 has parameters set for durability testing of master cylinders in the trailer braking system. These standards are set for cold-temperature and high-temperature durability.

A durability testing machine was designed to test the surge brakes. This machine has the following anticipated benefits/uses

- 1. The durability testing will help analyze the quality of production parts. Products supplied by different suppliers can be easily accessed and compared with this test.

- 2. The machine can complete 500,000 cycles within 10 days. Data collected from this test will help in making future design changes to the products.

- 3. The machine uses a simple mechanical cam and cam follower mechanism for actuation. It is very flexible and can be used for durability testing of other products such as suspension springs, hitch-ball and hitch-receiver assemblies.

- 4. This durability test simulates forces experienced in real time and, hence, the data obtained will be very useful to simulate field failures.

Various types of computer software were used in this project. Autodesk Inventor was used to create 3D models. Microsoft Excel and Minitab were used to tabulate and analyze the data. The MSC ADAMS software was used to create a simulation model of the automatic surge brake system. In order to minimize the cost of the machine, commercial standard parts and in-stock components were used. The machinery handbook [2] was used as a standard guide for all of the part selections. Few specialized parts such as the cam shaft and cam were machined locally.

This paper presents the design of the machine, implementation and testing results, and is organized as follows: Section 2 presents the detailed design and development of the durability testing machine. Section 3 discusses the reliability analysis and vendor comparison case study. Finally, section 4 presents the conclusion.

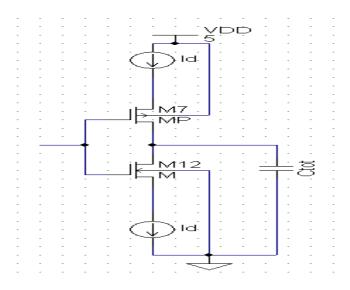

# Design of a Durability Testing Machine

The design and development of the durability testing machine involved various stages like developing preliminary specifications of the machine, conceptual design, mechanism design, dynamic analysis, machine component design, assembly, construction and testing. A conceptual mechanism initially proposed to actuate a surge brake is shown in Figure 2. This mechanism is a simple cam and roller follower. The surge is actuated with the forces generated by the follower. The cam is powered with an electric motor. The camfollower returns back to its initial position with the help of

return springs in the surge actuator. The efficient cycling of the surge brake depends greatly on the performance of the return springs. If the return spring does not return to its initial position, the cam follower will not be in positive contact with the cam and will damage the cam and cam follower over a period of time. The surge brake is linked to a hydraulic drum brake and the brake lines are filled completely with the brake fluid. The pressure maintained within the system should be within the OEM design specifications.

The surge action does not follow a straight line. The path followed by the surge action is an arc. As a result of this curved path, the mechanism needs to be designed such that path variations are allowed, thus a hinge is incorporated between the hitch receiver assembly and the cam follower. This hinge sustains significant vertical loads and protects the linear motion bearing from overload and wear. In order to actuate and test multiple surge brakes simultaneously and maintain dynamic stability, a symmetric actuation mechanism is desirable.

Figure 2. Conceptual design

#### **Dynamic Analysis**

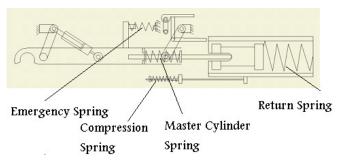

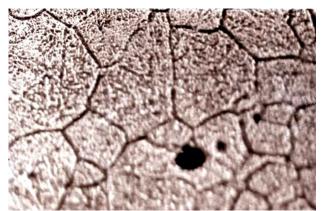

In order to get the loads and toque requirements, a dynamic analysis was carried out. For dynamic analysis, a simple free-body diagram of the surge brake was drawn as shown in Figure 3. The simulation model was created in MSC-ADAMS based on this free-body diagram. All of the components except emergency springs were included in the simulation model.

Figure 3. Free-body diagram

The surge brake actuates when there is an inward force. The surge returns back to its initial position with the help of return springs. The surge brake also has safety features to stop the trailer in case of disconnection from the towing vehicle. These emergency brakes are a set of compressed springs which are released when the emergency brakes are pulled. These compressed springs provide the energy to actuate the master cylinder and generate brake pressure. It should be noted that these springs are activated only in case of emergency and, hence, not included in the MSC ADAMS model.

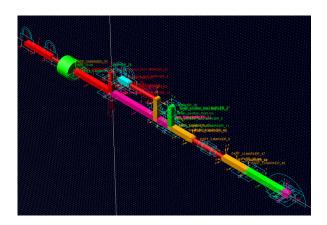

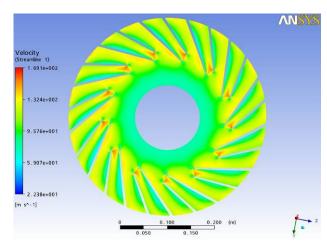

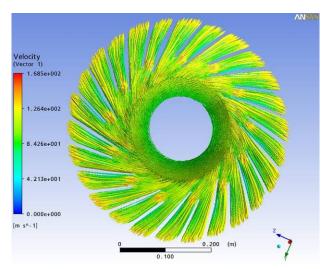

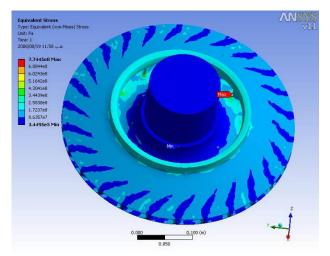

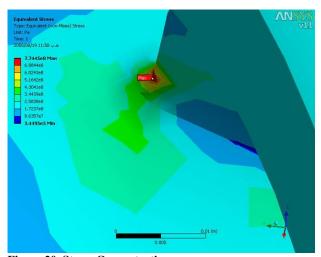

The MSC ADAMS simulation model is shown in Figure 4. The purpose of this simulation was to get a better understanding of the dynamics of the surge brake action and compute forces and power required. These forces can be used for finite element analysis of the machine components.

Figure 4. MSC ADAMS simulation model

The simulation model was comprised of the following springs:

- Compression spring

- Return spring

- Master cylinder spring

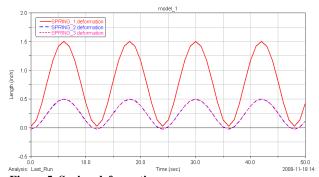

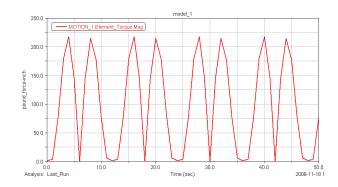

The sample simulation results are shown in Figures 5 and 6. The time step for simulation was 0.01 seconds. However, the results are plotted for 10-second intervals. Figure 5 shows the spring deformations corresponding to the compression spring (Spring 1), return spring (Spring 2) and the master cylinder spring (Spring 3). It should also be noted that spring displacements corresponded well with the data provided by manufacturer.

Figure 5. Spring deformation

The torque required to drive the surge brake assembly is shown in Figure 6. Here, MSC ADAMS simulations were carried out to get torque requirements for different types of surge brake assemblies with different springs and inertial properties at different operating speeds. This analysis helped to determine the maximum power required to operate the machine and motor selection.

Figure 6. Torque requirements

A torque analysis was carried out for 1 surge brake assembly. In the initial design, the machine was anticipated to operate a minimum of 4 surge brakes at a time; hence, the total torque requirement would be 4 times (about 1000 lb.in).

#### Components of the Machine

Based on the requirement, cost and benefit analyses, the following components were selected for the machine.

#### NORD DRIVE SYSTEM:

A 5-horse-power Nord motor was selected to power this machine. The motor was coupled with a gear box with a double-sided solid-shaft output. The maximum output torque generated for this power plant was 9000in-lb at 35 rpm. Even though the maximum torque required was 1000lb-in, this drive system was selected as it was available in-stock and using this existing drive system would have lowered the cost of machine significantly. It was also envisioned that in case the durability machine were expanded to test more surge brakes at the same time, this power plant would be able to support the additional capacity.

#### YASKAWA VARIABLE FREQUENCY DRIVE:

A variable-frequency drive was used to control the speed of the motor. The variable-frequency drive controls the frequency of the alternating current. This, in turn, controls the output speed of the motor.

#### LINEAR MOTION BEARINGS:

Linear motion bearings were used to constrain the motion of the connecting rod to only one translation axis. These linear motion bearings were fixed into a fully enclosed and sealed pillow block to support them. They have recirculating roller bearings to improve the life of the bearings.

#### JAW COUPLING:

A jaw coupling was used to couple the output shaft of the motor with the camshaft assembly. This jaw coupling has two hubs with protruding jaws. These jaws overlap axially and interlock torsionally through a compliant insert of rubber or soft metal material. The clearances allow some axial, angular and parallel misalignment, but can also allow some undesirable backlash.

#### TAPERED ROLLER BEARINGS:

Tapered roller bearings are used to support the drive shaft. These bearings experience an alternating force of 1500lbs. The input force on the surge brakes is equivalent to the forces on these bearings. Tapered rollers bearings were chosen as they are capable of taking higher axial loads. These bearings have a longer life and are generally used in very high load applications. In this machine, each shaft was sup-

ported by two tapered roller bearings on either side of the cam.

#### LOAD RUNNER PLAIN YOKE STYLE:

A load runner rolls smoothly over the circumference of the CAM with minimum friction. The load runner can accept very high forces. The load runner was sandwiched between two metal pieces. It was held in position with a long shank bolt. The load runner has tapered roller bearings that can withstand radial forces.

The following components were specially designed for the machine.

- 1. Driveshaft and CAM assembly

- 2. Cam follower assembly

- 3. Cycle testing supporting structure

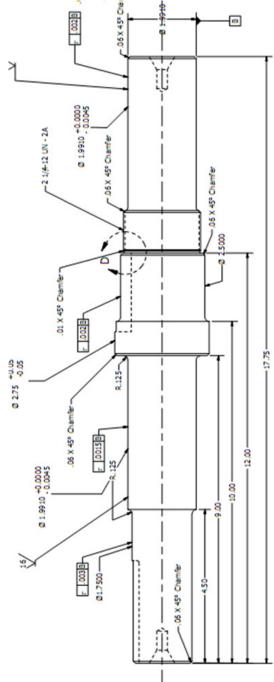

The driveshaft of the durability testing machine was one of the crucial components. It was subjected to high torques and bending forces. The output torque of the motor was 9000in-lb and shear force of 1500lbs. The shaft was attached to the cam. This cam generated the displacement to cycle-test the surge brakes. The cam was made of steel and had a diameter of 7.5 inches. The shaft was coupled to a 5hp motor. The shaft was coupled at one end with the output shaft of the motors gearbox. The shaft was held in position with the help of two heavy duty roller bearings with pillow blocks. The cam was placed between two pillow blocks. The heavy duty bearings gave good support to the shaft to reduce the deflection.

The design of the shaft was made based on the Machine Design Reference [3]; some of the crucial design factors were the diameter of the shaft, the dimensions and type of keyways used in the shaft. The calculations were based on the following procedures [3].

- Shaft design for steady torsion and fully reversed bending

- Shaft design for repeated torsion and repeated bending

- 3. Designing a stepped shaft to minimize deflection

The material selected for shaft design was steel 4340. It is a high-quality steel used generally for aerospace applications. The hardness level of the shaft was 40-45 Rockwell hardness on the 'C' scale. The driveshaft was designed to have very tight tolerances. The shaft drawing is shown in Figure 7.

Figure 7. Driveshaft drawing

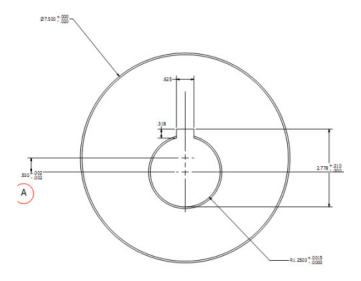

The cam designed was circular with an offset center. The final displacement achieved by the cam was equal to twice the offset. The cam was made using SAE HR 8617 Steel. The cam drawing is shown in Figure 8.

Figure 8: Cam drawing

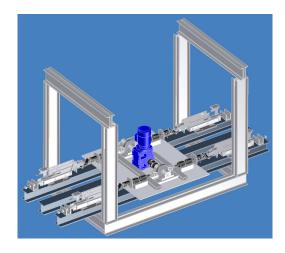

The final assembly of the durability testing machine is shown in Figures 9 and 10.

Figure 9. Durability testing machine model

Figure 10. Durability testing machine assembly

#### Reliability Analysis

The purpose of the machine was to test the performance and durability of surge brakes. These surge brakes were supplied by several suppliers. In this section, a method for vendor comparison and selection is proposed. For durability or fatigue testing, one way to analyze the data is by plotting reliability curves [5]. Reliability can be calculated by plotting Weibull graphs [4, 6]. The Weibull distribution has been used extensively in reliability engineering as a model of time to failure for electrical and mechanical components and systems [6]. The Weibull method is also used for electronic devices such as memory elements and mechanical components such as bearings, structural elements in aircrafts and automobiles. Today most statistical packages offer simple ways to create the Weibull distribution and plot reliability graphs [7]. The two software packages used in this study are Minitab and Microsoft Excel.

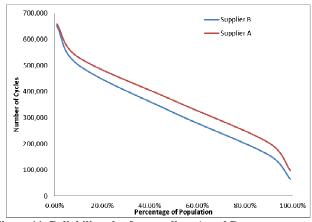

The method for plotting a reliability curve in Excel is explained with a case study. Consider two suppliers for the surge brake assemblies. The company has to choose the supplier based on the quality of the surge brakes. Each supplier supplies ten complete surge brake assemblies. Ten surge brakes are cyclically tested in the durability testing machine where insufficient brake pressure is developed in the master cylinder at full stroke due to a variety of reasons (SR: Sluggish Response, SF: Spring Failure, SL: Seal Leakage, AJ: Assembly Jammed, OT: Other) as given in Table 1. Table 1 presents the Surge Brake Number, Cycles To Fail (CTF) and Primary Failure Cause (PFC).

Table 1. Surge brake test data

| Surge<br>Brake<br>Number | Supplier A CTF | Sup-<br>plier A<br>PFC | Suppli-<br>er B<br>CTF | Sup-<br>plier B<br>PFC |

|--------------------------|----------------|------------------------|------------------------|------------------------|

| 1                        | 400,000        | AJ                     | 280,000                | SL                     |

| 2                        | 415,000        | SF                     | 320,000                | AJ                     |

| 3                        | 500,000        | AJ                     | 375,000                | SR                     |

| 4                        | 385,000        | SF                     | 390,000                | OT                     |

| 5                        | 427,000        | SL                     | 410,000                | SF                     |

| 6                        | 398,000        | OT                     | 435,000                | SR                     |

| 7                        | 287,000        | SL                     | 485,000                | SF                     |

| 8                        | 157,000        | SL                     | 490,000                | AJ                     |

| 9                        | 293,000        | OT                     | 330,000                | SR                     |

| 10                       | 370,000        | SR                     | 161,000                | SL                     |

It can be seen that, based on the data collected, it is difficult to predict the reliability directly. The data can be interpreted in a better way using the reliability graph. The Weibull analysis can be carried out using the procedure described by Dorner [8]. The Weibull reliability function [6] is given in equation (1).

$$R(t) = e^{-\left(\frac{t}{\alpha}\right)\beta} \tag{1}$$

Beta  $(\beta)$  is referred to as the shape parameter. If  $\beta$  is less than one, the failure rate is decreasing over time. If  $\beta$  is greater than one, the failure rate is increasing over time. If  $\beta$  is equal to one, the failure rate is constant over time. Alpha  $(\alpha)$  is called the characteristic life. This is the value at which, when  $t = \alpha$ , 63.2% of all Weibull failures occur regardless of the shape parameter.

The method of least squares was used to fit a straight line to a set of points in order to determine the estimates of the parameters of the two-parameter Weibull distribution [9]. A measure of how well a linear model fits the data was found using the correlation coefficient, denoted by  $\rho$ . It is a measure of the correlation between the median ranks and the data. Median ranks are values used to estimate the cumulative distribution function (CDF) for each failure (e.g., Bernards approximation MR = (j-0.3)/(N+0.4) where j is the rank failure position and N is the total number of failures observed).

The correlation coefficient,  $\sigma$ , was calculated using equation (2)

$$\rho = \frac{\sigma_{xy}}{\sigma_x \sigma_y} \tag{2}$$

where.

$\sigma_{xy}$  is the covariance of x and y

$\sigma_{x}$  is the standard deviation of x

$\sigma_{v}$  is the standard deviation of y

The range of  $\rho$  is  $-1 \le \rho \le +1$ . Values of  $\rho \ge 0.75$  are desirable. However, values of  $\rho \ge 0.90$  are more desirable. A value of +1 is a perfect fit with a positive slope, while -1 is a perfect fit with a negative slope. When the value is closer to  $\pm 1$ , the paired values  $(x_i, y_i)$  lie on a straight line.

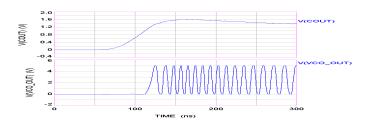

The reliability curves for suppliers A and B are computed via a Weibull analysis and are shown in Figure 11.  $\rho$  values for suppliers A and B are 0.86 and 0.82, respectively. For a detailed computation, one can refer to Shah [10]. Figure 11 shows the reliability comparison of suppliers A and B, where the number of cycles to failure are plotted against the percentage of population. The reliability curves for both the suppliers are parallel to each other. They have similar lower and upper reliability values but, in the intermediate section, supplier A has a higher reliability. Thus, it can be seen that supplier A is more reliable than supplier B.

Figure 11. Reliability plot for suppliers A and B

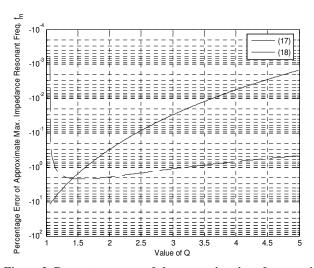

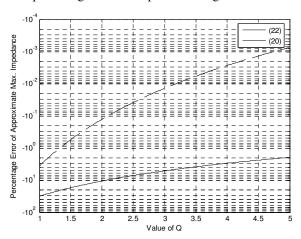

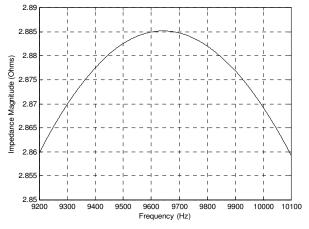

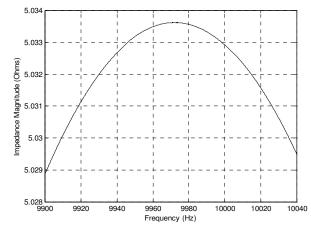

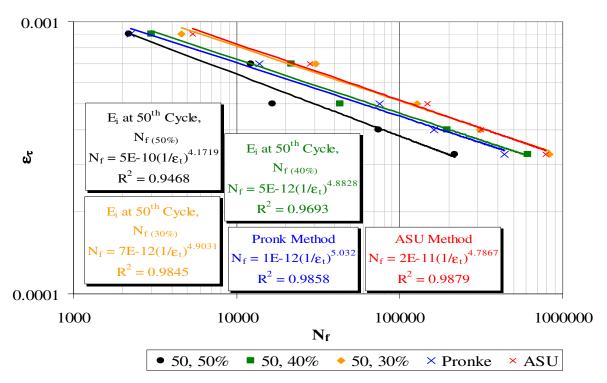

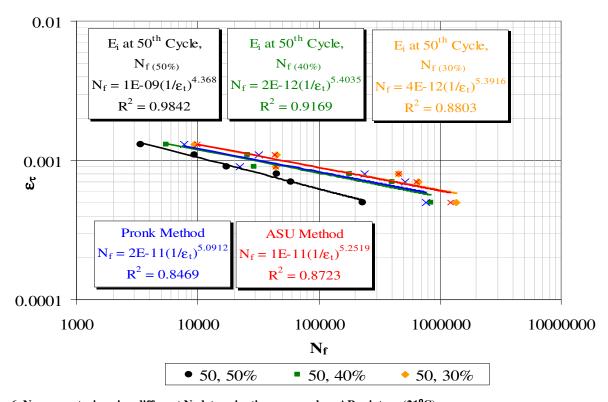

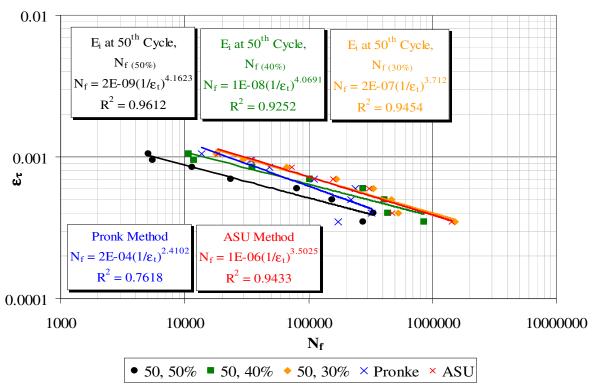

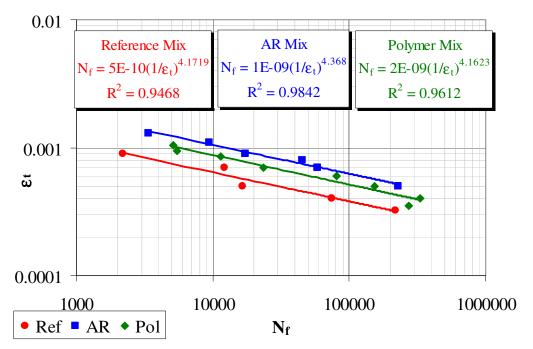

#### Conclusion