# M68HC05EVM

# Evaluation Module User's Manual

HARDWARE PREPARATION AND INSTALLATION INSTRUCTIONS

2

**OPERATING INSTRUCTIONS**

3

**FUNCTIONAL DESCRIPTION**

4

SUPPORT INFORMATION

5

S-RECORD INFORMATION

A

May 1992

ADDENDUM

TO

M68HC05EVM

**EVALUATION MODULE**

USER'S MANUAL

M68HC05EVM/AD4

This addendum corrects text (via change pages) contained in the M68HC05EVM/AD4 user's manual. Attached to this addendum are two change pages (2-5 and 2-6). These pages are to be inserted into your manual. Make certain that the pages you are replacing are removed from your manual.

Information contained in this document applies to REVision (D) M68HC05EVM evaluation modules.

After the change pages are inserted into the user's manual, this page of the addendum should be placed after the user's manual title page and saved as a record of the changes made to the manual. Pages affected by this addendum are:

2-5

2.6

# M68HC05EVM EVALUATION MODULE USER'S MANUAL

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any ticense under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended.

Information contained in this document applies to REVision (D) M68HC05EVM evaluation modules, serial numbers 1000 through 9999.

EVMbug and EXORciser are trademarks of Motorola Inc.

IBM-PC is a registered trademark of International Business Machines Corp.

The computer program stored in the Read Only Memory of the device contains material copyrighted by Motorola Inc., first published 1987, and may be used only under a license such as the License For Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

Fourth Edition

Copyright 1990 by Motorola Inc.

Third Edition February 1989

# PREFACE

The user is responsible for installing the MC68HC05L6 MCU surface mount socket (U54) and I/O port connectors (J12 and J24). These components are not supplied with the EVM.

Unless otherwise specified, all address references are in hexadecimal throughout this manual.

An asterisk (\*) following the signal name denotes that the signal is true or valid when the signal is low.

# TABLE OF CONTENTS

|           |                                                    | PAGE |

|-----------|----------------------------------------------------|------|

| CHAPTER 1 | GENERAL INFORMATION                                |      |

| 1.1       | INTRODUCTION                                       | 1-1  |

| 1.2       | FEATURES                                           | 1-1  |

| 1.3       | SPECIFICATIONS                                     |      |

| 1.4       | GENERAL DESCRIPTION                                | 1-4  |

| 1.5       | EQUIPMENT REQUIRED                                 | 1-5  |

| CHAPTER 2 | HARDWARE PREPARATION AND INSTALLATION INSTRUCTIONS |      |

| 2.1       | INTRODUCTION                                       | 2-1  |

| 2.2       | UNPACKING INSTRUCTIONS                             | 2-1  |

| 2.3       | HARDWARE PREPARATION                               | 2-1  |

| 2.3.1     | Mode Select Headers (J22 and J24)                  | 2-5  |

| 2.3.2     | Normal/Test Select Header (J5)                     | 2-7  |

| 2.3.3     | MC68HC705C8/MC68HC805C4 Program                    |      |

|           | Select Header (J16)                                | 2-7  |

| 2.3.4     | Evaluation/Program Select Header (J21)             | 2-8  |

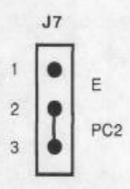

| 2.3.5     | PC2/E Select Header (J7)                           | 2-8  |

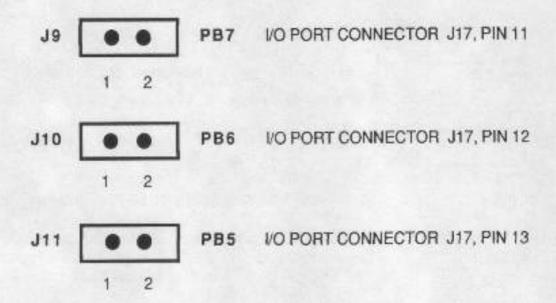

| 2.3.6     | PB Select Headers (J9 thru J11)                    | 2-9  |

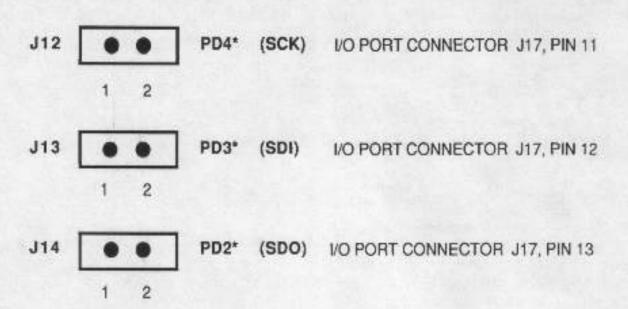

| 2.3.7     | PD Select Headers (J12 thru J14)                   | 2-10 |

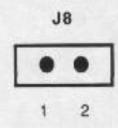

| 2.3.8     | TCAP Select Header (J8)                            | 2-11 |

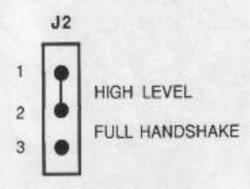

| 2.3.9     | Host Port CTS Select Header (J2)                   |      |

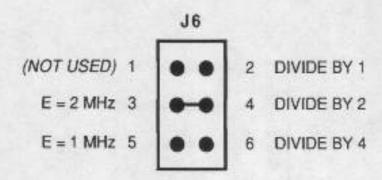

| 2.3.10    | Clock Frequency Select Header (J6)                 | 2-12 |

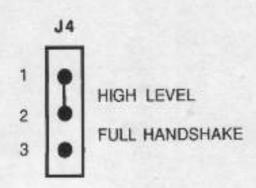

| 2.3.11    | Terminal Port RTS Select Header (J4)               | 2-13 |

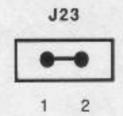

| 2.3.12    | DACIA Map Select Header (J23)                      | 2-13 |

| 2.3.13    | Clock Input Select Header (J27)                    | 2-14 |

| 2.3.14    | 8K/16K Man Select Header (J25)                     | 2-15 |

| 2.3.15    | Write Protect Disable Header (J3)                  | 2-15 |

| 2.4       | COMPONENT IMPLEMENTATION                           | 2-16 |

| 2.4.1     | Resident MC68HC05L6 Evaluation Circuitry           | 2-16 |

| 2.4.2     | Resident MCU Sockets                               | 2-16 |

| 2.4.3     | MCU Programming Sockets                            |      |

| 2.5       | INSTALLATION INSTRUCTIONS                          | 2-22 |

| 2.5.1     | Power Supply - EVM Interconnection                 |      |

| 2.5.2     | Terminal - EVM Interconnection                     |      |

| 2.5.3     | Host Computer - EVM Interconnection                | 2-24 |

| 2.5.4     | Target System - EVM 28-Pin Interconnection         | 2-26 |

| 2.5.5     | Target System - EVM 40-Pin Interconnection         | 2-29 |

| 2.5.6     | Target System - EVM 60-Pin Interconnection         |      |

| 2.5.7     | Target System - EVM 68-Pin Interconnection         |      |

# TABLE OF CONTENTS (cont'd)

| 10000        | 0.00 | 190 | 100 | - |

|--------------|------|-----|-----|---|

| 100          | U.S. | AC. | 200 |   |

|              | m    | 50  | 76  |   |

| and the same |      |     |     |   |

# CHAPTER 3 OPERATING INSTRUCTIONS

| 3.1    | INTRODUCTION                        | 3-1  |

|--------|-------------------------------------|------|

| 3.2    | CONTROL SWITCHES                    |      |

| 3.3    | LIMITATIONS                         |      |

| 3.4    | OPERATING PROCEDURE                 |      |

| 3.5    | COMMAND LINE FORMAT                 | 3-7  |

| 3.6    | MONITOR (EVMbug) COMMANDS           | 3-8  |

| 3.6.1  | Assembler/Disassembler (ASM)        |      |

| 3.6.2  | Block Fill (BF)                     |      |

| 3.6.3  | Breakpoint Set (BR)                 |      |

| 3.6.4  | Bulk Erase (BULK)                   |      |

| 3.6.5  | Check (CHCK)                        |      |

| 3.6.6  | Copy (COPY)                         |      |

| 367    | Go (G)                              |      |

| 3.6.8  | Help (HELP)                         |      |

| 3.6.9  | Load (LOAD)                         |      |

| 3.6.10 | Memory Display (MID)                |      |

| 3.6.11 | Memory Modify (MM)                  |      |

| 3.6.12 | Remove Breakpoint (NOBR)            |      |

| 3.6.13 | Proceed (P)                         |      |

| 3.6.14 | Program (PROG)                      | 3.54 |

| 3.6.15 |                                     |      |

| 3.6.16 | Register Display (RD)               | 3.20 |

| 3.6.17 |                                     |      |

| 3.6.18 | Speed (SPEED)                       |      |

| 3.6.19 | Trace (T)                           |      |

| 3.6.20 | Transparent Mode (TM)               |      |

|        | Verify (VERF)                       | 3-33 |

| 3.7    | MCU PROGRAMMING PROCEDURES          |      |

| 3.7.1  | Checking                            |      |

| 3.7.2  | Erasing                             |      |

| 3.7.3  | Programming                         |      |

| 3.7.4  | Copying                             |      |

| 3.7.5  | Verifying                           | 3-42 |

| 3.8    | ASSEMBLING/DISASSEMBLING PROCEDURES |      |

| 3.9    | DOWNLOADING PROCEDURES              |      |

| 3.9.1  | EXORciser to EVM                    |      |

| 3.9.2  | IBM-PC to EVM                       | 3-48 |

# TABLE OF CONTENTS (cont'd)

|            |                                      | PAGE |

|------------|--------------------------------------|------|

| CHAPTER 4  | FUNCTIONAL DESCRIPTION               |      |

| 4.1        | INTRODUCTION                         | 4-1  |

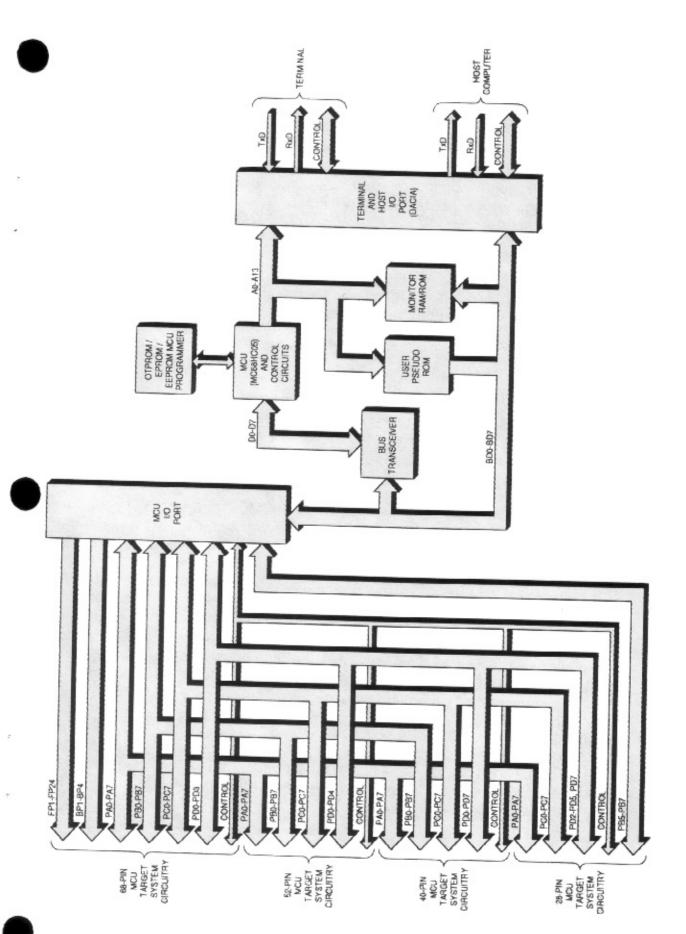

| 4.2        | EVM DESCRIPTION                      | 4-1  |

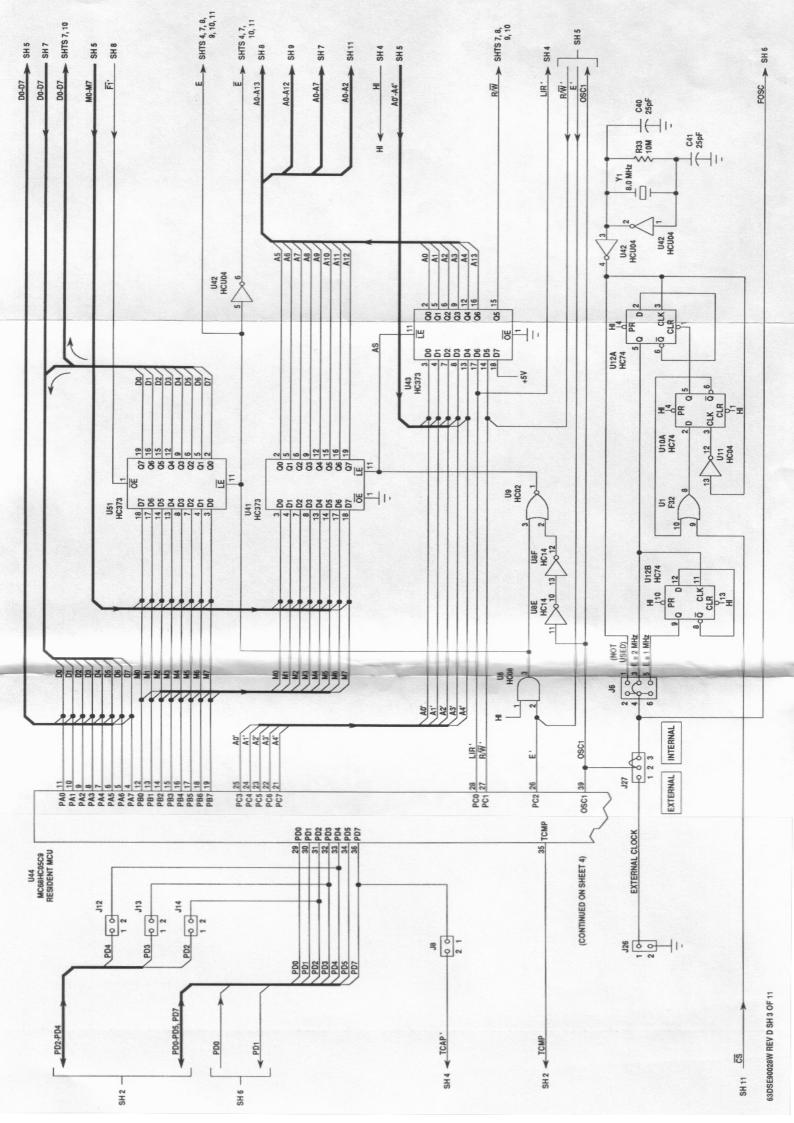

| 42.1       | MCLL and Control Circuits            | 4-1  |

| 4.2.1.1    | Map Switching                        | 4-2  |

| 4.2.1.2    | Ahort                                | 4-4  |

| 4.2.1.3    | Address Decoding                     | 4-4  |

| 4.2.2      | Monitor and User Memory              | 4-4  |

| 4221       | Monitor Map Area                     | 4-10 |

| 4.2.2.2    | User Mao Area                        | 4-10 |

| 423        | Terminal and Host Computer I/O Ports | 4-11 |

| 4231       | Terminal I/O Port Circuitry          | 4-11 |

| 4.2.3.2    | Host Computer I/O Port Circuitry     | 4-11 |

| 4.2.4      | MCU Extension I/O Ports              | 4-12 |

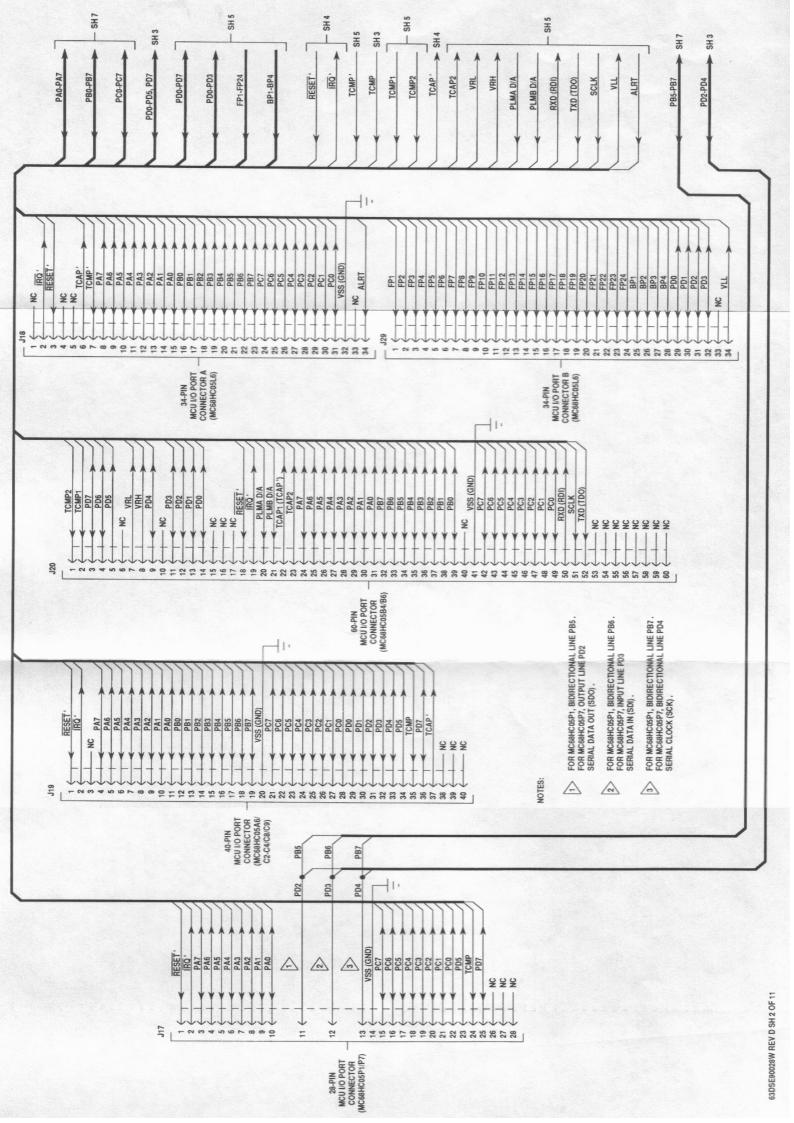

| 4.2.4.1    | 28-Pin I/O Port                      | 4-12 |

| 42.4.2     | 40-Pin I/O Port                      | 4-12 |

| 4.2.4.3    | 60-Pin V0 Port                       | 4-12 |

| 4.2.4.4    | 34-Pin I/O Ports                     | 4-12 |

| 4.2.5      | OTPROM/EPROM/EEPROM MCU Programmer   | 4-13 |

| 4.2.5.1    | MC68HC805C4 EEPROM MCU Programming   |      |

| 4.2.5.2    | MC68HC805B6 EEPROM MCU Programming   |      |

| 4.2.5.3    | MC68HC705C8 OTPROM/EPROM Programming | 4-14 |

| CHAPTER 5  | SUPPORT INFORMATION                  |      |

| 5.1        | INTRODUCTION                         | 5-1  |

| 5.2        | CONNECTOR SIGNAL DESCRIPTIONS        | 5-1  |

| 5.3        | PARTS LIST.                          | 5-11 |

| 5.4        | DIAGRAMS                             | 5-16 |

| APPENDIX . | A S-RECORD INFORMATION               | A-1  |

# LIST OF ILLUSTRATIONS

|              |                                                       | PAGE |

|--------------|-------------------------------------------------------|------|

| FIGURE       |                                                       |      |

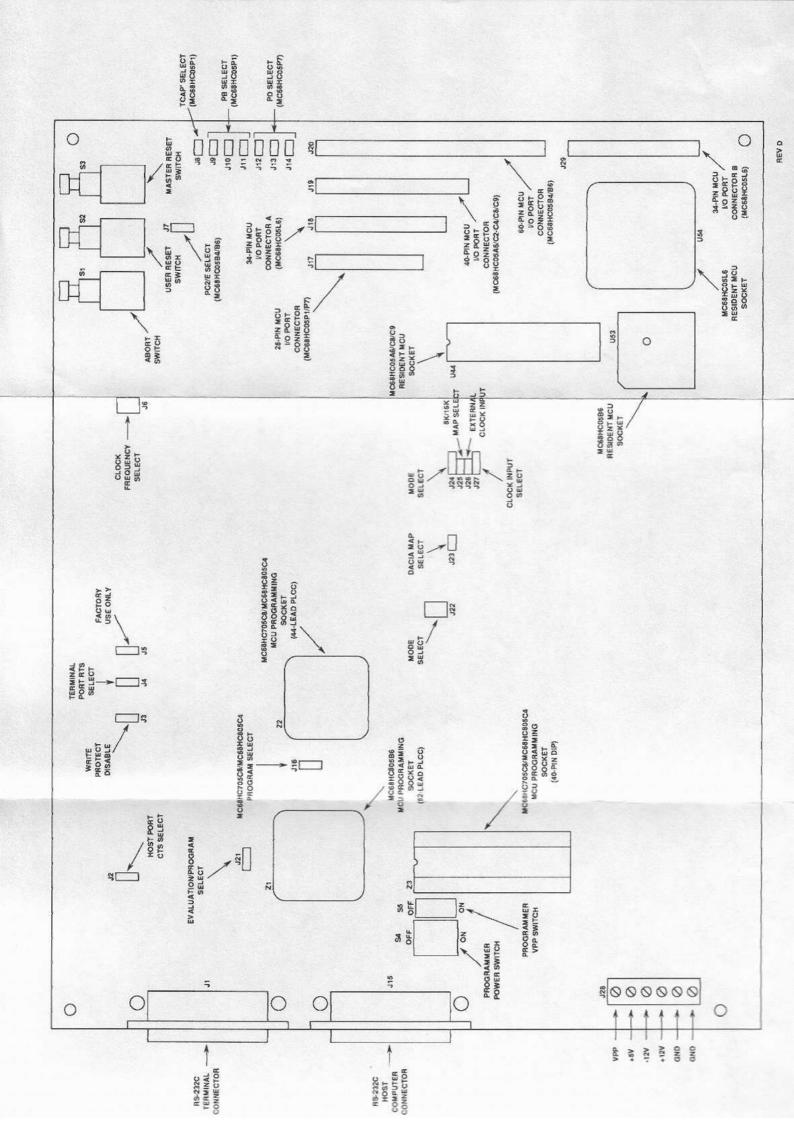

| 2-1.         | EVM Connector, Switch, and Jumper Header              |      |

|              | Location Diagram                                      | 2-3  |

| 2-2.         | Terminal or Host Computer Cable Assembly              | 2-25 |

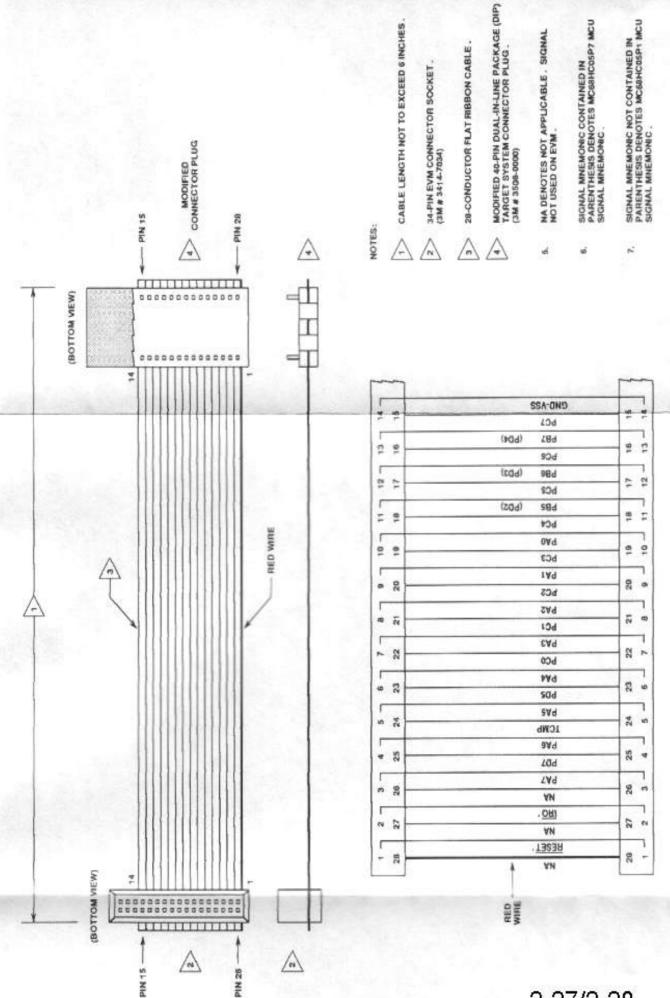

| 2-3.         | 28-Pin DIP Target System Emulation Cable              |      |

|              | Assembly Diagram                                      | 2-27 |

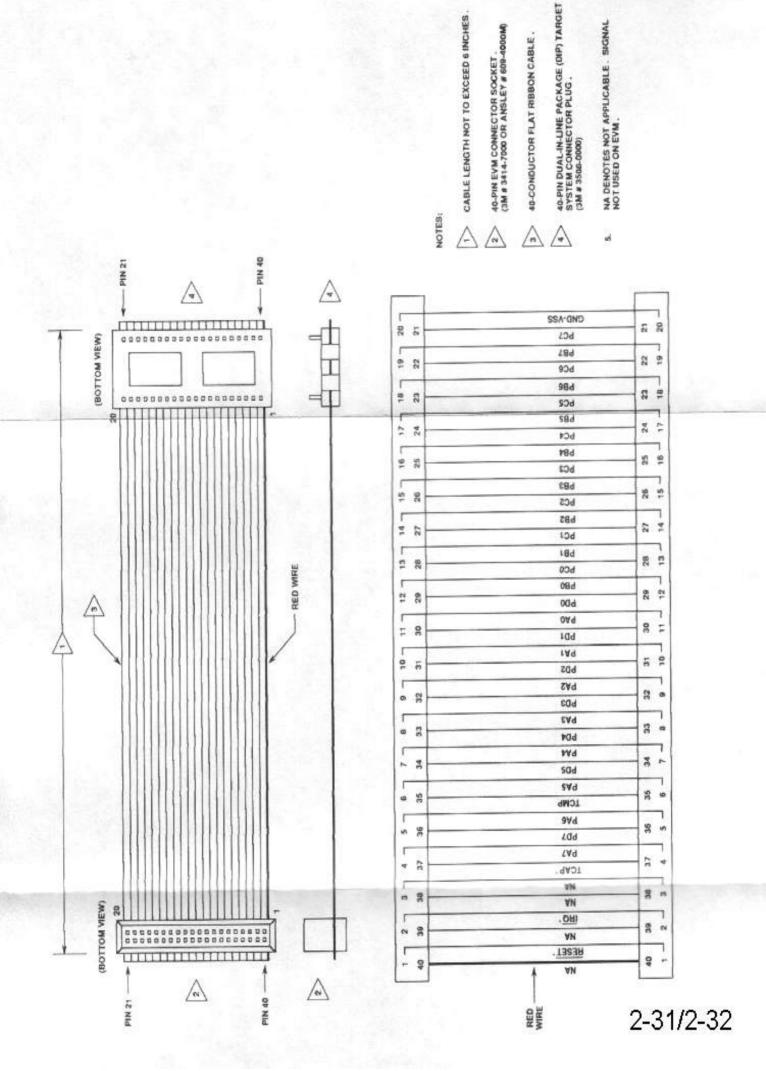

| 2-4.         | 40-Pin DIP Target System Emulation Cable              | -    |

| 2 7.         | Assembly Diagram                                      | 2-31 |

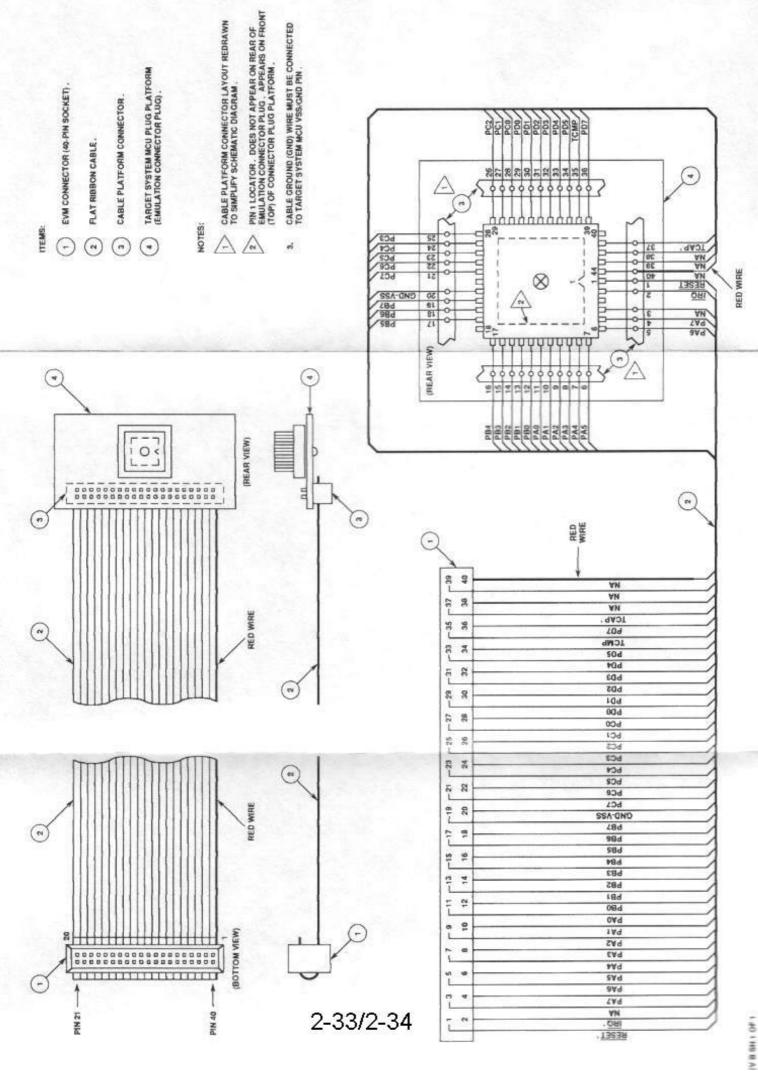

| 2-5.         | 44-Lead PLCC Target System Emulation Cable            | 101  |

| 20.          | Assembly Diagram                                      | 2.33 |

| 2-6.         | 52-Lead PLCC Target System Emulation Cable            | 2.00 |

|              | Assembly Diagram (2 Sheets)                           | 2.37 |

| 2-7.         | 68-Pin Header Target System Emulation Cable           | 201  |

| 4-1,         | Assembly Diagram                                      | 0.40 |

| 4-1          | EVM Block Diagram                                     |      |

| 4-2.         | EVM (A6) Memory Map                                   | 4.0  |

| 4-3.         | EVM (B4/B6/805B6) Memory Map                          | 4.0  |

| 4-4          | EVM (04/00/04/04/04/05/05/05/04) Manage Man           | 4-0  |

| 4-5          | EVM (C2/C3/C4/C8/705C8/805C4) Memory Map              |      |

| 4-5          | EVM (C9) Memory Map                                   | 4.0  |

| 5-1.         | EVM (P1/P7) Memory Map                                |      |

| 5-1.<br>5-2. | EVM Parts Location Diagram                            | 5-17 |

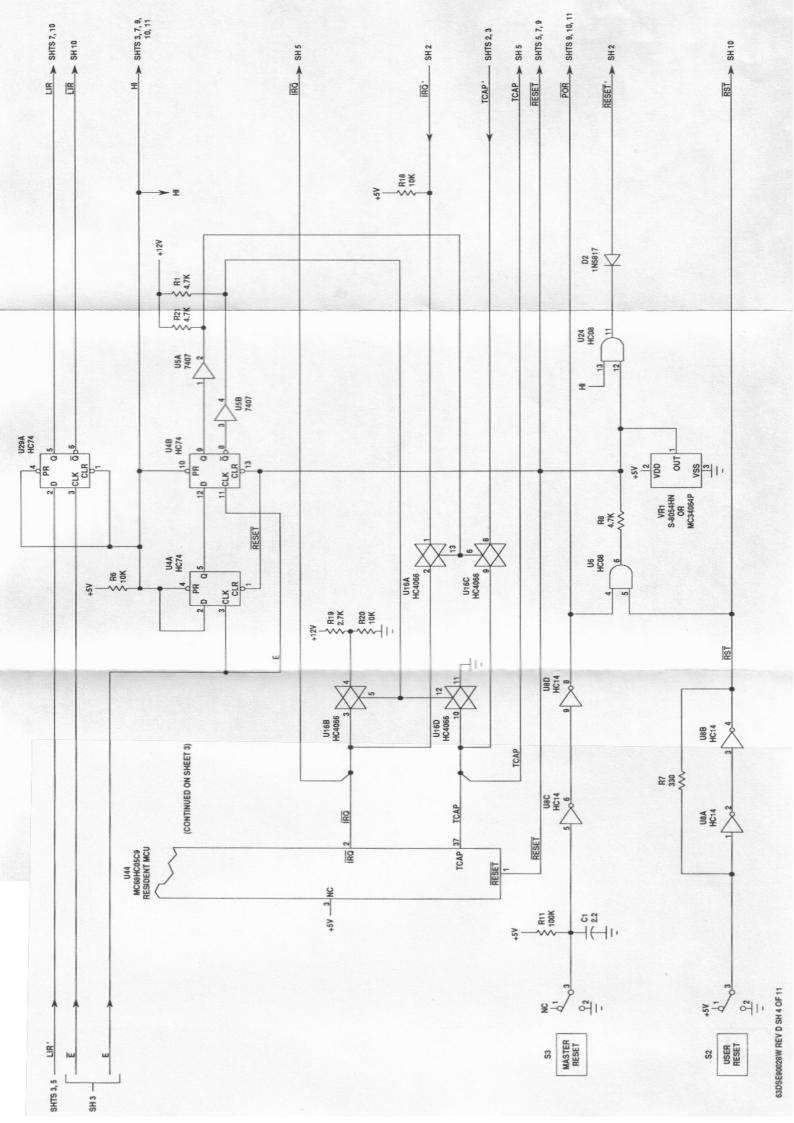

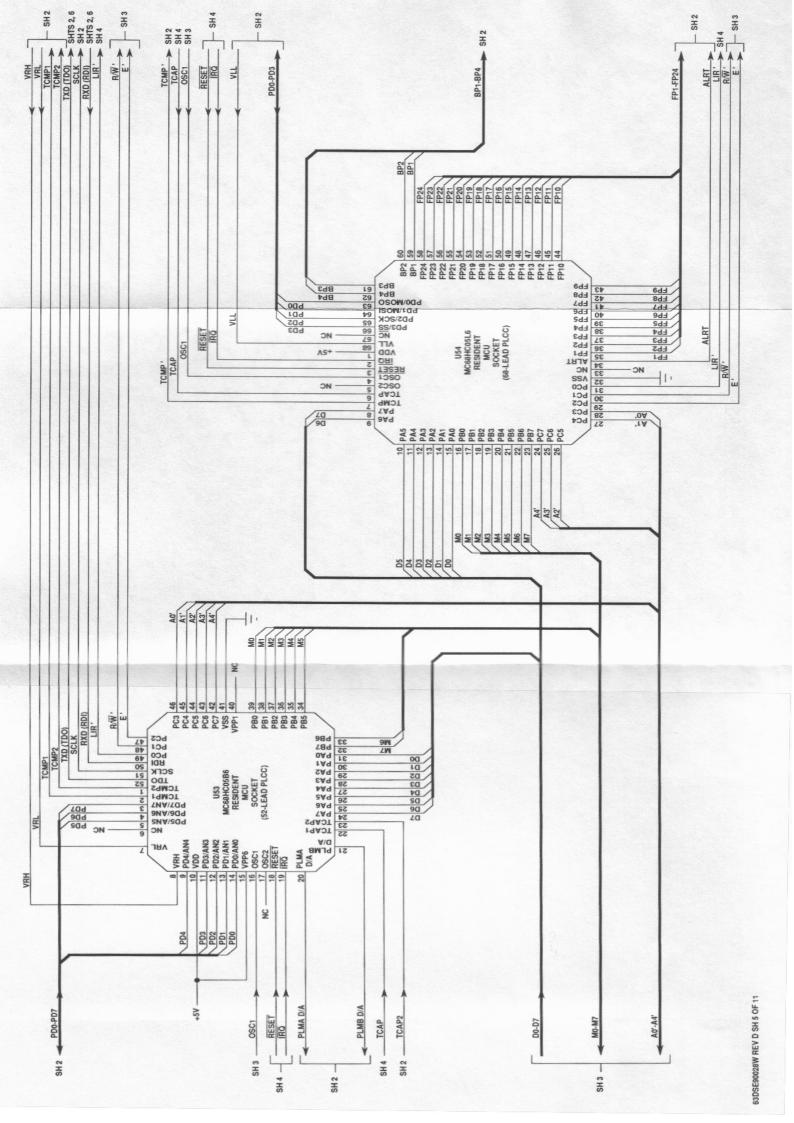

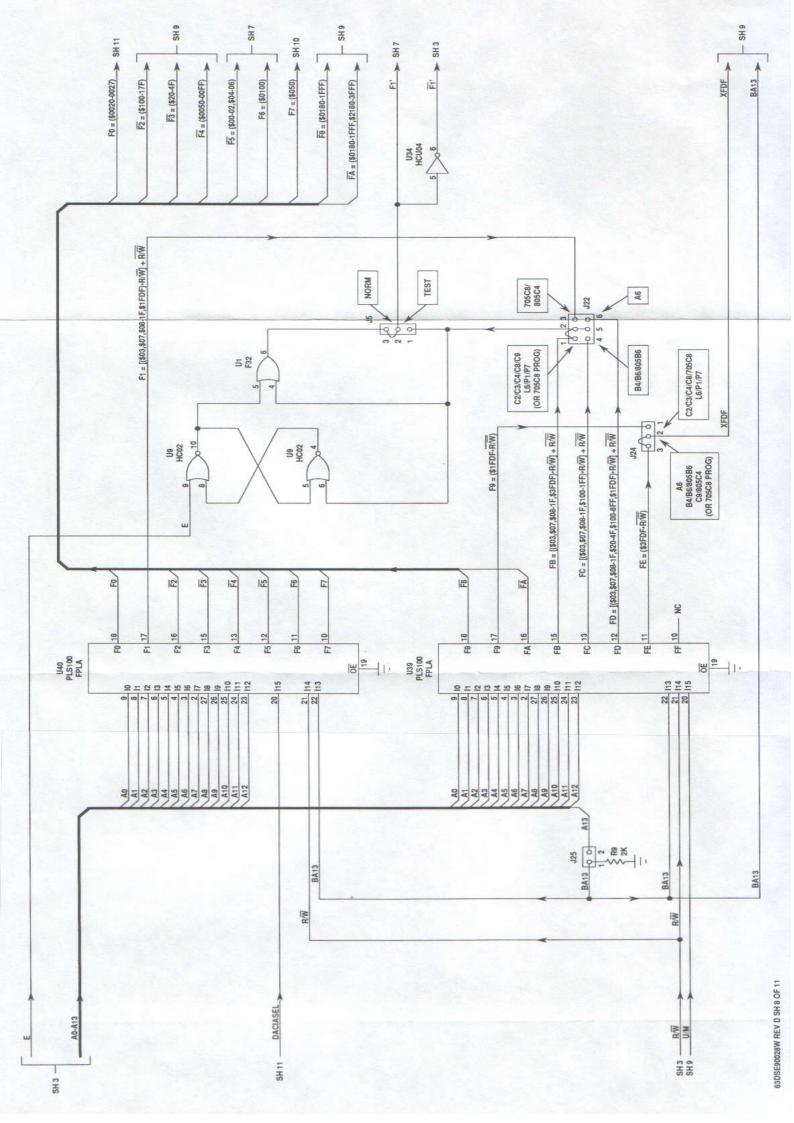

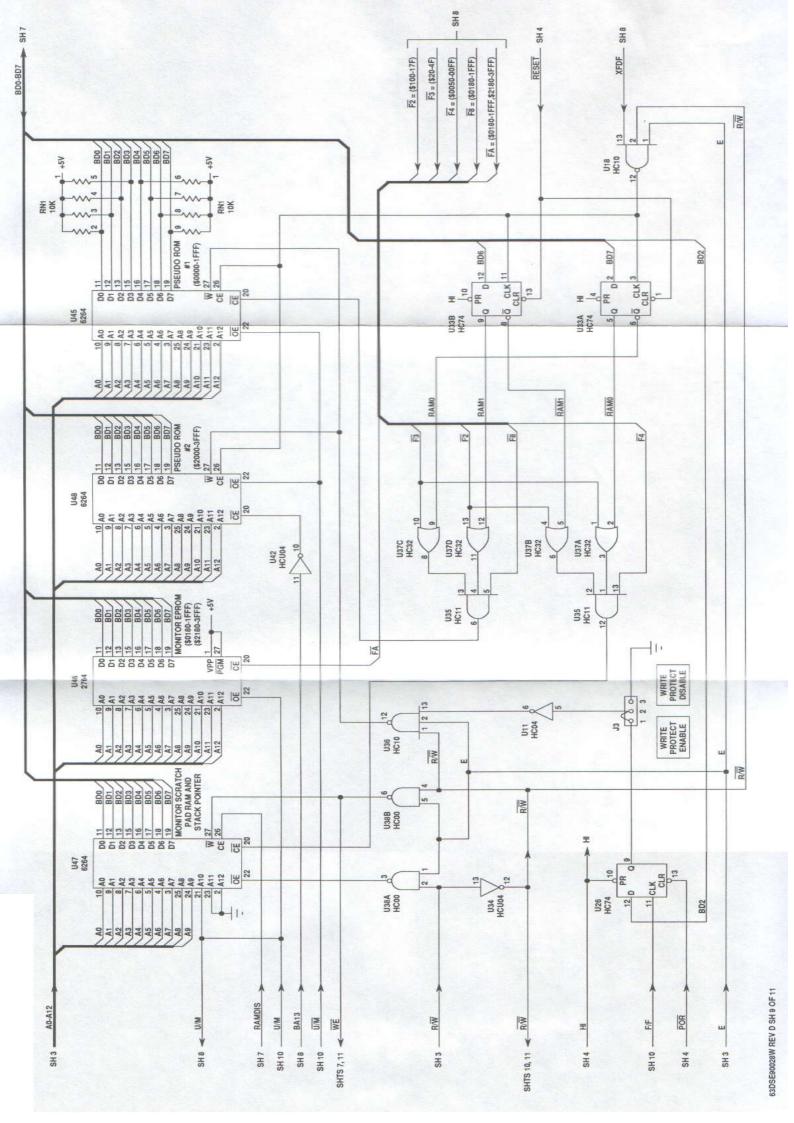

| 3.2.         | EVM Schematic Diagram (11 Sheets)                     | 5-19 |

|              | LIST OF TABLES                                        |      |

|              |                                                       | PAGE |

| TABLE        |                                                       |      |

| 1-1.         | EVM Specifications                                    | 1.2  |

| 1-2.         | External Equipment Requirements                       |      |

| 3-1.         | EVM Control Switches                                  | 3.2  |

| 3-2.         | Monitor (EVMbug) Commands                             |      |

| 5-1.         | RS-232C Terminal Port Connector J1 Pin Assignments    | 5-2  |

| 5-2.         | RS-232C Host Port Connector J15 Pin Assignments       |      |

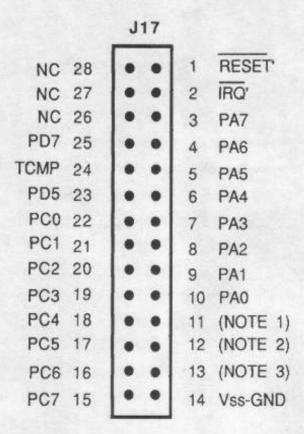

| 5-3.         | 28-Pin MCU I/O Port Connector J17 Pin Assignments     |      |

| 5-4.         | 40-Pin MCU I/O Port Connector J19 Pin Assignments     | 5-5  |

| 5-5.         | 60-Pin MCU I/O Port Connector J20 Pin Assignments     |      |

| 5-6.         | 34-Pin MCU I/O Port Connector (A) J18 Pin Assignments |      |

| 5-7.         | 34-Pin MCU I/O Port Connector (B) J29 Pin Assignments |      |

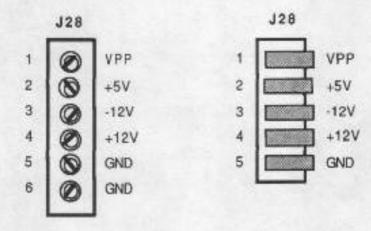

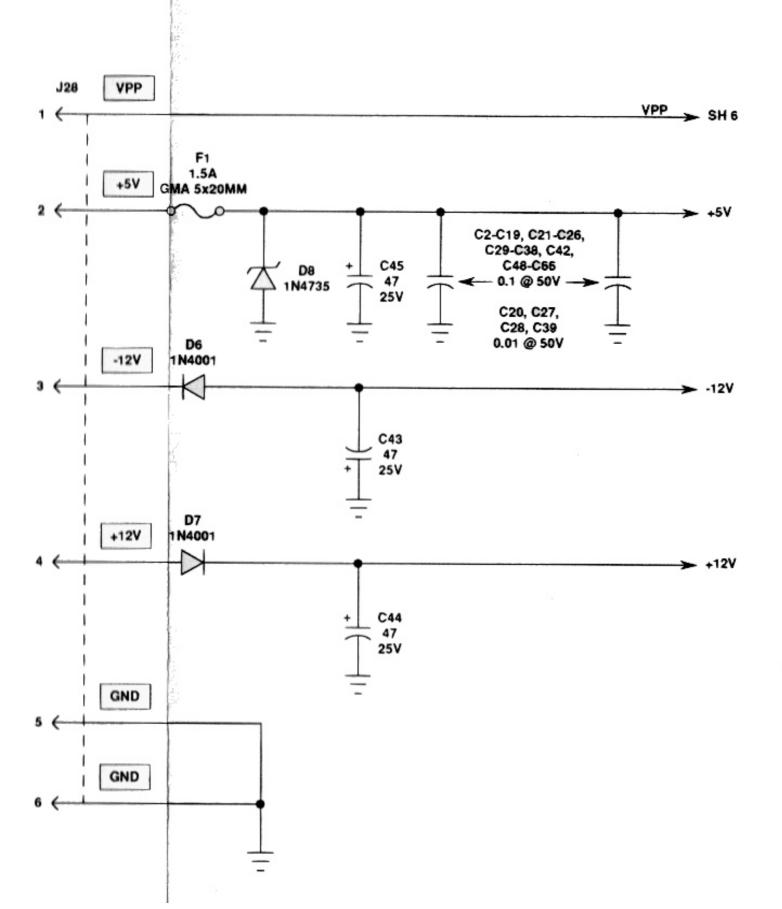

| 5-8.         | Input Power Connector J28 Pin Assignments             |      |

| 5-9.         | EVM Parts List                                        |      |

|              |                                                       | 7    |

# CHAPTER 1

### GENERAL INFORMATION

### 1.1 INTRODUCTION

This manual provides general information, hardware preparation, installation instructions, operating instructions, functional description, and support information for the M68HC05EVM Evaluation Module (hereafter referred to as EVM). Appendix A contains EVM downloading S-record information.

### 1.2 FEATURES

EVM features include:

Economical means of evaluating target systems incorporating M68HC05 HCMOS MCU family devices.

Monitor/debugger firmware

One-line assembler/disassembler

Host computer download capability

Dual 8K-byte memory maps:

8K monitor EPROM 8K/16K User Pseudo ROM

MC68HC805B6 EEPROM MCU programmer

MC68HC705C8 OTPROM/EPROM MCU programmer

MC68HC805C4 EEPROM MCU programmer

28-pin MCU extension I/O port for MC68HC05P1/P7 evaluation

40-pin MCU extension I/O port for MC68HC05A6, HC05C2/C3/C4/C8/C9, HC705C8, HC805C4, HCL05C4/C8, and HSC05C4/C8 evaluation

52-pin MCU extension I/O port for MC68HC05B4/B6 and HC805B6 evaluation

68-pin MCU extension I/O port for MC68HC05L6 evaluation

RS-232C terminal and host computer I/O ports

Table 1-1 lists the EVM specifications.

TABLE 1-1. EVM Specifications

| CHARACTERISTICS          | SPECIFICATIONS                                                                                                |

|--------------------------|---------------------------------------------------------------------------------------------------------------|

| Internal Clock           | 1 or 2 MHz bus operation (8 MHz crystal controlled, divided-by-two or four)                                   |

|                          | 2 or 4 MHz bus operation (16 MHz<br>crystal controlled, divided-by-two<br>or four) for optional HSC operation |

| External Clock           | Up to 8 MHz<br>(2 MHz maximum bus operation)                                                                  |

|                          | Up to 16 MHz<br>(4 MHz maximum bus operation<br>for optional HSC operation)                                   |

| Memory size:             |                                                                                                               |

| Monitor EPROM            | 8K bytes                                                                                                      |

| Pseudo ROM               | 8K/16K bytes                                                                                                  |

| MCU extension I/O ports: | HCMOS compatible                                                                                              |

| Terminal/host I/O ports  | RS-232 compatible                                                                                             |

| Temperature:             |                                                                                                               |

| Operating                | +25 degrees C                                                                                                 |

| Storage                  | -40 to +85 degrees C                                                                                          |

|                          | 0 to 90% (non-condensing)                                                                                     |

# CHARACTERISTICS

# SPECIFICATIONS

# Power requirements:

+5 Vdc @ 1.0 A (max) Module

+12 Vdc @ 0.1 A (max)

-12 Vdc @ 0.1 A (max)

# Programmer (VPP):

### MC68HC705C8:

(Mask 0B67H) +14,00 Vdc +/- 0.10 Vdc

@ 10 mA (max)

+14.75 Vdc +/- 0.25 Vdc (Mask 1B67H)

@ 10 mA (max)

+14.75 Vdc +/- 0.25 Vdc (Mask B44S)

@ 10 mA (max)

+14.75 Vdc +/- 0.25 Vdc (Future Masks)

@ 10 mA (max)

### MC68HC805B6:

+19 Vdc @ 2 mA (max) (BULK erase)

+19 Vdc @ 100 uA (max) (Program)

MC68HC805C4 +19 Vdc @ 100 uA (max)

Dimensions:

Width 12.0 in. (30.5 cm)

9.25 in. (23.5 cm) Length

### 1.4 GENERAL DESCRIPTION

The EVM provides a tool for designing, debugging, and evaluating MC68HC05A6, HC05B4/B6, HC05C2/C3/C4/C8/C9, HC05L6, HC05P1/P7, HC705C8, HC805B6, and HC805C4 Microcomputer Unit (MCU) based target system equipment. By providing all of the essential MCU timing and I/O circuitry, the EVM simplifies user evaluation of the prototype hardware/software product. The EVM requires a user supplied power supply and an RS-232C compatible terminal for operation.

# NOTE

The EVM cannot emulate the low power capabilities of the MC68HCL05C4/C8 MCU devices. The EVM can emulate the high speed (4 MHz) capabilities of the MC68HSC05C4/C8 MCU devices.

The M68HC05 Family of HCMOS MCU devices are evaluated (emulated) by the EVM resident MC68HC05xx MCU. Several types of resident MCUs can be used. The EVM is shipped with an MC68HC05C9 resident MCU device. This device will evaluate MC68HC05C2/C3/C4/C8/C9, HC805C4, HCL05C4/C8, HSC05C4/C8, and HC05P1/P7 MCUs. For other MC68HC05 MCU devices (e.g., MC68HC05A6, HC705C8, HC05B4/B6, HC805B6, HC805C4, and HC05L6), the resident MC68HC05C9 MCU is replaced by the specific MCU device required for evaluation.

Entering data, program debugging, and EPROM MCU programming is accomplished by the monitor ROM firmware via an external RS-232C compatible terminal connected to the EVM terminal port connector. A fixed 9600 baud rate is provided for the terminal port, and a software selectable 300-19.2K baud rate selection is provided for the host port.

Downloading programs (via Motorola S records) directly from an RS-232C compatible host computer to the EVM is accomplished via either the host or terminal port connector. Downloading is accomplished by the use of the monitor commands.

The EVM simulates the single-chip mode of operation. 28-pin MCU I/O port connector facilitates interconnection of the EVM to the target system for MC68HC05P1/P7 evaluation purposes. 40-pin MCU I/O port connector facilitates interconnection of the EVM to the target system for MC68HC05A6, HC05C2/C3/C4/C8/C9, HC705C8, and HC805C4 MCU evaluation purposes. 60-pin MCU I/O port connector facilitates interconnection of the EVM to the target system for MC68HC05B4/B6 and HC805B6 MCU evaluation purposes. Two 34-pin MCU I/O port connectors A and B (68-pins) facilitate interconnection of the EVM to the target system for MC68HC05L6 MCU evaluation purposes.

MCU code may be generated using the resident one-line assembler/disassembler, or may be downloaded to the user program RAM (pseudo ROM) through the host or terminal port connectors. User code may then be executed using various debugging commands in the monitor. User code may also be executed using the user reset switch. MCU device ROM is simulated by write protecting user program RAM during program execution.

IRO level/edge sensitivity selection is software programmable. Jumper selectable options such as clock frequency, clock input, and 8K/16K map selection are provided on the EVM, as well as an OTPROM/EPROM/EEPROM MCU programmer. The MCU programmer, under monitor firmware control, allows the user to check, erase, program, verify, and copy the contents of either a 40-pin Dual-In-line Package (DIP) or a 44-/52-lead Plastic Leaded Chip Carrier (PLCC) MCU devices. Switches allow user control of the reset and abort functions, and OTPROM/EPROM/EEPROM MCU programming functions.

# 1.5 EQUIPMENT REQUIRED

Table 1-2 lists the external equipment requirements for EVM operation.

TABLE 1-2. External Equipment Requirements

# EXTERNAL EQUIPMENT

+5, +12, -12 Vdc power supply\*

VPP power supply\*

Terminal (RS-232C compatible)

Host computer (RS-232C compatible)\*\*

Terminal/host computer - EVM RS-232C cable assembly\*

Target system - EVM emulator cable assemblies\*\*\*

### Notes:

- (1) \* Refer to Chapter 2 for details.

- (2) \*\* Optional not required for basic operation.

- (3)\*\*\* DIP cable assemblies fabricated by user.

PLCC cable assembly supplied with EVM.

# CHAPTER 2

# HARDWARE PREPARATION AND INSTALLATION INSTRUCTIONS

### 2.1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation, component implementation, and installation instructions for the EVM.

# 2.2 UNPACKING INSTRUCTIONS

### NOTE

If shipping carton is damaged upon receipt, request carrier's agent be present during unpacking and inspection of the EVM.

Unpack EVM from shipping carton. Refer to packing list and verify that all Items are present. Save packing material for storing or reshipping the EVM.

# 2.3 HARDWARE PREPARATION

This portion of text describes the inspection/preparation of EVM components prior to target system installation. This description will ensure the user that the EVM components are properly configured for target system operation. The EVM has been factory-tested and is shipped with factory-installed jumpers.

The EVM should be inspected/prepared for jumper placements prior to target system installation. Figure 2-1 illustrates the EVM connector, switch, and jumper header locations.

Connectors J1, J15, J17 through J20, J26, J28, and J29 facilitate interconnection of external equipment to the EVM. Switches S1 through S5 provide user control of the EVM. Refer to Chapter 3 for switch descriptions.

- a. Mode select (J22 and J24)

- b. Normal/test select (J5) Factory use only.

- MC68HC705C8/MC68HC805C4 program select (J16)

- d. Evaluation/program select (J21)

Jumper header locations J7 through J14 provide specific I/O port configuration capabilities as follows:

- PC2/E select (J7) MC68HC05B4/B6 operation only.

- PB select (J9 thru J11) MC68HC05P1 operation only.

- PD select (J12 thru J14) MC68HC05P7 operation only.

- TCAP' select (J8) MC68HC05P1 operation only.

Jumper header locations J2 through J4, J6, J23, J25, and J27 provide general selection capabilities that are applicable for all modes of operation as follows:

- a. Host port CTS select (J2)

- b. Clock frequency select (J6)

- c. Terminal port RTS select (J4)

- d. DACIA map select (J23)

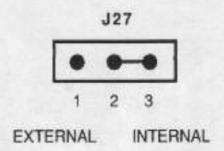

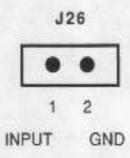

- e. Clock input select (J27)

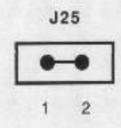

- t. 8K/16K map select (J25)

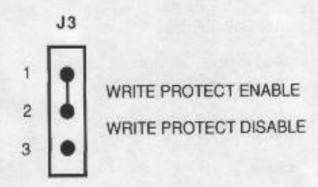

- Write protect disable (J3)

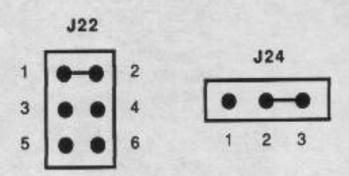

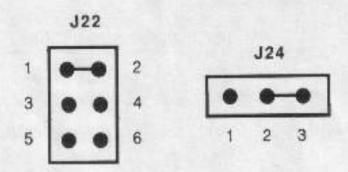

# 2.3.1 Mode Select Headers (J22 and J24)

Configure jumper headers J22 and J24 for EVM evaluation of a specific MCU operation. J22 and J24 are factory configured for evaluating the MC68HC05C4 MCU (shown below). MCU device limitations must be considered when configuring the EVM for a specific MCU operation (refer to page 2-18).

Jumper header J22 and J24 basic configurations for the M68HC05 family of devices are provided in the table below.

| RESIDENT MCU | EVALUATION MCU(1)                                                             | J22        | J24 |

|--------------|-------------------------------------------------------------------------------|------------|-----|

| MC68HC05A6   | MC68HC05A6 w/<br>Internal EEPROM (2)<br>MC68HC05A6 w/<br>Pseudo EPROM         | 5-6<br>3-5 | 2-3 |

| MC68HC05B6   | MC68HC05B6/805B6 w/<br>Internal EEPROM<br>MC68HC05B6/805B6 w/<br>Pseudo EPROM | 2-4        | 2-3 |

| MC68HC05B4   | MC68HC05B4,<br>MC68HC05B6,<br>MC68HC805B6                                     | 1-2        | 2-3 |

# 2.3.1 Mode Select Headers (J22 and J24)

Jumper headers J22 and J24 are use to configure the EVM for a specific microcontroller unit (MCU) evaluation operation. The EVM is factory configured and shipped for MC68HC05C4 evaluation operation as shown below.

Jumper header J22 and J24 basic configurations for the M68HC05 family of devices are provided in the table shown below.

| ASIC CONFIGURATIONS | JUMPER | HEADER |

|---------------------|--------|--------|

| MODE OF OPERATION   | J22    | J24    |

| MC68HC05A6          | 5-6    | 3-5    |

| MC68HC05B4/B6/805B6 | 2-4    | 3-5    |

| MC68HC05C2-C4/C8    | 1-2    | 1-2    |

| MC68HC05C9*         | 1-2    | 3-5    |

| MC68HC705C8         | 3-5    | 1-2    |

| MC68HC805C4         | 3-5    | 3-5    |

| MC68HC05L6          | 1-2    | 1-2    |

| MC68HC05P1/P7       | 1-2    | 1-2    |

| MC68HCL05C4/C8      | 1-2    | 1-2    |

| MC68HSC05C4/C8      | 1-2    | 1-2    |

NOTE: \* Denotes 16K memory map configured via J25 for C9 configuration.

All other configurations require 8K memory map (see para. 2.3.14).

Specific MCU device limitations (refer to page 2-18) must be considered when configuring the EVM for a specific MCU operation. The following page describes specific configurations for specific device evaluation operations.

| RESIDENT MCU                                                  | EVALUATION MCU                                                                                                                                                                                     | J22        | J24 |      |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|

| MC68HC05C9                                                    | MC68HC05A6,<br>MC68HC05C2,<br>MC68HC05C3,<br>MC68HC05C4,<br>MC68HC05C6,<br>MC68HC05L6<br>MC68HC05P1,<br>MC68HC05P7,<br>MC68HCL05C4,<br>MC68HCL05C4,<br>MC68HSC05C4,<br>MC68HSC05C4,                | 1-2        | 2-3 |      |

| MC68HC05C9(3)                                                 | MC68HC05C9 w/<br>16K memory map <sup>(4)</sup>                                                                                                                                                     | 1-2        | 2-3 | * "  |

| MC68HC705C8, or<br>MC68HC805C4                                | MC68HC05A6,<br>MC68HC05C2,<br>MC68HC05C3,<br>MC68HC05C4,<br>MC68HC05C8,<br>MC68HC05L6,<br>MC68HC05P1,<br>MC68HC05P7,<br>MC68HC05C4,<br>MC68HCL05C4,<br>MC68HCL05C4,<br>MC68HSC05C4,<br>MC68HSC05C8 | 3-5        | 2-3 | 19   |

| MC68HC705C8 <sup>(5)</sup> , or<br>MC68HC805C4 <sup>(5)</sup> | MC68HC805C4<br>MC68HC705C8                                                                                                                                                                         | 3-5<br>3-5 | 2-3 | * 10 |

Except where noted all emulation MCUs require at lest 8K for the memory map.

2. Option register is readable and writeable.

3. Write option register at \$3FDF.

Install a jumper on jumper header J25 to enable the 16K memory map.

5. Write option register at \$1FDF.

|                                                                                                |                                         | CON                                                  | FIGUE                                         | RATION                                                         |                                                                                                                     |                                                      |

|------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| MODE                                                                                           | MCU                                     | (J22)                                                | (J24)                                         | (J25)                                                          | NOTES                                                                                                               |                                                      |

| MC68HC05A6<br>MC68HC05A6                                                                       | MC68HC05A6                              | 5-6<br>3-5                                           | 2-3<br>2-3                                    | Removed<br>Removed                                             | Internal EEPROM<br>Pseudo EPROM                                                                                     | (1.)                                                 |

| MC68HC05B6                                                                                     | MC68HC05B6<br>or<br>MC68HC805B6         | 1-2<br>2-4                                           | 2-3<br>2-3                                    | Removed<br>Removed                                             | Pseudo EPROM<br>Internal EEPROM                                                                                     |                                                      |

| MC68HC05C2<br>MC68HC05C3<br>MC68HC05C4<br>MC68HC05C8<br>MC68HC05P1<br>MC68HC05P7<br>MC68HC05A6 | MC68HC05C9                              | 1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2        | 1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2 | Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed | 8K memory map<br>8K memory map<br>8K memory map<br>8K memory map<br>8K memory map<br>8K memory map<br>8K memory map | (2.)<br>(2.)<br>(2.)<br>(2.)<br>(2.)<br>(2.)<br>(2.) |

| MC68HC05C2<br>MC68HC05C3<br>MC68HC05C4<br>MC68HC05C8<br>MC68HC05P1<br>MC68HC05P7<br>MC68HC05A6 | MC68HC705C8<br>or<br>MC68HC805C4        | 3-5<br>3-5<br>3-5<br>3-5<br>3-5<br>3-5<br>3-5<br>3-5 | 2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3 | Removed<br>Removed<br>Removed<br>Removed<br>Removed<br>Removed | 8K memory map<br>8K memory map<br>8K memory map<br>8K memory map<br>8K memory map<br>8K memory map<br>8K memory map | (3.)<br>(3.)<br>(3.)<br>(3.)<br>(3.)<br>(3.)<br>(3.) |

| MC68HC05C9                                                                                     | MC68HC05C9                              | 1-2                                                  | 2-3                                           | Installed                                                      | 16K memory map                                                                                                      |                                                      |

| MC68HC705C8                                                                                    | MC68HC705C8                             | 3-5                                                  | 1-2                                           | Removed                                                        | 8K memory map                                                                                                       |                                                      |

| MC68HC805C4                                                                                    | MC68HC805C4                             | 3-5                                                  | 2-3                                           | Removed                                                        | 8K memory map                                                                                                       | 633578                                               |

| MC68HC05B4                                                                                     | MC68HC05B4<br>MC68HC05B6<br>MC68HC805B6 | 1-2<br>1-2<br>1-2                                    | 2-3<br>2-3<br>2-3                             | Removed<br>Removed                                             | 8K memory map<br>8K memory map<br>8K memory map                                                                     |                                                      |

NOTES:

- Option register readable and writeable.

Write option register at \$3FDF.

Write option register at \$1FDF.

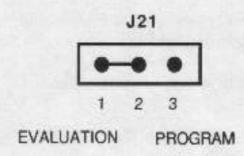

# 2.3.4 Evaluation/Program Select Header (J21)

Jumper header J21 is use to configure the EVM for either the evaluation mode of operation or the programming mode of operation. The EVM is factory configured and shipped for evaluation mode of operation as shown below.

To select the programming mode of operation, reinstall J21 fabricated jumper between pins 2 and 3.

### 2.3.5 PC2/E Select Header (J7) (MC68HC05B4/B6/805B6 operation only.)

Jumper header J7 is used only for MC68HC05B4/B6/805B6 MCU evaluation. Jumper header J7 is used to select either PC2 for normal I/O operations, or E for the CPU E-clock out option. The EVM is factory configured and shipped for normal I/O evaluation operation as shown below.

To select the CPU E-clock out option, reinstall J7 fabricated jumper between pins 1 and 2.

Jumper headers J9 through J11 are used only for MC68HC05P1 MCU evaluation. Jumper headers J9 through J11 are used to select PB5 through PB7 signal lines for MC68HC05P1 I/O port operations. When the fabricated jumpers are installed, PB5 through PB7 signal lines are routed to the 28-pin I/O port connector J17 pins 11 through 13, respectively. The EVM is factory configured and shipped with jumpers not installed as shown below.

Prior to installing fabricated jumpers on jumper headers J9 through J11, ensure that fabricated jumpers are removed from jumper headers J12 through J14. Conversely, prior to installing fabricated jumpers on jumper headers J12 through J14, ensure that fabricated jumpers are removed from jumper headers J9 through J11.

# CAUTION

MCU damage may occur if jumpers are installed on both PB and PD select headers.

If fabricated jumpers are installed on both the PB (J9 thru J11) and PD (J12 thru J14) select headers simultaneously, erratic MCU I/O port and/or EVM operation will result. To avoid erratic port and/or EVM operation, only one group of select headers (either PB or PD) must be jumpered for a specific port operation (MC68HC05P1 or MC68HC05P7).

Jumper headers J12 through J14 are used only for MC68HC05P7 MCU evaluation. Jumper headers J12 through J14 are used to select PD2 through PD4 signal lines for MC68HC05P7 I/O port operations. When the fabricated jumpers are installed, PD2 through PD4 signal lines are routed to the 28-pin I/O port connector J17 pins 11 through 13, respectively. The EVM is factory configured and shipped with jumpers not installed as shown below.

# NOTE

Above asterisks (\*) denote if parallel I/O is required instead of SPI, J9 thru J11 jumpers must be installed instead of J12 thru J14.

Prior to installing fabricated jumpers on jumper headers J12 through J14, ensure that fabricated jumpers are removed from jumper headers J9 through J11. Conversely, prior to installing fabricated jumpers on jumper headers J9 through J11, ensure that fabricated jumpers are removed from jumper headers J12 through J14.

Jumper header J8 is used only for MC68HC05P1 MCU evaluation. Jumper header J8 is used to generate the TCAP' signal for the resident MCU. When the fabricated jumper is installed, TCAP' signal is generated via the PD7 signal line. The EVM is factory configured and shipped with jumpers not installed as shown below.

# 2.3.9 Host Port CTS Select Header (J2)

Jumper header J2 is used to configure the RS-232C host computer I/O port for semi- or fullhandshaking operation. The EVM is factory-configured for semi-handshaking (high level) operation. This semi-handshaking configuration (high level) is accomplished by the installation of a fabricated jumper on jumper header J2 as shown below.

Should the host computer or modern require full-handshake capability, the jumper is repositioned between pins 2 and 3. Refer to the schematic diagram located in Chapter 5 (Figure 5-2, sheet 11 of 11) for CTS signal wiring information.

Jumper header J6 is used to select the internal EVM clock frequency. The EVM is shipped with an internal 8 MHz crystal, and factory configured for 4 MHz clock (E = 2 MHz) operation as shown below.

The divide by one option (pins 1 and 2) is not used. Do not attempt to operate the EVM with low speed devices (e.g., A6, B6, L6, etc.) above 4 MHz clock (E = 2 MHz). Improper EVM operation (device evaluation) will result.

# NOTE

For HSC operation, the user is required to replace the 8 MHz crystal (Y1) with a 16 MHz crystal. When the 16 MHz crystal is installed, the divide by 2 and divide by 4 options become E = 4 MHz and E = 2 MHz, respectively.

# 2.3.11 Terminal Port RTS Select Header (J4)

Jumper header J4 is used to configure the RS-232C terminal I/O port for semi- or fullhandshaking operation. The EVM is factory-configured for semi-handshaking (high level) operation. This semi-handshaking configuration (high level) is accomplished by the installation of a fabricated jumper on jumper header J4 as shown below.

Should the host computer or modem require full-handshake capability, the jumper is repositioned between pins 2 and 3. Refer to the schematic diagram located in Chapter 5 (Figure 5-2, sheet 11 of 11) for RTS signal wiring information.

# 2.3.12 DACIA Map Select Header (J23)

# NOTE

Jumper header J23 is for factory use only.

Jumper header J23 is for factory use only. The installed fabricated jumper (shown below) should not be removed during normal EVM operations.

Jumper header J27 is used to select either internal or external clock source to be used by the EVM. The internal clock source is an 8 MHz crystal. The EVM is factory-configured and shipped with the clock input selected to internal clock operation as shown below. To select an external clock source, reinstall jumper between pins 1 and 2.

When the external clock source is selected, connector J26 (2-pin header) is used to facilitate interconnection of the external clock source.

# 2.3.14 8K/16K Map Select Header (J25)

Jumper header J25 is used to select either the 16K memory map which is required for MC68HC05C9 operations, or the 8K memory map which is applicable for all other operations. The EVM is factory-configured and shipped with the 16K memory map enabled. This is accomplished by the installation of a fabricated jumper on pins 1 and 2 as shown below. To enable the 8K memory map, remove jumper from pins 1 and 2.

# NOTE

Jumper is removed for all evaluation operations except when evaluating the MC68HC05C9 MCU.

# 2.3.15 Write Protect Disable Header (J3)

Jumper header J3 is used to write protect the user program space during program execution (pseudo ROM). The EVM is factory-configured and shipped with the write protect function enabled. This is accomplished by the installation of a fabricated jumper on pins 1 and 2 as shown below. To disable the write protect function, remove jumper from pins 1 and 2, and reinstall jumper on pins 2 and 3.

### 2.4 COMPONENT IMPLEMENTATION

This portion of text describes the components required for MC68HC05L6 evaluation, specifies resident MCUs for specific target system evaluation, and illustrates proper resident MCU installation techniques. One time programmable read only memory (OTPROM), erasable programmable read only memory (EPROM), and electrically erasable programmable read only memory (EPROM) MCU installation techniques for programming operations are also provided.

# 2.4.1 Resident MC68HC05L6 Evaluation Circuitry

As shown in Figure 2-1; the resident MC68HC05L6 MCU, MCU socket (U54), and MCU I/O port connectors (J18 and J29) are supplied and installed by the user. PCB feed-thru holes and conductive lands (traces) are provided on the EVM for the user to install the PLCC socket and two 34-pin I/O port connectors. A 68-lead PLCC surface mount socket (Plastronics # P2068SP) must be installed at socket location U54. Two 34-pin connectors (Aptronics # 929715-01-17) must be installed at connector locations J18 and J29. These connectors consist of two 17-pin headers, double row post. Care in socket and connector installation/soldering will save many hours of troubleshooting and repair after assembly.

### 2.4.2 Resident MCU Sockets

There are three resident MCU sockets (U44, U53, and U54) available on the EVM. Only one resident MCU may be installed on the EVM for a specific evaluation. Multiple resident MCUs will cause MCU damage and/or erratic EVM operation. On the following page is a list of recommended resident MCUs used for evaluation purposes.

When required, the resident 40-pin DIP MCU must be inserted into resident socket location U44. Inspect socket locations U53, U54, Z1, Z2, and Z3. Remove MCUs (if installed).

# CAUTIONS

The resident M68HC05B6 MCU must be inserted right side up in socket U53. Incorrect MCU insertion will cause MCU damage.

The resident M68HC05L6 MCU must be inserted upside down in socket U54. Incorrect MCU insertion will cause MCU damage.

Forcing the resident MCU into the surface mount socket can result in damage to the socket. Surface mount sockets are fragile.

Only one resident MCU may be installed on the EVM for a specific evaluation. Multiple resident MCUs will cause MCU damage and/or erratic EVM operation.

EVALUATION MODULE USER'S MANUAL 2-16

# Recommended Resident MCUs for Evaluation

| RESIDENT<br>MCU | SOCKET              | PACKAGE<br>TYPE | MCU<br>EVALUATION        |

|-----------------|---------------------|-----------------|--------------------------|

| MC68HC05A6      | U44                 | 40-PIN DIP      | MC68HC05A6               |

| MC68HC05C4      | U44                 | 40-PIN DIP      | MC68HC05C2               |

| (MC68HC05C9*)   |                     |                 | MC68HC05C3               |

|                 | 6514572.65          |                 | MC68HC05C4               |

|                 |                     |                 | MC68HC05C8               |

|                 |                     |                 | MC68HC05P1               |

|                 | On The State of the |                 | MC68HC05P7               |

|                 |                     |                 | MC68HCL05C4              |

|                 | Law St.             |                 | MC68HCL05C8              |

|                 |                     |                 | MC68HSC05C4              |

|                 |                     |                 | MC68HSC05C8              |

| MC68HC05C9*     | U44                 | 40-PIN DIP      | MC68HC05C9               |

| MC68HC705C8     | U44                 | 40-PIN DIP      | MC68HC705C8              |

| MC68HC805C4     | U44                 | 40-PIN DIP      | MC68HC805C4              |

| MC68HC05B4      | U53                 | 52-LEAD PLCC    | MC68HC05B4               |

| MC68HC05B6      | U53                 | 52-LEAD PLCC    | MC68HC05B4<br>MC68HC05B6 |

| MC68HC805B6     | U53                 | 52-LEAD PLCC    | MC68HC805B6              |

| MC68HC05L6      | U54                 | 68-LEAD PLCC    | MC68HC05L6               |

- NOTES: (1) \* Denotes EVM shipped with MC68HC05C9 device installed in resident MCU socket U44, and the 16K memory map configured via jumper header J25.

- (2) \* Also denotes MC68HC05C9 resident MCU can evaluate all device types specified for the MC68HC05C4 resident MCU. Jumper must be removed from jumper header J25 to configure 8K memory map operations.

- (3) Operational limitations for specific MCUs are provided on the following page.

# Resident MC68HC05C9 MCU Operational Limitations

The MC68HC05C9 MCU option register resides internally at location \$3FDF. Therefore, when evaluating other HC05xx family devices with option registers residing at \$1FDF, all accesses to the resident HC05C9 MCU option register must be made at \$3FDF as opposed to \$1FDF even though the 8K memory map is selected.

The HC05C9 MCU cannot be used to exactly replicate SPI operations for all HC05Cx MCU devices.

The HC05C9 MCU DDRD has a negative implication affecting serial peripheral interface (SPI) operations. All port D lines used as output lines must have corresponding DDR bits set to a logic 1 (i.e., SCK (master), MOSI (master), MISO (slave)) when evaluating all HC05Cx MCU devices.

The HC05C9 MCU contains a port D data direction register (DDRD) that can be used to emulate the MC68HC05P1 and MC68HC05P7 MCU port D, bit 5 (PD5). The user must be aware that the entire DDRD is implemented and other DDRD bits must not be accidently written to. When evaluating HC05P1 and HC05P7 devices with the resident HC05C9 MCU, the user must write \$20 value to DDRD location \$07 when configuring PDDR5 as an output line. This step will ensure that other port D pins remain as input lines as required for correct HC05P1 and HC05P7 evaluation.

# Resident MC68HC705C8 MCU Operational Limitations

When evaluating with a resident MC68HC705C8 MCU the option register is accessed at location \$1FDF. The HC705C8 option registers must be written to if edge-only interrupts are to be used. The HC705C8 option register contains RAM/ROM bits used for dynamic mapping of internal RAM/ROM.

The HC705C8 MCU can be used to exactly replicate SPI operations for all HC05Cx MCU devices.

# Resident MC68HC805C4 MCU Operational Limitations

When evaluating with a resident MC68HC805C4 MCU the option register is accessed at location \$1FDF. The HC805C4 option register must be written to if edge-only interrupts are to be used. The HC805C4 option register only configures IRQ options.

The HC805C4 MCU can be used to exactly replicate SPI operations for all HC05Cx MCU devices.

# General Operational Limitations

The EVM cannot emulate the low power capabilities of the MC68HCL05C4/C8 MCU devices.

The EVM can emulate the high speed (4 MHz) capabilities of the MC68HSC05C4/C8 MCU devices by replacing the 8 MHz crystal (Y1) with a 16 MHz crystal. Refer to paragraph 2.3.10. When required, the resident 52-lead PLCC MC68HC05B6 MCU is inserted right side up in resident socket location U53 as shown below. Inspect socket locations U44, U54, Z1, Z2, and Z3. Remove MCUs (if installed).

Resident 52-lead PLCC MC68HC05B6 MCU (U53) Installation

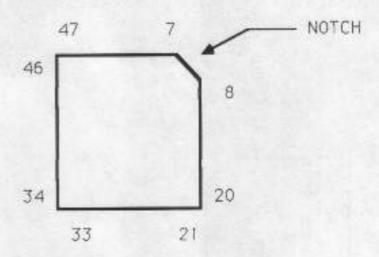

When required, the resident 68-lead PLCC MC68HC05L6 MCU is inserted upside down (horizontal flip) in resident socket location U54 as shown below. Inspect socket locations U44, U53, Z1, Z2, and Z3. Remove MCUs (if installed).

Resident 68-lead PLCC MC68HC05L6 MCU (U54) Installation

There are three MCU programming sockets (Z1, Z2, and Z3) available on the EVM. As shown in Figure 2-1, the MC68HC805C4/MC68HC705C8 MCU programming socket Z3 consists of a 40-pin DIP socket, and Z2 consists of a 44-lead PLCC surface mount socket.

# CAUTION

Forcing the OTPROM/EEPROM MCU into the surface mount socket can result in damage to the socket. Surface mount sockets are fragile.

Only one programmable MCU must be installed on the EVM for a specific programming operation. Multiple MCUs will cause MCU damage and/or erratic EVM operation.

When programming the 40-pin DIP MC68HC705C8 OTPROM, MC68HC705C8 EPROM, or MC68HC805C4 EEPROM MCU, the device is inserted into programming socket Z3. Inspect socket locations Z1, Z2, U53, and U54. Remove MCUs (if installed).

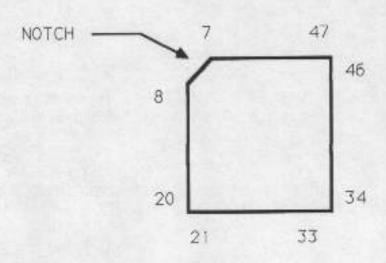

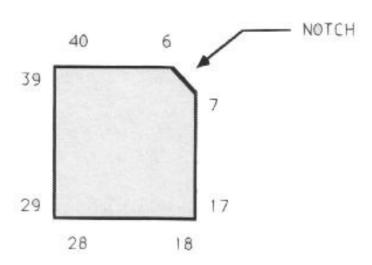

When programming the 44-lead PLCC MC68HC705C8 OTPROM or MC68HC805C4 EEPROM MCU, the device must be inserted upside down (horizontal flip) into programming socket Z2 as shown below. Inspect socket locations Z1, Z3, U53, and U54. Remove MCUs (if installed).

44-lead PLCC MC68HC705C8/MC68HC805C4 MCU (Z2) Installation

As shown in Figure 2-1, the MC68HC805B6 EEPROM MCU programming socket Z1 consists of a 52-lead PLCC surface mount socket.

# CAUTION

Forcing the EEPROM MCU into the surface mount socket can result in damage to the socket. Surface mount sockets are fragile.

Only one MCU must be installed on the EVM for a specific programming operation. Multiple MCUs will cause MCU damage and/or erratic EVM operation.

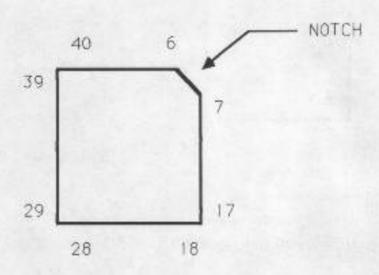

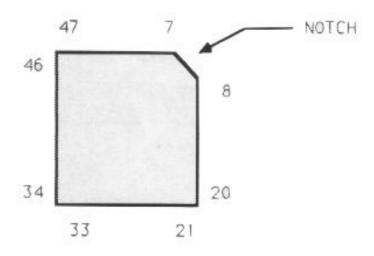

When programming the 52-lead PLCC MC68HC805B6 EEPROM MCU, the device must be inserted upside down (horizontal flip) in programming socket Z1 as shown below. Inspect socket locations Z2, Z3, U44, and U54. Remove MCUs (if installed).

52-lead PLCC MC68HC805B6 MCU (Z1) Installation

The EVM is designed for table top operation. A user supplied power supply and RS-232C compatible terminal are required for EVM operation. An RS-232C compatible host computer may be connected to the EVM, but is not required for basic EVM operation.

# 2.5.1 Power Supply - EVM Interconnection

The EVM requires +5 Vdc @ 1.0 A, +12 Vdc @ 0.1 A, and -12 Vdc @ 0.1 A for operation.

Appropriate programming voltage (VPP) is determined by the data sheet of the MCU device to be programmed. Refer to page 3-34 for additional VPP information.

### CAUTION

When external VPP power is connected to the EVM power connector J28 pin 1, VPP must be controlled by the EVM programmer VPP switch S5. The user must perform the programming procedures as specified in paragraphs 3.7.1 through 3.7.5. Failure to control VPP power via switch S5 will cause damage to the OTPROM/EPROM MCU device.

The user supplied power supply is connected to connector J28, which is a terminal block designed to accept 14-22 AWG wire. Two types of terminal blocks are used in the manufacturing of the EVM. Interconnection of the power supply wiring to the EVM is accomplished via either connector type shown below.

### 2.5.2 Terminal - EVM Interconnection

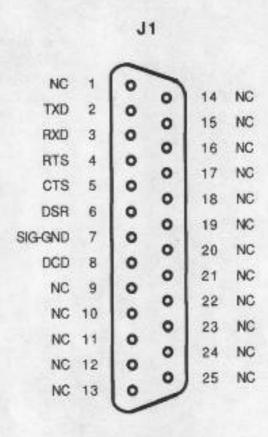

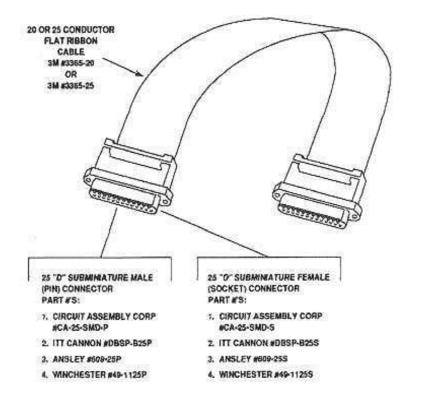

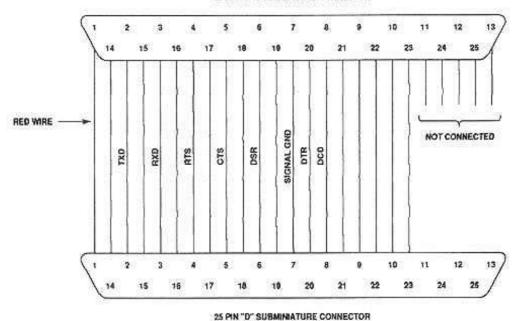

Interconnection of an RS-232C compatible terminal to the EVM is accomplished via a user supplied 20 or 25 conductor flat ribbon cable assembly as shown in Figure 2-2. One end of the cable assembly is connected to the EVM connector J1 (shown below) labeled TERMINAL. The other end of the cable assembly is connected to the user supplied terminal. For connector pin assignments and signal descriptions of the EVM terminal port connector J1, refer to Chapter 5.

TERMINAL

# 2.5.3 Host Computer - EVM Interconnection

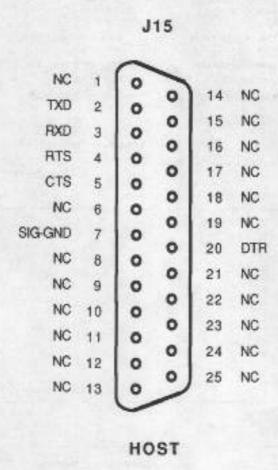

The EVM can be operated with a host computer directly or a remotely located host computer via a modem. Interconnection of an RS-232C compatible host computer to the EVM is accomplished via a user supplied 20 or 25 conductor flat ribbon cable assembly as shown in Figure 2-2. One end of the cable assembly is connected to the EVM connector J15 (shown below) labeled HOST. The other end of the cable assembly is connected to the user supplied host computer or modem. For connector pin assignments and signal descriptions of the EVM host port connector J15, refer to Chapter 5.

#### 25 PIN "D" SUBMINIATURE CONNECTOR

FIGURE 2-2. Terminal or Host Computer Cable Assembly

# 2.5.4 Target System - EVM 28-Pin Interconnection

Target system to EVM interconnection for the MC68HC05P1/P7 operation is accomplished via EVM connector J17, and a user supplied 28-pin dual-in-line plastic (DIP) cable assembly as shown in Figure 2-3. MCU I/O port connector J17 is a 28-pin header (shown below) that facilitate the interconnection of the cable assembly for evaluation purposes. For connector pin assignments and signal descriptions of the EVM connector J17, refer to Chapter 5.

### NOTES:

- HC05P1 = PB5

HC05P7 = PD2 (SDO)

- HC05P1 = PB6

HC05P7 = PD3 (SDI)

- HC05P1 = PB7

HC05P7 = PD4 (SCK)

28-Pin MCU I/O Port Connector (MC68HC05P1/P7)

2-27/2-28

# 2.5.5 Target System - EVM 40-Pin Interconnection

Target system to EVM interconnection for the MC68HC05A6/C2-C4/C8/C9 and MC68HC705C8/805C4 operation is accomplished via EVM connector J19, and a user supplied 40-pin dual-in-line package (DIP) cable assembly as shown in Figure 2-4. Figure 2-5 illustrates the factory supplied 44-lead plastic leaded chip carrier (PLCC) cable assembly. MCU I/O port connector J19 is a 40-pin header (shown below) that facilitate the interconnection of either cable assembly for evaluation purposes. For connector pin assignments and signal descriptions of the EVM connector J19, refer to Chapter 5.

|       |    | J19 |    |         |

|-------|----|-----|----|---------|

| NC    | 40 |     | 1  | RESET   |

| NC    | 39 |     | 2  | ĪRQ"    |

| NC    | 38 |     | 3  | NC      |

| TCAP' | 37 |     | 4  | PA7     |

| PD7   | 36 |     | 5  | PA6     |

| TCMP  | 35 |     | 6  | PA5     |

| PD5   | 34 |     | 7  | PA4     |

| PD4   | 33 |     | 8  | PA3     |

| PD3   | 32 |     | 9  | PA2     |

| PD2   | 31 |     | 10 | PA1     |

| PD1   | 30 |     | 11 | PA0     |

| PD0   | 29 |     | 12 | PB0     |

| PC0   | 28 |     | 13 | PB1     |

| PC1   | 27 |     | 14 | PB2     |

| PC2   | 26 |     | 15 | PB3     |

| PC3   | 25 |     | 16 | PB4     |

| PC4   | 24 |     | 17 | PB5     |

| PC5   | 23 |     | 18 | PB6     |

| PC6   | 22 |     | 19 | PB7     |

| PC7   | 21 |     | 20 | GND-Vss |

40-Pin MCU I/O Port Connector (MC68HC05A6/C2-C4/C8/C9) (MC68HC705C8/805C4)

# 2.5.6 Target System - EVM 60-Pin Interconnection

Target system to EVM interconnection for the MC68HC05B4/B6 and MC68HC805B6 operation is accomplished via EVM connector J20, and a factory supplied 52-lead plastic leaded chip carrier (PLCC) cable assembly as shown in Figure 2-6. MCU I/O port connector J20 is a 60-pin header (shown below) that facilitate the interconnection of the cable assembly for evaluation purposes. For connector pin assignments and signal descriptions of the EVM connector J20, refer to Chapter 5.

|          |    | J20 |    |               |         |    | ~ ^ |    |           |

|----------|----|-----|----|---------------|---------|----|-----|----|-----------|

| TCMP2    | 1  |     | 2  | TCMP1         | PAO     | 31 |     | 32 | PB7       |

| PD7      | 3  |     | 4  | PD6           | PB6     | 33 |     | 34 | PB5       |

| PD5      | 5  |     | 6  | NC            | PB4     | 35 |     | 36 | PB3       |

| VRL      | 7  |     | 8  | VRH           | PB2     | 37 |     | 38 | PB1       |

| PD4      | 9  |     | 10 | NC            | PB0     | 39 |     | 40 | NC        |

| PD3      | 11 |     | 12 | PD2           | Vss-GND | 41 |     | 42 | PC7       |

| PD1      | 13 |     | 14 | PD0           | PC6     | 43 |     | 44 | PC5       |

| NC       | 15 |     | 16 | NC            | PC4     | 45 |     | 46 | PC3       |

| NC       | 17 |     | 18 | RESET'        | PC2     | 47 |     | 48 | PC1       |

| IRQ'     | 19 |     | 20 | PLMA D/A      | PC0     | 49 |     | 50 | RXD (RDI) |

| PLMB D/A | 21 |     | 22 | TCAP1 (TCAP') | SCLK    | 51 |     | 52 | TXD (TDO) |

| TCAP2    | 23 |     | 24 | PA7           | NC      | 53 |     | 54 | NC        |

| PA6      | 25 |     | 26 | PA5           | NC      | 55 |     | 56 | NC        |

| PA4      | 27 |     | 28 | PA3           | NC      | 57 |     | 58 | NC        |

| PA2      | 29 |     | 30 | PA1           | NC      | 59 |     | 60 | NC        |

|          |    |     |    |               |         |    |     |    |           |

60-Pin MCU I/O Port Connector (MC68HC05B4/B6) (MC68HC805B6) PIN 59

A SRI OF 2

A SRI OF 3

TARGET SYSTEM MCU PLUG PLATFORM.

(EMULATION CONNECTOR PLUG., 52-LEAD PLCC TYPE)

FLAT RIBBON CABLE (-)

EVM CONNECTOR (60-PIN SOCKET). 0

60-PIN PLUG, QUICK RELEASE TYPE CONNECTOR.

(1)

60-PIN SOCKET.

NOTES

60-PIN PLUG CONNECTOR (S) MOUNTED ON TOP SIDE OF PLATFORM CONNECTOR REDRAWN TO SIMPLIFY SCHEMATIC DIAGRAM. A

60-PIN CABLE SOCKET (7) CONNECTS TO 60-PIN PLATFORM PLUG CONNECTOR (5) ON TOP SIDE OF PLATFORM.

PLATFORM LAYOUT REDRAWN TO SIMPLIFY SCHEMATIC DIAGRAM. A

REFER TO EVM CONNECTOR J20 ILLUSTRATION FOR SPECIFIC CONNECTOR SIGNAL MNEMONIC.

CABLE ASSEMBLY WIRING IS FABRICATED TO A ONE-TO-ONE RELATIONSHIP (E.G., PRI ) CONNECTED TO PIN 1, PIN 2 CONNECTED TO PIN 2, ETC.). 10

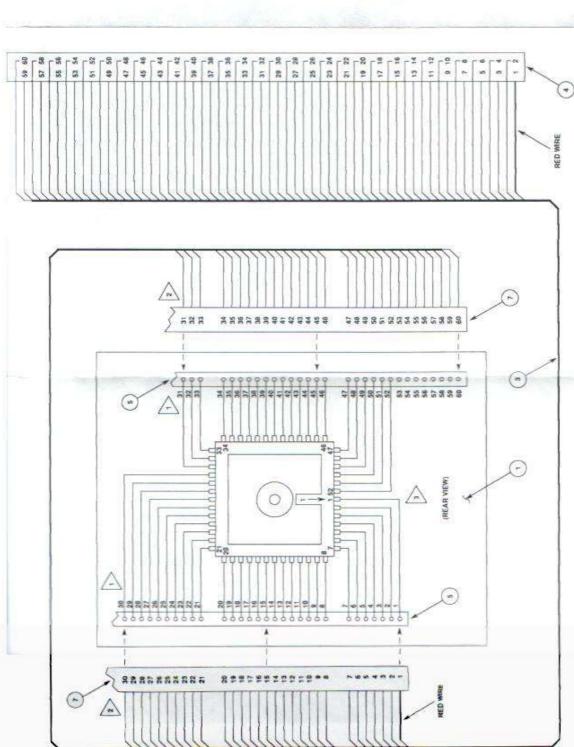

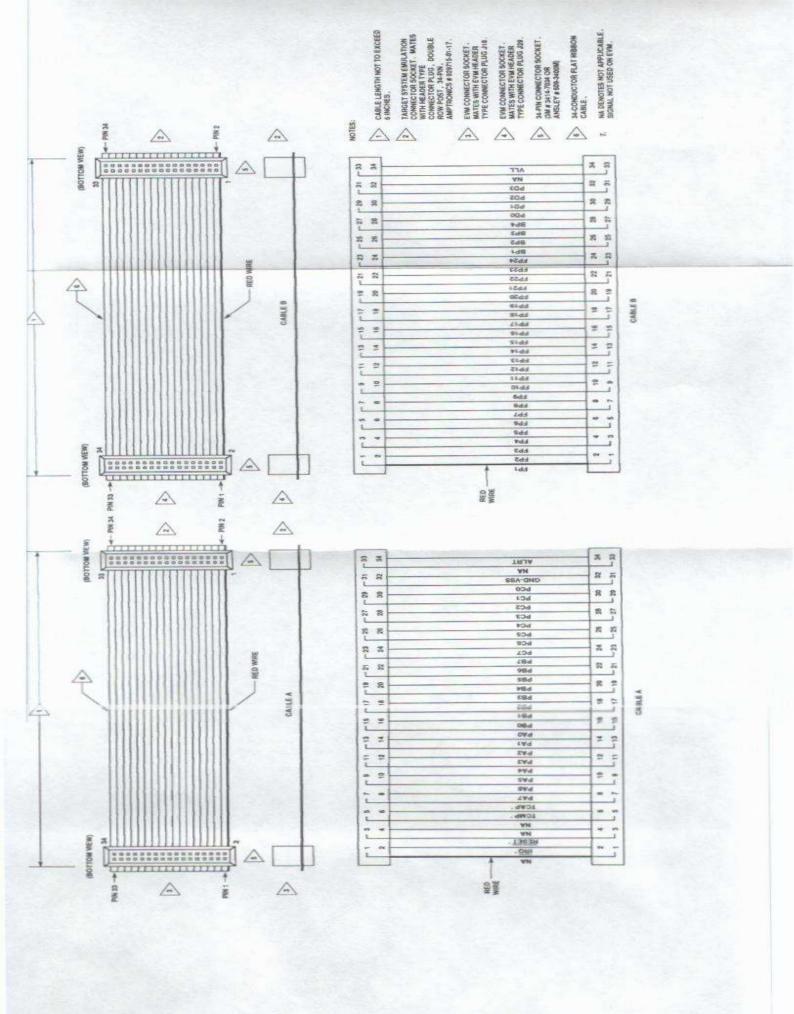

# 2.5.7 Target System - EVM 68-Pin Interconnection

Target system to EVM interconnection for the MC68HC05L6 operation is accomplished via EVM connectors J18 and J29, and user supplied 34-pin header type cable assemblies shown in Figure 2-7. Both MCU I/O port connector A (J18) and connector B (J29) are 34-pin headers (shown below) that facilitate the interconnection of the cable assemblies for evaluation purposes. For connector pin assignments and signal descriptions of EVM connectors J18 and J29, refer to Chapter 5.

|       |    | J18 |    |         |      |    | J29 |    |      |

|-------|----|-----|----|---------|------|----|-----|----|------|

| NC    | 1  |     | 2  | ĪRQ'    | FP1  | 1  |     | 2  | FP2  |

| RESET | 3  |     | 4  | NC      | FP3  | 3  |     | 4  | FP4  |

| NC    | 5  |     | 6  | TCMP'   | FP5  | 5  |     | 6  | FP6  |

| TCAP' | 7  |     | 8  | PA7     | FP7  | 7  |     | 8  | FP8  |

| PA6   | 9  |     | 10 | PA5     | FP9  | 9  |     | 10 | FP10 |

| PA4   | 11 |     | 12 | PA3     | FP11 | 11 |     | 12 | FP12 |

| PA2   | 13 |     | 14 | PA1     | FP13 | 13 |     | 14 | FP14 |

| PAO   | 15 |     | 16 | PB0     | FP15 | 15 |     | 16 | FP16 |

| PB1   | 17 |     | 18 | PB2     | FP17 | 17 |     | 18 | FP18 |

| PB3   | 19 |     | 20 | PB4     | FP19 | 19 |     | 20 | FP20 |

| PB5   | 21 |     | 22 | PB6     | FP21 | 21 |     | 22 | FP22 |

| PB7   | 23 |     | 24 | PC7     | FP23 | 23 |     | 24 | FP24 |

| PC6   | 25 |     | 26 | PC5     | BP4  | 25 |     | 26 | BP3  |

| PC4   | 27 |     | 28 | PC3     | BP2  | 27 |     | 28 | BP1  |

| PC2   | 29 |     | 30 | PC1     | PD0  | 29 |     | 30 | PD1  |

| PC0   | 31 |     | 32 | Vss-GND | PD2  | 31 |     | 32 | PD3  |

| NC    | 33 |     | 34 | ALRT    | NC   | 33 |     | 34 | VLL  |

34-Pin MCU I/O Port Connector A 34-Pin MCU I/O Port Connector B

(MC68HC05L6)

### CHAPTER 3

### OPERATING INSTRUCTIONS

#### 3.1 INTRODUCTION

This chapter provides the necessary information to initialize and operate the EVM in a target system environment. One time programmable read only memory (OTPROM), erasable programmable read only memory (EPROM), and electrically erasable programmable read only memory (EEPROM) MCU programming, assembling/disassembling, and downloading procedures are also provided. Information contained in this chapter will be presented in the following order:

- Control switch descriptions

- b. Limitations

- Operating procedures

- d. MCU programming procedures

- e. Assembling/disassembling procedures

- f. Downloading procedures

The EVM is factory tested for target system evaluation and OTPROM/EPROM/EEPROM MCU programming operations. Refer to paragraph 2.4 COMPONENT IMPLEMENTATION for components required for MC68HC05L6 evaluation, resident MCUs required for specific target system evaluation, and resident MCU and OTPROM/EPROM/EEPROM MCU installation techniques.

The monitor is the resident firmware (EVMbug) for the EVM, which provides a self contained programming and operating environment. The monitor interacts with the user through predefined commands that are entered from a terminal. These commands perform functions such as display or modify memory, display or modify MCU internal registers, program execution under various levels of control, control access to various I/O peripherals connected to the EVM, and control programming and reading of OTPROM/EPROM/EPROM MCUs.

# CONTROL SWITCHES

The EVM contains five switches that allow the user to control specific functions. Switches S1 through S3 control the reset and abort functions. Switches S4 and S5 control the MCU programming power. Table 3-1 identifies these switches by name, description, and function.

TABLE 3-1. EVM Control Switches

| NAME                               | DESCRIPTION AND FUNCTION                                                                                                                                                                                                                                                                                 |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABORT<br>switch (S1)               | Momentary action pushbutton switch - when pressed, returns EVM operation to the monitor map from the user map assuming proper operation of user code. (If MCU gets lost in the user map, the abort is useless and a master reset must be issued.) The abort function has no effect when operating in the |

| USER<br>RESET<br>switch (S2)       | Momentary action pushbutton switch - when pressed, resets EVM MCU and user I/O, and enables map switching to the user map. This switch is used as a map switch for execution of user code from the user reset vector.                                                                                    |

| MASTER<br>RESET<br>switch (S3)     | Momentary action pushbutton switch - when pressed, resets EVM MCU and user I/O, places EVM operation in the monitor map, and enables the EVM prompt to be displayed on terminal CRT.                                                                                                                     |

| Programmer<br>power<br>switch (S4) | On-off slide switch - applies +5 Vdc and +12 Vdc power to the programmable MCU device installed in sockets Z1, Z2, and Z3. Power is applied when the switch is placed in the ON position.                                                                                                                |

| Programmer<br>Vpp<br>switch (S5)   | On-off slide switch - applies programming voltage (Vpp) from connector J28 pin 1 to the programmable MCU device installed in sockets Z1, Z2, and Z3. Vpp is applied when the switch is placed in the ON position.                                                                                        |

### 3.3 LIMITATIONS

The user may not trace an RTI instruction with an interrupt enabled and pending due to MCU interrupt handling. Attempting this will cause an interrupt in the monitor map which will perform a software reset of the EVM. User breakpoints will be left in the user map, but will not be recognized by the monitor. The user stack pointer will also reflect the occurrence of an interrupt.

Mixing interrupt requests (IRQs) and user software interrupts (SWIs) should be avoided whenever possible, due to IRQ-SWI EVM timing. If a concurrent hardware interrupt and SWI should happen, an EVM failure could occur which may stop program execution. Activation of the MASTER RESET switch will restore the EVM to proper operation. These conditions will statistically occur very seldom.

No protection is provided to limit user programs to the exact amount of MCU ROM available. The user must be aware of the memory map of the MCU being simulated and ensure that only valid ROM locations are used.

The baud rates of the terminal and host I/O ports are independent; however, during transparent mode, characters from the host computer to the terminal may occasionally be lost if the terminal baud rate is not higher than the host baud rate. This occurs only during the transparent mode, and does not apply when downloading to memory.

During MC68HC05A6/C2-C4/C8/C9 MCU evaluation, the user should not write to locations \$001E and \$001F. These locations are Computer Operating Properly (COP) and test register locations.

During MC68HC05B4/B6 MCU evaluation, the user should not write to location \$0020. This location is a test register location for factory use only.

Programming and bulk erase operations cannot be performed on MC68HC805C4 MCU A65G mask sets, but blank checking, copying, and verifying can be performed.

The EVM cannot emulate the low power capabilities of the MC68HCL05C4/C8 MCU devices. The EVM can emulate the high speed capabilities of the MC68HSC05C4/C8 MCU devices by the replacement of the 8 MHz crystal (Y1) to a 16 MHz crystal. Refer to paragraph 2.3.10.

(Specific resident MCU operational limitations are provided on the following page.)

# Resident MC68HC05C9 MCU Operational Limitations

The MC68HC05C9 MCU option register resides internally at location \$3FDF. Therefore, when evaluating other HC05xx family devices with option registers residing at \$1FDF, all accesses to the resident HC05C9 MCU option register must be made at \$3FDF as opposed to \$1FDF even though the 8K memory map is selected.

The HC05C9 MCU cannot be used to exactly replicate SPI operations for all HC05Cx MCU devices.

The HC05C9 MCU DDRD has a negative implication affecting serial peripheral interface (SPI) operations. All port D lines used as output lines must have corresponding DDR bits set to a logic 1 (i.e., SCK (master), MOSI (master), MISO (slave)) when evaluating all HC05Cx MCU devices.

The HC05C9 MCU contains a port D data direction register (DDRD) that can be used to emulate the MC68HC05P1 and MC68HC05P7 MCU port D, bit 5 (PD5). The user must be aware that the entire DDRD is implemented and other DDRD bits must not be accidently written to. When evaluating HC05P1 and HC05P7 devices with the resident HC05C9 MCU, the user must write \$20 value to DDRD location \$07 when configuring PDDR5 as an output line. This step will ensure that other port D pins remain as input lines as required for correct HC05P1 and HC05P7 evaluation.

# Resident MC68HC705C8 MCU Operational Limitations

When evaluating with a resident MC68HC705C8 MCU the option register is accessed at location \$1FDF. The HC705C8 option registers must be written to if edge-only interrupts are to be used. The HC705C8 option register contains RAM/ROM bits used for dynamic mapping of internal RAM/ROM.

The HC705C8 MCU can be used to exactly replicate SPI operations for all HC05Cx MCU devices.

# Resident MC68HC805C4 MCU Operational Limitations

When evaluating with a resident MC68HC805C4 MCU the option register is accessed at location \$1FDF. The HC805C4 option register must be written to if edge-only interrupts are to be used. The HC805C4 option register only configures IRQ options.

The HC805C4 MCU can be used to exactly replicate SPI operations for all HC05Cx MCU devices.

### 3.4 OPERATING PROCEDURE

Applying power to the EVM causes a Power On Reset (POR) to occur. This POR condition causes the MCU and user I/O port circuitry to be reset, and the monitor invoked. All user registers are in an unknown state during monitor power-up.

A fixed 9600 baud rate is provided for the terminal port, and a software selectable 300-19.2K baud rate selection is provided for the host port. The monitor automatically configures the baud rate setting for the host I/O port. The default baud rate for the host I/O port is 9600 baud. The host I/O port baud rate can be reconfigured via the SPEED command.

The terminal Cathode Ray Tube (CRT) displays the following message:

where:

X is a revision of the software or an unknown register state.

Condition code register (CCR) HINZC bits are as follows:

- 1 = Fixed bit, set to logic 1

1 = Fixed bit, set to logic 1

1 = Fixed bit, set to logic 1

H = Half carry bit

- I = Interrupt mask bit N = Negative bit

- Z = Zero bit

- C = Carry/borrow bit

When all CCR bits are set (logic 1), bits are displayed as follows:

S=XX

P=XXXX

A=XX

X=XX

C=FF

111HINZC

When all CCR bits are cleared (logic 0), bits are displayed as follows:

S=XX

P=XXXX

A = XX

X=XX

C=E0

111....

When a specific bit is set (I), bits are displayed as follows:

S=XX

P = XXXX

A=XX

X = XX

C=E8

111.I...

When specific bits are set (H, I, and C), bits are displayed as follows:

S=XX

P=XXXX

A=XX

X=XX

C=F9

111HI..C

After initialization or return of control to the monitor, the terminal CRT displays the prompt " > " and waits for a response. If an invalid response is entered, the terminal CRT displays "ILLEGAL/INSUFFICIENT ENTRY" followed by the prompt " > ".

The EVM waits for a command line input from the user terminal. When a proper command is entered, the operation continues in one of two basic modes. If the command causes execution of a user program, the monitor may or may not be reentered, depending upon the desire of the user. For the alternate case, the command is executed under the control of the monitor, and the system returns to a waiting condition after the command is completed. During command execution, additional user input may be required, depending on the command function.

The user can use any of the commands supported by the monitor. A standard input routine controls the EVM operation while the user types a command line. Command processing begins only after the command line has been terminated by depressing the keyboard carriage return (RETURN) key.

#### 3.5 COMMAND LINE FORMAT

The command line format is as follows:

><command> [<parameters>](RETURN)

where:

> EVMbug monitor prompt.

<command> Command mnemonic.

<parameters> Expression or address.

(RETURN) RETURN keyboard key - depressed to enter command.

#### NOTES:

- (1) The command line format is defined using special characters which have the following syntactical meanings:

- <> Enclose syntactical variable

- [] Enclose optional fields

- []... Enclose optional fields repeated

These characters are not entered by the user, but are for definition purposes only.

- (2) Fields are separated by a single space.

- (3) All input numbers are interpreted as hexadecimal. A dollar sign (\$) may precede any number input, but is not required.

- (4) All input commands can be entered either upper or lower case lettering. All input commands are converted automatically to upper case lettering except for downloading commands sent to the host computer, or when operating in the transparent mode.

- (5) A maximum of 30 characters may be entered on a command line. After the 30th character is entered, the monitor automatically terminates the command entry and processes the command line.

- (6) Parameters are interpreted to be the last two or three characters in the parameter file. Parameter errors may be corrected by backspacing. This is accomplished via the terminal keyboard (CTRL)H function.

#### 3.6 MONITOR (EVMbug) COMMANDS

The monitor (EVMbug) commands are listed alphabetically by mnemonic in Table 3-2. Each of the commands are described in detail following the tabular command listing.

Additional terminal keyboard functions are as follows:

(BREAK) Abort command

(CTRL)A Default transparent mode exit character

(CTRL)H Backspace

(CTRL)S Freeze screen

(CTRL)X Cancel command line

(RETURN) Enter command

#### NOTE

When using the control key with a specialized command such as (CTRL)X, the (CTRL) key is depressed and held, then the X key is depressed. Both keys are then released.

During memory display output to terminal, (CTRL)S will delay the output until another character is entered.

Command line input examples in this chapter are amplified with the following:

Underscore entries are user-entered on the terminal keyboard.

Command line input is entered when the keyboard (RETURN) key is depressed.

Typical example of this explanation is as follows:

>MD 100 21F

TABLE 3-2. Monitor (EVMbug) Commands

| COMMAND                                                   | DESCRIPTION                          |  |  |

|-----------------------------------------------------------|--------------------------------------|--|--|

| ASM <address></address>                                   | Assembler/disassembler (interactive) |  |  |

| BF <addr1> <addr2> <data></data></addr2></addr1>          | Block fill memory with data          |  |  |

| BR [ <address>]</address>                                 | Breakpoint set                       |  |  |

| BULK <device></device>                                    | Bulk erase EEPROM                    |  |  |

| CHCK [ <addr1> <addr2>] <device></device></addr2></addr1> | Blank check OTPROM/EPROM/EEPROM      |  |  |

| COPY [ <addr1> <addr2>] <device></device></addr2></addr1> | Copy OTPROM/EPROM/EEPROM             |  |  |

| G [ <address>]</address>                                  | Go (execute program)                 |  |  |

| HELP                                                      | Help (display commands)              |  |  |

| LOAD <port> [=<text>]</text></port>                       | Load (S-records*) from I/O port      |  |  |

| MD <addr1> [<addr2>]</addr2></addr1>                      | Memory display                       |  |  |

| MM <address></address>                                    | Memory modify (interactive)          |  |  |

| NOBR [ <address>]</address>                               | Remove breakpoint                    |  |  |

| P [ <count>]</count>                                      | Proceed (thru breakpoint)            |  |  |

| PROG [ <addr1> <addr2>] <device></device></addr2></addr1> | Program OTPROMEPROMEEPROM            |  |  |

| RD                                                        | Register display                     |  |  |

| RM                                                        | Register modify (interactive)        |  |  |

| SPEED <baud rate=""></baud>                               | Host I/O port baud rate select       |  |  |

| T ( <count>)</count>                                      | Trace                                |  |  |

| TM ( <exit character="">)</exit>                          | Transparent mode                     |  |  |

| VERF [ <addr1> <addr2>] <device></device></addr2></addr1> | Verify OTPROMEPROMEEPROM             |  |  |

### 3.6.1 Assembler/Disassembler

ASM <address>

where <address> is the starting address for the assembler operation.

The assembler/disassembler is an interactive assembler/editor in which the source program is not saved. Each source line is converted into the proper machine language code and is stored in memory on a line-by-line basis at the time of entry. In order to display an instruction, the machine code is disassembled and the instruction mnemonic and operands are displayed. All valid opcodes are converted to assembly language mnemonic. All invalid opcodes return a Form Constant Byte (FCB) conversion.

The ASM command allows the user to create, modify, and debug MC6805 MCU code. No provision is made for line numbers or labels.

Assembler input must have exactly one space between the mnemonic and the operand. There must be no space between the operand and the index specification (,X) except in the case of indexed no offset. Assembler input must be terminated by a carriage return. No comments, etc., are allowed after the instruction input. Examples are as follows:

- a. >LDA 0.X

- b. >STA 10.X

- C. >ASRA

- d. >COMX

- θ. >CMP 200

After each new assembler input line, the new line is disassembled for the user before stepping to the new instruction. The new line may assemble to a different number of bytes than the previous one.

For Branch if High or Same (BHS)/Branch if Carry Clear (BCC) mnemonics, disassembly displays the BCC mnemonic. For Branch if Lower (BLO)/ Branch if Carry Set (BCS) mnemonics, disassembly displays the BCS mnemonic.

Branch address offsets are automatically calculated by the assembler, thus the address is inputted as the operand rather than an offset value.