## **EPIC: An Architecture for Instruction-Level Parallel Processors**

Michael S. Schlansker, B. Ramakrishna Rau Compiler and Architecture Research HP Laboratories Palo Alto HPL-1999-111 February, 2000

E-mail:{schlansk, rau}@hpl.hp.com

EPIC architecture, VLIW architecture. instruction-level parallelism, MultiOp, nonunit assumed latencies, NUAL, rotating register files. unbundled branches. control speculation, speculative opcodes, exception tag, predicated execution, fully-resolved predicates, wired-OR and wired-AND compare opcodes, prioritized loads and stores, data speculation, cache specifiers, precise interrupts, NUAL-freeze and NUALdrain semantics, delay buffers, replay buffers, EQ and LEQ semantics, latency stalling, MultiOp-P and MultiOp-S semantics. dynamic translation, MultiTemplate and VariOp instruction formats, history of EPIC

Over the past two and a half decades, the computer industry has grown accustomed to, and has come to take for granted, the spectacular rate of increase of microprocessor performance, all of this without requiring a fundamental rewriting of the program in a parallel form, without using a different algorithm or language, and often without even recompiling the program. The continuation of this trend is the topic of discussion of this report. For the time being at least, instruction-level parallel processing has established itself as the only viable approach for achieving the goal of providing continuously increasing performance without having to fundamentally re-write applications. In this report, we introduce the Explicitly Parallel Instruction Computing (EPIC) style of architecture which was developed, starting eleven years ago, to enable higher levels of instruction-level parallelism without unacceptable hardware complexity. We explain the philosophy underlying EPIC as well as the challenges faced as a result of adopting this philosophy. We also describe and discuss the set of architectural features that together characterize the EPIC style of architecture, and which can be selectively included in some specific instance of an EPIC instruction set architecture.

# **1** Introduction

Over the past two and a half decades, the computer industry has grown accustomed to, and has come to take for granted, a spectacular rate of increase in microprocessor performance, all of this without requiring a fundamental rewriting of the program in a parallel form, without using a different algorithm or language, and often without even recompiling the program. The benefits of this have been enormous. Computer users have been able to take advantage of of faster and faster computers while still having access to applications representing billions of dollars worth of investment. This would be impossible if software had to be continually re-written to take advantage of newer and faster computers. Continuing this trend, of ever-increasing levels of performance without re-writing the applications, is the topic of discussion of this report.

Higher levels of performance benefit from improvements in semiconductor technology which permit shorter gate delays and higher levels of integration, both of which enable the construction of faster computer systems. Further speedups must come, primarily, from the use of some form of parallelism. Instruction-level parallelism (ILP) results from a set of processor and compiler design techniques that speed up execution by causing individual RISC-style machine operations, such as memory loads and stores, integer additions and floating point multiplications, to execute in parallel. ILP systems are given a conventional high-level language program written for sequential processors and use compiler technology and hardware to automatically exploit program parallelism. Thus an important feature of these techniques is that like circuit speed improvements, but unlike traditional multiprocessor parallelism and massively parallel processing, they are largely transparent to application programmers. In the long run, it is clear that the multiprocessor style of parallel processing will be an important technology for the main stream computer industry. For the present, instruction-level parallel processing has established itself as the only viable approach for achieving the goal of providing continuously increasing performance without having to fundamentally re-write applications. It is worth noting that these two styles of parallel processing are not mutually exclusive; the most effective multiprocessor systems will probably be built using the most effective ILP processors.

A computer architecture is a contract between the class of programs that are written for the architecture and the set of processor implementations of that architecture. Usually this contract is concerned with the instruction format and the interpretation of the bits that constitute an instruction, but in the case of ILP architectures it can extend to information

embedded in the program pertaining to the available parallelism between the instructions or operations in the program. The two most important types of ILP processors, to date, differ in this respect.

- **Superscalar** processors [1] are ILP processor implementations for sequential architectures—architectures for which the program is not expected to convey and, in fact, cannot convey any explicit information regarding parallelism. Since the program contains no explicit information regarding the ILP available in the program, if this ILP is to be employed, it must be discovered by the hardware, which must then also construct a plan of action for exploiting the parallelism.

- Very Long Instruction Word (VLIW) processors [2, 3] are examples of architectures for which the program provides explicit information regarding parallelism<sup>1</sup>. The compiler identifies the parallelism in the program and communicates it to the hardware by specifying which operations are independent of one another. This information is of direct value to the hardware, since it knows with no further checking which operations it can start executing in the same cycle.

In this report, we introduce the **Explicitly Parallel Instruction Computing (EPIC)** style of architecture, an evolution of VLIW which has absorbed many of the best ideas of superscalar processors, albeit in a form adapted to the EPIC philosophy. EPIC is not so much an architecture as it is a philosophy of how to build ILP processors along with a set of architectural features that support this philosophy. In this sense EPIC is like RISC; it denotes a class of architectures, all of which subscribe to a common architectural philosophy. Just as there are many distinct RISC architectures (Hewlett-Packard's PA-RISC, Silicon Graphic's MIPS and Sun's SPARC) there can be more than one instruction set architecture (ISA) within the EPIC fold. Depending on which features are picked from EPIC's repertoire of features, an EPIC ISA can be optimized for domains as distinct as general-purpose computing or embedded computing. The EPIC work has been motivated by both domains of computing. In general, any specific ISA that subscribes to the EPIC philosophy will select the subset of EPIC features needed in that ISA's domain of application—no one EPIC ISA need possess all of the features. Furthermore, each specific EPIC ISA will, typically, have additional features which differentiate it from another EPIC ISA targeted at the same domain.

<sup>&</sup>lt;sup>1</sup> Corporaal's book [4], though focused primarily on transport-triggered architectures, provides an excellent, indepth treatment of many issues relevant to VLIW processors.

The first instance of a commercially available EPIC ISA will be Intel's IA-64 [5]. However, the IA-64 is not the topic of our discussion. Rather, we shall focus our discussion upon the broader concept of EPIC as embodied by HPL-PD [6, 7] which encompasses a large space of possible EPIC ISA's. HPL-PD, which was defined at Hewlett-Packard Laboratories in order to facilitate EPIC architecture and compiler research, is more appropriate for our purposes since it abstracts away from the idiosyncratic features of a specific ISA and concentrates, instead, upon the essence of the EPIC philosophy.

In the rest of this section we outline the considerations that led to the development of EPIC, the key tenets of the EPIC philosophy, as well as the primary challenges that this philosophy must face. In Sections 2 through 4, we discuss the various architectural features that were developed in support of the EPIC philosophy. We start off with somewhat of a purist's viewpoint, motivating and explaining these features without regard to the three challenges listed above. Then, in Sections 5 through 7 we describe the mechanisms and strategies provided in order to address these three challenges. This enables us, in Section 8, to look at how the domain of application of an EPIC ISA specifies the relevance of the three challenges and, consequently, determines the relative importance of the various EPIC features. Section 9 discusses the history of EPIC and its intellectual antecedents. We make some concluding observations in Section 10.

#### 1.1 The motivation behind EPIC

HP Labs' EPIC research program was started by the authors early in 1989<sup>2</sup> at a time when superscalar processors were just gaining favor as the means to achieve ILP. However, as a research activity which we knew would take a number of years to influence product design, we felt that it was important to look five to ten years into the future to understand the technological obstacles and opportunities that would exist in that time frame. We came to two conclusions, one obvious, the other quite controversial (at least at that time). Firstly, it was quite evident from Moore's Law<sup>3</sup> that by 1998 or thereabouts it would be possible to fit an entire ILP processor, with a high level of parallelism, on a single die. Secondly, we believed that the ever increasing complexity of superscalar processors would have a

<sup>&</sup>lt;sup>2</sup> However, the name EPIC was coined later, in 1997, by the HP-Intel alliance.

<sup>&</sup>lt;sup>3</sup> Moore's Law states that the number of transistors, on a semiconductor die, doubles every eighteen to twenty four months. This prediction has held true since 1965, when Gordon Moore first articulated it.

negative impact upon their clock rate, eventually leading to a leveling off of the rate of increase in microprocessor performance<sup>4</sup>.

Although the latter claim is one that is contested even today by proponents of the superscalar approach, it was, nevertheless, what we belived back in 1989. And it was this conviction that gave us the impetus to look for an alternate style of architecture that would permit high levels of ILP with reduced hardware complexity. In particular, we wished to avoid having to resort to the use of out-of-order execution, an elegant but complex technique for achieving ILP that was first implemented commercially in the IBM System/360 Model 91 [8] and which is almost universally employed by all high-end superscalar microprocessors today. The VLIW style of architecture, as represented by Multiflow's and Cydrome's products [2, 3], addressed the issue of achieving high levels of ILP with reduced hardware complexity. However, these machines were specialized for numerical computing and had shortcomings with respect to scalar applications, i.e., applications that are branch-intensive and characterized by pointer-based memory accesses. It was clear to us that this new style of architecture would need to be truely generalpurpose—capable of achieving high levels of ILP on both numerical and scalar applications. In addition, existing VLIWs did not provide adequate object code compatibility across an evolving family of processors as would be required for a generalpurpose processor.

The code for a superscalar processor consists of a sequence of instructions which, if executed in the stated order, will yield the desired result. It is strictly an algorithm, and except for the fact that it uses a particular instruction repertoire, it has no explicit understanding of the nature of the hardware upon which it will execute or, the precise temporal order in which the instructions will be executed. In contrast, the code for a VLIW processor reflects an explicit plan for how the program will be executed. This plan is created statically, i.e., at compile-time. This plan specifies when each operation will be executed, using which functional units, and with which registers as its operands. We shall refer to this as the **plan of execution (POE)**. The VLIW compiler designs the POE, with full knowledge of the VLIW processor, so as to achieve a desired **record of execution** (**ROE**), i.e., the sequence of events that actually transpire during execution. The POE is communicated, via an instruction set architecture that can represent parallelism explicitly,

<sup>&</sup>lt;sup>4</sup> Although we shall find occasion to compare EPIC to superscalar in order to illustrate certain points, the purpose of this report is not to try to establish that EPIC is superior to superscalar. Nor is it to defend EPIC. Rather, it is to explain the chain of reasoning that has led to EPIC.

to hardware which then executes the specified plan. The existence of this plan permits the VLIW processor to have relatively simple hardware despite high levels of ILP.

A superscalar processor takes the sequential code and dynamically engineers a POE. While this adds hardware complexity; it also permits the superscalar processor to engineer a POE which takes advantage of various factors which can only be determined at run-time.

## **1.2 The EPIC philosophy**

One of our goals for EPIC was to retain VLIW's philosophy of statically constructing the POE, but to augment it with features, akin to those in a superscalar processor, that would permit it to better cope with these dynamic factors. The EPIC philosophy has the following key aspects to it.

**Providing the ability to design the desired POE at compile-time.** The EPIC philosophy places the burden of designing the POE upon the compiler. The processor's architecture and implementation can either assist or obstruct the compiler in performing this task. EPIC processors provide features that actively assist the compiler in successfully designing the POE.

A basic requirement is that the run-time behavior of EPIC processors be predictable and controllable from the compiler's viewpoint. Dynamic scheduling, and especially out-of-order execution, obfuscate the compiler's understanding of how its decisions will affect the actual ROE constructed by the processor; the compiler has to second-guess the processor, which complicates its task. An "obedient" processor, that does exactly what the program instructs it to do, is preferable.

The essence of engineering a POE at compile-time is to re-order the original sequential code to take best advantage of the application's parallelism and make best use of the hardware resources, thereby minimizing the execution time. Without suitable architectural support, re-ordering can violate program correctness. One example is when the relative order of a branch and an operation that it guards are exchanged in order to reduce the execution time. A requirement of EPIC's philosophy of placing the burden of designing the POE upon the compiler is a commitment to provide architectural features that support extensive code reordering at compile-time.

**Providing features that permit the compiler to "play the statistics".** An EPIC compiler is faced with a major problem in constructing the POE at compile-time which is

that certain types of information that necessarily affect the ROE can only be known for sure at run-time. Firstly, the compiler cannot know for sure which way a conditional branch will go and, in certain cases, it cannot even know for sure what the target of the branch will be. Secondly, when scheduling code across multiple basic blocks in a control flow graph, the compiler cannot know for sure which control-flow path is taken. It is often imposible to jointly optimize an operation's schedule over all paths through the control flow graph when it is dependent upon operations in multiple preceeding basic blocks or when operations in multiple successor blocks depend upon it. The operation is scheduled conservatively so as to accommodate all such paths. Likewise, a conservative view must be taken of which resources might be in use when operations overlap branches within such a control flow graph. A third source of ambiguity, which can often only be resolved at run-time is whether two memory references are to the same location. If they are, they need to be sequentialized. If not, they can be scheduled in any order. The fourth source of compiletime ambiguity concerns the non-deterministic latency of certain operations, which can affect the schedule profoundly. For memory loads, the ambiguity arises from not knowing, for instance, at what level in the cache hierarchy the data will be found.

In the worst case, there is little that can be done other than to react to these ambiguities at run-time, once the information is known. Very often, however, the situation is quite a bit better. Although we may not know for sure at compile-time what will happen, it is often the case that there is a very strong probability of a particular outcome. An important part of the EPIC philosophy is for the compiler to play the odds under such circumstances. The POE is constructed, and optimized for, the likely case. However, architectural support—such as control and data speculation, which we discuss later—must be provided to ensure the correctness of the program's semantics even when the guess is incorrect. When the gamble does not pay off, a performance penalty is incurred, but these occasions should be infrequent. For instance, the penalty may be visible in the program schedule when a branch diverts control flow away from optimized code for the frequent case to compensation code which ensures correctness in the less likely, non-optimized case. Alternatively, the penalty may be reflected in stall cycles, which are not visible in the program schedule; certain operations may execute at full performance for the likely, optimized case but might stall the processor to ensure correctness for the less likely, non-optimized case.

**Providing the ability to communicate the POE to the hardware.** Having designed a POE, the compiler needs to be able to communicate it to the hardware. In order to do so, the ISA must be rich enough to express the compiler's decisions as to when each operation is to be issued and which resources are to be used. In particular, it should be

possible to specify which operations are to issue simultaneously. The alternative would be to create a sequential program which is presented to the processor and re-organized by it dynamically in order to yield the desired ROE. But this defeats EPIC's goal of relieving the hardware of the burden of dynamic scheduling.

In addition to communicating such information to the hardware, it is important to do so at the appropriate time. A case in point is the branch operation which, if it is going to be taken, requires that instructions start being fetched from the branch target well in advance of the branch being issued. Rather than providing branch target buffer hardware [9] to deduce when to do so and what the target address is, the EPIC philosophy is to provide this information to the hardware, explicitly and at the correct time, via the code.

There are other decisions made by the micro-architecture that are not directly concerned with the execution of the code, but which do affect the execution time. One example is the management of the cache hierarchy and the associated decisions of what data to promote up the hierarchy and what to replace. The relevant policies are typically built into the cache hardware. EPIC extends its philosophy, of having the compiler orchestrate the ROE, to having it also manage these other micro-architectural mechanisms. To this end, EPIC provides architectural features that permit programmatic control of these mechanisms which normally are controlled by the micro-architecture.

# **1.3 Challenges faced by the EPIC philosophy**

EPIC has evolved from, and subsumes, VLIW which has been associated with certain limitations. The importance of these limitations depends upon the domain of application of the ISA and is quite different depending on whether the domain is, for instance, generalpurpose processing or embedded digital signal processing. The three issues discussed below are the most frequently raised concerns. We believed it was necessary for EPIC to provide a strategy for dealing with each of them in order for EPIC to be suitable for use in those domains where the issues are important.

**Interruptions.** We shall use the term **interruption** to refer to the entire class of events that cause a program's execution to be paused, for it to be swapped out, and then resumed after some interruption handler has been executed. Interruptions include events external to the program, such as interrupts, as well as **exceptions**, a term we shall use to collectively refer to events caused by the execution of the program, such as divide by zero exceptions or page faults. The problem in common is that the schedule created by the compiler is

disrupted by the interruption; the schedule is torn apart, as it were, at the point in the program that the interruption is fielded. The properties of the EPIC hardware along with the compiler's conventions must together ensure that the POE allows this disruption while maintaining correct program semantics.

**Object code compatibility.** Object code compatibility is the ability to take code that was compiled for one particular processor within a family of processor implementations having the same ISA, and to be able to execute it on any other member of that family. This poses two main challenges for a family of EPIC processors. One is that the operation latencies that were assumed by the compiler may not be correct for the processor in question. The second one is that the assumed and actual parallelism of the processor, in terms of the number of function units, may not match.

Compatibility is made more difficult by the use of shared libraries, especially in a network setting. The various executables may have been compiled with different members of the processor family in mind, but are now to be executed by a single processor which must switch dynamically between modules compiled with different assumptions regarding the processor.

**Code size.** A defining feature of EPIC is the ability to specify multiple operations within one wide instruction. This is how the compiler explicitly specifies the parallel POE that it has devised. The instruction format must be wide enough to be able to express the maximum parallelism of which the processor is capable. But when the parallelism in the program is unable to sustain this level of parallelism, no-ops need to be specified, leading to wasted code space.

EPIC processors require efficient static schedules for branch-intensive loop and scalar programs. Techniques for generating efficient static schedules often require code replication which can dramatically increase code size. For example, when efficient static schedules are developed for innermost loops with embedded conditionals, the need to overlap conditionals from adjacent loop iterations may require the generation of static schedules which replicate code for many possible dynamic paths through consecutive then- and else-clauses. EPIC provides features which reduce the need to replicate code even when highly overlapped static schedules are required for efficient execution.

# **2** Basic features to support static scheduling

EPIC's most basic features are directly inherited from VLIW and are concerned with the fundamental requirements of being able to create a POE statically and communicate it to the hardware. The two characteristics that are most strongly associated with VLIW are the ability to specify multiple operations per instruction and the notion of architecturally exposed latencies, often of non-unit length.

## 2.1 Multiple operations per instruction (MultiOp)

**MultiOp** is the ability to specify a set of operations that are intended to be issued simultaneously, where each operation is the equivalent of an instruction of a conventional sequential processor. We shall refer to such a set of operations as a MultiOp instruction. In addition, each MultiOp instruction has a notion of time associated with it; exactly one instruction is issued per cycle of the **virtual time** which serves as the temporal framework within which the POE is created<sup>5</sup>. Virtual time differs from actual time when run-time stalls, that the compiler did not anticipate, are inserted by the hardware at run-time. Together, these two attributes of MultiOp are the primary mechanisms by which an EPIC compiler is able to communicate the statically designed POE to the EPIC processor.

In constructing a POE, the compiler must be fully aware of the number of resources of each type available in the processor and, in order to be sure that it has a viable plan, it must perform resource allocation to ensure that no resource is over-subscribed. Given that it has already done so, the EPIC philosophy is to communicate these decisions to the hardware via the code so that the hardware need not re-create the resource allocation at run-time. One way of achieving this is by using a positional instruction format, i.e., the position of an operation within the MultiOp instruction specifies the functional unit upon which it will execute. Alternatively, this information can be specified as part of each operation's opcode.

## 2.2 Architecturally visible latencies

The execution semantics for traditional sequential architectures are defined as a sequence of atomic operations; conceptually, each operation completes before a subsequent operation begins, and the architecture does not entertain the possibility of one operation's register

$<sup>^{5}</sup>$  Herein lies an important distinction between EPIC code and conventional sequential code. An EPIC program constitutes a temporal plan for executing the application, whereas sequential code is merely a step-by-step algorithm.

reads and writes being interleaved in time with those of other operations. With MultiOp, operations are no longer atomic. When the operations within a single MultiOp instruction are executed, they all read their inputs before any of them writes their results. Thus, the non-atomicity of operations, and their latencies, are already exposed architecturally. Moreover, in reality, operations often take multiple cycles to execute. An ILP implementation of a sequential architecture must cope with the non-atomicity of its operations, in practice, while ensuring the very same semantics as if the operations really were atomic. This leads to many of the hardware complexities of a superscalar processor.

To avoid these complexities, EPIC does away with the architectural notion of atomic operations and recognizes that the read and write events of an operation are separated in time. It is these read and write events that are viewed as the atomic events. The semantics of an EPIC program are determined by the relative ordering of the read and write events of all the operations. By raising the micro-architectural reality to the level of the architecture, the semantic gap between the architecture and the implementation is closed, eliminating the need, as required in the superscalar processor, to project an illusion (of atomic operations) that does not really exist. The primary motivation for architecturally non-atomic operations is hardware simplicity in the face of operations that, in reality, take more than one cycle to complete. If the hardware can be certain that no attempt will be made to use a result before it has been produced, the hardware need have no interlocks and no stall capability. If, in addition, the compiler can be certain that an operation will not write its result before its assumed latency has elapsed, tighter schedules can be crafted; the successor operation in an anti- or output dependence relationship can be scheduled earlier by an amount equal to its latency.

Assumed latencies serve as the contractual guarantee, between the compiler and the hardware, that these assumptions will be honored on both sides. With EPIC assumed latencies are part of the overall architectural contract between the processor and the compiler. The concept of virtual time, built into an EPIC program, is central to the provision of this guarantee. Recall that (the issuance of) each instruction in EPIC represents a unit of virtual time. This enables the compiler and the hardware to have a common notion of time, and it is within this temporal framework that the compiler and the hardware are able to create this contractual guarantee. Conventional architectures, having no such notion of time, are unable to do so.

A non-atomic operation which has at least one result with an architecturally assumed latency that is greater than one cycle is termed a **non-unit assumed latency** (**NUAL**)

operation. A non-atomic operation which has an architecturally assumed latencies of one cycle for all of its results is termed a **unit assumed latency** (**UAL**) operation. NUAL operations can possess **differential latencies**, where each source and destination operand can have a different sample and write time, respectively, relative to the time of issue of the operation [10, 11]. For instance, this might occur in a multiply-add operation of the form  $(a \times b)+c$  which computes the product of a and b before reading c and performing a final sum<sup>6</sup>.

Assumed latencies can be specified as constants implicitly agreed upon by the EPIC compiler and the EPIC processor. Or, they may be specified dynamically by the program prior to or during execution. This can be done in a number of different ways, each representing a different trade-off between cost and generality [6]. The hardware then uses the assumed latency specification to ensure correct program interpretation.

When the actual latencies are really not one cycle, UAL represents the extreme case of assumed latencies differing from actual latencies. Although this leads to some of the same problems that one faces with atomic operations, there is one important benefit. If all the operations in an ISA are UAL, these constant assumed latencies need not be specified, and all software is correctly interpreted using the same unit latency assumptions. This eliminates the need to attend to the troublesome case of an operation's assumed latency spanning a transfer of control between functions. It can also greatly simplify matters in a system environment where applications make use of shared and dynamically linked libraries which may have been compiled with different members of the processor family in mind. When all members of an architectural family use identical (e.g. unit) assumed latencies, this problem is eliminated.

We shall refer to two other types of latencies which should not be confused with the assumed latencies defined above. The **actual latency** is the true latency of the operation in the processor under consideration, which can be either greater or less than the assumed latency. It is the hardware's burden to ensure correct program semantics if actual latencies are different from assumed latencies (see Section 6.1.1). The **compiler latency** is the latency used by the compiler during scheduling and register allocation. The compiler latency is the specifies an appropriate distance between an operation and a dependent successor,

$<sup>^{6}</sup>$  Differential input latencies complicate the discussion pertaining to compatibility and the handling of interruptions. In order to simplify the exposition, we assume hereafter that all inputs are sampled during the cycle of issue.

used by the compiler, to optimize the program. If not the same as the assumed latency, it is the compiler's responsibility to ensure that program semantics are preserved by erring on the conservative side; the scheduler must use a compiler latency that is greater than or equal to the assumed latency, whereas the register allocator must assume a latency that is less than or equal to the assumed latency. The assumed latencies serve as the contractual interface between the compiler and the hardware, allowing compiler and actual latencies to be different without compromising the correctness of execution.

The compiler may wish to knowingly schedule to latencies that are quite different from the actual hardware latencies. For example, in the face of non-deterministic actual load latencies, load operations on the critical path may use a short compiler latency to expedite the critical path, while loads which are off the critical path may use a longer assumed latency to better overlap cache misses with further processing.

**Scheduling benefits**. MultiOp instructions take immediate advantage of non-atomicity, even in the case of UAL operations. Since an operation takes at least one cycle to execute, its result will not be written prior to all the operations, that were issued in the same instruction, having read their inputs<sup>7</sup>. Therefore, operations with anti-dependences can be scheduled in the same instruction, yielding shorter schedules. It is even possible for two operations in the same instruction to be anti-dependent upon each other, as in the case of a register exchange implemented as two copy operations, each of which writes to the other's source register.

Often, operations take multiple cycles to complete. The EPIC compiler must understand these latencies in order to achieve correct and high quality schedules. For best results, it must understand exactly when an operation reads its inputs and writes its outputs, relative to the time of issue of the operation. Given that this is the case, the compiler can benefit from this knowledge by taking advantage of the fact that the old value in each operation's destination register, is available not just until the time that the operation is issued, but until the operation completes execution and overwrites it. By reserving the register for this operation's result only at the end of the operation, the register pressure can be reduced.

<sup>&</sup>lt;sup>7</sup> This takes advantage of our assumption that all operations read their inputs during their first cycle of execution even if their execution latency is greater than one cycle. For a discussion of the general case, the reader is referred to the technical report by Rau, et al. [10].

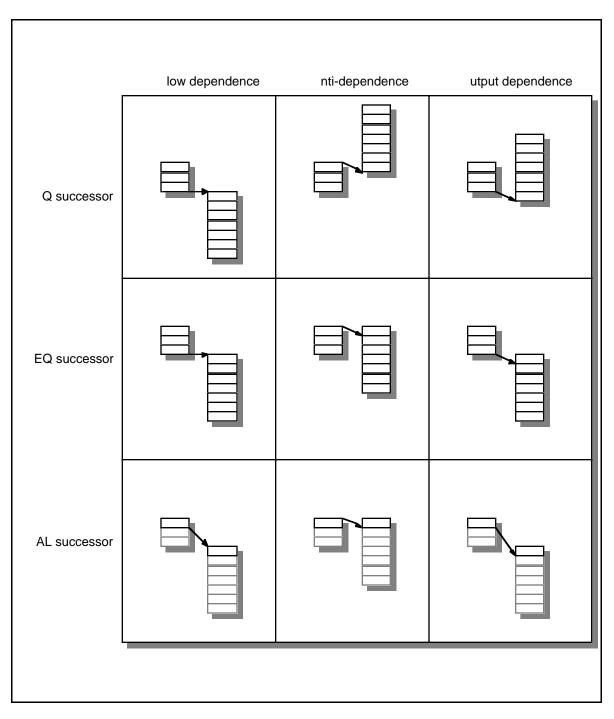

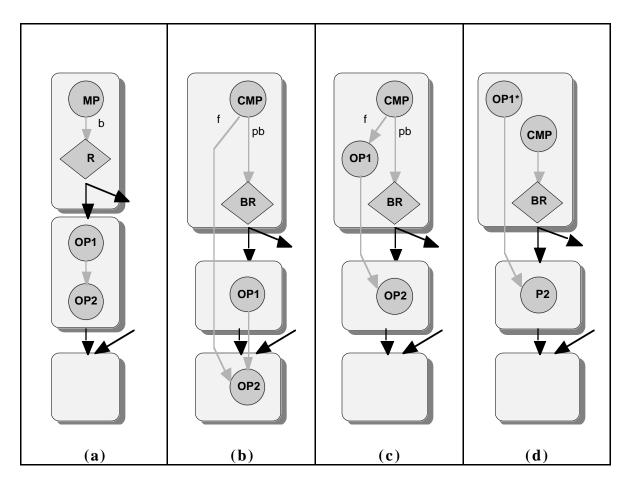

Figure 1: Scheduling implications of EQ, LEQ and UAL operations in the context of flow, anti- and output dependences. The arrows indicate the precedence relationships that must be maintained between the predecessor and successor operations to ensure correct semantics. The relative placement in virtual time of the two operations reflects what a scheduler might do in order to minimize the schedule length.

We define two versions of NUAL semantics which allow EPIC architects to make appropriate tradeoffs between performance, hardware simplicity, and compatibility among differing hardware implementations. We call the strictest form of a NUAL operation an "equals" (EQ) operation. The EQ operation reads its input operands precisely at issue time and delivers results precisely at the specified latency in virtual time. The other version of NUAL is the "less than or equals" (LEQ) operation. A NUAL operation with LEQ semantics is an operation whose write event latency can be anything between one cycle and its assumed latency. Codes scheduled using LEQ operations are correct even if the operations complete earlier than the assumed latency. The distinction between EQ and LEQ vanishes for a UAL operation whose assumed latency is exactly one.

EQ and LEQ semantics affect the set of constraints that the scheduler must honor to ensure correctness, as well as the nature of the ideal schedule from a performance viewpoint. Figure 1 illustrates scheduling constraints for flow, anti-, and output dependences for EPIC processors which employ EQ, LEQ, and UAL latency semantics as well as the preferred relative schedule for the predecessor and successor operations. To understand the relationship of these relative schedules to the corresponding dependences, it is necessary to understand that in our notion of virtual time register writes happen at the end of a virtual cycle—at the time of the virtual clock— whereas register reads occur sometime after the start of a virtual cycle. Also, in this example, the actual latency of the predecessor operation is 7 cycles.

We, first consider flow dependence where the predecessor operation computes an operand which is read as an input by a flow dependent successor operation. NUAL programmatically exposes latency which, in this example, is assumed to match the actual latency. The flow dependent successor must be scheduled to issue at least three cycles later than the operation upon which it depends. The three cycle delay is required for both EQ and LEQ semantics because, the schedule must accommodate the worst case situation for the LEQ which occurs when the first operation delivers its result at the maximum latency of three cycles. With UAL semantics, the flow dependent successor could be correctly scheduled only one cycle after the operation upon which it depends. However, this would typically stall cycles into the processor's ROE and would degrade performance. A high performance schedule would allow the the same three cycles between operations even though it is not required for correctness.

An anti-dependence occurs when the predecessor operation reads an operand before it is overwritten by its anti-dependent successor. With EQ semantics, the earliest time that the anti-dependent successor operation may finish is on the same cycle as the issue cycle for the operation upon which it depends. If this occurs, the predecessor operation reads its input operands just before they are overwritten at the end of the same cycle. In this example, the anti-dependent successor may issue as many as six cycles before the operation upon which it depends. For scheduling purposes, latencies between operations are measured from the issue cycle of the predecessor operation to the issue cycle of the successor operation. Accordingly, the correct latency for this anti-dependence is -6 cycles. This negative "issue-to-issue" latency means that the successor operation may precede the predecessor by no more than six cycles. With LEQ semantics, the successor operation may complete in as little as a single cycle. Hence, the earliest time at which it may issue is concurrent with the operation upon which it depends. In the UAL case, the successor appears to execute in one cycle and, again, the earliest time that the successor may issue is concurrent with its predecessor.

An output dependence occurs when a predecessor operation writes a result operand which is overwritten by an output dependent successor operation. The final value must be the value written by the successor. With EQ semantics, the earliest time that the successor can finish is one cycle later than its predecessor. In this case, the first operation will write its value to the operand and, one cycle later, the successor writes the correct final value to the same operand. A negative issue-to-issue latency of -3 cycles specifies that the successor operation may issue as many as three cycles prior to the predecessor. For LEQ semantics, the schedule must accommodate the worst case situation in which the predecessor operation takes its full three cycle latency while the successor operation completes within a single cycle. In this case, the successor may issue as early as one cycle after the latest completion time of the operation upon which it depends and, the issue-to-issue latency for this output dependence is three. In the UAL case, the output dependent successor may be correctly scheduled a single cycle after the operation upon which it depends, but this may again introduce stall cycles into the processor's ROE. A three cycle issue-to-issue latency ensures stall-free execution.

EQ semantics can be of significant advantage in achieving a shorter schedule if the critical path through the computation runs through these two operations, and if the dependence between them is either an anti- or output dependence.

**Architectural state**. In accordance with Corporaal's terminology [4], an EPIC processor's architectural state can consist of two components: the visible state and the hidden state. The **visible state** is that which is accessible to the operations of the normally

executing program, e.g., the contents of the architectural register files. The **hidden state** is the rest of the processor state, typically in the form of the state of the functional unit pipelines.

For a sequential ISA, with its atomic operations, there is no architectural notion of hidden state. A superscalar processor might, in fact, have plenty of hidden state during execution, for instance the contents of the reorder buffers, but this state must be disposed of prior to any point at which the architectural state can be externally examined. When an interruption occurs, processors typically ensure that all instructions prior to some program location are complete and all instructions after that program location have not yet begun. At such a moment, the atomic nature of operations ensures that architecturally visible state is sufficient to resume operation.

At any moment in a program schedule with non-atomic NUAL operations, it is possible that some operations have started but are not yet completed. In fact, it may be impossible to complete all operations prior to some point in the program schedule and not begin any operation after that point in the schedule without violating NUAL program semantics. In this case, when an interruption occurs, hidden state must be used to represent the action of operations which have started but are not yet completed. If present, it should be possible to save and restore the hidden state, on the occurrence of an interruption, just as one can the visible state. The inclusion of hidden architectural state is an option which comes with its own set of benefits and drawbacks which we shall discuss in Section 5.

## 2.3 Architecturally visible register structure

High levels of ILP require a large number of registers, regardless of the style of the ILP processor. Parallelism is achieved by scheduling (statically or dynamically) a number of independent sub-computations in parallel, which leads to an increased number of temporary values residing in registers simultaneously. Consequently, having a large number of registers is as indispensable to high levels of ILP as is having a large number of functional units. Superscalar processors, which do dynamic scheduling, can make use of a large number of physical registers even though the number of architectural registers is limited, using a hardware mechanism known as register renaming [12]. However, as we shall see below, such techniques are inadequate when static scheduling is employed and the demands placed upon the architectural registers are more stringent.

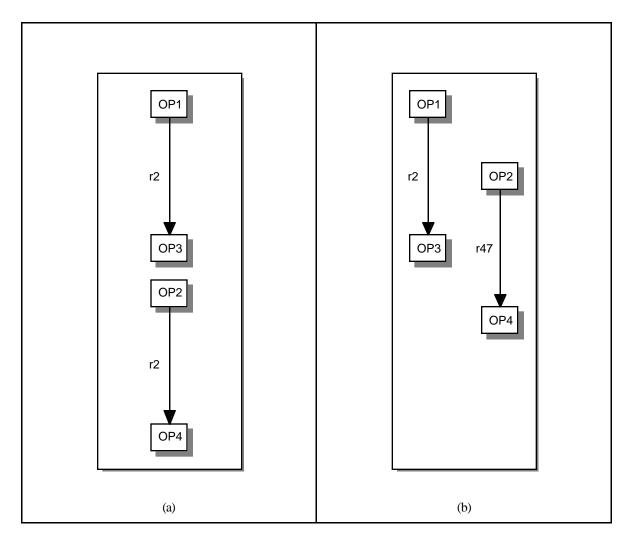

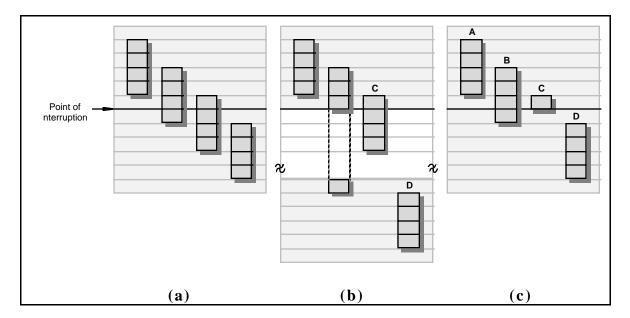

**Large number of architectural registers.** Static scheduling, along with high levels of ILP, requires a large number of architecturally visible registers. Consider the fragment shown in Figure 2a of a schedule that the compiler has constructed for a processor that has 32 architectural registers, and assume that the schedule makes full use of these 32 registers (i.e., there are 32 simultaneously live values). Assume, also, that the functional units of the processor are under-utilized with the specified schedule. Even so, the compiler cannot construct a more parallel schedule. It cannot, for instance, create the more parallel schedule of Figure 2b, in which the two lifetimes overlap, since both are allocated to register r2, and since there are no architectural registers available to which to re-assign one of the lifetimes.

Figure 2: The impact of a limited number of architectural registers upon the achieveable schedule.

An out-of-order processor with register renaming can achieve a ROE similar to that of Figure 2b with just 32 architectural registers, although it might require 64 physical registers. Whereas the compiler delivers to the processor the legal, but relatively sequential schedule of Figure 2a, the superscalar processor renames the registers and executes the instructions of out order, to achieve a ROE that is approximately that of Figure 2b. Of course, this is precisely what EPIC is trying to avoid having to do.

In contrast, with static scheduling, the more parallel schedule requires more architectural registers. With 64 architectural registers, the compiler can re-assign one of the lifetimes to r47 to get the valid schedule of Figure 2b. Note that both processors require the same number of physical registers for equivalent levels of ILP. The difference is that static scheduling requires that they all be architecturally visible. The benefit, of course, is that dynamic scheduling is eliminated.

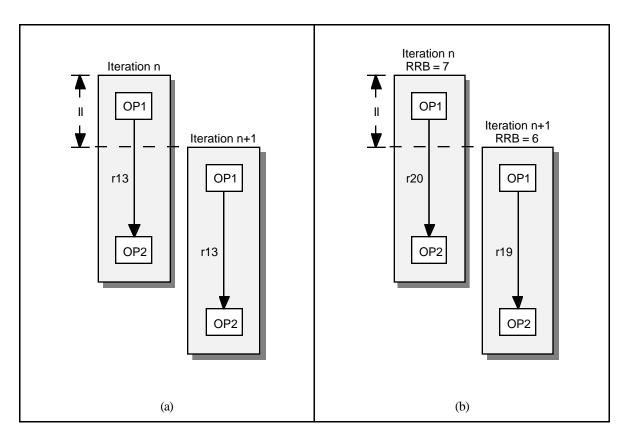

**Rotating registers.** Modulo scheduling [13] engineers the schedule for a loop so that successive iterations of the loop are issued at a constant interval, called the **initiation interval** (II). Typically, the initiation interval is less than the time that it takes to execute a single iteration. As a result, the execution of one iteration can be overlapped with that of other iterations. This overlapped, parallel execution of the loop iterations can yield a significant increase in performance. However, a problem faced while generating the code for a modulo schedule is to prevent results from the same operation, on successive iterations, from overwriting each other prematurely.

Consider the example in Figure 3a which shows the schedule for two consecutive iterations, n and n+1, of a loop. In each iteration, OP1 generates a result which is consumed by OP2. The value is communicated through register r13. The execution of OP1 in iteration n will write a result into r13. The lifetime of this value extends to the cycle in which OP2 is scheduled. Meanwhile, II cycles later OP1 will be executed again on behalf of iteration n+1 and will overwrite the value in r13 before it has been read by the OP2 of the previous iteration, thereby yielding an incorrect result.

One could unroll the code for the body of a loop and use static register renaming to address this problem [14]. However, the systematic unrolling of program loops, and the need to interface code for the unrolled loop body to code reached after exiting the loop body, cause substantial code growth [15]. The use of rotating registers both simplifies the construction of highly-optimized software pipelines and eliminates this code replication.

Figure 3: Compiler-controlled register renaming with rotating registers.

The rotating register file [3] provides a form of register renaming such that successive writes to r13 actually write to distinct registers, thereby preserving correct semantics. A rotating register file has a special register, the **rotating register base** (RRB) register, associated with it. The sum of the register number specified in an instruction with the value of the RRB, modulo the number of registers in the rotating register file, is used as the actual register address. Special loop-closing branch operations [15], which are used for modulo scheduling, decrement RRB each time a new iteration starts, thereby giving the same operation, from different iterations, distinct registers to hold its results. In the case of our example in Figure 3, OP1 in iteration n writes to register r20 since the instruction specifies r13 and the RRB is 7 (Figure 3b). In the next iteration, the RRB has been decremented to 6. As a result, OP1 writes to register r19.

Rotating register files provide dynamic register renaming but under the control of the compiler. It is important to note that conventional hardware renaming schemes cannot be used in place of rotating register files. In a modulo scheduled loop, successive definitions of a register (r13 in the above example) are encountered before the uses of the prior

definitions. Thus, it is impossible even to write correct software pipelined code with the conventional model of register usage.

We have presented some of the fundamental features in EPIC that enable and facilitate the compiler in engineering a desired POE and in communicating it to the hardware. It is precisely these features, especially MultiOp and NUAL, that generate concern regarding the handling of interruptions, object code compatibility and code size. We shall return to these issues in Section 5, 6 and 7, respectively.

# **3** Features to address the branch problem

Many applications are branch-intensive and execute only a few non-branch operations for every branch. Frequent branches present barriers to instruction-level parallelism often greatly reducing execution efficiency. Branch operations have a hardware latency which extends from the time when the branch begins execution to the time when the instruction at the branch target begins execution. During this latency, a branch performs a number of actions:

- a branch condition is computed,

- a target address is formed,

- instructions are fetched from either the fall-through or taken path, depending on the branch condition, and

- the instruction at the location reached after the branch completes is decoded and issued for execution.

The fundamental problem is that although the conventional branch is specified as a single, atomic operation, its actions must actually be performed at different times, spanning the latency of the branch. This latency, measured in processor cycles, grows as clock speeds increase and represents a critical performance bottleneck. When an insufficient number of operations are overlapped with branch execution, disappointing performance results. This is especially problematic for wide-issue processors which may waste multiple issue slots during each cycle of branch latency.

Superscalar processors use innovative hardware to deal with this problem. They do so by executing elements of the branch before operations which precede the branch in order to make it appear as if the branch occurred without significant delay. For example, in order to hide the instruction memory latency, branch target instructions may start to be fetched from

memory right after the fetch of the branch has been initiated, and well before operations needed to compute the branch condition have completed. This can result in the concurrent fetch of taken and fall-through branch successor instructions. Unneeded instructions are later discarded after the branch condition is known. When multiple branches are overlapped, the number of program paths for which instructions must be fetched may grow exponentially.

Superscalar processors also use dynamic, out-of-order execution to move operations across one or more branches. Operations, on one or both paths following the branch, may be executed speculatively before the branch condition is known [16, 17]. When the branch condition is determined, operations on the path that was supposed to be followed are committed, while those on the remaining paths are dismissed [18]. When speculation is performed on both paths and past multiple branches, many speculative operations are dismissed, causing inefficient execution.

To avoid this inefficiency, dynamic branch prediction [9, 19] is used, at each branch, to speculate down only the likely path, ignoring the unlikely path. When a branch is correctly predicted, its latency may be hidden. When a branch misprediction occurs, any operations which are speculatively executed after the branch must be dismissed, and the processor stalls. It is unable to issue new operations until instructions from the correct path have been fetched from memory and have emerged from the instruction pipeline ready to execute, at which point execution resumes on the correct path. In this case, the branch latency is fully exposed. With accurate prediction, relatively few speculative operations are later dismissed.

Modern high-performance processors take advantage of both high-speed clocks and highdensity circuitry. This leads to processors with wider issue-width and longer operation latencies. Out-of-order execution must move operations across more operations and across more branches to keep multiple deeply pipelined resources busy. This is precisely what we are trying to avoid with EPIC, but without it branches have a hidden latency consisting of stall cycles which may occur in connection with the branch. Stall cycles are not visible in the compiler's program schedule but degrade run-time performance, nevertheless. EPIC's philosophy is to eliminate stall cycles by trading them for architecturally visible latencies which can then be minimized or eliminated, under compiler control, by overlapping branch processing with other computation. Rather than relying on hardware alone to solve the problem, EPIC provides architectural features which facilitate the following three capabilities:

- explicit specification in the code as to when each of the actions of the branch must take place

- compile-time code motion of operations across multiple branches without violating correctness, and

- elimination of branches, especially those that are hard to predict accurately.

Whereas EPIC's static scheduling techniques have parallels to dynamic scheduling, the responsibility is shifted from hardware to software, thus allowing simpler, highly parallel hardware.

#### 3.1 Reducing branch stall cycles

EPIC architectures provide NUAL branches which expose branch latency to the compiler. If the assumed branch latency is equal to the actual branch latency, branches can execute without speculation and without stalls. A NUAL branch evaluates its condition and, if its condition is true, it begins fetching instructions from the taken path. Otherwise it continues fetching from the fall-through path. This allows the implementation of a pipelined branch which does not require dynamic branch prediction, speculative instruction prefetch or speculative execution of the dynamic type, and which also does not require instruction issue to be stalled. However, exposed latency branches (both UAL and NUAL) require careful treatment. For UAL branches, operations within the same MultiOp instruction as a branch execute regardless of the branch condition. These operations are in the delay slot of a UAL branch. For NUAL branches the operations in its delay slots are all of the operations in the L consecutive instructions, starting with the one which contains the branch, where L is the branch latency.

The compiler must assume the responsibility for generating efficient schedules by filling up the delay slots of the branch. Even when instructions at the branch target address reside in the first-level cache, the branch latency can be greater than one. If instructions at the branch target are in a second-level cache or main memory, the branch latency is far greater. EPIC's architectural features, which we discuss in Sections 3.2 and 3.3, facilitate high quality

static scheduling with NUAL branches. Despite these features, NUAL branches with very long latencies can be problematic, particularly so in branch-intensive programs.

To address this problem, EPIC also supports a viewpoint that does not treat the branch as an atomic operation; rather than viewing a branch as an single long-latency operation, EPIC unbundles branches [9] into three distinct operations: a compare computes the branch condition; a prepare-to-branch calculates the target address and provides it to the branch unit; and the actual branch marks the location in the instruction stream where control flow is conditionally transferred.

Unbundling the branch architecture is used to reduce both the exposed latency and the hidden (stall) latency required by branches. The exposed branch latency is reduced because of the simpler and less time-consuming nature of the actual branches, and because other branch components have completed much of the work before the actual branch is reached. When work required within a bundled branch is removed from the actual branch operation (e.g. computing the branch condition or target address), the simplified branch is implemented with reduced latency.

The unbundling of branches allows the compiler to move the prepare-to-branch and the compare operations sufficiently in advance of the actual branch so that in-order processors can finish computing the branch condition and prefetching the appropriate instructions by the time that the actual branch is reached. If a compare computes a branch predicate and a subsequent prepare-to-branch (guarded by this predicate) is statically scheduled far enough in advance of the actual branch, then the processor can fully overlap branch processing without prediction, speculation or redundant execution, just as it was able to with the long latency NUAL branch.

The unbundling of the branch also enhances freedom of code motion. Branch components move to previous basic blocks and are replicated as needed by code motion across program merges. This facilitates the overlap of the long latency involved in branch processing, especially when instructions are fetched from a slower cache or from main memory, across multiple basic blocks. Furthermore, the prepare-to-branch can be executed speculatively—before the branch condition is known—achieving a further reduction in program dependence height. When speculation is performed, EPIC's prepare-to-branch provides a static branch prediction hint used to select which program path to follow when instruction fetch bandwidth does not permit speculative prefetch along multiple paths. While static prediction assists processors which do not provide dynamic branch

predication, dynamic branch prediction hardware can be incorporated into EPIC and may override a static prediction after sufficient branch prediction history is acquired.

Once the latency of an individual branch has been dealt with, the next bottleneck that arises is a chain of dependent branches, each of which is guarded by the preceding branch. If branch-intensive code, with few operations per branch, is to be executed on a wide-issue processor, the ability must exist to schedule multiple branches per instruction. Both UAL and NUAL branches are ambiguous when multiple branches take simultaneously. In this case, the branch target is indeterminate and the program is illegal. For UAL branches, this ambiguity can be treated using branch priority [20] which executes simultaneous branches in prioritized order; lower priority branches are dismissed if a higher priority branch is taken. Each branch, in the chain of dependent branches, has a lower priority than the one upon which it is dependent.

Pipelined NUAL branches open up the possibility of having multiple taken branches in execution simultaneously. That is, a branch may take in the delay slot of a previous taken NUAL branch before the effect of that prior branch is complete. When multiple taken branches are overlapped, branch pipelining complicates the compiler's task. Rather than treating each branch sequentially and separately, the compiler's scheduler must consider, and generate customized code for, a large number of possible combinations of the taken and not-taken conditions for multiple overlapped branches. As we shall see in Section 3.3.4, EPIC processors can use an alternate, simpler strategy for scheduling branches within the delay slots of prior branches.

## 3.2 Architectural support for predicated execution

EPIC supports predicated execution, a powerful tool to assist in the parallel execution of conditionals arising from source code branches. Predicated execution refers to the conditional execution of operations based on a boolean-valued source operand, called a predicate. For example, the generic operation "r1 = op(r2,r3) if p1" executes normally if p1 is true and is nullified (i.e., has no effect on the architectural state) if p1 is false. In particular, the nullified operation does not modify any destination register or memory location, it does not signal any exceptions and, it does not branch. Omitting the predicate specifier for an operation is equivalent to executing the operation using the constant predicate true. Predicated execution is often a more efficient method for controlling execution than branching and it provides additional freedom for static code motion.

EPIC support for predicated execution is an enhanced version of the predication provided by the Cydra 5 [3]. EPIC provides a family of compare-to-predicate<sup>8</sup> operations, which are used to compute guarding predicates for operations. A two-target compare-to-predicate operation has the following format:

The compare is interpreted from left to right as: "p1" - first destination predicate; "p2" - second destination predicate; "CMPP" - compare-to-predicate op-code; <cond> - the compare condition which is to be evaluated; <D1-action> - first destination action; <D2-action> - second destination action; "(r1,r2)" - data inputs to be tested; and "p3" - predicate input. A single-target compare is specified by omitting the second destination predicate operand and the second destination action specifier.

Allowed compare conditions include "=", "<", "<=", and other tests on data which yield a boolean result. The boolean result of a comparison is called its compare result. The compare result is used in combination with the predicate input and destination action to determine the destination predicate value.

The possible actions on each destination predicate are denoted as follows: unconditionally set (UN or UC), conditionally set (CN or CC), wired-OR (ON or OC), or wired-AND (AN or AC). The first character (U, C, O or A) determines the action performed on the corresponding destination predicate; the second character (N or C) indicates whether the compare result is used in "normal mode" (N), or "complemented mode" (C). When an action executes in complemented mode, the compare result is complemented before performing the action on the destination predicate.

| Predicate | Compare | On result |    |    |    | On complement<br>of result |    |    |    |

|-----------|---------|-----------|----|----|----|----------------------------|----|----|----|

| input     | result  | UN        | CN | ON | AN | UC                         | CC | OC | AC |

| 0         | 0       | 0         | _  |    |    | 0                          |    |    |    |

| 0         | 1       | 0         |    |    |    | 0                          |    |    |    |

| 1         | 0       | 0         | 0  | -  | 0  | 1                          | 1  | 1  |    |

| 1         | 1       | 1         | 1  | 1  |    | 0                          | 0  |    | 0  |

Table 1: Behavior of compare-to-predicate operations.

$<sup>^{8}</sup>$  This name derives from the fact that the destination of this type of compare operation is a predicate register.

Table 1 defines the action performed for each of the allowed destination action specifiers. The result of an action is specified for all four combinations of predicate input and compare result. Each cell describes the result corresponding to the input combination indicated by the row, and action indicated by the column. The cell specifies one of three actions on the destination predicate register: set to zero ("0"), set to one ("1"), or leave unmodified ("-").

The names of destination action specifiers reflect their behavior. In Table 1, we see that with the **unconditional** actions (UN or UC), a compare-to-predicate operation *always* writes a value to its destination predicate. In this case, the predicate input acts as an input operand rather than as a guarding predicate, and the compare-to-predicate operation is never nullified. The value written to the destination predicate register is simply the conjunction of the predicate input and the compare result (or its complement, if the action is UC). On the other hand, cmpp operations using the **conditional** actions (CN or CC) behave truly in a predicated manner. In this case, a cmpp operation writes to its destination register only if the predicate input is 1, and leaves the destination register unchanged if the predicate input is 0. The value written is the compare result (if CN is specified) or its complement (if CC is specified).

The **wired-OR** action is named for the familiar circuit technique of computing a high fanin OR by directly connecting the outputs of suitable devices, instead of computing the OR of those outputs using an OR gate. In the compare-to-predicate operation, the wired-OR action specifies that the operation write a 1 to its destination predicate only if the predicate input is 1 (i.e. the operation is not nullified) and the compare result is asserted (1 if ON, else 0 for OC). Since a wired-OR cmpp operation either leaves its destination predicate unchanged or writes only the value 1, multiple wired-OR cmpp operations that target the same destination predicate can execute in parallel or in any arbitrary order. The parallel write semantics are well-defined since the multiple values being written (if not nullified) are guaranteed to be the same, namely 1. Furthermore, wired-OR compares with the same destination predicate can be statically scheduled in any order without affecting the result; no output dependence exists between these compare operations.

By initializing a predicate register p to 0, the disjunction of any number of compare conditions can be computed in parallel, or in any arbitrary order, using wired-OR cmpp operations all of which have the same destination, p. The value of p will be 1 if and only if one or more of the compare operations executes with its compare result asserted. The **wired-AND** compare is used in a similar manner, but to compute the conjunction of any number of compare conditions. The common destination predicate is initialized to 1.

## **3.3** Overcoming the branch barrier

Branches present a barrier to the unrestricted static re-ordering of operations that is desirable for creating the best schedules. EPIC provides two important features, predicated execution and control speculation, for increasing the mobility of operations across branches.

#### 3.3.1 Control speculation with biased branches

Traditional compilers schedule each basic block separately. While this produces highquality code for sequential processors, it produces inefficient code for ILP processors. To improve efficiency, ILP compilers use region-based schedulers to enhance the scheduling scope. Region-based schedulers operate on larger regions of code consisting of multiple basic blocks on high probability paths through the program. These schedulers move operations over the full scope of a region to efficiently use processing resources. The regions are best formed using branch profiles gathered from sample runs of the program. It has been shown that sample runs usually accurately predict branch profiles for differing program data [21]. Compilers can also directly estimate branch profiles from the program's syntax, but the accuracy is reduced.

Many branches are highly biased, and easily predicted statically. When scheduling code with biased branches, ILP compilers use linear regions which capture the likely paths through the program<sup>9</sup>. Code is moved within these regions (along the likely paths) to increase performance. In doing so, compilers balance the cost of unnecessarily executing an operation against the reduced height achieved by moving it across a branch. When branches are highly biased, code is moved speculatively across multiple branches and efficiency is maintained because few operations are later dismissed. Linear region types include: the **trace** [20] which allows multiple entries and multiple exits, and the **superblock** [22] which allows a single entry and multiple exits. Both trace scheduling and superblock scheduling expose substantial instruction-level parallelism and often produce

$<sup>^{9}</sup>$  Note that this is essentially what dynamic speculation does as well and that it is in the context of biased branches that dynamic speculation is most successful.

very efficient program schedules. For simplicity, superblocks are used to describe subsequent examples.

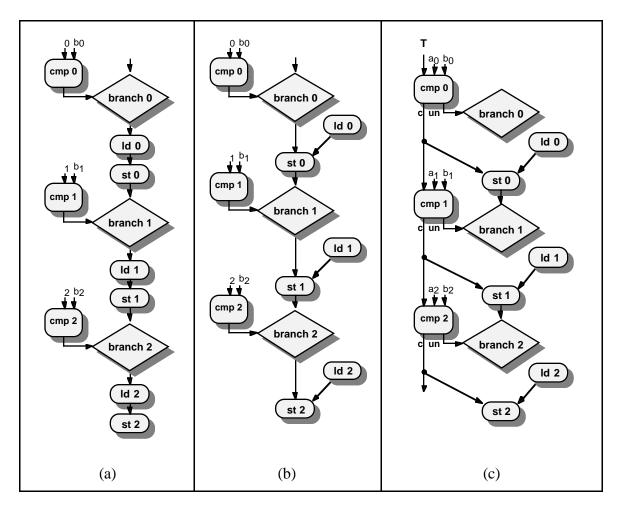

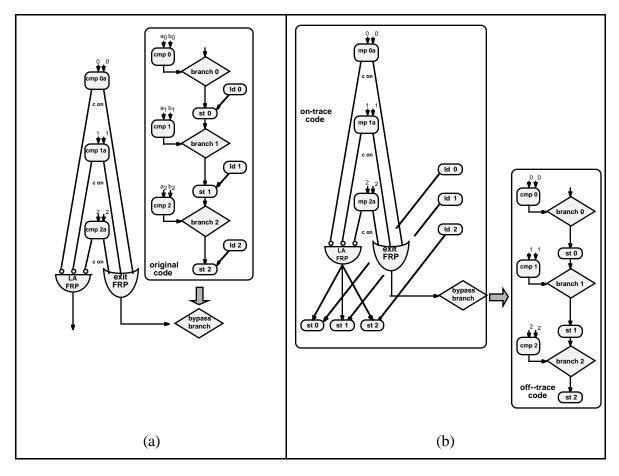

Figure 4: Control speculation of operations in a superblock. (a) A superblock with basic block dependences. (b) The same superblock with speculative code. (c) The superblock with FRPized code.

Figure 4a, shows a superblock with basic block dependences. Each branch precedes a load operation (ld) which produces a value that is stored using a store operation (st) before the following branch. Without speculation, operations remain trapped between branches; each load is trapped below a previous branch and each store is trapped above the subsequent branch. In Figure 4b static speculation of the load operations is allowed. Dependences are removed from branches to subsequent loads and loads can now move upward across preceding branches to enhance ILP. Load operations can now execute even when they would not have executed in the original program.

While static speculation enhances available ILP, it also requires hardware assistance to handle exceptions, for instance, when an operation results in an illegal memory reference or division by zero. If exceptions from speculative operations are reported immediately, it may lead to the reporting of spurious exceptions. For example, assume that the first branch in Figure 4b is taken. All three subsequent loads should be dismissed because they did not execute in the original (non-speculative) program. If a load is speculatively scheduled above the first branch and the error is reported immediately, then it is reported even though it never occurred in the original program. EPIC uses a 1-bit tag in each register, termed the NAT (Not A Thing) bit, to defer the reporting of exceptions arising from speculative operations to be delayed until it is clear that that operation would have been executed in the original (non-speculative) program.

A brief description of EPIC's hardware support for speculation follows. For every type of operation that may be speculated and can generate an exception, there are two versions of the opcode—the speculative one and the normal non-speculative one. Operands are tagged as correct or erroneous by the NAT bit. Non-speculative operations report exceptions that they generate immediately. Speculative operations never report exceptions immediately; when a speculative operation generates an exception, it merely tags its result as erroneous. When a speculative operation uses an erroneous input from a previous speculative operation, its result is also tagged as erroneous. Non-speculative operations, however, report an exception when one of their inputs is erroneous, since this indicates an exception that has been propagated from a prior speculative operation and since it is now clear that that speculative operation would have, in fact, been executed in the original program. An exception can thus propagate through a chain of data dependent speculative operations until it finally is reported by a non-speculative operation. Thereafter, code generated by the compiler is responsible for determining the cause of the exception and what action to take.

The processing of exceptions often requires more complex interaction between an application and an exception handler. Flow-of-control is often transferred from the application to an exception handler (where the exception is processed) and back as the application is resumed. Again EPIC can use tagged data to defer an exception that is produced while executing a speculative operation. The deferred exception is processed later by a non-speculative operation, at which point the exception handler is invoked. The compiler must ensure that any data required during exception processing is not overwritten prior to the execution of the operation where the exception is processed.

Speculative and non-speculative versions for each operation can be provided using multiple approaches. One approach defines two opcodes for every potentially speculative operation: speculative and non-speculative operation forms which defer or report the error, respectively. Typically, no extra operations are needed in order to handle errors but the number of opcodes is doubled to accommodate two versions of most instructions. An alternative approach removes the responsibility for reporting exceptions from the non-speculative operations as well and hands it over to special exception checking operations called sentinels [24]. Here, extra operations are scheduled to check whether the results of chains of speculated operation are erroneous, but opcodes need only be specified in one form which is, effectively, the speculative version.

#### 3.3.2 Control speculation with unbiased branches

With unbiased branches, traces and superblocks can not be readily identified. Linear code motion speculates along a single preferred path and expedites one path at the expense of others which are equally important. When scheduling unbiased branches in linear regions, control often flows off-trace onto paths that were not statically optimized and efficiency suffers. Scheduling using more general non-linear regions [25, 26] can improve performance. Speculative scheduling using non-linear regions allows operations to move prior to a branch from either or both branch targets and simultaneously expedites multiple paths.

When optimizing programs with unbiased branches, an EPIC compiler schedules unbundled branch components like other operations. When large basic blocks contain many non-branch operations, branch overlap is easily achieved as branch components are moved upward within their home basic block. However, with small basic blocks, scheduling branch components before the actual branch may hoist compare and prepare-to-branch operations speculatively across multiple branches.

Excessive speculation leads to inefficient execution. When an operation is speculatively moved across a single unbiased branch, it may be dismissed about half of the time. When an operation is moved speculatively across multiple unbiased branches, it is dismissed most of the time. Schedulers limit excessive speculation by balancing the cost of executing unneeded speculative operations against reduced critical path length, in an attempt to achieve the shortest possible schedule [27]. Thus, branch components are sometimes scheduled too close to the actual branch and branches are not always efficiently overlapped. As we shall see, EPIC facilitates the elimination of branches where beneficial.

#### 3.3.3 Non-speculative code motion

Speculative motion alone is not sufficient to fully exploit instruction-level parallelism. Operations like branches and stores to memory are not speculatively executed since they cause side-effects that are not easily undone. EPIC uses predicated execution to facilitate code motion by allowing operations to move non-speculatively across branches. This is accomplished using fully-resolved predicates. A **fully-resolved predicate** (**FRP**) for an operation is a boolean which is true if and only if program flow would have reached that operation's home block in the original program. An operation's **home block** is its original basic block in the non-speculative program. FRPs are also computed for branches. A branch FRP is true when program flow reaches the branch's home block and the branch takes, otherwise the branch FRP is false.

FRPs are used as predicates to guard operations, that are moved above branches, in order to keep them non-speculative. The FRP ensures that the operation is nullified whenever control branches away from the operation's home block in the original program. Figure 4c illustrates FRPized code. Each compare computes two predicate results using an input predicate and two data values. Recall that the UN modifier indicates unconditional action (U) for a normal (N) condition, while the UC modifier indicates unconditional action for a complemented (C) condition. If the input predicate is false, both UN and UC target predicates are false. If the input predicate is true, the value of the UN predicate is the compare result and the value of the UC predicate is the complement of the compare result. Each compare computes an FRP for the branch exiting the current basic block (UN target), as well as an FRP for the subsequent basic block (UC target).

FRPized regions do not require dependences between branches and subsequent FRPguarded non-speculative operations (including stores and succeeding branches). These FRP-guarded non-speculative operations can move upward across prior branches. In particular, the three branches in Figure 4c may be scheduled to occur simultaneously or in any arbitrary order relative to one another.

Note that a chain of dependences through branches in 1b has been exchanged for a chain of dependences through compares in 1c. To the extent that this chain of dependences is the bottleneck to achieving a good schedule, one can shorten the critical path by employing wired-AND compares. There are six different FRPs that must be computed in Figure 4c, three for the branches and three for the stores. Each of these is a conjunction of up to three compare results (possibly after they have been complemented). One or more of these six

FRPs may be computed using wired-AND compares in order to reduce the critical path length to the point where it is no longer the bottleneck.

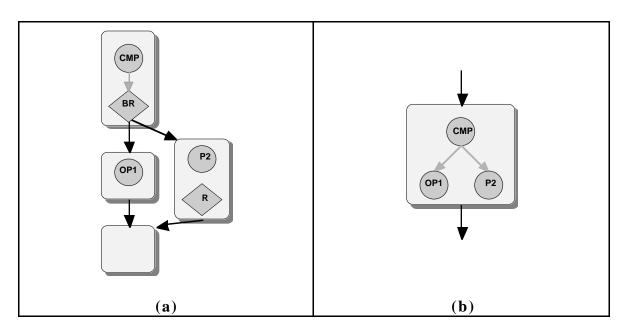

#### 3.3.4 Operation mobility across branches

Branches present barriers to the static re-ordering of operations needed for efficient schedules. Even without predicated execution and control speculation, the compiler can move an operation down into the delay slots of the branch, that is in its home block, and beyond (but with replication along all paths from the branch). But with predication and speculation, the mobility of operations bracketed by branches is greatly increased.