# VGA Function Specification GXm/MXi Processors

January 16, 1998 - Rev. 0.1

Cyrix Corporation Confidential

©1998 Copyright Cyrix Corporation. All rights reserved. Printed in the United States of America

Cyrix is a registered trademark of Cyrix Corporation.

Cyrix Trademarks include: Cx5520, Cx5530, Display Compression Technology (DCT), MediaGX, XpressAUDIO, XpressGRAPHICS, XpressRAM, Virtual System Architecture (VSA)

All other products mentioned herein are trademarks of their respective owners and are hereby recognized as such. Cyrix is a wholly-owned subsidiary of National Semiconductor® Corp.

Cyrix Corporation 2703 North Central Expressway Richardson, Texas 75080 United States of America

Cyrix Corporation (Cyrix) reserves the right to make changes in the devices or specification described herein without notice. Before design-in or order placement, customers are advised to verify that the information on which orders or design activities are based is current. Cyrix warrants its products to conform to current specifications in accordance with Cyrix' standard warranty. Testing is performed to the extent necessary as determined by Cyrix to support this warranty. Unless explicitly specified by customer order requirements, and agreed to in writing by Cyrix, not all device characteristics are necessarily tested. Cyrix assumes no liability, unless specifically agreed to in writing, for customer's product design or infringement of patents or copyrights of third parties arising from use of Cyrix devices. No license, either express or implied, to Cyrix patents, copyrights, or other intellectual property rights pertaining to any machine or combination of Cyrix devices is hereby granted. Cyrix products are not intended for use in any medical, life saving, or life sustaining systems. Information in this document is subject to change without notice.

ii Rev. 0.1

| 1 | VGA  | Function Overview                                                                                                                                                                                                                                                                                                     |

|---|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1  | Introduction                                                                                                                                                                                                                                                                                                          |

|   | 1.2  | VGA Modes       .1         1.2.1 Text Modes       .1         1.2.2 Graphics Modes       .2         1.2.3 Major Components       .2                                                                                                                                                                                    |

| 2 | VGA  | Operation                                                                                                                                                                                                                                                                                                             |

|   | 2.1  | Frame Buffer                                                                                                                                                                                                                                                                                                          |

|   | 2.2  | Sequencer                                                                                                                                                                                                                                                                                                             |

|   | 2.3  | Graphics Controller       .4         2.3.1 Write Modes       .5         2.3.2 Read Modes       .6                                                                                                                                                                                                                     |

|   | 2.4  | Attribute Controller                                                                                                                                                                                                                                                                                                  |

|   | 2.5  | General Registers                                                                                                                                                                                                                                                                                                     |

|   | 2.6  | Video DAC                                                                                                                                                                                                                                                                                                             |

|   | 2.7  | CRT Controller                                                                                                                                                                                                                                                                                                        |

| 3 | Regi | sters                                                                                                                                                                                                                                                                                                                 |

|   | 3.1  | General Registers       10         3.1.1 Miscellaneous Output Register       10         3.1.2 Input Status Register 0       10         3.1.3 Input Status Register 1       11         3.1.4 Feature Control Register       11                                                                                         |

|   | 3.2  | Sequencer Registers       12         3.2.1 Sequencer Registers Summary       12         3.2.2 Sequencer Index Register       12         3.2.3 Reset Register (Index 0)       12         3.2.4 Clocking Mode (Index 1)       13         3.2.5 Map Mask (Index 2)       13         3.2.6 Memory Mode (Index 4)       14 |

|   | 3.3  | CRT Controller Registers                                                                                                                                                                                                                                                                                              |

|     | 3.3.2 Horizontal Total (Index 0)                                               |

|-----|--------------------------------------------------------------------------------|

|     | 3.3.3 Horizontal Display Enable End (Index 1)                                  |

|     | 3.3.4 Horizontal Blank Start (Index 2)                                         |

|     | 3.3.5 Horizontal Blank End (Index 3)                                           |

|     | 3.3.6 Horizontal Sync Start (Index 4)                                          |

|     | 3.3.7 Horizontal Sync End (Index 5)                                            |

|     | 3.3.8 Vertical Total (Index 6)                                                 |

|     | 3.3.9 Overflow (Index 7)                                                       |

|     | 3.3.10 Preset Row Scan (Index 8)                                               |

|     | 3.3.11 Maximum Scan Line (Index 9)                                             |

|     | 3.3.12 Cursor Start (Index 0xA)                                                |

|     | 3.3.13 Cursor End (Index 0xB)                                                  |

|     | 3.3.14 Cursor Location High (Index 0xE) and Cursor Location Low (Index 0xF) 20 |

|     | 3.3.15 Vertical Sync Start (Index 0x10)                                        |

|     | 3.3.16 Vertical Sync End (Index 0x11)                                          |

|     | 3.3.17 Vertical Display Enable End (Index 0x12)                                |

|     | 3.3.18 Offset (Index 0x13)                                                     |

|     | 3.3.19 Underline Location (Index 0x14)                                         |

|     | 3.3.20 Vertical Blank Start (Index 0x15)                                       |

|     | 3.3.21 Vertical Blank End (Index 0x16)                                         |

|     | 3.3.22 CRTC Mode Control (Index 0x17)                                          |

|     | 3.3.23 Line Compare (Index 0x18)                                               |

|     | 3.3.24 CPU Data Latch State (Index 0x22)                                       |

|     | 3.3.25 Attribute Index/Data FF State (Index 0x24)                              |

|     | 3.3.26 Attribute Index State (Index 0x26)                                      |

| 3.4 | Graphics Controller Registers                                                  |

|     | 3.4.1 Graphics Controller Index Register                                       |

|     | 3.4.2 Set/Reset (Index 0)                                                      |

|     | 3.4.3 Enable Set/Reset (Index 1)                                               |

|     | 3.4.4 Color Compare (Index 2)                                                  |

|     | 3.4.5 Data Rotate (Index 3)                                                    |

|     | 3.4.6 Read Map Select (Index 4)                                                |

|     | 3.4.7 Miscellaneous (Index 6)                                                  |

|     | 3.4.8 Color Don't Care (Index 7)                                               |

|     | 3.4.9 Bit Mask (Index 8)                                                       |

| 3.5 | Attribute Controller Registers                                                 |

| 5.0 | 3.5.1 Attribute Controller Index Register                                      |

|     | 3.5.2 EGA Palette (Indexes 0x00 - 0x0F)                                        |

|     |                                                                                |

|   | 3.6  | 3.5.3 Attribute Mode Control (Index 0x10)       31         3.5.4 Overscan Color (Index 0x11)       31         3.5.5 Color Plane Enable (Index 0x12)       32         3.5.6 Horizontal Pel Panning (Index 0x13)       32         3.5.7 Color Select (Index 0x14)       33         Video DAC Registers       34         3.6.1 Palette Address Register       35         3.6.2 DAC State Register       35         3.6.3 Palette Data Register       35 |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 3.6.4 Pel Mask Register                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4 | Exte | nded Registers                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 4.1  | ExtendedRegisterLock (Index 0x30)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.2  | SoftVgaRevision (Index 0x31)                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 4.3  | DisplayDataChannel (Index 0x32)                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 4.4  | DirectDrawMemoryBase (Index 0x3C)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.5  | DirectDrawMemorySize (Index 0x3D)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.6  | GraphicsMemorySize (Index 0x3E)                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 4.7  | ModeSwitchControl (Index 0x3F)                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 4.8  | ModeNumber (Index 0x40)                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 4.10 | HorizontalTimingExtension (Index 0x42)                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 4.9  | VerticalTimingExtension (Index 0x41)                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 4.11 | ExtendedAddressControl (Index 0x43)                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 4.12 | ExtendedStartAddress (Index 0x44)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.13 | ExtendedColorControl (Index 0x46)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 4.14 | WriteMemoryAperture (Index 0x47)                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 4.15 | ReadMemoryAperture (Index 0x48)                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 4.16 | DisplayCompression (Index 0x49)                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | 4.17 | DriverControl (Index 0x4A)                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 4.18 | DACControl (Index 0x4B)                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 4.19 | ClockControl (Index 0x4C)                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 4.20 | CrtClockFrequency (Index 0x4D)                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 4.21 | CrtClockFrequencyFraction (Index 0x4E)                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.22 | RefreshRate (Index 0x4F)            |

|------|-------------------------------------|

| 4.23 | DisplayEnable (Index 0x50)          |

| 4.24 | FpResolution (Index 0x52)           |

| 4.25 | FpControl (Index 0x53)              |

| 4.26 | FpDither (Index 0x54)               |

| 4.27 | FpClockFrequency (Index 0x55)       |

| 4.28 | FpHorizontalTotal (Index 0x56)      |

| 4.29 | FpVerticalTotal (Index 0x57)        |

| 4.30 | FpHorizontalSyncStart (Index 0x58)  |

| 4.31 | FpHorizontalSyncEnd (Index 0x59)    |

| 4.32 | FpVerticalSyncStart (Index 0x5A)    |

| 4.33 | FpVerticalSyncEnd (Index 0x5B)      |

| 4.34 | CrtHorizontalSyncStart (Index 0x5C) |

| 4.35 | CrtHorizontalSyncEnd (Index 0x5D)   |

| 4.36 | CrtVerticalSyncEnd (Index 0x5F)     |

| 4.37 | PanOffsetLow (Index 0x60)           |

| 4.38 | PanOffsetHigh (Index 0x61)          |

| 4.39 | PanOffsetExtended (Index 0x62)      |

| 4.40 | ExtendedFontControl (Index 0x63)    |

| 4.41 | TVControl (Index 0x67)              |

| 4.42 | TVMode (Index 0x68)                 |

| 4.43 | TVHorizontalPosition (Index 0x69)   |

| 4.44 | TVVerticalPosition (Index 0x6A)     |

| 4.45 | TVBrightness (Index 0x6B)           |

| 4.46 | TVEncoder (Index 0x6C)              |

#### 1 VGA Function Overview

#### 1.1 Introduction

The VGA graphics subsystem is compatible with the IBM VGA as defined in the IBM Video Subsystem Technical Reference manual. Additional functionality is provided to support the VESA BIOS Extensions (VBE) which provide higher screen addressability and color content than the base VGA alone. Support is also provided for a number of hardware-specific features.

#### 1.2 VGA Modes

A VGA "mode" is a programmed VGA configuration defined by the VGA BIOS that produces a graphics frame buffer format and a screen image with specific characteristics. The base VGA function provides coded text modes for text-based applications, and graphics modes for graphics-based applications. Many of these modes are compatible with older graphics adapter standards, such as MDA, CGA, and EGA.

#### 1.2.1 Text Modes

There are five text modes defined by VGA BIOS as shown in Table 1-1. Each of the text modes provides a coded frame buffer consisting of a 16-bit value for each character. The low byte is the ASCII character code for the character to display, and the high byte is an attribute byte that determines how the character is displayed (foreground, background colors, blink, underline, etc.). There are two formats defined by BIOS for the attribute byte: color and monochrome as shown in Table 1-2.

Table 1-1 VGA Text Modes

| BIOS Mode # | Screen Size in Characters | Attribute Type | Buffer Address | Compatibility |

|-------------|---------------------------|----------------|----------------|---------------|

| 0, 1        | 40x25                     | Color          | B8000-BFFFF    | CGA           |

| 2, 3        | 80x25                     | Color          | B8000-BFFFF    | EGA, VGA      |

| 7           | 80x25                     | Monochrome     | B0000-B7FFF    | MDA           |

Table 1-2 Text Mode Attribute Byte Format

| Bit | Color Definition                 | Monochrome Definition            |

|-----|----------------------------------|----------------------------------|

| 7   | Blink                            | Blink                            |

| 6   | Background Color (R)             | Background                       |

| 5   | Background Color (G)             | Background                       |

| 4   | Background Color (B)             | Background                       |

| 3   | Foreground Intensity/Font Select | Foreground Intensity/Font Select |

| 2   | Foreground Color (R)             | Foreground                       |

| 1   | Foreground Color (G)             | Foreground                       |

| 0   | Foreground Color (B)             | Underline                        |

#### **VGA Function Overview**

#### 1.2.2 Graphics Modes

The graphics modes listed in Table 1-3 are defined by VGA BIOS.

#### 1.2.3 Major Components

VGA consists of several major components. These are:

- Frame Buffer 256KB of memory organized as 64K DWORDS. It is viewed by the CPU as a flat buffer or as four planes (or maps) of 64K bytes each depending on the mode programmed.

- Sequencer Controls clocking and converting multi-byte CPU accesses into discrete byte accesses for the Graphics Controller.

- *Graphics Controller* Provides frame buffer manipulation assistance for the CPU. Frame buffer data can be read and written in various formats. Functions such as ROP, masking, and color compare are available.

- Attribute Controller Formats the data read from the frame buffer for display on the screen.

- General Registers Provide various control functions such as memory and I/O space location.

- Video DAC Converts the digital pixel values to the analog RGB signals used by the display. It also contains the color lookup table.

- CRT Controller Generates frame buffer address for display refresh, and display timing signals.

Table 1-3 VGA Graphics Modes

| BIOS Mode # | Screen Size in Pixels | # of Colors | Frame Buffer<br>Format | Buffer Address |

|-------------|-----------------------|-------------|------------------------|----------------|

| 4, 5        | 320x200               | 4           | Packed Pixel           | B8000-BFFFF    |

| 6           | 640x200               | 2           | Packed Pixel           | B8000-BFFFF    |

| 0xD         | 320x200               | 16          | Planar                 | A0000-AFFFF    |

| 0xE         | 640x200               | 16          | Planar                 | A0000-AFFFF    |

| 0xF         | 640x400               | 4           | Planar                 | A0000-AFFFF    |

| 0x10        | 640x350               | 16          | Planar                 | A0000-AFFFF    |

| 0x11        | 640x480               | 2           | Planar                 | A0000-AFFFF    |

| 0x12        | 640x480               | 16          | Planar                 | A0000-AFFFF    |

| 0x13        | 320x200               | 256         | Packed Pixel           | A0000-AFFFF    |

#### 2 VGA Operation

This chapter provides more details of the operation of the various components of the VGA subsystem. Each of the seven major components mentioned in the previous chapter is described in detail.

#### 2.1 Frame Buffer

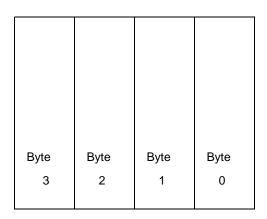

The VGA frame buffer consists of 256KB of memory organized as 64K DWORDS. Each byte in the DWORD is treated as a separate map (i.e. bytes 0, 1, 2, &3 are maps 0, 1, 2, & 3 respectively). In planar graphics modes, the maps correspond to the red, green, blue, and intensity color planes.

The CPU and the CRT refresh activity view the frame buffer in different ways depending on the setting of various VGA control bits. These two views are independent of each other. The CPU could be viewing the frame buffer in one way, and the CRT in another. The video BIOS modes set the two views to be (somewhat) consistent with each other, but it is possible for software to program the two in different ways (many games do this).

#### 2.2 Sequencer

The Sequencer provides clocking to the other VGA sections. It generates the dot clock, character clock, and the shift/load signals used to control the operation of the video serializers. It also manages part of the CPU accesses to video memory.

The Map Mask register in this section enables or disabled CPU writes to each of the 4 memory maps.

Figure 2-1 Frame Buffer Organization

64K DWORDS

#### 2.3 Graphics Controller

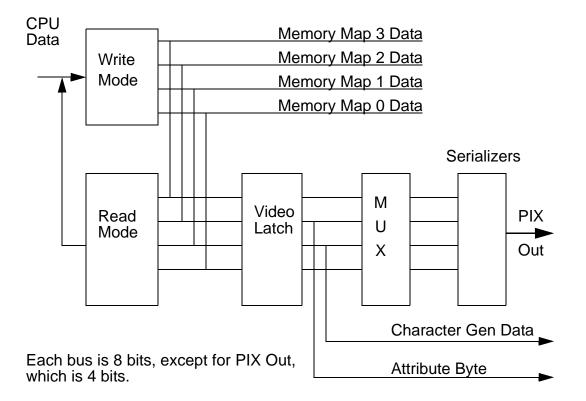

The Graphics Controller manages the CPU interaction with video memory, and contains the video serial-izers that feed the front end of the Attribute Controller. Several memory read and write modes are supported that provide various forms of acceleration for VGA graphics operations. A high-level diagram of the Graphics Controller is shown below.

Figure 2-2 Graphics Controller High-Level Diagram

#### 2.3.1 Write Modes

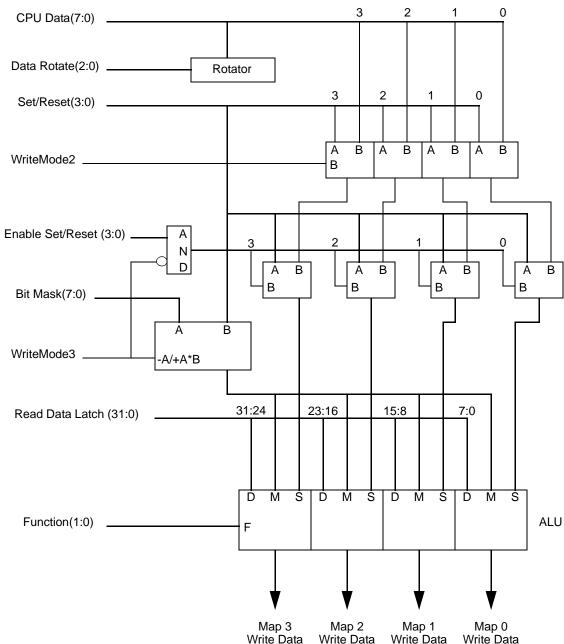

There are four write modes supported by the Graphics Controller (Mode 0, 1, 2, & 3). These write modes provide assistance to the CPU when the frame buffer is in a planar graphics format. The diagram below shows the data flow logic that supports these modes.

Figure 2-3 Write Mode Data Flow

#### 2.3.2 Read Modes

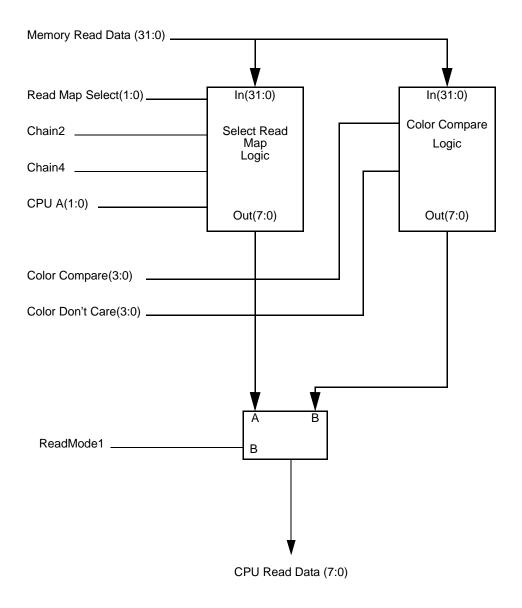

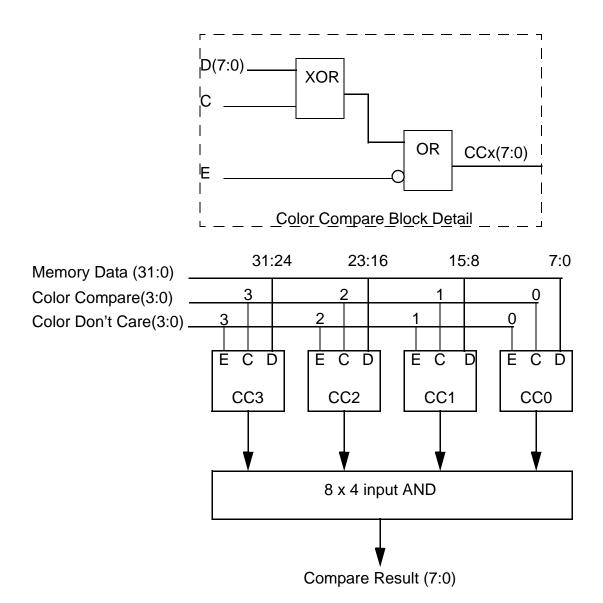

There are two read modes provided to assist the CPU with graphics operations in planar modes. Read mode 0 simply returns the frame buffer data. Read mode 1 allows the CPU to do a single color compare across 8 pixels. Figure 2-4 shows the data flow for read modes. Figure 2-5 shows how the Color Compare block works in the previous figure.

Figure 2-4 Read Mode Data Flow

Figure 2-5 Color Compare Operation

#### **VGA Operation**

#### 2.4 Attribute Controller

The Attribute Controller takes serialized video memory data from the serializers in the Graphics Controller and formats it to be sent to the video DAC. In text modes, the character bit pattern is operated on by the attribute byte value.

#### 2.5 General Registers

The General Registers contain miscellaneous registers that control general parts of the VGA, such as address decoding. Several status registers provide information about the video subsystem state.

#### 2.6 Video DAC

The Video DAC takes an 8-bit pixel stream from the Attribute Controller and uses it as an index into the 256-location color lookup table (CLUT). Each entry in the CLUT is an 18-bit value containing 6 bits for each of the red, green, and blue color components. The appropriate color value is then converted to an analog signal by a high-speed DAC. The analog RGB signals are then sent to the display, along with the sync signals from the CRT Controller.

#### 2.7 CRT Controller

The CRT Controller is responsible for generating the timing signals for the display (horizontal sync, vertical sync, blanking, etc.). It also initiates the display refresh memory reads that provide data to the video serializers in the Graphics Controller.

# 3 Registers

Table 3-1 VGA Register I/O Addresses

| Register/ Group                 | I/O Read<br>Address | I/O Write<br>Address | Comments                        |

|---------------------------------|---------------------|----------------------|---------------------------------|

| Miscellaneous Output Register   | 0x3CC               | 0x3C2 (W)            |                                 |

| Input Status Register 0         | 0x3C2               | -                    |                                 |

| Input Status Register 1         | 0x3?A               | -                    | ? = B (monochrome) or D (color) |

| Feature Control Register        | 0x3CA               | 0x3?A                | ? = B (monochrome) or D (color) |

| Sequencer Index Register        | 0x3C4               | 0x3C4                |                                 |

| Sequencer Data Register         | 0x3C5               | 0x3C5                |                                 |

| CRT Controller Index Register   | 0x3?4               | 0x3?4                | ? = B (monochrome) or D (color) |

| CRT Controller Data Register    | 0x3?5               | 0x3?5                | ? = B (monochrome) or D (color) |

| Graphics Controller Index Reg.  | 0x3CE               | 0x3CE                |                                 |

| Graphics Controller Data Reg.   | 0x3CF               | 0x3CF                |                                 |

| Attribute Controller Index Reg. | 0x3C0               | 0x3C0                |                                 |

| Attribute Controller Data Reg.  | 0x3C1               | 0x3C0                |                                 |

| Video DAC Index (CLUT Writes)   | 0x3C8               | 0x3C8                |                                 |

| Video DAC Index (CLUT Reads)    | -                   | 0x3C7                |                                 |

| Video DAC Data Register         | 0x3C9               | 0x3C9                |                                 |

| Video DAC Pel Mask Register     | 0x3C6               | 0x3C6                |                                 |

**Note:** The '?' in the I/O addresses above is determined by bit 0 of the Miscellaneous Output Register. See the description of this register for more information.

The following sections cover the six groups of registers that make up the VGA register set.

# **General Registers**

## 3.1 General Registers

## 3.1.1 Miscellaneous Output Register

Read Address: 0x3CC Write Address: 0x3C2

| Bits | Function                                                                                                                                                                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Vertical Sync Polarity — Selects a positive-going VSYNC pulse (bit=0) or a negative-going VSYNC pulse (bit=1).                                                                                                                                                             |

| 6    | Horizontal Sync Polarity — Selects a positive-going HSYNC pulse (bit=0) or a negative-going HSYNC pulse (bit=1).                                                                                                                                                           |

| 5    | Page Bit — This bit is used to replace memory address bit A0 as the LSB when bit 1 of the Graphics Controller Miscellaneous Register is set to 1.                                                                                                                          |

| 4    | Reserved                                                                                                                                                                                                                                                                   |

| 3:2  | Clock Select — Selects the VGA pixel clock source:  00 = Selects clock for 640/320 pixels per line  01 = Selects clock for 720/360 pixels per line  10 = Reserved  11 = Reserved                                                                                           |

| 1    | RAM Enable — Enables the video frame buffer address decode when set to 1.                                                                                                                                                                                                  |

| 0    | I/O Address Select — Determines the I/O address of the CRTC registers (0x3?4 & 0x3?5), Feature Control Register (0x3?A), and Input Status Register 1 (0x3?A) as follows: ?=B when bit set to 0 (MDA I/O address emulation), ?=D when bit set to 1 (CGA address emulation). |

## 3.1.2 Input Status Register 0

Read Address: 0x3CC

| Bits | Function                                                                                                                                              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | CRTC Interrupt Pending — When a 1, indicates that a CRTC interrupt is pending.                                                                        |

| 6:5  | Reserved                                                                                                                                              |

| 4    | <b>Display Sense</b> — Returns the state of the wire AND of the RGB signal comparator outputs. This is used for display type sensing and diagnostics. |

| 3:0  | Reserved                                                                                                                                              |

## 3.1.3 Input Status Register 1

Read Address: 0x3BA or 0x3DA

| Bits | Function                                                                                                                                                      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4  | Reserved                                                                                                                                                      |

| 3    | Vertical SYNC — When a 1, indicates that the VSYNC signal is active.                                                                                          |

| 2:1  | Reserved                                                                                                                                                      |

| 0    | <b>Display Enable</b> — Reads as a 0 when both horizontal and vertical display enable are active. Reads as a 1 when either display enable signal is inactive. |

# 3.1.4 Feature Control Register

Write Address: 0x3BA or 0x3DA

Read Address: 0x3CA

| Bits | Function |

|------|----------|

| 7:0  | Reserved |

## **Sequencer Registers**

#### 3.2 Sequencer Registers

Index Register Address: 0x3C4

Data Register Address: 0x3C5

The Sequencer registers are accessed by writing an index value to the Sequencer Index Register (0x3C4) and reading or writing the register using the Sequencer Data Register (0x3C5).

#### 3.2.1 Sequencer Registers Summary

| Index | Register             |  |

|-------|----------------------|--|

| -     | Sequencer Index      |  |

| 0     | Reset                |  |

| 1     | Clocking Mode        |  |

| 2     | Map Mask             |  |

| 3     | Character Map Select |  |

| 4     | Memory Mode          |  |

#### 3.2.2 Sequencer Index Register

| Bits | Function |

|------|----------|

| 7:3  | Reserved |

| 2:0  | Index    |

#### 3.2.3 Reset Register (Index 0)

| Bits | Function                                                                                                                                                                                                                                   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2  | Reserved                                                                                                                                                                                                                                   |

| 1:0  | <b>Enable Display</b> — Both these bits should be set to 1 (value=11b) to enable display of the VGA screen image. If either of these bits are 0, the display will be blanked. The VGA will continue to respond to I/O and memory accesses. |

## 3.2.4 Clocking Mode (Index 1)

| Bits | Function                                                                                                                                                                                                                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6  | Reserved                                                                                                                                                                                                                                                                                                                   |

| 5    | Screen Off — Setting this bit to a 1 will blank the screen while maintaining the HSYNC and VSYNC signals. This is intended to allow the CPU full access to the memory bandwidth. This bit must be 0 for the display image to be visible.                                                                                   |

| 4    | **Not Supported ** (Shift4)                                                                                                                                                                                                                                                                                                |

| 3    | Dot Clock by 2 — When set to 1, the incoming pixel clock will be divided by 2 to form the actual dot clock. When 0, the incoming pixel clock will be used unchanged.                                                                                                                                                       |

| 2    | **Not Supported** (Shift Load)                                                                                                                                                                                                                                                                                             |

| 1    | Always 1                                                                                                                                                                                                                                                                                                                   |

| 0    | 8-Dot Character Width — When set to a 1, the character cells in text mode will be 8 pixels wide. When set to 0, the character cells will be 9 pixels wide. The 9th pixel will be equal to the 8th pixel for character codes 0xC0-0xDF (the line graphics character codes), and will be 0 (background) for all other codes. |

#### 3.2.5 Map Mask (Index 2)

Enable Map 3 (bit 3), Enable Map 2 (bit 2), Enable Map 1 (bit 1), Enable Map 0 (bit 0)

These bits enable (bit = 1) writing to their corresponding bytes in each DWORD of the frame buffer. (i.e. EM3 enables byte 3, EM2 enables byte 2, etc.) The 4 maps or planes correspond to the 4 bytes in each DWORD of the frame buffer. Reads to all maps are always enabled, and are unaffected by these bits.

| Bits | Function     |

|------|--------------|

| 7:4  | Reserved     |

| 3    | Enable Map 3 |

| 2    | Enable Map 2 |

| 1    | Enable Map 1 |

| 0    | Enable Map 0 |

## **Sequencer Registers**

#### **Table 3-2 Character Map Select (Index 3)**

Character Map A (bits 5,3:2) and Character Map B (bits 4, 1:0)

These fields determine which font tables are used when displaying a character in text mode. When attribute bit 3 = 1, Character Map A is used. When attribute bit 3 is a 0, Character Map B is used. The font tables are stored in the 64KB in map 2. There are 8 font tables. The character map codes select the font tables:

| Code | Font Table Location in Map 2 |

|------|------------------------------|

| 0    | 8KB block 0                  |

| 1    | 8KB block 2                  |

| 2    | 8KB block 4                  |

| 3    | 8KB block 6                  |

| 4    | 8KB block 1                  |

| 5    | 8KB block 3                  |

| 6    | 8KB block 5                  |

| 7    | 8KB block 7                  |

|      |                              |

| Bits | Function                 |  |

|------|--------------------------|--|

| 7:6  | Reserved                 |  |

| 5    | Character Map A bit 2    |  |

| 4    | Character Map B bit 2    |  |

| 3:2  | Character Map A bits 1:0 |  |

| 1:0  | Character Map B bits 1:0 |  |

## 3.2.6 Memory Mode (Index 4)

| Bits | Function                                                                                                                                                                                                                                                                                           |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:4  | Reserved                                                                                                                                                                                                                                                                                           |  |

| 3    | Chain4 — When set to a 1, CPU address bits 1 and 0 are used to select the map or plane in the frame buffer DWORD. For example, if CPU A1:A0 = 3, then map 3 is selected. If CPU A1:A0=1, then map 1 is selected. If Chain4 is 0, then the frame buffer addressing is controlled by the Chain2 bit. |  |

| 2    | Chain2 (was Odd/Even) — When set to a 1, CPU address bit 0 selects between frame buffer maps 0 and 1, or maps 2 and 3 depending on the value in the Graphics Controller Read Map Select Register. For example, if CPU A0 is 0, then map 0 (or 2) is selected.                                      |  |

| 1    | <b>Extended Memory</b> — This bit should always be set to a 1. It is a throwback to EGA where the standard frame buffer size was 64KB and was upgradeable to 256KB. VGA always has (at least) 256KB.                                                                                               |  |

| 0    | Reserved                                                                                                                                                                                                                                                                                           |  |

#### 3.3 CRT Controller Registers

Index Register Address: 0x3B4 or 0x3D4

Data Register Address: 0x3B5 or 0x3D5

The CRTC registers are accessed by writing an index value to the CRTC Index Register (0x3B4 or 0x3D4) and reading or writing the register using the CRTC Data Register (0x3B5 or 0x3D5). See the description of the I/O Address Select bit in the Miscellaneous Output Register for more information on the I/O address of the CRTC registers.

Note that the Extended VGA Registers are accessed through the CRTC interface. This section only discusses the base VGA registers, however. See the Extended VGA Registers chapter for more information on the extended registers.

Table 3-3 CRTC Registers Summary

| Index | Register                      |

|-------|-------------------------------|

| -     | CRTC Index                    |

| 0x00  | Horizontal Total              |

| 0x01  | Horizontal Display Enable End |

| 0x02  | Horizontal Blank Start        |

| 0x03  | Horizontal Blank End          |

| 0x04  | Horizontal Sync Start         |

| 0x05  | Horizontal Sync End           |

| 0x06  | Vertical Total                |

| 0x07  | Overflow                      |

| 0x08  | Preset Row Scan               |

| 0x09  | Maximum Scan Line             |

| 0x0A  | Cursor Start                  |

| 0x0B  | Cursor End                    |

| 0x0C  | Start Address High            |

| 0x0D  | Start Address Low             |

| 0x0E  | Cursor Location High          |

| 0x0F  | Cursor Location Low           |

| 0x10  | Vertical Sync Start           |

| 0x11  | Vertical Sync End             |

| 0x12  | Vertical Display Enable End   |

| 0x13  | Offset                        |

| 0x14  | Underline Location            |

| 0x15  | Vertical Blank Start          |

| 0x16  | Vertical Blank End            |

| 0x17  | CRTC Mode Control             |

| 0x18  | Line Compare                  |

| 0x22  | CPU Data Latch State          |

| 0x24  | Attribute Index/Data FF State |

| 0x26  | Attribute Index State         |

# **CRT Controller Registers**

## 3.3.1 CRTC Index Register

| Bits | Function |

|------|----------|

| 7    | Reserved |

| 6:0  | Index    |

## 3.3.2 Horizontal Total (Index 0)

| Bits | Function                                                                                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | Horizontal Total — This value specifies the number of character clocks per horizontal scanline minus 5. It determines the horizontal line rate/period. |

## 3.3.3 Horizontal Display Enable End (Index 1)

| Bits | Function                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | Horizontal Display Enable End — This value specifies the number of displayed characters minus 1. It determines the width of the Horizontal Display Enable signal. |

## 3.3.4 Horizontal Blank Start (Index 2)

| Bits | Function                                                                                                                                  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | <b>Horizontal Blank Start</b> — This value specifies the character position on the line where the horizontal blanking signal goes active. |

## 3.3.5 Horizontal Blank End (Index 3)

| Bits | Function                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Set to 1                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6:5  | <b>Display Enable Skew Control</b> — This value is a binary encoded value that specifies how many character clocks are needed to skew the horizontal display enable signal by (0 character clocks - 3 character clocks) before it is sent to the Attribute Controller. This field is used to accommodate differences in the length of the video pipeline (frame buffer to pixel output) in various text and graphics modes. |

| 4:0  | Horizontal Blank End 4:0 — This 6-bit value is a compare target for the character count where the horizontal blank signal will end. Bit 5 of this value is in the Horizontal Sync End Register (bit 7). Note that not all horizontal counter bits are compared, which can create aliased compares depending upon the binary values involved in the count range and compare values.                                          |

## 3.3.6 Horizontal Sync Start (Index 4)

| Bits | Function                                                                                                               |

|------|------------------------------------------------------------------------------------------------------------------------|

| 7:0  | <b>Horizontal Sync Start</b> — This value specifies the character position where the horizontal sync pulse will start. |

## 3.3.7 Horizontal Sync End (Index 5)

| Bits | Function                                                                                                                   |

|------|----------------------------------------------------------------------------------------------------------------------------|

| 7    | Horizontal Blank End bit 5 — See the description of the Horizontal Blank End Register (index 5).                           |

| 6:5  | **Not Implemented** (HSync Delay)                                                                                          |

| 4:0  | Horizontal Sync End — These bits represent the low 5 bits of the character position where the Horizontal Sync signal ends. |

## 3.3.8 Vertical Total (Index 6)

| Bits | s | Function                                                                                                                                                                                                                                                                                             |

|------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | ) | <b>Vertical Total bits 7:0</b> — This represents the low 8 bits of a value that specifies the total number of scanlines on the screen minus 2. This value includes the blanking area and determines the vertical refresh rate. The high 2 bits of this value are in the Overflow Register (Index 7). |

## **CRT Controller Registers**

## 3.3.9 Overflow (Index 7)

These are the high-order bits for several of the vertical programming values. See the descriptions of the respective vertical registers for descriptions of these fields.

| Bits | Function                          |

|------|-----------------------------------|

| 7    | Vertical Sync Start bit 9         |

| 6    | Vertical Display Enable End bit 9 |

| 5    | Vertical Total bit 9              |

| 4    | Line Compare bit 8                |

| 3    | Vertical blank Start bit 8        |

| 2    | Vertical Sync Start bit 8         |

| 1    | Vertical Display Enable End bit 8 |

| 0    | Vertical Total bit 8              |

## 3.3.10 Preset Row Scan (Index 8)

| Bits | Function                                                                                                                                                                                                                                                                                                 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Reserved                                                                                                                                                                                                                                                                                                 |

| 6:5  | <b>Byte Panning</b> — This value causes the pixel data stream to be fetched 0, 1, 2, or 3 character positions early for use with pel panning in the Attribute Controller. This field is used when the video serializers are chained together (by 2 or by 4).                                             |

| 4:0  | Starting Row Scan — This specifies the value loaded into the row scan counter on the first text line of the screen. Changing this value in text modes allows the screen to be scrolled on a scanline basis rather than a text line basis. The starting row scan count for all subsequent scanlines is 0. |

#### 3.3.11 Maximum Scan Line (Index 9)

| Bits | Function                                                                                                                                                                                                                                                                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | <b>Double Scan</b> — When this bit is set to a 1, the row scan counter increments every other scan line. When this bit is cleared to 0, the row scan counter increments on every scan line. This bit is used to make 200 line text modes occupy 400 physical scan lines on the screen. |

| 6    | <b>Line Compare bit 9</b> — See the description of the Line Compare Register (Index 0x18) for a description of this field.                                                                                                                                                             |

| 5    | Vertical Blank Start bit 9 — See the description of the Vertical Blank Start Register (Index 0x15) for a description of this field.                                                                                                                                                    |

| 4:0  | <b>Maximum Scan Line</b> — This field specifies the number of scan lines per character row minus 1. The row scan counter will count up to this value then go to 0 for the next character row.                                                                                          |

## 3.3.12 Cursor Start (Index 0xA)

| Bits | Function                                                                                                                                                                                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6  | Reserved                                                                                                                                                                                                                                                                                      |

| 5    | Cursor Off — When set to 1, the cursor will be turned off and will not appear on the screen. When this bit is 0, the cursor will be displayed. This bit is only applicable in text modes.                                                                                                     |

| 4:0  | Cursor Start — This field specifies the first scanline in the character box where the cursor is displayed. If this value is greater than the Cursor End value, then no cursor will be displayed. If this value is equal to the Cursor End value, then the cursor occupies a single scan line. |

## 3.3.13 Cursor End (Index 0xB)

| Bits | Function                                                                                                                                                                                    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Reserved                                                                                                                                                                                    |

| 6:5  | <b>Cursor Skew</b> — This field allows the cursor to be skewed by 0, 1, 2, or 3 character positions to the right.                                                                           |

| 4:0  | Cursor End — This field specifies the last scan line in the character box where the cursor is displayed. See the description of the Cursor Start Register (Index 0xA) for more information. |

## Start Address High (Index 0xC) and Start Address Low (Index 0xD)

Start Address

This value specifies the frame buffer address used at the beginning of a screen refresh. It represents the upper left corner of the screen.

| Bits        | Function                      |  |

|-------------|-------------------------------|--|

| Start Addre | ess High (Index 0xC)          |  |

| 7:0         | Start Address bits 15:8       |  |

| Start Addr  | Start Address Low (Index 0xD) |  |

| 7:0         | Start Address bits 7:0        |  |

## **CRT Controller Registers**

#### 3.3.14 Cursor Location High (Index 0xE) and Cursor Location Low (Index 0xF)

**Cursor Location**

This value specifies the frame buffer address where the cursor will be displayed in text mode. The cursor will appear at the character whose memory address corresponds to this value.

| Bits                             | Function                  |

|----------------------------------|---------------------------|

| Cursor Location High (Index 0xE) |                           |

| 7:0                              | Cursor Location bits 15:8 |

| Cursor Location Low (Index 0xF)  |                           |

| 7:0                              | Cursor Location bits 7:0  |

#### 3.3.15 Vertical Sync Start (Index 0x10)

| Bits | Function                                                                                                                                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | <b>Vertical Sync Start bits 7:0</b> — This value specifies the scanline number where the vertical sync signal will go active. This is a 10-bit value. Bits 8 and 9 are in the Overflow Register (Index 0x8). |

## 3.3.16 Vertical Sync End (Index 0x11)

| Bits | Function                                                                                                                                                                                                                             |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7    | Write-protect Registers 0-7 — This bit is used to prevent old EGA programs from writing invalid values to the VGA horizontal timing registers. The Line Compare bit in the Overflow Register (Index 7) is not protected by this bit. |  |

| 6    | **Not Implemented** (Refresh Cycle Select)                                                                                                                                                                                           |  |

| 5    | **Not Implemented** (Enable Vertical Interrupt)                                                                                                                                                                                      |  |

| 4    | **Not Implemented** (Clear Vertical Interrupt)                                                                                                                                                                                       |  |

| 3:0  | Vertical Sync End — This field represents the low 4 bits of a compare value that specifies which scan line that the vertical sync signal goes inactive.                                                                              |  |

## 3.3.17 Vertical Display Enable End (Index 0x12)

| Bits | Function                                                                                                                                                                                                                                                                     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | Vertical Display Enable End bits 7:0 — This is a 10-bit value that specifies the scan line where the vertical display enable signal goes inactive. It represents the number of active scan lines minus 1. Bits 8 and 9 of this value are in the Overflow Register (index 7). |

## 3.3.18 Offset (Index 0x13)

| Bits | Function                                                                                                                                                                                                                                               |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | Offset — This field specifies the logical line width of the screen. This value (multiplied by 2 or 4 depending on the CRTC clocking mode) is added to the starting address of the current scan line to get the starting address of the next scan line. |

## 3.3.19 Underline Location (Index 0x14)

| Bits | Function                                                                                                                                                                                                                                                                                                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Reserved                                                                                                                                                                                                                                                                                                                                                                    |

| 6    | <b>Doubleword Mode</b> — When this bit is a 1, CRTC memory addresses are DWORD addresses, and the CRTC refresh counter effectively increments by 4. When this bit is a 0, the address increment is determined by the Byte Mode bit in the CRTC Mode Control Register (Index 0x17). See the description of the CRTC Mode Control Register (index 0x17) for more information. |

| 5    | Count by 4 — When this bit is a 1, the CRT memory address counter is clocked with the character clock divided by 4. This is used with Doubleword mode.                                                                                                                                                                                                                      |

| 4:0  | <b>Underline Location</b> — This field specifies the row scan value where the underline will appear in the character box in text modes.                                                                                                                                                                                                                                     |

## 3.3.20 Vertical Blank Start (Index 0x15)

| Bits | Function                                                                                                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | <b>Vertical Blank Start bits 7:0</b> — This the low 8 bits of a value that specifies the starting scan line of the vertical blank signal. This is a 10-bit value. Bit 8 is in the Overflow Register (Index 7) and bit 9 is in the Maximum Scan Line Register (index 9). |

## 3.3.21 Vertical Blank End (Index 0x16)

| Bits | Function                                                                                                                                                                 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | <b>Vertical Blank End bits 7:0</b> — This value specifies the low 8 bits of a compare value that represents the scan line where the vertical blank signal goes inactive. |

# CRT Controller Registers

## 3.3.22 CRTC Mode Control (Index 0x17)

| Bits | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | <b>Enable Syncs</b> — When set to 1, this bit will enable the horizontal and vertical sync signals. When 0, this bit will hold both sync flip-flops reset.                                                                                                                                                                                                                                                                                                                                     |

| 6    | Byte Mode — If the Doubleword Mode bit in the Underline Location register is 0, then this bit will configure the CRTC addresses for byte addresses (Byte Mode=1) or word addresses (Byte Mode=0). If the Doubleword Mode bit is a 1, then the Byte Mode bit is ignored. See the diagram at the end of this section for more information on the various CRTC addressing modes.                                                                                                                  |

| 5    | Address Wrap — When the CRTC is addressing the frame buffer in Word Mode (Byte Mode=0, Doubleword Mode=0) then this bit determines which address bit occupies the MA0 bit position of the address sent to the frame buffer memory. If Address Wrap=0, CRTC address counter bit 13 occupies the MA0 position. If Address Wrap=1, then CRTC address counter bit 15 is in the MA0 position. See the diagram at the end of this section for more information on the various CRTC addressing modes. |

| 4    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3    | Count by 2 — When this bit is a 1, the CRTC address counters are clocked by the character clock divided by 2. When this bit is a 0, the CRTC address counters are clocked by the normal character clock. This bit is overridden (a don't care) if the Count by 4 bit in the Underline Location Register (index 0x14) is a 1.                                                                                                                                                                   |

| 2    | <b>VCLK Select</b> — This bit determines the clocking for the vertical portion of the CRTC. If this bit is 0, the horizontal sync signal clocks the vertical section. If this bit is 1, the horizontal sync divided by 2 clocks the vertical section.                                                                                                                                                                                                                                          |

| 1    | Select Row Scan Bit — This bit determines which CRTC signal appears on the MA14 address bit sent to the frame buffer memory. If this bit is a 0, bit 1 of the Row Scan counter appears on MA14. If this bit is a 1, then CRTC address counter bit 14, 13, or 12 appears on MA14. See the table at the end of this section for more information.                                                                                                                                                |

| 0    | Select A13 — This bit determines which CRTC signal appears on the MA13 address bit sent to the frame buffer memory. If this bit is a 0, bit 0 of the Row Scan counter appears on MA13. If this bit is a 1, then CRTC address counter bit 13, 12, or 11 appear on MA13. See the table at the end of this section for more information.                                                                                                                                                          |

Table 3-4 illustrates the various frame buffer addressing schemes. In the table, MAx represents the frame buffer memory address signals, Ax represents the CRTC address counter signals, RSx represents row scan counter output bits. The binary value in the column headings is a concatenation of the Doubleword Mode and Byte Mode bits. (i.e. {DoublewordMode, ByteMode} in Verilog.)

Table 3-4 CRTC Memory Addressing Modes

| Frame Buffer<br>Memory Address bit | Byte Mode (01) | Word Mode (00) | DWORD Mode (1X) |

|------------------------------------|----------------|----------------|-----------------|