# ARM810: Dancing to the Beat of a Different Drum

**Guy Larri**

90 Fulbourn Road, Cherry Hinton, Cambridge, CB1 4JN, England Guy.Larri@arm.com

# **Commercial Drivers For ARM810**

#### • As always, need more Performance

- Twice the performances of ARM710 on same process

### • Embedded, low power, portable applications, requires:

- Inexpensive = small die, small plastic package, limited pin count

- Very Focused on Low Power

### • Licensing Business Model Requires:

- Performance increase on commodity processes

- Low power

- Portable to commodity 0.6µm/0.5µm 3.3V 3-Layer Metal CMOS processes, migration path to 0.35µm

- Modular Design: ARM8 Integer Core is separate product

Cache size variants

Variant with no MMU

- Use as an embedded macrocell and stand-alone cached processor.

## ARM810 ...

| Architecture  | ARMv4 Processor                                   |

|---------------|---------------------------------------------------|

| CPU           | 5 stage pipeline + static branch prediction       |

| Cache         | 8kB Unified Cache<br>Write-Through and Copy-Back  |

| TLB           | 64 entry TLB, 3 Mapping sizes                     |

| Performance   | 84 Dhrystone MIPs @ 72MHz                         |

| Power         | 0.5W @ 3.3V                                       |

| Die Size      | 53.5mm <sup>2</sup> (not including pad ring)      |

| First Process | CMOS 3-layer metal, 0.6µm drawn 0.5µm drawn gates |

| Portable to   | Commodity 0.6µm/0.5µm/0.35µm CMOS                 |

| Package       | 144 TQFP                                          |

| Nice features | Integrated PLL, Lockable Cache/TLB                |

| Markets       | PDA, Network Computer                             |

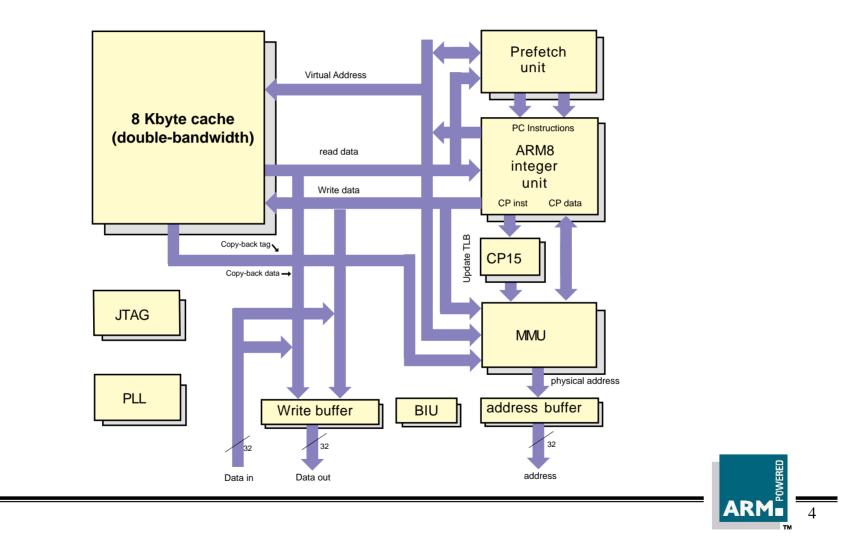

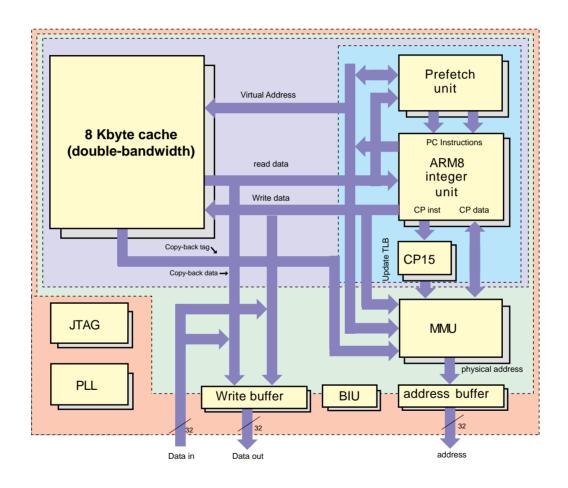

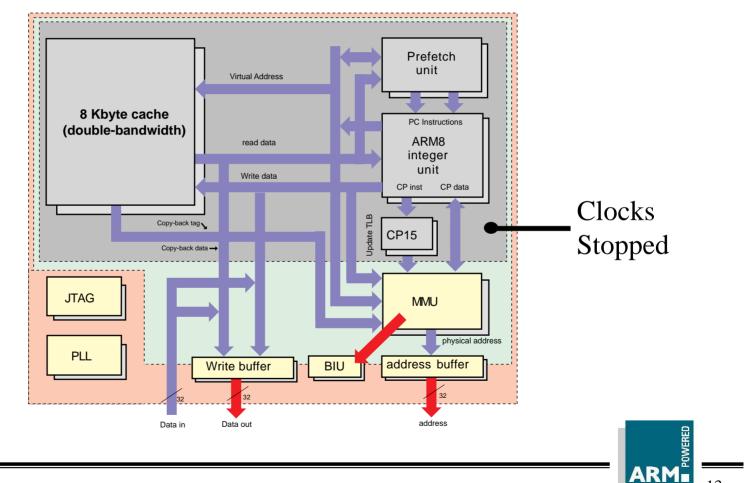

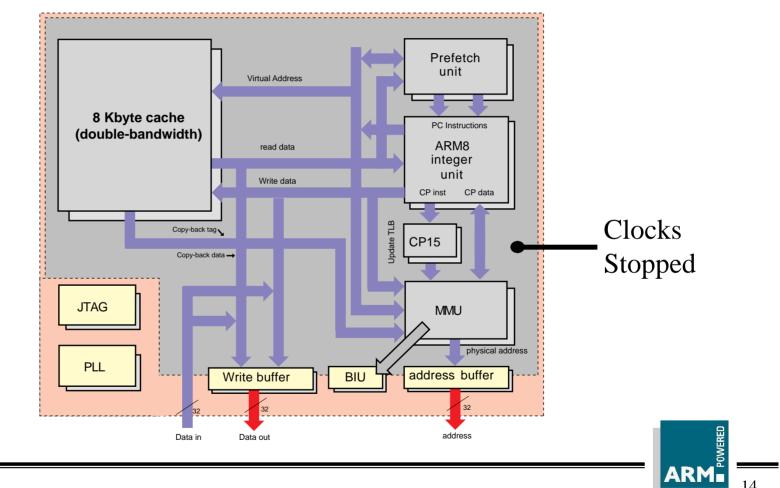

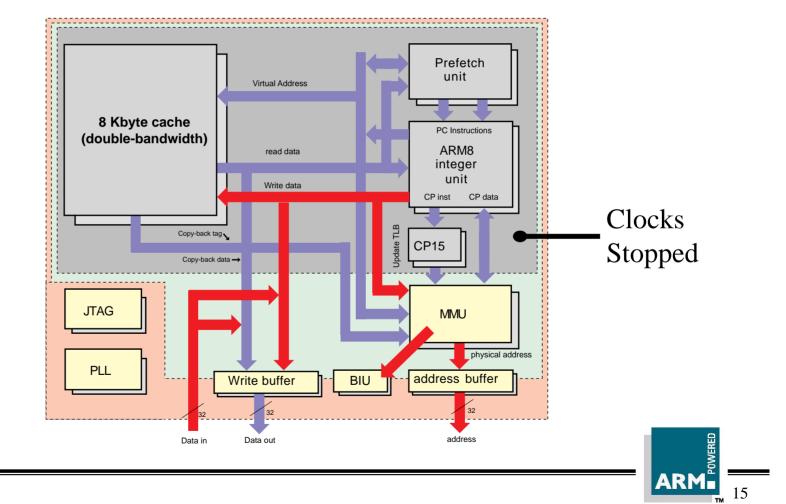

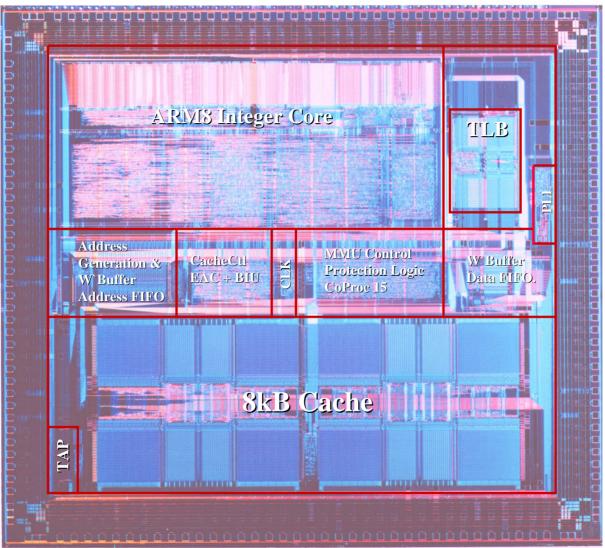

## **ARM810 Block Diagram**

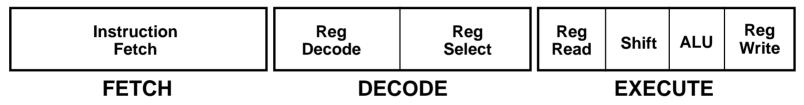

## **Pipeline changes for ARM8**

#### **ARM 7 Pipeline**

#### **ARM 8 Pipeline**

| Instruction<br>Fetch | Reg<br>Decode Reg | Complex Shift         | Memory<br>Access | Memory<br>Write |

|----------------------|-------------------|-----------------------|------------------|-----------------|

|                      | + Read<br>Select  | Simple Shift<br>+ ALU | ALU<br>Write     |                 |

| FETCH                | DECODE            | EXECUTE               | MEMORY           | WRITE           |

### **Integer Core CPI Improvement**

### ARM8 CPI ~ 1.4 ARM7 CPI ~ 1.9 Improvement achieved by

| Feature                     | % Improvement<br>over ARM7 |

|-----------------------------|----------------------------|

| Single Cycle LDR            | ~ 12 %                     |

| Single Cycle STR            | ~ 4 %                      |

| Double bandwidth<br>LDM     | ~ 6 %                      |

| Static Branch<br>Prediction | ~ 10 %                     |

| Total                       | ~ 35 %                     |

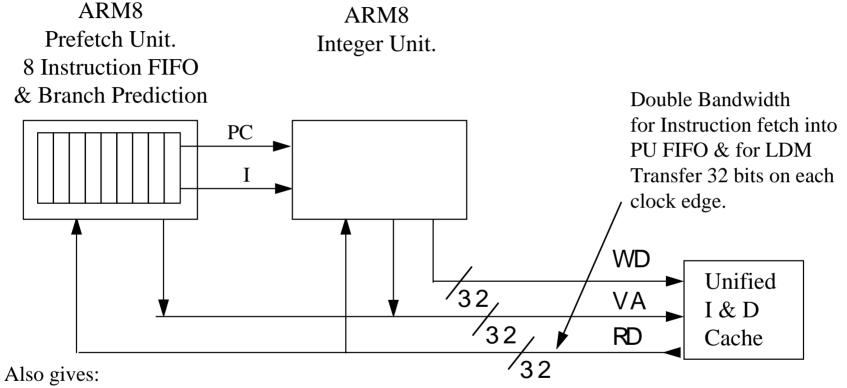

# **Satisfying Bandwidth Requirement**

Single memory port for ROM/SRAM (Cache-less) systems. Small number of Buses

### **Cycle Count Summary**

| Branch                                    | min 0                                            |                                 |          |       |

|-------------------------------------------|--------------------------------------------------|---------------------------------|----------|-------|

|                                           | max 3                                            | Incorrectly or Not Predicted    |          |       |

| Branch and Link                           | min 1                                            | Correctly Predicted             |          |       |

|                                           | max 3                                            | Not Predicted                   |          |       |

| Multiply and                              | min 3                                            | $32 \ge 8 \rightarrow 32$       |          |       |

| Accumulate                                | max 7                                            | $32 \ge 32 + 64 \rightarrow 64$ |          |       |

|                                           | Normal case                                      | Complex                         | 3rd read | Write |

|                                           |                                                  | Operand                         | operand  | to PC |

|                                           |                                                  | Shift *                         |          |       |

| Logical                                   | 1                                                |                                 | +1       | +2    |

| Add, Subtract                             | 1                                                | +1                              | +1       | +2    |

| Load Word, Half, Byte                     | 1                                                | +1                              |          | +4    |

| Store Word, Half, Byte                    | 1                                                |                                 | +1       |       |

| Load Multiple Words                       | $\lceil n/2 \rceil + 1$ where $n = \#$ registers |                                 |          | +4    |

| Store Multiple Wordsnwhere n = #registers |                                                  |                                 |          |       |

\* = Shift other than LSR by 0, 1, 2 or 3 bits

## **Cache Features**

- 8kB Unified Instruction and Data Cache

- 4 Words per Cache Line, 64-way associative

- Random Replacement Algorithm

- Cache supports Copy-Back and Write-Through operation

- Selectable per-page in page-table entry

- Copy-Back reduces write traffic to main memory

- $\rightarrow$  more main memory bandwidth available for DMA

- $\rightarrow$  lower system power

- Write-Though good for frame buffers and easy upgrade from ARM710

- Flexible Cache & TLB locking for real time applications

- Cache contents can be locked with granularity of 128 bytes

- Gives low interrupt latency / guaranteed execution time for real-time applications

# **Cache Implementation**

#### • Cache is virtually addressed $\rightarrow$ low power

- No address translation required for cache read-hits

- No address translation required for cache write-hits to copy-back regions

#### • Cache stores only virtual tags

Translate addresses for cache-line cast-outs when they occur

→ Avoids storing 512 lines \* 25 bits = 1.6kB of physical tags

### • Cache implemented from 1kB CAM-RAM segments

- Only 1 segment active for each access

- Segment selected by 3 bits of Virtual Address

- Easy to build cache size variants

### • Double bandwidth read port to ARM8

# ARM810 µArchitecture Design Style for Low Power

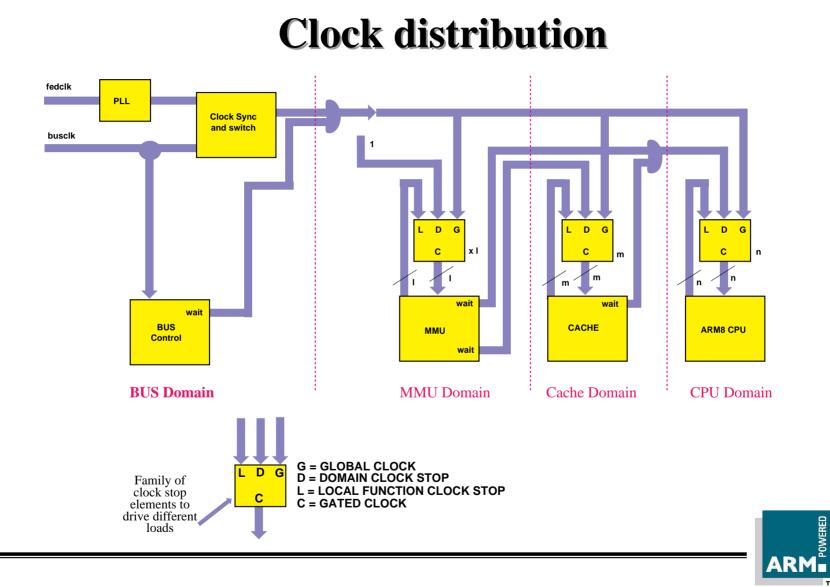

### • Hierarchy of Clocking Domains

Stop clocks to as much of chip as possible for each stall type or off-chip access.

e.g. TLB miss stops clocks to Cache and ARM8 until page-table walk completes.

When TLB requests use of bus, bus controller will stop clock to TLB until write buffer empties, making the bus available to the TLB.

### • Separate controllers for each clocking domain.

Yields modular control logic

e.g. No change to cache control or to ARM8 if MMU is removed.

### • Pipelined Cache and Bus Controller

- Maintain 1 write per cycle into cache and write-buffer while giving multiple cycles to resolve all controller scenarios.

- Yields low power via clean synchronous signal transitions on pins.

- Yields optimal use of sequential bursting on external bus.

07/08/96

#### **Example: TLB Miss following buffered writes**

#### Wait for write buffer empty

#### Page table walk completes

16

07/08/96

# **Design Methodology**

- Instruction Trace Analysis for Performance Evaluation

- Modelling and high level design validation in VHDL

- Logic Synthesis for complex combinatorial control logic

- Schematics for datapath, latch selection, and clocking

- Extensive static and dynamic timing analysis using EPIC tools on extracted transistor netlist.

- Power consumption sanity check using EPIC dynamic simulation.

- SPICE analysis for CAM-RAMs, datapath, FIFOs.

# **Implementation Technology**

- Full custom layout for Datapath, FIFOs, TLB, Cache CAM-RAMs.

- Standard-Cell for Control Logic.

- Combination of hand-routed and auto-routed layout composition.

- Process portable 0.6µm/0.5µm ruleset with proprietary automated conversion to target process, *except* ...

... Cache CAM-RAM Segments in target process rules.

### **ARM810**

07/08/96

### **ARM810 Development Team**