Microelectronics System Design Research Group School of Electrical and Electronic Engineering

## Redressing Timing Issues for Speed-Independent Circuits in Deep Sub-micron Age

Yu Li

Technical Report Series NCL-EEE-MSD-TR-2012-180

July 2012

Contact: yu.li1@ncl.ac.uk

NCL-EEE-MSD-TR-2012-180 Copyright © 2012 Newcastle University

Microelectronics System Design Research Group School of Electrical and Electronic Engineering Merz Court Newcastle University Newcastle upon Tyne, NE1 7RU, UK

http://async.org.uk/

# Redressing Timing Issues for Speed-Independent Circuits in Deep Sub-micron Age

## Yu Li Faculty of Science, Agriculture and Engineering Newcastle University

A thesis submitted for the degree of Doctor of Philosophy

2012 July

1. Reviewer:

2. Reviewer:

Day of the defence:

Signature from head of PhD committee:

## Abstract

With continued advancement in semiconductor manufacturing technologies, process variations become more and more severe. These variations not only impair circuit performance but may also cause potential hazards in integrated circuits (IC). Asynchronous IC design, which does not rely on the use of an explicit clock, is more robust to process variations compared to synchronous design and is suggested to be a promising design approach in deep-submicron age, especially for low-power or harsh environment applications.

However, the correctness of asynchronous circuits is also becoming challenged by the shrinking technology. The increased wire delays compared to gate delays and threshold variations could bring glitches into the circuit.

This work proposes a method to generate a set of sufficient timing constraints for a given speed-independent circuit to work correctly when the isochronic fork timing assumption is lifted into a weaker timing assumption. The complexity of the entire process is polynomial to the number of gates. The generated timing constraints are relative orderings between the transition events at the input of each gate and the circuit is guaranteed to work correctly by fulfilling these constraints under the timing assumption.

The benchmarks show that both the number of total constraints and the constraints that are only needed to eliminate strong adversary paths are reduced by around 40% compared to those suggested in the current literature, thus claiming the weakest formally proved conditions.

## Acknowledgements

I would like to express my gratitude to my supervisor, Prof. Alex Yakovlev, for his tremendous help during my Ph.D study. He gave me freedom when new ideas entered my mind and guided me to the right way when I was frustrated. His rigorous attitude to research and diligence to work gave me great encouragement not only in my Ph.D study but also in my future career.

I would like to thank Dr. Terrence Mak for his education on research in both technique aspect and non-technique aspect.

I would like to thank Dr. Fei Xia, Dr. Andrey Moknov and Dr. Danil Sokolov for reading through my thesis and helping me with my English.

I would like to thank Chao Jin and Liuyang Li for their inspiring discussion.

I would like to thank my whole group for their help on my life and for the joy they brought to me.

Especially, I would like to give thanks to my parents. For the incomputable hardships they conquered when bring me up.

# Contents

| Li       | st of          | Figures                                       | vi |

|----------|----------------|-----------------------------------------------|----|

| Li       | st of          | Tables                                        | x  |

| 1        | Intr           | oduction                                      | 1  |

|          | 1.1            | Synchronous and asynchronous circuits         | 1  |

|          | 1.2            | The data path and control path                | 6  |

|          | 1.3            | Significance of the thesis                    | 7  |

|          | 1.4            | Organization of thesis                        | 9  |

|          | 1.5            | Publications                                  | 10 |

| <b>2</b> | Bac            | kground                                       | 11 |

|          | 2.1            | Gate                                          | 11 |

|          | 2.2            | Delay models and types                        | 13 |

|          | 2.3            | Signal and Circuit                            | 14 |

|          | 2.4            | Operation modes                               | 15 |

|          | 2.5            | Asynchronous control circuits                 | 16 |

|          |                | 2.5.1 Asynchronous design paradigms           | 16 |

|          | 2.6            | Discussions on the delay model of SI circuits | 20 |

| 3        | $\mathbf{Spe}$ | ed-independent Circuits                       | 23 |

|          | 3.1            | Why SI design                                 | 23 |

#### CONTENTS

|          | 3.2                  | Petri Net                                                                                                                                                                                                                                               | 25                                                                                                         |

|----------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|          | 3.3                  | Signal Transition Graph                                                                                                                                                                                                                                 | 28                                                                                                         |

|          | 3.4                  | State Graph                                                                                                                                                                                                                                             | 30                                                                                                         |

|          | 3.5                  | Summary                                                                                                                                                                                                                                                 | 33                                                                                                         |

| 4        | $\operatorname{Tim}$ | ning Issues in SI Circuits                                                                                                                                                                                                                              | 34                                                                                                         |

|          | 4.1                  | Timing assumptions in SI circuits                                                                                                                                                                                                                       | 34                                                                                                         |

|          | 4.2                  | Existing research on isochronic fork reliability                                                                                                                                                                                                        | 35                                                                                                         |

|          |                      | 4.2.1 Input negations                                                                                                                                                                                                                                   | 36                                                                                                         |

|          |                      | 4.2.2 Threshold variations                                                                                                                                                                                                                              | 37                                                                                                         |

|          |                      | 4.2.3 Buffer insertion                                                                                                                                                                                                                                  | 39                                                                                                         |

|          | 4.3                  | Recent research on isochronic fork relaxation                                                                                                                                                                                                           | 41                                                                                                         |

|          | 4.4                  | Summary                                                                                                                                                                                                                                                 | 46                                                                                                         |

|          |                      |                                                                                                                                                                                                                                                         |                                                                                                            |

| <b>5</b> | Haz                  | zard checking method                                                                                                                                                                                                                                    | <b>48</b>                                                                                                  |

| 5        | <b>Haz</b><br>5.1    | zard checking method<br>Introduction                                                                                                                                                                                                                    | <b>48</b><br>49                                                                                            |

| 5        |                      |                                                                                                                                                                                                                                                         |                                                                                                            |

| 5        |                      | Introduction                                                                                                                                                                                                                                            | 49                                                                                                         |

| 5        | 5.1                  | Introduction                                                                                                                                                                                                                                            | 49<br>50                                                                                                   |

| 5        | 5.1                  | Introduction                                                                                                                                                                                                                                            | 49<br>50<br>52                                                                                             |

| 5        | 5.1                  | Introduction                                                                                                                                                                                                                                            | 49<br>50<br>52<br>53                                                                                       |

| 5        | 5.1<br>5.2           | Introduction                                                                                                                                                                                                                                            | 49<br>50<br>52<br>53<br>55                                                                                 |

| 5        | 5.1<br>5.2           | Introduction5.1.1Overall flowDeriving the Local STG5.2.1Decomposition of a free-choice STG into MGs5.2.2Projecting MG components on operator signalsTiming ordering relaxation                                                                          | <ol> <li>49</li> <li>50</li> <li>52</li> <li>53</li> <li>55</li> <li>56</li> </ol>                         |

| 5        | 5.1<br>5.2           | Introduction5.1.1Overall flowDeriving the Local STG5.2.1Decomposition of a free-choice STG into MGs5.2.2Projecting MG components on operator signalsTiming ordering relaxation5.3.1Classification of arcs in the local STG                              | <ol> <li>49</li> <li>50</li> <li>52</li> <li>53</li> <li>55</li> <li>56</li> <li>58</li> </ol>             |

| 5        | 5.1<br>5.2           | Introduction5.1.1Overall flowDeriving the Local STG5.2.1Decomposition of a free-choice STG into MGs5.2.2Projecting MG components on operator signalsTiming ordering relaxation5.3.1Classification of arcs in the local STG5.3.2Arc relaxation algorithm | <ol> <li>49</li> <li>50</li> <li>52</li> <li>53</li> <li>55</li> <li>56</li> <li>58</li> <li>59</li> </ol> |

#### CONTENTS

|   | 5.5            | Optimal relaxation order 81                                                                                                                                          |

|---|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 5.6            | Top level algorithm                                                                                                                                                  |

|   |                | 5.6.1 Complexity analysis                                                                                                                                            |

|   |                | 5.6.2 Proof of correctness                                                                                                                                           |

|   | 5.7            | Delay padding to fulfill timing constraints                                                                                                                          |

|   | 5.8            | Summary                                                                                                                                                              |

| 6 | OR             | -causality Decomposition 91                                                                                                                                          |

|   | 6.1            | OR-causality 91                                                                                                                                                      |

|   |                | 6.1.1 OR-causality in relaxation case 2                                                                                                                              |

|   |                | 6.1.2 OR-causality in relaxation case 3                                                                                                                              |

|   | 6.2            | Decomposition of OR-causality                                                                                                                                        |

|   |                | 6.2.1 Generating the solution group                                                                                                                                  |

|   |                | 6.2.2 Decomposition according to the solution group 110                                                                                                              |

|   | 6.3            | Summary                                                                                                                                                              |

| 7 | $\mathbf{Res}$ | ults 119                                                                                                                                                             |

|   | 7.1            | Design example                                                                                                                                                       |

|   | 7.2            | Simulation and Analysis                                                                                                                                              |

|   | 7.3            | Benchmarks                                                                                                                                                           |

|   |                | 7.3.1 Description of the Tool $\ldots \ldots \ldots$ |

|   |                | 7.3.2 Results                                                                                                                                                        |

|   | 7.4            | Summary                                                                                                                                                              |

| 8 | Con            | clusion and Future Work 135                                                                                                                                          |

|   | 8.1            | Conclusion                                                                                                                                                           |

|   | 8.2            | Future work                                                                                                                                                          |

#### CONTENTS

| 8.2.1      | Non-free-choice place |

|------------|-----------------------|

| 8.2.2      | Not pure SI circuits  |

| References | 141                   |

| Index      | 152                   |

# List of Figures

| 1.1 | A synchronous circuit and the equivalent asynchronous circuit     | 2  |

|-----|-------------------------------------------------------------------|----|

| 2.1 | A logic gate                                                      | 12 |

| 2.2 | Pure delay and inertial delay                                     | 14 |

| 2.3 | The Huffman style asynchronous circuit and the Muller style asyn- |    |

|     | chronous circuit                                                  | 18 |

| 2.4 | A 2-input C-element                                               | 19 |

| 2.5 | Glitches with respect to delay models                             | 21 |

| 3.1 | A PN example                                                      | 26 |

| 3.2 | PN properties                                                     | 28 |

| 3.3 | An SI circuit with its $STG_{spec}$ and $STG_{imp}$               | 30 |

| 3.4 | An STG with its SG                                                | 32 |

| 4.1 | Glitches caused by inverter delay                                 | 36 |

| 4.2 | Glitch caused by threshold variation                              | 38 |

| 4.3 | Timing difference caused by buffer insertion                      | 40 |

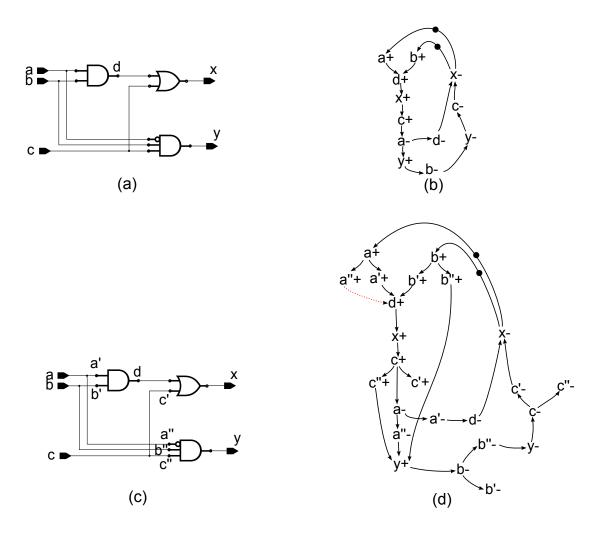

| 4.4  | (a) An SI circuit, (b) the STG corresponding to (a), (c) The SI                                        |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | circuit with all wires explicitly denoted by signals and $(d)$ the STG                                 |    |

|      | corresponding to (c) when the isochronic fork assumption is removed                                    | 43 |

| 4.5  | Intra operator fork timing assumption                                                                  | 44 |

| 4.6  | A counter-example                                                                                      | 44 |

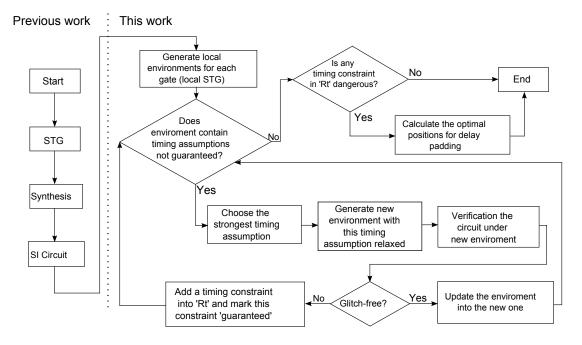

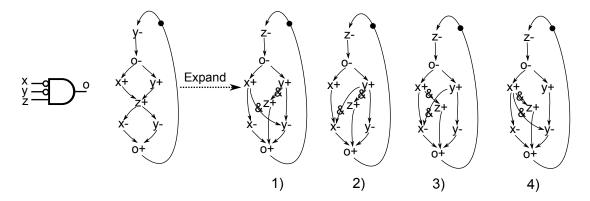

| 51   | The entire flow of this work                                                                           | 50 |

| 5.1  | The entire flow of this work                                                                           | 50 |

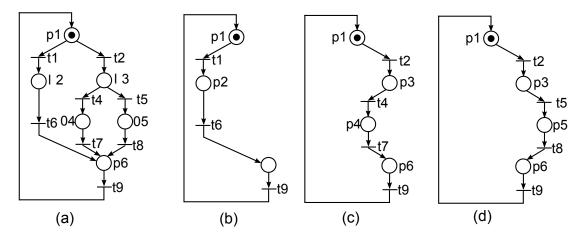

| 5.2  | A live and safe free-choice PN (a), and its MG components (b)-(d)                                      | 54 |

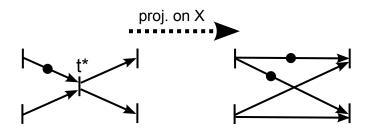

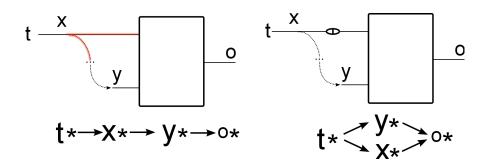

| 5.3  | Projection of an STG segment on X and $t \notin X$                                                     | 56 |

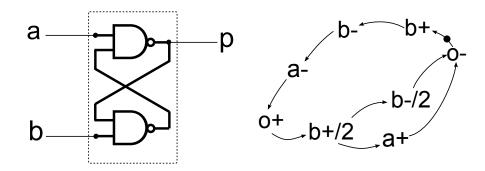

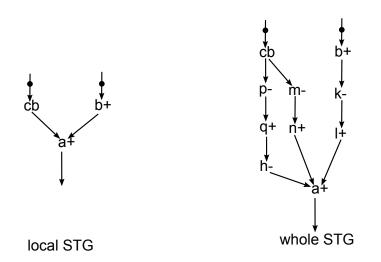

| 5.4  | An $\overline{SR}$ -latch with its local STG $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 59 |

| 5.5  | Demonstration of a type (4) arc                                                                        | 60 |

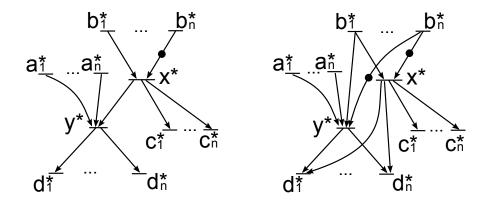

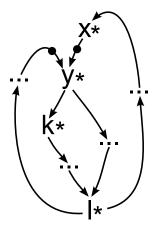

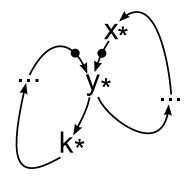

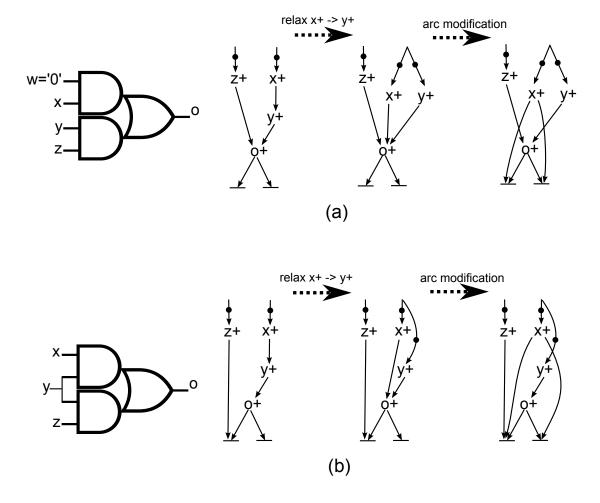

| 5.6  | relaxation of arc $x^* \Rightarrow y^*$ in the most general case                                       | 61 |

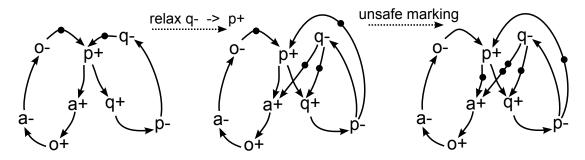

| 5.7  | un-safeness caused by relaxation                                                                       | 63 |

| 5.8  | possible unsafe places after relaxation                                                                | 63 |

| 5.9  | If two cycles have a common vertex $l$                                                                 | 64 |

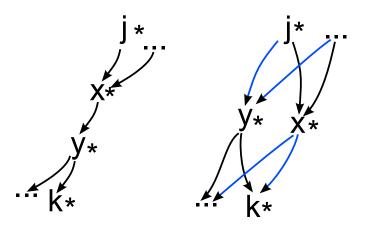

| 5.10 | Shape of MG that will have an unsafe place $\langle x*, k* \rangle, k* \in y*^{\triangleright}$        |    |

|      | after relaxing $x^* \Rightarrow y^*$                                                                   | 66 |

| 5.11 | Shape of the MG that will have an unsafe place $< j*, y* >, j* \in \triangleleft$                      |    |

|      | $x*$ after relaxing $x* \Rightarrow y*$                                                                | 66 |

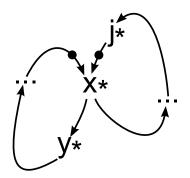

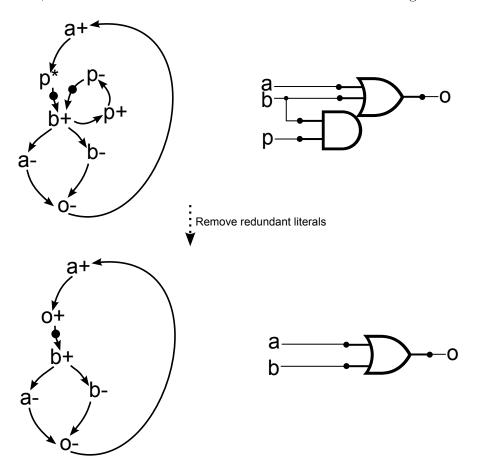

| 5.12 | Gate $o$ has a redundant literal $p$                                                                   | 67 |

| 5.13 | redundant arcs due to the relaxation                                                                   | 68 |

| 5.14 | Property of shortcut places                                                                            | 70 |

| 5.15 | Check for shortcut places using Dijkstra's algorithm                                                   | 72 |

| 5.10      | 6 Illustration of timing conformance. (a) the gate and (b)-(d) local      |     |

|-----------|---------------------------------------------------------------------------|-----|

|           | STGs and the corresponding SGs                                            | 74  |

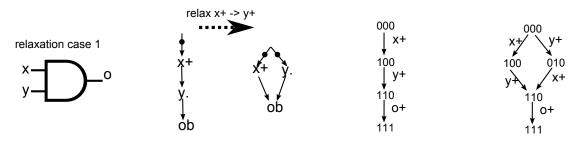

| 5.1'      | 7 Relaxation case 1                                                       | 75  |

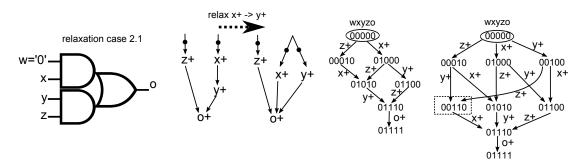

| 5.18      | 8 Relaxation case 2                                                       | 76  |

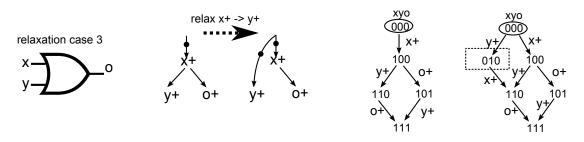

| 5.19      | 9 Relaxation case 3                                                       | 77  |

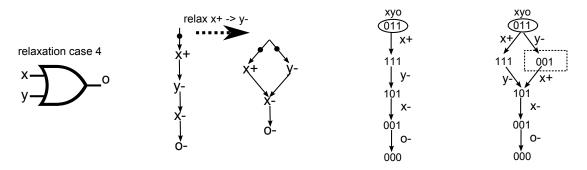

| 5.20      | O Relaxation case 4                                                       | 78  |

| 5.2       | 1 Arc modification in case 2. (a) without OR-causality and (b) with       |     |

|           | OR-causality.                                                             | 80  |

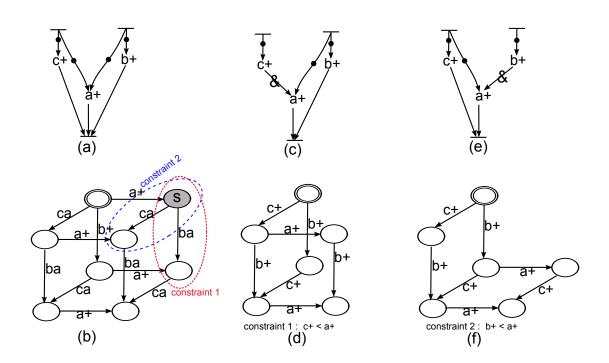

| 5.22      | 2 Preventing the gate entering hazardous state $s$                        | 82  |

| 5.23      | 3 Different timing constraints due to different relaxation ordering .     | 83  |

| $5.2^{4}$ | 4 Calculate the weight of an arc from $STG_{imp}$                         | 84  |

| 5.2       | 5 Padding positions                                                       | 89  |

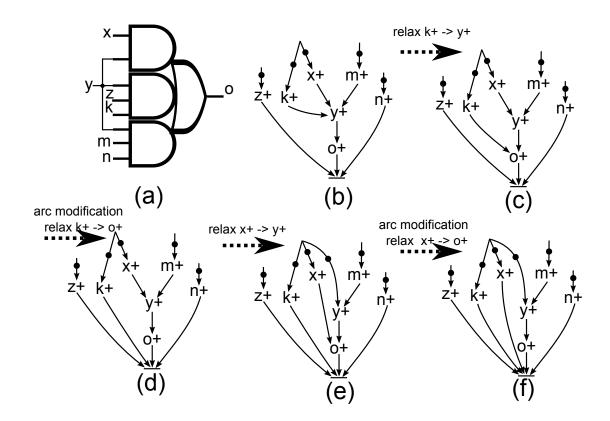

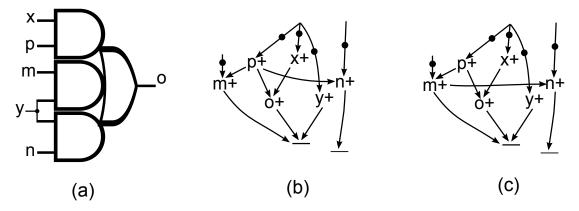

| 6.1       | OR-causality in relaxation case 2. (a) the gate and (b)-(f)relaxation     |     |

|           | steps                                                                     | 94  |

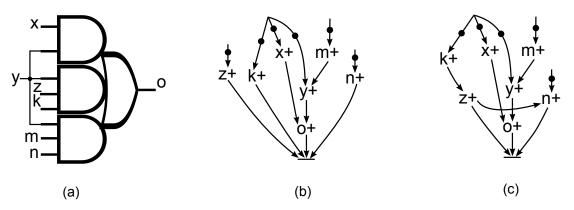

| 6.2       | Candidate clause and transition for OR-causality in relaxation case       |     |

|           | 2. (a) the gate, (b) and (c) two different STG segments $\ldots$ $\ldots$ | 96  |

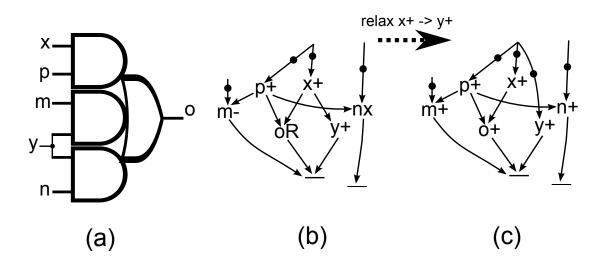

| 6.3       | OR-causality in relaxation case 3. (a) the gate, (b) and (c) two          |     |

|           | different STG segments                                                    | 98  |

| 6.4       | Candidate clause and transition for OR-causality in relaxation case       |     |

|           | 3. (a) the gate, (b) and (c) two different STG segments $\ldots$ .        | 100 |

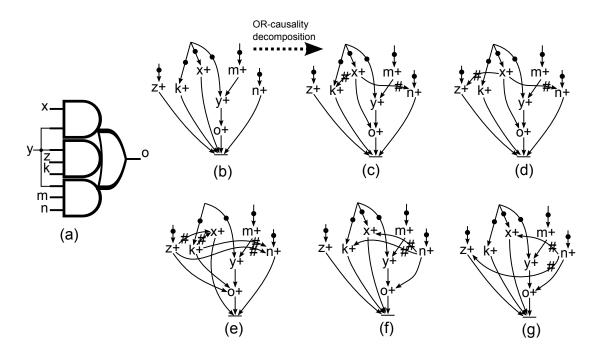

| 6.5       | OR-causality decomposition example. (a) the gate, (b) STG seg-            |     |

|           | ment before decomposition and (c)-(g)resulting subSTG segments            | 102 |

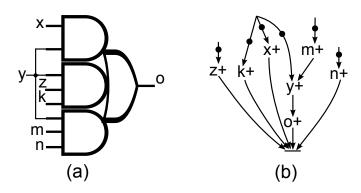

| 6.6 | An OR-causality relation in case 2. (a) the gate and (b) its local              |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | STG segment                                                                     | 114 |

| 6.7 | Decomposition results for the OR-causality relation in Figure 6.6.              |     |

|     | (a)-(e) resulting subSTG segments                                               | 115 |

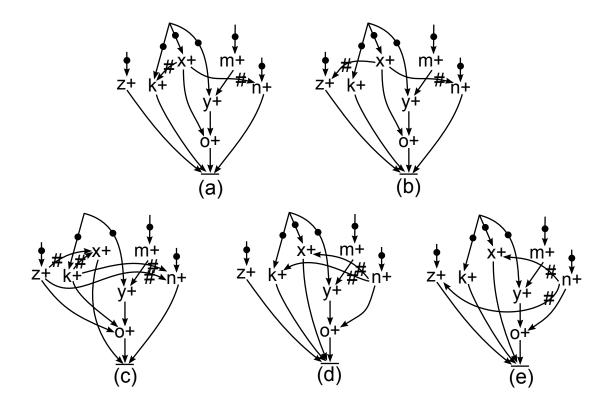

| 6.8 | An OR-causality relation in case 3. (a) the gate and (b) its local              |     |

|     | STG segment                                                                     | 116 |

| 6.9 | Decomposition results for the OR-causality relation in Figure 6.8.              |     |

|     | (a)-(d) resulting subSTG segments                                               | 117 |

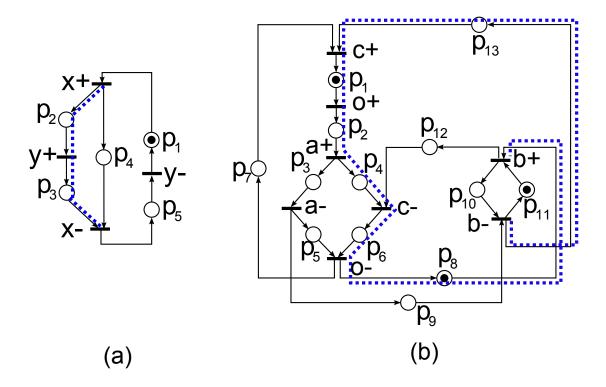

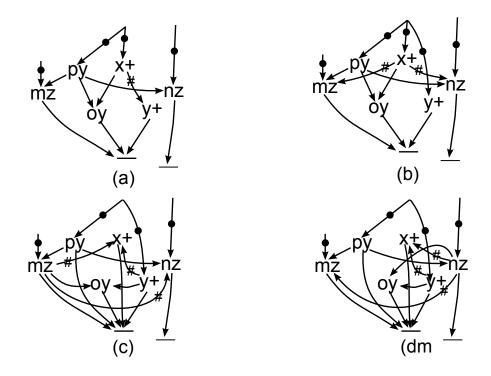

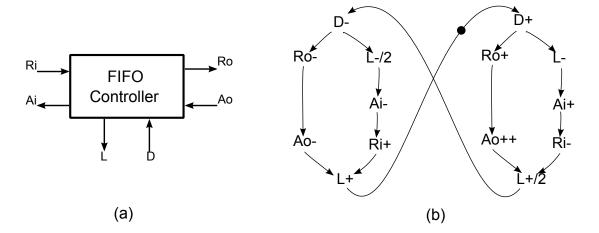

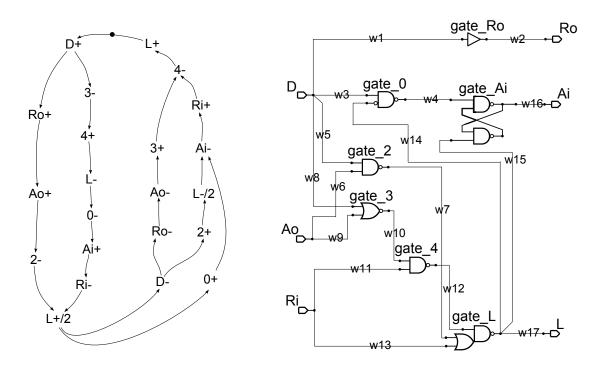

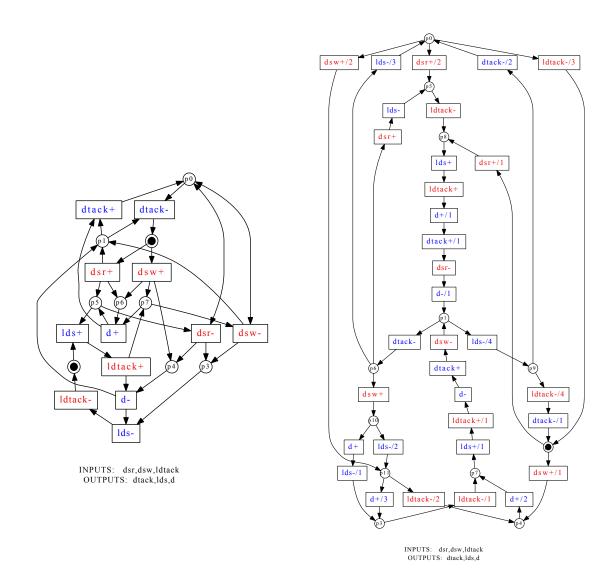

| 7.1 | The block diagram and STG specification of FIFO                                 | 120 |

| 7.2 | The implementation STG and circuit diagram of FIFO                              | 121 |

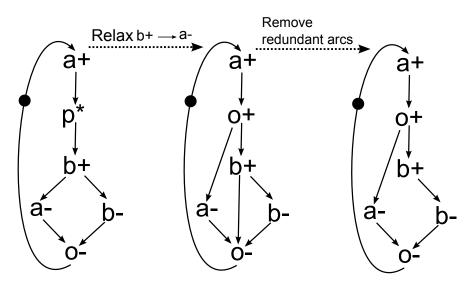

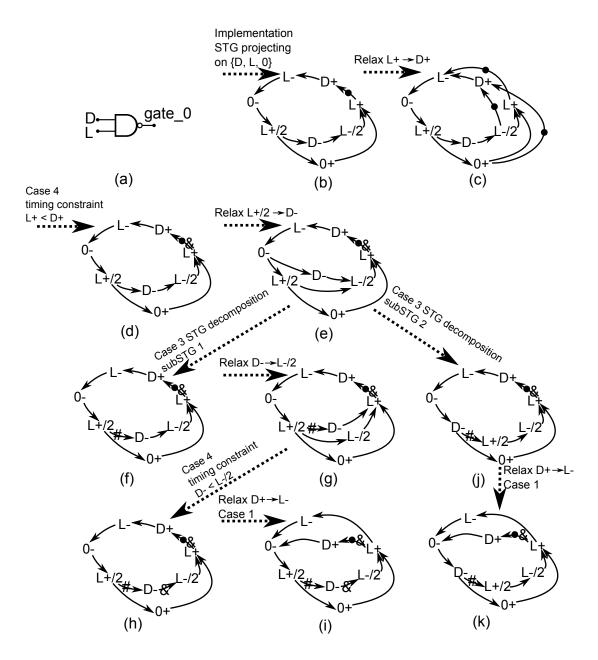

| 7.3 | The STG relaxation procedure of the gate $_0$                                   | 122 |

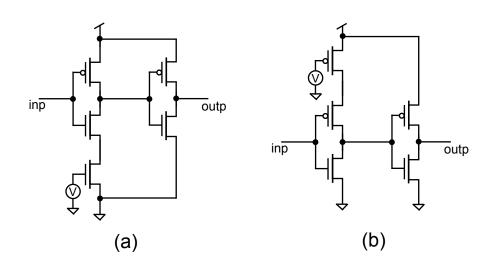

| 7.4 | The current starved delays. (a) controlled delay for rising transi-             |     |

|     | tion and (b) controlled delay for falling transition $\ldots$ $\ldots$ $\ldots$ | 125 |

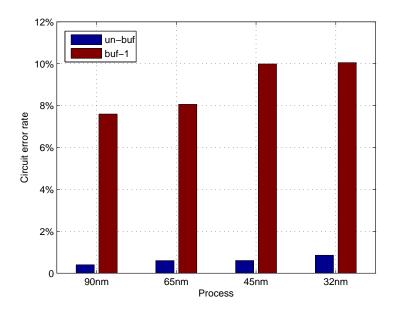

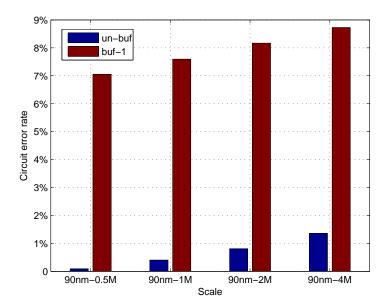

| 7.5 | The trend of error rate as the technology shrinks                               | 126 |

| 7.6 | The trend of error rate as the scale increases                                  | 127 |

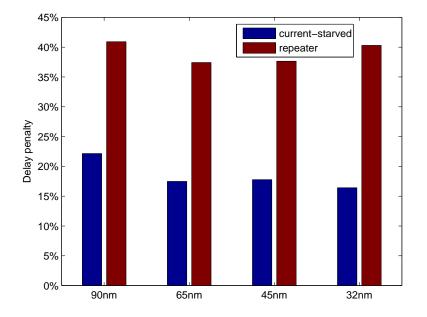

| 7.7 | The delay penalty                                                               | 128 |

| 8.1 | A non-free choice STG and its equivalent free-choice STG                        | 139 |

# List of Tables

| 7.1 | List of timing constraints           | • | • | • | • | • | • | • | ••• | • | • | • | • | • | • | • | 124 |

|-----|--------------------------------------|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|-----|

| 7.2 | Comparison of the timing constraints | • | • |   | • | • |   | • |     |   | • | • |   |   | • | • | 133 |

## Chapter 1

## Introduction

As the process shrinks, the traditional synchronous design faces great challenges. Meanwhile, the asynchronous design exhibits advantages in many important aspects, such as the tolerance to process variation and reduced power consumption. This chapter briefly compares the advantages and disadvantages of synchronous and asynchronous designs to illustrate why the asynchronous design suggests a promising design approach in the near future.

## 1.1 Synchronous and asynchronous circuits

Digital circuits can be partitioned into combinational logic, in which the output signals depend only on the current input signals, and sequential logic, in which the output depends both on current input and the past history of inputs(state of the circuit). Sequential logic is combinational logic with storage components (latches). In synchronous circuits all latches change according to the same periodic global signal, called the *clock*. Inputs to latches must be stable before clock events arrive and all latches change simultaneously when the clock events arrive. Clock is used to synchronize the data transferring between combinational logic blocks and filter out unexpected transient events (called glitches) before the circuit becomes stable. In contrast, asynchronous circuits do not use the clock. Operation on one latch is triggered by the events coming from its controller, which communicates with other controllers by handshake protocols.

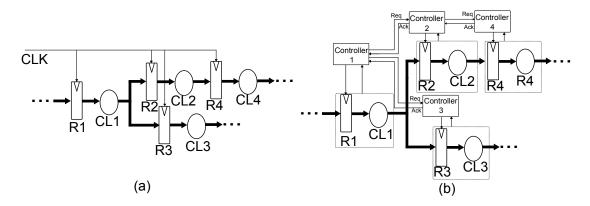

Figure 1.1: A synchronous circuit and the equivalent asynchronous circuit -

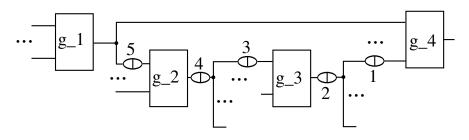

The schematic diagram of a synchronous circuit is shown in the diagram (a) in Figure 1.1 with the schematic diagram of the equivalent asynchronous circuit shown in diagram (b). In the synchronous circuit, four registers (R1-R4) are controlled by the clock signal (CLK). The clock cycle period must be greater than the worst delay of all combinational logic blocks in the circuit and all combinational logic blocks (CL1-CL4) will be synchronized by the end of each clock cycle. However, in the asynchronous circuit, the clock is not used. The transformations

on the data are synchronized by the handshake signals. Request (Req) will be sent to the controller of the sink of the data from the source controller when the data from the source is ready and the acknowledge (Ack) will be sent back to indicate the completion of the operation.

Thanks to the Moore's law<sup>[1]</sup>, the complexity of the integrated circuit doubles every 18 months. Nowadays, a single chip could contain more than one billion transistors. Certain problems, which were not quite severe in the last few decades, are becoming critical today or will be critical in the near future. The synchronous design, which introduces a global clock to mask glitches and divide the combinational and sequential logics, has been the mainstream in the digital integrated circuit community. However, the weakness of synchronous design is exposed when the semiconductor technology shrinks.

#### Performance and power:

It is very costly to distribute a global clock signal on a multi-billion transistor chip. Clock signal skews along the large distribution tree. As the number of transistors increases and the delay of transistor decreases, the clock skew problem becomes more and more severe. Additional area or clock magnitude needs to be sacrificed in order to guarantee the correctness of the circuit. In addition, the power consumption related to the distribution clock signal consumes the largest proportion in a synchronous circuit. Currently, up to 40% of total power is consumed by the clock distribution network [2] and this situation becomes worse as the complexity and the frequency of the circuit grows [3].

Meanwhile, although the clock could prevent glitches from causing errors in synchronous circuits, glitches do dissipate energy. Glitches are useless transitions, which could propagate in the combinational logics and cause additional transitions. As reported in [4], the power dissipation related to glitches in CMOS technology consumes up to 15% of total power.

As the feature size of technology shrinks, the process variations become a new important factor that influences the performance of digital circuits. In order to get an acceptable yield, synchronous design needs to set its clock period conservatively.

Unlike the synchronous design in which glitches could be filtered out by the clock, asynchronous circuits are usually vulnerable to glitches. The handshake protocols cannot distinguish between a real transition and a glitch. Any glitch could be considered by some logic as a premature transition and causes hazards. Designers of asynchronous circuits usually put quite a lot of effort to avoid dangerous races in the circuit. This always results in that asynchronous design consumes more area and efforts compared to the synchronous design. Due to the simplicity, synchronous design dominates the integrated circuit market during past decades. But, as the mobile electronics devices become the mainstream of the consumer electronics, the performance and energy dissipation become the two most concerned aspects for industry designs. In contrast, the area now becomes a less concerned aspect. All those above indicate that asynchronous circuits suggest a promising design paradigm, which offers a high performance and low power consumption solution in the coming decades for both the technical and commercial reasons.

#### Modularity:

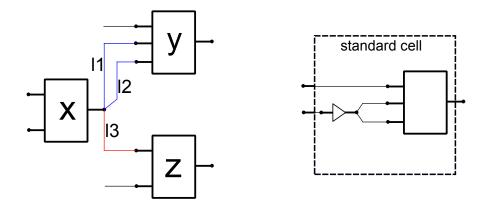

The circuit design trends to compose a powerful system by many small com-

putational modules or intellectual property (IP) cores, which communicate with each other through protocols to achieve higher energy efficiency. Directly connecting multiple synchronous modules together is very difficult if not impossible. The asynchronous handshake suggests a promising approach to be the interface protocol to connect sub-modules. As expected by ITRS [5], by 2022, up to 45% signals of a design will be driven by handshake.

Without doubt, asynchronous circuits will attract more designers' attention in the coming decades. The inherent request and acknowledgement mechanism can avoid the clock skew and distribution problem. Also, this mechanism will automatically shut down unused parts in a circuit and avoid generating the unneeded transitions and thus reduces the power consumption. Different modules could be easily connected together under protocol based scheme. The strict glitch-free requirement and the conservative delay assumption makes asynchronous circuits have much stronger variation tolerance ability compared to the synchronous counterpart.

However, the asynchronous design paradigm also meets challenges.

Without the clock to filter out glitches, asynchronous circuits suffer from race hazards[6], which means that circuits might exhibit glitches or even go into the wrong state depending on differences in delay of elements in circuits. In order to avoid race hazards, the synthesis of asynchronous circuits needs to fulfill additional requirements. These requirements make asynchronous circuits more difficult to design compared with synchronous circuits. Also, the automatic synthesis of asynchronous circuits usually needs to explore the entire state space to fulfill the hazard-free requirement and optimize the logic. Asynchronous circuits

usually exhibit highly concurrency among events. The computation complexity is in the order of  $O(2^n)$ , with respect to the number of signals (n) in the circuit. This makes asynchronous circuits hard to design even in moderate size.

Asynchronous circuit design paradigm does not have an entire design flow support. The EDA tool support for asynchronous design is poor, not only because there is no uniformed design paradigm but also the real difficulty behind this matter. Also, the asynchronous circuit is not only hard to design but also to test.

Due to the problems mentioned above, designing asynchronous circuit always requires experienced designers. Therefore, the time cost for designing asynchronous circuit is usually much greater than for designing a synchronous one.

Nowadays, the semiconductor technology goes into deep sub-micron age and the design trends to many-core, low power, environment variation robust and process variation tolerance applications. These requirements just meet the characteristics of asynchronous circuits.

### 1.2 The data path and control path

A circuit is typically partitioned into two main parts, the data path and the control path. The data path usually includes the units to process the data, e.g. adders and the units for storage and communication e.g. registers. The control path usually provides signals that control the data path to work properly, e.g. operation codes and the clock signal. In Figure 1.1, the control of the two circuits includes the clock (CLK) and asynchronous controllers; the datapath includes registers and the combinational logic. This thesis focuses on controllers in asyn-

chronous circuits (like the controllers 1-4 in diagram (b) in Figure 1.1. Circuits discussed in this thesis refer to the control circuits if not specified otherwise.

### **1.3** Significance of the thesis

Among all asynchronous design paradigms, delay-insensitive circuits, which could tolerate arbitrarily large delay variations on both gates and wires, show the strongest process variation tolerance ability. However, delay-insensitive circuits have been proved to be quite limited that only a very small set of specifications have a delay-insensitive implementation[7]. This also indicates that for almost all useful specifications, the implementations should contain some timing assumptions in them. Speed-independent circuits, which only take the isochronic fork timing assumption, are supposed to be the paradigm that imposes the weakest timing assumption. Speed-independent circuits could work correctly under many harsh situations, e.g. VDD variations and the gate delay variations. However, the other variations like the threshold variation could still cause speed-independent circuits to malfunction.

Speed-independent circuits suggest a good starting point to correctly implement circuit under unprecedented variations. Unlike the design paradigms that introduce the real time information in synthesis, speed-independent circuits only compare the arriving orders of events. They therefore redress only those timing issues needed to guarantee the required orders. This is desirable in the deep submicron age. The delay variations are quite large that estimating the exact time is difficult and unreliable in the deep submicron age. However, orders between two events are much easier to predict and fix. Currently, most layout tools does not directly support relative timing constraints. This is because the synchronous design is widely adopted by the industry and synchronous tool is well developed where the numerical delay is used. However, the layout tool for the asynchronous design that supports the relative timing constraints could be developed as the asynchronous design becomes more and more important.

The verification of the timing fulfillment is a very difficult and time consuming task. The time complexity usually reaches the exponential or even double exponential order with respect to the number of signals in a circuit. This is hardly acceptable even for a moderate scale circuit.

This thesis proposes an efficient method to verify and re-synthesize speedindependent circuits. It takes a reasonably weaker timing assumption compared to the isochronic fork timing assumption and then introduces a series of algorithms to verify circuit and generate a set of sufficient timing constraints to guarantee the correctness of the circuit. The generated timing constraints could always be fulfilled.

The main contributions of this thesis are:

1) It corrects some wrong conclusions given by previous researchers about the weakest timing assumption in speed-independent circuits.

2) It introduces a hazard checking criterion for speed-independent circuits when the isochronic fork timing assumption is relaxed.

3) Most importantly, this thesis proposes a method utilizing properties of the speed-independent circuit to do the timing verification in polynomial time. This method divides the entire verification problem into smaller sub-problems and thus

avoids exploring the full state space.

The limitation of this thesis is that in the point 3) mentioned above, one operation "projecting a Petri Net on a subset of transitions" is needed. However, this is an open question for general Petri Nets. Thus, the input signal transition graph to this technique (one kind of Petri Net) is limited to a free-choice Net, where Hack's algorithm[8] could apply.

### **1.4** Organization of thesis

This thesis is organized as follows:

**Chapter 1** briefly introduces the synchronous and asynchronous design and presents the significance of this thesis.

Chapter 2 defines the terms used in asynchronous community and introduces different asynchronous design paradigms.

**Chapter 3** introduces the related descriptions and models of speed-independent circuits, which will be used in the following chapters and explains why speed-independent circuits are adopted by this thesis among asynchronous design paradigms.

Chapter 4 investigates the possible situations that could cause failures of the isochronic fork and discusses the technology trends that affect these situations. Also, related research is overviewed in this chapter.

Chapter 5 presents the main method for hazard checking when the fundamental timing assumption of speed-independent circuits is relaxed.

**Chapter 6** analyzes one complex problem, the OR-causality, which may occur during the hazard checking process presented in Chapter 5 in detail and proposes

a technique to solve this problem.

**Chapter 7** presents the benchmark results of the method. This chapter compares the tightness of the generated timing constraints with similar research. Also one design example is presented in detail to demonstrate the proposed method and to show the penalty introduced by eliminating the potential hazards.

Chapter 8 concludes the thesis and discusses the possible ways to break the limitations of the proposed method to make it suitable for broader range of specifications.

## 1.5 Publications

The main results of the thesis have been published in the following paper:

• "Relative Timing Applied to Asynchronous Circuit Synthesis and Decomposition" (19th UK Asynchronous Forum)

• "Conditions and Techniques for Correctness of SI/QDI Circuits Under Large Variability" (21st UK Asynchronous Forum)

• "Redressing timing issues for speed-independent circuits in deep submicron age" (DATE'11)

## Chapter 2

## Background

This chapter gives the definitions of basic elements and concepts of a digital circuit and also introduces popular asynchronous design paradigms.

## 2.1 Gate

Gates are basic elements in a circuit. In this thesis, a *gate* is defined as an n inputs and *one* output boolean variable. If the inputs contain its output variable, the gate is sequential, otherwise it is combinational. For every gate there is an associated logic function f to compute it.

The definition of logic function in [9] is adopted.

A logic function f with n input variables is a mapping  $f : \{0, 1\}^n \mapsto \{0, 1\}$ , where  $\{0, 1\}^n$  is a binary vector over its input variables called *input state*. The set of input states that maps to '1' is the *on-set* of f, while that maps to '0' is its *off-set*. A literal is a variable x or its complement  $\overline{x}$ . A cube c is a set of literals on different variables, which means that literal x cannot appear multiple times and x and  $\overline{x}$  cannot appear simultaneously in a cube. A cube c represents the vertexes corresponding to the boolean product of its literals. A cube c' is covered by another cube c'' if  $c'' \subseteq c'$ , denoted by  $c' \sqsubseteq c''$ .

A cube is an *implicant* of a logic function f if it does not cover any vectors in off-set of f. An implicant of f is called a *prime implicant* if it cannot be covered by any other implicants of f. A cover U is a set of cubes, which represents the boolean sum of its cubes. A cover U is an on-set cover of logic function f if each cube in U is an implicant of f and each vertex in f is covered by at least one cube in U. A cover D is an off-set cover of logic function f if D is an on-set cover of  $\overline{f}$ , where  $\overline{f}$  is a logic function obtained by exchanging the on-set and off-set of f. A cover U is a prime cover of logic function f if all its cubes are prime implicants of f. A cube c is redundant in a cover D of logic function f, if  $D \setminus c$  is still a cover of f. A cover D is redundant for f if at least one cube in it is redundant, otherwise it is irredundant. An irredundant prime cover of logic function f is denoted by  $f_{\uparrow}$  and an *irredundant prime cover* of  $\overline{f}$  if denoted by  $f_{\downarrow}$ . Each cube in  $f_{\uparrow}$  and  $f_{\downarrow}$ is called a clause. The notation  $f_{a\uparrow}$  and  $f_{a\downarrow}$  is used if f computes gate a.

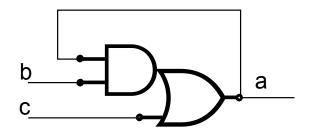

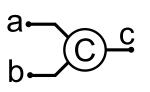

Figure 2.1: A logic gate -

An example of a gate a is shown in Figure 2.1, the gate a is a sequential gate. Its inputs are a, b and c.  $f_{a\uparrow} = a \cdot b + c$  and  $f_{a\downarrow} = \overline{a} \cdot \overline{c} + \overline{b} \cdot \overline{c}$ .

### 2.2 Delay models and types

Delay is an inherent property of all electronic components. For simplicity, in digital circuits, the delays are usually abstracted out of the component and are denoted as separated elements. The original components are then assumed to be instantaneous. The property of delay is depicted by a separated delay element. For different designs and circumstances, different delays are used [6].

A delay element is a *pure* delay if the delay only shifts every transition for a given magnitude.

A delay element is an *inertial* delay if the delay not only shifts transitions but also absorbs any pulse that is narrower than the magnitude of the delay.

A delay is *unbounded* if the magnitude of the delay could be any positive value. A delay is *bounded* if the interval of the delay magnitude is given.

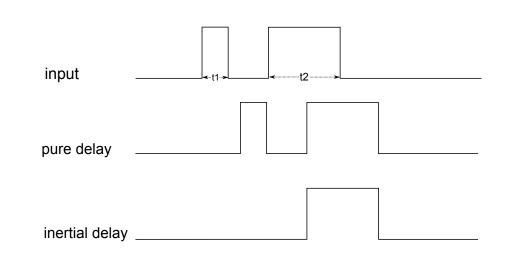

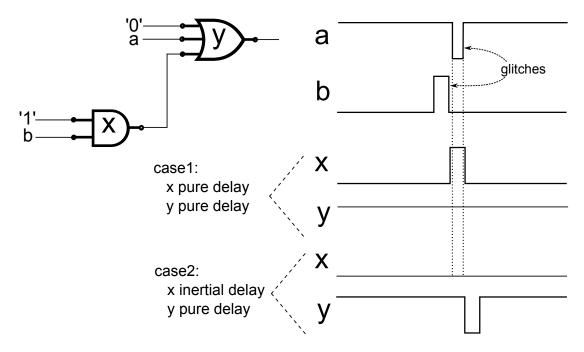

Figure 2.2 represents the comparison of the pure delay with the inertial delay. The delay magnitudes for these two delays are larger than t1 but smaller than t2.

In speed-independent circuits, every gate has a pure and unbounded delay and each wire does not have any delay. The effect of this assumption is that every gate computes its new output as soon as its inputs change and if there is a transition due to the input change, the transition will be delayed for a given time and then transmitted to its next-level simultaneously. The pure delay assumption is always much safer compared to the inertial delay assumption with respect to

Figure 2.2: Pure delay and inertial delay -

glitch-freedom as will be analyzed in the following section.

## 2.3 Signal and Circuit

Transitions on signals represent the dynamics of a circuit. The set of signals should depict the entire reachable states of a circuit. Here, we define the signals of a circuit (denoted by the set A) to be the union of the primary input variables and gate variables. For circuits which are in context with their environment (ENV), the signals coming from the primary inputs are denoted by a set I, the gate variables which feedback to the ENV are primary outputs denoted by a set O and the gate variables that are not primary outputs are internal signals denoted by a set R. For autonomous circuits, we have  $I = O = \emptyset$  and R = A.

A circuit is defined as a pair  $C = (A, \varphi)$ , where A is a set of signals and  $\varphi$  is a labeling function which labels a wire between each signal  $a \in I \cup R$  and each fan-out of a. In the definition above, only input signals and gate variables are used to describe the dynamics of a circuit, wires will not be shown explicitly. This is because the type of the asynchronous circuit under discussion is the speed-independent circuit, where wires could be considered to have zero delays, the dynamics of wires could be fully represented by the gate behaviors. When the isochronic fork is relaxed (as will be specified in the following chapters), we will still use techniques to avoid introducing signals to wires. The reason behind this is as follows. Firstly, the number of wires is always equal to or more than the number of gates in a circuit, so encoding using wire signals would increase the computational complexity. Secondly, introducing signals to wires will break some properties that are necessary for us to model the behavior of speed-independent circuits (will break the safeness of a PN).

### 2.4 Operation modes

The interface mode defines how a circuit interacts with its environments. There are two classical modes [6] that adopted by different asynchronous design paradigms:

1) The *fundamental mode/burst mode*, when the circuit is stable, one primary input/one or more primary inputs are allowed to change. The environment cannot change inputs again unless the entire circuit becomes stable.

2) The *input-output mode*, the environment could change the primary inputs of the circuit as soon as it sees the expected transitions on primary outputs.

The fundamental mode requires that the environment keeps all transitions on primary input signals longer than the maximum delay in the circuit. This requires designer to estimate the real delays in a circuit. While input-output mode requires that every signal transition is acknowledged to make sure that when the environment sees the expected transitions on primary outputs, all internal signal transitions have happened.

### 2.5 Asynchronous control circuits

The class of asynchronous circuits is a very broad class. Different researchers often propose quite different design flows, where different specification formalisms, various assumptions, synthesis techniques and manpower are utilized. This section will focus on the introduction of popular asynchronous design methods and their trade-offs. Circuits discussed in this section refer to the control circuits if not specified otherwise. Also, methods referred in this thesis are mainly related to the design of control. The datapath usually contains a large number of signals in high concurrency. Techniques that focus on the control are usually not capable of handling datapath and the synthesized circuits would be inefficient. However, a large body of research exists for datapath circuits as well[10] [11] [12].

#### 2.5.1 Asynchronous design paradigms

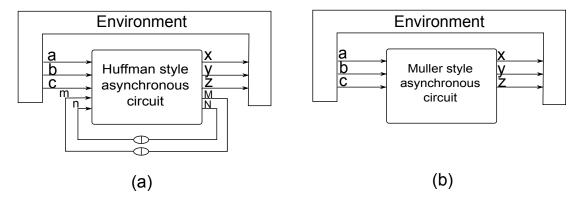

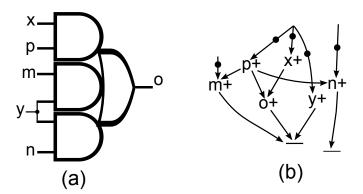

The Huffman style asynchronous circuits: The Huffman style asynchronous circuits are first proposed in [13], which take the bounded wire and gate delay model and operate under the fundamental mode. The schematic diagram of the Huffman style asynchronous circuits is shown in Figure 2.3 (a).

The specification of the fundamental mode Huffman style asynchronous circuits is often a Huffman flow table which represents an asynchronous finite state machine (ASFM). The circuit consists of primary input signals (a, b, c in Figure 2.3 ), primary output signals (x, y, z), state signals (feedback signals from output to input, M, N, m, n) and the combinational part of the circuit. In the initial state, one input of the circuit is allowed to change. Then the combinational part of the circuit starts to compute the new output value and the next state value. When the environment receives the new output value, it cannot provide a new input transition until the circuit becomes stable after receiving the next state value.

The Huffman style asynchronous circuits, which are quite similar to the synchronous circuits, are easier to design compared to those in other design methods. But this kind of circuits has two limitations. Firstly, the operations of the circuit must follow a strict order that one input must change first followed by the state signals and the output signals. Therefore, concurrency between the input changes and output changes is not allowed (also the finite state machine cannot depict this kind of concurrency). Secondly, delays or other techniques must be used to guarantee that the next state value cannot propagate to the combinational part too early and the environment does not provide a new input transition too early.

The fundamental mode Huffman style asynchronous circuits have the limitation that only one input could change at one time. The early work related to the synthesis of fundamental mode Huffman style asynchronous circuit is presented in [13] [14]. Steven Nowick proposed a burst mode Huffman style asynchronous paradigm in [15], which expanded the concurrency to allow a constrained set of input signals (input burst) to change concurrently. However, the burst mode asynchronous circuits still do not allow the concurrencies between input bursts and output bursts and still require the timing constraints in the fundamental mode. The synthesis of the burst mode asynchronous circuits is automated in the tool MINIMALIST[16].

The burst mode design style is further expanded by Yun and Dill into the extended burst mode design style [17][18], which allows an input signal to change concurrently with output signal and allows control flow to depend on the input levels. With these extensions, the burst mode design style covers a wide spectrum of sequential ranging from asynchronous to synchronous. The extended burst mode specification could be synthesized by the 3D synthesis tool[19].

Figure 2.3: The Huffman style asynchronous circuit and the Muller style asynchronous circuit -

The Muller style asynchronous circuits: Unlike the Huffman style asynchronous circuits, the Muller style circuits do not put so many restrictions on specifications and the environment. The schematic diagram of the Muller style circuit is presented in Figure 2.3 (b). The operation of the circuit is based on the following

protocol: the environment is allowed to provide new inputs as soon as it sees expected outputs. Also, the specification of Muller style circuits does not constraint the concurrency between signals. The design of input-output mode Muller style asynchronous circuits was introduced in [20] [21].

The Delay-Insensitive (DI) circuits:

The DI circuits are one kind of Muller style asynchronous circuits that work correctly even if every wire and gate has unbounded delay. A very important type of gate in DI circuits is a C-element. The symbol and the truth table of a 2-input C-element is shown in Figure 2.4. A more general definition for C-element is that output changes if and only if all of its inputs change. So, an inverter is also a 1-input C-element. Among all asynchronous design paradigms, only DI circuits do not have any timing assumption. So, DI circuits could tolerate arbitrary delay variations on their components.

But as was proved in [22], the DI circuits are quite limited: if an autonomous DI circuit is built of single output gates, then all gates must be C-elements. Moreover, the C-element itself does not have a DI implementation built of basic gates[23].

| а | b | С                       |

|---|---|-------------------------|

| 0 | 0 | 0                       |

| 0 | 1 | <b>C</b> <sub>n-1</sub> |

| 1 | 0 | <b>C</b> <sub>n-1</sub> |

| 1 | 1 | 1                       |

Figure 2.4: A 2-input C-element -

The Speed-Independent (SI) circuits:

The DI circuits are quite limited and most practical specifications do not have DI implementations. The SI circuits are usually adopted to enlarge specifications that could be synthesized. As was proved in [24], there exists an SI implementation for any deterministic computation<sup>1</sup>. The SI circuits also allow unbounded delays on gates, but wires in a fork must have the same magnitude delay. If the delays on wires in a fork (since they have the same magnitude) are combined into the corresponding gate delay, the timing assumption behind the SI circuits is equal to say that gates in an SI could have unbounded delays but wires are instantaneous.

#### 2.6 Discussions on the delay model of SI circuits

Glitches are unwanted transitions on a signal often generated by the delay variations on gates and wires. Synchronous circuits could use the clock to filter the glitches to prevent them from causing hazards. While in asynchronous circuits, especially for the circuits in input-output mode, all signals should be valid at any time and therefore any glitch could be recognized as a pre-mature transition.

The appearances of glitches are usually dependent on the delay model. The pure delay is usually considered to be a safer delay model compared to the inertial delay, because potential glitches might be absorbed by an inertial delay if they are narrow enough. But in [26], the author exemplifies that a circuit might manifest a

<sup>&</sup>lt;sup>1</sup>Even though the Quasi Delay Insensitive (QDI) circuits [25] have different definition, specification form and synthesis flow, they behaviorally equal to the SI circuits. In this thesis, the QDI circuits are indistinguishably recognized as the SI circuits.

hazard under inertial delay model while it would be safe under pure delay model.

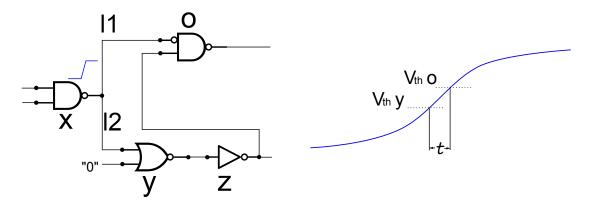

One example of this situation is presented in Figure 2.5, where gate x is an internal gate and gate y is a primary output. There are two glitches appear on the two inputs a and b. The output of gate y is expected to stay at '1'. Assume the gate y has a pure delay. If the delay model of gate x is pure (case 1 in Figure 2.5), then the glitch on input a will be canceled out by the glitch on gate x, the primary output y is hazard-free. However, if the gate x has an inertial delay (the gate y is still under pure delay model) then the glitch on input a will go through y and appear at the primary output as a hazard(case 2 in Figure 2.5).

Figure 2.5: Glitches with respect to delay models -

The above example shows that the pure delay model is not always safer than the inertial delay model. But it is only true when one glitch is used to cancel out another glitch. When we discuss the glitch-free implementation (no glitches are allowed at any signal), the pure delay model will always be a safer mode compared with the inertial delay model.

# Chapter 3

# Speed-independent Circuits

The class of asynchronous circuits is a broad class. Usually, each design paradigm has its own flow. This chapter further explains why SI design is more interesting than other asynchronous design paradigms. Also, this chapter introduces the mathematical models used in the SI design flow.

## 3.1 Why SI design

As was introduced in the previous chapter, there are many asynchronous design paradigms. Unfortunately, these paradigms have totally different design flows. Synthesis techniques for one kind of design cannot be used in others. In this thesis we adopt the SI design, which we think has the following advantages over others:

#### Strong variation tolerance ability:

The SI design which only has an isochronic fork timing assumption is robust

to process variations and harsh environment.

As the technology develops, process variations become quite severe. The design paradigms that need to evaluate the real timing or compare the relative timing between similar components become unreliable. Moreover, all kinds of unreliable environments could appear as the portability of devices increases. The power supply might be from the energy harvesting devices and/or the circuit itself might operate under subthreshold voltage. The SI design has been proved to adjust well to the harsh environment, while other design paradigms are more vulnerable to variations.

As will be shown in the following chapters, the isochronic fork timing assumption could be safely relaxed into a much looser timing assumption and this timing assumption is easier to implement. The overhead to fix the potential hazards is not expensive.

#### Comparatively well supported by EDA tools:

One critical obstacle to asynchronous design for general use is the lake of EDA tool support. Many commercial circuits like [27] and [28] involve remarkable manual efforts. Compared with other asynchronous design paradigms, SI design is comparatively well studied and better supported by EDA tools in the design flow. For example, there are [29] [30] [31] [32] [33] and [34] for synthesis. [35] [36] [37] and [38] for decomposition and technology mapping, [39] [40] [41] and [42] for verification and [43] for testing. Almost each step in design flow is supported or partially supported by existing automation techniques.

### 3.2 Petri Net

Petri net was first formally introduced by Carl Adam Petri in his Ph.D. thesis [44] as a modeling language for discrete distributed systems. It has strict mathematical definition and semantics as well as visually graphic representation. The explicit representations of enabling, disabling, concurrency and conflict make Petri Net quite suitable to model asynchronous systems. Especially, one particular subset of interpreted Petri Net, called the Signal Transition Graph is quite popular in describing the behavior of SI circuits. Formally,

A Petri Net (PN) is a quadruple  $N = (P, T, F, m_0)$ , where

P is a finite set of *places*,

- T is a finite set of *transitions*,

- $F \subseteq (P \times T) \cup (T \times P)$  is a flow relation and

- $m_0: P \to \mathbb{N}$  is the *initial marking*.

Places represent conditions and are usually depicted as circles ( $\bigcirc$ ) in graphical representation and transitions are events in a system and usually denoted by bars (-). A place  $p \in P$  (transition  $t \in T$ ) is an input place (transition) of a transition  $t \in T$  (place  $p \in P$ ) if  $p \times t \in F$  ( $t \times p \in F$ ) or is an output place (transition) of a transition t (place p) if  $t \times p \in F$  ( $p \times t \in F$ ). The set of input places (transitions) of a transition t (place p) is denoted by  $\bullet t$  ( $\bullet p$ ) and the set of output places (transitions) of a transition t (place p) is denoted by  $t^{\bullet}$  ( $p^{\bullet}$ ). This definition also applies to a set of places (transitions). For example, for the set of places  $P_1 \subseteq P$ ,  $\bullet P_1 = \bigcup_{p \in P_1} \bullet p$ .

The marking of a PN is a function  $M: P \to \mathbb{N}$ , which gives each place a

non-negative integer representing the number of *tokens* in this place. A place p is *marked* if M(p) > 0, otherwise it is *blank*. Graphically, a token is drawn as a dot (•).

A transition t is *enabled* in a marking m, if every place in  $\bullet t$  is marked. An enabled transition may *fire*, which will remove one token in each place in  $\bullet t$  and add one token to each place in  $t^{\bullet}$ . This firing will change the marking m into a new marking m' and this transformation is denoted by  $m \stackrel{t}{\to} m'$ .

A marking m' is said to be reachable from marking m, if there exists a firing sequence  $\sigma : t_1 t_2 \dots t_n$  which transforms the marking m to m'. The marking set  $\mathfrak{M}$  of a PN is the set of all markings reachable from the initial marking  $m_0$ .

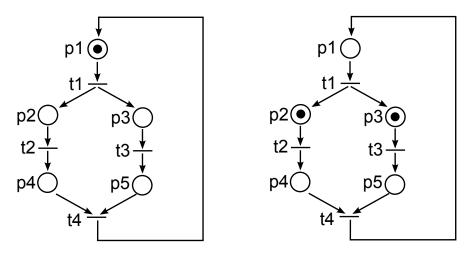

Figure 3.1: A PN example -

The PN example in the left diagram in Figure 3.1 has five places  $P = \{p_1, p_2, p_3, p_4, p_5\}$ , four transitions  $T = \{t_1, t_2, t_3, t_4\}$  and the initial marking  $m_0 = (1, 0, 0, 0, 0)$ . t1 is the only transition that is enabled in the initial marking. When it fires, the initial marking transfers into another marking  $m_1 = (0, 1, 1, 0, 0)$  as is shown in the right diagram in Figure 3.1. The marking set of this PN is

$\{(1, 0, 0, 0, 0), (0, 1, 1, 0, 0), (0, 0, 1, 1, 0), (0, 1, 0, 0, 1), (0, 0, 0, 1, 1)\}.$

Besides the basic semantics of the PN, the properties and concepts [45] introduced below are often involved when certain kinds of PN are used to depict the behavior of asynchronous circuits.

A transition t is said to be *live* in a marking m, if there exists a marking m'reachable from m, such that t is enabled in m'. A PN is live if every transition is live in any reachable marking from the initial marking  $m_0$ .

A PN is *safe* if each place could have at most one token in any reachable marking from the initial marking  $m_0$ .

A place is said to be a *choice place* [46] if it has more than one output transition. A place is said to be a *merge place* if it has more than one input transition. A choice place is further a *free-choice place* if this place is the only input place of all of its output transitions. A PN is a free-choice PN if all its choice places are free-choice places. A PN is said to be a *Marked Graph (MG)* if it does not have any choice and merge place.

Two transitions  $t_1$  and  $t_2$  are in *conflict*, if there is a marking m, where  $t_1$  and  $t_2$  are enabled but fire one will make another from enabled to disabled in the resulting marking.  $t_1$  and  $t_2$  are *concurrent* if for all markings, where  $t_1$  and  $t_2$  are both enabled, they are not in conflict.

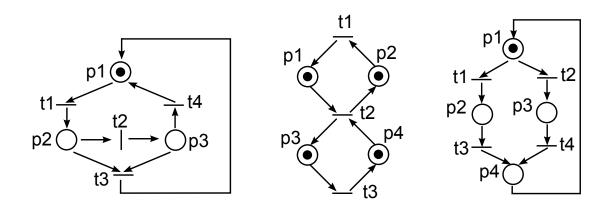

The PN shown in the left diagram of Figure 3.2 is neither live nor free-choice. The transition  $t_3$  will never be enabled and it has two choice place  $p_2$  and  $p_3$  as its input places. The PN shown in the middle diagram of Figure 3.2 is not safe because every place in it could have up to two tokens; the transitions  $t_1$  and  $t_3$ are concurrent in this net. Finally, the PN in the right diagram of Figure 3.2 is

Figure 3.2: PN properties -

live, safe and free-choice and the transitions  $t_1$  and  $t_2$  are in conflict.

A transition  $t_1$  ( $t_2$ ) is a predecessor transition (successor transition) of transition  $t_2$  ( $t_1$ ), if  $t_1^{\bullet} \cap^{\bullet} t_2 \neq \emptyset$  and denoted by  $t_1 \Rightarrow t_2$ . The set of predecessor transitions (successor transition) of transition t is denoted by  ${}^{\triangleleft}t(t^{\triangleright})$ .

## 3.3 Signal Transition Graph

The signal transition graph, which is an interpreted PN, was introduced in [47] (called Signal Graph) and [48] as a high level description of asynchronous circuits. The transitions in the underlying PN are signal transitions in the circuit. Formally,

A Signal Transition Graph (STG) is a triple  $G = (N, A, \lambda)$ , where

N is the underlying PN,

A is a finite set of signals and

$\lambda$  is a labeling function which assigns transitions in N to  $A\times\{+,-\}.$

For all  $a \in A$ , a+ depicts a rising transition (from logic low to logic high) on

signal a, a- depicts a falling transition (from logic high to logic low) on signal a and a\* is used to depict either a+ or a-. The index i (like a\*/i) is used to distinguish multiple occurrences of transitions on the same signal in an STG when necessary.

As a special kind of PN, STG inherits all the semantics belonging to PN. Moreover, in order to model the SI circuits, STG needs fulfilling additional requirements.

Usually, STG is produced by the designer either manually from text description, or by translating the timing diagram with some automatic tools [49]. The STG, whose signal set  $A = I \cup O$ , which only depicts the interactions between the circuit and the environment, is called a *specification STG*, denoted by  $STG_{spec}$ ; while the STG, whose signal set  $A = I \cup R \cup O$  that depicts all event orders in an SI circuit, is called an *implementation STG*, denoted by  $STG_{imp}$ .

The PN containing non-free-choice places or unsafe places could be very complex for analyzing. In this thesis, the underlying PN of an STG is restricted to be live, safe and free-choice if not specified. One technique to process some non-free-choice STGs will be discussed in the last chapter of this thesis.

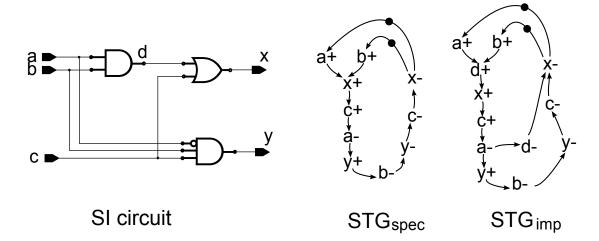

Graphically, STG is often short-handed by omitting the places which have only one input and output transitions and using labeled transitions to instead the bars in the underlying PN. Figure 3.3 shows an SI circuit (left), in which,  $I = \{a, b, c\}, R = \{d\}$  and  $O = \{x, y\}$ . Its  $STG_{spec}$  (middle) only depicts the signal transitions on circuit's interface while its  $STG_{imp}$  (right) depicts all the signal transitions within the circuit.

In an STG, the transitions on the same signal must have *consistency*. It means

that in any firing sequences, the rising transitions and falling transitions on the same signal must appear alternatively.

Figure 3.3: An SI circuit with its  $STG_{spec}$  and  $STG_{imp}$  -

### 3.4 State Graph

An STG explicitly describes the relations between events. So, the STG is suitable for high level modeling and manipulating the behavior of an asynchronous system. While, the logic synthesis, optimization and verification are much easier to be carried on a low level model, where the reachable states of an STG are explicitly presented.

The state graph (also called the transition diagram in [47] or state transition diagram in [9]) is a binary labeled finite automaton. Each state in the finite automaton is a reachable marking of its STG. The binary value of a state represents the value of signals in the corresponding circuit.

A state graph (SG) is a quintuple  $SG = (A, S, E, \pi, s_0)$ , where

A is a finite set of signals,

S is a set of states,

$E = S \times S$  is a set of transitions,

$\pi$  is a labeling function which labels each state  $s \in S$  with a bit-vector over A and

$s_0$  is the initial state.

The value of signal a in state s is denoted by s(a). Two states s and s' are adjacent if  $(s, s') \in E$ . A transition from state s to its adjacent state s' by firing a\* is denoted by  $s \xrightarrow{a*} s'$ . For  $s \xrightarrow{a*} s'$  the triple (s, a\*, s') is said to be consistent if when a\* = a + then s(a) = 0, s'(a) = 1 and s(b) = s'(b) for all  $b \in A$  and  $b \neq a$ . An SG is considered to have a consistent state encoding if each possible triple (s, a\*, s) in this SG is consistent.

An SG of an STG could be derived by recursively firing enabled transitions from the initial marking and labeling the resulting marking set. An SG derived from an STG will have a consistent state encoding if and only if the rising and falling transitions on the same signal appear iteratively [48] in the STG.

The concept of region used data mining was introduced into the SG in [50] for classifying the states in order to accelerate the manipulations on an SG. States in each region have the same properties with respect to the corresponding signal.

Event  $a^*$  is *excited* in state s if there exists a state  $s' \in S$  such that  $s \xrightarrow{a^*} s'$ . Signal a is *stable* in state s if  $a^*$  is not excited in s. A set of states  $S' \subset S$  is said to be the i - th positive excitation region of signal a, denoted by  $ER_i(a+)$ , if it is the i - th largest connected set of states such that for every state  $s \in S'$ , a+is excited in s. A set of states  $S' \subset S$  is said to be the i - th negative excitation region of signal a,  $ER_i(a-)$ , if it is the i-th largest connected set of states such that for every state  $s \in S'$ , a- is excited in s. A set of states  $S' \subset S$  is said to be the i-th positive quiescent region of signal a+, denoted by  $QR_i(a+)$ , if it is the i-th largest connected set of states such that for every state  $s \in S'$ , a is stable and s(a) = 1. A set of states  $S' \subset S$  is said to be the i-th negative quiescent region of signal a-, denoted by  $QR_i(a-)$ , if it is the i-th largest connected set of states such that for every state  $s \in S'$ , a is stable and s(a) = 0.

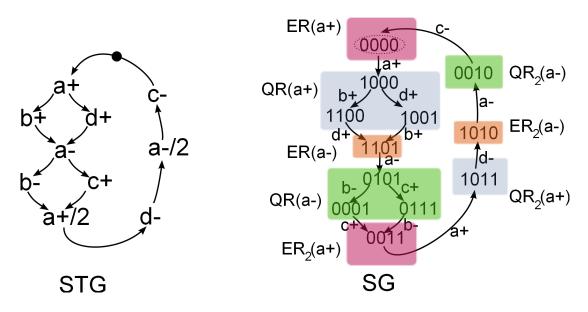

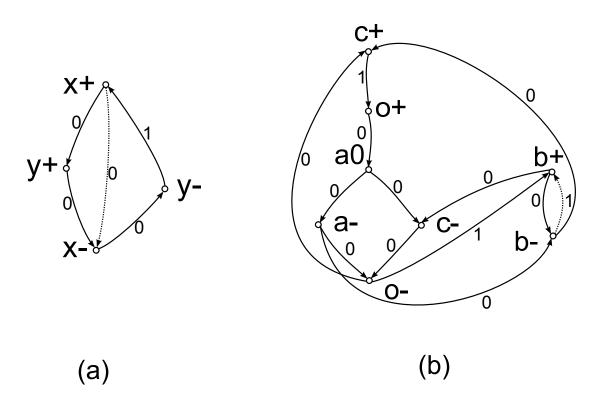

Figure 3.4 shows an STG and the SG derived from this STG. All regions defined above are explicitly shadowed.

Figure 3.4: An STG with its SG -

## 3.5 Summary

This chapter introduces the popular models that are often adopted by existing methods to synthesis and verification SI circuits. The high level behavior of SI circuits is often denoted by a labeled live and safe PN called the STG. The entire reachable state of the circuit could be explicitly expressed by one kind of low level finite automaton, called the SG. In the chapter 5, the STG will be used to describe and manipulate the event causalities in an SI circuit and the hazards will be checked in the corresponding SG of the STG. The combination use of STG and SG makes the proposed method work efficiently.

# Chapter 4

# Timing Issues in SI Circuits

The timing issues for SI circuits have attracted lots of attention from researchers. This chapter presents the main factors that would cause the failure of the isochronic fork timing assumption. A relaxed timing assumption that will be adopted in the following chapters will also be introduced.

## 4.1 Timing assumptions in SI circuits

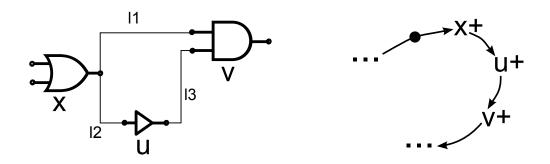

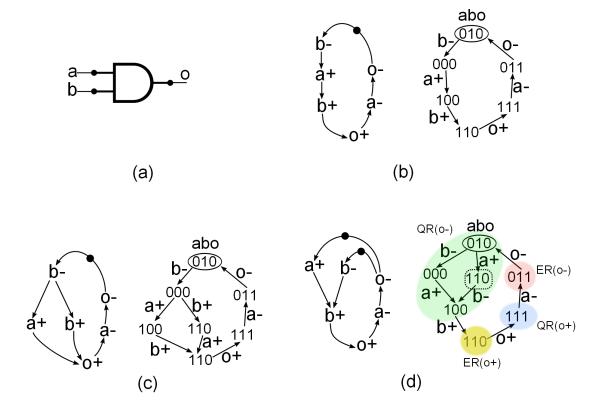

The cornerstone of SI circuits is the concept of *acknowledgement*. We say one signal transition a\* is acknowledged by another signal transition b\* if b\* cannot happen until a\* happens. E.g. for an *AND* gate with inputs a and b and output o, one could say that the rising transition of o will acknowledge both a+ and b+; but the falling transition of o could at most acknowledge one falling transition either on a- or b-.

The fundamental assumption of the SI circuits is so called the *isochronic*

fork timing assumption, which assumes that when a transition at any branch in a fan-out fork is acknowledged, this transition will also be acknowledged at other branches in the fork. The hypothesis behind the assumption is that a transition on a gate is only required to be acknowledged by one branch in its fanout fork. Those branches which are not acknowledged explicitly are considered to be acknowledged by isochronic fork timing assumption.

### 4.2 Existing research on isochronic fork reliability

Much previous research has investigated the issues related to the isochronic fork timing assumption. On the one hand, some researchers tried to improve the circuit performance by introducing more aggressive timing assumptions to the circuits. For example, in [51], researchers extended the isochronic fork into multi level isochronic forks and in [50] concurrency reduction and lazy transition timing techniques were used to improve the circuit performance. On the other hand, some researchers investigated the reliability of the isochronic fork timing assumption [52] [53] [54] [55]. They tried to find out what aspects might cause the failure of isochronic fork timing assumption and what was the consequence when the isochronic fork timing assumption was no longer guaranteed.

The next few subsections present the possible causes that could lead to the failure of the isochronic fork timing assumption. One could conclude that: as the technology develops, isochronic forks become more and more unreliable and additional techniques must be used to guarantee the correctness of SI circuits in the near future.

#### 4.2.1 Input negations

The first observation about the violation of isochronic fork is the input negations. When a netlist is implemented, the input negations must be decomposed into individual inverters. Glitches might appear if the delays of these inverters are large enough.

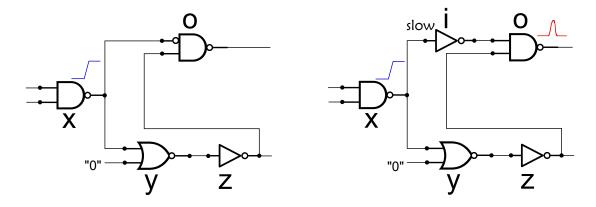

Figure 4.1: Glitches caused by inverter delay -

The left diagram in Figure 4.1 shows a circuit with initial values of the signals x, y, z and o at "0", "1", "0" and "0" respectively. The output of the gate o is expected to maintain at "0" after  $x + \Rightarrow y - \Rightarrow z +$ . But when the input inversion bubble attached to the gate "o" is decomposed into an individual gate i (as is shown in the right diagram), this gate might stay at "1" while gate z has risen to "1". This will cause a positive glitch at the gate o.

When an SI circuit is synthesized from the SG based method such as *petrify* [50], certain gates in the circuit are inevitable to contain input negations. In [52], the author found an error caused by the input inverter and concluded that in order to guarantee the correctness of SI circuits, certain inverters attached to

gate inputs must be considered having negligible delay compared to that of gates.

Much previous research has attempted to solve this problem by specification refinement [56, 57]. These works tried to introduce additional signals in the original specifications (e.g. STG) to make sure that the final synthesized circuit did not have any input bubbles requiring negligible delays. These techniques often generate compact and fast circuits. But they are not only hard to automate but also not easy to utilize manually except for experienced designers and thus cannot be considered as a general solution. Moreover, as the gate becomes faster, the interconnect wire delay could far exceed the gate delay. The consequence is when a long wire appears, its delay might be large enough for generating glitches even though no inverters appear on it.

#### 4.2.2 Threshold variations

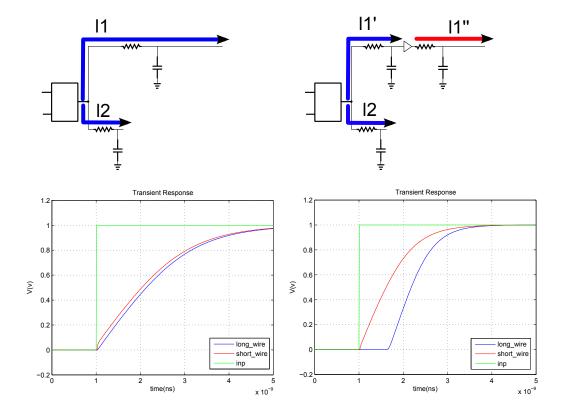

In [53], the author investigated the situations under which glitches might appear due to threshold variations. One important experiment showed that compared with the delay introduced by the input negation or wire delays, the threshold variations are more dangerous.