Volume 11, Number 4, Fourth Quarter 2000

#

SEPTEMBER

JUNÊ

MARCH

ELECTRONICS ENGINEERS, INC.

## **Recent Advances** in System-Level **nterconnect Prediction**

Dirk Stroobandt

### IEEE Circuits and Systems Society Newsletter Newsletter Homepage-http://www.nd.edu/~stjoseph/newscas

#### **Editor-in-Chief**

Michael K. Sain **Electrical Engineering Department** University of Notre Dame Notre Dame, IN, USA 46556-5637 Phone: (219) 631-6538 Fax: (219) 631-4393 E-mail: jordan@medugorje.ee.nd.edu

#### **Features Editors**

Guanrong Chen Department of Electronic Engr. City University of Hong Kong Hong Kong, P. R. China (on leave from U. Houston) Phone: (852) 2788-7922 Fax: (852) 2788-7791 E-mail: gchen@ee.cityu.edu.hk

Rui J. P. de Figueiredo Department of Electrical and Computer Engineering University of California, Irvine Irvine, CA, USA 92697-2625 Phone: (949) 824-7043 Fax: (949) 824-2321 E-mail: rui@uci.edu

#### **IEEE Publishing Services**

Robert Smrek Production Manager **IEEE Service Center** 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331, USA Phone: (732) 562-3944

#### **Frequency of Publication**

Ouarterly

#### **Newsletter Deadlines**

Articles for the CAS Newsletter issues must be received by the Editor by the following dates:

| Issue          | Due Date   |

|----------------|------------|

| First Quarter  | February 1 |

| Second Quarter | May 1      |

| Third Quarter  | August 1   |

| Fourth Quarter | November 1 |

© 2000 IEEE. Information contained in this newsletter may be copied without permission provided that the copies are not made or distributed for direct commercial advantage, and the title of the publication and its date appear.

IEEE Circuits and Systems Society Newsletter is published quarterly by the Circuits and Systems Society of the Institute of Electrical and Electronics Engineers, Inc., Three Park Avenue, New York, NY 10016-5997. Four dollars per member per year (included in Society fee) for each member of the Circuits and Systems Society. Printed in U.S.A. Periodicals Postage Paid at New York, NY, and at additional mailing offices. Postmaster: Send address changes to IEEE Circuits and Systems Society Newsletter, Attn: Change of Address, IEEE, 445 Hoes Lane, Piscataway, NJ 08855-1331.

#### In This Issue

The Hopes of the Future Are Built on the Contributors of the Past: page 3

> See How to Predict Your Interconnects: page 4

CAS President

Reader Interest Has Brought Additional Response: page 22

#### CAS Election Results Announced— And On Time: page 47

| Technical News                             |    |

|--------------------------------------------|----|

| Stroobandt: Interconnect Prediction        | 4  |

| Hui/Tang/Chung: PCB Transformer Addendum   | 22 |

| Fradkov: Oscillations and Chaos            | 26 |

| Society                                    |    |

| Thanks for the Memories                    | 3  |

| Call for Papers in the CAS Magazine        | 21 |

| Newsletter Credits                         |    |

| Distinguished Lecturer Program continued   | 30 |

| IEEE Fellow Nominations                    | 40 |

| Board of Governors Report                  | 41 |

| T-Multimedia Special Issue Call for Papers | 45 |

| New CAS Officers/BOG Members               | 47 |

| CAS Awards Prizes Increased for 2001       | 47 |

| People                                     |    |

| CAS 2000 IEEE Fellow Profiles              | 36 |

| The Adventures of the 'Umble Ohm           | 47 |

| Places                                     |    |

| Calls for Papers                           |    |

| Euroimage '01                              | 45 |

| 2nd MPEG-4 Workshop                        | 45 |

| MWSCAS '01                                 | 45 |

| ICME '01                                   | 45 |

| Coming Events                              |    |

| ISCAS 2001                                 | 48 |

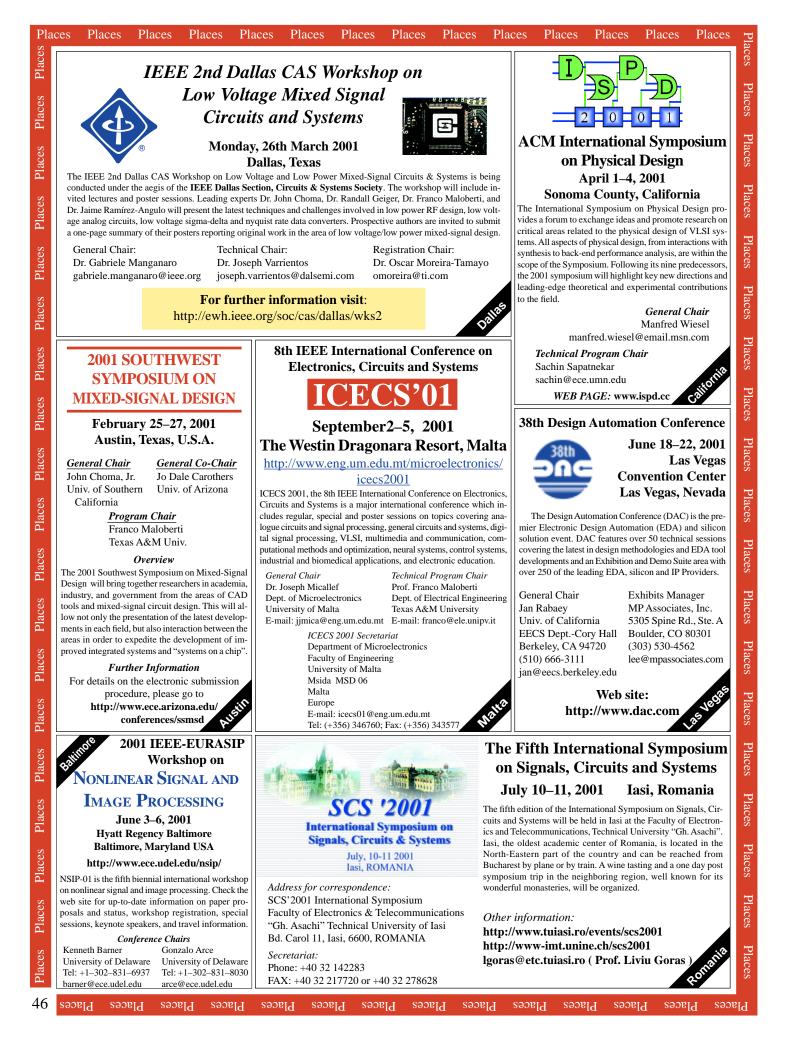

| DAC '01                                    | 46 |

| ICECS '01                                  | 46 |

| SSMSD' 01                                  | 46 |

| ISPD 2001                                  | 46 |

| CAS Workshop on Emerging Technologies      | 46 |

| SCS '01                                    | 46 |

| NSIP '01                                   | 46 |

### Thanks for the Memories...

Well, the moment has arrived. This is the final issue of the *IEEE Circuits and Systems Society Newsletter*.

#### 44, 11, 952

Numerically, this is the 44th consecutive number in the current series of eleven volumes, with the first number coming into being eleven years ago in March 1990. In terms of pages, this eleven-year run began at 16 per issue, expanded to 24 per issue eight years later, on the occasion of the passing of Sidney Darlington, rose to 32 per issue just four numbers later, and finally jumped to 48 per issue in December 1999, the issue marking the Society's Golden Anniversary. Cumulatively that is 952 pages, the last nine numbers being in full color.

#### **An Appreciation**

We have many, many people to thank at this time. Here in the editor's office, where we have for these eleven years produced the IEEE Circuits and Systems Society Newsletter by means of desktop publishing, we wish to acknowledge our associates over the years, without whom these pages would not have come to be. The opening mention goes to Julia Jordan, who got the project off the ground. Thank you, Julia. We are indebted also to Joanne Birdsell, managing editor in Notre Dame's Engineering Graphics and Publications Office, who helped us out from time to time early on, when we experienced transitions of one sort or another. Susan Larsen, a wizard with Pagemaker, and Martha Van Overberghe, who also helped with the Society budget, were with the Newsletter for a year or two, and both participated in the development of the publication style. We appreciate all that they did along the way. Finally, we give a very heartfelt special thanks to Eric Kuehner, who has been with us as we went to a new level, tripling the number of pages and introducing full color.

At the IEEE end of things, we wish to express our sincere appreciation to Bob Smrek, whose office receives our films and interfaces with the printer to produce very high quality issues and see them off to the CAS members all around the world. Thanks so much, Bob, to you and your staff.

And it all started with Tony Michel, who asked me one day if I would like to take on another challenge in editing. Tony and I had worked together on the *IEEE Transactions on Automatic Control*, during one of my five years as Editor there. Thanks for asking, Tony....

A seminal role has been played by Rui de Figueiredo, who contacted me in the Fall of 1997 to say that the Society wanted to begin publishing technical articles in the Newsletter, to expand in an orderly manner and eventually to seek the conversion of the Newsletter into a Magazine. This was a most challenging goal; and it has led to some of the most interesting editorial experiences that I have ever had. I am deeply indebted to Rui for all his help, his advice, his ideas, and his direct participation in all steps of this process. We would not be where we are without Rui, who along the way became an official Features Editor for our Newsletter. Thank you, Rui. Another special thank you goes to Ron Chen, who wrote the cover article in that March 1998 issue, our first technical article. Over these last three years, Ron has written in several different ways on the pages of our Newsletter, displaying a most enjoyable versatility, whether writing a meeting report, a book review, or a newsletter article. Also accepting a post as Features Editor, Ron has worked hard behind the scenes on behalf of our readers, even during his leave-of-absence time when others would have declined.

Early on in the Newsletter evolution, we were joined by Shlomo Karni, who is the creator of the 'Umble Ohm. This regular cartoon has lent a very human side to all our more mundane efforts to publish news and articles. Thank you Shlomo for those many, many images. We are happy to say that we have in hand another 'Umble Ohm for the first issue of the forthcoming Magazine!

For a couple of years we were able to run a most unusual crossword puzzle with technical hints. Thanks for this effort go first to Pat Sain and Cheryl Schrader, and then to Pat who continued on for a time after Cheryl graduated. Once again, little worldly advantage accrued from this effort, but we are aware of quite a number of folks who used to work those puzzles.

We have come to believe that it takes a very community oriented CAS member to write for the Newsletter. The whole purpose of the Newsletter is to make information available to everyone in the Society. Much of this type of writing is nontechnical in nature, and will not score many points with one's supervisor as an item on the resume. The situation is even more critical for an article of technical nature. On the one hand, the way to write for a general audience is quite different from the way to write for, say, a transactions. Of course the benefit is a much, much larger audience. On the other hand, many of our superiors would discourage even listing a Newsletter article in one's list of activities during the year, for various reasons which we can all recite.

We have during these eleven years been fortunate indeed to encounter many CAS members who were community oriented enough to write for the Newsletter, with virtually no recompense other than that of knowing that they were serving the Society. In honor of these persons we have prepared a special list of credits, which appears on Page 29. You all know who you are, everyone from Society officers to chapter members. We feel most truly indebted to each and every one of you. Thank you so much for participating when we were "only" a Newsletter.

And so it is time to lead the caterpillar into its cocoon, from which it will emerge next quarter, in 2001, as *IEEE Circuits and Systems Magazine*. This metamorphosis was finally approved last June in Vancouver at the TAB meetings.

We hope that each of you who participated in the Newsletter these eleven years will feel very much a part of the Magazine, for indeed you have been such a part. Thanks again for the memories....

### Recent Advances in System-Level Interconnect Prediction

**A** bstract—The exciting, new field of System-Level Interconnect Prediction emerged from research of the early 1970's but it took until 1999 before a cohesive research community for interconnect prediction was established. New research results are becoming available and the last couple of years have brought both more interest and more progress in the field than in the thirty years before. This paper is an introduction to the field and provides an overview of some of the recent advances in system-level interconnect prediction.

#### Introduction

As mainstream processors surpass gigahertz global clock frequencies and new design and process technologies enable even higher performance, much attention is directed toward managing the influence of interconnects in deep submicron designs. Today, interconnects are the limiting factor for both performance and density, *i.e.*, the value and the cost of the VLSI system.

Guided by better models of interconnect performance at the atomic and grain levels of structure and at multigigahertz operating frequencies, we adopt new process technologies (e.g., reverse-scaled copper wires, low-permittivity dielectrics). Effects previously considered unimportant become significant (e.g., mutual inductance), and previously reasonable approximations (e.g., lumped-capacitance gate load models) become useless.

Due to these trends, chip planning and layout tools must embrace new paradigms. System-level interconnects must be treated as distributed RLC lines with embedded repeaters. Wiring layer assignment, e.g., based on statistical models of the system interconnect structure, becomes critical.

Today, a focal point for improved interconnect modeling, more cost-effective system architectures, and more productive design technology centers on new methods and models for system-level interconnect prediction. Although basic works in this area are almost thirty years old, no cohesive research community for interconnect prediction was established until the First International Workshop on System-Level Interconnect Prediction [1] in April 1999. A collection of recent research work in the System-Level Interconnect Prediction field can be found in a special issue of IEEE Transactions on VLSI Systems [2]. In 2001, the SLIP Workshop will be held for the third time and a new special issue of TVLSI is planned.

This paper aims at introducing the field of System-Level Interconnect Prediction and at providing an overview of recent research work in this new and exciting area. The next section starts with an introduction on *a priori* interconnect prediction and the

Dirk Stroobandt\*

importance of Rent's rule, the basis for all modeling. The third section gives an overview of wirelength estimation models and provides a common framework for such models. In the last section applications of wirelength estimations are presented.

#### A Priori Interconnect Prediction and Rent's Rule

The Computer-Aided Design (CAD) tools for placement of logic gates in a circuit optimize for small interconnection lengths between gates. This requires knowledge of the interconnect routing. Routing, on the other hand, can only be done after the place of the gates is known. Hence, during the layout of computer chips, several iterations between placement and routing are needed. To reduce or even eliminate the number of placement/ routing iterations, a priori estimations of interconnection lengths are very helpful because they allow an evaluation of placements without a routing

As mainstream processors surpass gigahertz global clock frequencies and new design and process technologies enable even higher performance, much attention is directed toward managing the influence of interconnects in deep submicron designs. Today, interconnects are the limiting factor for both performance and density, *i.e.*, the value and the cost of the VLSI system.

step, leading to a better initial placement and a better initial routing result. CAD tools for layout generation therefore could benefit from *a priori* (*i.e.*, pre-layout) wirelength estimation techniques.

Current applications of *a priori* interconnect estimation are found in technology extrapolation [3], e.g., the International Technology Roadmap for Semiconductors (ITRS) [4]. For estimations of the performance of future designs, very little is known about the design and *a priori* techniques are essential. The same applies to the evaluation of new computer architectures. *A priori* estimates immediately provide

... continued on Page 6

<sup>\*</sup> Dirk Stroobandt is a Postdoctoral Fellow of the Fund for Scientific Research (F.W.O., Flanders, Belgium), at Ghent University, ELIS Department, Sint-Pietersnieuwstraat 41, B-9000 Gent, Belgium. E-mail: dstr@elis.rug.ac.be

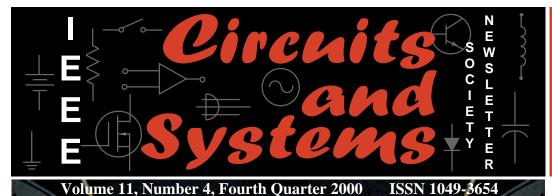

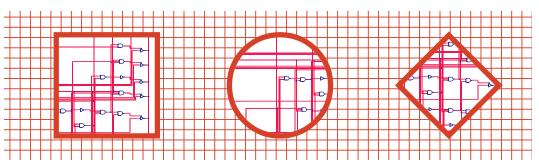

Figure 1. The three components of models for physical design: the circuit, the architecture and the layout generation. The combination of these models results in the (model for the) layout.

Current practice models the circuit as a collection of logic gates connected to each other through interconnections, models the architecture as a (two-dimensional) Manhattan grid, and assumes a "good" placement (*i.e.*, one that successfully minimizes wire lengths) and enough space available to route all interconnects along the shortest (Manhattan) path. However, these simple models do not suffice to make powerful estimations about the resulting layout. For this, one needs to have a notion of (i) the complexity of the interconnection topology and (ii) the quality of the placement. This information is provided by the so-called Rent's rule.

#### Recent Advances ... continued from Page 5

a solid ground for drawing preliminary conclusions about the benefits of new architectures and for comparing different architectures to each other. These applications are discussed in the last section.

*A priori* interconnect estimation typically requires three models (Fig. 1): (i) a circuit model (ii) a model for the physical architecture the circuit

will be placed in, and (iii) a model for the layout generation (placement and routing). Current practice models the circuit as a collection of logic gates connected to each other through interconnections, models the architecture as a (two-dimensional) Manhattan grid, and assumes a "good" placement (i.e., one that successfully minimizes wire lengths) and enough space available to route all interconnects along the shortest (Manhattan) path. However, these simple models do not suffice to make powerful estimations about the resulting layout. For this, one needs to have a notion of (i) the complexity of the interconnection topology and (ii) the quality of the placement. This information is provided by the so-called Rent's rule.

In 1971 Landman and Russo [5] described a relationship between the average number of terminals T of a part of the circuit (a *module*) and the average number of logic gates (basic logic blocks B) inside the module. This relation is given by

$T=t B^{p}$ (1)

and is called *Rent's rule*. The parameter *t* is the average number of terminals per logic gate and the exponent *p* is the *Rent exponent*. Its value depends

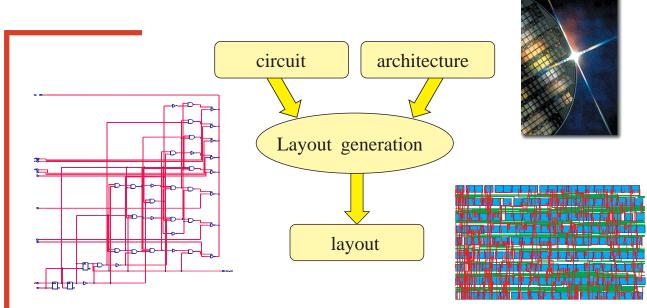

on the complexity of the interconnect topology (with higher values for more complex topologies) and on the quality of the placement (with higher values for less placement optimization). The maximal value of the Rent exponent p is 1 for a very complex topology or a random placement [6]. Rent's rule proves to be valid for most designs and it is recently shown that it applies to any homogeneous design [6]. Rent's rule has also been extended for heterogeneous systems in [7, 8]. Figure 2 shows the result of a circuit partitioning in a log-log plot of number of terminals versus number of logic gates. The validity of Rent's rule follows from the fact that all points followon average—a straight line in the plot.<sup>1</sup> With Rent's rule, sufficiently accurate

... continued on Page 8

<sup>1</sup> The deviation from the straight line for high values of T and B is known as Rent's region II and has been described in [5, 11]. Another deviation at the low end is described in [12].

Figure 2. Rent's rule: number of terminals per module **T** versus number of gates per module **B** during the partitioning of a benchmark circuit (ISCAS'89 [9] benchmark 's953') with the 'ratiocut' partitioning method [10]. The size of the circles corresponds to the percentage of modules (on a total number of modules around an average number of gates, at equal distances in the log-log plot) that has **B** gates and **T** terminals.

### **Recent Advances in System-Level Interconnect Prediction**

#### Recent Advances ... continued from Page 7

estimates of interconnection lengths can be made.

In the remainder of this paper the use of Rent's rule for wirelength estimation is described. Some direct applications of Rent's rule include:

- estimation of the number of terminals to aid circuit partitioning [13];

- generation of benchmark circuits [14–17].

#### **Wirelength Estimation**

#### Donath's Model

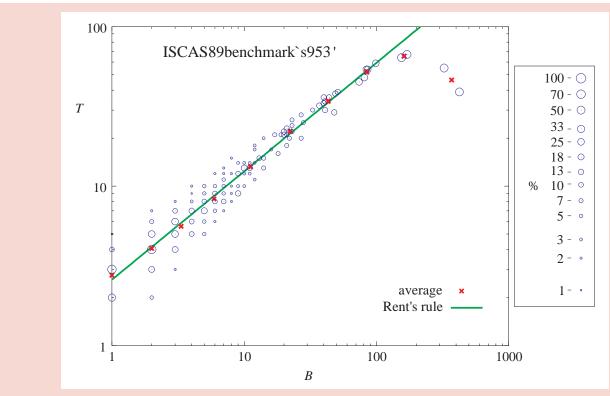

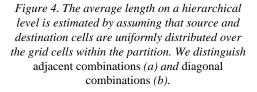

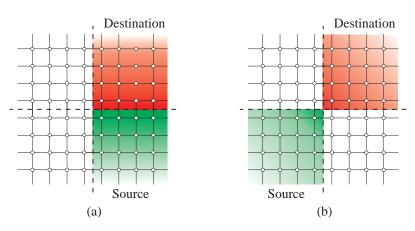

Rent's rule has been used for wirelength estimation for the first time by (Fig. 3(b)) and each circuit part is mapped to a grid part. This partitioning process is repeated recursively until all logic gates are assigned to a single grid cell in the Manhattan grid. The average number of interconnections between parts at a certain hierarchical level is estimated from Rent's rule (details can be found in [18]) and the average length of a connection at each hierarchical level is estimated by assuming that source and destination cells are uniformly distributed over the grid part for that hierarchical level (Fig. 4). This placement model ensures that shorter interconnects (at deeper

of both circuit (a) and Manhattan grid (b) and mapping of circuit parts to grid parts.

Donath in 1979 [18]. The idea is simple: the circuit is partitioned hierarchically into equally large parts (see Fig. 3(a); four parts in each hierarchical step). The Manhattan grid is partitioned as well in a symmetrical way hierarchical levels) will outnumber longer ones (due to the use of the hierarchical model together with Rent's rule) but keeps the placement of cells within a hierarchical part simple (random).

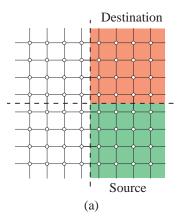

Despite the simplicity of Donath's

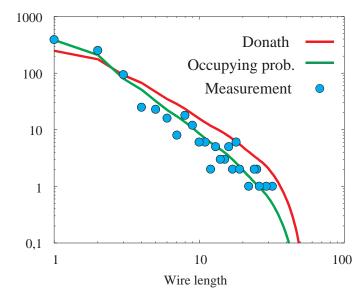

model, it is able to predict the scaling of the average wirelength as a function of circuit size quite well. Figure 5

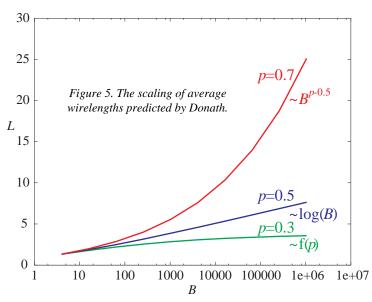

shows that circuits of low complexity (p < 0.5) result in an average wirelength that converges to a constant value (depending on the value of the Rent exponent) for large circuits. The average wirelength of circuits of average complexity (p = 0.5) scales with the logarithm of the circuit size and for complex circuits the average wirelength increases without bounds for increasing circuit sizes. This result has also been observed for real circuit placements. However, Donath found that his quantitative average wirelength predictions were approximately a factor of 2 off from measured values for real circuits, as can be seen from Fig. 6.

#### Introducing the Occupying Probability

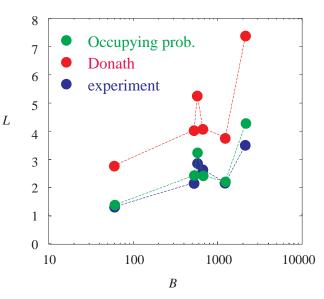

In [19, 20] Stroobandt et al. attributed the discrepancy between Donath's model and real results to the uniform placement of source and destination cells within a hierarchical level. Indeed, a good placement will try to place connected gates closer to each other and hence will favour the placement of source and destination cells closer to the border between connected hierar-

... continued on Page 10

Figure 6. Donath's average wirelength estimates and estimates considering the occupying probability versus measurements on actual circuit designs.

The use of the third dimension, especially with the introduction of optical links, leads to anisotropic systems. Third dimension interconnects have different properties (possibly larger latency, lower interconnection density requiring detours, possible limitation of the minimal distance in the third dimension, ....).

#### Recent Advances ... continued from Page 9

chical parts, as in Fig. 7. To model this, they separate the wirelength distribution into two parts [20, 21–23]: (i) a *site density function* that enumerates all possible paths between all possible cell pairs in the Manhattan grid [24, 25] and (ii) an *occupying probability* that assigns a probability of occurrence

Figure 7. Placement of source and destination cells according to a probability distribution (darker regions have higher probability) for adjacent (a) and diagonal (b) combinations.

to each of the possible paths [20]. With Donath's assumption of uniform cell placement within a hierarchical level, this occupying probability is a constant but the actual occupying probability is a decreasing function of path length. Based on theoretical arguments and Rent's rule [20], it is found to be proportional to  $\ell^{2p-4}$  where  $\ell$  is the interconnection length. The results of this improvement on the average wirelength are shown in Fig. 6. Figure 8 shows the difference in the entire wirelength distribution between Donath's estimates and the ones using the occupying probability and compare both to an actual wirelength distribution for a placed design.

Independently, Davis *et al.* [26] proposed a non-hierarchical method for wirelength estimation that uses Rent's rule on Manhattan circles (diamonds) around each gate. This results in a more accurate occupying probability that can be approximated by  $\ell^{2p-4}$  and hence leads to very similar results as in [20]. A more detailed analysis of different wirelength models can be found in [6].

#### Other Model Extensions

The introduction of three-dimensional computer systems has induced the need to extend the wirelength estimation models to three-dimensional

Figure 8. Donath's wirelength distribution and the distribution with probability function versus actual measurements for a placed circuit.

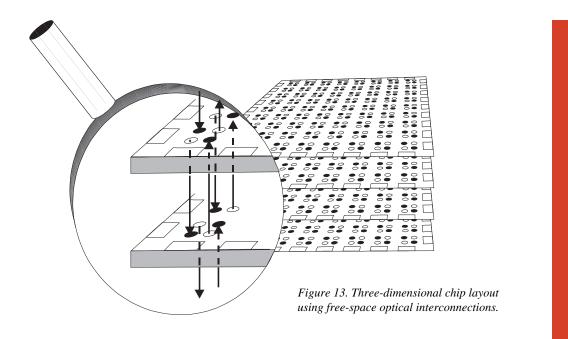

grids. An initial extension of Donath's model was presented by Masaki and Yamada [27]. The occupying probability for three-dimensional systems was introduced in [28] and Davis' technique has been extended to 3D in [29]. The use of the third dimension, especially with the introduction of optical links, leads to anisotropic systems. Third dimension interconnects have different properties (possibly larger latency, lower interconnection density requiring detours, possible limitation of the minimal distance in the third dimension, etc.). Extensions to include issues for anisotropic systems have been presented in [30, 31] and were mainly used to evaluate opto-electronic three-dimensional anisotropic systems [32-35].

Other extensions include taking into account external interconnections [36] and multi-terminal nets [37, 38] and estimating the global wirelength distribution (for heterogeneous systems-on-a-chip) separately [8].

#### Applications of Wirelength Estimation

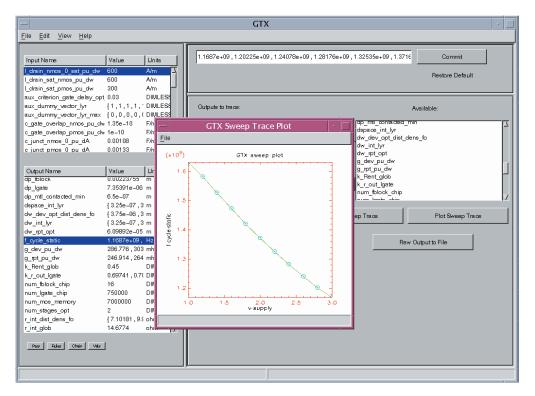

Up to now, the most common application of *a priori* wirelength estimation was found in methods and tools to predict the performance of future circuits. The wirelength estimation methods are used to estimate the average interconnection length in the critical path model for determining the attainable operating frequency [39–43]. An interesting project has been developed at UCLA where the MARCO GSRC Technology Extrapolation (GTX) sys-

tem [3] provides a robust, portable framework for interactive specification and comparison of modeling choices ... continued on Page 12

Unlike previous "hardcoded" systems such as [40, 41, 43], GTX adopts a paradigm wherein parameters and rules allow users to flexibly capture an essentially unbounded space of attributes and relationships that are germane to VLSI technology and design. User-defined rules can be composed in numerous ways to define rule chains, which are then executed by a derivation engine to perform studies.

### **Recent Advances in System-**

#### Recent Advances ... continued from Page 11

(e.g., for predicting system cycle time or power dissipation). Unlike previous "hard-coded" systems such as [40, 41, 43], GTX adopts a paradigm wherein parameters and rules allow users to flexibly capture an essentially unbounded space of attributes and relationships that are germane to VLSI technology and design. User-defined rules can be composed in numerous ways to define *rule chains*, which are then executed by a *derivation engine* to perform studies. The results can then be plotted by the graphical user interface (Fig. 9). A similar use of wirelength prediction techniques can be found in the analysis of process yield [44].

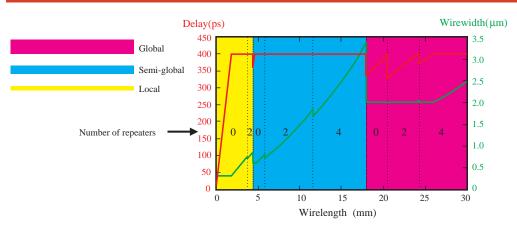

Other uses of wirelength estimation models combine the resulting estimations (which represent the required routing resources) with models for available routing resources (considering routing efficiencies, loss of space due to power and ground wires, and the impact of vias) [42, 45–47]. This combination allows one to predict the number of wiring layers needed for given technological layer parameters or, if this number is fixed, to decide whether or not the design will be routable (prior to any layout step!). Accurate estimates of routing demand and supply could also be used to guide layout tools to promising solutions (wire planning). One can also optimize the characteristic layer parameters for

Figure 9. Graphical user interface of the GTX system [3].

### **Level Interconnect Prediction**

Figure 10. A typical example result of the layer assignment method of [48].

future designs (number of layers, wire width and pitch per layer, ...). For this, a layer assignment model is needed. In [48] an optimal layer assignment scheme is searched for by taking into account (i) the optimal wire width, number and size of the repeaters for each wire on each possible layer; (ii) the requirement to meet consistent stage delay constraints for all wires; (iii) a total repeater area constraint; and (iv) the impact of vias on routing. The method minimizes the number of layers needed and returns the optimal width for each wire and the number and size of the repeaters that have to be used. The method can also easily handle different delay constraints on different wires, *i.e.*, a 2-D distribution of wire lengths and required wire performances.

Figure 10 shows a typical result for a layer stack with local, semi-global and global wiring layers [48]. For the shortest wires, a minimum-sized wire at the local layers is sufficient to meet the delay constraint. Once the constraint is reached (in this case the constraint was set to 400 ps), the wire width increases as the length increases. At some point it is beneficial to add repeaters.<sup>2</sup> For longer wires a semi-

... continued on Page 14

The layer assignment method allows an interesting study of the optimal layer stack. The authors of [48] confirmed that the traditional monotonic layer stack with wide wires (global wires) on top performs much better than a uniform layer stack (all layers are equal). A more interesting result shows that a non-monotonic layer stack sometimes performs even better.

<sup>&</sup>lt;sup>2</sup> For the reported result, the number of repeaters was limited to an even number to allow the use of inverters.

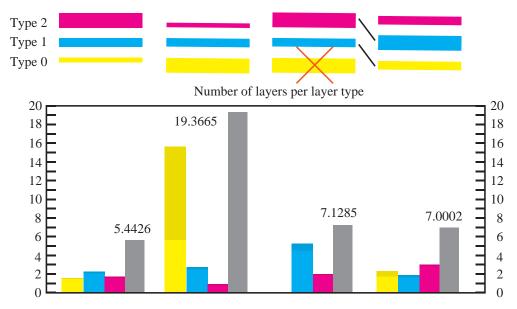

Figure 11. Results for different wiring layer configurations: number of layers needed for each layer type (corresponding colors) with darker colors representing the space lost due to the via impact. The total number of layers needed for each combination is represented in grey.

Recent Advances ... continued from Page 13

global layer is needed and for the longest wires only the global layers are sufficient.

The layer assignment method allows an interesting study of the optimal layer stack. The authors of [48] confirmed that the traditional mono-

tonic layer stack with wide wires (global wires) on top performs much better than a uniform layer stack (all layers are equal). A more interesting result shows that a non-monotonic layer stack sometimes performs even better. In Fig. 11 four layer stacks are evaluated. The first one is the traditional approach, the second one is its inverse (local layers on top). Clearly, this layer stack is less optimal in terms of number of layers needed than the original one, mainly because of the huge via impact on the lower layers. We can also investigate non-monotonic layer stacks such as the third one, which has a global layer type on the bottom and a "conventional" layer stack on top of that. As could be expected, the bottom type is not used at all. This indicates that the conventional approach is indeed better. However, a conventional layer stack with a local layer type at the top (last stack in Fig. 11) does not result in a vacant top layer. Indeed, the results show it is beneficial to move some of the wires to the top layers! Note, however, that the difference in total cost is small.

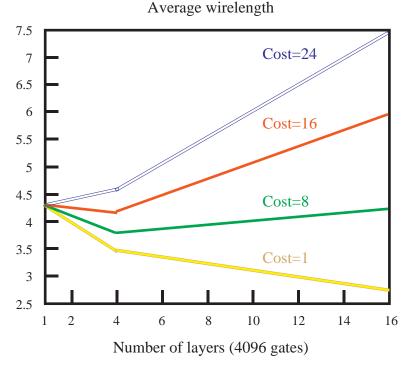

A last example of the use of *a priori* interconnect prediction is the evaluation of new computer architectures [49], especially three-dimensional opto-electronic architectures. Since such architectures are not yet available, their possible benefits have to be quantified by predictive techniques. Results show [28, 29, 33, 35, 50] that three-dimensional systems (*i.e.*, where the gates are placed on a three-dimensional grid) have significantly lower wire lengths than two-dimensional systems (Fig. 12). The connections in the third dimension could be implemented as optical links as in Fig. 13. Whatever the implementation, it is likely that the third dimensional electrical counterparts. Therefore, a cost has to be included in the predictions.

A last example of the use of a priori interconnect prediction is the evaluation of new computer architectures [49], especially three-dimensional opto-electronic architectures. Since such architectures are not yet available, their possible benefits have to be quantified by predictive techniques. Results show [28, 29, 33, 35, 50] that three-dimensional systems (*i.e.*, where the gates are placed on a three-dimensional grid) have significantly lower wire lengths than two-dimensional systems (Fig. 12). The connections in the third dimension could be implemented as optical links as in Fig. 13. Whatever the implementation, it is likely that the third dimension inter-

Dirk Stroobandt

It took thirty years for research on system-level interconnection prediction to mature but significant progress has been made in the last couple of years. We have introduced the field and the models that are the basis for wirelength prediction: Rent's rule and Donath's wirelength estimation model. Recent advances have been highlighted and we have reviewed some of the applications of *a priori* interconnect pre-

diction, notably technology extrapolation, wiring layer assignment and the evaluation of three-dimensional opto-electronic systems. In each of these applications, system-level interconnect prediction techniques allow the *a priori* estimation of interconnection lengths and resource demands for interconnects.

#### Recent Advances ... continued from Page 15

connects will behave differently from their two-dimensional electrical counterparts. Therefore, a cost has to be in-

cluded in the predictions. Such anisotropic three-dimensional architectures have been evaluated in [30, 35] and the benefits quantified as a function of the cost of the third dimension interconnects (see Fig. 14).

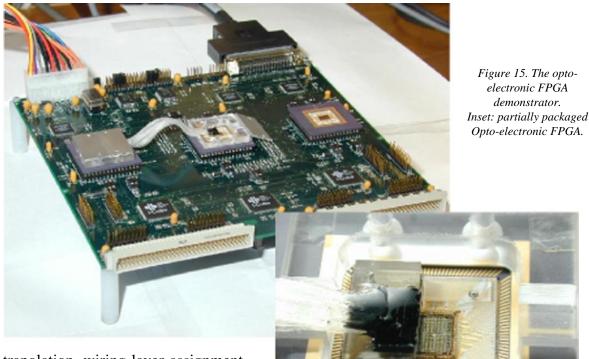

Based on the results from the interconnect length prediction analysis, an opto-electronic demonstrator has been built as part of a European project [35, 51]. A prototype is shown in Fig. 15.

#### Conclusions

It took thirty years for research on system-level interconnection prediction to mature but significant progress has been made in the last couple of years. We have introduced the field and the models that are the basis for wirelength prediction: Rent's rule and Donath's wirelength estimation model. Recent advances have been highlighted and we have reviewed some of the applications of *a priori* interconnect prediction, notably technology ex-

trapolation, wiring layer assignment and the evaluation of three-dimensional opto-electronic systems. In each of these applications, system-level interconnect prediction techniques allow the *a priori* estimation of interconnection lengths and resource demands for interconnects.

In summary, system-level interconnect prediction will be enabling tomorrow's convergent system-level design and hand-off to physical implementation. The field provides a key bridge between process technology, system architecture, and design tools. The references in this paper provide a unique view of the state-of-the-art in system-level interconnect prediction. We hope that they will inspire many researchers to increase their efforts in this important research domain.

#### References

- D. Stroobandt and A. B. Kahng, Workshop Notes First International Workshop on System-Level Interconnect Prediction, April 1999. Notes available at http:// www.elis.rug.ac.be/~dstr/SLIP.html.

- [2] D. Stroobandt and A.B. Kahng (guest eds.), IEEE Transactions on VLSI Systems, Special Issue on System-Level Interconnect

... continued on Page 18

**Dirk Stroobandt** graduated in 1994 and obtained the Ph.D. degree in electrotechnical engineering in 1998 from Ghent University, Belgium. From 1994 to 1998, he was research assistant and currently he is post-doctoral fellow with the Fund for Scientific Research— Flanders, Belgium (F.W.O.). Dr. Stroobandt is affiliated with the Department of Electronics and Information Systems (ELIS), Parallel Information Systems group (PARIS) of Ghent University. His research is oriented towards *a priori* estimations of interconnection lengths in electronic systems and its applications to CAD, computer architecture evaluation, and design optimization. He is the inaugural winner of the ACM/SIGDA Outstanding Doctoral Thesis Award in Design Automation and initiator and co-founder of the ACM International Workshop on System-Level Interconnect Prediction (SLIP), as well as the general chair of SLIP-2000. From July 1999 to June 2000, he visited UCLA as a post-doctoral researcher affiliated with the group of Andrew B. Kahng.

- Recent Advances ... continued from Page 17 Prediction, September 2000. Web:http:// www.elis.rug.ac.be/~dstr/TVLSI.html.

- [3] A. Caldwell, Y. Cao, A. Kahng, F. Koushanfar, H. Lu, I. Markov, M. Oliver, D. Stroobandt, and D. Sylvester, "GTX: The MARCO GSRC Technology Extrapolation System", *IEEE/ACM Design Automation Conference*, June 2000. Web: http://vlsicad.cs.ucla.edu/GSRC/GTX/.

- [4] Semiconductor Industry Association. International Technology Roadmap for Semiconductors, December 1999. http:// www.itrs.net/.

- [5] B. S. Landman and R. L. Russo, "On a Pin Versus Block Relationship for Partitions of Logic Graphs", *IEEE Transactions on Computers*, vol. 20, pp. 1469–1479, 1971.

- [6] P. Christie and D. Stroobandt, "The Interpretation and Application of Rent's Rule", *IEEE Transactions on VLSI Systems*, Special Issue on System-Level Interconnect Prediction, September 2000.

- [7] P. Zarkesh-Ha, J. A. Davis, W. Loh, and J. D. Meindl, "On a Pin Versus Gate Relationship for Heterogeneous Systems: Heterogeneous Rent's Rule", *Proceedings IEEE Custom Integrated Circuit Conference*, pp. 93–96, 1998.

- [8] P. Zarkesh-Ha, J. A. Davis, and J. D. Meindl, "Prediction of Net Length Distribution for Global Interconnects in a Heterogeneous System-on-a-Chip", *IEEE Transactions on VLSI Systems*, Special Issue on System-Level Interconnect Prediction, September 2000.

- [9] F. Brglez, D. Bryan, and K. Kozminski, *ISCAS'89 Benchmarks*, May 1989. Distributed on tape to participants of the Special Session on Sequential Test Generation, International Symposium on Circuits and Systems; partially characterized in F. Brglez, D. Bryan, and K. Kozminski, "Combinational Profiles of Sequential Benchmark Circuits", *Proceedings IEEE International Symposium on Circuits and Systems*, pp. 1929–1934, 1989.

- [10] Y.-C. Wei and C.-K. Cheng, "Ratio Cut Partitioning for Hierarchical Designs", *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 10, no. 7, pp. 911–921, July 1991.

- [11] H. Van Marck, D. Stroobandt, and J. Van Campenhout, "Toward an Extension of Rent's Rule for Describing Local Variations in Interconnection Complexity", S. Bai, J. Fan, and X. Li (eds.), *Proceedings Fourth International Conference for Young Computer Scientists*, pp. 136–141. Peking University Press, 1995.

- [12] D. Stroobandt, "On an Efficient Method for Estimating the Interconnection Complexity of Designs and On the Existence of Region III in Rent's Rule", M. A. Bayoumi and G. Jullien (eds.), *Proceedings Ninth Great Lakes Symposium on VLSI*, IEEE Computer Society Press, pp. 330–331, March 1999.

- [13] D. Stroobandt. "Pin Count Prediction in Ratio Cut Partitioning for VLSI and ULSI", M. A. Bayoumi (ed.), Proceedings IEEE International Symposium on Circuits and Systems, IEEE, pp. VI–262– VI–265, May 1999.

- [14] J. Darnauer and W. Dai, "A Method for Generating Random Circuits and Its Application to Routability Measurement", *Proceedings ACM/SIGDA International Symposium on Field Programmable Gate Arrays*, pp. 66–72, 1996.

- [15] D. Stroobandt, J. Depreitere, and J. Van Campenhout, "Generating New Benchmark Designs Using a Multi-Terminal Net Model", *Integration, The VLSI Journal*, vol. 27, no. 2, pp. 113–129, 1999.

- [16] P. Verplaetse, J. Van Campenhout, and D. Stroobandt, "On Synthetic Benchmark Generation Methods", *Proceedings IEEE International Symposium on Circuits and Systems*, vol. IV, pp. 213–216, May 2000.

- [17] D. Stroobandt, P. Verplaetse, and J. Van Campenhout, "Generating Synthetic Benchmark Circuits for Evaluating CAD Tools", *IEEE Transactions on Computer*-

Aided Design of Integrated Circuits and Systems, 2000, in press.

- [18] W. E. Donath, "Placement and Average Interconnection Lengths of Computer Logic", *IEEE Transactions on Circuits* and Systems, vol. 26, pp. 272–277, 1979.

- [19] D. Stroobandt, H. Van Marck, and J. Van Campenhout, "An Accurate Interconnection Length Estimation for Computer Logic", *Proceedings Sixth Great Lakes Symposium on VLSI*, IEEE Computer Society Press, pp. 50–55, 1996.

- [20] D. Stroobandt and J. Van Campenhout, "Accurate Interconnection Length Estimations for Predictions Early in the Design Cycle", *VLSI Design*, Special Issue on Physical Design in Deep Submicron, vol. 10, no. 1, pp. 1–20, 1999.

- [21] R. Keyes, *The Physics of VLSI Systems*. Addison-Wesley, 1987.

- [22] P. Christie, "Clouds, Computers, and Complexity", S. K. Tewsbury (ed.), Frontiers of Computer Systems Research, vol. 2, ch. 4. Plenum, 1991.

- [23] P. Christie, "A Canonical Ensemble Analysis of Interconnect Limited Systems", Proceedings IEEE International Symposium on Circuits and Systems, pp. 2108–2111, June 1991.

- [24] J. E. Cotter and P. Christie, "The Analytical Form of the Length Distribution Function of Computer Interconnections, *IEEE Transactions on Circuits and Systems*, vol. 38, pp. 317–320, 1991.

- [25] D. Stroobandt and H. Van Marck, "Efficient Representation of Interconnection Length Distributions Using Generating Polynomials", *Proceedings ACM International Workshop on System-Level Interconnect Prediction (SLIP 2000)*, pp. 99–105, April 2000.

- [26] J. A. Davis, V. K. De, and J. D. Meindl, "A Stochastic Wire-Length Distribution for Gigascale Integration (GSI) — PART I: Derivation and Validation", *IEEE Transactions on Electron Devices*, vol. 45, no. 3, pp. 580–589, 1998.

- [27] A. Masaki and M. Yamada, "Equations for Estimating Wire Length in Various Types of 2–D and 3–D System Packaging Structures", *IEEE Transactions on Computers, Hybrids, and Manufacturing Technology*, vol. CHMT-10, no. 2, pp. 190–198, 1987.

- [28] D. Stroobandt and J. Van Campenhout, "Estimating Interconnection Lengths in Three-Dimensional Computer Systems", *IEICE Transactions on Information and Systems*, Special Issue on Synthesis and Verification of Hardware Design, vol. E80– D, no. 10, pp. 1024–1031, October 1997.

- [29] A. Rahman, A. Fan, and R. Reif, "System-Level Performance Evaluation of Three-Dimensional Integrated Circuits", *IEEE Transactions on VLSI Systems*, Special Issue on System-Level Interconnect Prediction, September 2000.

- [30] H. Van Marck and J. van Campenhout, "Modeling and Evaluating Optoelectronic Architectures", R. T. Chen and J. A. Neff (eds.), *Optoelectronics II*, vol. 2153 of *SPIE Proceedings Series*, SPIE, pp. 307– 314, 1994.

- [31] H. Van Marck and J. Van Campenhout, "Modeling Signal Delay Distribution in Optoelectronic Architectures", R. T. Chen and H. S. Hinton (eds.), *Optoelectronic Interconnects III*, vol. 2400 of *SPIE Proceedings Series*, pp. 267–276. SPIE, 1995.

- [32] H. M. Ozaktas and J. Goodman, "Implications of Interconnection Theory for Optical Digital Computing", *Applied Optics*, vol. 31, pp. 5559–5567, 1992.

- [33] H. Van Marck and J. Van Campenhout, "Three-Dimensional Optoelectronic Architectures for Massively Parallel Processing Systems", J. Goodman, S. Hinton, T. Pinkston, and E. Schenfeld (eds.), Proceedings Fourth International Conference on Massively Parallel Processing Using Optical Interconnections, IEEE Computer Society Press, pp. 178–182, 1997.

- [34] H. Van Marck, M. Brunfaut, J. Dambre, H. Neefs, and J. Van Campenhout, "De-... continued on Page 20

- Recent Advances ... continued from Page 19 sign Issues for Three-Dimensional Optoelectronic Architectures", A. Priou (ed.), *Proceedings PIERS 98*, vol. 3, p. 1064, July 1998.

- [35] J. Van Campenhout, H. Van Marck, J. Depreitere, and J. Dambre, "Optoelectronic FPGAs", *IEEE Journal of Selected Topics in Quantum Electronics on Smart Photonic Components, Interconnects, and Processing*, vol. 5, no. 2, pp.306–315, March/April 1999.

- [36] D. Stroobandt, H. Van Marck, and J. Van Campenhout, "Estimating Logic Cell to I/O Pad Lengths in Computer Systems", T. Sasao (ed.), *Proceedings Workshop on* Synthesis and System Integration of Mixed Technologies, SASIMI'97, S. Insatsu, Osaka, Japan, pp. 192–198, December 1997.

- [37] D. Stroobandt and F. J. Kurdahi, "On the Characterization of Multi-Point Nets in Electronic Designs", M. A. Bayoumi and G. Jullien (eds.), *Proceedings Eighth Great Lakes Symposium on VLSI*, IEEE Computer Society Press, pp. 344–350, February 1998.

- [38] P. Zarkesh-Ha, J. A. Davis, W. Loh, and J. D. Meindl, "Prediction of Interconnect Fan-Out Distribution Using Rent's Rule", *Proceedings ACM International Workshop on System-Level Interconnect Prediction*, pp. 107–112, 2000.

- [39] H. B. Bakoglu, Circuits, Interconnections, and Packaging for VLSI. Addison-Wesley, 1990.

- [40] J. C. Eble, V. K. De, D. S. Wills, and J. D. Meindl, "A Generic System Simulator (GENESYS) for ASIC Technology and Architecture beyond 2001", *Proceedings Ninth Annual IEEE International ASIC Conference*, pp. 193–196, 1996.

- [41] B. M. Geuskens, Modeling the Influence of Multilevel Interconnect on Chip Performance, Ph.D. Thesis, Rensselaer Polytechnic Institute, Troy, New York, 1997. http://latte.cie.rpi.edu/ripe.html.

- [42] G. Sai-Halasz, "Performance Trends in High-Performance Processors", *Proceed*ings IEEE, pp. 20–36, 1995.

- [43] D. Sylvester and K. Keutzer, "System-Level Performance Modeling with BACPAC—Berkeley Advanced Chip Performance Calculator", Notes International Workshop System-Level Interconnect Prediction, pp. 109–114, 1999. http:// www.eecs.berkeley.edu/~dennis/bacpac/.

- [44] P. Li, P. Nag, and W. Maly, "Cost Based Tradeoff Analysis of Standard Cell Designs", Proceedings ACM International Workshop on System-Level Interconnect Prediction, pp. 129–135, April 2000.

- [45] P. Chong and R. Brayton, "Estimating and Optimizing Routing Utilization in DSM Design", D. Stroobandt and A.B. Kahng, (eds.), Notes International Workshop on System-Level Interconnect Prediction, pp. 97–102, 1999.

- [46] Q. Chen, J. Davis, P. Zarkesh-Ha, and J. Meindl, "A Compact Physical Via Blockage Model", *IEEE Transactions on VLSI Systems*, Special Issue on System-Level Interconnect Prediction, September 2000.

- [47] A.B. Kahng, S. Mantik, and D. Stroobandt, "Requirements for Models of Achievable Routing", *Proceedings International Symposium on Physical Design* (ISPD 2000), pp. 4–11, April 2000.

- [48] A.B. Kahng and D. Stroobandt, "Wiring Layer Assignments with Consistent Stage Delays", Proceedings ACM International Workshop on System-Level Interconnect Prediction (SLIP 2000), pp. 115–122, April 2000.

- [49] S. Chai, T. Taha, D. Wills, and J. Meindl, "Heterogeneous Architecture Models for Interconnect-Motivated System Design", *IEEE Transactions on VLSI Systems*, Special Issue on System-Level Interconnect Prediction, September 2000.

- [50] K. Saraswat, S. Souri, K. Banerjee, and P. Kapur, "Performance Analysis and Technology of 3-D ICs", *Proceedings* ACM International Workshop on System-

## NEWARTICLES

The IEEE Circuits and Systems Society Newsletter will become the IEEE Circuits and Systems Society Magazine in January, 2001.

### **Style Considerations**

- 1) Articles are readable by the entire CAS membership.

- 2) Articles are about eight published pages in length. We can, however, accommodate longer or shorter items if the situation seems appropriate.

- 3) Articles communicate primarily by graphs, diagrams, and pictures. Many authors have begun the inevitable transition to color, as may be seen in back issues of the *Newsletter*, available at www.nd.edu/ ~stjoseph/newscas/. In issue layout, the editors often build upon the colors chosen by the authors.

- Equations are to be used sparingly, except for special situations. When equations are present, they may receive special graphical design treatment.\*

### **Submission Information**

- File format for diagrams, figures, graphs, and photos is .eps format. If another format is needed, permission should be obtained from the editor at sain.1@nd.edu. Such files should be provided separately from the text. If an embedded document is submitted, say for ease of review, then accompanying text and separate .eps files should also be provided.

- 2) Abstracts, or complete papers, are submitted to the Features Co-Editors, who will review them to determine if final papers will be a good fit. All papers are subject to review and requests for revision.

#### **Features Editors**

Guanrong Chen Department of Electronic Engr. City University of Hong Kong Hong Kong, P. R. China (on leave from U. Houston) Phone: (852) 2788–7922 Fax: (852) 2788–7791 E-mail: gchen@ee.cityu.edu.hk Rui J. P. de Figueiredo Department of Electrical and Computer Engineering University of California, Irvine Irvine, CA, USA 92697–2625 Phone: (949) 824–7043 Fax: (949) 824–2321 E-mail: rui@uci.edu

\* Note that December 1999 is an exception to the equation restriction. Future exceptions are likely to be rare.

### Addendum on CORELESS PRINTED CIRCUIT BOARD (PCB) TRANSFORMERS—

### FUNDAMENTAL CHARACTERISTICS AND PPLICATION POTENTIAL

S. Y. (Ron) Hui

S. C. Tang

H. Chung

Since the article [1] on coreless PCB transformers was published in the last *IEEE Circuits and Systems Newsletter*, many inquiries about the details of their applications have been received. This supplementary article is a collective response to these inquiries.

#### **PCB Laminate Thickness**

In our research, we use standard FR4 PCBs. Nominal thickness of standard PCB is: 0.4mm, 0.6mm, 0.8mm, 1.0mm and 1.5mm. For the gate drive circuits for power mosfets and IGBTs, we use PCB with thickness of 1.5mm. For power transfer applications such as power transformers for power converters, we use PCB with thickness of 0.4mm. The choice of thickness depends on the applications. The magnetic coupling of coreless PCB transformers increases if the PCB thickness (i.e., the distance between the two printed planar transformer windings) becomes smaller. For signal transfer with low power involvement, a standard PCB of 1.5mm is acceptable. However, for high power transfer, using thin PCB is more appropriate because it offers higher magnetic coupling than thick PCB. In general, we use standard

low-cost PCB with 1 ounce copper/sq. ft. for low-power applications. The results obtained so far are based on lowcost PCBs. However, we are now studying coreless PCB transformers for power transfer applications using PCB with 3 ounce copper/sq. ft.

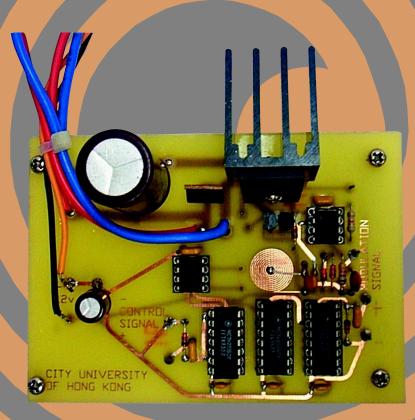

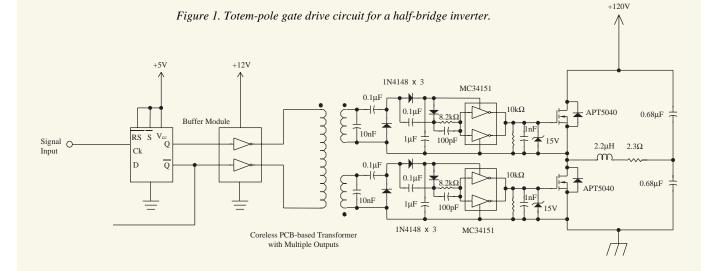

#### **Power Electronic Gate Drives**

We have compared the core-based and the coreless approaches in some applications. An example is the totem pole gate drive circuit shown in Fig. 1. The same circuit has been tested with

We have compared the corebased and the coreless approaches in some applications. An example is the totem pole gate drive circuit shown in Fig. 1. The same circuit has been tested with both core-based transformer and coreless transformer [2].

<sup>...</sup> continued on Page 24

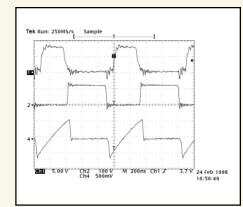

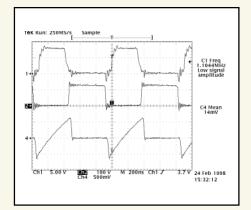

Figure 2a. Measured switching waveforms using core-based transformer at 1.1 MHz. Top trace: Gating Signal (5V/div) Middle trace: Drain-source voltage (100V/div) Bottom trace: Drain current (5A/div)

#### PCB Transformers Addendum... continued from Page 23

both core-based transformer and coreless transformer [2]. Figure 2a and Fig. 2b show the measured results of the *core-based* and *coreless* approaches, respectively. Essentially, there is no major difference in the gate drive performance in both cases. This is a good indication that the coreless approach is as good as the core-based approach in some existing applica-

At high frequency operations, the shortcomings of core-based transformers (such as frequency limits, core saturation and core losses) could become limiting factors for their applications. The advantages of coreless PCB transformers over their core-based counterparts become more obvious when the operating frequency increases.

Figure 2b. Measured switching waveforms using coreless transformer at 1.1 MHz. Top trace: Gating Signal (5V/div) Middle trace: Drain-source voltage (100V/div) Bottom trace: Drain current (5A/div)

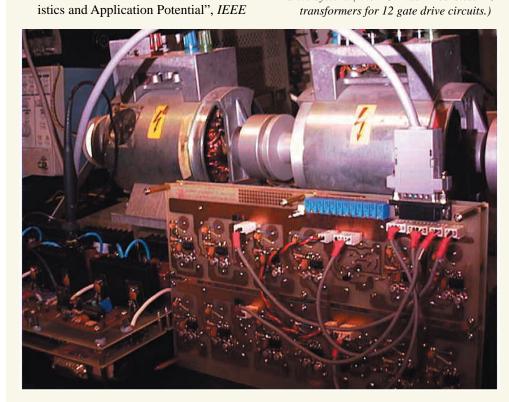

tions. Figure 3 shows the PCB of the control and gate drive circuit for a neutral-clamped 3-level power inverter motor drive system that has 12 power switches. This PCB contains 12 gate drives and thus 12 coreless PCB transformers. Despite the notorious noise problems in motor drive environments, this control PCB has been working reliably for over 2 years [3].

#### **Other Application Potentials**

It is envisaged that coreless PCB transformers can replace core-based transformers in some industrial applications. At high frequency operations, the shortcomings of core-based transformers (such as frequency limits, core saturation and core losses) could become limiting factors for their applications. The advantages of coreless PCB transformers over their core-based counterparts become more obvious when the operating frequency increases. There are many other aspects of coreless PCB transformers or similar structures to be explored. For example, when fabricated on dielectric materials, the coreless printed windings can form part of an integrated circuit structure. Coreless

Department of Electronic Engineering City University of Hong Kong Tat Chee Avenue, Kowloon Hong Kong (<u>eeronhui@cityu.edu.hk</u>)

PCB transformers can also be printed

on flexible PCBs. The primary and

secondary planar windings need not

be printed on the same PCB. Thus,

the coreless PCB transformer tech-

nology may be potentially useful for

smart card applications because both

energy and signal (information) can

be transferred to the smart card inte-

grated circuits. The potentials and

limitations of coreless PCB trans-

formers deserve more investigation.

**References** [1] S.Y.R. Hui, S.C. Tang and H. Chung,

"Coreless Printed Circuit Board (PCB)

Transformers - Fundamental Character-

S. Y. (Ron) Hui

S. C. Tang

*Circuits and Systems Society Newsletter*, vol. 11, no. 3, pp. 3–15, 2000.

- [2] S.C. Tang, S.Y.R. Hui and H. Chung, "Coreless Printed Circuit Board (PCB) Transformers with Multiple Secondary Windings for Complementary Gate Drive Circuits", *IEEE Transactions on Power Electronics*, vol. 14, no. 3, pp. 431–437, May 1999.

- [3] Y. Shrivastava and S.Y.R. Hui, "Analysis of Random PWM Switching Methods for Three-Level Power Inverters", *IEEE Transactions on Power Electronics*, vol. 14, no. 6, pp. 1156–1163, November 1999.

Figure 3. Picture of the control PCB for a neutral-clamped 3-level power inverter motor drive system. (The PCB has 12 coreless PCB

H. Chung

25

### St. Petersburg

Figure 1. Dom Uchenyh (House of Scientists) - Conference venue.

### **Control of Oscillations and Chaos:** Report of the 2nd International Conference

he emerging field of control-L ling chaotic behavior of complex systems attracted increasing attention during the last decade, from both control experts and general audiences. Although the theme of controlling chaos and oscillations has been well represented in the programs of several major conferences related to nonlinear dynamics and control systems during recent years, common interest in the theme has been so strong that conferences where control of complex behavior would be the main topic were still strongly demanded. The first such international conference, entitled "Control of Oscillations and Chaos" (COC'97) took place in St. Petersburg, Russia, in 1997. It attracted about 200 participants from more than 30 countries (for more details, see http://

www.ipme.ru/coc97.html). Because of the success of COC'97, it was decided to organize the second such conference three years after, also in St. Petersburg. Thus, the 2nd International Conference "Control of Oscillations and Chaos" (COC 2000) took place in St.Petersburg on July 5-7, 2000. It was organized by the Institute for Problems of Mechanical Engineering of the Russian Academy of Sciences, St. Petersburg State University, and the St. Petersburg Informatics and Control Society, and co-sponsored by the IEEE Circuits and Systems Society, the International Union of Theoretical and Applied Mechanics (IUTAM), the Russian Academy of Sciences and the Russian Foundation for Basic Research, along with technical co-sponsorship of the IEEE

Control Systems Society and the Russian IEEE Section. Various problems related to analysis, synchronization and control of complex oscillatory dynamical systems, with emphasis on both theory and applications, were presented and discussed. Many papers from different scientific fields (mathematics; physics; mechanics; chemistry; mechanical, electrical and civil engineering; biology; economics; and so forth) were presented and published in the conference proceedings.

About 180 papers were selected by the International Program Committee from among 210 submissions for inclusion in the final conference Program. More than 170 participants, including 68 speakers from outside of Russia, registered. A total of 7 plenary, 9 semi-plenary, 96 regu-

### Russia

Figure 2. Neva embankment. To the left—Dom Uchenyh, to the right—The Hermitage.

lar and 40 poster papers were presented. Three volumes of conference proceedings were published, which include 165 papers representing 33 countries. The numbers of papers presented are from Russia (87), USA (14), Italy (8), Japan (6), Germany (6), Brazil (4), Korea (4), Argentina (3), P.R.China (3), France (3), Ukraine (3), and Yugoslavia (3). The conference took place in the "Dom Uchenyh" ("House of Scientists")-a beautiful palace in the historical center of St. Petersburg, next to the Tsar's Winter Palace and the Hermitage museum. Social Programs included sightseeing tours: survey bus tour of St. Petersburg, tours of the Hermitage, and a bus tour to Peterhof. The conference banquet took place on Friday, July 7 in the House of Scientists.

#### Summary of the Scientific Program

The conference as a whole has demonstrated continuing interest in analysis and control methods for chaotic dynamics and oscillations. Papers from various scientific fields were presented at the conference. Most papers were devoted to dynamics and control of systems from the two broad fields: mechanical systems (main applications are motion control, robotics, and vibrational technologies); and electrical or electronic systems (main applications are in the field of telecommunications and power systems). It brought together many experts to cross-fertilize ideas from these fields that have common features and similarities. Such a gathering was made possible by the financial support to the conference from different resources, particularly from the IEEE and the IUTAM.

A number of the papers addressed the problems of analysis of complex behavior in physical systems. Significant attention was paid to analysis and design of neural networks, and studies of complexity and synchronization in nonlinear systems. Also, many papers with applications to chemical technologies, geophysics, medicine, economics, and so forth, were presented. Some plenary and semi-plenary papers contained important theoretical results: O. M. Belotserkovsky, Yr.D. Shevelev, and F. A. Maksimov(Russia): "Some Problems of Turbulence and Instabili-

... continued on Page 28

Figure 3. From left to right: Prof. F. L. Chernousko, member of the Russian Academy of Sciences and chair of International Program Committee of COC 2000; Prof. Rui J. P. de Figueiredo, University of California, Irvine, and IEEE CAS Society Distinguished Lecturer; Prof. W. Schielen, University of Stuttgart, Germany, and president, International Union of Theoretical and Applied Mechanics; and Prof. A. L. Fradkov, St. Petersburg State University and chair of the National Organization Committee, COC 2000.

#### COC Report... continued from Page 27

ties"; I. I. Blekhman and K. A. Lurie (Russia-USA): "Creating Dynamical Materials as a Problem of Control"; F. L. Chernousko (Russia): "Snake-Like Motions of Multibody Systems over a Rough Plane"; M. Dimentberg, D. Iourtchenko and A. Bratus (USA-Russia): "Optimal Bounded Control of Random Vibration"; K. S. Hedrih (Yugoslavia): "Nonlinear Dynamics of a Gyrorotor and Sensitive Dependence on the Initial Conditions of the Forced Vibration of a Heavy Gyrorotor"; P. C. Mueller (Germany): "Nonlinearity Estimation and Compensation by Linear Observers-Theory and Applications"; A. N. Sharkovsky and S. A. Berezovsky (Ukraine): "Phase Transitions in Computer Turbulence"; and F. Udwadia (USA): "New Developments in Dynamics of Constrained Systems with Applications to Tracking Control".

Other speeches were devoted to applications in telecommunications, mechanical engineering, and biology; A. S. Dmitriev, A. L. Panas, and S. O. Starkov (Russia): "Multiple Access Communication Based on Control of Special Chaotic Trajectories"; E. Kreuzer and M. Wendt (Germany): "Nonlinear Dynamics of Ship Oscillations"; E. Mosekilde (Denmark): "Chaotic Synchronization in Living Systems"; F. Pfeiffer, Th. Rossmann, and K. Loffler (Germany): "Control of a Tube Crawling Machine"; and W. Schiehlen (Germany): "Motion Control of Vehicles in Convoy". Finally, the IEEE Distinguished Lecture entitled "A Reproducing Kernel Hilbert Space (RKHS)

Figure 4. White Night in St.Petersburg. Dom Uchenyh and The Hermitage are behind halfs of the opened bridge.

Approach to the Optimal Modeling, Identification, and Design of Nonlinear Adaptive Systems" was delivered by Prof. Rui J.P. de Figueiredo (USA), at the closing plenary session. Regular papers were distributed over the following eleven theme sections (four sessions in parallel):

- Control of Oscillations, A. Fradkov, chairman;

- *Control of Chaos*, R. Genesio, A. Tesi, A. Pogromsky, co-chairmen;

- *Control of Mechanical Systems*, V. Yu. Rutkovsky, chairman;

- Mathematics of Stability and Instability, G. A. Leonov, chairman;

- Identification and Reconstruction of Parameters, A. N. Sharkovsky, chairman;

- *Synchronization*, I. I. Blekhman, chairman;

- Nonlinear Dynamics and Chaos in Physical Systems, A. K. Abramyan, S. A. Vakulenko, co-chairmen;

- Nonlinear Dynamics and Chaos in Mechanical Systems,

D. A. Indejtsev, chairman;

- Nonlinear Dynamics and Chaos in Electronics, Communications and Power Systems, A.S. Dmitriev, chairman;

- Nonlinear Dynamics and Chaos in Biomedical, Ecological and Neural Systems, V. S. Anischenko, chairman;

- *Methods of System Analysis*, E. N. Rozenwasser, chairman.

The major goal of the conference-to bring together researchers from various fields, to advance the state-of-the-art control theory and technology for the control and analysis of complex oscillatory dynamical systems, and to gain some general and unified perspectives in this interdisciplinary field of advanced research-was achieved. Another goal of the conference-to get the world scientific community acquainted with recent achievements of Russian experts in nonlinear dynamics and nonlinear control-was achieved too.

> -Prof. Alexander Fradkov NOC Chairman, COC2000

Thank you... continued from Page 3

Vol. 1, No. 1-John Greenbaum, Ruey-wen Liu, Kenneth R. Laker, Anthony N. Michel, Randall L. Geiger; Vol. 1, No. 2-Ming Liou, Ronald H. Johnston, John Greenbaum, T; Vol. 1, No. 3–John Greenbaum, Adrian Ioinovici, Rolf Schaumann; Vol. 1, No. 4-Sung-Mo (Steve) Kang, Anthony C. Davies, Ruey-wen Liu, John Greenbaum, E; Vol. 2, No. 1-Harlan E. Anderson, Ian Getreu, Randall L. Geiger, John Greenbaum, B. A. Shenoi; Vol. 2, No. 2–Steve Kang, Ω, 🖬; Vol. 2, No. 3–Steven C. Bass, John Greenbaum, M. -T. Sun, Martin Hasler, Moncef Gabbouj, Benjamin J. Leon, J. K. Pal, Zhenming Chai, Ω; Vol. 2, No. 4–W. Kent Fuchs, Phillip E. Allen, Ω, Reddeppa N. Pothuri, Moshe Kam, 🖥; Vol. 3, No. 1–Randall L. Geiger, Ω, Phillip E. Allen; Vol. 3, No. 2–Sung-Mo (Steve) Kang, Martin Hasler, Anthony C. Davies, J. K. Pal, Sharad Seth, Ω, 🖥 ; Vol. 3, No. 3–Randall L. Geiger, Wai-Kai Chen, Anthony C. Davies, Eric M. Dowling, Ω, Sarah A. Rajala, Armen Zemanian; Vol. 3, No. 4–Randall L. Geiger, W. Kent Fuchs, Anthony C. Davies, E. Pun, Mehmet Ali Tan, Ω, Jacek Zurada, 📑 Vol. 4, No. 1–Wai-Kai Chen, Robert Spence, Phillip E. Allen, Moon Key Lee, D. Otter, Anthony C. Davies, Ω; Vol. 4, No. 2–Wai-Kai Chen, Moncef Gabbouj, Anthony C. Davies, Robert J. Marks II, Mani Soma, Sergio Takeo Kofuji, N. Ranganathan, 📕,  $\Omega$ ; Vol. 4, No. 3–Philip v. Lopresti, Moncef Gabbouj, Michael M. Green, Chris Toumazou, Robert Spence, Wai-Kai Chen, Ω; Vol. 4, No. 4-Wai-Kai Chen, Steve Kang, Gaynor Taylor, 📕, Ω; Vol. 5, No. 1-Tatsuo Ohtsuki, Anthony C. Davies, Ibrahim Gedeon, King N. Ngan, Michael M. Green, Martin Hasler, Ω; Vol. 5, No. 2–N. Ranganathan, Malgorzata Marek-Sadowska, T, Ω; Vol. 5, No. 3–Michael Green, Jack L. Meador, Steve Kang, Kou-Hu Tzou, Anthony C. Davies, Moncef Gabbouj, David Haigh, F. Seifert, David Allstot, Ω; Vol. 5, No. 4-Wai-Kai Chen, J. K. Pal, Anthony C. Davies, Takashi Matsumoto, Florin Constantinescu, Martin Hasler, S. Ω; Vol. 6, No. 1–Rueywen Liu, Jacques Kowalczuk, Craig Cobb, Michael Green, Adrian Ioinovici, Chris Toumazou, Min-Yu Hsueh, Jalil Fadavi; Vol. 6, No. 2–Martin Hasler, Phillip E. Allen, N. Ranganathan, Mohammed Ismail, 📱, Ω; Vol. 6, No. 3–Anthony Davies, David Haigh, Peter Pirsch, Edgar Sánchez-Sinencio, Eby Friedman, Bing Sheu, Ω; Vol. 6, No. 4–Ruey-wen Liu, John Choma, Jr, B. D. Reljin, Andreas Andreau, Moncef Gabbouj, Min-Yu Hsueh, Adrian Ioinovici, Michael Green, B. A. Shenoi, Ω, Vol. 7, No. 1–Michael Lightner, Ming-Ting Sun,  $\Omega$ ; Vol. 7, No. 2–John Choma, David Haigh, Craig Cobb, N. Ranganathan & Sharad Seth,  $\Omega$ ; Vol. 7, No. 3, J. K. Pal, Árpád Csurgay, Josef A. Nossek, Edward J. Coyle,  $\Omega$ ; Vol. 7, No. 4–Michael Lightner,  $\Omega$ ,  $\Omega$  (Paul J. Daniels), Richard M. Chen, Barbara Wehner & Clifford Lau; Vol. 8, No. 1–John Choma, Jr., Barbara Wehner & Clifford Lau,  $\Omega$ ; Vol. 8, No. 2-Evelyn Pate Van Valkenberg, José Silva-Martinez, Anthony Davies, Joannis Pitas, Michael Peter Kennedy, Maciej J. Ogorzalek, Sharad Seth & N. Ranganathan,  $\Omega$ ; Vol. 8, No. 3–Barbara Wehner & John Choma, Thanos Stouraitis, Eby Friedman,  $\Omega$ ; Vol. 8, No. 4–Edgar Sánchez-Sinencio, Mohammed Ismail, Guanrong Chen, Richard Snyder, Ω; Vol. 9, No. 1–Guanrong Chen, Yannis Tsividis, Rui J. P. de Figueiredo, Rui J. P. de Figueiredo, Ernest S. Kuh & Irwin W. Sandberg, Mervyn E. Jones, Liviu Goras, José Silva-Martinez, Anthony C. Davies, Hari C. Reddy, Norman Balabanian, Ω; Vol. 9, No. 2–John Choma, Jr., Graham R. Hellestrand, Chris Toumazou & Mervyn Jones, Vamsi Krishna, Ljiljana Trajkovic, Ω; Vol. 9, No. 3–Yih-Fang Huang & Paulo S. R. Diniz, Géza Kolumbán & Michael Peter Kennedy, Wayne Wolf, José Silva-Martinez, Panajotis Agathoklis, Rui J. P. de Figueiredo, Barbara Wehner, Ω; Vol. 9, No. 4–M. E. Zaghloul, Markus Helfenstein & George S. Moschytz, Rui J. P. de Figueiredo, Rui J. P. de Figueiredo, B. A. Shenoi, Anthony Davies, Q; Vol. 10, No. 1–Taehyung Wang & Phillip C.-Y. Sheu, Lee M. Garth, Gang Huang, & Jean-Jacques Werner, Ming-hau Lee, Guangming Lu, Hartej Singh, Nader Bagherzadeh, Fadi J. Kurdahi, Eliseu M. C. Filho, & Vladimir Castro Alves, Rui J. P. de Figueiredo, Magdy A. Bayoumi, Barbara Wehner, George S. Moschytz, Anthony Davies, Ω; Vol. 10, No. 2–Guanrong Chen, Jorge L. Moiola, & Hua O. Wang, K. S. Tang, Kim-Fung Man, & S. Kwong, Babak Ziaie, Ω; Vol. 10, No. 3–Juan E. Cousseau, Lang Hong, Eby G. Friedman, H. K. Kwan, Ω; Vol. 10, No. 4–Mario di Bernardo, Harold Szu, Eby Friedman & Wayne Wolf,  $\Omega$ ; Vol. 11, No. 1–Orla Feely, Chi K. Tse, Guanrong Chen, Barbara Wehner,  $\Omega$ ; Vol. 11, No. 2-Rui J. P. de Figueiredo & George C. Lai, Luis Antonio Aguirre, Nasser Kehtarnavaz & Victor Cheng, B. A. Shenoi, Dirk Stroobandt, Q; Vol. 11, No. 3–S. Y. (Ron) Hui, S. C. Tang, & H. Chung, Stefan Gruhl, Tajje-eddine Rachidi, A. Echihabi, Michael Link, & Michael Söllner, Hao Ying, Peter Aronhime, Bertram Shi, Csaba Rekeczky, Marco Gilli, & Mamoru Tanaka,  $\Omega$ ; Vol. 11, No. 4–Dirk Stroobandt, S. Y. (Ron) Hui, S. C. Tang, & H. Chung, B. A. Shenoi, Barbara Wehner, Ω

### CAS Society Distinguished Lecturer Program—Part II

### 2000 Distinguished Lecturers

Professor José E. da Franca

### Analog Libraries in Digital CMOS

*Abstract*—Advanced digital CMOS technologies are becoming an increasingly important manufacturing platform for mixed analog-digital integrated circuits. While such technologies provide ever improving performance for digital circuits, by contrast, analog circuits face a variety of design hurdles not usually present in "older" technologies with analog options. Chief among these are the unavailability of double-poly capacitors and high resistivity poly, poor transistor models and poorly characterized compatible bipolar transistors, and of course operation in highly "polluted" digital environments.

In this lecture we will review the fundamental problems and will provide practical answers for designing high performance analog circuits in mainstream digital CMOS. By making extensive use of such techniques as oversampling and noise-shaping, current-mode processing, self-calibration and digital correction, among others, several mixed-signal chip designs will be shown that can achieve the level of performance and robustness required in some of today's most relevant applications, thus allowing their integration in cost competitive digital VLSI processes.

### Multirate Analog Signal Processing

*Abstract*—Multirate signal processing emerged in the 70's as a specialized branch of digital signal processing, driven by the need for solving, in the most efficient possible way, a number of problems mainly related to the migration of telephone multi-

The following article is the second in a series, taken from an article written by B. A. Shenoi detailing the CAS Distinguished Lecturer Program, the lecturers, and their lectures. Begun in the June 2000 issue of the CAS Newsletter and continued here, it is a reminder to all of the excellent Distinguished Lecturers Program, a tribute to longtime chairman Belle Shenoi, and an introduction of Ellen Yoffa, the new chair of the program effective July 1, 2000. —Editor

plexing and transmission systems from analog and digital solutions. Subsequently, the technique found many more application areas of great relevance of which, today, the decimation and interpolation techniques applied to oversampling data converters are more familiar examples. The emergence of other non-digital signal processing technologies, such as charge transport devices and switched-capacitors, which are also discrete-time, although the signal amplitudes are represented in analog form, led to the development of analog multirate signal processing techniques which have found important application areas in the realization of complex filtering systems with very high Q-factors, as well as in highspeed interface and data acquisition systems of which video coders/ decoders and magnetic disk read channel coders are some of the most visible examples. Today, new design solutions are emerging, which combine the benefits of both digital and analog multirate signal processing to achieve high efficiency in silicon and power consumption in modern mixed analogdigital integrated circuits.

This lecture introduces the basic concepts of multirate theory and discusses its practical application to the design of analog sampled-data circuits, both switched capacitors and switched-currents. First, we will show how the ubiquitous switched-capacitors can efficiently realize the signal processing functions needed for analog-digital and digital-analog interfacing, frequency division multiplexing, high-Q filtering and even the currently "hot" subsampling mixers that might be employed in integrated radio receivers. Then, new switched-current realizations of multirate filters will also be shown for very high-frequency video processing applications.

*Abstract*—In a not too distant past, analog-to-digital (A/D) and digital-toanalog (D/A) signal converters were realized as standard components, produced by only a few highly specialized manufacturers worldwide, for assembly in larger boards or maybe even hybrid modules. Today the relentless trend of electronics integration and miniaturization is rapidly changing the way signal converters are used, designed and even produced. Because

### **XIOS Analog-Digital** Conversion

such converters are being increasingly used as macrocells embedded into larger VLSI mixed-signal systems, rather than standard discrete parts for board assembly, the traditional label of "general purpose" components they used to carry is quickly vanishing to pave the way to "tailor-made" components that can optimally meet target specifications for performance, cost and energy consumption. As a result, their design is no longer the exclusive specialty of a few manufacturers and instead is gaining preeminence also as an integral part of the expertise of the large teams usually involved in the design of those VLSI systems. This, in turn, leads to the fact that their production as part of completed mixed-signal VLSI chips is also shifting from the traditional manufacturers of generalpurpose standard components to the ASIC manufacturers. Therefore, the market dominant CMOS technology is also quickly replacing other processing technologies that have been widely used in the past for data converters.

Prof. José E. da Franca

Instituto Superio Vecnico IST Center for Microsystems

Av. Rovisco Pais. 1

1096, Lisboa Codex

Tel: +351 1 8417676

Fax: +351/1/841/1675

franca@ecsm4.ist.utl.pt

jfranca@ebipidea.pt

PORTUGAL

E-mail:

E-mail;

This lecture provides an overview of the most relevant circuit techniques currently employed for designing A/D

#### Distinguished Lecturers ... continued from Page 31

and D/A converters in CMOS technology. Practical examples will be given of about 10 high performance CMOS data converter designs covering a wide range of specifications both in terms of speed and resolution.

### High Resolution Pipeline CMOS ADCs

Abstract—Pipelined analog-todigital converters (ADCs) with specifications ranging from 12 to 14 bits of resolution at 50 to 100 MHz will play a key role in future CMOS integrated systems for portable multimedia and communication applications. Traditional designs of pipelined ADCs, particularly for resolutions up to 10 bits, have considered optimum 1-bit-perstage architectures yielding maximum speed of operation while minimizing area and power dissipation. For resolutions above 10 bits where self-calibration techniques are required for linearizing inter-stage residue generation and amplification, such design strategy no longer holds and we have to consider instead multibit-per-stage optimization procedures taking into account the constraints introduced by thermal noise, the self-calibration technique employed for accuracy enhancement of capacitor matching as well as the requirements for practical feasibility of the active analog components.

To attack the complex analytical formulation of such a multivariable problem, a systematic computer-assisted methodology has been developed that efficiently handles the critical design issues yielding optimum tradeoffs between power dissipation and area consumption while minimizing stringent requirements of the con-

Prof, José E, da França

stituting building blocks and significantly reducing the complexity of the calibration circuitry.

The lecture discusses the practical integrated circuit implementation of such converts, starting with the design of efficient analog-based calibration techniques for the critical high linearity low resolution front-end stages and then going through a systematic computer-assisted methodology that efficiently handles design tradeoffs between power dissipation and area consumption while minimizing stringent requirements of the constituting building blocks. Practical design examples are presented to consolidate the relevant conclusions.

### Self-Adjusted Analog-Digital Integrated Circuits

Abstract—Advanced digital CMOS technologies are becoming an increasingly important manufacturing platform for mixed analog-to-digital integrated circuits. Because of its generally acknowledged hostility toward analog circuits, such a technology environment requires that appropriate circuit design techniques are devised to enhance the performance of analog circuits, even when subject to significant accuracy limitations. Among those techniques, digitally self-adjusted circuits are particularly interesting because of their use of inexpensive on-board digital circuitry to assist the operation of analog circuits.

Although several self-adjusted analog circuits have been developed in the past, the underlying basic concepts have been kept quite apart with little or no synergistic interaction between rather different classes of circuit functions (e.g. self-calibrated converters, self-tuned filters, and so forth). In this lecture we attempt to establish a simple framework for self-adjusted analogdigital RAM and the universal calibrator, which can be used in a wide variety of applications, even those as far apart as filtering and conversion.

Examples given of self-adjusted circuits actually built in CMOS integrated circuit form include several types of data converters, a very highfrequency continuous-time filter, a very low power high-frequency comparator, a switched-current delta-sigma modulator and even a quadrature modulator (I&Q) transmit interface for radio communications.

Professor Yih-Fang Huang

Prof. Xih-Fang Huang Department of Electrical Engineering University of Notre Dame Notre Dame, IN 46556 Tel: +1 219-631/5480 Fax: +1 219-631/3493 E-mail: yih-fang,huang,2@pd.edu