## 495-PIN AND 615-PIN MICRO-PGA ZIF SOCKET DESIGN SPECIFICATION

**Application Note**

October 5, 1999

Order Number: 245284-001

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein. Intel does not warrant or represent that such use will not infringe such rights.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Intel disclaims any liability for selection, use, manufacture, sales or distribution, by any user or vendor, of any socket having a design suggested by, or based upon, the information contained in this document. The hardware vendor remains solely responsible for the design, sale and functionality of its product, including any liability arising from product infringement or product warranty, and Intel assumes no liability for vendor products, either alone or in combination with Intel products.

Intel processors may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Such errata are not covered by Intel's warranty. Current characterized errata are available on request.

Intel may make changes to specifications and product descriptions at any time, without notice.

Third-party brands and names are the property of their respective owners.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may obtained by calling 1-800-548-4725, or by visiting Intel's literature center at http://www.intel.com.

Copyright © Intel Corporation 1994-98

## Contents

| 1. | INTRODUCTION                                                                                                 | 5 |

|----|--------------------------------------------------------------------------------------------------------------|---|

|    | 1.1. Purpose                                                                                                 | 5 |

|    | 1.2. SCOPE                                                                                                   |   |

|    |                                                                                                              | - |

| 2. | 2. PACKAGE DESCRIPTION                                                                                       |   |

|    | 2.1. PACKAGE LAYOUT                                                                                          | 5 |

|    | 2.2. PACKAGE DIMENSIONS                                                                                      |   |

|    | 2.3. PACKAGE SEATING                                                                                         |   |

| 3. |                                                                                                              |   |

|    |                                                                                                              |   |

|    | 3.1. SOCKET SIZE                                                                                             |   |

|    | 3.1.1. Contact Array                                                                                         |   |

|    | <ul> <li>3.1.1.1 615-Pin Micro-PGA Contact Array</li> <li>3.1.1.2 495-pin Micro-PGA Contact Array</li> </ul> |   |

|    | 3.1.1.2 495-pin Micro-PGA Contact Array<br>3.1.2. Motherboard Landing Zone                                   |   |

|    | 3.1.2. Momerbourd Landing Zone                                                                               |   |

|    | 3.2. MATERIALS                                                                                               |   |

|    | 3.2.1. Socket Housing                                                                                        |   |

|    | 3.2.2. Color                                                                                                 |   |

|    | 3.2.2. Color                                                                                                 |   |

|    | 3.2.3.1 Orientation Mark                                                                                     |   |

|    | 3.2.3.2 Open/Close Designation                                                                               |   |

|    | 3.2.4. Contact Characteristics                                                                               |   |

|    | 3.2.4.1 Number of Contacts                                                                                   |   |

|    | 3.2.4.2 Base Material                                                                                        |   |

|    | 3.2.4.3 Contact Area Plating                                                                                 |   |

|    | 3.2.4.4 Solder Ball/Surface Mount Feature Characteristics                                                    |   |

|    | 3.2.4.5 Lubricants                                                                                           |   |

|    | 3.2.5. Environmental Concerns Requirements                                                                   |   |

|    | 3.3. VISUAL INSPECTION                                                                                       |   |

|    | 3.3.1. Damaged, Missing, or Misaligned Solder Balls/Leads                                                    |   |

|    | 3.3.2. Bent/Missing Contacts                                                                                 |   |

|    | 3.3.3. Missing Plating                                                                                       |   |

|    | 3.3.4. Cover/Base Alignment                                                                                  |   |

|    | 3.3.5. Damaged Housing                                                                                       |   |

|    | <ul><li>3.3.6. Damaged/Missing Tabs</li><li>3.4. SOCKET/INTERPOSER ACTUATION</li></ul>                       |   |

|    | 3.4. SOCKET/INTERPOSER ACTUATION<br>3.4.1. Actuation Tool                                                    |   |

|    |                                                                                                              |   |

|    | 3.4.2. Locking Mechanism                                                                                     |   |

|    | 3.4.3. Socket/Package Pin Field Movement<br>3.4.4. Package Pin/Motherboard Pad Position                      |   |

|    | 3.5. SOCKET MANUFACTURABILITY REQUIREMENTS                                                                   |   |

|    | 3.5.1. Insertion/Extraction Force                                                                            |   |

|    | 3.5.1. Insertion/Extraction Force                                                                            |   |

|    | 3.5.2. Socket Engagement/Disengagement Force                                                                 |   |

|    | 3.5.2.1 Level                                                                                                |   |

|    | 3.5.3. Socket Retention Force                                                                                |   |

|    | 3.5.4. Durability                                                                                            |   |

|    | 3.5.5. Motherboard Attachment                                                                                |   |

|    | 3.5.5.1 Coplanarity and True Position                                                                        |   |

|    | 3.5.5.2 Flatness                                                                                             |   |

|    | 3.5.5.3 Pick & Place                                                                                         |   |

|    | 3.5.5.4 Reflow                                                                                               |   |

|    | 3.6. CRITICAL TO FUNCTION (CTF) PARAMETERS                                                                   |   |

| 4.1. ELECTRICAL PERFORMANCE SPECIFICATIONS |    |

|--------------------------------------------|----|

| 4.2. ELECTRICAL QUALIFICATION REQUIREMENTS |    |

| 4.2.1. Inductance (self and mutual)        |    |

| 4.2.1.1 Solving for unknowns               |    |

| 4.2.2. Capacitance                         |    |

| 4.2.3. Contact Resistance                  |    |

| 4.2.3.1 Initial Contact Resistance:        |    |

| 4.2.3.2 Final Contact Resistance:          |    |

| 4.2.4. Test Voltage and Current Rating     |    |

| 4.2.5. Dielectric Withstand Voltage        |    |

| 4.2.6. Pin-to-Pin Insulation Resistance    |    |

| 5. RELIABILITY TARGETS                     | 20 |

## 1. INTRODUCTION

This document defines the SMT ZIF (Zero Insertion Force) socket that will support the 615-pin Micro-PGA and 495-pin Micro-PGA mobile processor packages. The 615-pin Micro-PGA and 495-pin Micro-PGA sockets must be low cost, low risk, robust, reliable, manufacturable in high volumes, and multi-sourceable. The 615-pin Micro-PGA mobile socket has 615 contacts with a pitch of 1.27 mm that mates with a 615-pin Micro-PGA package. The 495-pin Micro-PGA mobile socket has 495 contacts with a 1.27 mm pitch that mates with the 495-pin Micro-PGA package.

## 1.1. Purpose

To define the mechanical, electrical, quality, and reliability requirements necessary to meet the product requirements of the 615-pin Micro-PGA and 495-pin Micro-PGA mobile processor package ZIF sockets.

## 1.2. Scope

This specification applies to all ZIF sockets designed for use with the Intel mobile processor 495-pin and 615-pin Micro-PGA packages.

## 2. PACKAGE DESCRIPTION

Information provided in this section is to ensure dimensional compatibility of the 615-pin Micro-PGA and 495-pin Micro-PGA sockets with the corresponding packages. The 615-pin Micro-PGA and 495-pin Micro-PGA packages must be insertable into the sockets with zero insertion force when the socket is not actuated.

## 2.1. Package Layout

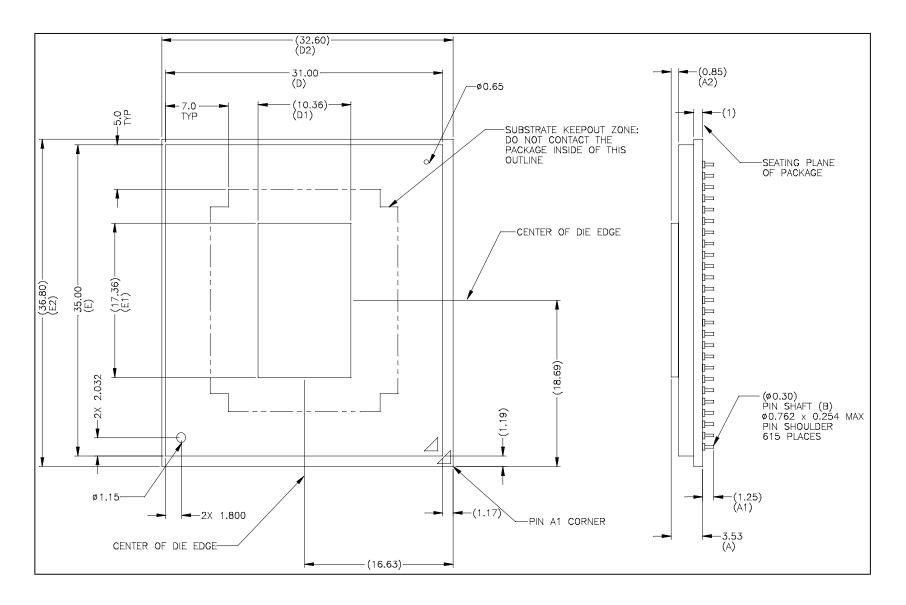

The outline of the packages that can be used with the 615-pin Micro-PGA and 495-pin Micro-PGA sockets are illustrated in **Figures 1 and 2**.

Figure 1a: 615-pin Micro-PGA package top and side view (see Figure 1b for package dimension).

| Symbol                                                                  | Parameter                                                                          | Min        | Max        | Unit    |  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------|------------|---------|--|

| А                                                                       | Overall height, top of die to seating plane of interposer                          |            | 3.83       | mm      |  |

| -                                                                       | Overall height, top of die to PCB surface, including socket(1)                     | 5.40       | 6.00       | mm      |  |

| A1                                                                      | Pin length                                                                         | 1.         | 25         | mm      |  |

| A2                                                                      | Die height                                                                         | 0.8        | 354        | mm      |  |

| В                                                                       | Pin diameter                                                                       | 0          | .3         | mm      |  |

| D                                                                       | Die substrate width                                                                | 30.85      | 31.15      | mm      |  |

| D1                                                                      | Die width                                                                          | 10         | .36        | mm      |  |

| D2                                                                      | Package interposer width                                                           | 32         | .60        | mm      |  |

| E                                                                       | Die substrate length                                                               | 34.85      | 35.15      | mm      |  |

| E1                                                                      | Die length 17.36 mm                                                                |            | mm         |         |  |

| E2 Package interposer length                                            |                                                                                    | 36         | .80        | mm      |  |

| е                                                                       | Pin pitch                                                                          | 1.27       |            | mm      |  |

| -                                                                       | Pin tip radial true position                                                       | <=0.127 mn |            | mm      |  |

| Ν                                                                       | N Pin count 615                                                                    |            | 15         | each    |  |

| S1                                                                      | S1 Pin row A to short edge of interposer 2.22                                      |            | 220        | mm      |  |

| S2                                                                      | Pin column 1 to long edge of interposer 1.415                                      |            | mm         |         |  |

| Pdie                                                                    | Allowable pressure on the die for thermal solution                                 | -          | 689        | kPa     |  |

| W                                                                       | Package weight 7.5 g                                                               |            |            | g       |  |

| Notes: All dimensions are PRELIMINARY and subject to change at an time. |                                                                                    |            |            |         |  |

| (1) Overall height with socket is based on measurements from the PC     |                                                                                    |            | surface to | the top |  |

|                                                                         | of the exposed die of uPGA packages in sockets with no thermal solution attached.  |            |            |         |  |

|                                                                         | Measurements were taken from pre-production units. This dimension may change based |            |            |         |  |

|                                                                         | on socket design, OEM motherboard design, or OEM SMT pro                           | cess.      |            |         |  |

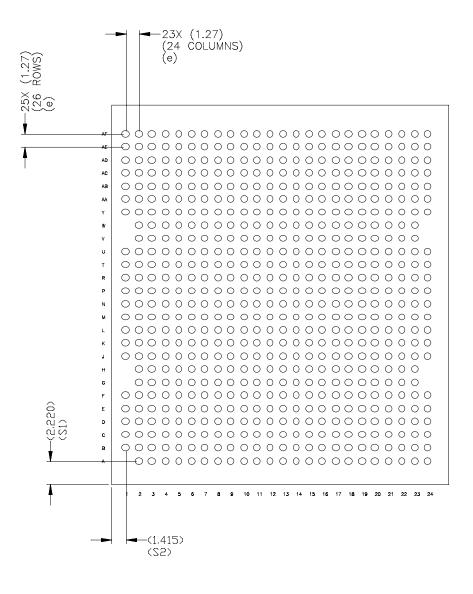

Figure 1b: 615-pin Micro-PGA package pin layout and key package dimensions.

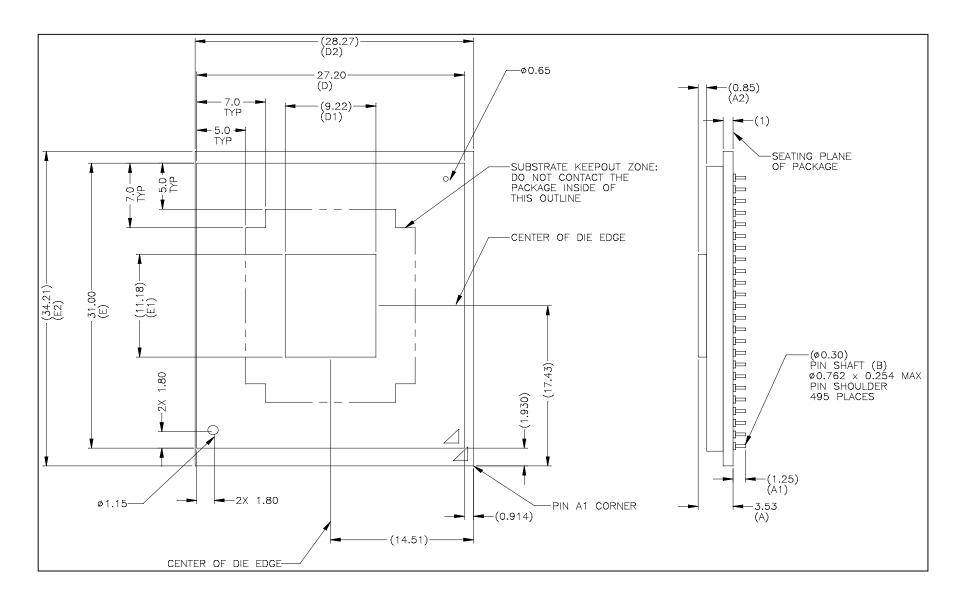

Figure 2a: 495-pin Micro-PGA package top and side view (see Figure 2b for package dimension).

| Symbol                                                                  | Parameter                                                                               | Min        | Max   | Unit |  |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------|-------|------|--|

| А                                                                       | Overall height, top of die to seating plane of interposer                               |            | 3.83  | m m  |  |

| -                                                                       | - Overall height, top of die to PCB surface, including sock et(1)                       |            | 6.00  | m m  |  |

| A1                                                                      | P in length                                                                             | 1.         | 25    | m m  |  |

| A2                                                                      | Die height                                                                              | 0.8        | 354   | m m  |  |

| В                                                                       | Pin diameter                                                                            | 0          | .3    | m m  |  |

| D                                                                       | Die substrate width                                                                     | 27.05      | 27.35 | m m  |  |

| D1                                                                      | D ie w id th                                                                            | 9.         | 22    | m m  |  |

| D2                                                                      | Package interposer width                                                                | 28         | . 27  | m m  |  |

| E                                                                       | Die substrate length                                                                    | 30.85      | 31.15 | m m  |  |

| E1                                                                      | Die length                                                                              | 11.18 m m  |       | m m  |  |

| E2                                                                      | Package interposer length                                                               | 34.21      |       | m m  |  |

| е                                                                       | P in pitch                                                                              | 1.27       |       | m m  |  |

| -                                                                       | Pin tip radial true position                                                            | <=0.127 n  |       | m m  |  |

| Ν                                                                       | Pin count                                                                               | 495 each   |       |      |  |

| S1                                                                      | Pin row A to short edge of interposer                                                   | 2.144 m m  |       |      |  |

| S2                                                                      | Pin colum n 1 to long edge of interposer                                                | 1.206 m.m. |       |      |  |

| Pdie                                                                    | die Allowable pressure on the die for thermal solution                                  |            | 689   | kРа  |  |

| W                                                                       | Package weight                                                                          | 6.2 g      |       | g    |  |

| Notes: All dimensions are PRELIMINARY and subject to change at an time. |                                                                                         |            |       |      |  |

|                                                                         | (1) Overall height with socket is based on measurements from the PCB surface to the top |            |       |      |  |

|                                                                         | of the exposed die of uPGA packages in sockets with no thermal solution attached.       |            |       |      |  |

|                                                                         | Measurements were taken from pre-production units. This dimension may change based      |            |       |      |  |

|                                                                         | on socket design, OEM motherboard design, or OEM SMT process.                           |            |       |      |  |

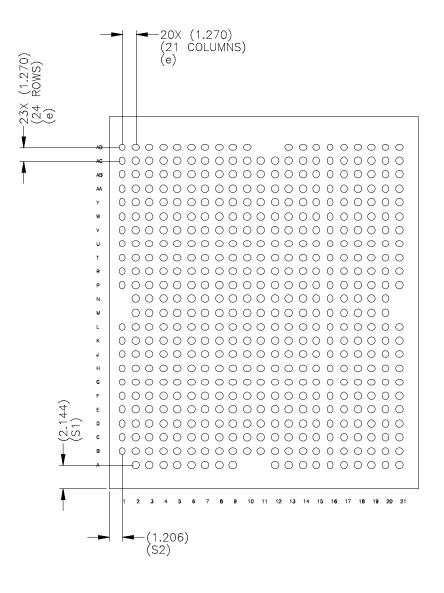

Figure 2b: 495-pin Micro-PGA package pin layout and key package dimensions.

## 2.2. Package Dimensions

| Parameter                                               | 615-pin Micro-PGA<br>(Max Values)  | 495-pin Micro-PGA<br>(Max Values)  | Comment                                                         |

|---------------------------------------------------------|------------------------------------|------------------------------------|-----------------------------------------------------------------|

| Pins                                                    |                                    |                                    |                                                                 |

| Pin Pitch                                               | 1.27 mm                            | 1.27 mm                            | Nominal value                                                   |

| Pin Tip True Position                                   | 0.254 mm                           | 0.254 mm                           | Max diametrical value pin to pin                                |

| Pin Diameter                                            | 0.305 + 0.0508 mm /<br>- 0.0254 mm | 0.305 + 0.0508 mm /<br>- 0.0254 mm |                                                                 |

| Pin Length                                              | 1.25 +/- 0.0508 mm                 | 1.25 +/- 0.0508 mm                 |                                                                 |

| Pin Shoulder/Solder<br>Fillet Diameter                  | 0.762 mm                           | 0.762 mm                           | Max value                                                       |

| Pin Shoulder/Solder<br>Fillet Height                    | 0.254 mm                           | 0.254 mm                           | Max value                                                       |

| 1 <sup>st</sup> Row to Edge See Figure 1b.<br>Distances |                                    | See Figure 2b.                     | Package must be<br>able to sit flush<br>against socket<br>cover |

| Substrate                                               |                                    |                                    |                                                                 |

| Thickness                                               | 1.0 +/- 0.15 mm                    | 1.0 +/- 0.15 mm                    |                                                                 |

| Width                                                   | 36.75 +/- 0.15 mm                  | 34.22 +/- 0.15 mm                  | Offset pin field                                                |

| Length                                                  | 32.56 +/- 0.15 mm                  | 28.27 +/- 0.15 mm                  | Offset pin field                                                |

| Flatness                                                | 0.7% mm/mm                         | 0.7% mm/mm                         |                                                                 |

## Table 1

## 2.3. Package Seating

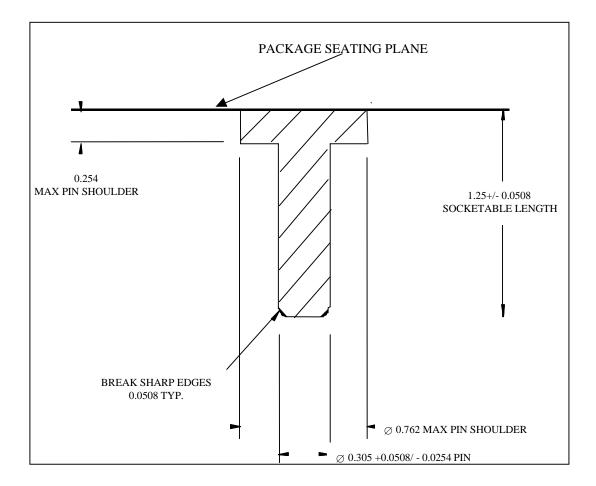

The package's pin shoulder and/or solder fillet should be able to completely fit inside the socket so that there is no gap between the package and the socket cover plate. See **Figure 3** for pin shoulder dimensions.

Figure 3: Pin shoulder drawing for 615-pin Micro-PGA and 495-pin Micro-PGA packages.

## 3. MECHANICAL REQUIREMENTS

- 3.1. Socket Size

- 3.1.1. Contact Array

#### 3.1.1.1 615-Pin Micro-PGA Contact Array

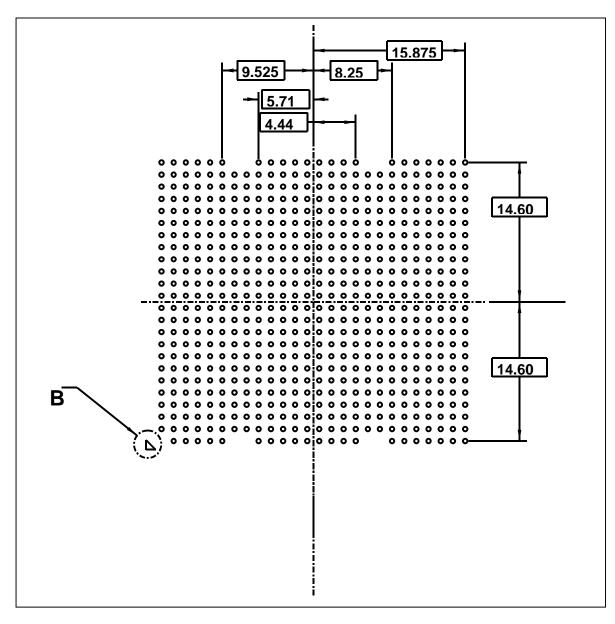

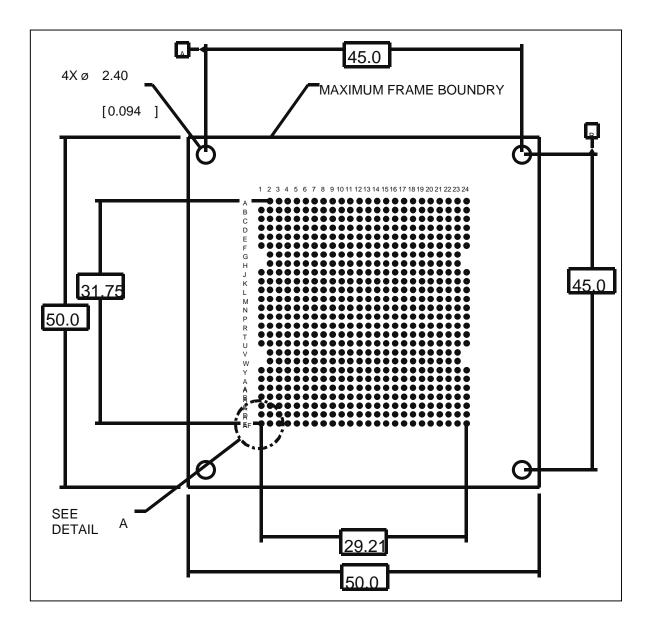

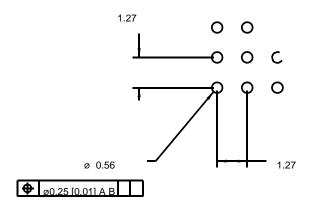

The 615 contacts are to be located in a 24 by 26 contact array. The centerline to centerline distance of the contacts, or pitch, is to be 1.27 mm. The overall dimensions of the contact array is 29.21 mm by 31.75 mm. See **Figure 4** for exact shape of contact array as viewed looking down at the mother board attach pads.

#### Figure 4: 615-pin Micro-PGA contact array

#### 3.1.1.2 495-pin Micro-PGA Contact Array

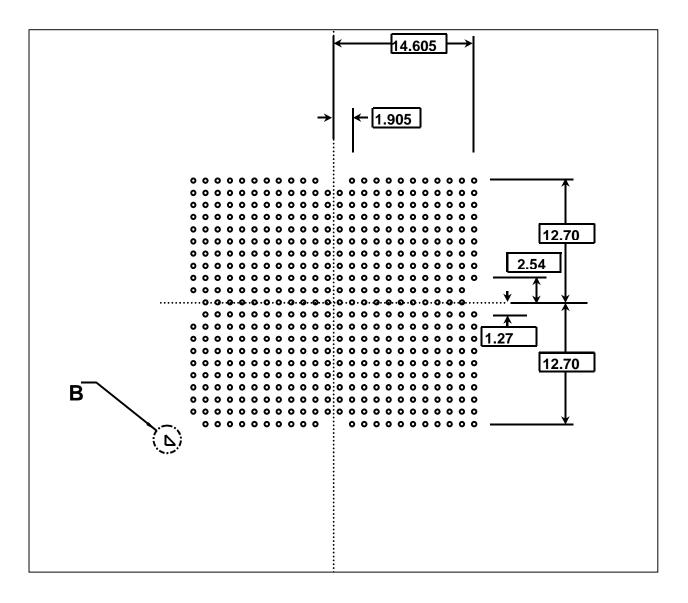

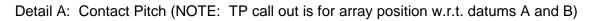

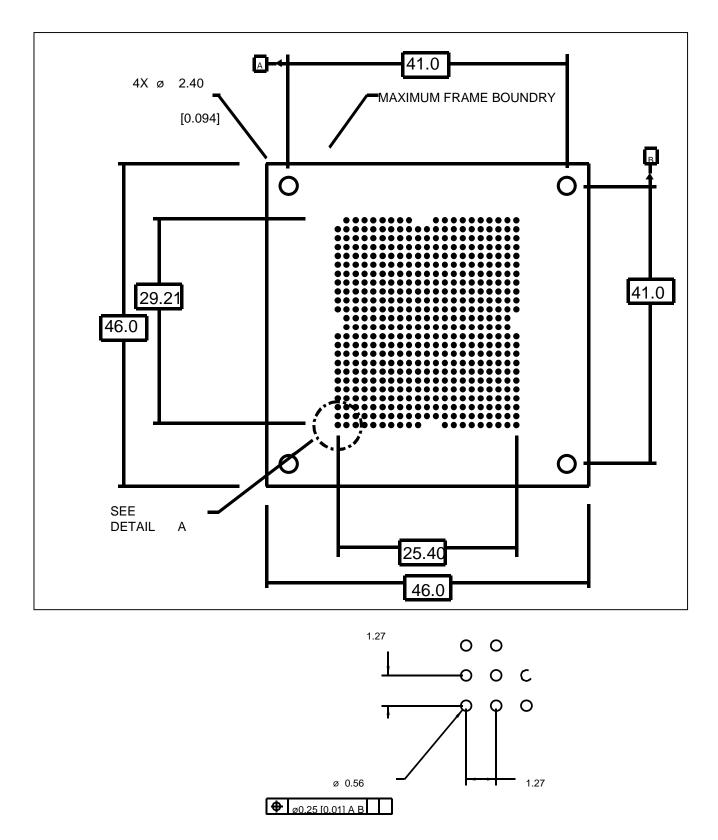

The 495 contacts are to be located in a 21 by 24 contact array. The centerline to centerline distance of the contacts, or pitch, is to be 1.27 mm. The overall dimensions of the contact array is 25.40 mm by 29.21 mm. See **Figure 5** for exact shape of contact array as viewed looking down at the mother board attach pads.

Figure 5: 495-pin Micro-PGA contact array

## 3.1.2. Motherboard Landing Zone

Use of the Intel thermal reference design requires the entire socket and frame to fit inside a specified landing zone that has four equally spaced threaded holes used to attach the thermal frame. The recommended landing zone for the 615-pin Micro-PGA package is 50 mm by 50 mm (hole spacing 45 mm by 45 mm) and 46 mm by 46 mm (hole spacing 41 mm by 41 mm) for the 495-pin Micro-PGA package. The solder ball array (bottom side of socket) is to be centered between the four frame holes for both the 615-pin Micro-PGA and 495-pin Micro-PGA. See **Figures 6 and 7** for location of the contact arrays with respect to the landing zone boundaries and thermal reference holes.

NOTE: The above landing zone sizes are minimum requirements that may vary depending on the thermal solutions used by OEMs.

Figure 6: 615-pin Micro-PGA landing zone

Figure 7: 495-pin Micro-PGA landing zone

## 3.1.3. Weight

The socket is not to exceed 14 grams for either the 615-pin Micro-PGA or 495-pin Micro-PGA packages.

#### 3.2. Materials

## 3.2.1. Socket Housing

Material with a UL 94V-0 flame rating that is capable of withstanding a SMT reflow process.

#### 3.2.2. Color

The Micro-PGA sockets will be off-white or brown in color.

#### 3.2.3. Visual Markings

The following marks can either be molded, laser marked, or ink marked on the cover of the socket. The mark must be able to withstand two reflows at temperatures of 240  $^{\circ}$ C for 30 seconds per cycles.

## 3.2.3.1 Orientation Mark

A triangular shape, on the pin 1 corner, must be located on the socket frame so that it is still visible when the interposer/OLGA is socketed to ensure proper orientation. In addition to the orientation mark, there will not be an eyehole or contact at pin 1. The purpose of this is to increase the insertion force needed to socket a misoriented interposer.

## 3.2.3.2 Open/Close Designation

Clear indicator marks must be located on the socket that identify the open and closed positions of the cover. These marks should still be visible after an interposer is inserted into the socket.

## 3.2.4. Contact Characteristics

#### 3.2.4.1 Number of Contacts

Total number of contacts: 615 for the 615-pin Micro-PGA socket and 495 for the 495-pin Micro-PGA socket.

## 3.2.4.2 Base Material

High strength copper alloy.

#### 3.2.4.3 Contact Area Plating

$0.254~\mu m$  minimum gold plating over 1.27  $\mu m$  minimum nickel underplate.

## 3.2.4.4 Solder Ball/Surface Mount Feature Characteristics

NOTE: Solder balls or other surface mount features may be used to attach the socket to the motherboard.

Solder Balls: Tin/Lead (63/37  $\pm$  0.5% Sn) with a 0.762 mm (0.030 in) diameter.

Surface Mount Feature: Surface mount feature must extend at least 0.175 mm from the bottom of the base housing to prevent solder paste from contacting the housing

#### 3.2.4.5 Lubricants

No lubricants are to be used on the socket contacts.

#### 3.2.5. Environmental Concerns Requirements

Cadmium shall not be used in the painting or plating of the socket. CFCs and HFCs shall not be used in manufacturing the socket.

#### 3.3. Visual Inspection

Visual inspection is to be performed at 1x except for lead inspection.

NOTE: The visual inspection requirements listed below contain defects that affect the functionality of the ZIF socket. Cosmetic defects will not be covered in this specification.

#### 3.3.1. Damaged, Missing, or Misaligned Solder Balls/Leads

**Requirement:** No damaged, malformed, missing or misaligned solder balls or leads used in attaching the socket to the motherboard. Lead inspection is to be inspected at 5-10 x magnification.

Note that dimensional measurements of solder ball or lead true position (Section 3.5.5. Motherboard Attachment) is the primary means of determining solder ball or lead alignment.

#### 3.3.2. Bent/Missing Contacts

**Requirement:** No contacts are to be missing or damaged in any way that will prevent proper functionality of the socket.

#### 3.3.3. Missing Plating

**Requirement:** No missing Au plating on the mating surface of the contact.

#### 3.3.4. Cover/Base Alignment

**Requirement:** No contacts are to be visible through the cover hole when the cover is located in the "open" position.

## 3.3.5. Damaged Housing

**Requirement:** No cracks are to be present on the socket housing that are visible at 1x.

## 3.3.6. Damaged/Missing Tabs

**Requirement:** The tabs/guides that connect the cover to the base are not to be missing or damaged. There should not be a visible gap between the cover and base.

#### 3.4. Socket/Interposer Actuation

#### 3.4.1. Actuation Tool

The socket should be designed so that it can be easily actuated in a high volume manufacturing environment. The preferred actuation tools are regular, Phillips, or hex screwdrivers. A design that requires the use of a custom tool is not recommended, however, a special actuation tool may be used if it is approved by OEMs.

#### 3.4.2. Locking Mechanism

The socket must have a locking mechanism that holds the cover in the open position to assure a zero package insertion force at the OEMs.

#### 3.4.3. Socket/Package Pin Field Movement

The socket will be designed so that the package pin field displacement will not exceed 1 mm during actuation and deactuation.

#### 3.4.4. Package Pin/Motherboard Pad Position

The true position of the package pin in the engaged position must be within 1 mm of the of the true position of the motherboard pads.

#### 3.5. Socket Manufacturability Requirements

#### 3.5.1. Insertion/Extraction Force

The insertion and extraction forces should both be zero when the socket is not engaged (in the "open" position).

#### 3.5.2. Socket Engagement/Disengagement Force

#### 3.5.2.1 Lever

Less than 44.48 N (10 lbf.) to move the screwdriver (or lever) in order to engage the socket.

## 3.5.2.2 Torque

Less than 0.92 N-m (8.16 lbf-in) of torque must be applied to engage the socket.

NOTE: This limit is based on using a screwdriver with a handle diameter of less than 1 in and holding it with the palm of the hand.

## 3.5.3. Socket Retention Force

A minimum pin retention force of 10 gm/pin must be met in order to secure the package to the socket during the manufacturing process. Retention force is defined as the force required to pull the pins out of the contacts when the socket is engaged.

#### 3.5.4. Durability

The socket must maintain mechanical and electrical characteristics after 20 insertion/extraction cycles.

## 3.5.5. Motherboard Attachment

The socket must be able to be surface mounted to motherboard pads ranging in diameter from 0.559 to 0.660 mm (0.022 to 0.026 in) with pad to pad true positions of 0.025 mm (0.001 in).

## 3.5.5.1 Coplanarity and True Position

The coplanarity and true position requirements will differ depending on the method used to mount the socket to the motherboard (solder balls vs. leads). For solder balls, the coplanarity requirement is 0.203 mm (0.008 in) and the ball true position is 0.102 mm (0.004 in). For leads, the coplanarity requirement is 0.152 mm (0.006 in) and the lead true position is 0.076 mm (0.003 in).

#### 3.5.5.2 Flatness

The flatness of the assembled socket is not to exceed 0.7%.

## 3.5.5.3 Pick & Place

Tape or a plastic cover must be present on the top of the socket to allow it to be placed by a vacuum nozzle. The tape must not outgas during reflow or leave behind any residue.

## 3.5.5.4 Reflow

Max temperature: 240°C

Figure 8: Typical Reflow Profile for 63Sn/37Pb solder

## 3.6. Critical to Function (CTF) Parameters

Critical to function dimensions are identified in **Table 2**. Also, the supplier will both provide and maintain Critical Process Parameters controlling these CTFs and provide direct measurements to meet ongoing quality requirements.

| Parameter                              | 615-Pin Micro-<br>PGA Socket                                      | 495-Pin Micro-<br>PGA Socket                                      | Comment                                                                                                        |

|----------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Outer Length                           | 40 mm Max                                                         | 36 mm Max                                                         | May exceed as long as it fits<br>inside landing zone and does<br>not interfere with thermal<br>reference holes |

| Outer Width                            | 40 mm Max                                                         | 36 mm Max                                                         | May exceed as long as it fits<br>inside landing zone and does<br>not interfere with thermal<br>reference holes |

| Mounted Z-Height                       | 2.2 mm Target                                                     | 2.2 mm Target                                                     | Motherboard to package seating plane of socket                                                                 |

|                                        | (Height necessary to<br>achieve 6.0 mm max<br>total stack height) | (Height necessary to<br>achieve 6.0 mm max<br>total stack height) | (Total stack height defined as<br>distance from motherboard to<br>top of die)                                  |

| Assembled<br>Cover/Base Flatness       | 0.7%                                                              | 0.7%                                                              | Value determined by length or<br>width of socket seating area<br>(whichever is larger)                         |

| Coplanarity<br>– Lead<br>– Solder Ball | 0.152 mm (0.006 in)<br>0.203 mm (0.008 in)                        | 0.152 mm (0.006 in)<br>0.203 mm (0.008 in)                        |                                                                                                                |

| Cover Hole<br>Diameter                 | 0.40 mm Min<br>0.50 mm Max                                        | 0.40 mm Min<br>0.50 mm Max                                        | Min size of hole for ZIF condition                                                                             |

| Cover Hole True<br>Position            | 0.10 mm                                                           | 0.10 mm                                                           | Max TP for ZIF condition                                                                                       |

| Cover Thickness                        | 0.75 mm                                                           | 0.75 mm                                                           | Max allowable based on pin length                                                                              |

| Contact Loop<br>(Inserted Position)    | Design specific                                                   | Design specific                                                   | Must not be visible through cover hole in open position                                                        |

| Contact Gap<br>(Actuated Position)     | Design specific                                                   | Design specific                                                   | Must achieve normal force requirements                                                                         |

| Contact True<br>Position               | 0.10 mm                                                           | 0.10 mm                                                           | Max - contact must not be<br>visible through cover hole,<br>must not affect pin actuation                      |

| Solder Ball/Lead<br>True Position      | 0.076 mm (0.003 in)                                               | 0.076 mm (0.003 in)                                               |                                                                                                                |

| Au Thickness                           | 0.254 <sub>µ</sub> m                                              | 0.254 <sub>μ</sub> m                                              | Min plating thickness                                                                                          |

| Ni Thickness                           | 1.27 <sub>µ</sub> m                                               | 1.27 <sub>µ</sub> m                                               | Min plating thickness                                                                                          |

| Actuation Distance                     | 1.0 mm                                                            | 1.0 mm                                                            | Minimum determined by contact design                                                                           |

## **Table 2 Critical to Function Parameters**

## 4. ELECTRICAL REQUIREMENTS

## 4.1. Electrical Performance Specifications

The contact design of the 615-pin Micro-PGA and 495-pin Micro-PGA sockets must be capable of meeting the following performance characteristics when mated with a Kovar pin.

Specifications are from the top of the socket to the top of test board to which it is attached.

All specifications are MAX (unless otherwise stated) for a single socket pin, but includes effects of adjacent pins where indicated.

Signal-to- $V_{SS}$  pin ratio is 2:1 and signal-to-combined  $V_{ss}/V_{cc}$  pin ratio 1:1.

Pin and socket inductance includes exposed pin from mated contact to bottom of the package.

|                                                                     |                                                                                                                                           |                  | 1                                                                                                                                                            |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     | Definition                                                                                                                                | Specification    | Measurement                                                                                                                                                  |

| Mated self<br>inductance of a<br>single pin                         | The inductance of a single<br>pin of mated package and<br>socket with no mutual<br>inductance from any other<br>conductor.                | 2nH              | Can not be measured<br>directly.<br>Calculated by: (0.5*Loop<br>inductance – mutual<br>inductance) of two nearest<br>pins.                                   |

| Mated loop<br>inductance of<br>two nearest<br>pins                  | The inductance of two<br>nearest pins of mated<br>socket and package<br>considering one forward<br>conductor and one return<br>conductor. | Maximum:<br>3nH  | Measured from the top pads<br>of the package for two<br>nearest pins (one as signal,<br>one as ground) shorted at<br>the bottom of the socket.               |

| Mated mutual<br>capacitance of<br>two nearest<br>pins               | The capacitance between<br>two nearest pins of mated<br>socket and package.                                                               | Maximum:<br>1pF  | Measured from the top pads<br>of the package for two<br>nearest pins (one as signal,<br>one as ground) but not<br>connected at the bottom of<br>the socket.  |

| Initial contact<br>resistance<br>(average of<br>minimum 40<br>pins) | The DC resistance of a single pin of mated package and socket.                                                                            | Maximum:<br>30mΩ | Measured for one pin from<br>the top pad of the package<br>to the bottom of the socket.<br>This is the initial resistance<br>before any reliability testing. |

| Final contact<br>resistance<br>(average of<br>minimum 40<br>pins)   | The DC resistance of a single pin of mated package and socket.                                                                            | Maximum:<br>30mΩ | Measured for one pin from<br>the top pad of the package<br>to the bottom of the socket.<br>This is the final resistance<br>after any reliability testing.    |

Table 3 Electrical requirements for Micro-PGA SOCKET

| Measurement<br>frequency for<br>capacitance.                | Frequency at which the S-<br>parameter measurement<br>performed. | 500MHz                                                                  |                 |

|-------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------|

| Measurement<br>frequency for<br>inductance.                 | Frequency at which the S-<br>parameter measurement<br>performed. | 500MHz                                                                  |                 |

| Socket<br>minimum<br>current rating<br>and test<br>voltages |                                                                  | 1.0 A/pin @ ≤<br>2 V and <<br>20°C temp<br>rise due to<br>Joule heating | Refer to 4.2.4. |

| Dielectric<br>withstand<br>voltage (min)                    |                                                                  | 1000 Vac                                                                | Refer to 4.2.5. |

| Pin-to-Pin<br>Insulation<br>Resistance<br>(min)             |                                                                  | 1000MΩ                                                                  | Refer to 4.2.6. |

## 4.2. Electrical Qualification Requirements

## 4.2.1. Inductance (self and mutual)

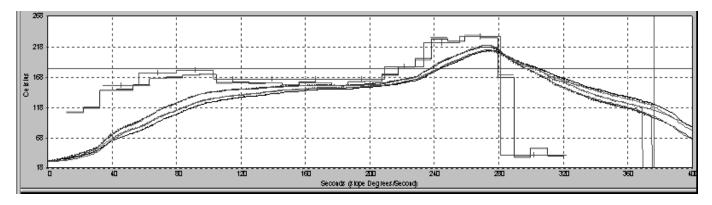

The mated self-inductance of a socket is the measured partial selfinductance of a socket pin. The components that are included in this computation are shown in **Figure 9**. These include the CPU pins after the CPU package, the socket and the socket pins before the MB connection. The definition of self-inductance does not include any mutual inductances, only the partial self-inductance of the pin with respect to infinity.

## Figure 9: Socket mated self-inductance

The mated mutual inductance of the socket is defined as the inductive coupling between pins.

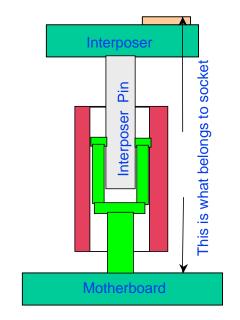

Figure 10: Cross-sectional view of the top and bottom L fixtures

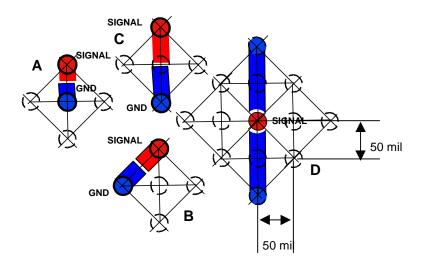

A set of probe pad patterns is designed on the Top L fixture to measure the specified parameters. This is shown in **Figure 11**.

#### Figure 11: Top L Fixture probing pad design (50 mil grid pattern)

As can be observed in **Figure 11**, there are 4 distinct structures for characterization, corresponding to the 4 parasitics that need to be extracted:

#### 50 mil grid array socket

- Pin Self Inductance (L<sub>s</sub>)

- Pin Mutual Inductance (50 mils) ( $M_{50}$  average of two directions)

- Pin Mutual Inductance (70.71 mils)  $(M_{70}$  average of two directions)

- Pin Mutual Inductance (100 mils)  $(M_{100}$  average of two directions)

The parasitics of the fixture are calibrated out by shorting the Top L fixture with the Bottom L fixture. The gap between the top and bottom fixtures should be as small as possible (ideal is no gap), and the maximum allowable gap on any sides is 10 mils. The pintail of the package pins should be trimmed off.

To calibrate out the fixture for surface mount sockets, the pins of the top fixture will need to be cut and shaved, and then mounted just as the socket would be mounted.

#### 4.2.1.1 Solving for unknowns

To obtain the 4 unknowns, 4 sets of measurements are made after obtaining the fixture parasitic. Denoting the structure as A,

B, C and D while giving the suffix for the fixture of each measurement as  $L_{fA}$ ,  $L_{fB}$ ,  $L_{fC}$ , and  $L_{fD}$ , the values of each parameters are solved using the 4 equations below:

| 50 mil grid                                                           |

|-----------------------------------------------------------------------|

| $2(Ls - M_{50}) = L_A, M_{50} = L_s - L_A/2$                          |

| $2(L_s - M_{70}) = L_B, M_{70} = Ls - L_B/2$                          |

| $2(L_s - M_{100}) = L_C, M_{100} = L_S - L_C/2$                       |

| $1.5L_{\rm S} - 2M_{100} + 0.5M_{200} = L_{\rm D}$                    |

| $1.5L_{s} - 2(L_{s} - L_{c}/2) = L_{D} (M_{280} \text{ assumed} = 0)$ |

| $L_{\rm S} = 2(L_{\rm C} - L_{\rm D})$                                |

| $L_{\text{LOOP}} = 2^* (L_{\text{S}} - M_{50})$                       |

## 4.2.2. Capacitance

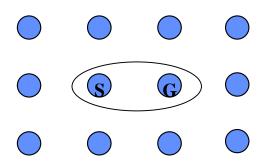

Pin-to-pin capacitance shall be measured as per EIA 364, Test procedure 30. Pin-to-pin contact capacitance shall be measured between adjacent signal pins (signal to signal) The signal to signal measurements and the signal to ground measurements will be done with a signal to ground ratio of 1:1 where the ground pin has 50 mil pitch to signal pin. Five (5) measurements each shall be made between random lateral, diagonal and vertical adjacent pins for a total of fifteen (15) measurements. This measurement is in the unmounted condition and includes the contact and solder balls.

Figure 12: Pin layout for capacitance meaurements

NOTE: Pin-to-pin capacitance is for the socket only, and is for signal pins coupled to other adjacent signal or  $V_{cc}/V_{ss}$  pins.

## 4.2.3. Contact Resistance

This is to make sure that the contact resistance (bulk resistance of contact, solder ball, and package pin + interface resistance) has not degraded during environmental testing. The measured value includes the mounted socket plus engaged package pin, and can be measured on any low voltage, current controlled tester.

Measure total contact resistance  $R_i$  for each of the 20 contact pairs (40 total contacts). To determine average contact resistance, sum up  $R_i$  for all contact pairs and divide by the number of contacts. That is, for Micro-PGA,

$R_{ave} = \sum R_i / (2^* \# \text{ of contact pairs})$

#### 4.2.3.1 Initial Contact Resistance:

Measured immediately after the first mating and actuation of the package and socket. The three performance requirements for initial contact resistance are:

- a) Initial total contact resistance average of 40 contacts is not to exceed  $30m\Omega$ .

- b) No pin can exceed the initial contact resistance of  $500m\Omega$ .

- c) 2 or more contacts per socket cannot exceed the initial contact resistance of  $35m\Omega$ .

## 4.2.3.2 Final Contact Resistance:

Measured after the environmental tests developed that are based on the expected field use environment for mobile products found in **Table 5**.

The requirement for the measured contact pairs is that the final average total contact resistance is not to exceed  $30m\Omega$  per contact.

## 4.2.4. Test Voltage and Current Rating

Test to be performed at 1.0 A/contact. Voltage can vary to a maximum of 2.0V during test to attain 1.0A. Less than 20°C rise in temperature due to Joule heating.

Once the current rating of 1.0 amp IDC is established, monitor the contact temperature for 5 minutes. Measure the temperature rise after stabilization has occurred. Contact current rating shall be measured for five contacts per socket. Testing shall be measured as per EIA 364, test procedure 70, method 13.

## 4.2.5. Dielectric Withstand Voltage

A minimum requirement of 1000 Vac as measured per EIA 364, Test Procedure 20.

Pin dielectric withstand voltage shall be measured between adjacent random lateral, diagonal and vertical adjacent pins.

Five (5) measurements shall be made for each of the above three options for a total of fifteen (15) measurements.

NOTE: This measurement is on socket only in unmated condition (no substrate mated).

## 4.2.6. Pin-to-Pin Insulation Resistance

A minimum requirement of  $1000M\Omega$ , as measured per EIA 364, Test Procedure 21.

Pin-to-pin insulation resistance shall be measured between adjacent random lateral, diagonal and vertical pins.

Five (5) measurements shall be made for each of the above three options to a total of fifteen (15) measurements.

## NOTE: This measurement is on socket only in unmated condition (no substrate mated).

#### 5. RELIABILITY TARGETS

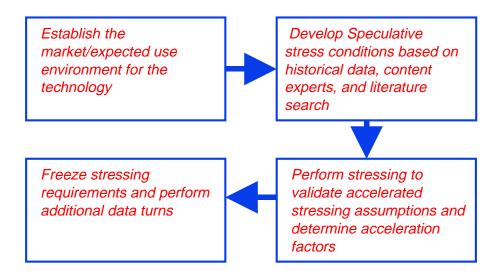

The reliability targets in this section are based on the expected field use environment for a mobile product. The test sequence for new sockets will be developed using the knowledge-based reliability evaluation methodology, which is acceleration factor dependent. A simplified process flow of this methodology can be seen in **Figure 13**. A more detailed description of this methodology can be found at: <a href="http://developer.intel.com/design/packtech">http://developer.intel.com/design/packtech</a>. The use environment expectations assumed for mobile processors, based on an expected life of 7 to 10 years, are listed in **Table 5**. The suggested target for the expected fail rates are 1% at 7 years and 3% at 10 years.

#### Table 5 Expected Field Use Environment

| Use Environment Expectations              | 7 Year Life Expectation                          |

|-------------------------------------------|--------------------------------------------------|

| Slow small internal gradient changes due  | 3000 cycles with a mean $\Delta T = 40^{\circ}C$ |

| to external ambient (temperature cycle or |                                                  |

| externally heated)-Temperature Cycle      |                                                  |

| High ambient moisture during low-power    | 62K hours at 30 <sup>0</sup> C/85%RH             |

| state (operating voltage)- THB/HAST       |                                                  |

| High Operating temperature and short      | 62K hours at Max operating temperature           |

| duration high temperature exposures -     |                                                  |

| Bake                                      |                                                  |

| Fast, large gradient On/off (to max       | 7500 cycles                                      |

| operating temperature) (power cycle or    |                                                  |

| internally heated including power save    |                                                  |

| features)- Power Cycle                    |                                                  |

| Mechanical Shock                          | Trapezoidal 50g. Velocity change 170             |

|                                           | in./sec 3 drops in each of 6 directions          |

| Mechanical Vibration                      | 5 Hz - 20 Hz .01 g2/Hz sloping up to .02         |

|                                           | g2/Hz 20 Hz - 500 Hz .02 g2/Hz 3.13              |

|                                           | gRMS, random10 minutes/axis                      |

| Operating Temperature                     | 0 °C to 105 °C                                   |

|                                           |                                                  |

|                                           |                                                  |

# intel

UNITED STATES, Intel Corporation 2200 Mission College Blvd., P.O. Box 58119, Santa Clara, CA 95052-8119 Tel: +1 408 765-8080

> JAPAN, Intel Japan K.K. 5-6 Tokodai, Tsukuba-shi, Ibaraki-ken 300-26 Tel: + 81-29847-8522

> > FRANCE, Intel Corporation S.A.R.L. 1, Quai de Grenelle, 75015 Paris Tel: +33 1-45717171

UNITED KINGDOM, Intel Corporation (U.K.) Ltd. Pipers Way, Swindon, Wiltshire, England SN3 1RJ Tel: +44 1-793-641440

> GERMANY, Intel GmbH Dornacher Strasse 1 85622 Feldkirchen/ Muenchen Tel: +49 89/99143-0

HONG KONG, Intel Semiconductor Ltd. 32/F Two Pacific Place, 88 Queensway, Central Tel: +852 2844-4555

CANADA, Intel Semiconductor of Canada, Ltd. 190 Attwell Drive, Suite 500 Rexdale, Ontario M9W 6H8 Tel: +416 675-2438

BRAZIL, Intel Semicondutores do Brasil Centro Empresarial Nações Unidas - Edifício Torre Oeste Av. das Nações Unidas, 12.901 - 18o. andar - Brooklin Novo 04578.000 São Paulo - S.P. – Brasil Tel: +55-11-5505-2296