# Preface

The 7th edition of the "Real Numbers and Computers" conference has been held in Nancy, France from July 10 to July 12, 2006. These proceedings contain all contributed papers presented at RNC'7, together with abstracts of the invited talks by Richard Brent, Stuart Oberman and Vadim Shapiro, and abstracts of the papers accepted in the poster session.

RNC'7 is the seventh of a series of conferences held in Europe. The first edition took place in St-Étienne (France) in 1995, followed by

- RNC'2 in Marseille (France),

- RNC'3 at Université Paris 6, Paris (France),

- RNC'4 in Schloss Dagstuhl (Germany),

- RNC'5 in Lyon (France), and

- RNC'6 in Schloss Dagstuhl (Germany).

The focus of the conference is on computer arithmetic in a rather broad sense, including e.g. computability, geometric algorithms and formal proofs in computer arithmetic. During RNC'7 has been held a friendly competition for multiprecision arithmetic packages, the "Moredigits" competition. This competition has been organized by L. Fousse, V. Lefèvre and N. Müller.

In response to the call for papers, the Program Committee received 22 submissions. Each submission has been anonymously referred by at least 3 referred. After a revision process by the authors, 12 papers have finally been accepted for presentation at the conference.

The topics addressed by these papers are rather broad. Several topics proved to be especially active by a good number of submissions: hardware design, computability and complexity, efficient implementation of mathematics libraries, representation of numbers, and reliable computations (algorithms and testing). On the other hand, two expanding topics are also represented: arithmetic on GPUs and formalization of real numbers.

We wish to thank all the authors who submitted papers for the conference, the members of the Program Committee and all the external reviewers who helped the Program Committee in its task of selection of the papers.

We acknowledge the financial help of our sponsors: LORIA, INRIA, CNRS, Université Henri-Poincaré Nancy 1, Institut National Polytechnique de Lorraine, Université Nancy 2, Communauté Urbaine du Grand Nancy and Conseil Régional de Lorraine and thank them for their support. We also would like to thank Mairie de Nancy for the reception organized at the town hall.

Finally, we would like to thank all the people who participated in the organization of this conference, especially Anne-Lise Charbonnier (financial aspects, practical organization), the "service communication" from LORIA and Emmanuel Thomé (webmaster, proceedings) who all did a great job.

Let us conclude by incitating everyone to submit papers to the forthcoming Arith'18 conference that will be held in Montpellier in 2007. Hopefully we shall be meeting again there!

Guillaume Hanrot Paul Zimmermann

RNC'7 co-chairs. http://rnc7.loria.fr ii

# Organisation

RNC'7 has been hosted in LORIA (Laboratoire Lorrain de Recherche en Informatique et Applications), Nancy, France, from July 10th to July 12th, 2006.

## **Program Committee**

| Elisardo Antelo    | Santiago de Compostela, Spain |

|--------------------|-------------------------------|

| Henk Barendregt    | Nijmegen, The Netherlands     |

| Vasco Brattka      | Cape Town, South Africa       |

| Nicolas Brisebarre | Saint-Étienne, France         |

| Hervé Brönnimann   | New York, United States       |

| Martín Escardó     | Birmingham, United Kingdom    |

| Guy Even           | Tel Aviv, Israël              |

| Christiane Frougny | Paris, France                 |

| Guillaume Hanrot   | Nancy, France (co-chair)      |

| Peter Kornerup     | Odense, Denmark               |

| Paolo Montuschi    | Torino, Italy                 |

| Norbert Müller     | Trier, Germany                |

| Michael Parks      | Santa Clara, United States    |

| Siegfried Rump     | Hamburg, Germany              |

| Paul Zimmermann    | Nancy, France (co-chair)      |

|                    |                               |

# Steering Committee

| Jean-Claude Bajard   | Montpellier, France     |

|----------------------|-------------------------|

| Vasco Brattka        | Cape Town, South Africa |

| Jean-Marie Chesneaux | Paris, France           |

| Marc Daumas          | Montpellier, France     |

| Christiane Frougny   | Paris, France           |

| Peter Kornerup       | Odense, Denmark (chair) |

| Dominique Michelucci | Diion France            |

| 0.0                  | ,                       |

# **Organisation** Committee

| Coordination           | Guillaume Hanrot      |

|------------------------|-----------------------|

|                        | Paul Zimmermann       |

| Website, proceedings   | Emmanuel Thomé        |

| Friendly competition   | Laurent Fousse        |

|                        | Vincent Lefèvre       |

|                        | Norbert Müller        |

| Registration, planning | Anne-Lise Charbonnier |

|                        | Céline Simon          |

| Poster, publicity      | Julian Rivierre       |

|                        | Bénédicte Maure       |

### Referees

| Elisardo Antelo        | Martín Escardó     | Jean-Michel Muller |

|------------------------|--------------------|--------------------|

| Henk Barendregt        | Guy Even           | Norbert Müller     |

| Andrej Bauer           | Laurent Fousse     | Russell O'Connor   |

| Valérie Berthé         | Christiane Frougny | Michael Parks      |

| Vasco Brattka          | Torbjörn Granlund  | Siegfried Rump     |

| Nicolas Brisebarre     | Guillaume Hanrot   | Damien Stehlé      |

| Herve Brönnimann       | Ahmad Hiasat       | Arnaud Tisserand   |

| Chichyang Chen         | Peter Kornerup     | Xavier Urbain      |

| Éric Colin de Verdière | Fabrizio Lamberti  | Liang-Kai Wang     |

| Pierre Courtieu        | Vincent Lefèvre    | Freek Wiedijk      |

| Florent de Dinechin    | Paolo Montuschi    | Paul Zimmermann    |

|                        |                    |                    |

## **Sponsoring Institutions**

CNRS (Centre National de la Recherche Scientifique) INRIA (Institut National de Recherche en Informatique et Automatique) Université Henri Poincaré – Nancy 1 Université Nancy 2 Institut National Polytechnique de Lorraine Mairie de Nancy Communauté Urbaine du Grand Nancy Conseil Régional de Lorraine

# Table of Contents

| I Abstracts of Invited Talks                                                                                                                                             |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| GPUs: Applications of Computer Arithmetic in 3D Graphics                                                                                                                 | 3  |

| Tolerancing and Metrology of Geometric Models                                                                                                                            | 5  |

| Fast Algorithms for High-Precision Computation of Elementary Functions<br>Richard P. Brent                                                                               | 7  |

| II Contributed Talks                                                                                                                                                     |    |

| Session 1: Distillation                                                                                                                                                  |    |

| Fast, Guaranteed-Accurate Sums of Many Floating-Point Numbers                                                                                                            | 11 |

| Implementation of Float-Float Operators on Graphics Hardware<br>Guillaume Da Graça, David Defour                                                                         | 23 |

| Session 2: Computability and Intervals                                                                                                                                   |    |

| An Ordinary Differential Equation Defined by a Computable Function whose Maximal<br>Interval of Existence is Non-Computable<br>Daniel S. Graça, Ning Zhong, Jorge Buescu | 33 |

| Interval Analysis Without Intervals (extended abstract)                                                                                                                  | 41 |

| Session 3: Hardware                                                                                                                                                      |    |

| Conditional Speculative Decimal Addition<br>Álvaro Vázquez, Elisardo Antelo                                                                                              | 47 |

| Pipelined Architecture for Accurate Floating Point Range Reduction<br>Francisco J. Jaime, Javier Hormigo, Julio Villalba, Emilio L. Zapata                               | 59 |

| Session 4: Elementary Functions                                                                                                                                          |    |

| Decidability of Collision between a Helical Motion and an Algebraic Motion<br>Sung Woo Choi, Sung-il Pae, Hyungju Park, Chee K. Yap                                      | 69 |

| Software Techniques for Perfect Elementary Functions in Floating-Point Interval<br>Arithmetic                                                                            | 83 |

Accurate Math Functions on the Intel IA-32 Architecture: A Performance-Driven Design 93 Cristina Anderson, Nikita Astafiev, Shane Story

# Session 5: New Representations

| The Sunity Representation to Improve the Accuracy of Some Computations 107<br>Tomás Lang, Javier D. Bruguera                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RN-Codings: New Insights and Some Applications 117<br>Peter Kornerup, Jean-Michel Muller                                                                     |

| Session 6: Testing                                                                                                                                           |

| Unifying Tests for Square Root 125<br>Michael Parks                                                                                                          |

| III Abstracts of Posters                                                                                                                                     |

|                                                                                                                                                              |

| An Experimental Stochastic Lazy Floating-Point Arithmetic 137<br>Keith Briggs                                                                                |

| * 0                                                                                                                                                          |

| Keith Briggs<br>Software Implementation of the IEEE 754R Decimal Floating-Point Arithmetic 139                                                               |

| Keith BriggsSoftware Implementation of the IEEE 754R Decimal Floating-Point Arithmetic 139Marius Cornea, Cristina AndersonAccurate Dot Products with FMA 141 |

| Author Index |  |  |  |  | 145 |

|--------------|--|--|--|--|-----|

|--------------|--|--|--|--|-----|

# Part I

# **Abstracts of Invited Talks**

# GPUs: Applications of Computer Arithmetic in 3D Graphics (extended abstract)

Stuart F. Oberman

NVIDIA Santa Clara, California USA

The rendering of 3D graphics places extreme demands on computational hardware. Dedicated Graphics Processing Units, or GPUs, are designed to enable high performance 3D graphics and multimedia. Modern GPUs incorporate highly-parallel architectures, making them more effective than traditional CPUs for a wide range of complex parallel algorithms, but especially for the challenges relating to image synthesis.

CPUs comprise a relatively small proportion of computational area relative to the area used for caches and instruction issue control. In 2006, a high-end dual-core x86 CPU contains about 150 million transistors, and it has a peak floating-point throughput of approximately 50 single-precision GFLOPS. In contast, a 2006 high-end GPU contains about 300 million transistors, and it has a peak floating-point throughput of nearly 300 single-precision GFLOPS of a traditional, programmable nature. In addition to this general programmable floating-point computational power, GPUs contain a wide variety of special purpose, fixed-function arithmetic, whose purpose it is to accelerate specific components of the 3D graphics pipeline. The total of all of the special purpose arithmetic hardware may exceed an additional several hundred GFLOPS. Some of this special purpose arithmetic operates on floating-point operands, although not necessarily in IEEE 754 compatible formats. Other arithmetic units operate on fixed-point operands. In total, comparing CPUs to GPUs, a current high-end GPU has about twice the transistor count of a high-end CPU, yet it has an order of magnitude more total arithmetic processing power.

In this talk I will provide some history of GPUs. This will include a discussion of the evolution of GPUs from their 2D-only ancestors, to the 3D-only accessory boards, to the modern Graphics Processor, motivated using representative images. A brief overview of the canonical 3D graphics pipeline will then be presented. A typical scene to be displayed is first described by triangles of materials simulated by sampled images and textures. Mathematical processing is performed on each of the triangles' vertices, in order to rotate, translate and scale each object in the scene, as well as to properly adjust the entire scene's position in the effective camera's field of view. This process of vertex processing is accomplished using *vertex shaders*. Processed triangles are then rasterized into pixels. The rasterization process involves identifying every pixel that belongs to a triangle. Several arithmetic units are required to perform the various tasks implicit in triangle rasterization. Finally, the pixels themselves are processed using *pixel shaders*. This pixel computation may include texture sampling, color calculation, and various blending functions.

I will then discuss the evolution of *shaders* from fixed-function hardware to fully programmable computational engines. The microarchitectures of modern GPUs will be explored to understand how each step of the graphics pipeline may map into either fixed-function arithmetic units or programmable shaders. I will then discuss in more detail some of the arithmetically intensive operations, including the core shading engines. The computational core of a modern shader will be examined, including floating-point multiplication, addition,

#### 4 Stuart F. Oberman

and multiply-add units, as well as the requirements and algorithms used for the various higher-order functions, such as reciprocal, reciprocal square-root, binary logarithm, binary exponential, and the sin and cos functions. Other shader arithmetic aspects to be examined include the details of per-pixel attribute interpolation and its mapping to arithmetic hardware. Finally, the details of texture sampling and filtering will be examined. Given a texture residing in memory, the usage of MIP maps will be discussed. The arithmetic algorithms used for finding the appropriate level-of-detail in a MIP map stack for a given pixel will be investigated, followed by a look at the arithmetic required for visually acceptable texture sample filtering.

# Tolerancing and Metrology of Geometric Models (extended abstract)

Vadim Shapiro<sup>\*</sup>

Mechanical Engineering and Computer Sciences University of Wisconsin - Madison vshapiro@engr.wisc.edu

Computer representations of geometric models of physical artifacts have become the principal means for creating, communicating, exchanging, and analyzing engineering information. Geometric modeling is supported by several elegant mathematical theories that assume the ability to compute and store geometric representations exactly. In contrast, all practical implementations rely on real number computations with finite computational resources. This incompatibility between the theories and their implementations led to emergence of new academic problems, broadly referred to as geometric robustness and tolerant modeling, that remain without satisfactory solutions. It is also a cause of great practical difficulties with substantial negative economic impact that is measured in billions of dollars annually. A whole new industry of geometric validation and repair has been created in an attempt to circumvent these fundamental challenges created by mismatch between the theory and practice. Several international standards are being created for cataloguing and categorizing both difficulties and ad hoc solutions to geometric data quality problems.

Important lessons can be learned by treating geometric models as manufactured objects, similar to traditional mechanical parts and assemblies. It is generally accepted that modern mass production and most of the manufacturing technologies of the past century could not have been possible without the doctrine of *interchangeability*. It dictates that a mechanical part may be replaced by another 'equivalent' component without affecting the overall function of the product. Prior to the adoption of this principle, manufacturing was a custom art practiced mainly by skilled artisans who made all components to nominal size, as precisely as possible, and on a very small scale. Implementation of the principle of interchangeability led to standardized principles of *tolerancing* (focused on specification and control of geometric variability) and *metrology* (inspection of manufactured parts through measurement and analysis of accuracy). Recent efforts focus on mathematical foundations of geometric dimensioning and tolerancing, using concepts of tolerance *zones* and material *containments* conditions.

I will argue that parallel efforts on tolerancing and metrology are needed to reconcile the theory of geometric modeling with the computational reality. The theory should recognize that modeling exactly, or as precisely as possible, is not a viable practical alternative. It is reasonable to expect that a more general theory of geometric modeling should include concepts of interchangeability, tolerances, zones, and containment, but it is also important that this theory contains the classical exact theory as a special case. An important difference between tolerances in manufacturing and in geometric modeling is that manufacturing accuracy concerns exclusively with variability of real *physical* objects, whereas geometric errors can easily render a *computer* geometric model non-physical, and therefore invalid. Establishing validity conditions for a toleranced geometric model is one of the key problems in metrology of geometric models. I will propose the beginnings of such a new theory for tolerancing and metrology of geometric models, but many challenging questions remain open.

<sup>\*</sup> Supported in part by National Science Foundation grants OCI-0537370, DMI-0500380, DMI-0323514

# Fast Algorithms for High-Precision Computation of Elementary Functions (extended abstract)

Richard P. Brent

Australian National University http://www.rpbrent.com/

In many applications of real-number computation we need to evaluate elementary functions such as  $\exp(x)$ ,  $\ln(x)$ ,  $\arctan(x)$  to high precision (see for example [1]). We shall survey some of the well-known (and not so well-known) techniques as well as mentioning some new ideas.

Let d be the number of binary digits required, so the computation should be accurate with relative (or, if appropriate, absolute) error  $O(2^{-d})$ . By "high-precision" we mean higher than can be obtained directly using IEEE 754 standard floating-point hardware, typically d several hundred up to millions.

We are interested both in "asymptotically fast" algorithms (the case  $d \to +\infty$ ) and in algorithms that are competitive in some range of d. Let M(d) denote the time (measured in word- or bit-operations) required to multiply d-bit numbers with d-bit accuracy (we are generally only interested in the upper half of the 2d-bit product). Classically  $M(d) = O(d^2)$ and the Schönhage-Strassen algorithm [12] shows that  $M(d) = O(d \log d \log \log d)$ . However, Schönhage-Strassen is only useful for large d, and there is a significant region  $d_1 < d < d_2$ where A. Karatsuba's  $O(d^{\lg 3})$  algorithm [8] is best ( $\lg 3 = \log_2 3 \approx 1.58$ ). In the region where Karatsuba's algorithm is best for multiplication, the best algorithms for elementary functions need not be those that are asymptotically the fastest.

Sometimes the best algorithm depends on the ground rules: are certain constants such as  $\pi$  allowed to be precomputed, or does the cost of their computation have to be counted every time in the cost of the elementary function evaluation?

Techniques for high-precision elementary function evaluation include the following. Often several are used in combination, e.g. argument reduction is used before power series evaluation.

1. Argument reduction using identities such as

$$\exp x = \left(\exp(x/2)\right)^2$$

,  $\arctan x = 2 \arctan\left(\frac{x}{1+\sqrt{1+x^2}}\right)$ , etc

2. Use of power series such as

$$\exp x = \sum_{k \ge 0} \frac{x^k}{k!} , \quad \ln(1+x) = \sum_{k \ge 0} \frac{(-1)^k x^{k+1}}{k+1} , \quad \arctan x = \sum_{k \ge 0} \frac{(-1)^k x^{2k+1}}{2k+1} .$$

perhaps evaluated using the technique of Smith [13], which applies more generally (for example to the evaluation of hypergeometric functions). Smith seems to be the first to apply his technique for real computation, but the idea was suggested by Paterson and Stockmeyer [10] and used in a different context by Brent and Kung [6] (but not in the author's multiple-precision package [5], because of the storage requirements).

By combining argument reduction and power series evaluation we get an  $O(M(d)d^{1/2})$  algorithm for  $\exp(x)$ , and using Smith's technique this can be improved to  $O(M(d)d^{1/3}) + O(d^{5/3} \log \log \log \log \log \log d)$  (the second term is essentially  $O(d^{5/3})$  in practice).

- 8 Richard P. Brent

- 3. Use of the arithmetic-geometric mean (AGM) to compute  $\ln x$  in time  $O(M(d) \log d)$  (asymptotically the fastest known), see [2–4]. In particular we mention the algorithm of Sasaki and Kanada [11], based on the elegant formula

$$\ln x = \frac{\pi}{\operatorname{AGM}(\theta_2^2(1/x), \theta_3^2(1/x))}$$

Because the theta functions have rapidly-converging series and this formula is exact, we can use it for smaller x than is possible with the usual "approximate" AGM-based formulae such as  $\ln x = \pi/((2 + O(1/x^2))\text{AGM}(1, 4/x))$ .

- 4. Use of Newton's method to compute inverse functions, for example we can compute  $\exp(x)$  from  $\ln(x)$  and *vice versa*. The overhead introduced by Newton's method can be reduced to a factor 1 + o(1) as  $d \to +\infty$  by using higher-order methods [3, §6-§9].

- 5. Use of complex arithmetic to compute a real result, for example

$$\arctan x = \frac{1}{2i} \ln \left( \frac{1+ix}{1-ix} \right) = \Im \ln(1+ix)$$

where the complex log can be computed by the AGM; this gives the asymptotically fastest known algorithm for arctan (although the complex arithmetic is a significant overhead).

6. Use of *binary splitting* [2, p. 329] (or similarly E. Karatsuba's *FEE method* [9]) to sum series with rational arguments [7]. For real arguments, we may be able to use a good rational approximation and then apply a small correction. To illustrate this we shall describe some new ideas for arctan evaluation which, although not asymptotically the fastest, are competitive for a wide range of precisions d (this is joint work with Jim White).

#### References

- D. H. Bailey, High-precision floating-point arithmetic in scientific computation, Computing in Science and Engineering, May-June 2005, 54-61; also report LBNL-57487. Available from http://crd.lbl.gov/ ~dhbailey/dhbpapers/.

- J. M. Borwein and P. B. Borwein, *Pi and the AGM*, Monographies et Études de la Société Mathématique du Canada, John Wiley & Sons, Toronto, 1987.

- 3. R. P. Brent, Multiple-precision zero-finding methods and the complexity of elementary function evaluation, in *Analytic Computational Complexity* (edited by J. F. Traub), Academic Press, New York, 1975, 151–176. Available from http://wwwmaths.anu.edu.au/~brent/pub/pub028.html.

- 4. R. P. Brent, Fast multiple-precision evaluation of elementary functions, J. ACM 23 (1976), 242–251.

- R. P. Brent, Algorithm 524: MP, a Fortran multiple-precision arithmetic package, ACM Trans. Math. Software 4 (1978), 71–81.

- R. P. Brent and H. T. Kung, Fast algorithms for manipulating formal power series, J. ACM 25 (1978), 581–595.

- 7. X. Gourdon and P. Sebah, Numbers, constants and computation: binary splitting method, http://numbers.computation.free.fr/Constants/Algorithms/splitting.html.

- A. Karatsuba and Y. Ofman, Multiplication of multidigit numbers on automata (in Russian), Doklady Akad. Nauk SSSR 145 (1962), 293–294. English translation in Sov. Phys. Dokl. 7 (1963), 595–596.

- E. A. Karatsuba, Fast evaluation of transcendental functions (in Russian), Probl. Peredachi Inf. 27, 4 (1991), 87-110. English translation in Problems of Information Transmission 27 (1991), 339-360. See also http://www.ccas.ru/personal/karatsuba/faqen.htm.

- M. S. Paterson and L. J. Stockmeyer, On the number of nonscalar multiplications necessary to evaluate polynomials, SIAM J. Computing 2 (1973), 60–66.

- 11. T. Sasaki and Y. Kanada, Practically fast multiple-precision evaluation of log(x), J. Inf. Process. 5 (1982), 247–250. See also [2, §7.2].

- 12. A. Schönhage and V. Strassen, Schnelle Multiplikation Grosser Zahlen, Computing 7 (1971), 281–292.

- D. M. Smith, Efficient multiple-precision evaluation of elementary functions, Math. Comp. 52 (1989), 131– 134.

# Part II Contributed Talks

# Fast, Guaranteed-Accurate Sums of Many Floating-Point Numbers

Yong-Kang Zhu and Wayne Hayes

School of Information and Computer Science University of California, Irvine, CA 92697 {yongkanz,wayne}@ics.uci.edu

Abstract. We present an algorithm for computing the faithfully-rounded sum of an array of n floating-point numbers. It requires no extended accumulator, and works in any base. Similar to the fastest recently published accurate approaches, its running time is about six times that of the naïve one-loop approach. We prove that it always produces a faithfully rounded result (modulo intermediate overflow), independent of both n and the condition number of the sum, as long as a sufficiently large temporary storage array is available. We argue, and observe empirically, that the maximum size of the temporary array is bounded by a small constant times the maximum number of non-overlapping mantissas that are representable by the machine arithmetic (39 in the case of IEEE754 double), although we have not yet proven this bound rigorously.

Keywords: floating-point summation, rounding error, distillation

#### 1 Introduction

The summation of n floating-point numbers,  $\sum_{i=1}^{n} x_i$ , is ubiquitous in numerical computations, and has been the subject of much recent work. Anderson [1] proposes a distillation algorithm as defined in [3], which iteratively and accurately deflates pairs of oppositely signed floating-point numbers until all of them have the same sign except for those with negligibly small absolute value. The final result is obtained by using compensated summation [4]. Comparisons between this method and other ones can be found in [6, 9].

A new distillation algorithm for floating-point summation was presented in [9], which is more robust and faster than Anderson's method. It adds two summands repeatedly, without discarding any significant digit until the partial sums cannot change the whole sum. It does not rely on the choice of radix or any other specific assumption. Furthermore, its error bound ( $\leq 1$ ulp) is independent of n and the condition number,  $R = \sum_{i=1}^{n} |x_i|/|\sum_{i=1}^{n} x_i|$ . However, it is significantly slower than some other recently proposed methods.

Ogita et al. [6] presented a method called SumK, which has an integer parameter K, representing a limit on the running time of the algorithm. For K large enough, the algorithm is guaranteed to produce a correct result, but K must increase both with the number of summands n, and the condition number, in order to produce a guaranteed exact result. The authors suggest a value of K = 3 for practical purposes, but then the algorithm is guaranteed to fail for certain inputs. Rump et al. [8] introduce a new algorithm named AccSum which works only in binary but whose accuracy is independent of the condition number, although it is still dependent upon n.

In this paper, a new fast algorithm for floating-point summation is presented. Our method guarantees that the result is faithfully rounded.

12 Yong-Kang Zhu and Wayne Hayes

Its accuracy is independent of both n and the condition number. Its typical running time is almost as fast as the method Sum3 [6], which is the K = 3 version of SumK algorithm. However, in very rare cases its running time can be dependent on n and the condition number. In the next section, we describe this method in detail and analyze its error bound. Comparisons are given in section 3. Some further discussion is provided in Section 4. Conclusions are drawn in section 5.

#### 2 Algorithm and analysis

#### 2.1 Algorithm

The accuracy of the method of Zhu et al. [9] is independent of n and the condition number. It uses two arrays to save the positive and negative numbers separately. The operations of adding and removing elements to the array are relatively expensive.

Therefore, it runs slower than the methods described in [6, 8]. Our new method improves upon [9] by pre-allocating an array for saving the terms comprising two temporary sums,  $s_p$ and  $s_n$ , in each loop. All operations are done in the given arrays. So, no elements need to be inserted or removed from the array.

Our method depends on the existence of the accurate addition between two floating-point numbers. Here, we assume  $\{s, e\} \leftarrow \text{AddTwo}(a, b)$  is such an algorithm that s + e = a + b and s = fl(a + b) (and so the mantissas of s and e do not overlap). There are several choices, such as TwoSum [6], Algorithm2 [9], and Algorithm2' [9]. In our numerical tests, Algorithm2' [9] is chosen, since this method is fast and accurate when using binary floating-point arithmetic. It contains only three standard floating-point additions. If used for other bases, then it can be replaced by other accurate algorithms. We also assume that the floating-point operations,  $\text{fl}(a \pm b)$ , are faithfully rounded [7]. That is, let y = fl(x) be the operation that returns the floating-point value of x, and  $|a| \leq |x| < |b|$ , where a and b are two consecutive floating-point numbers with the same sign as x. Here, y is called faithfully rounded if and only if y = awhenever x = a and either y = a or y = b whenever  $x \neq a$ . (Note that this is not as stringent as round-to-nearest, which we do not guarantee.) Our algorithm also makes no effort to avoid intermediate overflow in the case that the sum is representable. The algorithm is described below. We use  $\beta$  to represent the base of the floating-point number, and t to represent the length of the mantissa (for example, in IEEE754 double,  $\beta = 2$  and t = 53).

ALGORITHM:  $s = \text{FastSum}(x, n, q, L, c_q).$

- Input: x, the array of the given floating-point summands;

- n, the number of summands;

- q, the accessory array for recording the temporary sums;

- L, the maximal size of the array q (in IEEE754 double, set L = 200);

- $c_q$ , the current number of elements in q (initially 0).

Output: s, the sum with a faithful rounding.

- 1.  $s \leftarrow 0$ ;  $loop \leftarrow 1$ ;

- //loop counts the number of *n*-sized loops

- 2. for  $i \leftarrow 1$  to n

- (1)  $\{s, x[i]\} \leftarrow \text{AddTwo}(s, x[i]);$

- 3. loop forever

```

(1) count \leftarrow n; s_p \leftarrow 0; s_n \leftarrow 0; loop \leftarrow loop + 1;

//count records the number of non-zero numbers remaining in the x and q arrays

//s_p and s_n accumulate the positive and negative summands respectively

(2) for i \leftarrow 1 to n

(a) if x[i] > 0, then \{s_p, x[i]\} \leftarrow \text{AddTwo}(s_p, x[i]);

(b) else \{s_n, x[i]\} \leftarrow \text{AddTwo}(s_n, x[i]);

(c) if x[i] = 0, then count \leftarrow count - 1;

(3) for i \leftarrow 1 to c_a

//notice if c_q < 1, then do nothing here and go to Step 3(4)

(a) if q[i] > 0, then \{s_p, q[i]\} \leftarrow \text{AddTwo}(s_p, q[i]);

(b) else \{s_n, q[i]\} \leftarrow \text{AddTwo}(s_n, q[i]);

(c) if q[i] \neq 0, then count \leftarrow count + 1;

(4) e_m \leftarrow count \cdot ulp(max(|s_p|, |s_n|));

//a weak upper bound on sum of remaining terms in x and q

(5) e_1 \leftarrow s_p; e_2 \leftarrow s_n;

(6) do

(a) \{e_1, e_2\} \leftarrow \text{AddTwo}(e_1, e_2);

(b) \{s, e_1\} \leftarrow \text{AddTwo}(s, e_1);

while (\mathrm{fl}(s + \mathrm{fl}(e_1 + e_2)) \neq s);

(7) c_q \leftarrow c_q + 1; q[c_q] = e_1;

(8) c_q \leftarrow c_q + 1; q[c_q] = e_2;

(9) if c_q >= L - 1, then return s;

//\text{error condition}, L \text{ is set too small}

(10) if fl(s+e_m) = s, then

(a) \{E_1, E_2\} \leftarrow \text{AddTwo}(e_1, e_2);

(b) if fl(fl(E_1 + fl(E_2 + e_m)) + s) = s and fl(fl(E_1 + fl(E_2 - e_m)) + s) = s, then

return s;

```

(c) else return  $s + \text{FastSum}(x, n, q, L, c_q)$ ;

```

4. END

```

Given the array x and the number of summands n, we first initialize an empty array q whose size is L, and then call FastSum(x,n,q,L,0) to compute the result s. In our algorithm FastSum, Step 2 makes an ordinary iterative summation, saving the errors in x. Step 3 is an infinite loop until the ending conditions (see Steps 3(9) and 3(10)) are satisfied. This loop works as follows. In Step 3(2), all the positive numbers are summed into  $s_p$ , while all the negative numbers are summed into  $s_n$ . Then in Step 3(3), we perform the same operation on the accessory array q. An upper bound on the sum of all the remaining numbers in x and q is computed in Step 3(4), according to the current temporary sums  $s_p$  and  $s_n$ . In Step 3(6),  $s_p$  and  $s_n$  are added to s and in Steps 3(7) and 3(8) the errors are stored into the accessory array q.

#### 2.2 **Proof of correctness**

**Theorem.** If FastSum does not return from Step 3(9), then it generates a result that is faithfully rounded.

*Proof.* Since AddTwo gives an exact addition between two floating-point numbers, all additions use AddTwo, and all the errors of AddTwo are stored, the algorithm FastSum does not discard any significant digits before it returns a result. All the errors are stored in the arrays x and q. Assume each floating-point number is represented as

$$x = \pm 0.d_1 d_2 \dots d_t \times \beta^{\exp(x)},\tag{1}$$

where  $\exp(x)$  is the exponent of the floating-point number x. Let  $ulp(x) = \beta^{\exp(x)-t}$ . For each  $\{s, e\} \leftarrow AddTwo(a, b)$ , we have |e| < ulp(s) since s = fl(a + b) with a faithful rounding. Therefore, after Steps 3(2) and 3(3) we have

$$|x[i]| < ulp(max(|s_p|, |s_n|)), \quad i = 1, 2, \cdots, n, |q[j]| < ulp(max(|s_p|, |s_n|)), \quad j = 1, 2, \cdots, c_q.$$

(2)

Recalling that *count* is the number of non-zero terms in the x and q arrays, we have

$$\left|\sum_{i=1}^{n} x[i] + \sum_{j=1}^{c_q} q[j]\right| \leq \sum_{i=1}^{n} |x[i]| + \sum_{j=1}^{c_q} |q[j]| < count \cdot ulp(\max(|s_p|, |s_n|)) = e_m.$$

(3)

It can be shown (using Lemma A from Appendix A) that Step 3(6) will stop after at most two loops, at which time  $|e_1 + e_2| < ulp(s)$ .

The algorithm may return a result at one of three positions: Steps 3(9), 3(10)(b), and 3(10)(c). We prove the correctness of the algorithm by cases. We disregard the first case since we believe we can set L large enough so that the algorithm never returns from Step 3(9). **Case 1: if** s **is returned from Step 3(10)(b).** When the condition in Step 3(10) is satisfied, we have

$$|e_m| < \mathrm{ulp}(s). \tag{4}$$

Let  $x[i]^{(0)}$  be the original summands, and let x[i] be the remaining errors in the array x. Then,

$$\sum_{i=1}^{n} x[i]^{(0)} = s + E_1 + E_2 + \sum_{i=1}^{n} x[i] + \sum_{j=1}^{c_q-2} q[j].$$

(5)

Note that Steps 3(7) and 3(8) are already executed at Step 3(10)(b). So, the last two numbers in q are  $e_1$  and  $e_2$ , which are not counted when calculating  $e_m$ . To prove s is a faithful rounding of  $\sum_{i=1}^{n} x[i]^{(0)}$ , our task is to prove

$$fl\left(s + E_1 + E_2 + \sum_{i=1}^n x[i] + \sum_{j=1}^{c_q-2} q[j]\right) = s.$$

(6)

Therefore, according to (3), if both

$$fl(s + E_1 + E_2 + e_m) = s$$

, and (7)

$$fl(s + E_1 + E_2 - e_m) = s,$$

(8)

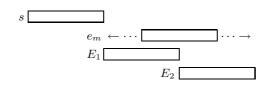

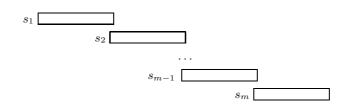

**Fig. 1.** Schematic illustration of the relationship between s,  $E_1$ ,  $E_2$ , and  $e_m$  after Step 3(10)(a). s,  $E_1$ , and  $E_2$ , have no mutual overlap, but  $e_m$  may appear anywhere "below" s.

are satisfied, then we can obtain (6). We will show the ending condition in Step 3(10)(b)

$$fl(s + fl(E_1 + fl(E_2 + e_m))) = s,$$

(9)

$$fl(s + fl(E_1 + fl(E_2 - e_m))) = s,$$

(10)

imply (7) and (8). From Steps 3(6) and 3(10), we have that  $fl(s+fl(E_1+E_2)) = s$ ,  $fl(E_1+E_2) = E_1$ , and  $fl(s+e_m) = s$  (see Figure 1). Since  $e_m \ge 0$ , without loss of generality, we can assume  $E_1 > 0$ , then (10) clearly implies (8). [ To see this, consider (10): (i) If  $E_2 \ge 0$ , then (10) and (8) are both satisfied due to the cancellation of  $E_1$  and  $e_m$ . (ii) If  $E_2 < 0$ , then  $E_1$  and  $e_m$  either overlap, or they do not. If they overlap, then we have  $|E_1 + fl(E_2 - e_m)| < \max(|E_1|, |e_m|)$ , which is too small to change s. If  $E_1$  and  $e_m$  do not overlap, then  $fl(E_2 - e_m)$  can decrease  $E_1$  by at most  $ulp(E_1)$ , which again is too small to change s. ] Thus, we only need to prove (9) implies (7). Since  $e_m, E_1 \ge 0$  and Step 3(10)(a) yields (Figure 1),

$$|E_2| < \operatorname{ulp}(E_1) \tag{11}$$

we have, according to (9) and (11),

$$fl(E_1 + E_2 + e_m) \ge E_1.$$

(12)

Hence, we obtain

$$|\mathrm{fl}(E_1 + E_2 + e_m)| = |\mathrm{fl}(E_1 + \mathrm{fl}(e_m + E_2))| < \mathrm{ulp}(s).$$

(13)

Case 2: if s is returned from Step 3(10)(c). In this case, we have  $|E_1 + E_2| < ulp(s)$  and  $|e_m| < ulp(s)$ . Hence,

$$|fl(E_1 + E_2 + e_m)| < 2ulp(s).$$

(14)

Assume FastSum is called recursively and FastSum always returns at Step 3(10)(c). In each call of FastSum, we can obtain an s. Let  $s_j$ , for  $j = 1, 2, \dots, m$ , denote the s in the j-th recursive call of FastSum, where  $s_1$  has the largest absolute value. With (14), every two neighbors, say  $s_j$  and  $s_{j+1}$ , have at most one digit overlapping between their mantissas (see Figure 2). If using one floating-point number  $\hat{s}$ , whose mantissa is long enough, to represent the exact value of  $\sum_{i=1}^{n} x[i]^{(0)}$ , then the length of the mantissa of  $\hat{s}$  is finite. Thus, m is finite. Furthermore, the last sum,  $s_m$ , returned by FastSum, is faithfully rounded, assuming the sums returned in Cases 1 and 3 are faithfully rounded. Therefore, the final result obtained by recursively summing  $s_i$  from j = m to 1 is faithfully rounded.

This concludes the proof of the Theorem.

**Fig. 2.** Schematic illustration of the relationship between  $s_i$ , for  $i = 1, 2, \dots, m$ .

#### 2.3 Memory requirements, and discussion of Step 3(9)

The third case, if s is returned from Step 3(9), is not a part of our theorem, because we do not guarantee that s is faithfully rounded in this case. In a real-world implementation, the programmer would have a choice either of returning the "best-guess" for the sum that is currently stored in s, or of returning an error condition. However, we believe that it is possible to choose an L large enough so that s is never returned from Step 3(9). The smallest value of L required to avoid Step 3(9) is a function of machine arithmetic. We will first give a general discussion, and then details for IEEE754.

All the positive and negative numbers in x and q (including e1 and e2) can be regarded as two separate sequences, summing to  $s_p$  and  $s_n$ , respectively. We argue in the Appendix that the algorithm can reach a stable state after finite loops such that each AddTwo either does nothing, or simply swaps the two input addends. This occurs when no two numbers in x and q have overlapping mantissas, so that when applying AddTwo to any of them, the addend with greater magnitude becomes the sum, and the smaller one becomes the error. In this state, the values in the arrays x and q do not change. As argued in the Appendix,  $s_p$  ( $s_n$ ) is the positive (negative) sum with a faithful rounding, and s is the whole sum with a faithful rounding. Furthermore, after finite loops, deflation causes each sequence to converge to being sorted by magnitude, with non-overlapping mantissas so that each element is the faithfully rounded sum of the elements before it, and none of the elements in the x and q arrays have overlapping mantissas with s. That is, our algorithm has in principle finished, in that

$$fl\left(s + \sum_{i=1}^{n} x[i] + \sum_{j=1}^{c_q} q[j]\right) = s.$$

(15)

However, we cannot *detect* that we are finished because 3(10) is not satisfied. This occurs because  $e_m$  is a pessimistic upper bound on the sum of remaining terms in x and q, and it is too pessimistic when *count* in Step 3(4) is too big, which in turn occurs when there are too many non-zero elements in the arrays x and q. Thus it is possible that  $fl(s + e_m) \neq s$  while (15) is satisfied. We now argue that this can be avoided as long as the algorithm is allowed to converge to the non-overlapping state described in the Appendix.

As we argue in the Appendix, after a finite number of loops, no two pairs of floating-point numbers in x or q have overlapping mantissas. Once the algorithm has converged to this state, the value of *count* is limited by the number of non-overlapping floating-point numbers that can be represented by the machine. For example, in IEEE754 *double*, the length of exponent is 11 binary digits, and t = 53. Therefore, the maximum value of *count* in the converged state is  $2^{11}/53 \approx 38.6$ . When using IEEE754 single precision, the maximum is  $2^8/24 \approx 10.7$ . Furthermore, we have observed empirically (see below) that our algorithm converges to the the fully non-overlapping state in at most  $48 \ loops$ , requiring at most L = 96. In order for  $e_m$  to change s in this converged state of  $\max(|s_p|, |s_n|) \approx \operatorname{ulp}(s)$  and  $e_m = \operatorname{count} \cdot \operatorname{ulp}(\max(|s_p|, |s_n|))$ , we would require  $e_m \approx \max(|s_p|, |s_n|)$ , which would require  $\operatorname{count} \approx \beta^t$ , which is typically far greater than 38.

We have set L = 200 in our algorithm, although we are almost certain that a value of 100 is sufficient.

#### 3 Numerical results

In this section, we make comparisons among the following five methods: ordinary recursive summation, denoted by ORS; Sum3 (K = 3 for SumK) [6]; Algorithm 5 [9], denoted by Zhu05; AccSum [8]; and our new method FastSum. The floating-point arithmetic used here is IEEE754 *double*.

Three kinds of testing data are used in our numerical tests. The first one is the wellconditioned data, R = 1. Here, we randomly generate positive floating-point numbers. The second one is the ill-conditioned data, which are generated by the method mentioned in [1]: after randomly generating n floating-point numbers, the mean of the data (calculated using recursive summation) is subtracted from each datum. The condition number of this case is more than  $10^9$ . The third one is the extremely ill-conditioned data, whose real sum is exactly zero, which are obtained by randomly generating a pair of floating-point numbers with the opposite signs, and then randomly disturbing the order of these n numbers.

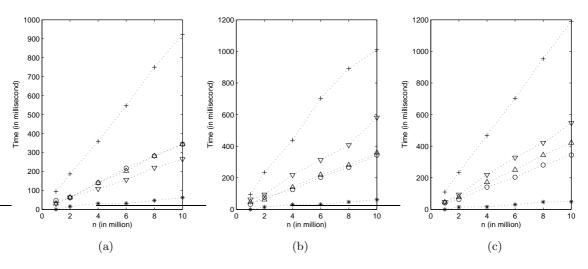

All algorithms are implemented with Visual C++ 6.0, and run on a machine with a Pentium M 1.4GHz processor, 512MB memory, and Microsoft Windows XP Pro. In our numerical tests, ORS method never produces a correct sum, and Zhu05, AccSum and FastSum always yield results with faithful rounding. Sum3 fails when the third kind of data is used and the maximal binary exponent difference between two summands is more than 90.

The running times of five methods are shown in Figure 4, and the ratios of them to that of the ordinary recursive summation are listed in Table 1. The observation is that FastSum runs about three times faster than Zhu05. The running times of Sum3, AccSum and FastSum are similar, all about 6 times slower than ORS. We can see from Figure 4 that the running times of all the algorithms are essentially linear with n.

| -         | -    |      |      |      |                    |

|-----------|------|------|------|------|--------------------|

| Data No.1 | 2    | 4    | 6    | 8    | $10 (\times 10^6)$ |

| Sum3      | 3.9  | 4.5  | 6.8  | 6.0  | 5.5                |

| Zhu05     | 11.7 | 11.6 | 17.1 | 16.0 | 14.9               |

| AccSum    | 4.0  | 3.5  | 4.9  | 4.7  | 4.3                |

| FastSum   | 4.0  | 4.5  | 6.3  | 5.9  | 5.5                |

| Data No.2 | 2    | 4    | 6    | 8    | $10 (\times 10^6)$ |

| Sum3      | 5.2  | 4.0  | 6.3  | 5.7  | 5.6                |

| Zhu05     | 15.7 | 14.1 | 21.9 | 18.9 | 16.6               |

| AccSum    | 6.3  | 7.0  | 9.8  | 8.7  | 9.5                |

| FastSum   | 4.1  | 4.5  | 6.8  | 5.9  | 5.8                |

| Data No.3 | 2    | 4    | 6    | 8    | $10 (\times 10^6)$ |

| Sum3      | 4.2  | 8.8  | 6.6  | 6.0  | 7.2                |

| Zhu05     | 15.6 | 29.3 | 22.7 | 20.3 | 24.7               |

| AccSum    | 6.3  | 13.7 | 10.5 | 9.0  | 11.4               |

| FastSum   | 5.2  | 10.7 | 8.1  | 7.3  | 8.8                |

Table 1. Ratio of the running times of summation methods to that of the ORS.

**Fig. 3.** Running time of summation methods using different data sets: (a) Data No.1, well-conditioned; (b) Data No.2, ill-conditioned; (c) Data No.3, the real sum equals zero, where ORS is denoted by '\*', Sum3 by ' $\circ$ ', Zhu05 by '+', AccSum by ' $\nabla$ ', and FastSum by ' $\Delta$ '

#### 4 Discussion

In the above numerical tests, we observe that FastSum always generates a result within 2 loops (*loop* = 2, see Steps 1 and 3(1)). That is, Steps 2 and 3 each execute precisely once. Furthermore, all the results are returned from Step 3(10)(b). We now explain why we believe L = 200 will always give a return from Step 3(10)(b). We have never observed a return from Step 3(10)(c).

Our algorithm takes advantage of a small relative error of the ordinary recursive summation when all the summands have the same sign. Therefore, when heavy cancellation happens, i.e. the condition number is large, our algorithm can make quick cancellations between positive and negative numbers. Using the third kind of data set, L = 200, and then gradually increasing the binary exponent difference between two summands, we observe that when the maximal exponent difference is greater than 90, then Sum3 generates errors. When the difference is greater than 2000, then AccSum produces an overflow. However the result obtained by FastSum is always observed to be correct, and the biggest *loop* is 48. As for the first and second kinds of data, the value of *loop* is always 2 even if we increase the exponent difference, since the condition number does not change much. Thus, we need a large L only when cancellation dominates.

In the case that the exact sum is zero (as in our third kind of data), our algorithm must cancel all the significant digits to produce a correct result. Assume we cancel m digits with each loop, and the maximal exponent difference between arbitrary two numbers is d. Then, our algorithm requires about  $\lceil d/m \rceil$  loops. Since in IEEE754 double, d = 2046, if we let m = t = 53, we have  $\lceil d/t \rceil = 39$ , assuming the algorithm can cancel 53 bits per loop, which is optimistic. Since our maximum loop is 48, we see that our algorithm cancels on average perhaps about 44 bits per loop. Thus, choosing  $L \approx 4d/t$  should be enough. In our test, we let L be 200, which allows Step 3 to loop at most 100 times. In practice, the case  $d \gg t$  is probably not realistic, since either  $s \ll ulp(M)$ , where

$$M = \max_{1 \le i \le n} (\left| x[i]^{(0)} \right|),$$

and so s probably does not represent a meaningful quantity; or  $s \gg S$ , where

$$S = \min_{1 \le i \le n} (\left| x[i]^{(0)} \right|)$$

Therefore, to save the space, we can make the size of q dynamically increasing from a small value (for instance, L = 6), since we believe that there exists an L which can let the algorithm return a faithfully rounding result. If it is known in advance that *loop* will be big (i.e., the sum is badly ill-conditioned and the maximum exponent difference is large), we note that each *loop* obliterates at least two values in the x array, so that the number of non-zero values is always decreasing. Thus, it may be advantageous to alternate between two copies of the x array, say  $x_0$  and  $x_1$ , copying only non-zero values from one to the other, and switching which one to use on the next *loop*, thus never having to deal with 0 values in Step 3(2). A similar approach can be used for Step 3(3). We did not implement this, because *loop* > 2 occurs only rarely.

Another question regards whether the many branches in our algorithm affect its efficiency. We tested the two AddTwo algorithms TwoSum [6] and Algorithm2' [9]. TwoSum is proposed by Knuth [5] which contains six floating-point addition operations without any branches. Algorithm2' is presented by Dekker [2] which has only three floating-point addition operations, but a branch is needed. Another aspect of efficiency is whether AddTwo requires a function call, or if the instructions are executed "inline". Table 2 gives the timings of FastSum under these four options. The environment is a Pentium M 1.4GHz processor under Windows XP Professional, compiled with Visual C++ 6.0. The compiler optimization option is "maximize speed", which is the default option for "Win32 Release" in Visual C++ 6.0. We observed that using Dekker's algorithm is always faster than using Knuth's algorithm. Thus, in our environment, empirical observations suggest that branches are not important. Although we find this surprising, we hypothesize that perhaps the Pentium's hardware branch prediction algorithm and optimal pipelining might reduce the cost of branches when the number of instructions inside the if/else construct is small.

|                          | with function calls | without function calls |

|--------------------------|---------------------|------------------------|

| Using Dekker's algorithm | 437                 | 375                    |

| Using Knuth's algorithm  | 469                 | 391                    |

Table 2. Running times (in milliseconds) of FastSum with four options.

Finally, we observe that the running time of FastSum is linear with n. In our numerical tests, we only give the results when n is huge. But we can compute its running time for another n from the existed results directly. For example, from Figure 4(c), the running time of FastSum when n = 10,000,000 is about 410 milliseconds. After testing, we found that the running time for FastSum (n = 1,000) running 10,000 times is also about 410 milliseconds, as it is for n = 100 running 100,000 times, etc.

#### 5 Conclusions

In this paper, we present a fast and accurate algorithm, FastSum. This algorithm improves upon [9], by running three times faster. In general cases, even if the condition number is about  $10^9$ , our algorithm returns a faithfully rounded result with two loops (loop = 2), and is never

20 Yong-Kang Zhu and Wayne Hayes

observed to require more than 48 loops, even in the worst-case of very unrealistic, contrived input data.

We depend on the existence of AddTwo, which is a black box for calculating the floatingpoint sum and the error of two arbitrary floating-point numbers, and on this condition our algorithm works independently of the base  $\beta$  of the floating-point arithmetic. Furthermore, we have proved that its accuracy does not depend on n or the condition number, although its running time may depend on n and the condition number in rare cases. We have also observed, and argued informally, that beyond the input array itself, the additional memory requirement is constant, although we have not formally proven it.

#### References

- I. J. Anderson. A distillation algorithm for floating-point summation. SIAM Journal on Scientific Computing, 20(5):1797–1806, 1999.

- 2. T. J. Dekker. A floating-point technique for extending the available precision. *Numer. Math.*, 18:224–242, 1971.

- N. J. Higham. The accuracy of floating point summation. SIAM Journal on Scientific Computing, 14(4):783– 799, 1993.

- N. J. Higham. Accuracy and Stability of Numerical Algorithms. SIAM. Philadelphia, second edition, 2002.

D. E. Knuth. The art of computer programming, volume 2/Seminumerical algorithms. Addison-Wesley, third edition, 1998.

- T. Ogita, S. M. Rump, and S. Oishi. Accurate sum and dot product. SIAM Journal on Scientific Computing, 26:1955–1988, 2005.

- D. M. Priest. On Properties of Floating Point Arithmetics: Numerical Stability and the Cost of Accurate Computations. PhD thesis, Mathematics Department, University of California, Berkeley, CA, 1992.

- 8. S. M. Rump, T. Ogita, and S. Oishi. Accurate floating-point summation. Technical report 05.12, Faculty for Information and Communication Sciences, Hamburg University of Technology, November 2005.

- Y.-K. Zhu, J.-H. Yong, and G.-Q. Zheng. A new distillation algorithm for floating-point summation. SIAM Journal on Scientific Computing, 26:2066–2078, 2005.

#### Appendix

#### Lemma A

In this section, we will show that

Claim 1: After finite loops FastSum can reach a stable status such that each AddTwo either does nothing, or simply swaps the two input addends, so that all the positive and negative elements, adding to  $s_p$  and  $s_n$  respectively, and thus the total sum s, are constant.

Our claim is based on the following Lemma.

```

ALGORITHM: SumA(w, n_w)

```

Input: w, the array of the given floating-point summands;  $n_w$ , the number of summands;

1. while (any two elements overlap)

```

(1) for i \leftarrow 2 to n_w

```

(a)  $\{w[i], w[i-1]\} = \text{AddTwo}(w[i], w[i-1])$

```

2. END

```

**Lemma A.** Algorithm SumA halts, at which time (i) no term overlaps any other, and (ii) each term  $w_i$  is a faithful sum of the terms before it.

*Outline of proof.* We omit the full proof (a) due to space limitations, and (b) because we believe this case is never satisfied, although we have not been able to prove that it is never satisfied. However, we will give a flavour of the proof of Lemma A.

The proof of part (i) is a direct consequence of the while statement in the algorithm; (ii) can be proved by contradiction. Let us imagine that the value of each w[i] represents mass. The fundamental observation is that the inner loop transfers mass towards higher-numbered elements (i.e., towards  $w[n_w]$ ), while residuals are pushed towards lower-numbered elements (i.e., towards w[1]). To see this, let us focus our attention on one particular element of the array, say w[k], 1 < k < n. On each execution of the outer loop, the inner loop touches w[k]twice, once when i = k and once when i = k + 1. Immediately after the i = k iteration, the mantissas of elements w[k] and w[k-1] do not overlap, by the definition of AddTwo. Effectively, if w[k-1] and w[k] did overlap before the AddTwo, then the AddTwo transfers some mass from w[k-1] to w[k], shrinking w[k-1] so that it does not overlap with w[k]. Similarly, on the i = k + 1 iteration, w[k] might shrink as some of its mass is transferred into w[k+1]—thus shifting w[k] down so that it again overlaps with w[k-1]. The net effect (and this is where the formal proof gets messy) is to transfer mass towards higher indices, and to reduce the amount of overlap between adjacent elements of the array. This process eventually converges, in finite iterations of the outer loop, to the point that no element overlaps any other. At this point some of the lower-indexed elements may be zero, and in fact some of them *must* be zero if  $n_w$  is greater than the greatest number of possible non-overlapping mantissas in the machine (38 in the case of IEEE754 double precision). Furthermore, by the definition of AddTwo, no mass is ever discarded, so that the total sum of material in the array never changes. But once the values converge so that none of the mantissas overlap each other, and they are sorted by increasing magnitude. Furthermore, the sum of the mass in elements 1 through i-1 can have no effect on the value of element i, since every element is smaller than the ULP of the next. In other words, at convergence, each element w[i] represents a faithful sum of the elements before it. This completes the outline of the proof of Lemma A.

#### Application of Lemma A

Note that after *loop* iterations of the main loop of our main algorithm,  $x[1], x[2], \dots, x[loop]$  are all identically zero. Thus, after at most n iterations of the loop, all elements of x are zero. After this point, each iteration of the main loop similarly obliterates one value in the q array, so that q[loop - n] = 0 as well.

We apply Lemma A independently to the values  $s_p$  and  $s_n$ , to show that equation (15) eventually holds, after finite iterations of the main loop on Step 3. To apply Lemma A, we first concatenate the arrays x and q together into one array z such that  $z[1] = x[1], z[2] = x[2], \dots, z[n] = x[n], z[n+1] = q[1], z[n+2] = q[2], \dots$ .

In order for L to be unbounded,  $c_q$  must grow without bound, incrementing by one for each iteration of the outer loop. However, as we have shown in the proof of the theorem, the value of *count*, and thus the total number of non-zero elements in the arrays x and q is never greater than n. Thus, the string of non-zero elements marches along the z array, with no non-zero elements below index *loop*, and no non-zero elements beyond index  $c_q$ , where  $c_q - loop \leq count \leq n$ . Thus, we apply Lemma A to the elements z[loop+1] though  $z[loop+c_q]$ ,

#### 22 Yong-Kang Zhu and Wayne Hayes

which, finally, demonstrates that (15) is true after finite loops. So, s is the sum with a faithful rounding. Since the sum and the number of summands are finite, after enough cancellations between  $s_p$  and  $s_n$ , it can be satisfied that  $fl(s_p + s_n) = s_p$  or  $fl(s_p + s_n) = s_n$ , and both the positive sequence and the negative sequence satisfy the lemma. Claim 1 follows as a corollary.

We emphasize again that we believe that this case never occurs as long as L is large enough, although we have not yet been able to prove it.

# Implementation of Float-Float Operators on Graphics Hardware

Guillaume Da Graça, David Defour

Dali, LP2A, Université de Perpignan, 52 Avenue Paul Alduy, 66860 Perpignan Cedex, France

**Abstract.** The Graphic Processing Unit (GPU) has evolved into a powerful and flexible processor. The latest graphic processors provide fully programmable vertex and pixel processing units that support vector operations up to single floating-point precision. This computational power is now being used for general-purpose computations. However, some applications require higher precision than single precision. This paper describes the emulation of a 44-bit floating-point number format and its corresponding operations. An implementation is presented along with performance and accuracy results.

#### 1 Introduction

There is significant interest in using graphics processing units (GPUs) for general purpose programming. These GPUs have an explicitly parallel programming model and deliver much higher performance for some floating-point workloads when compared to CPUs. This explains the growing concern in using a graphic processor as a stream processor for executing highly parallel applications.

#### 1.1 The graphics pipeline

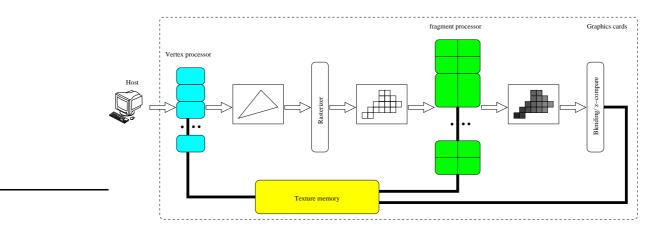

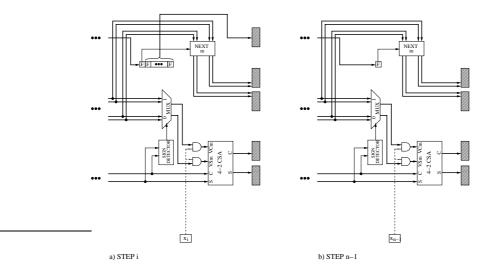

Data processed by the GPU are mainly pixel, geometric objects and elements that create the final picture in the frame buffer. These objects require an intensive computation before getting the final image. This computation is done within the "Graphics Hardware Pipeline". The pipeline contains several steps in which the 3D application sends a sequence of vertices to the GPU that are batched into geometric primitives (polygons, lines, points). These vertices are processed by the programmable vertex processor that has the ability to perform mathematical operations. Then the resulting primitives are sent to the programmable fragment processor. Fragment processors require the same mathematical operation as the vertex processors, plus some texturing operations. A representation of this pipeline is shown in figure 1.

The computational workhorse of the GPU is located within the 2 programmable processors: vertex processors and fragment processors. The amount of these processors embedded in GPUs has greatly increased over the years; for example the latest Nvidia 7800GTX chip integrates 8 vertex shaders and 24 pixel shaders. In this chip, each vertex shader is made up of 1 multiply and accumulate (MAD) unit and 1 special function unit that can compute log, exp, sin, cos. The implementation of a similar unit is detailed in [18]. Each pixel shader of the 7800GTX consists of 2 consecutive MADs, therefore the 7800GTX is able to execute 56 MAD which correspond to 112 floating-point operations in single precision per clock cycle at a peak rate.

Fig. 1. This figure illustrates the current graphics pipeline found in recent PC graphics cards.

#### 1.2 Representation formats available in GPUs

Vertex and pixel shaders were originally composed of fixed-point operators that have evolved into partial support of the IEEE-754 single precision floating-point format. For example, the Nvidia GeForce 6 series offers a 32-bit format similar to single precision. The other main GPU manufacturer, ATI, integrated a 32-bit floating-point arithmetic required by shader version 3.0 in their latest chips, the X1k series. Older ATI hardware performed floating-point operations on a 24-bit format in spite of the fact that they stored values in the IEEE standard 32-bit format as described in table 1.

| Sign | Exponent                           | Mantissa | Support for special<br>values (NaN, Inf) |

|------|------------------------------------|----------|------------------------------------------|

| 1    | ۲                                  | 10       | , , ,                                    |

|      | 5                                  | - •      | Yes<br>Yes                               |

| 1    | 8                                  |          | No                                       |

| 1    | 7                                  | - 0      | No                                       |

| 1    | 8                                  | -•       | ? / not tested                           |

|      | Sign<br>1<br>1<br>1<br>1<br>1<br>1 | 1 5      | 1 8 23+1                                 |

Table 1. Floating-point format currently supported by the Nvidia and the ATI chips.

In addition to these formats, current GPUs support other data types that are of lower precision. Therefore, applications where accuracy is paramount are not well suited for a GPU execution due to the lack of the double precision format, the non uniformity within the floating-point format and the non-respect of the IEEE-754 requirement (such as rounding or denormal number which are typically flushed to zero [6]).

The purpose of this article is to propose a software solution to the limitation of precision in floating-point operations and storage. This solution consists of an implementation of a *float-float* format which doubles the hardware accuracy. This corresponds to a 44-bit precision on Nvidia architecture.

#### 1.3 Outline of this paper

Based on the above clarification, hence section 2 presents similar work related to multiprecision operators. Section 3 describes the floating-point arithmetic available in current GPU. Section 4 proposes a representation and the algorithms for the basic multiprecision operations. Section

5 describes our initial implementation used to conduct tests and comparisons which results are discussed in section 6.

#### 2 Related work

Many modern processors obey the IEEE-754 [15] standard for floating-point arithmetic, which defines the single and double precision format. For some applications, however, the precision provided by the hardware operators does not suffice. These applications include large scale simulation, number theory and multi-pass algorithm like shading, lighting [21].

Applications encountering accuracy problems are commonly executed on a CPU. As a consequences, most of the research was done to develop a *multiprecision* format on the CPU (a representation format with a precision higher than the one available in the hardware).

#### 2.1 CPU related work

Many software libraries were proposed to address the precision issue in hardware limitation. These libraries emulate arithmetic operators with higher precision than the one provided by the hardware. They either use integer units or floating-point units, depending on the internal representation of their number.

Libraries based on an integer representation All the libraries in this category, internally represent multiprecision numbers as an array of integers, which are machine numbers (usually 32-bit or 64-bit) to store the significant of the multiprecision numbers. It is the case for GMP [9], on top of which several other libraries are built (see MPFR [2]). These libraries allow the user to dynamically set the precision of the operation during the execution of the program. However some other libraries [1, 7] set the precision at compilation time to get higher performance.

Libraries based on a floating-point representation The actual trend of CPUs is to have highly optimized floating-point operators. Some libraries, such as the MPFUN [3], exploit these floating-point operators by using an array of floating-point numbers.

Other libraries represent multiprecision numbers as the unevaluated sum of several doubleprecision FP numbers such as Briggs' double-double [4], Bailey's quad-doubles [13] and Priest's floating-point expansions [19]. This representation format is based on the IEEE-754 features that lead to simple algorithms for arithmetic operators. However this format is confined to low precision (2 to 3 floating-point numbers) as the complexity of algorithms increases quadratically with the precision.

#### 2.2 GPU related work

The available precision provided through the GPU's graphical pipeline is limited; for example the color channel is usually represented with a 8-bit number. Before the introduction of the shader 3.0 that requires support of 32-bit floating-point numbers, developers and researchers that were facing accuracy problems developed software solutions to extend the hardware precision.

For example, Strzodka [21] proposed a 16-bit fixed-point representation and operation out of the 8-bit fixed-point format. In his work, two 8-bit numbers were used to emulate 16-bit.

The author claimed that operators in his representation format were only 50% slower than normal operators, however no measured timings were provided. Strzodka recently implemented a solvers for Finite Element simulations in double precision on GPU [11], nevertheless double precision computation were sent to the CPU. This method involves time consuming memory transfer.

#### 3 Floating-point arithmetic on GPUs

Floating-point computations on GPUs are often called into question. Current GPUs do not strictly conform to the IEEE-754 floating-point standard. This produces differences between the same computation performed on the GPU and the CPU, and among GPUs themselves. Floating-point computation details vary with GPU models and they are kept secret by GPU manufacturers.

Recently, one tool has been developed to understand some of the details of the floatingpoint arithmetic for a given GPU [14]. We executed this tool on GPUs, which is an adaptation of Paranoia, and got some resulting errors reported in table 2. This tools is only available as an executable with poor documentation so these data should be taken with caution and real bounds may be larger. We will assume in the rest of this paper that these bounds hold for all possible inputs.

| Operation      | Exact       | Chopped | R300            | NV35            |

|----------------|-------------|---------|-----------------|-----------------|

|                | rounding    |         |                 |                 |

| Addition       | [-0.5, 0.5] | (-1, 0] | [-1.0, 0.0]     | [-1.0, 0.0]     |

| Subtraction    | [-0.5, 0.5] | (-1, 1) | [-1.0, 1.0]     | [-0.75, 0.75]   |

| Multiplication | [-0.5, 0.5] | (-1, 0] | [-0.989, 0.125] |                 |

| Division       | [-0.5, 0.5] | (-1, 0] | [-2.869, 0.094] | [-1.199, 1.375] |

Table 2. Floating-point error in ulp from the execution of the paranoia Test [14]

Table 2 shows us that the addition is truncated after the last bit on both ATI R300 and Nvidia NV35. This software tells us that the subtraction is done with an extra bit (guard bit) on Nvidia processors and not on ATI. This property is very important for numerical algorithms as we will see later on in this paper. The error of the multiplication is strictly lower than one ulp (faithfully rounded) on both the ATI and the Nvidia. Because GPUs do not provide a division instruction, every division is performed as a reciprocal followed by a multiplication; thereby the floating-point error for the division incurs double floating-point errors.

#### 4 Proposed format

The proposed format is an adaptation of the double-double format described in [4]. For our algorithm we chose to represent multiprecision numbers as the unevaluated sum of 2 floating-point numbers handled in hardware. The type of hardware representation used is described in Table 1.

In the core of the GPU, the graphical pipeline is made up of several computational units. These processing units are not designed to efficiently perform tests and comparisons, therefore whenever it is possible, we should avoid tests even at the expense of extra computations. In addition, software that does not use branches remains compatible with older GPU. In our case, two versions of Add12 algorithms exist [20]; one with one test and another one, that should be preferred, with 3 extra floating-point operations.

#### 4.1 Mathematical background

In this section we present some basic properties and algorithms of the IEEE floating-point arithmetic used in our format. In this paper we assume that GPUs have a guard bit for the addition/subtraction with a truncation as rounding mode as it seems to be the case with latest Nvidia chips. We will consider single precision number. The multiplication will behave as observed in section 3. This assumption conforms to the actual trends follow by the GPU and the shader model 3.0. For any mathematical operator +, -, \*, /, we use  $\oplus, \oplus, \otimes, \otimes$  to represent the hardware operator that may involve a rounding error.

**Theorem 1 (Sterbenz lemma ([12] Th. 11)).** If subtraction is performed with a guard digit, and  $y/2 \le x \le 2y$ , then  $x \ominus y$  is computed exactly.

**Theorem 2 (Add12 theorem (Knuth [16])).** Let a and b be normalized floating-point numbers. The following algorithm computes  $s = a \oplus b$  and r = (a+b)-s such that s+r = a+b exactly, provided that no exponent overflow or underflow occurs.

```

\begin{array}{lll} Add12(a, b)\\ s &= a \oplus b\\ v &= s \oplus a\\ r &= (a \oplus (s \oplus v)) \oplus (b \oplus v)\\ return & (s, r) \end{array}

```

*Proof.* The proof of correctness of the Add12 algorithm, in an environment with a correctly rounded arithmetic, is described in Knuth [16] or Shewchuk [20] articles. However, by examining these proofs, one can observe that they are based on Sterbenz lemma. This lemma only requires a guard bit to be true, therefore the Add12 theorem is true on Nvidia hardware.  $\Box$

**Theorem 3 (Split theorem (Dekker [8])).** Let a be p-bit floating-point number, where  $p \geq 3$ . Choose a splitting point s such that  $p/2 \leq s \leq p-1$ . Then the following algorithm will produce a (p-s)-bit value  $a_{hi}$  and a non-overlapping (s)-bit value  $a_{lo}$  such that  $|a_{hi}| \geq |a_{lo}|$  and  $a = a_{hi} + a_{lo}$ .

SPLIT(a)  $1 c = (2^{s} \oplus 1) \otimes a$   $2 a_{big} = c \ominus a$   $3 a_{hi} = c \ominus a_{big}$   $4 a_{lo} = a \ominus a_{hi}$   $5 return (a_{hi}, a_{lo})$

*Proof.* This proof is an adaptation of the proof from [20] to fit the condition observed on GPUs. Line 1 is equivalent to computing  $2^{s}a \oplus a$ , because multiplying by a power of two only changes its exponent. The addition is subject to rounding, so we have  $c = 2^{s}a + a + err(2^{s}a \oplus a)$ . Line 2 is subject to rounding, so  $a_{big} = 2^{s}a + err(2^{s}a \oplus a) + err(c \oplus a)$ . Both  $|err(2^{s}a \oplus a)|$  and  $|err(c \oplus a)|$  are bounded by ulp(c), so the exponent of  $a_{big}$  can only be larger than that of  $2^{s}a$  if every bit of the significant of a is nonzero except the last two bits. By manually checking the behavior of SPLIT in these 4 cases, one can verify that the exponent of  $a_{big}$  is

never larger than that of  $2^{s}a$ . Then  $|err(c \ominus a)| \leq ulp(2^{s}a)$ , and so the error term  $err(c \ominus a)$  is expressible in s bits.

By Sterbenz lemma line 3 and 4 are calculated exactly. It follows that  $a_{hi} = a - err(c \ominus a)$ and  $a_{lo} = err(c \ominus a)$ ; the latter is expressible in s bits. Either  $a_{hi}$  has the same exponent as a either  $a_{hi}$  has an exponent one greater than that of a and in both case  $a_{hi}$  is expressible in p - s bits.

**Theorem 4 (Mul12 theorem (Dekker [8])).** Let a and b be normalized floating-point numbers. The following algorithm produces two floating point numbers x and y as results such that  $a \cdot b = x + y$ , where x is an approximation to  $a \cdot b$  and y represents the roundoff error in the calculation of x.

```

\begin{array}{l} Mul12(a,b)\\ 1 \ x = a \otimes b\\ 2 \ (a_{hi}, a_{lo}) = SPLIT \ (a)\\ 3 \ (b_{hi}, b_{lo}) = SPLIT \ (b)\\ 4 \ err1 = x \ominus (a_{hi} \otimes b_{hi})\\ 5 \ err2 = err1 \ominus (a_{lo} \otimes b_{hi})\\ 6 \ err3 = err2 \ominus (a_{hi} \otimes b_{lo})\\ 7 \ y = (a_{lo} \otimes b_{lo}) \ominus err3\\ 8 \ return \ (x,y) \end{array}

```

*Proof.* Line 1 computes  $x = ab + err(a \otimes b)$  with  $err(a \otimes b)$  the rounding error of the multiplication. One can noticed that all the other multiplications and subtractions are exact and compute  $y = -err(a \otimes b)$ .

**Theorem 5 (Add22 theorem).** Let ah + al and bh + bl be the float-float arguments of the following algorithm:

The two floating-point numbers rh and rl returned by the algorithm verify

$rh + rl = (ah + al) + (bh + bl) + \delta$

Where  $\delta$  is bounded as follows:

$\delta \le \max(2^{-24} \cdot |al + bl|, 2^{-44} \cdot |ah + al + bh + bl|)$

**Theorem 6 (Mul22 theorem).** Let ah + bl and bh + bl be the float-float arguments of the following algorithm:

The result rh + rl returned by the algorithm verify

$$rh + rl = ((ah + al) * (bh + bl)) * (1 + \epsilon)$$

Where  $\epsilon$  is bounded as follows:

$$|\epsilon| \le 2^{-44}$$

*Proof.* The detailed proof of the Add22 and the Mul22 theorem were proposed by Lauter in [17] for the particular cases of double-double format on an IEEE compliant architecture. The proof of these 2 theorems with GPU conditions (single precision, faithful rounding and guard bit) is very similar and is therefore not detailed here for the sake of brevity.  $\Box$

#### 5 Implementation

We developed a Brook [5] implementation of the float-float format and of Add12, Add22, Split, Mul12, Mul22 algorithms. Brook is a high level programming language designed for general purpose programming on GPUs. This language allows us to test our algorithms with ease over various systems, drivers and graphics hardware with minor modifications.