### Parallelizing Queue Compiler

by

Arquimedes Canedo

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Engineering

Graduate School of Information Systems University of Electro-Communications Tokyo, Japan

September 2008

### Parallelizing Queue Compiler

by

Arquimedes Canedo

Approved by Supervisory Committee:

Member: Prof. Masahiro Sowa Prof. Masanori Idesawa Prof. Toshihiko Kato Asoc. Prof. Tsutomu Yoshinaga Asoc. Prof. Tsuneyasu Komiya Asoc. Prof. Masaaki Kondo Copyright 2008 by Arquimedes Canedo

All rights reserved

To Petty Monster

#### Abstract

キュープロセッサは、中間結果格納用にFIFOレジスタを持っており、キュー内のデータは キューの先頭から取り出され、データの入力は、キューの末尾にされる。この計算モデル は、従来のランダムアクセスを用いるレジスタマシンやスタックマシンとは異なるもので あるため、現用のコンパイラと同様のコード生成方法を適用する事は不可能である。本論 文では、初めて実用に近いコードをコンパイルすることができるようになったキュープロ セッサ用並列コンパイラの設計及び開発手法について述べるものである。

本キュープロセッサ用並列コンパイラは、C言語で書かれた任意のプログラムを、キュー プロセッサの機械語に変換する。キューコンパイラでは、全てのコード生成段階において キュー計算モデルに沿ってコードを生成しなければならないので、従来のコンパイラとは 異なる構造と手続きを必要とする。そのため内部構造は、従来のコンパイラとは大幅に異 なる構造になっている。

本コンパイラではプログラムのコントロールフロー及びデータフローグラフを構成し、 それをキューコード生成に適したQTreeに変換し、そこから幅優先トラバース用のLeveled DAGを生成する。次に、オフセットの計算を行うため、グラフの解析と変換を行い、最後 に、ターゲットとなるキューマシンへのコード生成を幅優先トラバースによって行う。こ れらの手続きの多くは未知のものであったため、様々な問題を解決するために新しく効率 的なアルゴリズムとデータ構造の開発を行った。

本コンパイラでは目的のプロセッサの要求にあうように、コードサイズ、並列性、性 能、オフセット最適化、キューサイズといった目的を指定したコードを生成する方法を同 時に開発した。

本コンパイラは成功裏に完成し、自身のコードを含め、任意のプログラムをコンパイル しキューオブジェクトコードを出力するコンパイラとなった。出力されたコードの質は、 従来のコンパイラの命令数、命令種の分布と似たようなものになり、並列性、コードサイ ズに関しては従来の結果を上回るものとなった。

#### Abstract

Queue processors arrange high-speed registers in a first-in first-out queue. All read accesses are performed in the head of the queue and all writes at the tail. This computation model is substantially different from conventional random access register machines and stack machines. Traditional code generation methods cannot be applied to queue machines, therefore, this doctoral dissertation presents the design and development of a parallelizing queue compiler framework. The queue compiler translates any program written in C language into queue processor's machine code. The most important characteristic of the queue compiler is the integration of the queue computing principle in all stages of code generation, making it the first available true queue compiler. Novel and efficient algorithms and data structures have been developed to facilitate and solve all the problems related to compilation for the queue model. This work is the result of two years of research and development, and it provides efficient solutions to a broad range of problems on queue computing including the principles of compiler development, automatic code generation, offset calculation, scheduling, parallelization, optimization, data allocation, and constrained compilation. Internally, the queue compiler is completely different to any other existing compiler, this due to the special characteristics of queue computing. First, control flow and data flow graphs of the input program are generated. Then a set of custom analyses and transformations are performed to compute the offset reference values. Finally, the data flow graph is scheduled in a level-order manner to generate the final instruction sequence for the target queue machine. The compiler is also capable of producing code for a set of objective functions such as code size, high parallelism, high performance, offset reference control, and queue control. The queue compiler has been successfully completed and any program, including itself, can be compiled into queue object code. Quantitatively and qualitatively, the generated queue programs are similar to the ones generated by conventional register compilers in terms of number of instructions, parallelism, code size, and instruction distribution.

## Table of Contents

| 1        | Intr | oducti  | on                                                         | 11 |

|----------|------|---------|------------------------------------------------------------|----|

|          | 1.1  | Main    | Objectives                                                 | 13 |

|          | 1.2  | Relate  | ed Work to Queue Machines                                  | 13 |

|          | 1.3  | Organ   | ization of this Dissertation                               | 16 |

| <b>2</b> | Que  | eue Co  | mputation Model                                            | 17 |

|          | 2.1  | Differe | ences with Conventional Computation Models                 | 17 |

|          | 2.2  | Code    | Generation for Queue Machines                              | 18 |

|          |      | 2.2.1   | Consumers-Producers Data Ordering Problem                  | 19 |

|          | 2.3  | Queue   | Computation Model Taxonomy                                 | 20 |

|          |      | 2.3.1   | Producer-Consumer Order Queue Computation Model (PC-QCM) . | 21 |

|          |      | 2.3.2   | Consumer Order Queue Computation Model (C-QCM)             | 22 |

|          |      | 2.3.3   | Producer Order Queue Computation Model (P-QCM)             | 24 |

| 3        | Pro  | ducer   | Order Queue Compiler Framework                             | 29 |

|          | 3.1  | Target  | Queue-based Architecture                                   | 29 |

|          |      | 3.1.1   | Offset Referenced Instructions Classification              | 31 |

|          | 3.2  | Comp    | iler Framework Design and Implementation                   | 32 |

|          |      | 3.2.1   | QTree Generation                                           | 33 |

|          |      | 3.2.2   | Queue Code Generation                                      | 36 |

|          |      | 3.2.3   | Offset Calculation                                         | 39 |

|          |      | 3.2.4   | Instruction Scheduling                                     | 43 |

|          |      | 3.2.5   | Assembly Generation                                        | 44 |

|          |      | 3.2.6   | Application Binary Interface (ABI)                         | 46 |

|   | 3.3 | Funct   | ionality                                                           | 50  |

|---|-----|---------|--------------------------------------------------------------------|-----|

|   |     | 3.3.1   | Self-Hosted Compiler                                               | 51  |

|   |     | 3.3.2   | Lower Bound Execution Time (LBET)                                  | 52  |

|   | 3.4 | Frame   | ework Complexity Evaluation                                        | 54  |

|   |     | 3.4.1   | Lines of Code Complexity                                           | 54  |

|   |     | 3.4.2   | Compile-time Complexity                                            | 55  |

| 4 | Cor | nstrain | t-Driven Compilation                                               | 57  |

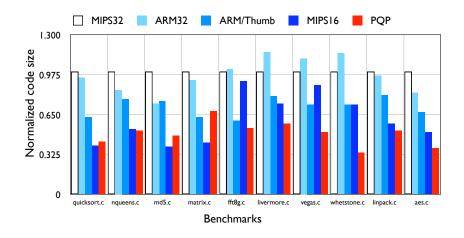

|   | 4.1 | Code    | Size-aware Compilation                                             | 58  |

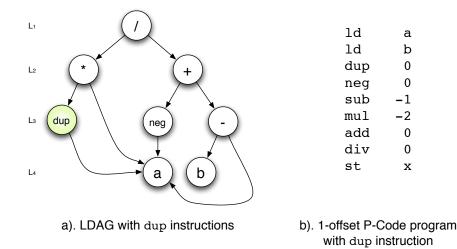

|   |     | 4.1.1   | 1-offset P-Code                                                    | 59  |

|   |     | 4.1.2   | Code Size Reduction-aware Code Generation                          | 60  |

|   |     | 4.1.3   | Code Size Reduction Evaluation                                     | 65  |

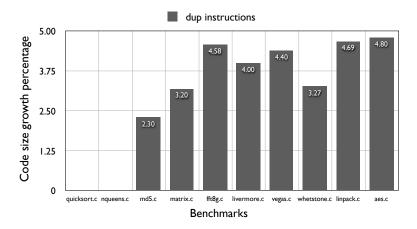

|   |     | 4.1.4   | Effect of dup instructions on Code Size                            | 66  |

|   |     | 4.1.5   | Discussion on Variable-length Instruction Set                      | 68  |

|   |     | 4.1.6   | Conclusion                                                         | 69  |

|   | 4.2 | Queue   | e Register File Optimization                                       | 70  |

|   |     | 4.2.1   | Related Work                                                       | 71  |

|   |     | 4.2.2   | Target Architecture: QueueCore processor                           | 72  |

|   |     | 4.2.3   | Algorithm for Queue Register File Constrained Compilation $\ldots$ | 73  |

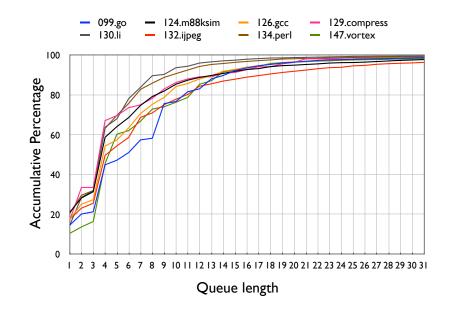

|   |     | 4.2.4   | Evaluation of Queue Register File Constrained Compilation          | 80  |

|   |     | 4.2.5   | QueueCore Processor Evaluation                                     | 86  |

|   |     | 4.2.6   | Conclusion                                                         | 88  |

|   | 4.3 | Classi  | c Optimization: Common Subexpression Elimination                   | 90  |

|   |     | 4.3.1   | Implementation of CSE in Queue Compiler                            | 91  |

|   |     | 4.3.2   | Effects of CSE on Queue Programs                                   | 92  |

|   |     | 4.3.3   | Evaluation                                                         | 94  |

|   |     | 4.3.4   | Conclusion                                                         | 98  |

|   | 4.4 | ILP C   | Optimization: Statement Merging Transformation                     | 100 |

|   |     | 4.4.1   | Algorithm                                                          | 101 |

|   |     | 4.4.2   | Evaluation                                                         | 104 |

|   |     | 4.4.3   | Conclusion                                                         | 105 |

| <b>5</b>     | Que | eue All | ocation:     | reducing    | g memory           | y traffic ir  | ı producer | order  | queue |   |

|--------------|-----|---------|--------------|-------------|--------------------|---------------|------------|--------|-------|---|

|              | mac | thines  |              |             |                    |               |            |        | 106   | ; |

|              | 5.1 | Shared  | Main Mer     | nory Con    | municatio          | n Method .    |            |        | 108   | 3 |

|              |     | 5.1.1   | Intra-block  | k Commu     | nication .         |               |            |        | 108   | ; |

|              |     | 5.1.2   | Inter-block  | k Commu     | nication .         |               |            |        | 110   | ) |

|              | 5.2 | Operar  | nd Queue f   | or Reduci   | ing Memor          | y Traffic in  | Queue Prog | rams . | 111   | - |

|              |     | 5.2.1   | Semantics    | of dup in   | struction .        |               |            |        | 113   | } |

|              |     | 5.2.2   | Algorithm    | for inser   | ting <b>dup</b> in | structions    |            |        | 114   | F |

|              |     | 5.2.3   | Using que    | ue for inte | er-block pa        | assed variab  | les        |        | 116   | ì |

|              |     | 5.2.4   | Enabling •   | Compiler    | Support .          |               |            |        | 117   | 7 |

|              | 5.3 | Evalua  | tion         |             |                    |               |            |        | 118   | 3 |

|              |     | 5.3.1   | Memory 7     | Traffic Red | luction .          |               |            |        | 119   | ) |

|              |     | 5.3.2   | Expense o    | of dup inst | tructions for      | or offset con | strain     |        | 119   | ) |

|              | 5.4 | Conclu  | sion         |             |                    |               |            |        | 121   | - |

| 6            | Que | eue Cor | nputing I    | Evaluatio   | on                 |               |            |        | 122   | 2 |

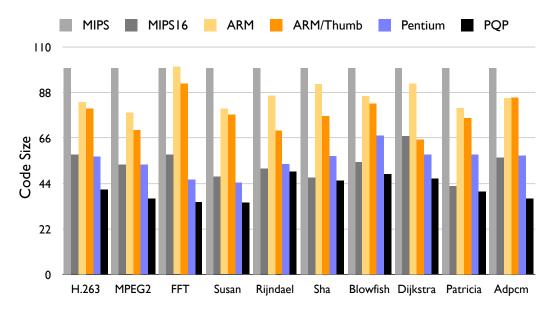

|              | 6.1 | Code S  | Size Compa   | arison      |                    |               |            |        | 122   | ) |

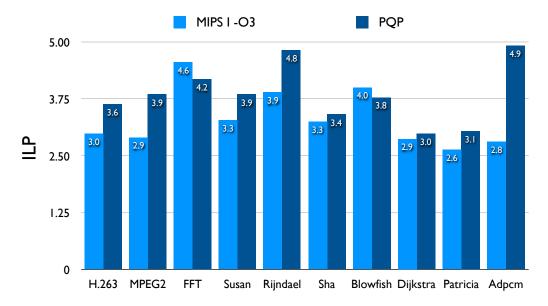

|              | 6.2 | Compi   | le-time Ext  | tracted IL  | P Compar           | rison         |            |        | 123   | } |

| 7            | Con | clusion | 1            |             |                    |               |            |        | 125   | , |

| $\mathbf{A}$ | P-C | ode In  | struction    | Set Arc     | hitecture          |               |            |        | 128   | 3 |

|              | A.1 | Notatio | on           |             |                    |               |            |        | 128   | 3 |

|              | A.2 | Arithm  | netic & Log  | gic Instruc | ctions             |               |            |        | 129   | ) |

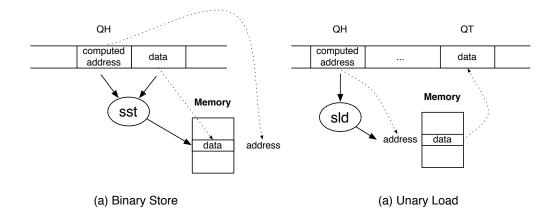

|              | A.3 | Memor   | y Instructi  | ions        |                    |               |            |        | 129   | ) |

|              |     | A.3.1   | Efficient A  | Addressing  | g Method f         | for Queue P   | rocessors  |        | 130   | ) |

|              | A.4 | Compa   | arison Instr | ructions .  |                    |               |            |        | 132   | ) |

|              | A.5 | Contro  | l Flow Inst  | tructions   |                    |               |            |        | 133   | } |

|              | A.6 | Data T  | Type Conve   | ersion Inst | tructions .        |               |            |        | 134   | F |

|              | A.7 | Special | l Instructio | ons         |                    |               |            |        | 134   | F |

|              | A.8 | Queue   | Control In   | structions  | 3                  |               |            |        | 134   | F |

|              | Bib | liograp | hy           |             |                    |               |            |        | 136   | ; |

| List of Publications | 146 |

|----------------------|-----|

| Author Biography     | 149 |

| Acknowledgments      | 150 |

# List of Figures

| 2.1 | Code generation for queue machines consist of: (a) traversing the DAG                       |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | in level-order manner, (b) obtain the instruction sequence of the queue                     |    |

|     | program, and (c) executing the program in the queue                                         | 20 |

| 2.2 | Producer-consumer model (PC-QCM) strictly uses $\mathtt{QH}$ and $\mathtt{QT}$ for reading  |    |

|     | and writing                                                                                 | 22 |

| 2.3 | Transforming a DAG into a Level-planar DAG                                                  | 22 |

| 2.4 | Consumer model (C-QCM) gives flexibility in writing but the reading                         |    |

|     | location remains fixed at QH                                                                | 23 |

| 2.5 | Consumer model (C-QCM) execution                                                            | 24 |

| 2.6 | Producer order model (P-QCM) gives flexibility in reading data but the                      |    |

|     | writing location remains fixed at QT. $\ldots$                                              | 24 |

| 2.7 | Producer Order model (P-QCM) execution                                                      | 25 |

| 2.8 | Comparison between (a) original directed acyclic graph, (b) PC-QCM level-                   |    |

|     | planar model, (c) P-QCM model                                                               | 27 |

| 3.1 | Queue compiler block diagram                                                                | 34 |

| 3.2 | High-level intermediate representation. (a) C fragment, (b) C-like GIM-                     |    |

|     | PLE representation, (c) GIMPLE representation                                               | 35 |

| 3.3 | QTrees. (a) C-like Qtree representation, (b) QTree representation using                     |    |

|     | low level generic queue instructions                                                        | 36 |

| 3.4 | Leveled DAG for expression $a[i] = (\&a + (i * sizeof(a))) * (x + y) \dots$                 | 37 |

| 3.5 | $\mathtt{QH}$ relative position for all binary and unary operations in a LDAG $\ . \ . \ .$ | 41 |

| 3.6 | QIR representation                                                                          | 46 |

| 3.7 | QueueCore assembly output                                                                   | 47 |

| 3.8  | Stack Frame Layout                                                                                                                                  | 48 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

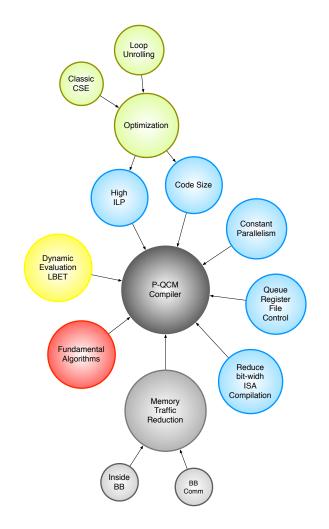

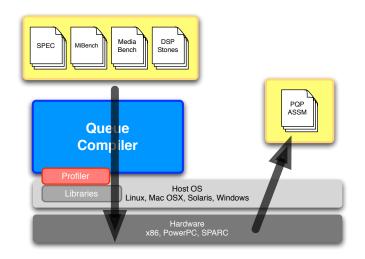

| 3.9  | Framework's functionality. Related techniques grouped by color                                                                                      | 52 |

| 3.10 | Cross-compiler configuration                                                                                                                        | 53 |

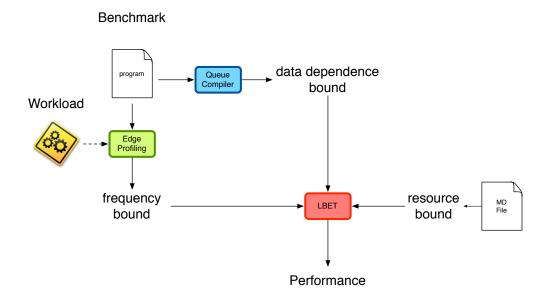

| 3.11 | Lower Bound Execution Time (LBET) model                                                                                                             | 54 |

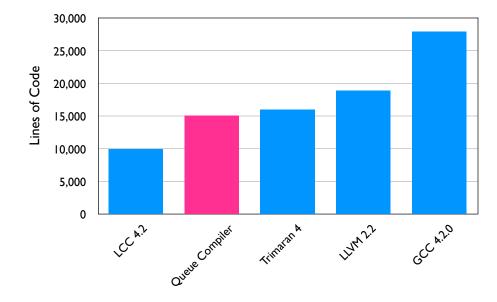

| 3.12 | Lines of Code complexity of five compiler back-ends                                                                                                 | 55 |

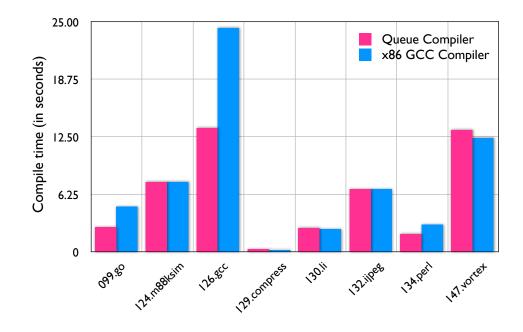

| 3.13 | Compile Time Compiler                                                                                                                               | 56 |

| 4.1  | 4-point Fourier transform directed acyclic graph                                                                                                    | 60 |

| 4.2  | Fourier transform's directed acyclic graph with dup instructions                                                                                    | 61 |

| 4.3  | Leveling of QTree into augmented LDAG for expression $x = \frac{a \cdot a}{-a + (b-a)}$                                                             | 64 |

| 4.4  | 1-offset constrained code generation from a LDAG                                                                                                    | 66 |

| 4.5  | Code size evaluation of 1-offset P-Code technique                                                                                                   | 67 |

| 4.6  | Overhead of dup instructions.                                                                                                                       | 68 |

| 4.7  | Queue size requirements. The graph quantifies the amount of queue                                                                                   |    |

|      | required to execute statements in SPEC CINT95 benchmarks. A point,                                                                                  |    |

|      | (x, y), denotes that $y%$ of the statements in the program require x, or less,                                                                      |    |

|      | queue words to evaluate the expression                                                                                                              | 71 |

| 4.8  | Queue length is determined by the width of levels and length of soft edges.                                                                         | 74 |

| 4.9  | Output of the labeling phase of the clusterization algorithm $\ldots \ldots \ldots$                                                                 | 76 |

| 4.10 | Output of the clusterization algorithm. Spill nodes marked in gray circles                                                                          |    |

|      | and reload operations in rectangles                                                                                                                 | 78 |

| 4.11 | Cluster Dependence Graph (CDG)                                                                                                                      | 80 |

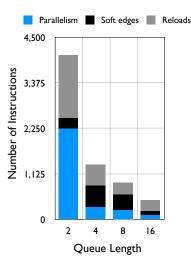

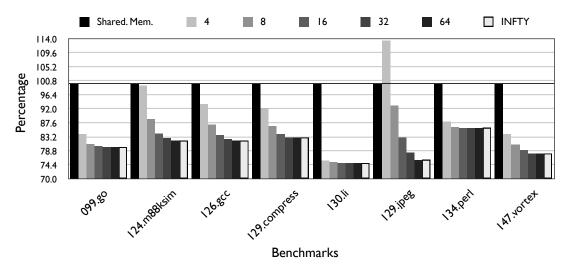

| 4.12 | Normalized instruction count measurement for different lengths of queue,                                                                            |    |

|      | $threshold = 2, 4, 8, 16, INFTY. \dots \dots$ | 82 |

| 4.13 | Spill code distribution of 124.m88ksim benchmark                                                                                                    | 83 |

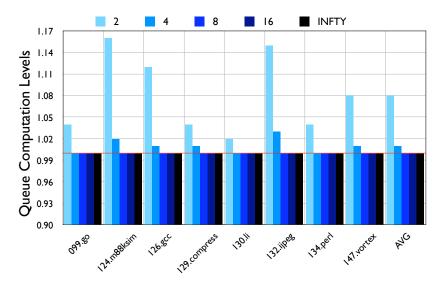

| 4.14 | Queue computation levels in the programs' data flow graph as an estimation                                                                          |    |

|      | of static execution time.                                                                                                                           | 84 |

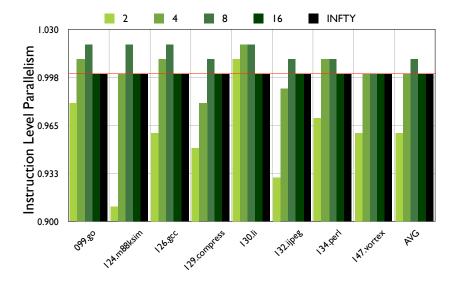

| 4.15 | Degree of instruction level parallelism for constrained compilation for                                                                             |    |

|      | different sizes of queue register file                                                                                                              | 85 |

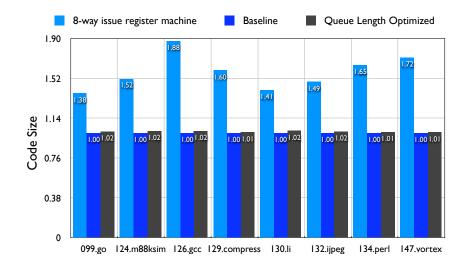

| 4.16 | Normalized size of the text segment for a conventional register machine                                                                             |    |

|      | and the QueueCore                                                                                                                                   | 88 |

#### LIST OF FIGURES

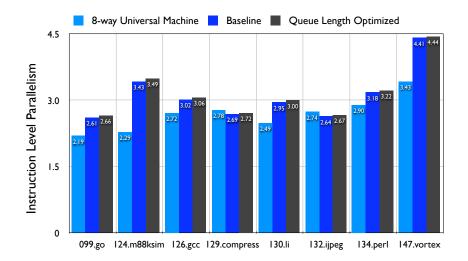

| 4.17 | Exposed instruction level parallelism by an ILP compiler for a conventional             |

|------|-----------------------------------------------------------------------------------------|

|      | multiple issue machine, and for the QueueCore without and with queue-                   |

|      | length optimization                                                                     |

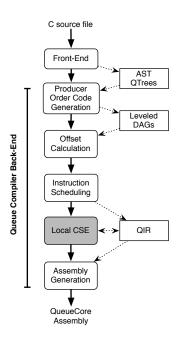

| 4.18 | Queue Compiler Block Diagram                                                            |

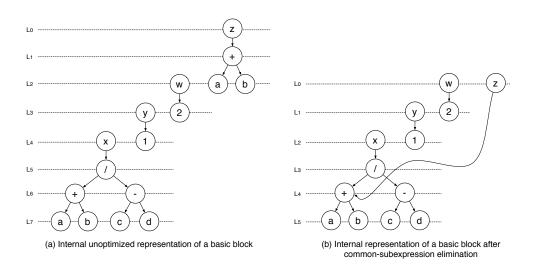

| 4.19 | Queue compiler's representation of basic block. (a) Original representation.            |

|      | (b) After common-subexpression elimination the redundant computation is                 |

|      | removed, the number of execution levels decreases, and an edge is stretched. $93$       |

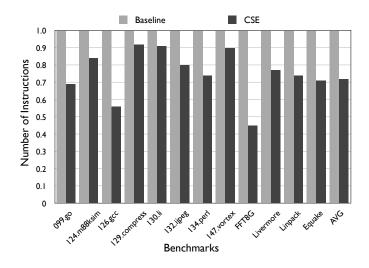

| 4.20 | Instruction count reduction                                                             |

| 4.21 | Computation levels reduction                                                            |

| 4.22 | Instruction level parallelism                                                           |

| 4.23 | Offsetted instructions distribution for scalar and numerical benchmarks $98$            |

| 4.24 | Statement merging transformation                                                        |

| 4.25 | Statement merging example                                                               |

| 4.26 | Merged statement with a height of $5+3 = 8$                                             |

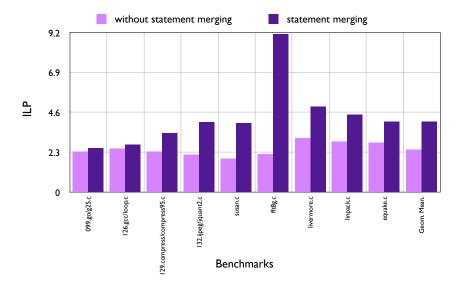

| 4.27 | Effects of statement merging transformation on compile-time ILP $\ . \ . \ . \ . \ 104$ |

| 4.28 | Queue utilization on peak parallelism                                                   |

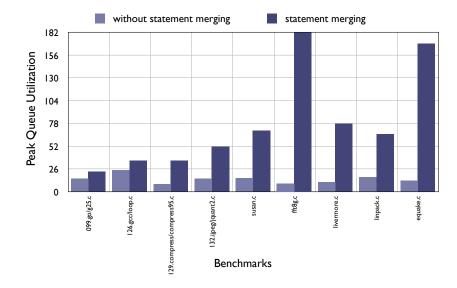

| 5.1  | Effect of compilation scope on offset characteristics. (a) sample basic                 |

|      | block, (b) resulting program of statement-based compilation scope with a                |

|      | maximum offset of $-2$ , and (c) resulting program of basic block compilation           |

|      | scope with a maximum offset of $-6109$                                                  |

| 5.2  | Maximum offset reference value for statement-based and basic block                      |

|      | compilation scopes                                                                      |

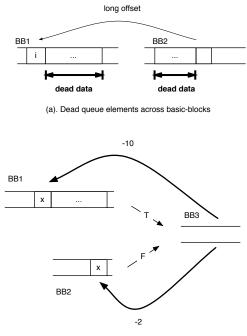

| 5.3  | Problems of sharing data in the queue across basic blocks. (a) long offset              |

|      | references of live variables across basic blocks produce large amounts of               |

|      | dead data. (b) BB3 faces an offset inconsistency problem since the correct              |

|      | offset value depends on runtime behavior and cannot be determined at                    |

|      | 1                                                                                       |

|      | compile-time                                                                            |

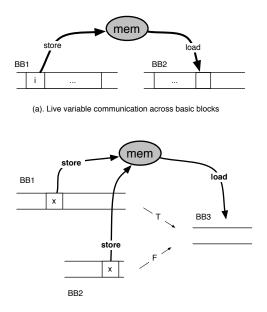

| 5.4  | Shared main memory for basic block communication. (a) long offsets and                  |

| 5.4  |                                                                                         |

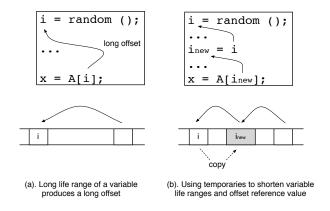

| 5.5  | Offset reduction by in-queue copies: (a) original program with long offset,                |  |  |

|------|--------------------------------------------------------------------------------------------|--|--|

|      | (b) compiler inserted copies to shorten offset references                                  |  |  |

| 5.6  | Semantics of dup instruction do not affect other instructions offset references.114        |  |  |

| 5.7  | Chain of $\mathtt{dup}$ instructions fit any offset reference into the threshold value 115 |  |  |

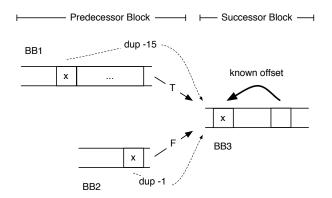

| 5.8  | Insertion of dup at the end of blocks solves the problem of offset                         |  |  |

|      | inconsistency for the successor blocks and allows the communication of                     |  |  |

|      | frequently used variables in the queue                                                     |  |  |

| 5.9  | Block diagram of the queue compiler                                                        |  |  |

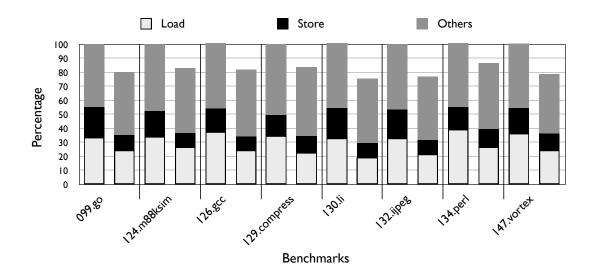

| 5.10 | Memory traffic reduction. For every benchmark the first column represents                  |  |  |

|      | the program compiled shared-memory communication model, and the                            |  |  |

|      | second column represents the program compiled with the new queue-based                     |  |  |

|      | communication model                                                                        |  |  |

| 5.11 | Overhead of dup instructions for different threshold values                                |  |  |

| 6.1  | Code Size Comparison                                                                       |  |  |

| 6.2  | Compile-time extracted instruction level parallelism                                       |  |  |

| A.1  | Semantics of the new memory instructions                                                   |  |  |

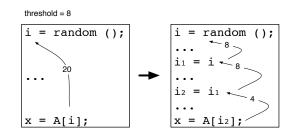

| A.2  | Level order traversal of parse tree with array address calculation 132                     |  |  |

| A.3  | Level order traversal of parse tree with array address calculation 133                     |  |  |

|      |                                                                                            |  |  |

## List of Tables

| 2.1 | Characteristics of queue computation model compared to conventional                             |    |

|-----|-------------------------------------------------------------------------------------------------|----|

|     | register and stack models                                                                       | 19 |

| 2.2 | C-QCM and P-QCM program characteristics for Livermore loops $\ \ldots \ \ldots$                 | 26 |

| 2.3 | Code Size and Depth of Application Graphs Comparison $\ . \ . \ . \ .$ .                        | 28 |

| 3.1 | Generic queue instructions                                                                      | 30 |

| 3.2 | Data type and sign information                                                                  | 31 |

| 3.3 | Examples of producer-order instructions                                                         | 32 |

| 3.4 | QIR specification                                                                               | 45 |

| 3.5 | Compiler complexity by compile-time analysis $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 56 |

| 4.1 | Distribution of PQP offsetted instructions for a set of embedded and                            |    |

|     | numerical applications.                                                                         | 59 |

| 4.2 | Characteristics of programs that affect the queue length in queue-based                         |    |

|     | computers                                                                                       | 72 |

| 4.3 | Estimation of constrained compilation complexity measured as compile-                           |    |

|     | time for the SPEC CINT 95 benchmark programs with threshold set to                              |    |

|     | two                                                                                             | 81 |

| 4.4 | Extra spill instructions and total number of instructions for QueueCore                         |    |

|     | and a conventional 8-way issue machine.                                                         | 87 |

# List of Algorithms

| 1  | dag_levelize (tree $t$ , level) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 39$                                                                          |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2  | qh_pos (LDAG $w$ , node $u$ )                                                                                                                                                |

| 3  | OffsetCalculation (LDAG $W$ )                                                                                                                                                |

| 4  | $prologue() \dots \dots$                                               |

| 5  | epilogue()                                                                                                                                                                   |

| 6  | dag_levelize_ghost (tree $t$ , level) $\ldots \ldots \ldots$ |

| 7  | 10ffset_codegen ()                                                                                                                                                           |

| 8  | dup_assignment $(i)$                                                                                                                                                         |

| 9  | labelize (LDAG $W$ )                                                                                                                                                         |

| 10 | clusterize (node $u$ , LDAG $W$ )                                                                                                                                            |

| 11 | stmt_merge $(B)$                                                                                                                                                             |

| 12 | merge $(S1, S2, a1, b1, a2, b2)$                                                                                                                                             |

| 13 | queue_communication (BB, threshold)                                                                                                                                          |

### Chapter 1

### Introduction

A compiler is a computer program that translates one computer language (source language) into another computer language (target language). Most of compilers translate a high-level programming language into machine language program called the object code. The goal of high-level programming languages is to hide the details of the microprocessor in a set of abstract, easy to use concepts to make complex programming simpler. Sophisticated programs such as operating systems and modern applications rely on high-level programming languages to facilitate their development, to reduce implementation time, and to avoid error-prone assembly programming. Compilers are a very important layer in the computer systems stack as they translate application code into machine code with comparable, or better, performance than hand-coded assembly.

Queue computing is a computation model that has not received much attention since the invention of microprocessors. A queue-based processor uses a first-in firstout queue to store and retrieve values for data processing. This model is analogous to conventional computers based on the concept of random access registers, or stack. In principle, register, stack, and queue architectures are implementations of sequential von Neumann architectures. To increase the performance of these kind of processors engineers have found ways to execute instructions in parallel. Microarchitectural techniques such as pipelining and multiple execution units have been developed to extract instructionlevel parallelism in a single processor. However, the fundamental characteristics of each model complicate or facilitate the parallelization of instructions in different degrees. The stack model, for example, uses the top of the stack to perform reads and writes and makes parallelization a challenging problem in the hardware and in the compiler. Compilers for superscalar and VLIW register must perform complex and sophisticated transformations to extract parallelism from the compiled programs. On the other hand, queue computing model allows parallelism to be easily extracted, yet no previous research has been conducted to understand the automatic compilation of programs for queue machines, and no compiler has been developed. Some previous attempts were made to use a conventional compiler and translate register-based code into queue code. These works made clear that conventional compilation techniques for register machines are not applicable to queue processors and, in order to obtain practical and competent code we needed to conduct original research to establish the principles of compilation for queue machines and to develop the first queue compiler.

Compiler development is a major engineering undertaking that requires significant time and efforts. Historically, the development time of an optimizing compiler takes longer than the development of the microarchitecture. Each computation model imposes distinct, yet very challenging problems to the compiler technology. For example, the recent trend in computer architecture design to achieve higher performance with identical VLSI technology is towards multi-core microprocessors. Although compiler technology is well understood for parallelizing programs for single processing elements, the introduction of many cores has brought major challenges for the compiler writers [75, 6, 53, 63, 83]. Compiling for queue computing paradigm requires a new and different approach. This dissertation presents the design and development of a compiler framework for queue machines. We tackle the fundamental problems of code generation and compiler development for queue machines with novel methods. We also introduce techniques to generate code for specific hardware constraints and program transformations dependent on the target queue machine.

At Sowa Laboratory [85, 86] we are researching and developing the first parallel queue-based processor. The queue compiler plays a very important role in the research, implementation, design, and testing of new ideas. Having the ability to generate queue code for actual applications allows the designers to identify areas of improvement on the microprocessor and the compiler itself. Once the actual queue processor has been completed, the compiler remains as a valuable development tool that facilitates the deployment of operating systems, system libraries, assemblers, and any application in general.

#### 1.1 Main Objectives

The primary goal of this dissertation is the research and development of the principles to compile high-level languages into machine code for queue-based processors. As a result of this investigation, we present a queue compiler framework able to translate and accommodate any program in an actual parallel queue processor. Second, we invented new techniques to generate code for specific objective functions such as code size, high parallelism, queue size control, offset reduction. Third, we aimed to the generation of code with quality comparable to that of production and research compilers in terms of number of instructions, code size, and compile-time instruction level parallelism. Fourth, to deliver a complete framework that contributes and promotes the study and progress of queue computing.

### **1.2** Related Work to Queue Machines

The concept of a queue machine was first proposed by Feller and Ercegovac in [24], they present and highlight some of the properties of queue machines for parallel processing such as fast instruction issue, fault-tolerance, and simple interconnection properties. In [71], Preiss discusses the fundamental techniques to generate programs for a queue machine by traversing the parse trees in level-order manner, and the complications [35] of generating code from a directed acyclic graph (DAG). Okamoto [67] proposed the actual design of a superscalar queue machine able to execute instructions in parallel. In [76], Schmit et al. proposed a queue machine as the execution engine for reconfigurable hardware with high parallelism properties and simple hardware complexity. In [87], Sowa et al. established a method to execute arbitrarily complex DAGs in a single queue without modifications to the original graph. Instead, this *producer order* model relies on allowing instructions to randomly access any operand in the queue with offset references indicating the place, relative to the head of the queue, from where to read the operands. Based on this model the QueueCore parallel processor was developed [1] together with a custom compiler [13]. QueueCore programs expose similar parallelism and are smaller than embedded RISC processors. With the same idea of high flexibility of queue computing, research has been conducted on *consumer order* [86] and *multidimensional* [29] queue computing. Where the consumer order model only gives flexibility when writing operands anywhere in the queue. And the multidimensional queue computing introduces the concept of multiple queues to reuse data as much as possible and thus avoiding long latency memory accesses.

Another class of computers such as the Astronautics ZS-1 [84] and the WM machine [96] decouple memory accesses from execution using visible queues for communication. Since execution runs asynchronously from memory accesses and instructions can read/write operands from/to the queues, streamlined processing can be effectively exploited. Inspired by the decoupled architectures, a VLIW processor using a queue register file was proposed to boost the execution of software pipelined loops [25]. The idea is extending the architected register file by connecting registers to queues. Thus, queues can hold more values than the architected registers. Every write access to register connected to a queue places the element at the tail of the connected queue, and every read access to a connected register dequeues on element. A modified register allocator emits rq\_connect instructions to map specific registers to specific queues, allowing values of different iterations to reside in the queues. This technique has also been demonstrated to be effective in solving register pressure problem in conventional superscalar machines [89].

Register machines using queues for extending the architected register file provided compiler support [25, 89]. Their approach is to use a traditional register compiler and modifying the conventional register allocator phase [16] by making visible a larger number of registers. The modified register allocator attempts to place the most important variables in the architected registers, while storing the less important variables in the queues or memory. After register allocator is complete, the compiler is required to emit the *connect* instructions to map registers to queues. This process emulates the register mapping table at compile time [44] instead of run time as the register renaming process [49]. Clearly, the compiler treats queues as additional low priority registers as the main computation is done by explicit referencing the architected registers. This simple approach is able to employ the queues as additional registers, however, it does not contribute to the design of code generation techniques for formal queue machines.

In [35], it was established that some directed acyclic graphs need more than one queue to be laid out, however, level-planar graphs can be always laid out in a single queue. Based on this property, Schmit et al. [76] proposed a heuristic to convert any non level-planar graph into level-planar. This conversion is achieved through inserting special instructions to duplicate and exchange position of data. However, no compiler with such functionality was developed.

Some efforts have been done to improve the performance of conventional high-level languages by the utilization of the queue computation model. In [58], the idea of using a queue machine for the implementation of a parallel functional language is discussed. An initiative to develop a queue-based Java Virtual Machine for parallelizing the execution of Java bytecode [55] was proposed in [80, 81]. This project developed a Java compiler capable of rearranging the abstract syntax trees of programs and extracting parallelism for direct execution on the queue-based Java virtual machine. This compiler generates bytecodes from abstract syntax trees and their method does not handle code generation from directed acyclic graphs. Based on this work, [42] presents an improved compiler able to calculate the correct location of operands relative to the head of the queue and thus generating offset references for instructions. The latter Queue-Java compiler is able to handle simple directed acyclic graphs and generate correct bytecode.

From 2000 to 2005, several attempts were made to develop a queue compiler based on a retargetable register compiler [68, 27, 37, 8, 11]. The idea was to map threeaddress register code into queue code. First, the data flow graph of the program had to be reconstructed and re-scheduled for the queue computation model. During this process register references had to be eliminated since queue machines do not have explicit operands. This mapping technique led to very complicated mapping algorithms and very poor output programs. Furthermore, these compilers were never completed and could only compile toy programs of less than a hundred lines of code with very simple operations and control flow. Such approach and results made clear that the fundamental problem lies on the compiler must be blind to the concept of registers. Since all back-ends of conventional compilers are based on the concept of registers, the need of a compiler crafted specifically for the queue computation model became clear.

### **1.3** Organization of this Dissertation

This dissertation is organized as follows: Chapter 2 presents the principles of queue computing. Chapter 3 establishes the concepts, abstractions, and algorithms to develop a queue compiler. Chapter 4 provides novel techniques to cope with the code generation for constrained hardware. Chapter 5 presents a technique to improve data allocation in the queue while reducing memory traffic. Chapter 6 presents the evaluation of queue computing by means of compiling a set of benchmark programs with the presented queue compiler. Chapter 7 discusses several aspects on the development of a queue compiler and concludes.

### Chapter 2

### **Queue Computation Model**

A queue-based computer employs a first-in first-out (FIFO) queue to evaluate expressions. To avoid high-latency memory accesses, the queue is implemented with high-speed registers arranged and accessed in special manner. The physical implementation of the queue is called the Queue Register File. Reading operation from the queue is done always through the head of the queue, and writing operation is done always through the tail of the queue. Therefore, the hardware must provide two pointers to track the head and tail of the queue. Such pointers are implemented as special registers, QH and QT to track the head and the tail positions of the queue. The Queue Computation Model (QCM) is the set of rules and conventions that allow programs to be executed in a queue processor. In this Chapter, the hardware and software aspects of the QCM are discussed.

### 2.1 Differences with Conventional Computation Models

The goal of any computer is to perform correct operations on data items. The underlying principles of a computer vary from one to another. Conventional register machines, such as RISC<sup>1</sup>, employ a set of random access registers to hold data and perform operations. A typical RISC instruction consists of a quadruple that specifies an operator, and three operands: a destination operand, and two source operands. For example, the instruction

<sup>&</sup>lt;sup>1</sup>Reduced Instruction Set Computer

"add R1, R2, R3" adds (operator) the contents of registers R3 and R2 (source operands), and places the result of the addition in register R1 (destination operand). An important characteristic of random access register machines is that all operands must be explicitly referenced by name (register number).

A stack machine employs a set of registers organized as a last-in first-out (LIFO) stack to perform computations. All accesses, read and write, to the stack are done through the *top of the stack*, or TOS. Since all accesses to the stack are fixed at TOS, operands can be omitted from the instruction allowing 0-operand instructions. For example, the stack instruction "**sub**" reads (pop) two elements from TOS, performs the subtraction, and writes (push) the result to TOS. Compared to RISC-based 3-operand instructions, 0-operand instructions are smaller and require less memory bandwidth for fetching, less hardware to decode, and improved instruction cache performance. Generally, stack-based computers require less hardware and have better power consumption characteristics than register machines. However, the performance of stack machines is fundamentally limited by the bottleneck created at the TOS [91, 73, 79].

The QCM inherits all characteristics of 0-operand computers and, contrary to the stack model, it is a fundamentally parallel computation model. Queue machines can easily and effectively exploit parallelism as two different locations are used for reading and writing. One important advantage of queue computers over conventional register computers is that queue programs are free of false dependencies and the hardware and power consumption can be greatly improved with the absence of register renaming techniques [49]. Table 2.1 summarizes the differences between the queue computation model and conventional random access register and stack models.

### 2.2 Code Generation for Queue Machines

Queue processors employ a different arrangement of registers with well established rules for accessing its elements and, therefore, conventional code generation techniques for register machines cannot be applied for the queue model. As the queue obeys the rule that the first inserted element is the element that will be read first, the generation of correct queue programs is guaranteed by a *level-order* traversal of the expression trees [71].

|                      | Queue | Register      | Stack                  |

|----------------------|-------|---------------|------------------------|

| Principle            | FIFO  | Random Access | LIFO                   |

| Operands             | 0     | 3             | 0                      |

| Instruction Encoding | small | large         | $\operatorname{small}$ |

| False Dependencies   | no    | yes           | no                     |

| Hardware Complexity  | low   | high          | low                    |

| Power Consumption    | low   | high          | low                    |

| Performance          | high  | high          | low                    |

Table 2.1: Characteristics of queue computation model compared to conventional register and stack models

Expression trees have the property that every produced element has only one consumer and therefore data cannot be used more than once. To reduce the size of the trees a directed acyclic graph (DAG) is constructed where elements have no limitation in the number of consumers, thus allowing to reuse data. Despite this property, queue programs are still generated by a level-order traversal of the expression DAGs [71]. However, a data ordering problem between producers and consumers is introduced and it should be solved by the hardware and the software.

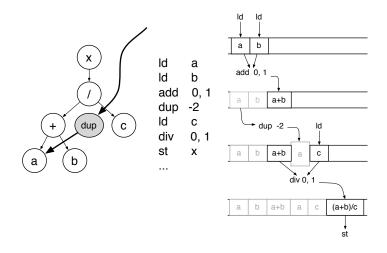

#### 2.2.1 Consumers-Producers Data Ordering Problem

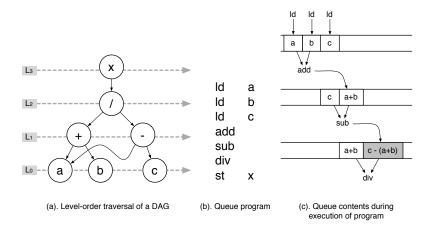

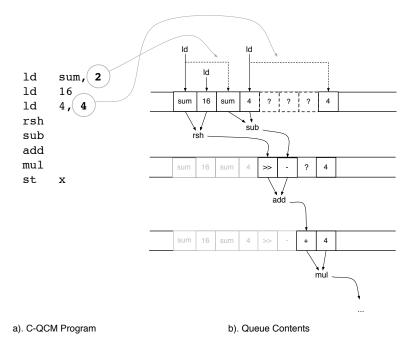

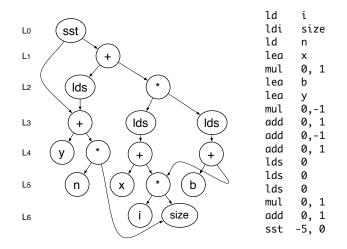

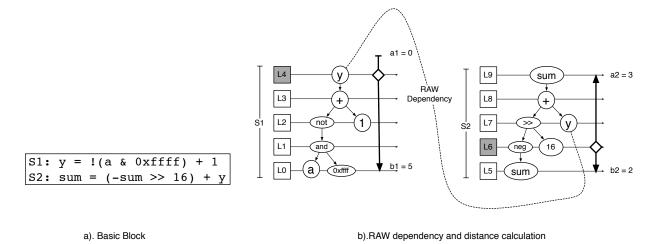

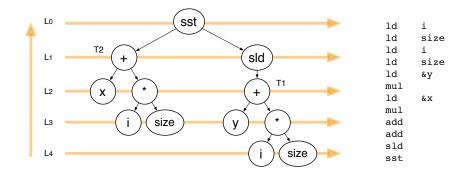

To illustrate the queue code generation from DAGs and the data ordering problem consider the expression in Figure 2.1. The Figure 2.1(a) shows the DAG of expression "x = (a + b)/(a - c)". The horizontal dotted lines show the level-order traversal starting at the deepest level ( $L_0$ ) and finishing at the root level ( $L_3$ ). For each level ( $L_0, L_1, L_2, L_3$ ) all nodes are visited from left to right. The level-order traversal generates the instruction sequence to evaluate the expression in a queue machine. Figure 2.1(b) shows the pseudoinstructions of the queue program. Figure 2.1(c) shows the contents of the queue during the execution of the program. For every stage, the head of the queue is represented by the left-most element and the tail of the queue by the right-most end of the queue. Firstly, operands a, b, c are loaded into the queue. The next instruction, "add", is a binary operation that takes its two operands a, b from the head of the queue and writes the addition a + b into the tail. Notice that after the addition is performed the elements "a" and "b" were consumed and no longer present in the queue. The problem appears when any further instruction has any of these consumed data as operand. For example, the following subtraction "sub" requires operands "b" and "c" but the head of the queue contains operand "c" and the contiguous element is the result of the addition "a+b". If the subtraction is executed the result would be "c + (a - b)" as shown in the shaded element in the Figure rather than "a - c". This situation leads to incorrect evaluation of the expression.

Figure 2.1: Code generation for queue machines consist of: (a) traversing the DAG in level-order manner, (b) obtain the instruction sequence of the queue program, and (c) executing the program in the queue.

### 2.3 Queue Computation Model Taxonomy

We identify three approaches that can be taken in the hardware and/or software to solve the problem of consumers-producers. These models constitute a variation of the queue computation model. In the first solution, called *producer-consumer order model*, the software is in charge of modifying the DAGs and the hardware remains intact as a pure queue machine. The other two solutions, called *consumer order model* and *producer order*  *model*, add hardware support for the execution of DAGs balancing the complexity between the software and the hardware.

### 2.3.1 Producer-Consumer Order Queue Computation Model (PC-QCM)

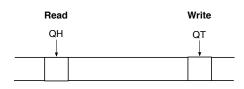

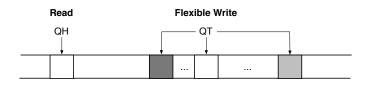

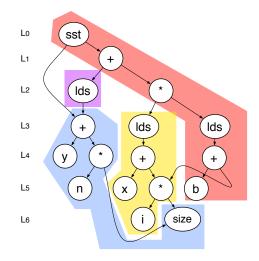

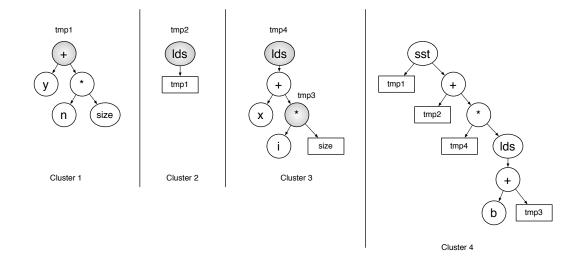

For this model, the rules of enqueueing and dequeueing remain intact. Reading is strictly performed at QH, and writing at QT as shown in Figure 2.2. During code generation, the compiler analyzes the data flow DAGs and determines whether any node incurs in a consumers-producers data ordering problem. This can be identified by dependency edges that intersect and by edges spanning across more than one level. In [76], a heuristic algorithm is proposed where the original DAG is verified to be *level-planar* [35]. A level-planar DAG has the properties that all edges span only one level and there are no crossing arcs, therefore can be executed as is in a pure queue machine. Level-planarity can be tested in linear time [40]. For non level-planar DAGs, the algorithm selectively places swap instructions to exchange position of data and remove crossing arcs, and fill<sup>2</sup> instructions to fill empty slots of edges spanning multiple levels. In this way any DAG can be converted into a level-planar DAG for direct execution in a pure queue machine.

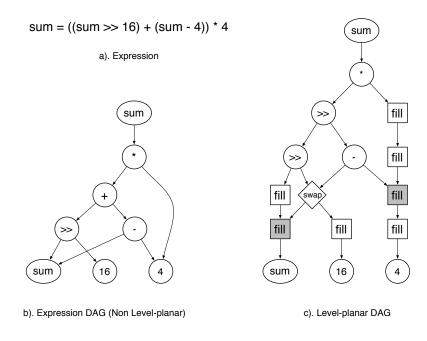

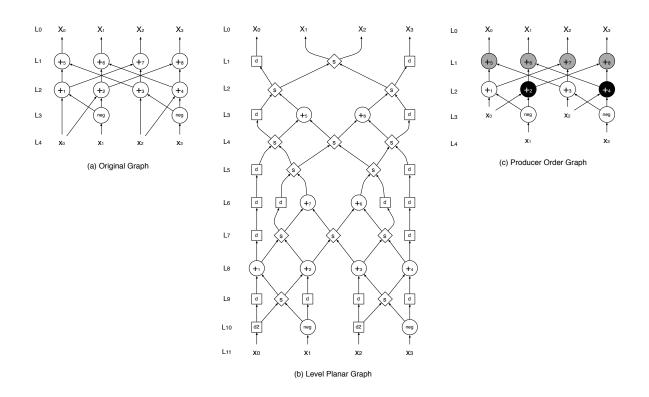

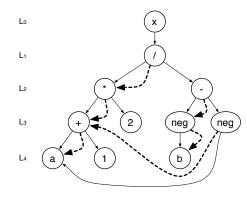

Figure 2.3(a) shows a sample expression whose straightforward representation in a DAG is non level-planar. In Figure 2.3(b), a crossing arc between (>>  $\rightarrow$  16) and ( $\rightarrow sum$ ) exists. Furthermore, the edge spanning from (\*  $\rightarrow$  4) has two empty levels. Figure 2.3(c) shows the transformed DAG into a level-planar DAG using fill (squared nodes) and swap instructions (diamond shaped nodes). Notice that the fill nodes shaded in gray produce two data. The swap node exchanges the position of a copy of sum with 16. And the chain of fill instructions in the right-most column converts the empty instruction slots into data. Executing the level-planar graph in the PC-QCM model is straightforward as no consumers-producers data ordering problem appears. However, the overhead of level-planarazing a DAG is the insertion of extra instructions and extra levels. For this example, the original DAG has 8 nodes and 5 levels, and the level-planar graph 16 nodes and 7 levels.

<sup>&</sup>lt;sup>2</sup>The original name of fill instruction in [76] is dup. The name has been changed not to confuse the reader the duplicate (dup) instruction used in this thesis.

Figure 2.2: Producer-consumer model (PC-QCM) strictly uses QH and QT for reading and writing.

Figure 2.3: Transforming a DAG into a Level-planar DAG

#### 2.3.2 Consumer Order Queue Computation Model (C-QCM)

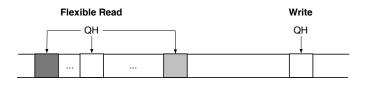

The Consumer order model, or C-QCM, was named after the strict rule that reading, or *consuming*, elements is done always through QH. The rule for writing is broken to give flexibility and solve the consumers-producers data ordering problem. The instructions in a C-QCM program, apart from producing always a datum in QT, have the ability to specify a location relative to the QT where to produce a copy of the produced data as shown in Figure 2.4. The hardware must be modified to enable the execution of such special cases of instructions, and the compiler must calculate the correct locations where to place copies of data. This is a hardware/software approach to solve the consumers-producers data ordering problem.

Figure 2.4: Consumer model (C-QCM) gives flexibility in writing but the reading location remains fixed at QH.

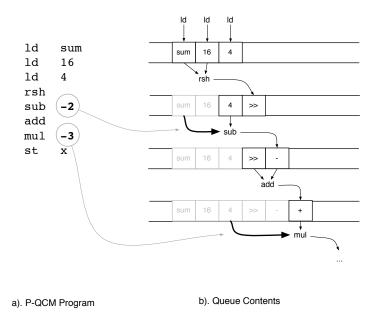

Figure 2.5(a) shows the C-QCM program generated to evaluate the expression "sum =  $((sum \gg 16) + (sum - 4)) * 4$ ". The program is obtained by a level-order traversal of the expression's DAG. Figure 2.5(b) shows the queue contents during the execution of the program. The first instruction loads sum into the queue and places a copy two locations after the current QT location. The second operand in the first instruction loads 16, the third instruction loads 4, and produces a copy four locations away to QH current position. Notice that the hardware must be capable of identifying the data that was produced ahead. The elements marked with a question mark, ?, represent queue registers that can be used for computation. However, the rightmost 4, should be not overwritten. The following instructions are executed and the ?-nodes are filled with computations to evaluate the expression. For clarity of tracking the progress of computations, the consumed data is shown by the light gray queue elements. This hardware/sofware mechanism solves the consumers-producers problem keeping instruction count same as the original problem and adding extra complexity to the instructions and the hardware.

The Indexed Queue Machine proposed in [71] follows this principle. The only difference is that the location to produce the extra copy is relative to QH rather than QT as in our method. Although same principle, we believe our method is superior than the Indexed Queue Machine since the offset reference used to specify the location is generally shorter when relative to the QT. Let the number of elements between QH and QT is N, and a C-QCM instruction needs to produce a copy M locations away from QT. Then, for our method the offset reference relative to QT M, and for the Indexed Queue Machine is N + M.

Figure 2.5: Consumer model (C-QCM) execution

#### 2.3.3 Producer Order Queue Computation Model (P-QCM)

The Producer Order model, P-QCM, is a hardware/software approach to solve the consumers-producers data ordering problem. The unique characteristic is that the rule for writing, *producing*, data remains fixed at QT and the rule for reading data has flexibility. Figure 2.6 shows the rationale behind the P-QCM model.

Figure 2.6: Producer order model (P-QCM) gives flexibility in reading data but the writing location remains fixed at QT.

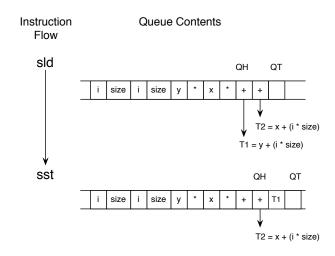

Figure 2.7(a) shows the P-QCM program generated for the same sample expression "sum = ((sum >> 16) + (sum - 4)) \* 4". The execution of the program and its queue contents are displayed in Figure 2.7. Execution flows normally up to the fourth instruction. The subtraction operation needs operands sum and 4. Notice that sum was consumed by

the rsh instruction in the first queue state. Therefore, the subtraction instruction must specify a location relative to QH to read its operand, for this case -2. The negative value denotes the access of a value that was already consumed by a previous operation. Graphically, it represents the access to a value on the left of QH. The addition consumes its two operands directly from QH, and the multiplication finds the same problem. It requires the access to operand 4 which is three queue registers away from QH, hence the offset reference is -3.

Figure 2.7: Producer Order model (P-QCM) execution

We believe the P-QCM offers the best alternative over the other two queue computation models. It provides great flexibility for executing scientific and conventional codes. The C-QCM programs have the tendency to be longer than P-QCM programs. Table 2.2 shows the fundamental characteristics of C-QCM and P-QCM for the Livermore loops program. The C-QCM needs 22% more instructions than the P-QCM program. The available parallelism at the instruction level is higher for the C-QCM but the execution time is the same for both models. This means that the C-QCM requires about 20% more hardware to execute the program in the same time as the P-QCM. The maximum queue utilization represents the amount of queue registers needed to execute the most demanding part of the program. For this benchmark program, the C-QCM needs 60%

|                               | C-QCM | P-QCM |

|-------------------------------|-------|-------|

| Generated Instructions        | 4094  | 3350  |

| Instruction Level Parallelism | 3.82  | 3.13  |

| Execution time                | 1542  | 1542  |

| Max. Queue Utilization        | 227   | 94    |

Table 2.2: C-QCM and P-QCM program characteristics for Livermore loops

more registers than the P-QCM.

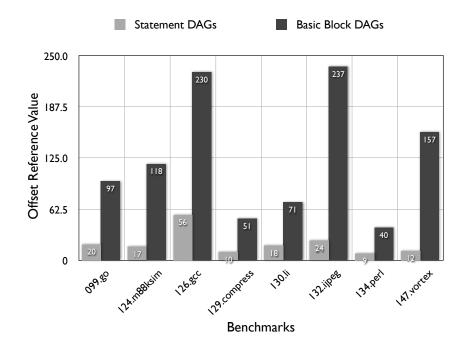

To illustrate the advantages of P-QCM over the PC-QCM consider the example in Figure 2.8(a), it shows the directed acyclic graph for a 4-point Fourier Transform. Using the method proposed in [76] the original DAG is transformed into a level-planar graph. Basically, edges spanning more than one level are eliminated by a *fill operator*, and crossing arcs are eliminated by a *swap operator*. By employing these two special instructions [76] the original DAG is transformed into a level-planar graph as shown in Figure 2.8(b). Duplicate operators are represented by the squared nodes, and swap operators are represented by the diamonds. As it is reported by its authors, this method increases the number of instructions and the depth of the graph, for the given example from 18 to 49 instructions and from 5 to 12 levels. Figure 2.8(c) shows the producer order graph. White circles represent instructions that read operands directly from QH gray circles represent instructions that take all its operands using the flexible reading rule. Compared to the PC-QCM model, the P-QCM model does not increase the number of instructions nor the depth of the graph.

Table 2.3 compares the code size and depth of data flow graphs (DFG) for the PC-QCM model and the P-QCM model for a set of benchmark programs. The P-QCM programs are from 55% to 80% smaller than PC-QCM programs. From the fact that all instructions belonging to the same level can be potentially executed in parallel, shallow data flow graphs are preferred over deep ones. The table shows that P-QCM data flow graphs are about 1.46 to 5.85 times shallower than the PC-QCM. For the aforementioned reasons, the P-QCM model is preferred over the other two queue computation models and

Figure 2.8: Comparison between (a) original directed acyclic graph, (b) PC-QCM levelplanar model, (c) P-QCM model

|                | PC-QCM Graph |       | P-QCM Graph |       |

|----------------|--------------|-------|-------------|-------|

| Application    | Code Size    | Depth | Code Size   | Depth |

| dct1           | 537          | 49    | 244         | 18    |

| fft8_iterative | 909          | 41    | 176         | 7     |

| haar16         | 918          | 17    | 248         | 6     |

| rc6            | 330          | 42    | 148         | 23    |

| idea           | 1462         | 235   | 606         | 160   |

| popcount       | 229          | 24    | 62          | 5     |

Table 2.3: Code Size and Depth of Application Graphs Comparison

all efforts of this thesis were made to develop a P-QCM compiler framework.

### Chapter 3

# Producer Order Queue Compiler Framework

Among all queue computation flavors, the producer-order model offers the highest flexibility for the software and the hardware. Programs generated for the producer-order model are characterized by being small and having two offset references that specify the location with respect of the head of the queue from where to read the source operands. This chapter presents the main contribution of this dissertation which is the establishment of the techniques to develop a queue compiler for the producer order queue computation model. The structure of the queue compiler is different from traditional compilers since it integrates the concept of queue computing to all phases of code generation. We introduce a novel data structure that facilitates the compilation process and allows the calculation of offset references and level-order scheduling. The functionality of the actual queue compiler implementation is presented and we analyze the complexity of the algorithms in terms of lines of lines of code and compile time against conventional compilers for a set of standard applications.

#### 3.1 Target Queue-based Architecture

To avoid compilation complexities introduced by specific hardware implementations, the queue compiler generates code for a generic producer-order instruction set architecture inspired by the Parallel Queue Processor (PQP) [87]. The target instruction set, or P-

| Class      | Instructions                  |  |

|------------|-------------------------------|--|

| Arithmetic | add, sub, div, mod, mul, neg, |  |

| & Logic    | rsh, lsh, ior, xor, and, not  |  |

|            | rrot, lrot, abs               |  |

| Memory     | ld, st, ldi, lea, sld, sst    |  |

| Comparison | ceq, cne, clt, cle, cgt, cge  |  |

| Ctl. Flow  | bt, bf, j, jal, ret           |  |

| Conversion | conv                          |  |

| Special    | copyp, dup, rot               |  |

| Queue      | moveqh, moveqt                |  |

Table 3.1: Generic queue instructions

Code, allows two offset references to be encoded without length restrictions. Hardware details such as type and number of functional units, memory hierarchy, queue register file size, instruction length, are parametrized in the compiler to allow flexibility and to gain the ability to target multiple implementations of queue processors. P-Code instructions are classified in seven classes as shown in Table 3.1: Arithmetic & Logic, Memory, Comparison, Control Flow, Special, and Queue. To differentiate between integer and floating point operations, each instruction defines its data type and sign. Table 3.2 shows the equivalence between C language data types and P-Code data types. For full description of P-Code instructions refer to Appendix A.

P-Code's instruction set format is as follows. Instructions using offset references such as arithmetic and logic, comparison and special groups, and **sst** and **sld** instructions the encoding is as follows:

| opcode | data type | offset1 | offset2 |

|--------|-----------|---------|---------|

|--------|-----------|---------|---------|

For memory instructions that do not use offset references the encoding is as follows:

| opcode data type | memory address |

|------------------|----------------|

|------------------|----------------|

Control flow instructions do not have a data type and the only operand is the target label symbol representing the target of jumps or function names.

| P-Code type                          | C-Type    |                      |

|--------------------------------------|-----------|----------------------|

| Description                          | Data Type |                      |

| Integer Byte Signed                  | ibs       | signed char          |

| Integer Byte Unsigned                | ibu       | unsigned char        |

| Integer Half-word Signed             | ihs       | signed short         |

| Integer Half-word Unsigned           | ihu       | unsigned short       |

| Integer Word Signed                  | iws       | signed {int, long}   |

| Integer Word Unsigned                | iwu       | unsigned {int, long} |

| Integer Long Signed                  | ils       | signed long long     |

| Integer Long Unsigned                | ilu       | unsigned long long   |

| Floating Point Single Precision      | fps       | float                |

| Double Precision Floating Point      | fpd       | double               |

| Long Double Precision Floating Point | fpD       | long double          |

Table 3.2: Data type and sign information

opcode | target label

# 3.1.1 Offset Referenced Instructions Classification

P-Code instructions are classified in three categories according the number of operands read by an offset reference. We say that "an operand is read by an offset reference" when it is not directly accessed by the current QH, in other words, QH+N where N $\leq$ 0. 2offset instructions read both operands by offset references, 1-offset instructions read only one operand by an offset reference, and 0-offset instructions do not use offset references. Thus, the binary instructions can be 2-offset, 1-offset, or 0-offset. Unary instructions can be 1-offset, and 0-offset. By notation, the two offsets values in binary instructions are explicitly given by a pair (N, M). Operand location is given by QH+N and QH+M for the first and second operands, respectively. We use the following convention to specify 0-operand binary instructions:

**Definition 3.1.** The pair of offset references (0, 1) defines a 0-operand binary instruction,

| Туре     | Binary     | Unary  |  |

|----------|------------|--------|--|

| 0-offset | mul 0, 1   | not O  |  |

| 1-offset | add -3, 0  | neg -3 |  |

|          | sub 0, -2  |        |  |

|          | div 1, 0   |        |  |

| 2-offset | rsh -3, -1 | N/A    |  |

Table 3.3: Examples of producer-order instructions

e.g. "div 0, 1".

Table 3.3 shows examples of binary and unary instructions according their Producer Order classification.

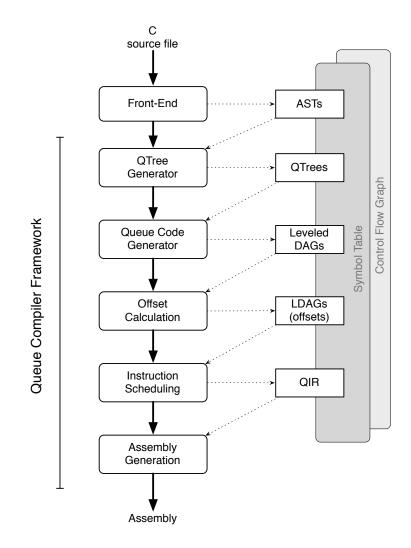

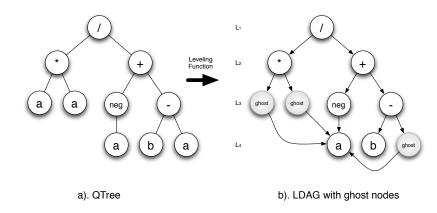

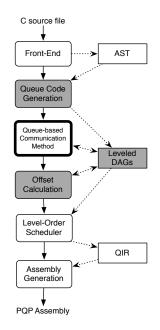

# 3.2 Compiler Framework Design and Implementation

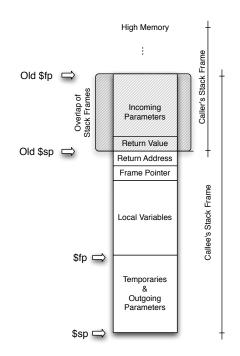

The queue compiler infrastructure consists of six phases, including the front-end. Figure 3.1 shows the block diagram of the queue compiler. The front-end parses C files into language independent abstract syntax trees (AST) which are a high level intermediate representation (HIR). These language independent ASTs facilitate the addition of any other high-level language parsers and permit the reutilization of the back-end of the compiler. The queue compiler framework consists of the remaining five phases. *QTree generation* phase lowers the high level constructs in ASTs into a generic low level sequence of queue instructions (P-Code instruction set). The resulting representation is a tree-like structure called QTrees and its main purpose is representing all program in queue-like instructions. QTrees completely ignore the concept of registers as the queue machine has none, instead, they represent a pure data flow graph model of the basic blocks. The second phase is the *Queue Code Generator* which takes QTrees as input where redundancies are eliminated and all nodes are assigned to a hierarchical structure formed by *levels* according data dependencies among instructions. This hierarchical structure is called a *leveled*  directed acyclic graph (LDAG) on which the compiler performs the offset calculation and tracking of the head of the queue. This structure facilitates also the scheduling of the program as all nodes are organized into levels. Although direct translation from ASTs to LDAGs is possible, we introduce the QTrees to separate instruction selection from redundancy elimination and to simplify the algorithms. The third phase, offset calculation, consumes the LDAGs and for every instruction it computes the offset reference values to reach its operands. Offset references are annotated in the LDAGs. The fourth phase, instruction scheduling traverses the LDAGs and produces a level-order scheduling of instructions that complies with the queue computing principle. As a result, this phase generates a low level intermediate representation called QIR. QIR is a linear representation designed to facilitate target dependent optimizations. The QIR is tightly coupled to the DFG which allows the retrieval of data dependency information among instructions. The fifth phase, assembly generation, converts QIR into target assembly code.

Throughout all the compilation process, a common symbol table is created and maintained by the compiler. This symbol table includes information about local variables, global variables, function parameters and arguments, function names, read-only data such as constants and strings, and target labels for jumps. A control flow graph (CFG) consisting of basic blocks of the compiled program is also built and maintained by the compiler. These two structures are global and accessible to any phase of the compiler.

One of the goals in our design was to keep the compiler implementation independent from the target architecture. Although the presented compiler generates code for a specific target architecture, the Parallel Queue Processor, all the algorithms and data structures are machine independent and can be applied for the queue computation model in general.

### 3.2.1 QTree Generation

The front-end of the compiler is based on GCC 4.0.2 and it parses C files into a language and target independent high-level intermediate representation called GIMPLE [64, 66]. Although our queue compiler is capable of generating code from GCC's optimized GIMPLE code, at this point we have not validated the results and correctness of such programs. For the rest of this section, the GIMPLE code used as input for the queue compiler is non-optimized code. GIMPLE representation is a tree-based three-address

Figure 3.1: Queue compiler block diagram

code suitable for code generation for register machines but not for queue machines. As the level-order scheduling traverses the full DAG of an expression, we facilitate the job of the scheduler by reconstructing GIMPLE trees into trees of arbitrary depth and width called QTrees. During the expansion of GIMPLE into QTrees we also translate the highlevel constructs such as aggregate types into their low level representation in generic queue instructions. The instruction selection phase is in charge of expressing any high level statement into generic queue instructions equivalent. Figure 3.2 shows a fragment of a C program and its GIMPLE representation. Notice that in the C-like GIMPLE representation in Figure 3.2(b), the statement inside the conditional is split into threeaddress statements with the help of compiler generated temporaries (i.e. D1098). To illustrate the high level nature of GIMPLE representation we show in Figure 3.2(c) the same program but using GIMPLE language. As shown in Figure 3.3(a), QTrees are unrestricted in the number of operands and operations. For the given example, the QTree representation is shown in Figure 3.3(b). Now the program is expressed through low level generic queue instructions.

(cond expr (eq\_expr (var\_decl: c) (integer\_cst: 1)) (goto\_expr: L1)) (modify\_expr (var\_decl: i.0) (var\_decl: i)) (modify\_expr (var\_decl: i.1) (var\_decl: i)) (modify\_expr (var\_decl: D1097) (array\_ref: a[i.1])) (modify\_expr (var\_decl: D1098) if(c == 1) { (plus\_expr (var\_decl: x) (var\_decl:y))) i.0 = i; (modify\_expr i.1 = i: if(c == 1) { (var\_decl: D1099) D1097 = a[i.1]a[i] = a[i] \* (x + y);(mult\_expr D1098 = x + y;D1099 = D1097 \* D1098; (var\_decl: D1097) (var\_decl:D1098))) (modify expr a[i.0] = D1099; (array\_ref: a[i.0]) (var\_decl: D1099)) } (a) C fragment (b) C-like GIMPLE representation (c) GIMPLE representation

Figure 3.2: High-level intermediate representation. (a) C fragment, (b) C-like GIMPLE representation, (c) GIMPLE representation

```

if(c == 1) {

a[i] = \&a + (i * sizeof(a)) * (x + y);

(a) C-like QTree representation

(bt: L1

(cne

(ld: c)

(ld: #1)))

(sst: a[i]

(mul

(sld: *a[i]

(add

(lea: &a)

(mul

(ld: i)

(ld:#4))))

(add

(ld: x)

(ld: y))

)

)

(b) QTree representation

```

Figure 3.3: QTrees. (a) C-like Qtree representation, (b) QTree representation using low level generic queue instructions

# 3.2.2 Queue Code Generation

The most important task of the code generator is to shape the program in a suitable format that facilitates offset reference calculation and level-order scheduling. Leveled DAGs offer such characteristics where scalar calculations such as distances between nodes and levels is simple. In this section we establish the rules and techniques to build LDAGs from ASTs.

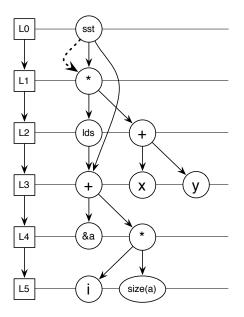

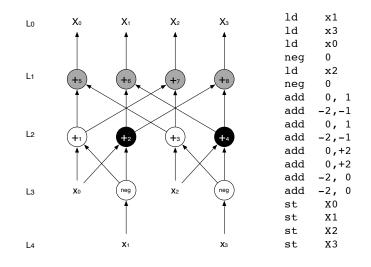

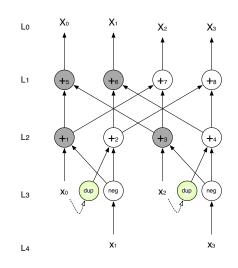

#### Leveled Directed Acyclic Graph (LDAG) Construction

Formally, a LDAG  $\vec{G} = (V, \vec{E})$  is the mapping of the nodes to integers such that if there is an edge from u to v, then lev(v) = lev(u) + N, N > 0 for all edges in the graph. A node v is a *level-j node* if lev(v) = j. The hierarchical organization of the nodes in the DAG according their true data dependencies is what makes LDAGs the most suitable representation for finding offset references. Notice that all instructions in the same level are independent from each other. Therefore, the queue compiler exposes maximum natural instruction level parallelism to the queue processor. The compiler builds a list of *slots* that bind together all nodes of every level. Figure 3.4 shows a LDAG for expression a[i] = (&a + (i \* sizeof(a))) \* (x + y). The squared nodes in the left of the figure are the slots that indicate the levels of the DAG.

Figure 3.4: Leveled DAG for expression a[i] = (&a + (i \* sizeof(a))) \* (x + y)

For describing the algorithm to build LDAGs from ASTs consider the following definitions:

Definition 3.2. A level is a non-empty list of elements.

**Definition 3.3.** An  $\alpha$ -node is the first element of a level.

Definition 3.4. The root node of the LDAG is the only node in Level-0.

**Definition 3.5.** The sink of an edge must always be in a deeper or same level than its source.

Algorithm 1 shows how the construction of a LDAG is performed by a recursive post-order depth-first traversal of the parse tree together with a lookup table that saves information about every node and its assigned level. The *levelizing* of parse trees to LDAGs works as follows. For every visited node in the parse tree a level is assigned and the lookup table is searched. If the node is not found in the table then it is its first appearance and a new entry is recorded in the table and the node is created in the LDAG. If the node is found in the table then a decision must be taken in order to satisfy the property in Definition 3.5. If the level of the new node is greater than the one in the lookup table, then the following steps should be performed: (1) create the new node with in its corresponding level in the LDAG, (2) the sink of all incoming dependency edges to the node in the table is replaced by the new node, (3) the old node is eliminated from the LDAG, and (4) the new level for the node is updated in the lookup table.

```

Input: Expression tree, t

Input: level

Output: LDAG node, new

1 begin

nextlevel \leftarrow level + 1

2

match \leftarrow lookup (t)

3

/* Satisfy Definition 3.5 */

4

if match \neq null then

5

if match.level < nextlevel then

6

relink \leftarrow dag_move_node (nextlevel, match)

7

return relink

8

else

9

return match

10

end

11

end

12

/* Insert the node to a new level or existing one */

\mathbf{13}

if nextlevel > get_Last_Level() then

\mathbf{14}

new \leftarrow new_level_with_alpha (t, nextlevel)

\mathbf{15}

record (new)

16

else

\mathbf{17}

new \leftarrow append_to_level (t, nextlevel)

18

record (new)

19

end

20

/* Post-Order Depth First Recursion */

\mathbf{21}

if t is binary operation then

22

lhs \leftarrow dag_levelize (t.right, nextlevel)

\mathbf{23}

make_edge (new, lhs)

\mathbf{24}

rhs \leftarrow dag\_levelize (t.right, nextlevel)

\mathbf{25}

make_edge (new, rhs)

26

else if t is unary operation then

\mathbf{27}

child \leftarrow dag_levelize (t.child, nextlevel)

\mathbf{28}

make_edge (new, child)

29

end

30

return new

31

32 end

```

```

Algorithm 1: dag_levelize (tree t, level)

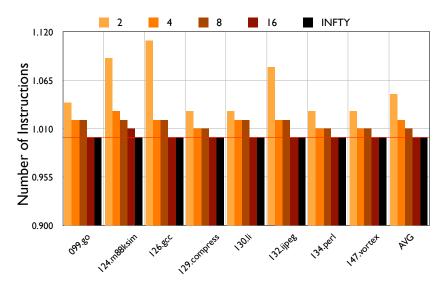

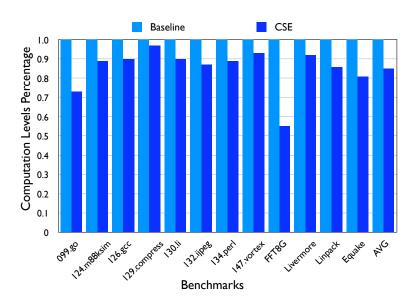

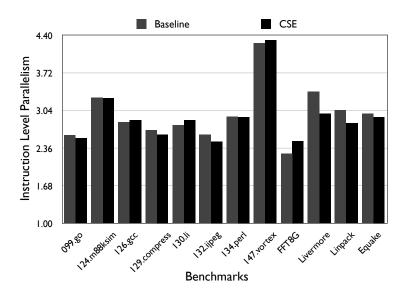

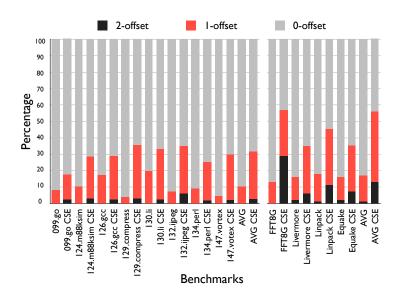

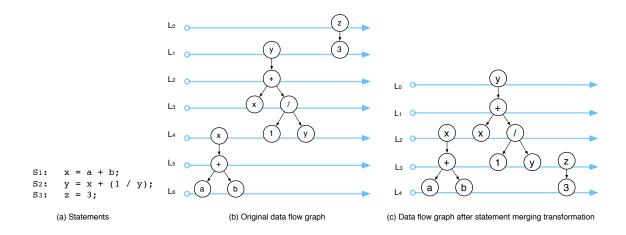

```