# T11.2 / Project 1230/ Rev 6

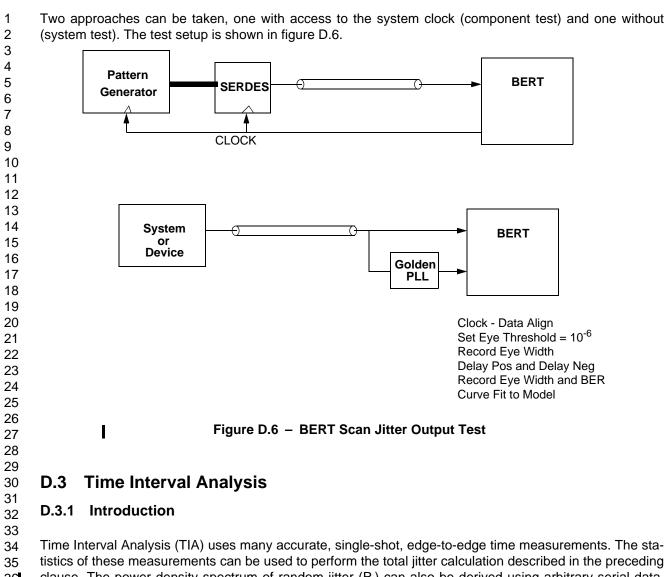

September 23, 1998

# Information Technology -

# Fibre Channel - Methodologies for Jitter Specification

Draft proposed Technical Report

Secretariat National Committee for Information Technology Standardization (NCITS)

This is a draft proposed technical report of Accredited Standards Committee NCITS. As such, this is not a completed technical report. The T11.2 Technical Committee may modify this document as a result of comments received during public review and its approval as a technical report.

Permission is granted to members of NCITS, its technical committees, and their associated task groups to reproduce this document for the purposes of NCITS standardization activities without further permission, provided this notice is included. All other rights are reserved. Any duplication for commercial or for-profit use is prohibited.

# ABSTRACT

This technical report reviews the jitter specification found in the Fibre Channel Physical layer standards. It provides the theory and test methodology to add a frequency component to the jitter specification of the physical layer specification. The existing 1,0625 GBd jitter specification is reviewed and a proposed modification to the jitter specification is proposed as an example of the application of the methodology presented in the technical report.

| Contacts: | Facilitator:                                               | <b>Technical Editor:</b>   |

|-----------|------------------------------------------------------------|----------------------------|

|           | Schelto van Doorn                                          | Steve Joiner               |

|           | Siemens Microelectronics, Inc.<br>Optoelectronics Division | Hewlett-Packard            |

|           | 1900 Homestead Rd.                                         | 3500 Deer Creek Rd.        |

|           | Cupertino, CA. 95014                                       | Palo Alto, CA 94304        |

|           | Voice: 408-725-3436                                        | Voice: 650-236-2129        |

|           | Fax: 408-725-3435                                          | Fax: 650-236-1644          |

|           | email: schelto.van-doorn@smi.siemens.com                   | email: steve_joiner@hp.com |

Reference number ISO/IEC \*\*\*\*\*: 199x NCITS.\*\*\* - 199x Printed 09/23/98

#### **Other Points of Contact:**

|        | T11 Chair:                           | T11 Vice-Chair        | NCITS Secretariat, ITI        |

|--------|--------------------------------------|-----------------------|-------------------------------|

|        | Roger Cummings                       | Edward L. Grivna      |                               |

|        | Distributed Processing<br>Technology | Cypress Semiconductor |                               |

|        | 140 Candace Drive                    | 2401 East 86th Street | 1250 Eye Street, NW Suite 200 |

|        | Maitland, FL 32751                   | Bloomington, MN 55425 | Washington, DC 20005          |

| voice: | 407-830-5522 x348                    | (612) 851-5046        | 202-737-8888                  |

| Fax:   | 407-260-5366                         | (612) 851-5087        | 202-638-4922                  |

| Email  | cummings_roger@dpt.com               | elg@cypress.com       | ncitssec@itic.nw.dc.us        |

T11 Reflector (for minutes, agendas, etc. Internet address for subscription to the T11 reflector: Note should contain a line stating .... Internet address for distribution via T11 reflector: Technical reflector (for technical discussions) Web Sites

Document Distribution Global Engineering 15 Inverness Way East Englewood, CO 80112-5704 Majordomo@network.com subscribe T11 <your email address> t11@network.com

http://www.ncits.prg/t11 or http:// www.t11.org/t11

Voice: 303-792-2181 or: 800-854-7179 FAX: 303-792-2192

#### PATENT STATEMENT

CAUTION: The developers of this technical report have requested that holder's of patents that may be required for the implementation of the technical report, disclose such patents to the publisher. However, neither the developers nor the publisher have undertaken a patent search in order to identify which, if any, patents may apply to this technical report.

As of the date of publication of this technical report and following calls for the identification of patents that may be required for the implementation of the technical report, no such claims have been made. No further patent search is conducted by the developer or the publisher in respect to any technical report it processes. No representation is made or implied that licenses are not required to avoid infringement in the use of this technical report.

Editors Notes for Revision 6.0 dated September 23, 1998.

These edits are the results of the MJS letter ballot in May and the meeting held on June 8, 1998 to review the MJS document. Also includes all input from the August meeting in the UK.

Revision 5 and 6 represent a major set of editorial changes and in some cases rewrite to convert figures and equations to native framemaker code. Thus much of the text needs to reviewed carefully for correctness. Use the change bars as a guide. The change bars reflect the changes from revision 4 to revision 6.

I have left the line numbers in the document to assist in preparing comments for the document. The line numbers will be removed for the final copy.

A separate document will be published with the responses to the comments from the first letter ballot.

The figures in Annex A still need to be converted to native framemaker format. Also the figures in Annex E could use some editorial work to make them more pleasing to the eye.

Pre-body Sections:

Body:

I

Annex A:

Annex B: Test Bit Sequences

Annex C: Jitter Tolerance Measurement Methods

Annex D: Jitter Output Measurement Methods

Annex E: Practical Measurements

Annex F: Compliance Point Examples

| I                    |        |                   |

|----------------------|--------|-------------------|

| 1<br>2<br>3          |        |                   |

| 4<br>5<br>6          | 1      | Int<br>1.1        |

| 7<br>8<br>9          | 2<br>3 | 1.2<br>Re<br>D    |

| 10<br>11<br>12       | -      | 3.1<br>3.2        |

| 13<br>14<br>15       | 4      | 3.3<br>Sc<br>4.1  |

| 16<br>17<br>18       | 5      | 4.2<br>Jit        |

| 19<br>20<br>21       | 6      | Fil<br>6.1<br>6.2 |

| 22<br>23<br>24       | 7      | 6.3<br>Ji<br>7.1  |

| 25<br>26<br>27<br>28 | 0      | 7.2<br>7.3        |

| 28<br>29             | 8      | Jit<br>8.1        |

| 30                   |        | 8.2               |

| 31                   |        | 0.4               |

# Contents

| 4        |                                                               |    |

|----------|---------------------------------------------------------------|----|

| 5        | 1 Introduction.                                               | 1  |

| 6        | 1.1 Document scope and purpose                                | 1  |

| 7        | 1.2 Document organization                                     | 1  |

| 8        | 2 References                                                  |    |

| 9        | 3 Definitions and conventions                                 | 2  |

| 10       | 3.1 Conventions                                               |    |

| 11<br>12 | 3.2 Acronyms.                                                 |    |

| 12<br>13 | 3.3 Definitions                                               |    |

| 14       | 4 Scope                                                       |    |

| 15       | 4.1 Motivation and goals                                      |    |

| 16       | 4.2 Authority                                                 |    |

| 17       | 5 Jitter overview.                                            |    |

| 18       |                                                               |    |

| 19       | 6 Fibre channel physical layer implementation                 |    |

| 20<br>21 | 6.1 FC-0 interface overview                                   |    |

| ∠1<br>22 | 6.2 Fibre channel storage implementation                      |    |

| 23       | 6.3 Jitter contribution elements 1                            |    |

| 24       | 7 Jitter specification methodology 1                          |    |

| 25       | 7.1 Current specification 1                                   |    |

| 26       | 7.2 Jitter measurement definitions 1                          |    |

| 27       | 7.3 Proposed specification methodology 1                      |    |

| 28       | 8 Jitter test methodologies 1                                 | 6  |

| 29       | 8.1 Goals                                                     | 6  |

| 30<br>21 | 8.2 Jitter tolerance test methodologies                       | 17 |

| 31<br>32 | 8.3 Jitter output test methodologies 1                        | 8  |

| 33       | 9 Example use of jitter specification methodology for FC-PH 1 |    |

| 34       | 9.1 Jitter specification measurement points                   |    |

| 35       | 9.2 Jitter Budget Allocation                                  |    |

| 36       | 9.3 Jitter Tolerance Specification                            |    |

| 37       | 9.4 Revised Jitter Output Allocation Tables                   |    |

| 38       | Annex A Bit Error Rate vs. Jitter Model                       |    |

| 39       | A.1 Description of Mathematical Model                         |    |

| 40<br>41 | A.2 Random Jitter                                             |    |

| 41       | A.3 Addition of Deterministic Jitter                          |    |

|          | Annex B Test Bit Sequences                                    |    |

| 43<br>44 | 1                                                             |    |

| 45       | B.1 Test bit sequence characteristics                         |    |

| 46       | B.1.1 Low Frequency Pattern                                   |    |

| 47       | B.1.2 Low transition density patterns                         |    |

| 48       | B.1.2.1 Half-rate square pattern                              |    |

| 49<br>50 | B.1.2.2 Quarter-rate square pattern                           |    |

| 50<br>51 | B.1.2.3 Ten contiguous runs of 3                              |    |

| 52       | B.1.3 Composite patterns 3                                    |    |

| 52<br>53 | B.2 Compliant transmit jitter test bit sequences 3            |    |

| 54       | B.2.1 Random test bit sequence                                | 34 |

| 55       | B.2.1.1 Background - fibre channel frame 3                    |    |

| 56       |                                                               |    |

| 1        | B.2.1.2 Original RPAT                                                           | 35 |

|----------|---------------------------------------------------------------------------------|----|

| 2        | B.2.1.3 Compliant RPAT (CRPAT)                                                  |    |

| 3        | B.3 Compliant Receive Jitter Test Bit Sequence                                  |    |

| 4        | B.3.1 Receive Jitter Tolerance Pattern.                                         |    |

| 5        | B.3.2 Compliant Receive Jitter Tolerance Pattern.                               |    |

| 6        | B.4 Supply Noise Test Bit Sequences                                             |    |

| 7<br>8   |                                                                                 |    |

| 9        | B.4.1 Supply Noise SPAT                                                         |    |

| 10       | B.4.2 Supply Noise CSPAT.                                                       |    |

| 11       | Annex C Jitter Tolerance Test Methodologies                                     |    |

| 12       | C.1 Calibration of a Signal Source using the BERT Scan Technique                |    |

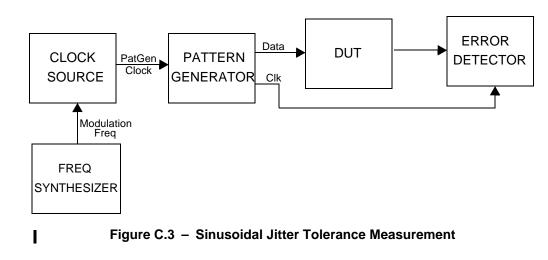

| 13       | C.2 Sinusoidal Jitter Modulation                                                |    |

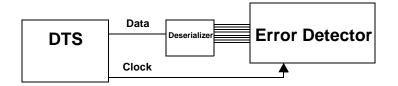

| 14       | C.3 Direct Time Synthesis                                                       |    |

| 15       | Annex D Jitter Output Test Methodologies (Informative)                          | 48 |

| 16       | D.1 Jitter Output Test Methodologies                                            | 48 |

| 17       | D.2 Time Domain Measurement - Scope and BERT Scan                               | 48 |

| 18<br>19 | D.2.1 Overview                                                                  | 48 |

| 20       | D.2.2 Golden PLL                                                                |    |

| 21       | D.2.3 Time Domain Scope Measurement                                             |    |

| 22       | D.2.4 BERT Scan.                                                                |    |

| 23       | D.3 Time Interval Analysis                                                      |    |

| 24       | D.3.1 Introduction                                                              |    |

| 25       | D.3.2 "Clock-less" Jitter Measurement                                           |    |

| 26       | D.3.3 TIA Data Reduction Procedure                                              |    |

| 27       | D.3.4 Total Jitter Calculation.                                                 |    |

| 28       |                                                                                 |    |

| 29<br>30 | D.3.5 Power Density Spectrum of Jitter                                          |    |

| 31       | D.3.6 Data Dependent (ISI) Jitter Measurement                                   |    |

| 32       | D.3.7 Jitter Measurement Using a Sampling Oscilloscope (DDJ and PWD)(           |    |

| 33       | D.4 Frequency Domain Measurement (Spectrum Analyzer)                            |    |

| 34       | Annex E Practical Measurements                                                  |    |

| 35       | E.1 Introduction                                                                |    |

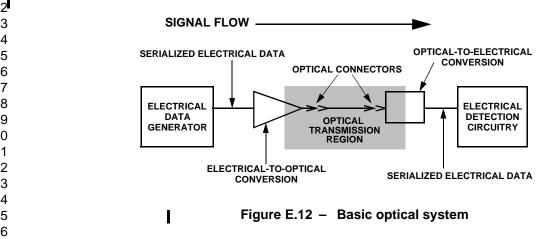

| 36       | E.2 Basic architecture                                                          | 63 |

| 37       | E.3 Instrumentation interface adapters                                          | 64 |

| 38       | E.3.1 Balanced copper                                                           | 65 |

| 39<br>40 | E.3.1.1 Source and sink adapters for balanced copper variants.                  | 66 |

| 40<br>41 | E.3.1.1.1 Balanced-unbalanced.                                                  |    |

| 42       | E.3.1.1.2 Balanced - balanced (alternative 1)                                   |    |

| 43       | E.3.1.1.3 Balanced - balanced (alternative 2)                                   |    |

| 44       | E.3.1.2 Tap adapters for balanced copper variants                               |    |

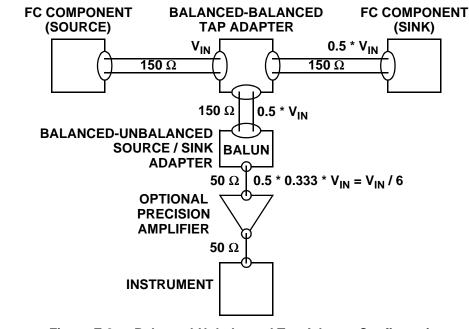

| 45       | E.3.1.2.1 Balanced-balanced (alternative 1)                                     |    |

| 46       | E.3.1.2.2 Balanced - balanced (alternative 2)                                   |    |

| 47       | E.3.1.2.3 Balanced-Unbalanced.                                                  |    |

| 48       |                                                                                 |    |

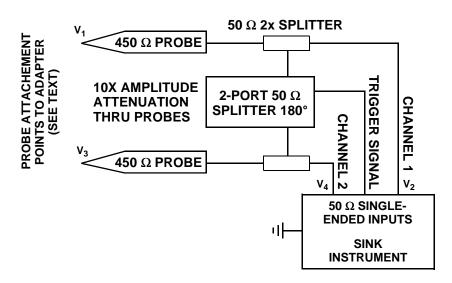

| 49<br>50 | E.3.1.3 Extracting a balanced trigger signal                                    |    |

| 50<br>51 | E.3.2 Unbalanced copper                                                         |    |

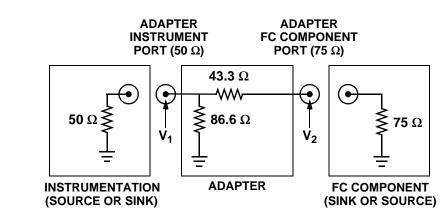

| 52       | E.3.2.1 Source and sink adapters for unbalanced copper variants (alternative 1) |    |

| 53       | E.3.2.2 Source and sink adapters for unbalanced copper variants (alternative 2) |    |

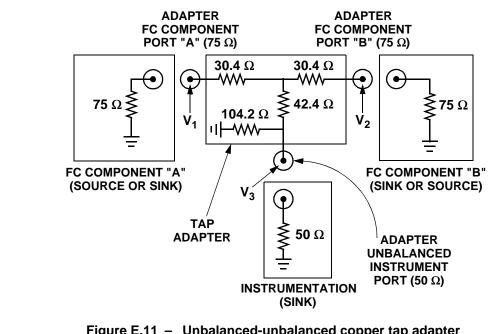

| 54       | E.3.2.3 Tap adapters for unbalanced copper variants (alternative 1)             |    |

| 55       | E.3.2.4 Tap adapters for unbalanced copper variants (alternative 2)             | 75 |

| 56       |                                                                                 |    |

| 1        | E.3.3 Optical                                       |

|----------|-----------------------------------------------------|

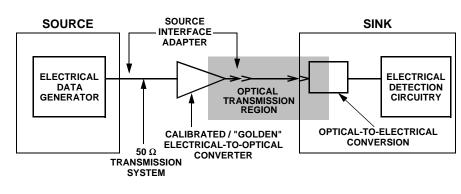

| 2        | E.3.3.1 Source interface adapters                   |

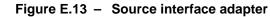

| 3        | E.3.3.2 Sink interface adapter 76                   |

| 4<br>5   | E.3.3.3 Optical tap                                 |

| 6        | E.3.4 Specific tests                                |

| 7        | E.3.5 Description of baluns                         |

| 8        | E.3.5.1 Balun requirements                          |

| 9        | E.3.5.1.1 Core and transmission-line requirements   |

| 10       | E.3.5.2 Specific wound core construction details    |

| 11<br>12 | E.3.5.2.1 Alternative 1 - wound toroid construction |

| 12       | E.3.5.2.2 Alternative 2 - wound toroid construction |

| 14       | E.3.5.2.3 Alternative 3 - wound bead construction   |

| 15       | E.3.5.3 Connection of wound cores into baluns       |

| 16       | E.3.5.4 Other source/sink adapter components 82     |

| 17<br>18 | Annex F Practical Examples for Jitter Compliance    |

| 18       | F.1 Introduction                                    |

| 20       | F.2 Elements contributing to Jitter 84              |

| 21       | F.3 Hubs                                            |

| 22       | F.4 Retiming Hubs                                   |

| 23       | F.5 Repeating Hubs                                  |

| 24       |                                                     |

| 25       |                                                     |

I

# Figures

| 4        |                                                                              | -  |

|----------|------------------------------------------------------------------------------|----|

| 5        | Figure 1 – Drawing conventions.                                              |    |

| 6        | Figure 2 – FC-0 transmitter interface (FC-PH Figure 9, Pg 17).               |    |

| 7        | Figure 3 – FC-0 receiver interface (FC-PH figure 10, pg 17)                  |    |

| 8        | Figure 4 – Fibre channel device                                              | 10 |

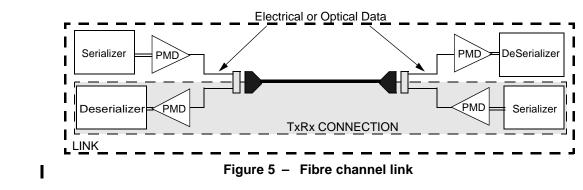

| 9        | Figure 5 – Fibre channel link                                                | 11 |

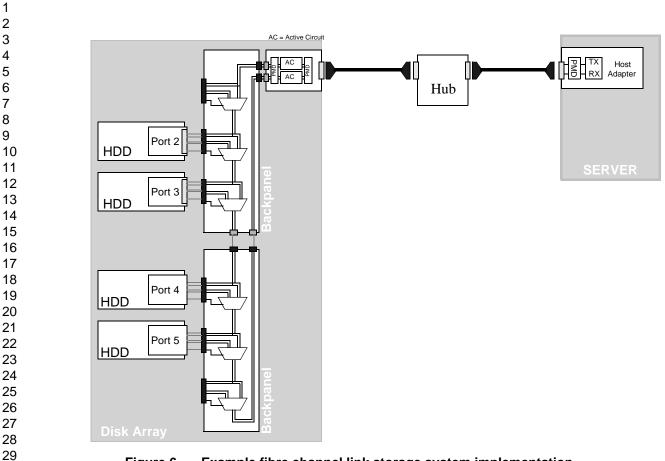

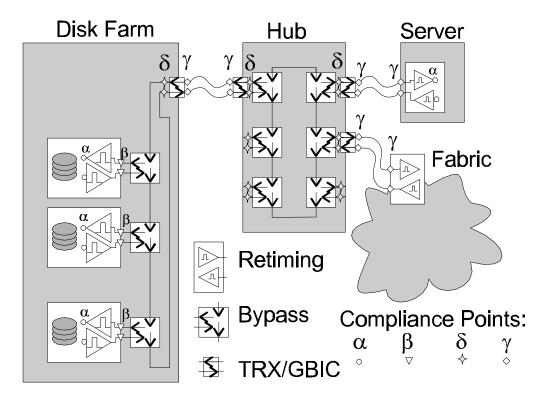

| 10<br>11 | Figure 6 – Example fibre channel link storage system implementation          | 12 |

| 12       | Figure 7 – Compliance points for example fibre channel links                 | 13 |

| 13       | Figure 8 – PLL response                                                      |    |

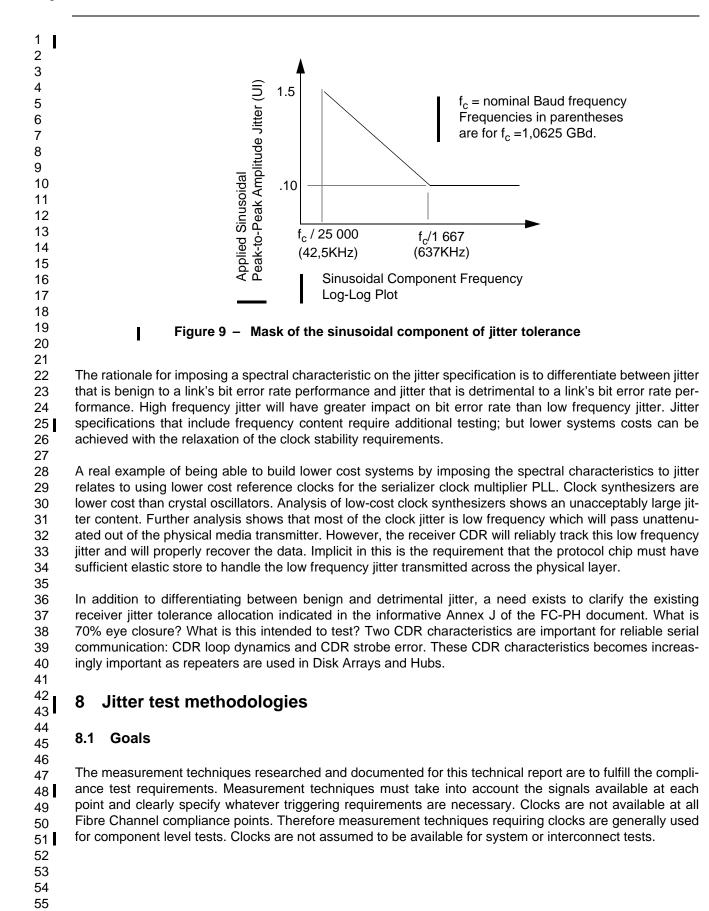

| 14       | Figure 9 – Mask of the sinusoidal component of jitter tolerance              |    |

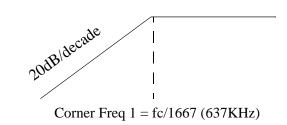

| 15       | Figure 10 – Jitter output measurement recovered clock filter characteristics |    |

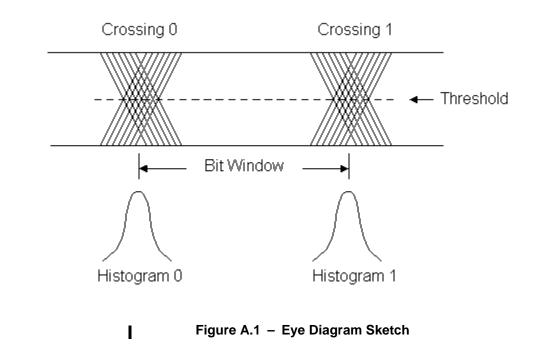

| 16       | Figure A.1 – Eye Diagram Sketch                                              |    |

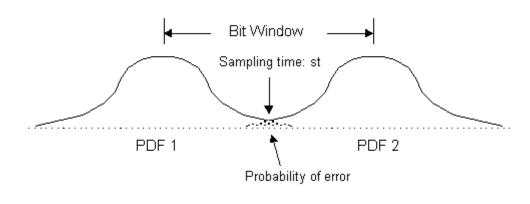

| 17       | Figure A.2 – Eye Sampling and Probability of Error                           |    |

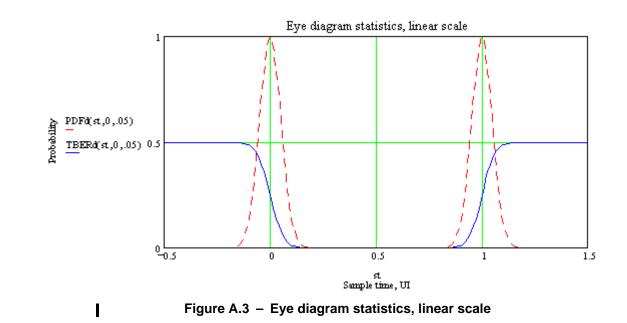

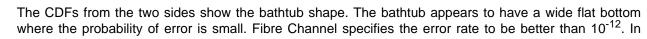

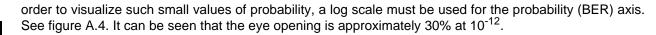

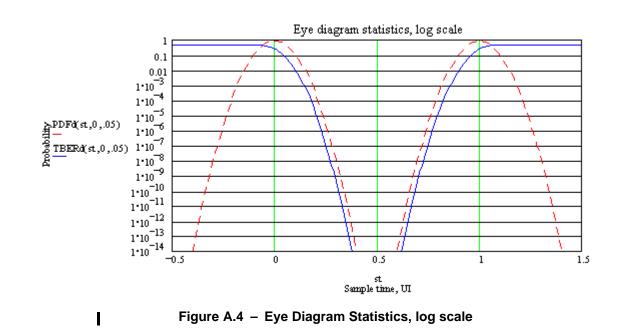

| 18       | Figure A.3 – Eye diagram statistics, linear scale                            |    |

| 19       | Figure A.4 – Eye Diagram Statistics, log scale                               |    |

| 20<br>21 |                                                                              |    |

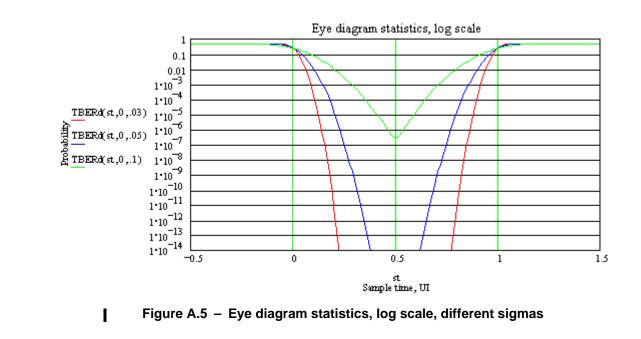

| 22       | Figure A.5 – Eye diagram statistics, log scale, different sigmas             |    |

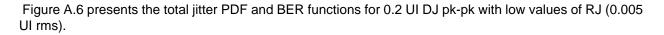

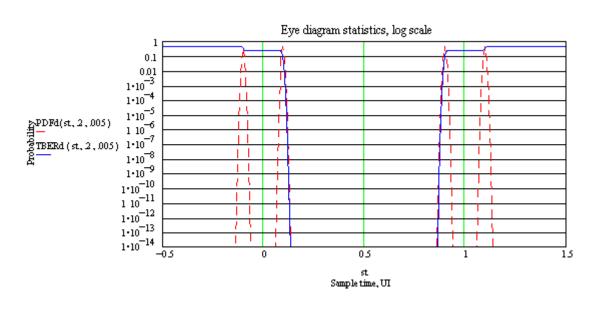

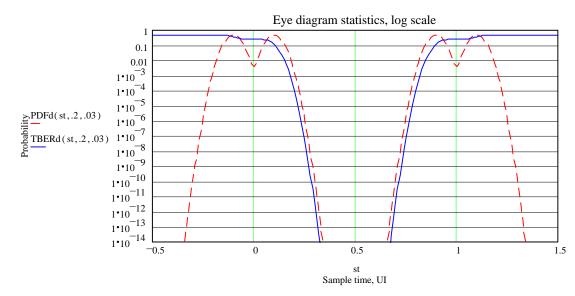

| 23       | Figure A.6 – Eye diagram statistics, dual-delta function DJ.                 |    |

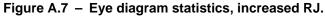

| 24       | Figure A.7 – Eye diagram statistics, increased RJ.                           |    |

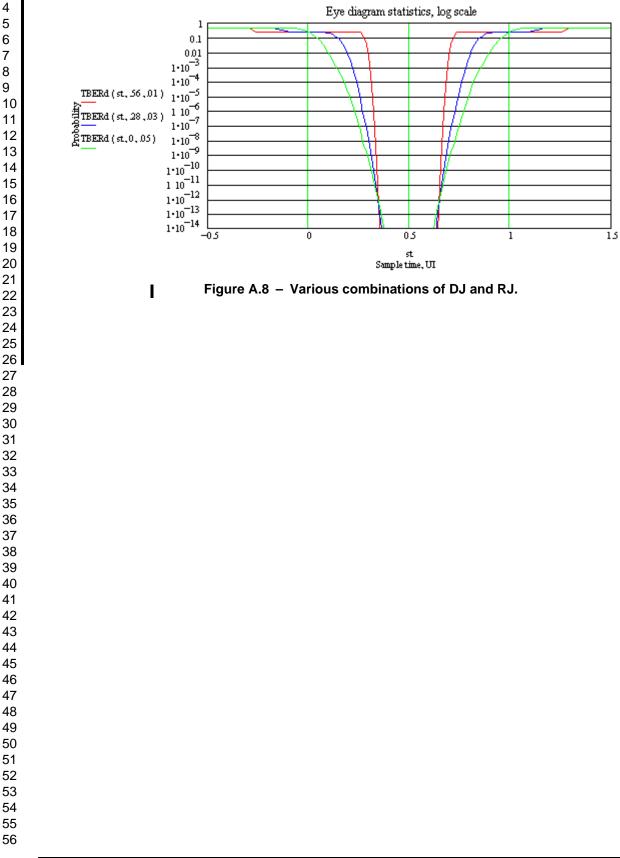

| 25       | Figure A.8 – Various combinations of DJ and RJ.                              |    |

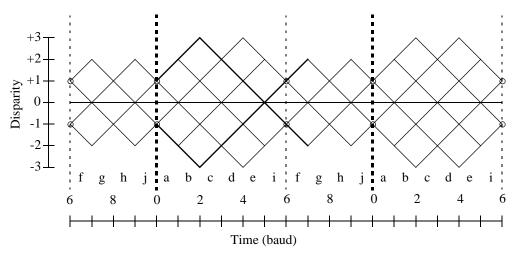

| 26       | Figure B.1 – 8B/10B code trellis diagram                                     |    |

| 27       | Figure B.2 – Fibre channel frame                                             |    |

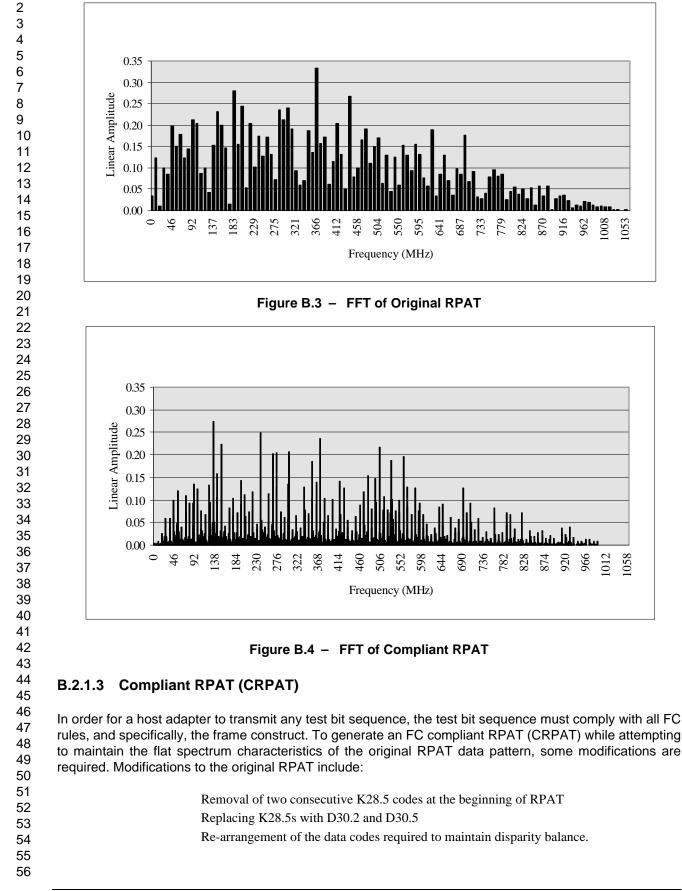

| 28       | Figure B.3 – FFT of Original RPAT                                            |    |

| 29       | Figure B.4 – FFT of Compliant RPAT                                           |    |

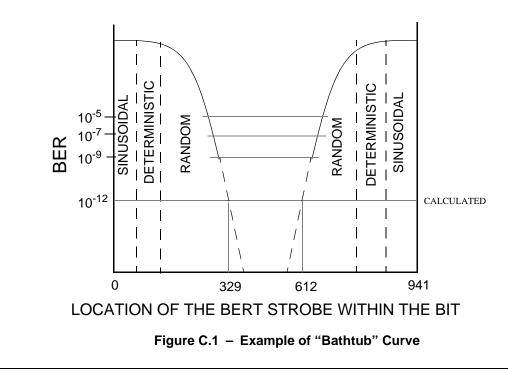

| 30<br>31 | Figure C.1 – Example of "Bathtub" Curve                                      | 44 |

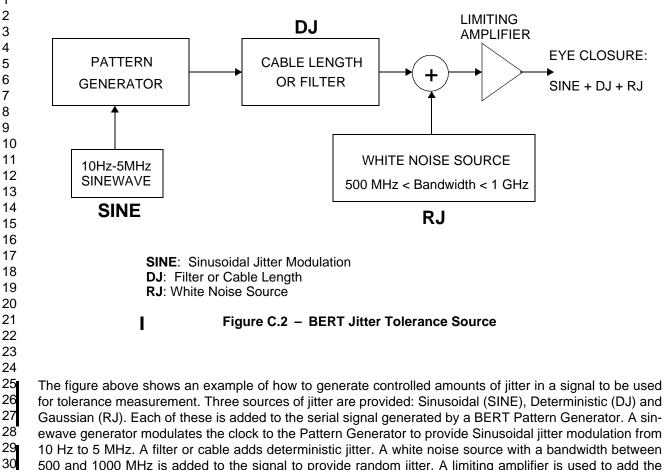

| 32       | Figure C.2 – BERT Jitter Tolerance Source                                    | 45 |

| 33       | Figure C.3 – Sinusoidal Jitter Tolerance Measurement                         | 46 |

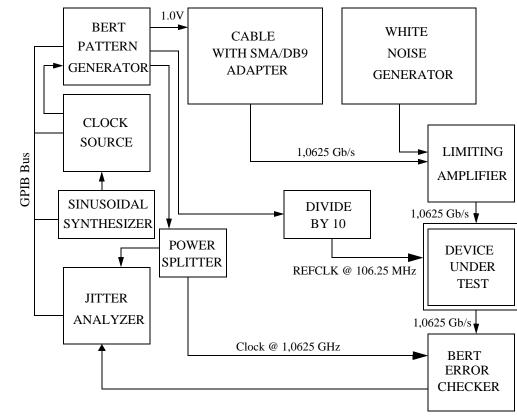

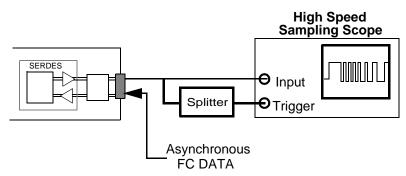

| 34       | Figure C.4 – Example of Jitter Test Setup for 10-bit SerDes                  | 47 |

| 35       | Figure C.5 – Direct Time Synthesis Jitter Tolerance Test Setup               | 47 |

| 36       | Figure D.1 – Time Domain Total Jitter Calculation.                           |    |

| 37       | Figure D.2 – Golden PLL Block Diagram                                        |    |

| 38       | Figure D.3 – Golden PLL Frequency Response                                   |    |

| 39<br>40 | Figure D.4 – Eye Mask                                                        |    |

| 40<br>41 | Figure D.5 – Time Domain Jitter Output Test (Golden PLL)                     |    |

| 42       | Figure D.6 – BERT Scan Jitter Output Test (Golden 1 EL)                      |    |

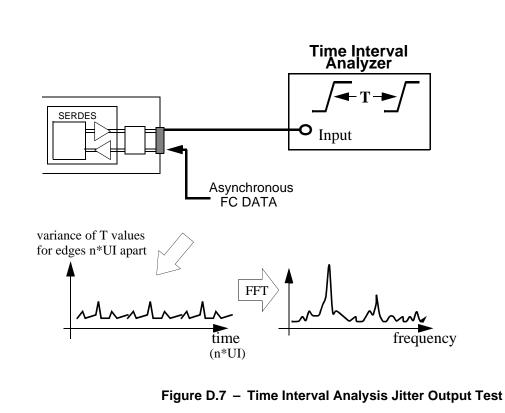

| 43       | Figure D.7 – Time Interval Analysis Jitter Output Test                       |    |

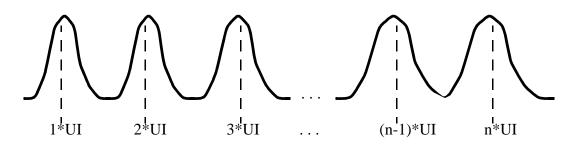

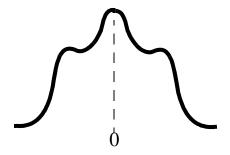

| 44       | Figure D.8 – Histogram of raw TIA data                                       |    |

| 45       | e e                                                                          |    |

| 46       | Figure D.9 – Histogram of Reduced TIA Data (multiples of UI removed)         |    |

| 47       | Figure D.10 – TIA Measurements using a Sampling Oscilloscope                 |    |

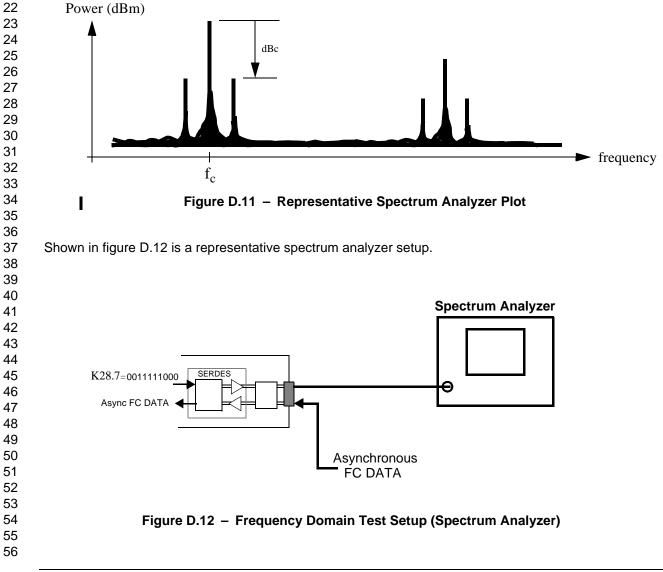

| 48       | Figure D.11 – Representative Spectrum Analyzer Plot                          |    |

| 49<br>50 | Figure D.12 – Frequency Domain Test Setup (Spectrum Analyzer)                |    |

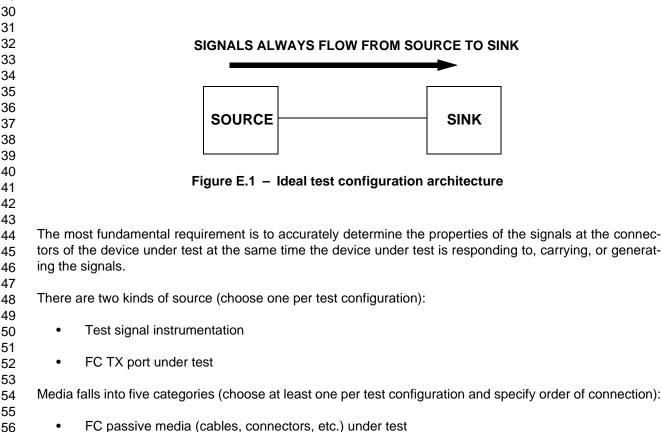

| 50<br>51 | Figure E.1 – Ideal test configuration architecture.                          |    |

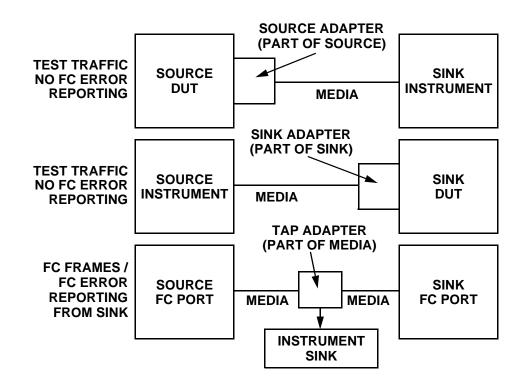

| 52       | Figure E.2 – Placement of adapters in test configurations                    |    |

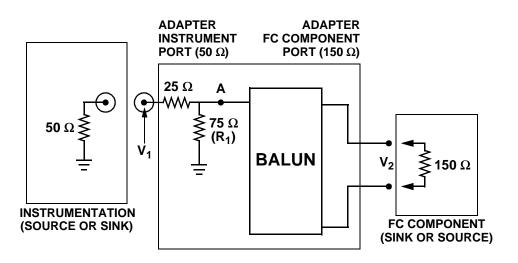

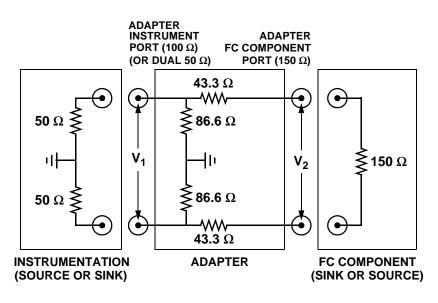

| 53       | Figure E.3 – Source/sink interface adapter matching network                  |    |

| 54       | Figure E.4 – Balanced-balanced source-sink adapter (alternative 1)           |    |

| 55       | Figure E.5 – Half of balanced-balanced source-sink adapter (alternative 2)   | 68 |

| 56       | -                                                                            |    |

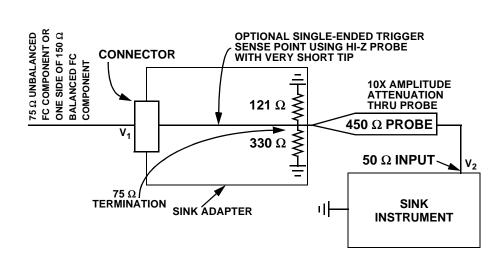

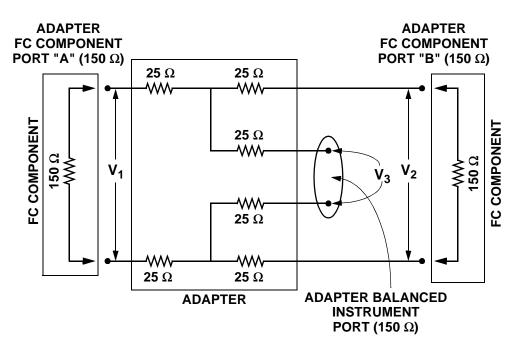

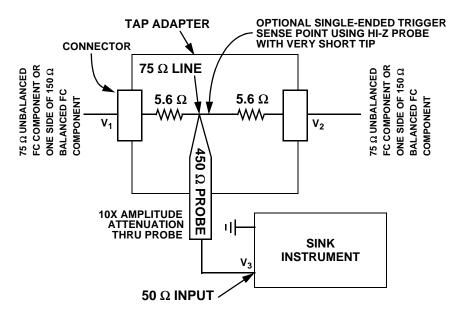

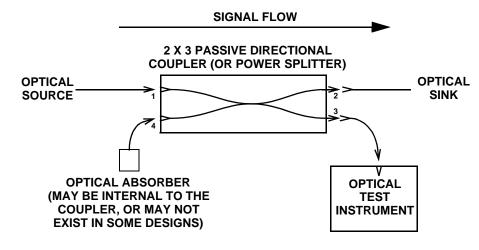

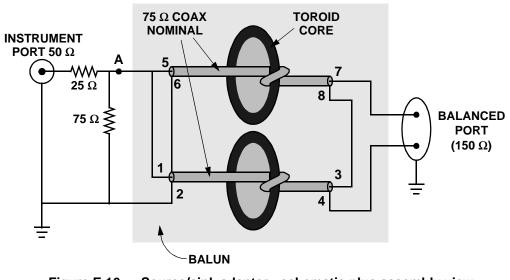

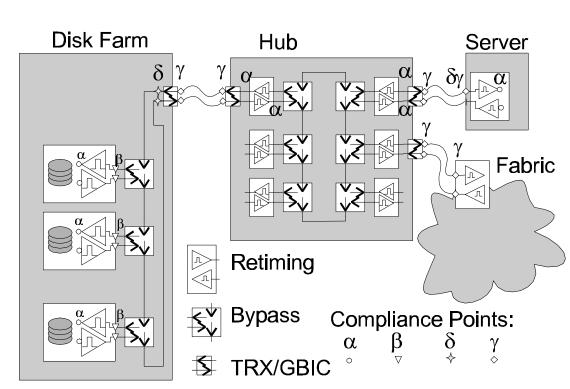

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                                                                                                                                            | Figure E.6 - Tap adapter matching network (balanced-balanced)Figure E.7 - Half of balanced-balanced tab adapter (alternative 2)Figure E.8 - Balanced-Unbalanced Tap Adapter ConfigurationFigure E.9 - Extracting a balanced trigger for a single-ended instrumentFigure E.10 - Source/sink interface adapter matching network for unbal - unbal copperFigure E.11 - Unbalanced-unbalanced copper tap adapterFigure E.12 - Basic optical systemFigure E.13 - Source interface adapterFigure E.14 - Sink interface adapterFigure E.15 - Optical tap adapter | . 71<br>. 72<br>. 73<br>. 73<br>. 74<br>. 75<br>. 76<br>. 77 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24                                                                                                                                                   | Figure E.16 – Source/sink adapter - schematic plus assembly viewFigure F.1 – Media Interchange Component Compliance Point ExamplesFigure F.2 – Example of Compliants PointsFigure F.3 – Hub Compliance Point ExampleFigure F.4 – Example of a repeating hubFigure F.4 – Example of a repeating hub                                                                                                                                                                                                                                                        | 85<br>86<br>87                                               |

| 25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |

| <ul> <li>38</li> <li>39</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> <li>45</li> <li>46</li> <li>47</li> <li>48</li> <li>49</li> <li>50</li> <li>51</li> <li>52</li> <li>53</li> <li>54</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |

I

Page viii

# Tables

| 1<br>2                                                                                                                                                                                                   | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                          | Table 1 - FC-PH GigaBaud portion of J.1 (FC-PH)Table 2 - Jitter contribution elements.Table 3 - Jitter tolerance componentsTable 4 - Jitter output measurement method summary comparisonTable 5 - 1,0625 GBaud jitter tolerance allocation for aRTable 6 - 1,0625 GBaud jitter output allocation (Passband of 637 KHz to greater than 5 MHz)Table 7 - 1,0625 GBaud jitter tolerance allocation exampleTable 8.1 - Eye closure penalties for low frequency pattern with n=12.Table B.2 - Low frequency patternTable B.3 - Low transition density patternTable B.4 - Half-rate and quarter-rate patternsTable B.5 - Ten runs of 3 assuming positive disparity                                                                                                                                             | 14<br>17<br>18<br>20<br>) 21<br>21<br>30<br>31<br>31<br>32<br>33                                                                                                                   |

| 19<br>20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36                                                                                                 | Table B.6 - Ten runs of 3 assuming negative disparity.Table B.7 - Valid fibre channel frame delimiters.Table B.7 - Valid fibre channel frame delimiters.Table B.8 - CRPAT Test Bit SequenceTable B.9 - JTPAT.Table B.10 - CJTPATTable B.11 - Supply Noise Test Bit SequenceTable B.12 - Compliant Supply Noise Test Bit SequenceTable D.1 - Frequency Domain ConversionTable E.1 - Ideal transfer function for source/sink adapter matching network of figure E.3Table E.3 - Transfer function for alternative 1 bal-bal source/sink network of figure E.4Table E.4 - Transfer function for bal-bal tap adapter of figure E.6Table E.5 - Ideal transfer function for unbal-unbal copper tap adapter of figure E.10Table E.7 - Ideal transfer function for unbal-unbal copper tap adapter of figure E.11 | <ul> <li>35</li> <li>37</li> <li>39</li> <li>40</li> <li>42</li> <li>42</li> <li>61</li> <li>66</li> <li>68</li> <li>69</li> <li>70</li> <li>71</li> <li>74</li> <li>75</li> </ul> |

| 37         38         39         40         41         42         43         44         45         46         47         48         50         51         52         53         54         55         56 | Table E.8 – Sample Test Configuration Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78                                                                                                                                                                                 |

## draft proposed NCITS Technical Report for Information Technology

## Fibre Channel \_\_\_\_ Methodologies for Jitter Specification

#### 1 Introduction

#### 1.1 Document scope and purpose

This document is an ANSI technical report on the definitions, measurement requirements, and allowed values of jitter on a 1,0625 gigabaud Fibre Channel link. These measurement methods and specifications are intended to be used for jitter and wander compliance testing. The purpose of this report is to provide background information for revising and expanding the jitter specification presently contained within the FC-PHn document and to increase the general understanding of jitter and wander in gigabaud serial transmissions. Documenting jitter test methods will motivate test and instrument companies to create test systems capable of supporting one gigabaud and higher transmissions on a single simplex serial connection.

Although this document is optimized for use with Fibre Channel the measurement methodologies are applicable to a broad range of serial transmission schemes.

This technical report applies to fully functional Fibre Channel subsystem and FC port implementations as well as to the individual components that comprise the link. This allows device and enclosure level qualification and the inclusion of system jitter contributions such as power supply noise, motor noise, crosstalk, and signal rejuvenaters.

The Jitter Methodology Technical Report is informative and advisory only. Certain contents of this document may be incorporated into the appropriate ANSI standards in the future.

#### **1.2** Document organization

This document consists of a main body and several annexes. The main body contains the summary of jitter measurement methodologies and the recommended new jitter test limits for compliance points. Jitter is a complex topic. The detailed discussions are embodied in the annexes due to the rapid deployment of low-cost, gigabaud links and the corresponding accumulation of new knowledge based on actual deployment testing.

### 2 References

The following documents contain provisions that, through reference in this text, constitute provisions of this technical report. At the time of publication the editions shown were valid. All standards and technical reports are subject to revision, and parties to agreements based on this technical report are encouraged to investigate the possibility of applying the most recent editions of the following list of documents. Members of IEC and ISO maintain registers of currently valid international standards

```

ANSI X3.230-1994 - Fibre Channel - Physical and Signaling Interface (FC-PH)

ANSI X3.297-1997 - Fibre Channel 2<sup>nd</sup> Generation Physical Interface (FC-PH2)

ANSI X3.303-1997 - Fibre Channel 3<sup>rd</sup> Generation Physical Interface (FC-PH3)

The three documents above are collectively referred to as FC-PHn

ANSI TR/X3.18-1997 - 10-bit Interface

```

### IEEE Std 610.7-1995

I

GR-253 - Issue 2 December 1995 - SONET

## Definitions and conventions

For the Jitter Working Group Technical Report, the following definitions, conventions, and symbols apply.

#### 3.1 Conventions

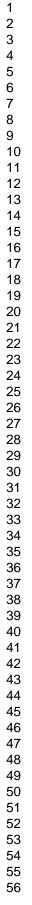

All drawings in this document will conform to the conventions in figure 1.

In the event of conflicts between the text, tables, and figures in this document, the following precedence shall be used: text, tables, and figures.

#### 3.2 Acronyms

I

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | RXReceiveSPATSSO PaSOFStart ofSSOSimultarTBCTransmit | n Pattern<br>Frame; a primitive bit sequence defined in FC-PH<br>neous Switching Outputs<br>t Byte Clock<br>nterval Analyzer<br>ter<br>t                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14                                                                |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                             |

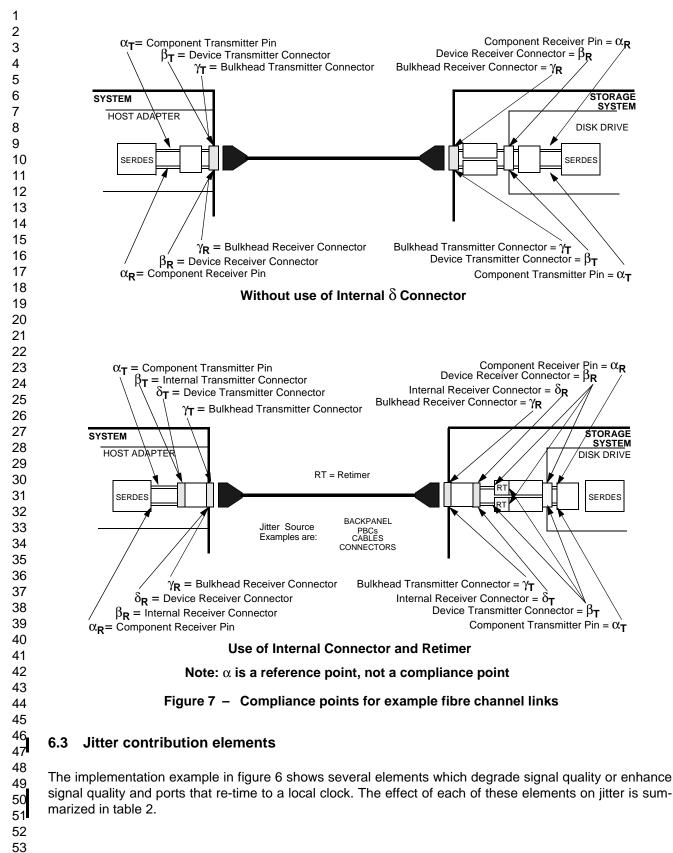

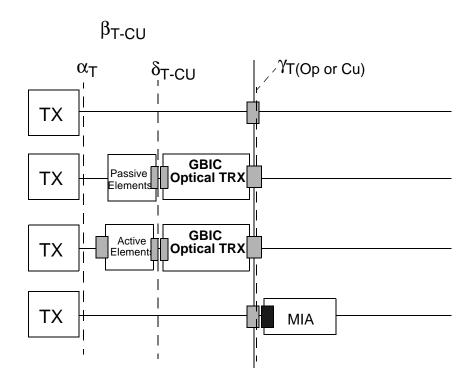

| 15<br>16<br>17                                                    | $\alpha_T, \alpha_R$                                 | Reference points used for establishing jitter budgets at the chip pins nearest the SERDES.                                                                                                                                                                                                                                                                                                                                  |

| 18<br>19<br>20                                                    | $\beta_T, \beta_R$                                   | Reference points used for establishing jitter budget at the internal connector nearest the re-timing element.                                                                                                                                                                                                                                                                                                               |

| 21<br>22<br>23                                                    | $\delta_T, \delta_R$                                 | Reference points used for establishing jitter budget at the internal user connector nearest the gamma point.                                                                                                                                                                                                                                                                                                                |

| 24<br>25<br>26                                                    | $\gamma_{\rm T}$ , $\gamma_{\rm R}$                  | Reference points used for establishing jitter budgets at the external enclosure connector.                                                                                                                                                                                                                                                                                                                                  |

| 27<br>28<br>29<br>30                                              | Baud                                                 | A unit of signaling speed, expressed as the maximum number of times per second the signal can change the state of the transmission line or other medium. (Units of Baud are $\sec^{-1}$ ) Note: With the Fibre Channel transmission scheme, a signal event                                                                                                                                                                  |

| 31<br>32                                                          |                                                      | represents a single transmission bit. [(Adapted from IEEE Std 610.7-1995 [A16].12)].                                                                                                                                                                                                                                                                                                                                        |

| 33<br>34<br>35<br>36                                              | Bit Error Rate (BER)                                 | A parameter that reflects the quality of the serial transmission and detection scheme.<br>The BER is calculated by counting the number of erroneous bits output by a receiver<br>and dividing by the total number of transmitted bits over a specified transmission                                                                                                                                                         |

| 30<br>37<br>38<br>39<br>40<br>41                                  |                                                      | period. For example, a BER of $10^{-12}$ is one bit error received in $10^{12}$ bits transmitted.<br>For a 1,0625 gigabaud datastream, $10^{-12}$ bit error rate translates into an average of one<br>bit error every 941 secs or one bit error every 16 minutes if the errors are occurring as<br>isolated single events. For cases where the errors occur in bursts the temporal<br>distribution must also be considered. |

| 42<br>43<br>44                                                    | Bulkhead                                             | The boundary between the shielded system enclosure (where EMC compliance is maintained) and the external interconnect attachment                                                                                                                                                                                                                                                                                            |

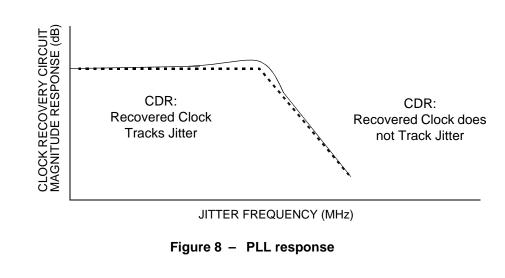

| 45<br>46<br>47<br>48<br>49<br>50<br>51<br>52<br>53                | CDR                                                  | The function is provided by the SERDES circuitry responsible for producing a regular clock signal from the serial data and for aligning this clock to the serial data bits. The CDR uses the recovered clock to recover the data.                                                                                                                                                                                           |

|                                                                   | Compliance points                                    | Physical positions between transmit and receive chips where measurements are<br>applied to determine if the properties satisfy the specification requirements.<br>Interoperability between components attached at compliance points is expected if the<br>specifications are met at the compliance points.                                                                                                                  |

| 54<br>55<br>56                                                    | Component                                            | Entities that make up the link. Examples are connectors, cable assemblies, transceivers, port bypass circuits and hubs.                                                                                                                                                                                                                                                                                                     |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12                                                                                                                            | Connectors                     | Electro-mechanical or opto-mechanical components consisting of a receptacle and a plug which provides a separable interface between two transmission media segments. Connectors may introduce physical disturbances to the transmission path due to impedance mismatch, crosstalk, etc. These disturbances can introduce jitter under certain conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                        | Coupler                        | A connector that mates two like media together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                        | Device                         | An entity that contains at least one Fibre Channel port. Examples are: host bus adapters, disk drives, and switches. Devices may have internal connectors or bulkhead connectors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

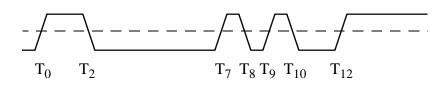

| 13<br>14<br>15<br>16                                                                                                                                                                   | Duty Cycle Distortion (DCD)    | Difference in the pulse width of a "1" pulse compared to the pulse width of a "0" pulse in a clock-like (repeating $0,1,0,1,$ ) bit sequence. DCD biases the DJ distribution and is measured at the ideal receiver threshold point.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17<br>18<br>19                                                                                                                                                                         | Enclosure                      | An outermost physical boundary surrounding one or more Fibre Channel ports that is intended to comply with EMI, safety, and other regulatory requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20<br>21                                                                                                                                                                               | Fibre Channel (FC)             | A collection of physical technologies described in the referenced Fibre Channel standards documents.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>52 | Fill Word                      | An IDLE or ARB primitive signal. These words are transmitted between frames, primitive signals, and primitive sequences to keep a link active (see FC-PHn clause 17).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                        | Gaussian                       | A statistical distribution (also termed "normal") characterized by populations that are<br>not bounded in value and have well defined "tails". Analog amplifiers are the most<br>important source of Gaussian noise in serial data transmissions. The term "random"<br>in this document always refers to jitter that has a Gaussian distribution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                        | "Golden"                       | An adjective describing a component having exceptionally tight performance and calibration requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                        | Interconnect                   | The means for providing the path between compliance points. The interconnect may<br>be as simple as a length of twinax or as complex as consisting of multiple components<br>such as: connectors, active elements (e.g. PBC's and retimers), hubs, and board<br>traces.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                        | Intersymbol Interference (ISI) | Data dependent deterministic jitter caused by the time differences required for the signal to arrive at the receiver threshold when starting from different places in bit sequences (symbols). For example when using media that attenuates the peak amplitude of the bit sequence consisting of alternating $0,1,0,1$ more than peak amplitude of the bit sequence consisting of $0,0,0,0,1,1,1,1$ the time required to reach the receiver threshold with the $0,1,0,1$ will be less than required from the $0,0,0,0,1,1,1,1$ The run length of 4 produces a higher amplitude which takes more time to overcome when changing bit values and therefore produces a time difference compared to the run length of 1 bit sequence. When different run lengths are mixed in the same transmission the different bit sequences (symbols) therefore interfere with each other. ISI is expected whenever any bit sequence has frequency components that are propagated at different rates by the transmission media. |

| 53<br>54<br>55<br>56                                                                                                                                                                   | Jitter                         | The deviation from the ideal timing of an event. The reference event is the differential zero crossing for electrical signals and the nominal receiver threshold power level for optical systems. Jitter is composed of both deterministic and Gaussian (random)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                          | content.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

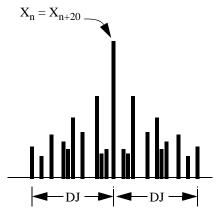

| Jitter, Deterministic    | Jitter with non-Gaussian probability density function. Deterministic jitter is always<br>bounded in amplitude and has specific causes. Four kinds of deterministic jitter are<br>identified: duty cycle distortion, data dependent, sinusoidal, and uncorrelated (to the<br>data) bounded. DJ is characterized by its bounded, peak-to-peak value.                                                                                                                  |

| Jitter Generation        | The quantity of jitter added to an incoming signal by a component, device, system, or media. This term is not used in this document. See jitter output.                                                                                                                                                                                                                                                                                                             |

| Jitter Output            | The quantity of jitter at a specific physical position in the link.                                                                                                                                                                                                                                                                                                                                                                                                 |

| litter, Peak-to-Peak     | For any type of jitter, the minimum, full range of the jitter values that excludes (includes all but) $10^{-12}$ of the total jitter population.                                                                                                                                                                                                                                                                                                                    |

| Jitter, Random           | Jitter that is characterized by a Gaussian distribution. Random jitter is defined to be the peak-to-peak value which is given to be 14 times the standard deviation of the Gaussian distribution for a BER of $10^{-12}$ .                                                                                                                                                                                                                                          |

| Jitter, RMS              | The root mean square value or standard deviation of jitter. For a Gaussian distribution, the RMS value is $1/14$ of the peak-to-peak value for BER $10^{-12}$ .                                                                                                                                                                                                                                                                                                     |

| Jitter Tolerance for CDR | The ability of a CDR circuit to recover an incoming datastream correctly despite jitter. It is characterized by the amount of jitter required to produce a specified bit error rate. Jitter tolerance is measured at the $\alpha_R$ point. The tolerance depends on the frequency content of the jitter. Since bit errors determine the tolerance, only devices capable of reporting FC port bit errors may be used. Jitter Tolerance tests are defined in Annex C. |

| Jitter, Total            | The sum of all random and deterministic jitter components.                                                                                                                                                                                                                                                                                                                                                                                                          |

| itter Transfer           | The ratio between the jitter output and jitter input for a component, device, or system often expressed in dB. A negative dB jitter transfer indicates the element removed jitter. A positive dB jitter transfer indicates the element added jitter. A zero dB jitter transfer indicates the element had no effect on jitter. The ratio should be applied separately to deterministic jitter components and Gaussian (random) jitter components.                    |

| Link                     | (1) A duplex serial data connection between two ports including the serializer, deserializer, PMD, connectors, and media. (as defined in FC-PH). (2) Two unidirectional fibres transmitting in opposite directions and their associated transmitters and receivers.                                                                                                                                                                                                 |

| Media                    | (1) General term referring to all the elements comprising the interconnect. This includes fiber optic cables, optical converters, copper cables, pc boards, connectors, hubs, and port bypass circuits. (2) May be used in a narrow sense to refer to the material in cable assemblies that are not part of the connectors.                                                                                                                                         |

| Physical Media Dependent | A transmit and receive network used to launch into a specific type of electrical or optical interconnect or to receive from a specific type of electrical or optical interconnect. The details of the network design depend on the type of interconnect.                                                                                                                                                                                                            |

| Port (or FC Port)        | A generic reference to a Fibre Channel Port. In this document, the components that together form or contain the following: the FC protocol function with elasticity buffers to re-time data to a local clock, the SERDES function, the transmit and                                                                                                                                                                                                                 |

I

1 receive network, and the ability to detect and report errors using the FC protocol. 2 3 Port Bypass Circuit An active multiplexer which is used to bypass FC ports or other ports that are unused 4 or nonfunctional. PBCs which do not re-time the signals to a local clock are 5 considered part of the interconnect. 6 Random 7 Random in this document always refers to jitter that has a Gaussian distribution 8 9 **Receive Network** A receive network consists of all the elements between the connector inclusive of the 10 connector and the deserializer or repeater chip input. This network may be as simple as a termination resistor and coupling capacitor or this network may be complex 11 12 including components like photodiodes and transimpedence amplifiers. The receive 13 network is bounded by interfaces R and d (figure 3). 14 15 Repeater A circuit for receiving either one-way or two-way communication signals and 16 delivering corresponding signals which are either amplified, reshaped, or both. 17 Repeaters are characterized by their jitter transfer. In the context of fibre channel jitter 18 methodology, the repeater could be a simple amplifier or a serial-data-in and 19 serial-data-out component that modifies jitter by re-generating the serial data edges to 20 a defined timing relation with a recovered bit clock. 21 22 A circuit that retransmits buffered FC data and whose transmit clock is derived from a Retimer 23 timing reference other than the received data. A retimer shall be capable of inserting 24 and removing fill words. In the context of fibre channel jitter methodology, a retimer 25 resets the accumulation of jitter in a link so that the output of a retimer has the jitter 26 budget of  $\alpha_{\rm T}$ 27 28 SERDES SERializer and DESerializer function. An example of Fibre Channel deployment is 29 based on a SERDES function with I/O functional and timing definitions as specified 30 in the "10-Bit Interface Specification." The CDR function is included in the 31 deserializer. 32 33 Transmit Network A transmit network consists of all the elements between a serializer or repeater output 34 and the connector inclusive of the connector. This network may be as simple as a 35 pulldown resistor and ac capacitor or this network may include laser drivers and 36 lasers. The transmit network is bounded by interfaces b and S (figure 2). 37 38 Unit Interval One nominal bit period for a given signaling speed. It is equivalent to the shortest 39 nominal time between signal transitions. UI is the reciprocal of Baud (Units of UI are 40 seconds) 41 42 Wander Long term deviation of the data rate frequency of a digital signal. Wander typically 43 refers to frequency deviation occurring at rates of less than 10 Hz. 44 45 Scope 46 47

### 48 **4.1 Motivation and goals**

The motivation for creating this technical report is to compile and provide information in order to clarify and to complete the jitter specification clause of the FC-PHn standard. The existing jitter specification is incomplete as a result of changes in how the electronics industry is implementing Fibre Channel systems today compared to how systems were expected to be implemented in the past. Examples of such changes are the increased interest in copper transmission, arbitrated loop implementation, and the use of repeaters in active hubs and disk arrays.

1 The goal of this technical report is to document the jitter requirements which will allow Fibre Channel devel-

- 2 opers to design low-cost, interoperable gigabaud links which will have bit error rates below 10<sup>-12</sup> and to

- 3 specify test methods which simplifies and standardizes compliance testing. 4

- Some specific areas for improvement in the current jitter specification are as listed below:

- 1.Spectral content defined on jitter

- 2. Measurement technique for jitter tolerance that works backwards from the receiver chip to the transmitter chip

- 3.Test method specified for jitter tolerance

- 11 4. Clarification of jitter compliance points.

13 This document provides a basis for revised jitter allocation budgets which clearly delineate interoperability 14 points and the transmitting and receiving compliance characteristics of the interoperability points. This is a 15 technical report and does not define a new set of jitter specifications but provides a basis for creating new 16 standards. The report contains a description of relevant test methods discovered during this effort. 17

#### 4.2 Authority

5

6 7

8

9

10

12

18

19 20

21

22

23 24

25

26 27 28

This Jitter Technical Report is generated by an Ad Hoc group of interested companies committed to providing a standard low cost interface for FC applications. This Ad Hoc group is sanctioned by and operates under the jurisdiction of the T11.2 technical committee of NCITS.

The Jitter Methodology Technical Report is informative and advisory only. Certain contents of this document may be incorporated into the appropriate ANSI standards in the future.

#### 5 **Jitter overview**

29 Serial data communication eliminates the physical and bandwidth limitations of clock and data bus trans-30 mission. In serial data communication, the data clock is not transmitted with the data, so the problem of 31 maintaining the clock and data temporal alignment is eliminated. However, other problems are created. 32 The key problems in high speed serial communication are minimization of jitter in data transmission, faith-33 ful clock extraction from the serial data, and network timing. 34

35 Jitter is simply the mis-positioning of the significant edges in a sequence of data bits from their ideal posi-36 37 tions. Sufficiently gross mispositioning will result in data errors.

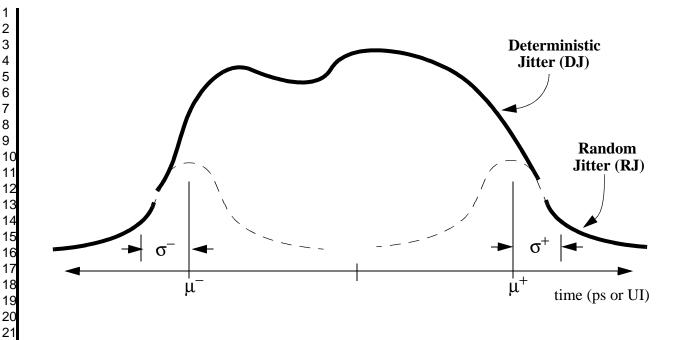

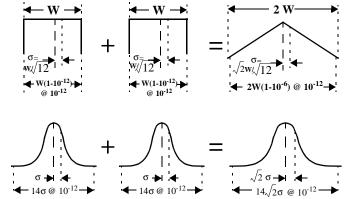

38 Jitter is characterized by two generalized types of jitter, deterministic (DJ) and random jitter (RJ). DJ and 39 RJ are also referred to as systematic and nonsystematic jitter respectively. The two categories of jitter are 40 used in jitter analysis because each category accumulates differently in the link. 41

42

Deterministic jitter is jitter that is due to non-Gaussian events. Deterministic jitter is always bounded in 43 amplitude and has specific causes. Four kinds of deterministic jitter are identified: duty cycle distortion, 44 data dependent, sinusoidal, and uncorrelated (to the data) bounded. An example of deterministic jitter that 45 is uncorrelated to data is power supply noise injection into the serial link. Deterministic jitter is measured as 46 a peak to peak value and adds linearly. 47

48

Random jitter is all jitter that is Gaussian in nature. An RMS value for random jitter is often measured due 49 to the long period of time required to acquire a statistically high confidence peak to peak value for a Gaus-50 sian event. Because practical measurements of random jitter must be measured as an RMS value, a 51 seemingly small amount of RMS random jitter corresponds to a large peak to peak value. If an RMS value 52 for random jitter is measured, it must be multiplied by 14 to result in a peak to peak random jitter value that 53 corresponds to a 10<sup>-12</sup> bit error rate; refer to the jitter mathematics in Annex A. A 10ps RMS random jitter 54 measurement represents a 140 ps peak-to-peak value or almost 15% of the total jitter budget for fibre 55

channel at 1063 Mbd. 56

The total jitter is the sum of the peak to peak values of deterministic jitter and random jitter. It is often diffi-cult to separate deterministic and random jitter from the measurement of total jitter. In this document, values of random jitter always refers to a peak to peak value. By defining random jitter as a peak to peak value, total jitter can always be a sum. The jitter output measurement methodologies covered in this docu-ment are separated into measurements of random jitter or deterministic jitter.

- It is not enough to consider only the jitter contribution of elements in a link in terms of total jitter. The behavior of the receiver in the presence of jitter must be specified. The key circuit in the receiver that must be specified is the Clock and Data Recovery (CDR) circuit. The CDR is the circuit that extracts the clock from the serial data. The recovered bit clock from the CDR is used to clock the serial data into a flip flop and deserialize the data for use by follow-on circuits.

I

CDR circuits, whether analog PLL-based (Phase-Locked Loops) or digital-based, react differently depending on the rate of change or frequency of the timing misplacement. If the rate of change is gradual and "trackable" by the CDR, no bit errors occur. If jitter is instantaneous (within one bit time) and of sufficient amplitude (such as 50% of a bit time), the CDR cannot track the timing shift and the recovered bit may be in error.

The ability of a CDR to successfully recover data in the presence of jitter is called jitter tolerance. Jitter tol-erance is measured as the jitter amplitude over a jitter spectrum for which the CDR achieves a specified bit error rate. A jitter tolerance measurement is performed as a bit error rate measurement under the pres-ence of a controlled amount of jitter.

Fibre Channel is a plesiochronous network. The FC network timing mechanism for accommodating nomi-nal Baud variation involves port elasticity buffers. Without this mechanism, a port cannot tolerate frequency differences. This means each port is responsible for absorbing the frequency difference and retransmitting based on its local frequency. Transmission frequency is assumed to be different at each port. Every Fibre Channel port has an elasticity buffer to absorb this frequency difference. The mechanism for network tim-ing is assumed to work and the implications regarding buffer size are not covered in this document.

Achieving the targeted 10<sup>-12</sup> bit error rate for an open market, multi-vendor solution, requires specifying and controlling the jitter response and contribution of the various components, devices, and systems used in the network.

#### Fibre channel physical layer implementation

## 6.1 FC-0 interface overview

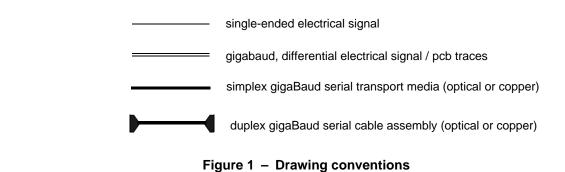

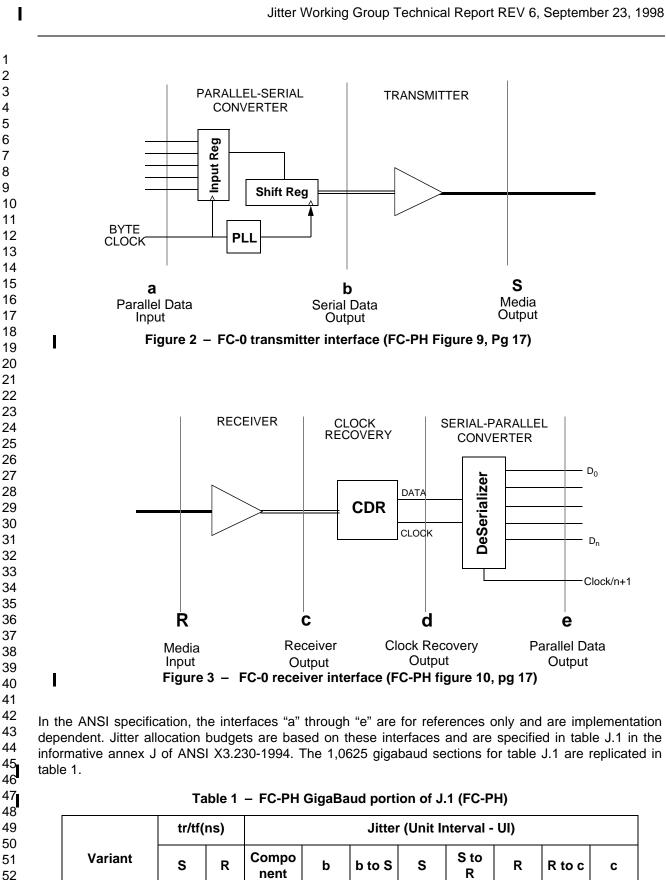

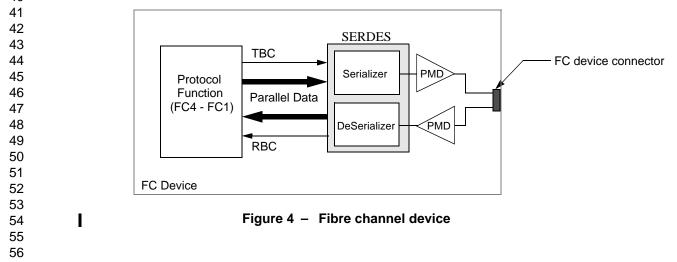

The ANSI X3.230-1994 (FC-PH) specification defines interfaces within Fibre Channel's FC-0 layer which span the parallel encoded transmitted data interface to the parallel, encoded receiver interface. The FC-0 transmitter interface definitions and the FC-0 receiver definitions are shown in figure 2 and figure 3 respec-tively.

DJ

RJ

Total

0,08

0,12

0,20

0,12

0,20

0,32

0,20

0,23

0,43

53

54

55

56

100-SM-LL-L

0,37

NA

0

0

0

0,20

0,23

0,43

0.08

0,35

0,43

0,28

0,42

0,70

|                            | tr/tf( | ns) | Jitter (Unit Interval - UI) |                      |                      |                      |                   |                      |                      |                      |

|----------------------------|--------|-----|-----------------------------|----------------------|----------------------|----------------------|-------------------|----------------------|----------------------|----------------------|