Shanghai Hometown Microsystems Inc

Volume 2, Number 6, June 2005

# System Design Frontier

#### **Editorial Board**

Carl Pixley Senior Scientist, Synopsys Inc Masahiro Fujita, Professor, The University of Tokyo Michael McNamara, Senior VP of Technology, Verisity Ltd Gabriele Saucier, Chairman of Design and Reuse Inc, IEEE Fellow Wayne Wolf, Professor, Princeton University, IEEE Fellow

# Hometown Outsourcing and BPO

Off-shore EDA Software Development & Technical Support Search Engine Optimization & Pay Per Click for Online Marketing

The Advancing Ubiquitous Society — Revealing What's Next, Changing Tomorrow

Tuesday, October 4 - Saturday, October 8, 2005 (5 days) Makuhari Messe (Nippon Convention Center)

### **Combined Exhibition of Advanced Technologies**

P+10 0:0 = 17

SPONSORSHIP CEATEC JAPAN Organizing Committee

JEITA Japan Electronics and Information Technology Industries Association (JEITA)

Communications and information network Association of Japan (CIAJ)

JPSA Japan Personal Computer Software Association (JPSA)

# 2005第九届中国国际软件博览会 INT'L SOFT CHINA 2005 Periotrotion: Doc 2004 April 2005

# Registration: Dec. 2004 - April. 2005

Exhibition, Forums & Business Meetings Come Here - We Introduce China Software Market to the World Join Hands - Let's Explore Software Markets together

We Invite Over 20 Countries and Regions. We Invite Global TOP 500. We Invite China TOP 500. We Invite Government & Industrial Buyers.

Sponsor:

Ministry of Information Industry

Organizers:

China Software Industry Association

China Information Industry Trade Association

China Information Industry Trade Association

China Information Industry Trade Association

China Information Industry Trade Association

China Information Industry Trade Association

China Information Industry Trade Association

China Information Industry Trade Association

China Information Industry Trade Association

China Information Industry Trade Association

China Information Industry

Co-organizers:

www.solu.net chanye.sina.net www.ccidnet.com

Time:

June 23-25, 2005

Venue:

China International Exhibition Center, Beijing, P.R.China

Enquiry:

8610-62143871, 8610-51527167, 8610-62188579(F)

Visit :

www.csia.org.cn

E-mail :

csia@css.com.cn

# Content

| Editorialformation of INformationEditor-in-Chief7                                                           |

|-------------------------------------------------------------------------------------------------------------|

| Power Optimization Within Nanometer Designs<br>Dr. Danny Rittman9                                           |

| <i>DI</i> . <i>Danny</i> Kuiman                                                                             |

| <i>Epistemologically Multiple Actor-Centred System:</i><br><i>Or, EMACS at work!</i>                        |

| <i>Yuwei Lin</i>                                                                                            |

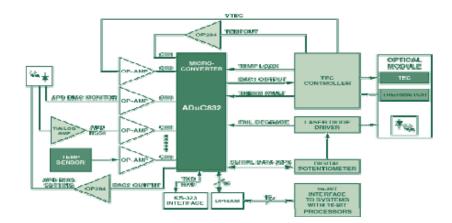

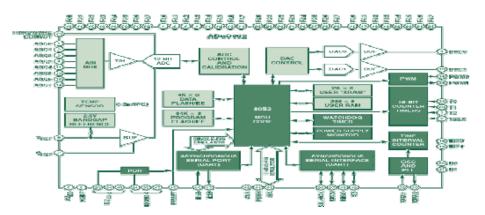

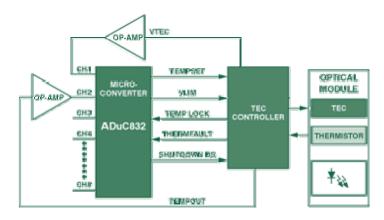

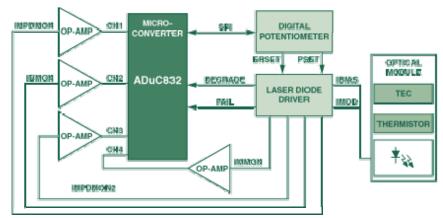

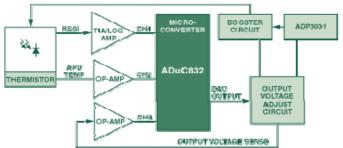

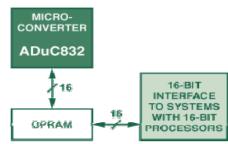

| Single-Chip Digitally Controlled Data-Acquisition as Core of Reliable DWDM Communication Systems            |

| Mark Malae                                                                                                  |

| Towards Next Generation URLs                                                                                |

| Thomas A. Powell and Joe Lima41                                                                             |

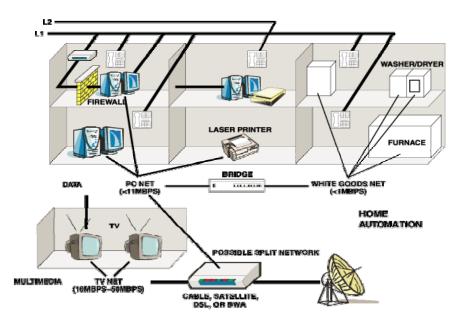

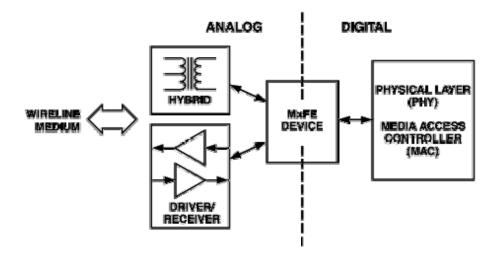

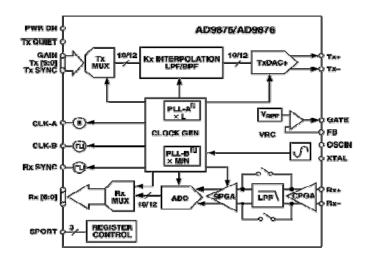

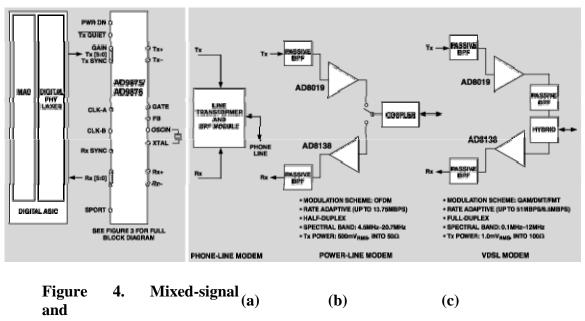

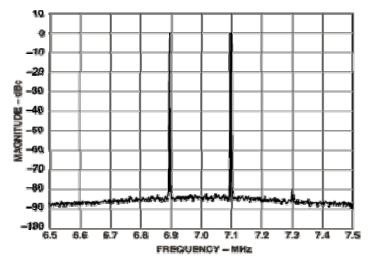

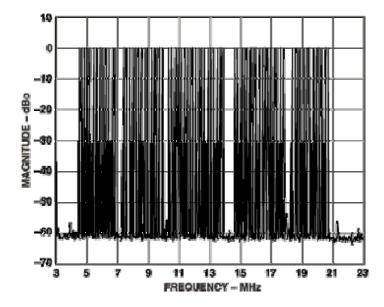

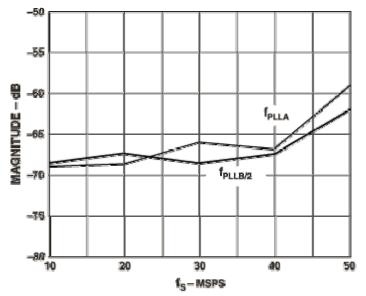

| Versatile Mixed-Signal Front Ends Speed Customized Design of<br>Wireline Broadband Modems and Home Networks |

| Joseph DiPilato, Iuri Mehr, Brian Harrington                                                                |

| A Natural Model for EDA Sensible IP Behavior                                                                |

| Melanie Yunk, Silicon Integration Initiative                                                                |

| The daemon, the gnu, and the Penguin                                                                        |

| A History of Free and Open Source                                                                           |

| Peter H. Salus                                                                                              |

**Copyrights** Copyright © 2004 ~ 2005, Shanghai Hometown Microsystems Inc ("Publisher"). All rights reserved. No part of System Design Frontier ("Publication") may be reproduced, transmitted, or translated, in any form or by any means, electronics, mechanical, manual, optical, or otherwise, without prior written permission of Publisher.

Disclaimer Publisher makes no warranty or any kind, express or implied, with regard to this Publication

#### EDITORIAL

### The formation of INformation Editor-in-Chief

In my one of previous editorials I recalled that, the first time I used the Internet was using the only email account in my colleague campus to contact with my first advisor abroad, it was not free, and that was in Beijing in later 1993. A year later, while I was attending my first graduate school, I got to know the first Internet browser Mosic as well as its commercial version Netscape, all a sudden, everyone was eager to create their own homepages. In less than two years, while I was attending another graduate school, yahoo! went to public, and all the people surrounding me were discussing the Internet mania, at that time both Amazon and eBay were still startups, and google was not even born yet. As a graduate student, searching relevant cited papers was my daily routine since it is part of research business, unfortunately, both search engines and directories at that time were not that as efficient as that of the-stateof-the-art. In other words, the information was not as that rich as that of today, and for the available scare information online, they were neither easy to locate, nor quick to retrieve.

Ten years passed, where are we here now and where can we get from here? Information now can be retrieved by anyone at anytime, anywhere in anyway. You can access the Internet, not only from either office or home, but also either at the airport or even on the road. The Internet now is not only rich in images, but also audios and videos beyond plain texts. PC is not the only Internet access device any more, as the merging of computation, communication and consumer electronics, Internet ready mobile phones, power-line, even the freezer at your kitchen are becoming more and more popular. Let's take China as an example, in China, the number of Netizen is 87 million as of June of 2004 according to an official report released by CNNIC; on the instant messenging side, the market leader NASDAQ listed Tencent owns 320 million registered members through its QQ platform, an IM system similar to MSN and yahoo! Messenger; on the mobile communication side, two hundred million Chinese possesses at least one mobile phone, and the number of short messages sent by Chinese in the first quarter of 2005 is 217 billion, according the Minister of Information Industry Ministry in China. We can see in the beginning of this century, now the key problem is not how to deal with information deficiency problem, instead it is how to tackle the challenge of information overflow

According to my observation, the Internet is just like a jet, which can make your information journey faster and cheaper, now without jet, can people still travel? Of course, except you are one of the few highly busy tycoons in the Silicon Valley, you do not need a jet (suppose you can afford that) to get to work. The key concern for you is how to choose most suitable car and find a most efficient route to reduce your commute time. The choice of such a car and such a route, here at Hometown Microsystems we call it the *formation of INformation*

但您是否察觉到随着IT系统的日益庞大和复杂,传统的人员维护已无法满足,而导致IT系统出现非良好运作, 电日本拥有20,000多家用户具有丰富的 使得它的作用没有得到充分的发挥,产生了巨大的损失? 这个时候您就需要划时代的日立JP1系统运行管理软件,来帮助您有效管理整个IT系统。

JP1系统运行管理软件由7个模块组成,具备高可靠性,易导入性,易操作性等特点,从四大方面支持企业的IT系统: (1)提高IT系统的运行质量,提供24小时×365天的高可靠性服务; (3) 提高IT环境的性能和实用性; (2) 减少IT系统的维护工作量和维护费用;

(4) 减少IT环境潜在的风险。

#### 追求高效无止境

IT系统运行管理经验,能够根据企业特点 进行组合和提供特定解决方案。 ■在日本销售量(97·02年连续六年)及客户 满意度(99年)名列前茅。 ■ 被广泛运用于金融、通讯、制造、电 众多行业。

日立信息系统(上海)有限公司 021-64728068 如果您需要了解具体信息清登录http://www.hiss.cn/p1 北京分公司 010-64679211 装252 广州分公司 020-38785566 认证业务伙伴:ePRO 易宝电脑系统(北京)有限公司 电话:010-64689391转213 或512 Shitch ===== 北京宇信鸿泰科技发展有限公司 电话:010-85288708

# Power Optimization Within Nanometer Designs

Dr. Danny Rittman danny@tayden.com

#### Abstract

As the integrated circuits (ICs) are scaled into deep nanometer dimensions and operate in giga-hertz frequencies, power optimization is becoming critical in determining system performance and reliability. Power dissipation is becoming one of the most challenging design constraints in nanometer technologies. For example, among various design implementation schemes, standard cell ASICs offers one of the best power efficiency for high-performance applications. The flexibility of ASICs allow for the use of multiple voltages and multiple thresholds to match the performance of critical regions to their timing constraints, and minimize the power everywhere else. Typically, implementing nanometer-scale ICs begins and ends with wires. The ability of an IC to perform its function is dependent upon the transformation of that function into a specific configuration of wires and their connections to cell-level and, ultimately, to transistor-level behaviors. This paper discusses nanometer power aware design, optimization and management that operate upon a behavioral design description.

#### Introduction

The steady downscaling of transistor dimensions over the past two decades has been the main reason to the growth of silicon integrated circuits (ICs) and the electronic industry. The more an IC is scaled, the higher becomes its packing density, the higher its circuit speed, and the lower its power dissipation. These have been the key in the evolutionary progress leading to today's computers and communication systems that offer superior performance, dramatically reduced cost per function, and much-reduced physical size compared to their predecessors. As ICs marched down the technology path from 0.13 to 90 nm, designers and their customers enjoyed faster and more complex IC, without a significant increase in power consumption. But at 90 nm and below, the cost of developing nanometer designs significantly increased, particularly in masks and NRE costs. In addition, more designs are targeted for mobile applications running off batteries resulting in new design constraints for both dynamic and static power. Finally, the physics of the silicon (power related) started to work against engineering. However, the increase in leakage current was most critical. Thinner gate oxides and lower threshold voltages result in a significant increase in leakage current and static power consumption. There are, in total, seven additional secondary sources of leakage current, all of which get worse at 130 nm and even more so at 90 nm and 65 nm. We begin with an overview of a power fundamentals and behavioral design methodology. We will continue with a description of how power issues interact with the nanometer design space and describes how some of these issues can be influenced early in the design cycle. The industry direction is towards behavioral design that is becoming an absolute necessity in order to address the many nearly intractable issues that rise in nanometer design. In 2004, consumer electronics, mostly mobile, battery-powered applications is one of the major driving forces in the growth of fabless IC companies. Gartner/Dataquest forecasts that global revenue from semiconductors used in consumer electronics will increase by 20% in 2004 (\$34.1 billion) and even more in 2005. Many of these devices will go into mobile and low power applications. No Doubt, the market is demanding an urgent solution to the nanometer power crisis.

#### **Power Fundamentals**

When discussing power fundamentals the two subjects to explore are two main effects that contribute to the total power dissipation on a chip. These effects are dynamic power and leakage power. Dynamic (also called active) power occurs when a transistor switches state and is due to capacitive charging and discharging. Leakage power arises due to leakage (also called static) current flowing through the transistor. Leakage current can even consume power in standby or sleep modes of operation. With each step down in process geometry, leakage power has more or less doubled in magnitude. For example, 90nm process technology leakage power contributes 40 to 50 percent of the total power budget, with active power dissipation from transistor switching making up the rest. The management of power effects in the design process should also be concerned with power integrity. This includes analysis of IR drop, which degrades performance and reduces noise immunity, and electromigration (EM). EM is due to high current density causing metal electrons migration, resulting in open or short circuits. EM also causes performance and reliability issues over time. The key power management challenges are to reduce device power consumption by controlling dynamic and leakage effects, and eliminate power-related failures by addressing IR drop and EM.

#### **Current approaches**

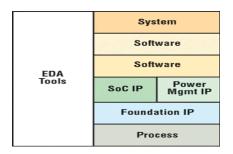

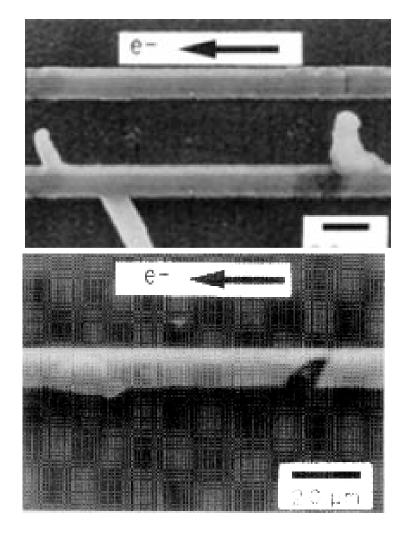

The VLSI technology today comprises devices because of their unique characteristic of negligible standby power, which allows the integration of tens of millions of transistors on a processor chip with only a very small fraction (<1%) of them switching at any given instant. As the CMOS dimension, in particular the channel length, is scaled to the nanometer regime (<100 nm), however, the electrical barriers in the device begin to lose their insulating properties because of thermal injection and quantum-mechanical tunneling. This results in a rapid rise of the standby power of the chip, placing a limit on the integration level as well as on the switching speed. IC design companies are mainly attacking the issue of nanometer power consumption. (Fig. 1) While individually effective in their own target areas, the current solutions really only provide a partial solution to the problem.

Fig. 1 – Nanometer power consumption issue.

Batteries have made significant strides in providing more power in a smaller space and with less weight. Yet these gains only offset the demand for more power as these products (laptops, PDAs, MP3 players, etc.) incorporate faster processors, advanced graphics and now micro hard drives in MP3 devices. Better batteries will not do it alone. EDA tools are used extensively throughout the design process. Analysis tools are doing excellent job of problem identification at the silicon level, but often do not provide a solution to the designer. The RTL optimization provides improvement in power, but as it is not tied to the actual silicon performance, it is at a fairly high level. Synthesis optimization for power is constantly improving, yet not enough for deep nanometer regime.

The wafer fabs have addressed the issue of power as well. Most fabs and independent foundries offer several process variations at 130 and 90 nm, each optimized for speed, power, or voltage. But all this really offers the designer is the classic power/speed tradeoff. They can have a high-speed high-leakage process or a low-speed low-leakage process. By raising the voltage threshold of the transistors, the leakage can be reduced, but this comes at a corresponding decrease in the speed of the transistor. The industry direction is to incorporate power management considerations throughout the design levels and not only at high level.

#### **Efficient Power Management**

In order to achieve effective power management an entire range of design techniques and tools must be applied, throughout the entire design process, to progressively diminish the main sources of power dissipation. Considering the system as a whole, applying power reduction measures through the process technology, circuit design, architecture, system and software, is the best strategy for effective power management. At the system level, it is clear that excessive clock speeds will dissipate power unnecessarily. The system must be clocked at a sufficient rate to meet the application software needs, and not higher. Along with determining the slowest possible clock speed, applying the lowest possible supply voltage also helps to reduce dynamic power. Conveniently, supply voltage scales with feature size. However, lowering supply voltage requires that device thresholds are also lowered, which can increase leakage currents.

Partitioning the architecture to enable multi-voltage design can help to ensure that different parts of the chip operate at the optimum clock rates and supply voltages, ensuring both dynamic and leakage power are minimized. Due to the fact that many applications demand processing performance that varies over time between compute intensive operations, background processing and system idle, an optimized system would adjust voltage and frequency to meet each demand. In general, the decisions taken at the system level will have the greatest impact on overall power consumption. Such decisions include the functionality (for example, whether floating-point arithmetic is really necessary), hardware-software partitioning, bus strategy, clocking strategy, physical partitioning and selection of intellectual property (IP). Choice of memory architecture and implementation can have a significant effect on power budget. Applying well-known techniques during implementation such as RTL clock-gating, gate-level optimization and operand isolation can help to reduce dynamic power considerably. Clock-gating can be applied globally, or at a block level. It is important that application of clock-gating techniques does not impair testability or the ability to perform timing and formal verification. Leakage reduction techniques such as multi-Vt

optimization, active well bias and state retention power gating can help to reduce leakage power considerably. Drawn feature sizes less than 100 nm (0.10 micron), dynamic power scaling trends can also lead to major packaging problems. To alleviate these concerns, techniques like thermal monitoring and feedback mechanisms can limit worst-case dissipation and reduce costs.

#### **Low-power IP Methods**

Low-power IP methods offer savings in power through the use of higher threshold transistors and by designing circuits for reduced power, but these methods come with a speed penalty. For low-speed applications, this technique produces acceptable results. The faster speed of the 130-nm process will offset the loss of performance of the low-power IP. For current-generation wireless baseband applications (cellular, Bluetooth) this works well. But for next-generation wireless products with greater graphics and video capabilities, and with high-speed wireless Internet connections, the performance trade-offs are unacceptable. What mobile electronic SoC designers require is a way to have their cake and eat it too.

They cannot make any sacrifices to the performance of their designs and still meet the hard cost requirements that are dictated by the consumer. We all want our cell phones to have a camera and Internet access, but we still want them to fit in our pockets. As more complex and high-performance applications go mobile, SoC designers have no choice but to adopt the use of power management IP to control the increasingly severe dynamic power and leakage power issues.

#### **Nanometer Power Obstacles**

**Design Size and Complexity** – Larger and more complex circuitry requires more power – for many reasons. Typically, it is a good idea to reduce the number of transistors required to implement a design, which reduces the total switching activity and the nanometer main issue, leakage current. It also helps overall if the design is organized hierarchically. When a design is organized hierarchically, it can be treated as a modular structure of cells. The largest possible collection of cells can be optimized, with the lowest level of cells instantiated from a library having a selection of cells matching the optimization function: low power, specific voltage, specific clock speed, and so on. This provides a basis for planning and estimating wiring, and the opportunity to revise the architecture or the wiring plan to deal with wire-related issues.

**Timing (Signal Integrity dependent)** – Signal Integrity has major impact on power design. Optimizing the architecture prior to establishing the RTL description, can ensure optimum power and thus minimum opportunity for these effects. This is accomplished through simultaneously optimizing power and clock speed within appropriately segmented domains of the design; a library of high level (complex) cells characterized for various speed and voltage combinations supports this optimization process. If need be, the power constraints can then be selectively relaxed to improve performance or area considerations. An essential need in the entire nanometer-scale optimization process is access to cells characterized for signal integrity, switching power and other characterizations.

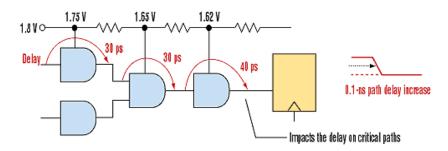

IR Drop - This issue is typically embedded within automated power optimization of

architecture in cooperation with a characterized library of macro cells, or even of large IP blocks. EDA tools provide a successful solution predicting IR drop effects based on power grid requirements derived from an architectural design.

Voltage drops through a chain of logic gates can severely influence SoC timing closure. Here, 0.1 ns of additional delay, which may not have been accounted for in static timing analysis, is imposed by an aggregate drop of less than 200 mV.

Image: Magma Design Automation

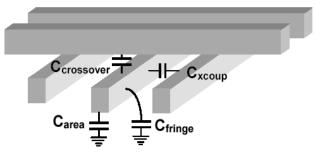

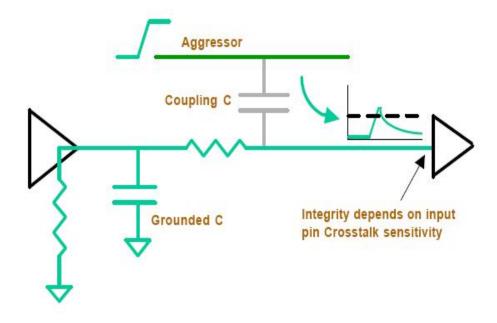

**Crosstalk and Inductance** – With the scaling of the horizontal dimensions of wires, the aspect ratio of the horizontal to vertical dimensions is reduced, resulting in increased ratios of coupling capacitance to ground capacitance (over or under crossovers or to substrate). A significant crosstalk noise may occur due to the relative rate of switching (rise and fall times of the signals) and the amount of mutual capacitance. Crosstalk noise, depending on its amplitude and its timing may cause false switching or delays. The ability of a physical design environment concurrently to analyze and correct for these various signal integrity problems during a physical implementation flow is highly dependent on the design system architecture. An integrated design closure in a timely manner.

This issue is also typically embedded within automated power optimization of architecture, performing global wiring. However, the optimization process can observe top-down constraints while growing a bottom-up design through the use of characterized cells. Behavioral design provides the means for minimizing the opportunity for crosstalk and other SI issues by managing voltage levels and clock speeds.

Crosstalk Noise Image: Magma Design Automation

**Electromigration** – Very Deep Sub Micron designs contain millions of devices and operate at very high frequencies. The current densities (current per cross-sectional area) in the signal lines and power are consequently high and can result in either signal or power electromigration problems. The electron movement induced by the current in the metal power lines causes metal ions to migrate. That phenomenon of transport of mass in the path of a DC flow, as in the metal power lines in the design, is termed power electromigration. There are two types of electromigration. Uni-Directional, for example power and static signals and Bi-Directional, for example clocks and other switching signals. The most critical is the Uni-Directional electromigration type since the electron 'erosion' move constantly in one direction and can cause signal line failure. The power electromigration effect is harmful from the point of view of design reliability, since the transport of mass can cause open circuits, or shorts, to neighboring wires. Determination of voltage levels within an architecture or segment of same has a major influence on EM. Especially at nanometer scales, EM can be minimized through selection of connectivity and cells. Performing this at the behavioral level provides the maximum flexibility in meeting other constraints, such as performance. In power-driven design, the goal is to minimize clock speeds, voltage levels, transistor switching and capacitive loading. This is accomplished step-wise, by proposing architecture and then improving it iteratively. Each instance of architecture is marked by specific scheduling of computations, by a controller design, and by assignment of leaf cells. The leaf cells are the key. They are usually large blocks implementing multi-bit functions or even greater functionality. The cells are (ideally) available over a range of voltage levels and clock speeds to meet the possible needs of the architecture under design. It is even possible that such cells can be synthesized in response to need. However, the cells must be characterized. The result of the architecture synthesis then is an RTL design containing leaf cells of known activity characterization, which activity can be further applied in the context of a predicted physical design to support estimation of IR, EM and crosstalk effects, among others, which can then be optimized through iteration.

Electromigration Effect – Open Circuit Image: Computer Simulation Laboratory

**Digital-Analog Integration** – These types of power issues typically are pre calculated within EDA tools results. Architectural optimization can account for voltages and clocks in order to minimize the effects of transitions in the area of analog blocks inside digital optimization cycle. It is unlikely to be practical to optimize it outside the cycle in real time.

**Power Consumption** – Power consumption is directly related to wiring concerns, for all the reasons already discussed. Addressing the magnitude of supply voltage, switching activity in the circuit, switching capacitive loads and clock frequency in a top-down, behavioral, iterative manner, can strongly affect many of the determinants of signal behavior, and in many cases optimize their effects achieving best results.

**Power Integrity -** Power integrity is a significant challenge as chip designs move to 90nm and below process technology. With the increasing of number of devise, technology scaling, increasing device integration, decreasing supply voltages, increasing leakage currents and

the use of low-power techniques negatively impact current distribution gradients (Ldi/dt) and compound power integrity issues. At 90nm, static (or average) IR-drop analysis is insufficient to capture the power-ground noise-related chip failure issues. Static IR-drop takes into account only the power grid resistance (R), which can be used to identify gross design violations. At 90nm, it is important to consider the complete dynamic nature of the power-ground noise, including capacitive and/or inductive effects, simultaneous switching noise, and the effect of decoupling capacitors (de-caps). Undetected and uncorrected, these effects can lead to design failure. Power integrity analysis has become a must as part of the design sign-off process.

#### **Power management IP**

Power management and power rail design are critical issues for very deep submicron (VDSM) designs. With decreasing supply voltages, increasing demand for low power applications and increasing device densities, the challenge to minimize power consumption, minimize voltage drop effects, and maximize product reliability cannot be handled by traditional physical design techniques. Traditional back-end verification of power and rail design are necessary for sign-off, but the cost of detecting and repairing such problems at the end is extremely high. The IC layout need to be analyzed and optimized to provide a layout that meets the designer's power and reliability constraints. The entire circuit power consumption should be optimized and reduced if possible. Voltage drop and electromigration violations should be correct. Accurate timing for the full design is needed including each cell's timing to reflect the local voltage condition. With the physics of the semiconductor working against engineering at nanometer process technologies, the designer must turn to the voltage and clock frequency of the IC to find power savings. In the simplest sense, designers want to be able to treat individual blocks of an IC in much the same way they did when the different parts of the IC were separate chips on a pc board.

These chips could run at different clock rates and different voltages and could be turned off when not in use in order to save power. The designer needs to be able to partition the IC into electrically autonomous areas, called power islands, based on functionality (CPU, MPEG4, memory, analog, etc.) and power requirements. They then need to be able to dynamically scale the voltage and clock frequency of the power islands, so that each island is only running at the performance required at that time. By enabling designers to dynamically manage the voltage and frequency of individual power islands, designers can significantly lower both the dynamic power, and the quiescent or leakage power, of their IC's designs. Dynamic voltage and frequency scaling can be additive to many of the other current power optimization techniques. But full implementation of this technique requires a vertically integrated approach within IC design supply chain, and power management IP. Power management IP is more than just low-power IP, it is IP that allows the designer to actively control and manage the power consumption of the IC during operation. Power management IP allows the CPU and software to issue commands to dynamically scale the voltage, frequency, and leakage current of the power islands of an IC. It allows the designer to leverage the enabling elements of the IC design supply chain—low-power IP (standard cells, memory, etc.), software, SoC IP (CPU, DSP, etc.), process technology and power supply IC—to dynamically manage the power of an IC while it is operating.

#### **Dynamic Power Analysis**

#### **1.** Power Heat Dissipation (Packaging)

As the semiconductor industry adopting the very deep-submicron (VDSM) technology, it creates a new demands on the packaging industry. Especially with high performance IC's the packaging is becoming a significant factor. Increased functionality, faster performance, lower operating voltages and reduced size are leading to increases in die density and I/Os, boosting package pin count and complexity. This has created the need for a new breed of high-density, multilayer, custom-designed packages. We will mention few; flip-chip, ball-grid-array (BGA), and pin-grid-array (PGA).

With chip's power rising, packaging technology must improve to meet heat dissipation demands. The reduction of thermal junction resistance requires advanced cooling techniques such as larger, more powerful fans, liquid/gas vapor cooling, etc'. Packaging experts believe cooled systems are the best solution for packaging high power density VDSM designs.

The advantages of cooling the ambient and junction temperatures are well known: improved voltage scalability due to reduced current leakage, higher carrier motilities, lower interconnect resistances, and improved reliability. Advanced cooling techniques like vapor compression are expensive and predicted to be used only for large IC's. Desktop applications are expected to use low power cooling methods.

Another approach to the packaging heat-constrain is dynamic thermal management. This concept involved thermal management technique that can be achieved in few ways. An example is Transmeta's approach to dynamically varies the supply voltage when the CPU is not heavily loaded. Another example is the thermal monitor in Intel's Pentium IV design which has an on-chip temperature sensor (The temperature sensor is a diode with a fixed voltage across it) along with a reference current source and current comparator to determine when the on-die temperature exceeds a given value. When the temperature (and power consumption) is exceeded the permitted level, the internal clock frequency is reduced, limiting power, throughput and performance. The immediate effect is a reduction in the chip thermal level to bring it to the permitted range.

The importance of dynamic thermal management techniques lies in their ability to reduce the chip power (Wattage) to the effective worst-case power dissipation rather than the theoretical worst-case. The effective worst-case power consumption, as found by running power-hungry applications, is about 75% of the theoretical worst-case, which is determined using synthetic input code sequences that are not realized in practice. This difference has major implications for packaging costs and design flexibility. Small increases in the maximum power can lead to significantly, expensive cooling techniques.

No Doubt, packaging will become more and more in the critical path of the high performance VDSM designs. The increase demand for larger and more powerful chips creates new challenges for the IC's packaging industry.

#### 2. Global Signaling

Global signaling within high performance VDSM designs is one of the serious challenges in the nanometer arena. The propagation of global signals across a large die in a shrinking clock period creates an entire series of electrical phenomenon. It appears likely that global signaling will use a slower clock than localized logic such as datapaths (although multicycles nets can be broken up using latches). Even with relaxed timing constraints on global communication, significant power is consumed to achieve the desired global clock speeds. Based on the current signaling paradigm of inserting large CMOS buffers along an RC line, this requires over 50 W of power in the nanometer arena. The proliferation of repeaters (nearly 106 required at 50-nm compared to about 104 in a large 180nm microprocessor and controllers) heightens difficulties in power distribution and floorplanning2. One solution is to use advanced signaling strategies such as differential and/or low-swing drivers and receivers for global communication.

In many cases, these approaches can lead to power and tpd (time propagation delay) savings due to smaller voltage transitions as well as major reductions in the scale of power grid current transients. For instance, the Alpha chip uses differential low-swing buses to communicate between functional units. Worst-case power for these buses was reduced considerably by limiting the voltage swing to 10% of Vdd. Differential signaling increases routing area, but the increase may be less than the expected factor of 2 due to the use of shielding in global signaling to limit coupling from neighboring signals on long lines. In addition, shielding may be insufficient to limit inductively coupled noise, whereas low-swing differential signaling creates less noise and is more noise immune than single-ended full-swing CMOS. With the industry trends indicating rising power consumption for global communication, the use of alternative signaling strategies will most likely increase. Further study is necessary to provide an efficient solution to the global signaling concern.

#### **3. Library Optimization**

Silicon-proven libraries, give designers and fabless companies very high performance solutions, using some of the most advanced processes available. While most high performance microprocessors rely heavily on custom design, library optimization can significantly enhance performance in these applications. Advances in library generation, and synthesis tools that take advantage of improved libraries, can together yield more automated, less expensive design flows. Libraries are one important reason that custom designs are significantly faster (6-10X) than counterpart ASIC designs. For instance, asserts that the lowest performance level (smallest) gates in modern libraries are nearly 10X larger than minimum-sized gates, leading to major power increases due to overdriving small loads. However, most current libraries contain a large number of drive strengths, including some very near minimum size. As evidence, we refer to the same 180 nm library as the smallest standard cell inverter has an input capacitance of just 1.5fF and the smallest inverter with balanced rise/fall delays has an input capacitance of 6.6fF. Other leading-edge libraries contain a rich set of drive strengths (e.g. 11 2-input NANDs, 16 inverter sizes), dual output polarities, and single pin inverted inputs on NAND/NOR's. This recent increase in library complexity seems to be closing the gap slightly between custom designed cells and those from libraries.

Today EDA vendors provide an entire line of optimized VDSM libraries in order to help customers to achieve efficient designs. For example like Synopsis (using Avant! Tools) provide today an entire set of optimized libraries including standard cells, IO's and memory compilers. The prediction is that in the near future the entire industry will use an optimized libraries provided by the foundries.

#### 4. Multiple Powers Vdd

One of the most efficient methods to rise of dynamic power in VDSM designs is to use multiple power supply lines. (Vdd's) The general idea called clustered voltage scaling (CVS). With two Vdd levels (Vdd\_h and Vdd\_l), the circuit is partitioned so that non-critical gates run at Vdd\_l and only critical gates use Vdd\_h. Level conversions, performed when gates running at Vdd\_l fan-out to gates at Vdd,h, are reduced by clustering Vdd,l and Vdd,h gates together to minimize the number of such interactions. Analysis indicates that Vdd\_l should be around 0.6 to 0.7 times Vdd\_h to maximize power savings. The dynamic power reduction by using two Vdd levels is readily calculated if one can estimate the fraction of cells that can be assigned to Vdd\_l. Existing media processor designs that use CVS report that ~75% of all gates can tolerate Vdd\_l without altering the critical path delay.

The key challenges to the use of multiple supplies on a chip lie in minimizing area overhead and providing EDA tool support for Vdd cell selection, placement given new clustering constraints, dual power grid routing, and enhanced library generation capabilities. Using this system within EDA tools provides a powerful capability for VDSM high performance designs.

### Static Power Analysis

#### 1. Multiple Vth Approaches

In order to reduce CMOS static power consumption several approaches have been developed. In this section we will briefly discuss several of these techniques that use multiple thresholds on a single chip to limit Ioff.

#### A. MTCMOS Method

Multi-Threshold CMOS (MTCMOS) gates a high-Vth transistor with a sleep mode signal to virtually eliminate leakage current in idle states. The sleep transistor is placed between ground and fast low-Vth CMOS logic. As it is in series, it adds delay, which can be reduced by increasing its area. Disadvantages include no leakage reduction in active mode, increased device area, and additional overhead for routing sleep signals. Other similar techniques include dual-Vth domino logic, substrate biasing to modify Vth in standby, and using negative NMOS gate voltages to bias the devices further into cut-off. A single threshold leakage reduction technique combines the concepts of sleep transistors and state dependent leakage. All these techniques trade off area to limit static power and most only reduce leakage in standby mode. In fact, they are currently limited to portable applications such as notebook processors. Also, some of the proposed methods do not scale well – the use of domino logic for example, and substrate bias controlled Vth (body bias is less effective at controlling Vth in scaled devices). Dual Vth insertion, described next, is the only technique used in current high-end MPUs.

#### **B. Dual-Vth Method**

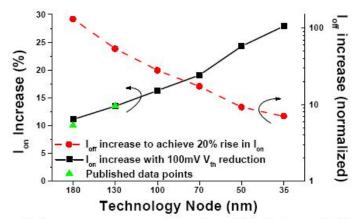

Today, circuit designers have access to multiple threshold voltages on a single IC to select between gates that use high or low thresholds. The impact of Vth on the delay and power of gates such as inverters and NANDs is significant. A reduction in Vth (with constant Vdd) exponentially increases off current and roughly linearly reduces the propagation delay. An additional threshold adjust ion implantation step allows designers to choose from a wider range within the power-performance design envelope. Gates located on critical paths can be assigned fast low Vth, while gates that are not timing critical can tolerate high Vth and slower response times. Typical results show leakage power reductions of 40-80% with minimal penalty in critical path delay compared to all low-Vth implementations. Figure 2 shows the increase in Ion for the low-Vth device. The relative difference in Ioff between the two devices will remain constant throughout the roadmap (at about a 15X increase in Ioff for 100 mV reduction in Vth). Given that the off current change is constant, the steady improvement in Ion with scaling demonstrates that the dual-Vth (or multi- Vth) approach to leakage reduction is inherently scalable. Figure 2 also shows the resulting Ioff increase for Ion to rise 20% beyond the

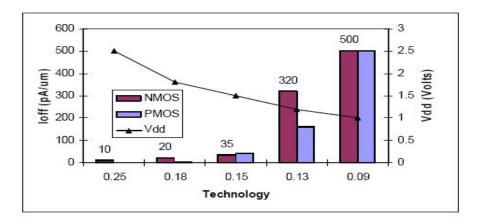

high-Vth case. At 35 nm, just a 7X rise in Ioff is required to yield 20% drive current improvement, compared with a factor of 54X today. In Figure 3 we can see the Ioff decrement with the process shrink and the reduction of Vdd.

Figure 2.  $I_{on}$  increases more rapidly with a 100mV change in V<sub>th</sub> for scaled technologies.  $I_{off}$  penalty for 20%  $I_{on}$  gain reduces with scaling.

Figure 3 - loff reduction with the process and power

#### 2. Scalable Dynamic/Static Power Approach

One of the most appealing approaches, in order to achieve scalable, flexible and cost effective design is a combination of multiple Vdd's and multiple Vth's. The combination of multiple Vdd's, multiple Vth's, and intra-cell size and Vth assignments points to a highly flexible, scalable, cost effective design approach to dynamic and static power minimization. With two voltage supply values available, different Vth's will allow designers or EDA tools to choose to emphasize speed, standby power, or dynamic power.

#### Summary

The EDA industry continues to face new challenges as process continues to shrink into nanometer geometries. With each successive advancement of semiconductor technology a new VDSM challenge is born. Especially with high performance reliable designs the industry has to face a wide variety of phenomenon such as heat dissipation, electromigration, interconnect coupling and more. Many EDA tools have been enhanced to deal with these issues. The keys to a successful nanometer design are:

1. Efficient and reliable power management techniques such as on-chip temperature monitors and multiple voltage supplies will reduce dynamic power, enabling cheaper packaging and higher integration densities.

2. Power distribution will be manageable from the standpoint of IR drop – given changes in the ITRS to take advantage of technological advancements in flip-chip packaging. However, large current transients may be exacerbated by the use of sleep/standby modes.

3. Alternative techniques to CMOS repeaters for global signaling need to be studied and implemented within EDA tools to minimize power consumed in global communications.

4. A multi-layered approach to power reduction (both dynamic and static), combining multiple threshold and supply voltages with flexible gate layouts using different thresholds and device sizes within a gate. Non-critical gates are first assigned to a reduced Vdd, followed by sizing and Vth selection to reduce power most efficiently.

Taken together, the various aspects described in this document form a methodology that provides comprehensive power optimization. The power optimization aspect needs to be performed throughout the entire design stages particularly during architectural synthesis phase in order to solve critical nanometer issues.

While the power crisis in the nanometer arena is clearly a challenge, designers are beginning to see the introduction of a new breed of power management IP integrate with other elements of the design supply chain. In the coming years, we can expect more innovative EDA products that will deliver powerful solutions for the nanometer power crisis.

#### References

[1] J. Cong, L. He, C.-K. Koh, D. Z. Pan, and X. Yuan, "TRIO: Tree, repeater and interconnect optimization package." http://cadlab.cs.ucla.edu/\_trio.

[2] J. Cong, L. He, A. B. Kahng, D. Noice, N. Shirali, and S. H.-C. Yen, "Analysis and justification of a simple, practical 2 1/2-d capacitance extraction methodology," in *Proc. ACM/IEEE Design Automation Conf.*, pp. 40.1.1–40.1.6, June,1997.

[3] J. Cong, L. He, C.-K. Koh, and P. H. Madden, "Performance optimization of VLSI interconnect layout," *Integration, the VLSI Journal*, vol. 21, pp. 1–94,1996.

[4] J. Cong, L. He, K.-Y. Khoo, C.-K. Koh, and D. Z. Pan, "Interconnect design for deep submicron ICs," in *Proc. Int. Conf. on Computer Aided Design*, pp. 478–485, 1997.

[5] Semiconductor Industry Association, *National Technology Roadmap for emiconductors*, 1997.

[6] J. Cong and D. Z. Pan, "Interconnect delay estimation models for synthesis and design planning," in *Proc. Asia and South Pacific Design Automation Conf.*, pp. 97–100, Jan., 1999.

[7] J. Cong and D. Z. Pan, "Interconnect estimation and planning for deep submicron designs," in *Proc. Design Automation Conf*, June, 1999.

[8] C.-P. Chen and D. F. Wong, "Optimal wire sizing function with fringing capacitance consideration," in *Proc. Design Automation Conf*, pp. 604–607, 1997.

[9] J. Cong, "Challenges and opportunities for design innovations in nanometer technologies," Dec. 1997. http://www.src.org/research/frontier.dgw.

[10] J. Cong, L. He, C.-K. Koh, and D. Z. Pan, "Global interconnect sizing and spacing with consideration of coupling capacitance," in *Proc. Int. Conf. on Computer Aided Design*, pp. 628–633, 1997.

[11] K. Usami and M. Horowitz, Clustered voltage scaling techniques for low-power Design, ISLPED 1995.

[12] C. Chen, A. Srivastava, and M. Sarrafzadeh, On gate level power optimization using dual-supply voltages, IEEE Trans. on VLSI Systems, vol.9, p.616-629, Oct. 2001.

[13] N. Rohrer, et al., A 480MHz RISC microprocessor in a 0.12\_m Le\_CMOS technology with copper interconnects, ISSCC 1998, p.240-241.

[14] S. Sirichotiyakul, et al., Standby power minimization through simultaneous threshold voltage selection and circuit sizing, DAC 1999, p.436-441.

[15] Q. Wang and S.Vrudhula, Algorithms for minimizing standby power in deep submicron, dual-Vt CMOS circuits, IEEE Transactions on CAD, vol.21, p.306-318, 2002.

[16] M. Hamada, Y. Ootaguro, and T. Kuroda, Utilizing surplus timing for power reduction, CICC 2001, p.89-92.

[17] K. Usami, et al., Automated Low-Power Technique Exploiting Multiple Supply Voltages Applied to a Media Processor, IEEE JSSC, Vol.33, No.3, 1998.

[18] M. Hamada, et al., A top-down low power design technique using clustered voltage scaling with variable supply-voltage scheme, CICC 1998, p.495-498.

[19] D. Sylvester and H. Kaul, Future performance challenges in nanometer design, DAC 2001, p.3-8.

[20] A. Srivastava and D. Sylvester, Minimizing total power by simultaneous Vdd/Vth assignment, Proc. Asia-South Paci\_c DAC 2003, p.400-403.

[21] C. Yeh, et al., Layout Techniques supporting the use of Dual Supply Voltages for Cellbased Designs, DAC 1999.

[22] D. Lackey, et al., Managing Power and Performance for SOC Designs using voltage islands, ICCAD 2002.

[23] S. Kosonocky, et al., Low Power Circuits and Technology for wireless digital Systems, IBM Journal of R&D, Vol. 47, No. 2/3, 2003.

[24] A. Correale, D. Pan, D. Lamb, D. Wallach, D. Kung, R. Puri, Generic Voltage Island: CAD Flow and Design Experience, Austin Conference on Energy E\_cient Design, March 2003 (IBM Research Report) 23

[25] W. Donath, et al., Tranformational Placement and Synthesis, DATE, 2000.

[26] R. Puri, E. D'souza, L. Reddy, W. Scarpero, B. Wilson,

Optimizing Power-Performance with Multi-Threshold Cu11-Cu08 ASIC Libraries, Austin Conference on Energy E\_cient Design, March 2003 (IBM Research Report).

[27] R. Puri, D. Pan, D. Kung, A Flexible Design Approach for the Use of Dual Supply Voltages and Level Conversion for Low-Power ASIC Design, Austin Conference on Energy E\_cient Design, March 2003 (IBM Research Report).

[28] Y. Taur, CMOS Design near the limit of scaling, IBM Journal of R&D, Vol. 46, No. 2/3, 2002.

[29] J. P. Fishburn, Clock Skew Optimization," IEEE Transactions on Computers C-39, pp 945-951, 1990.

[30] T. G. Szymanski, Computing Optimal Clock Schedules," DAC 1992, p.399-404.

[31] C. Albrecht, B. Korte, J. Schietke and J. Vygen, Cycle Time and Slack Optimization for VLSI-Chips, ICCAD 1999, p.232-238.

[32] S. Bhattacharya, J. Cohn, R. Puri, L. Stok and D. Sunderland, Power reduction of Hardwired DSPs in standard ASIC methodology, Submitted to CICC, 2003.

[33] L. Stok, et al., BooleDozer Logic Synthesis for ASICs, IBM

Journal of R&D, Volume 40, no. 3/4, 1996.

[34] F. Beeftink, P. Kudva, D. Kung, R. Puri, L. Stok, Combinatorial cell design for CMOS libraries, Integration: the VLSI Journal, V.29, p.67, 2000

[35] P. Kudva, D. Kung, R. Puri, L. Stok, Gain based Synthesis, ICCAD Tutorial, 2000.

# **Europe Union FP6 Program**

http://www.delchn.cec.eu.int/en/Science\_Technology/FP6.htm

Dr Jurgen SANDER Counsellor for Sci. & Tech., EU Delegation Beijing jurgen.sanders@cec.eu.in

### Epistemologically Multiple Actor-Centred System: Or, EMACS at work!

#### Yuwei Lin University of York, Uk

#### Abstract

The paper begins with the story of EMACS (short for Editing MACroS), an editor programme originally written for TECO (Text Editor and Corrector) language and PDP-10 machines in the MIT AI Lab by Richard Stallman, from which various more sophisticated versions have been developed. I analyse how the innovation of EMACS took place over time as a socio-technical process. The EMACS story serves to illustrate how the innovation process in the FLOSS (Free/Libre Open Source Software) community occurred, but one that is then adopted and deployed in other social contexts, including the commercial sector. The analysis of EMACS is especially useful since it spans the period that saw the origins of the free software movement and the subsequent developed and employed/deployed in mundane programming within an actor-centred network. Actors from different backgrounds contribute multiple ways of knowing, understanding and resolving problems that arise in the innovation process. A socio-technical perspective is employed to analyse how EMACSen are shaped by diverse actors, and at the same time also shape these actors and their practices.

To widen the scope of the paper in terms of its implication in a wider societal dimension, anchored in sociology of intellectual/knowledge, this paper also contributes to our understanding of the formation of knowledge in the Internet era, where information and knowledge flow fluidly and rapidly. The EMACS case denotes various key factors of forming cosmopolitan knowledge: how actors network together (e.g. shared interests), how they interact with one another (e.g. problem-solving process), and how local epistemologies and tacit knowledge being translated into cosmopolitan expertise in an in/tangible form (e.g. materiality of software). I believe this empirical enquiry will provide us with a means of retaining the holistic and meaningful characteristics of real-life events. Methodologically speaking, the contextual thickness makes a case study appropriate for "how" and "why" research questions because answering these questions deals with operational links needing to be traced over time. The detailed investigation of FLOSS phenomenon with attention to its context by using multiple sources of evidence and various methods of data collection will help to examine the innovation process by which new FLOSS technologies are created, arguing that this is ongoing and involves diverse groups who give the technology different meanings.

#### **1.Introduction**

The paper begins with the story of EMACS (short for Editing MACroS), an editor programme originally written for TECO (Text Editor and Corrector) language and PDP-10 machines in the MIT AI Lab by Richard Stallman, from which various more sophisticated versions have been developed. I analyse how the innovation of EMACS took place over time as a socio-technical process. The EMACS story serves to illustrate how the innovation process in the FLOSS (Free/Libre Open Source Software) community occurred, but one that is then adopted and deployed in other social contexts, including the commercial sector. The analysis of EMACS is especially useful since it spans the period that saw the origins of the free software movement and the subsequent development of a broader FLOSS social world.

#### 2. EMACS

In 1976 Richard Stallman, an employee at MIT AI Lab, and his colleagues, wrote the editor EMACS to upgrade the previous editor TECO on an ITS (Incompatible Time-Sharing System), which was the software running on the AI Lab's Digital PDP-10 mini-computer. In the text-based pre-graphical world that existed before the Apple Macintosh and Microsoft Windows, the editor was a programme crucially important for creating and manipulating text (Moody 2001: 16). Instead of typing commands when editing texts, the TECO editor enabled users to employ macros, command strings for a cluster of TECO programmes, which provided a more immediate onscreen feedback for users. TECO had already had the WYSIWYG<sup>\*</sup> (What You See Is What You Get) feature named Control-R, written by Carl Mikkelson, which allowed users to enter macros (command strings) and discarded them after entering them. Borrowing the idea from another WYSIWYG editor named  $\overline{E}$ , Stallman then brought additional functionality to TECO to make it possible to save macro shortcuts on file and call them up at will. It is said that this improvement was subtle but significant in that this raised TECO to the level of a user-programmable WYSIWYG editor, which later on enabled innovation at another meta level that became the progenitor of FLOSS (Williams 2002: 82). The amended macro function in TECO permitted users to redefine their own screen-editor commands, pass them around and improve them, make them more powerful and more general, and then the collections of user-redefinitions gradually became system programmes in their own right (ibid.). In so doing, users extended the original TECO system by adding or replacing functions based on their self-defined definitions of <sup>-</sup> the problem<sup>\*</sup>. Users were not, then, limited by the decisions made or problem-solving approaches taken by the original innovators (Stallman 1998: 2). The extensibility made TECO more flexible for use and in turn attracted a larger number of users to incorporate the macro function into their TECO programmes.

However, a new problem emerged along with this new feature. While the new full-screen capabilities were embraced vigorously, various customised visions of TECO also led to over-complexity. The most obvious example was that one had to spend more time than before figuring out what macro commands did what in terms of an individual's self-definition of <sup>-</sup> the problem <sup>×</sup> when improving each other's work. Guy Steele, a colleague of Stallman's at the AI Lab, recognised this problem and sought to address it. He firstly gathered together four different macro packages and began assembling a chart that he believed identified and organised the most useful macro commands (Williams 2002: 83). In the course of implementing the design specified by the chart, Steele's work attracted Stallman's attention and led to the latter's participation in this renovation project. Together with David Moon and Dan Weinreib, the four tried on the one hand, to develop a standard

system of macro commands, and on the other hand, to still keep the command set openended to enable ongoing programmability/extensibility by others. The programme was named EMACS.

The distribution of EMACS marked another milestone in the software history. In response to the prevalence and technical opacity associated with the practice of entirely self-defined commands, and to endorse the hacker tenet of sharing information, Stallman set the terms of on which EMACS could be used in the statement linked to the source code when distributing the editor. EMACS, as noted in Stallman's biography, served as a social contract that rendered communal sharing the basis of its distribution. Users, on the one hand, were able to modify and redistribute the code; on the other hand, they were asked to report back the extensions they might have made to Stallman so that he could incorporate and distribute those again. In so doing, Stallman strengthened the functionality of EMACS, making programming with macros more standardised through creating a reciprocal understanding of the written codes through sharing problem solutions, as well keeping the extensibility that macros afforded. Consequently, a library was created for users to load new or redefined functions and to publish and share their extensions. - By this route, many people can contribute to the development of the system, for the most part without interfering with each other. This has led the EMACS system to become more powerful than any previous editor." (Stallman 1998: 2). Since then, an archetype of EMACS had been established.

#### 3. Affordance and EMACS: Extensibility and Customisation

The earlier generation of EMACS had been successful because it provided flexible use with an embedded programming language, TECO. Because of this feature, editing commands could be written in that programming language and users could load new commands into her/his editor while s/he was editing. EMACS resembled a system that was useful for things other than programming, and yet one could program it while s/he was using it. It was claimed to be the first editor that could operate in this way (Stallman 2002: 1). Consequently, the socio-technical networks of EMACSen have been expanded. GNU Emacs for example, is now available for Unix, VMS, GNU/Linux, FreeBSD, NetBSD, OpenBSD, MS Windows, MS-DOS, and other systems. GNU Emacs has been re-configured more than 30 times as part of other systems. Other variants include GOSMACS, CCA Emacs, UniPress Emacs, Montgomery Emacs, and XEmacs. Jove, Epsilon, and MicroEmacs are limited lookalikes. These systems on the other hand also have requirements, needs, and visions that differ from the original GNU Emacs. This phenomenon widens the range of what we might see as <sup>-</sup> digital epistemologies<sup>-</sup> (ways of ordering and knowing software) and their expression through software artefacts in the FLOSS social world.

#### 4. Problems and solutions: the sine qua non of the software innovation process

In light of the EMACS account above, problems play a crucial role in the innovation process. Triggering a problem or perceiving a problem and dealing with it are important tasks for scientists and engineers, and through their resolution help generate innovation. A problem thus can be seen as the inauguration of an innovation. The confronting of a problem provides an opportunity of coming up with something new or different. A problem de facto denotes one's perception of the situation, one's knowledge, and skills. Accordingly a problem signifies one's identity as an expert or a novice, for example.

Efficiency was an important parameter in the process of defining software problems. A problem would not exist if users did not recognise the existing practice (e.g. composing code with printing terminal editors in the 70s) as inefficient. As efficiency is regarded as key within the field of engineering; engineers were and are still taught to design efficient technologies. Efficiency is not however, self-evident: Stallman reports that he did not have a strong sense of the need for a real-time display editor until he encountered the  $^-E \\$  programme when he visited the Stanford Artificial Intelligence Lab in 1976. He was inspired by the function E afforded and sought to expand TECO's functionality in the same way and helped form the group that was to work on a real-time display system. Meanwhile, there were other parallel groups providing solutions for real-time display systems, and their work could become complementary to the work that Stallman's group were undertaking. Stallman's macros improvement to TECO enhanced Mikkelson's earlier WYSIWYG feature for TECO. As a result, with this greater affordance and functionality, TECO became more popular. The TECO socio-technical network expanded when more people accepted the macro innovations and incorporated them into their own versions of the TECO programme.

It is worth noting that Stallman did not sit down and write the editor system programme immediately after his encounter with E. Instead, he looked up the database and found that Mikkelson had made a WYSIWYG feature for TECO. He then integrated his idea into that. If Mikkelson's work had not existed, we may have seen a different technical option taken, as the - problem - may have been defined differently. This points to the contingency of the innovation process. This process is reflected in many FLOSS developers' own reflections on their systems as seen in Stallman's and Torvald's biographies (e.g. Torvald said he probably would not have started the Linux kernel project if the GNU Hurd had already existed; Stallman said he would not have started to write the GCC compiler if Tanenbaum had agreed to share his work). Hence, looking for existing material and tools is another common practice in solving problems in software innovation. Software engineering, as in other fields, is built on existing technologies. Programmers typically explore existing databases and see whether any tool is available; if not, they are likely to try to create one to solve the problem.

Access to problems is another issue that needs to be discussed in light of the data from my fieldwork. The accessibility of problems measures the relative ease with which problems can be understood. If one problem entails an opportunity for innovation, an active innovation field should welcome more problems. In a less open innovation system, problems are less accessible, and the boundary is relatively impermeable to new entrants and new ways through which the system can be enhanced. In such an innovation system, problems are less likely to be seen to appear, innovation options likely to be more pre-defined, and innovators sharing a consensus on - what needs to be done -. On the contrary, I want to argue that in a heterogeneous field where diverse actors are found, more problems arise or are triggered. If the boundary of the social group centring on the problem is soft, more diverse actors will be included in the circle. There is a positive correlation between the elasticity of the boundary of an innovation field and the momentum behind the pace of innovation because the more accessible the problem is, the higher the level of multivocality existing in the innovation system.

The elasticity of the boundary can be manipulated through a range of educational, legal, political, economic, social and technical means. In the 1970s, software problems were more

accessible in the sense that fewer regulations were applied to restrict programmers to access key materials (codes peculiarly). There was a so-called  $\bar{}$  collaborative hacker  $\check{}$  approach, sharing knowledge and improving each other's work, that encouraged programmers to continually to redefine the boundaries of the problem (e.g. conducting reverse engineering to deconstruct a software to understand how a code was written). As a result, a wide range of software programming tools (languages, editors, compilers etc.) was created in the 1970s (Ceruzzi, 2003).

However, the generation of too many problems may become counterproductive to innovation. The ability to solve problems is key to innovation. The more a problem is accessible, as noted above, the more diverse actors will be invited to participate in the innovation group centring on the problem. As there is no single perfect solution for a problem, multiple voices and silences should always be welcome (Bowker & Star, 1999: 41). If a problem is presented in an intelligible/perceivable/accessible way, it will encourage more participants to craft solutions (though there may be nothing wrong with asking a dumb  $\check{}$  question, as the dumbest question can sometimes produce the best answers). As noted by a number of commentaries, well-defined problems in which the given information, operations, and goal are clearly specified will more likely to have solutions than ill-defined problems (Glass et al., 1979; Borgman, 2003). Furthermore, such sources argue that an expert can articulate the queries more specifically and completely than could someone new to the domain. This ability to articulate problems becomes one of the parameters that defines expertise, which will be discussed later in this paper.

As I noted above, while Stallman's innovation was celebrated because of its extensibility and flexibility, it did however create new problems. One that many saw was the sense of a growing confusion derived from the plethora of self-defined macro commands, which was seen to eventually work against a more efficient process of programming. In response, another member of the AI group, Steele, tried to provide a solution by charting the macros. Steele's solution encouraged Stallman, Moon and Weinreib to participate in a solutioncrafting innovation group. These four who shared the same interest in this project formed a social network of expertise and began to fashion the digital tools that would be seen to provide the solution they were looking for: in this sense the path they took and tools they developed reflected a shared conceptual frame that was <sup>-</sup> not accidental, but constitutive. (Clarke, 1998; Bowker & Star, 1999: 36). What made the process more intriguing is the relationships and interactions between the actors themselves and the actants (materials), and the boundary crossings the transitions that a problem so identified enabled. Boundary crossings can require both getting in (e.g. gaining access to the problems) and getting out (e.g. forging an alternative solutions different from the original one). These boundaries are interpreted or constructed through the problem-solving process of software design. In the process, actors move across boundaries and shift their identities as outsiders or insiders to the core innovation group.

#### 5. Shared interests and translation of interests

As seen in the story of EMACS, engaging actors in a network is the key to effective innovation in that the range of expertise in the network will affect a group's abilities to solve problems. Since everyone is an expert with regard to some things and a novice with regard to others, a problem/question in an open environment will be answered sooner or later. It is

worth noting, however, actors' involvement in a network is not randomly assembled, but determined by shared interests. As Latour articulates,

The first and easiest way to find people who will immediately believe the statement, invest in the project, or buy the prototype is to tailor the object in such a way that it caters to these people's explicit interests. As the name – inter-esse – indicates, – interests – are what lie in between actors and their goals, thus creating a tension that will make actors select only what, in their own eyes, helps them reach these goals amongst many possibilities. (Latour 1987: 108-9).

After Stallman left the MIT AI Lab and planned to write an Unix-like operating system for non-commercial distribution, a range of ICTs facilitated his individual action. Stallman's GNU project, as if many other FLOSS projects, precisely took advantage of ICTs to target peers to join his innovation network. These artefacts enabled him to maintain communication with other programmers and even helped to secure some innovation resources when he worked alone. On 27 September 1983, Stallman posted the message below onto the Usenet newsgroup net.unix-wizards in order to invite people who shared the same interest or parallel knowledge to join the discussion. Stallman posted the following message:

Starting this Thanksgiving I am going to write a complete Unix-compatible software system called GNU (for GNU's Not Unix), and give it away free to everyone who can use it. Contributions of time, money, programs and equipment are greatly needed. (Williams 2002: 89)

In this message, Stallman revealed his defined problem and the proposition for possible solutions a complete Unix-compatible software system. Because he had lost institutional support (financial and intellectual) from the MIT AI Lab, he was more likely to find peers interested in joining the social network of developing a new operating system and to engage their attention by posting messages onto the Unix newsgroup, where specific users/programmers share the same interest inhabit. Without knowing who was going to get in touch with, the message posted entailed uncertainty and risk in Stallman's project. While Stallman posted this message, he created a social network of crafting a new operating system. If Stallman was able to invite many programmers to join this project, the network would grow and the project would take off. Here, making decisions of which listserv or newsgroup a message should be posted to in order to attract as many actors as possible is another form of classification shaping the innovation process. Stallman reckoned the Unix group was the one where he would be most likely to find his target peers. This tendency of looking for peers who share the same interests echoes my previous argument that a shared interest among peers is crucial for the continuation of collaboration. The common interests engage actors to work together, share knowledge and exchange information. The teamwork gets more complex with higher peer participations. If the management style stays in a democratic/open way, the boundary of the team will remain soft. This type of innovation is more accessible because open debate within the team is more likely to produce multiple topics to attract actors. Here, the construction of a shared interest or a common topic is resonant with Latour's notion of inter-essant (1987), through which actors are enrolled to mobilise innovation networks. The working environment at MIT AI Lab in the 70s was

similar to this way. Most of the FLOSS projects that rely on virtual collaboration also meet the criteria of Latourian inter-esse/sant. In contrast, a closed or centralised direction of a project would reinforce innovation boundaries and restrict accessibility to the innovation process. In so doing, a project can be kept under control to eliminate risks and uncertainties generated by multivocality. Following this route, a project will approach closure eventually. Proprietary software is mostly managed in this way.

#### 6. EMACS as a Boundary Object

Hitherto, I have investigated how a software innovation network is created and developed in terms of classifications of problems, identifications of solutions and common interests. Actors and actants are brought together, interact and negotiate with each other to solve problems. Boundaries of networks, which determine access to innovation systems, vary in different contexts. A successful innovation, as discussed, is the one that manages to bring in as many actors and actants as possible by translating their interests to extend and mobilise the network as well as handles the uncertainties and risks emerging during the process.

In reviewing the innovation story of EMACS, a variety of EMACSen have been innovated/renovated by diverse actors for different purposes. The functions of EMACS have been expanded and are still expanding. In other words, the affordance of EMACS is sustained. While diverse innovation repertoires are brought into the social network to tackle a joint problem, they also complicate the situation by defining and redefining EMACS<sup>\*</sup> innovation concept over and over again. If different definitions of innovation concepts cannot be reconciled, a project diverges, as the development of many versions of EMACS show. The reasons for the divergences vary in social scope (e.g. disagreement on Stallman's social contract), technical/material scope (e.g. original EMACS did not run on other programming language than TECO, so new version of EMACS was designed for other programming language such as Lisp, such as EINE and ZWEI, developed by Weinreb, a fellow colleague working on the original version of EMACS as well), or other contingent factors (e.g. experimental projects-- just for fun, perhaps). These parallel processes demonstrate the dynamic in the innovation network of EMACS. Facing the challenge of the heterogeneity, authors and maintainers of EMACSen try to enhance their legitimacy and uniqueness in providing greater socio-technical functions.

In this account, EMACS, as an extensible editor that can be used flexibly, has served as a boundary object for diverse users. They interpret the role of EMACS in different ways according to their situated practices. A number of common practices of EMACS can be summarised. Some take EMACS as a pure tool for editing texts, programming, gaming, web browsing. Others contribute to the FLOSS community by reporting bugs of EMACS while using it, and still the others residing in the core of EMACS innovation system take EMACS as an artefact or even art work. Because EMACS denotes so many different meanings, the diverse interpretations and manipulations of EMACS can prevent it becoming a stereotyped editor, even though its material effects (as affordances) do give it a specific technical character. This is in contrast to other proprietary software products. For example, Microsoft Office Word software has enrolled a huge number of users for processing their Word documents. When mentioning "Word " people take Microsoft Office Word for granted. Accordingly, Microsoft Office Word is used not more than for typing and word processing. But for EMACS, its high affordance enables many roles to be played in mundane computing

practices. Once EMACS is mentioned, people would like to know which version of EMACS is indicated (e.g. GNU Emacs, XEmacs each indicates different usage habits, particular interests in programming languages, or even political views), and for what purpose it is used. The potentiality of EMACS for different functions is resilient. Unlike Microsoft Office Word, the open trait of EMACS gives users more space to configure and customise their own versions which meets individual requirements.

Since EMACSen are used in many different ways and denotes various socio-cultural meanings, diverse projects have symbolised users' habits and preferences (socially and technically). In adopting specific tools and participating in specific projects, users are attached to the artefacts. These artefacts grow to be norms to demarcate boundaries. For example, the users of GNU Emacs see themselves different from those of XEmacs, while the broad range of users of Emacs distinguish themselves from other users of other editor programmes, such as vi. Holy wars happen often because these users want to fortify their boundaries against each other to show their identities. Accordingly, software programmes containing symbolic contents should be seen not merely as algorithm codes but also as social codes. It would be interesting to see how these projects are symbolised as norms, how they are interpreted and used. That is, in the course of explaining the heterogeneous FLOSS social world, one can study the socio-technical meanings given to various projects to understand "FLOSS ". This actor-centred view may provide a distinctive research result from the prevailing structure-centred or essentialist approaches in the FLOSS studies.

Life in EMACS will continue to change, but the crucial presumption will be whether the boundary of the innovation network can be maintained to sustain the innovation. For instance, Gosling did not continue to share his codes, rather, he sold his EMACS version to a commercial company. His version of EMACS therefore did not continue to grow. This is not to say that selling software to a commercial company will kill the product. There are other reasons for the elimination of a software product and sometimes the involvement of commercial companies does provide other sources for sustaining or developing a product. But in the case of Gosling Emacs: 1) He thought selling the product to a firm might broaden the network. But the transaction symbolised Gosling's failure to continue the network expansion. 2) The commercial product was not successful. The firm failed to engage actors' interest in it. The commercialised software forms a firmer boundary than FLOSS community projects to exclude outsiders of the developing team from the innovation. In that case, problems will not be triggered that easily. If problems are the initiatives of innovation, a less diverse character in the team will not help the innovation at that point. When GNU Emacs was just invented and still in an unstable stage, it did not put users off, instead, the existing problems invited peers to tackle them. GNU Emacs was able to engage actors in its social network of innovation. The network expanded and a variety of functions were developed. These functions become cornerstones to attract more actors/users as if a snowball effect. Unlike some proprietary software firms try to lock users in by using proprietry document formats (and critics say they do this in order to dominate the market), EMACSen engage users by presenting greater shared interests in socio-cultural or technical aspects. The story of EMACS sheds some light on the FLOSS innovation, albeit the commercial impetus should be taken into account in order to understand the situation completely.

#### Reference