# IPS

# HIGH LEVEL PROGRAMMING OF SMALL SYSTEMS

Second Edition

Karl Meinzer, Ph.D. University of Marburg 1978

### IPS - High Level Programming of Small Systems

© Karl Meinzer 1978

First edition 1978 Second edition and first printing 1997. Third edition (electronic PDF) with corrections 2016

Published by James Miller, Cambridge CB23 7PS, England.

No part of this publication may be reproduced or transmitted in any form or by any means electronic, mechanical, photocopying, recording or otherwise, or stored in any retrieval system of any kind without the written permission of the copyright holder and the publisher, application for which should be made to the publisher.

Author and publisher have used their best efforts in preparing this book. They make no warranty of any kind, expressed or implied with regard to programs or documentation contained in this book. The author and publisher shall not be liable in any event for incidental or consequential damages in connection with, or arising out of material contained in this book.

This book was produced on an *Acorn Risc Computer* by James Miller. It was edited with the StrongED text editor, and typeset using the Impression Style DTP package.

Printed and bound by The Tavistock Press (Cambridge) Ltd.

ISBN 0-9530507-0-X

## Contents

| vi   |

|------|

| viii |

| Х    |

| Х    |

|      |

## **CHAPTER I**

| 1 | Hardware requirements for IPS               | 1  |

|---|---------------------------------------------|----|

| 2 | Keyboard Operations                         | 4  |

|   | 2.1 Your computer and IPS                   | 4  |

|   | 2.1.1 Communicating with IPS                | 4  |

|   | 2.2 The Stack                               | 5  |

|   | 2.2.3 Arithmetic operations                 | 6  |

|   | 2.2.4 Logical operators                     | 7  |

|   | 2.3 Stack manipulations                     | 8  |

|   | 2.4 Named constants and variables           | 9  |

|   | 2.5 Fields                                  | 10 |

|   | 2.6 Byte manipulations                      | 13 |

|   | 2.7 Error messages                          | 14 |

| 3 | Programming                                 | 15 |

|   | 3.1 Definitions                             | 15 |

|   | 3.2 Text handling                           | 20 |

|   | 3.3 Tape cassette operations                | 22 |

|   | 3.4 Process control programming             | 24 |

|   | 3.5 Repeated execution and multiprogramming | 27 |

| 4 | IPS - Operation and memory organization     | 31 |

|   | 4.1 The address space                       | 31 |

|   | 4.2 The dictionary                          | 32 |

|   | 4.3 The emulator (inner interpreter)        | 33 |

|   | 4.4 The 20 ms pseudo-interrupt              | 34 |

|   | 4.5 The compiler                            | 34 |

| 5 | Cassette tape operations on binary data | 35 |

|---|-----------------------------------------|----|

|   | 5.1 Data storage                        | 35 |

|   | 5.2 Reading data cassettes              | 35 |

|   | 5.3 Program storage                     | 35 |

| 6 | IPS programming hints and exercises     | 37 |

|   | 6.1 Programming method                  | 37 |

|   | 6.2 Exercises                           | 38 |

|   | 6.3 Solutions to the exercises          | 39 |

|   |                                         |    |

## **CHAPTER II**

| 1 | General                                        | 43 |

|---|------------------------------------------------|----|

| 2 | Basic philosophy of the assemblers             | 44 |

| 3 | The CDP 1801 assembler                         | 46 |

|   | 3.1 Register allocations                       | 46 |

|   | 3.2 The instruction mnemonics                  | 47 |

|   | 3.3 An 1801 assembler example                  | 47 |

|   | 3.4 Listing of the CDP 1801 Assembler          | 48 |

| 4 | The 8080 assembler                             | 49 |

|   | 4.1 Resource allocations                       | 49 |

|   | 4.2 The instruction mnemonics                  | 49 |

|   | 4.3 An 8080 assembler example                  | 50 |

|   | 4.4 Assembler for the 8080; 5. 3. 78 for IPS-N | 50 |

| 5 | The 6800 assembler                             | 52 |

|   | 5.1 Resource allocations                       | 52 |

|   | 5.2 The instruction mnemonics                  | 52 |

|   | 5.3 A 6800 assembler example                   | 53 |

|   | 5.4 The 6800 assembler for IPS-N, 27.1.78      | 53 |

| 6 | The 6502 assembler                             | 56 |

|   | 6.1 Resource allocations                       | 56 |

|   | 6.2 The instruction mnemonics                  | 56 |

|   | 6.3 A 6502 assembler example                   | 58 |

|   | 6.4 The 6502 Assembler for IPS-N, 23. 1. 78    | 58 |

| 7 | The CDP 1802 assembler                         | 61 |

|   | 7.1 Listing of the CDP 1802 Assembler          | 61 |

## Contents

### **CHAPTER III**

| 1 | General design considerations             | 63  |

|---|-------------------------------------------|-----|

| 2 | The IPS implementation                    | 67  |

| 3 | Structure of the pseudocode               | 68  |

| 4 | The Executive                             | 70  |

| 5 | The machine independent part              | 72  |

|   | 5.1 Compiler and the chain                | 72  |

|   | 5.2 Compiler support routines             | 76  |

|   | 5.3 Compiler auxiliary routines           | 80  |

|   | 5.4 Entry generating routines             | 80  |

|   | 5.5 Structuring words                     | 82  |

|   | 5.6 Address fetching                      | 82  |

|   | 5.7 Text handling routines                | 83  |

|   | 5.8 Stack display                         | 83  |

|   | 5.9 Chain control operators               | 84  |

|   | 5.10 Miscellaneous high level routines    | 86  |

| 6 | The machine dependent routines            | 87  |

|   | 6.1 More details about the executive      | 87  |

|   | 6.2 Directly available code routines      | 88  |

|   | 6.3 Code routines managed by the compiler | 89  |

|   | 6.4 Initialization                        | 90  |

| 7 | Typical IPS Compiler Routines             | 90  |

| A | ppendix A IPS - Short Reference Summary   | 97  |

| A | ppendix B The AMSAT cassette standard     | 102 |

| A | ppendix C The ASCII code                  | 104 |

## **Preface to 1st Edition**

#### ARE YOU

owner of a microcomputer based on the 8080, 6800, 6502 or the CDP 1801/2 ?

#### ARE YOU

looking for an efficient, easy and clean way to program your computer using a high level language ?

#### DO YOU

wish to use your microcomputer in time critical applications like controlling devices, robotics or fancy games ?

#### DO YOU

wish to have your computer look after several tasks at the same time ?

#### THEN LOOK NO FURTHER !!!

IPS has been designed to solve these problems for the AMSAT space projects (communication satellites for radio amateurs) and has since been found to be a very useful tool for programming small systems. It uses an extremely modular and structured approach to develop programs interactively. Because IPS is a high level language, it allows the sharing of programs regardless of the processor for which they were developed.

## **Preface to 2nd Edition**

This manual was written by Karl Meinzer in 1978 during the evolution of the IPS operating system, but was never published in any substantive form. A hand corrected draft printout was circulated to a few interested engineers who then reproduced it ad hoc, minus several chunks, via ever worsening photocopies. But the paper original was declared lost.

Happily, in 1996 the IPS manual was discovered to have survived on Atari 800XL (ca. 1980) computer cassette tapes, and moreover had recently been transferred to floppy disc by Robin Gape, a prominent IPS contributor in the mid '80s. Thus it became practical to republish the document.

In the late '70s, disc systems were uncommon. Thus the manual refers throughout to cassette tape as its input/output medium; IPS computers usually had two recorders. This anachronism does not detract in any way from the relevance of IPS, and for the sake of consistency has been left in the document.

IPS development has not stood still. It has been written for the Atari ST and in 1996 for 32-bit Acorn RISC Computers. The latter are based on the ARM family of processors, and run IPS 100-1000x faster than the early 1802/6502/8080 systems. Hopefully re-publication of this manual will encourage versions for other machines, notably the IBM-PC.

A significant application of IPS has been its use as the Operating System for AMSAT's Phase III series of communications spacecraft. The Oscar-13 (Phase III C) satellite's 1802/IPS computer functioned without missing a beat for eight years until it re-entered the atmosphere in 1996. Impressive for any computer's OS, let alone one functioning in space.

This re-publication is dedicated to Dr Karl Meinzer DJ4ZC in recognition of 30 years outstanding contributions to the Amateur Space Programme.

James Miller Cambridge, England, 1997.

## Introduction

One of the most significant technological innovations during the last few years is the integrated microcomputer. This device is permeating all walks of life; it allows solution of a large number of engineering problems that previously could not be solved due to excessive hardware complexity. With microcomputers the limiting factor has become the effort one is required to invest in software engineering. There are two phases to each project.

- 1. The problem must be analyzed and the activities the computer is to perform must be defined.

- 2. A program has to be written and tested.

The work involved in point 1 can never be eliminated by programming aids, but the workload of point 2 is heavily dependent on the quality of the programming support used; with ideal support the work involved in point 2 should constitute only a small fraction of the total effort.

Most programming aids available fall far short of this goal. The conventional "high-level" programming aids are derived from the classical data processing environment with different goals and constraints than given with microcomputers, so it is not surprising that most microcomputer programming is still done at assembler level. This means that the problem must be broken down into the small steps the computer is able to execute, and one is thus forced to live with the sometimes quite unsystematic structure of a computer resulting from hardware constraints.

For some time it has been known that the usual mini- and microcomputer architectures (with their linear structure) are poorly matched to the "human" method of understanding and decomposing a problem. Humans tend to think in alternatives and hierarchies. This eventually led to the programming concepts of "top-down design" and structured programming.

To date, there are no computers available matching these concepts. The next best thing one can do is to use a conventional microcomputer to simulate (emulate) such a high-level computer. The programming system IPS described in this book uses a general approach somewhat similar to FORTH (Moore [1]), but was designed to provide more demanding user interaction mechanisms and to use the typical low-cost peripherals of microcomputers. IPS mostly is a high level language allowing extremely modular structured programming. In contrast to other languages it is essentially free of syntax rules. It uses RPN (reverse polish notation) to make parameter passing between modules extremely simple and is designed to be as unrestrictive as low-level assemblers.

The high-level emulation technique is extremely economical in terms of memory usage - the entire system resides in 6 Kbytes of memory. But programs execute only two to three times slower than optimum assembler code. In most instances this represents no problem, however extremely time-critical applications or special hardware may require some assembly language interfaces. IPS thus employs an integral assembler to facilitate these extensions.

The design of IPS allows high level extensions as well. A detailed discussion of the philosophy of IPS is given at the beginning of chapter III.

This book is organized into three chapters of increasing sophistication. *Chapter I* presents an introduction to the language; the material presented there will enable you to accomplish all "regular" programming tasks. *Chapter II* introduces the assemblers for the COSMAC 1801/1802, the 8080, the 6800 and the 6502 allowing low-level extensions and interfaces. Finally, *Chapter III* describes and documents the inner workings of IPS; this material will be useful if you wish to extend or change IPS itself.

The easiest way to learn IPS is to have access to a computer with IPS installed, so that you may "learn by doing" as you progress through this book.

Since IPS is an integrated programming system with no other software required, it necessarily needs a number of interfaces to the particular hardware. If your installation does not have the same configuration as the system for which IPS was designed, some adaptations may be necessary. These generally are rather trivial for a person familiar with IPS, but if this is your first exposure, it may be a good idea to procure the assistance of someone more familiar with IPS during the first installation on your system.

I am certain you will find IPS a useful tool for a vast number of programming projects. If you should discover any errors or improvements, I will be pleased to learn of them.

Karl Meinzer Marburg, 1978.

### Acknowledgements

The development of IPS was triggered by the demanding and stimulating environment of AMSAT, a volunteer organization building communications satellites for radio amateurs as a public service with practically no funds.

Among the many individuals having contributed to IPS, I in particular wish to acknowledge the many helpful discussions and suggestions from G. Groh who suffered with me through the first implementations.

J. Lipfert applied IPS to a number of real-time applications within the University of Marburg. His fighting with the many traps of early IPS resulted in the present error philosophy.

R. Gerlich wrote a first implementation of IPS for the 6502. His work made many problems transparent particular to that processor, enabling the more compact version in this book.

R. Dunbar helped with the English mnemonics, the polishing of this book and (in 10 hectic nights) bringing up the 8080 IPS.

#### References

| 1. C.H. Moore    | Forth: A new way to program a minicomputer                     |

|------------------|----------------------------------------------------------------|

|                  | Astron. Astrophys. Suppl. 15,497-511, 1974                     |

| 2. T. Dollhoff   | Making hash with tables                                        |

|                  | Byte, vol. 2, No.1, 18-30, January 1977                        |

| 3. J.F. Herbster | Improving quadratic rehash                                     |

|                  | Byte, vol. 2, No.5, 142, May 1977                              |

| 4. W.W. Peterson | Prüfbare und korrigierbare Codes                               |

|                  | R.Oldenbourg Verlag, Munich and Vienna 1967                    |

| 5. N. Wirth      | Software Practice and Experience                               |

|                  | Modula, (3 papers) vol. 7, 3-35, 37-65, 67-84, 1977            |

| 6. D.W. Johnson  | Multitask $\mu P$ executive routine uses only six instructions |

|                  | Electronic Design 4, February 15, 1978                         |

## **CHAPTER I**

#### How to use IPS

#### **1** Hardware requirements for IPS

This book describes IPS for four microprocessors:

- The RCA COSMAC (CDP 1801/1802)

- The 8080 ( thus also covering the Z80 )

- The 6800

- The 6502

All four processors demonstrate similar performance in the IPS environment and require about the same amount of memory to support IPS. The system occupies about 6 Kbytes; in order to have sufficient space for user programs 16 Kbytes are recommended as the memory complement. My experience indicates that the remaining space is sufficient to accommodate even very large programs. As a guideline, you may assume that IPS programs require about one half the memory of similar BASIC programs.

IPS is an extremely interactive system. Key to these interactions is a video memory organized as 16 lines by 64 characters. This memory is part of the processor address space; by storing into these addresses, the content is immediately displayed on a TV-screen. (During processor access to this memory, the TV-screen is blanked).

Some TV-memories on the market possess scrolling and selective blanking features to facilitate emulating a teletype mode. IPS does not use a teletype emulation mode and thus does not need nor use these features.

The TV-memory should at least be able to display the 64 ASCII character subset. It should also allow inverting character and background brightness in order to be able to display a cursor. If you utilize a hardcopy device having lower-case capability, I recommend a display having the full 128 character set. This will allow you to edit normal correspondence or other written material in a generally acceptable form.

To enter text into the system, an ASCII keyboard is required. The COSMAC and 8080 systems use a bit-serial approach for entering the characters, the other two versions enter the seven character-bits in parallel. The 8080 may also be used with the parallel configuration. The parity-bit is not used.

The keyboard preferably should have the "CTRL" characters marked on the keys. Otherwise you will be required to mark some of the keys as to their control function. Also, the keyboard should have a provision for locking it in upper case. Make sure that the keyboard has the full ASCII character set; some keyboards do not have the @ character ( which is frequently used in IPS ).

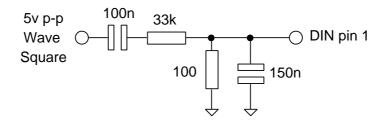

Mass storage in the IPS versions described in this book is done using standard tape cassettes. The four systems use the AMSAT cassette standard. (See appendix B). From a software point of view the significant property of this standard is the fixed length of the records; all records are 512 bytes long and may contain arbitrary data (character or binary). This length allows the use of the TV-screen as an input buffer; one record (block) fills exactly one half of the TV-screen.

The AMSAT standard uses a synchronous rate of 400 bit/s and thus is approximately twice as fast as the asynchronous 300 bit/s *Kansas-City* standard. The AMSAT standard is marginally acceptable from a speed point of view. If you do not intend to use the AMSAT recording technique, any other standard faster than this system and capable of blocks of 512 arbitrary bytes could be used; of course the software drivers may have to be changed.

The IPS represents a multiprogramming system. It thus cannot use timing loops or other programming techniques which tie up the computer in a single task. In order to have a means of coordinating the various activities and to keep time, a 20 ms hardware input of a sort is required. This input also allows the software clocks to keep time. With the COSMAC this input is applied to "External Flag 1 "; with the other processors it forces an interrupt.

Finally, the system requires a bootstrap capability to enter IPS initially. This may be a hardware load feature ( COSMAC ) or a small ROM program containing a loader.

Note that no front-panel switches or indicators are required; all communication with the system is effected via the keyboard and the TV-display. Only the cassette recorders need to be manipulated additionally.

Here is a summary of the hardware requirements for an IPS installation:

- Processor : CDP 1801, CDP 1802, 8080, Z80, 6800 or 6502

- Memory : 16Kbytes RAM + loader ROM

- Display : 1024 byte video-RAM (16 x 64) ASCII character set, bit 7 to invert background and character

- Keyboard : ASCII keyboard featuring full character set

- Mass storage: Cassette system enabling the recording of 512 byte long blocks with arbitrary content

e.g. the AMSAT cassette recorder standard

- Timing: 20 ms crystal derived input to processor (ext. flag or interrupt)

- Front-panel : None required

Chapter III contains information on how to install IPS on computers using other microprocessors than the ones mentioned. You may assume that in a system like IPS most good points and bad points of the various processors average out, so the performance variations between the different 8-bit-processors are not very significant. A better guideline for the choice of a system would be hardware availability and simplicity ( chip-count ).

Nevertheless, a processor should meet certain minimal criteria. Most important, it should have 16-bit addressing capability (at least 15-bit) without any data addressing discontinuities such as paging. Having to handle such discontinuities would considerably slow down the system. Preferably the processor should incorporate some 16-bit registers on the chip allowing indirect addressing. Ideally they should have an auto increment feature and indexing capability.

The COSMAC architecture comes closest to these requirements. The 8080 is less well matched to IPS, but the powerful 16-bit instructions are a compensation. With the 6800 operations requiring multiple 16-bit pointers are awkward, but the capability of indexing with reference to the stack is very powerful. The 6502 suffers from not having a single 16-bit register on the chip. The high speed of this processor and the additional addressing modes nevertheless make this processor about as fast as the other ones. But the emulator code is significantly more voluminous than that of the other processors.

IPS also could be installed on 16-bit computers. It will run there about 2 to 5 times faster than on 8-bit machines. I doubt that there are many installations where this speed would actually be required. On the other hand, cost goes up nearly by a factor of two; presently memories are only available as 16K by 1, but not as 8K by 2. Also the choice of the processor becomes more critical; processors well matched to a stack-organization (e.g. PDP 11) may perform significantly faster than processors designed for a workspace concept.

#### 2 Keyboard Operations

#### 2.1 Your computer and IPS

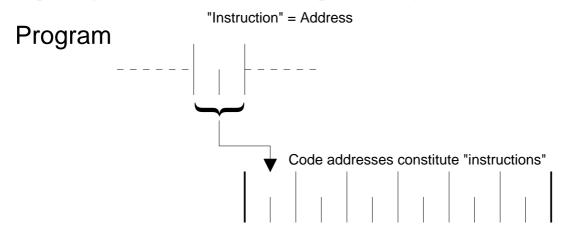

Your computer, by its design, requires the instructions it is to perform as a binary pattern in its memory. These instructions are difficult for humans to handle, not only because of the binary nature, but also because of the linear arrangement in the computer memory. A belated insertion, for example, requires that the rest of the memory contents be modified.

Programming is much simplified, if we can instruct the computer in a language which matches our thinking. In addition, programs thus become self documenting, which eliminates the need for separate documentation ( which is a pain in the neck and thus is often badly neglected ). We also need a simple and transparent means of testing our programs. IPS is designed to provide these services and to translate your program into a format which the computer can execute.

IPS uses a kind of dictionary. This dictionary contains the name of an activity and a description of the steps constituting that activity. IPS itself is largely such a dictionary, defining the translation process. Each process the computer can execute may be described by such a dictionary. Creating such a dictionary describes to the computer how to handle the process. The computer can interpret this dictionary, hence the name *Interpreter for Process Structures* (IPS). Most of this book describes how to create such a dictionary by merely explaining to the computer the problem you wish to solve.

#### 2.1.1 Communicating with IPS

The following sections assume that you have loaded IPS into your computer.

The TV-screen has 16 lines with 64 characters each. In the lower 8 lines the computer expects its instructions from you via the keyboard or from cassettes. The cursor ( a black bar ) indicates the next position you may write into. The eight upper lines are used by the computer to communicate back to you.

All input to the computer consists of *words*; they are separated by one or more blanks. Words may consist of arbitrary strings of characters without blanks. There are three different kinds of words: numbers, IPS-words and words you have defined yourself. After you have written some words, and if you have made no typing error, you press CR (Carriage Return) to tell the computer to process the words. If the computer can process the words without error, it clears your entry to indicate that it has complied with your text.

If you made a typing error, you may correct it before pressing CR by using the following keys:

BS (CTRL-H) Backspace, moves the cursor 1 position back

FS (CTRL-\) Forwardspace, moves the cursor to next position

LF (Line Feed) Moves the cursor 1 line down

You cannot move the cursor off the screen; if you try to move it beyond the last line, it will show up in the first line and vice versa.

You correct your writing by simply overwriting the erroneous parts. The division of the screen into lines of 64 characters is invisible to the computer; you may write words over line boundaries without separation signs. The computer "sees" the screen as a single line of 1024 characters.

After the CR, the computer reads the text from the beginning of the 8-th line to the CR. You may write into the first 8 lines as well, but the computer ignores this text.

#### 2.2 The Stack

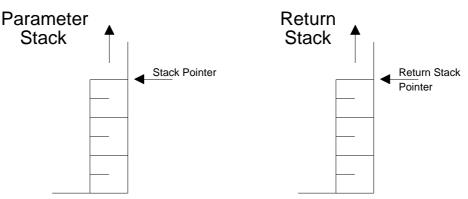

Before you attempt to make the computer perform simple operations, the *stack* should be introduced. It is a temporary storage for numbers. You may visualize it as a number of cards, each having one number written on it; these cards are then "stacked" on top of each other in the sequence they are written. The last number thus is on top.

Most instructions of IPS expect some numbers on the stack; they remove these and replace them by results. Instructions expecting one number always refer to the top of the stack, instructions expecting two numbers refer to the two top numbers and so on. The results are then placed on top of the stack.

You will see that such a stack is an ideal place to store and to pass intermediate results within program modules as well as between them. To simplify program development and debugging, the contents of the stack are displayed in the first two lines of the TV-screen. The stack contents are displayed with the top entries to the right. If there are more than 16 stack entries, only the 16 topmost are shown. The stack display may be switched off.

#### 2.2.1 Numbers

All numbers used by IPS are stored internally as 16-bit integers and thus range from -32768 to 32767. Other number types may be defined if necessary.

The internal representation of the numbers is binary, with positive numbers bit 15 is zero; with negative numbers bit 15 is set to one. Logically they are produced by counting backwards from zero (-1 thus corresponds to 1111111111111111, or in hexadecimal writing #FFFF)

#### 2.2.2 Number entries

In order to place a number on the stack, you simply type it on the keyboard.

- *a*. Unsigned numbers are read by IPS as positive decimal numbers and placed on the stack. (a + sign is not allowed)

- b. A sign followed by figures is read as a negative decimal number.

For example:

**123** -415 <CR> produces a stack display of 123 -415 <CR> will now be tacitly assumed to follow all entries. You may remove numbers from the stack one at a time by typing the word DEL . **DEL DEL** will thus remove both of the above numbers.

c. In addition to decimal numbers you may also enter binary or hexadecimal numbers. Hexadecimal numbers are numbers starting with the # and having the digits 0 - 9 and A - F (10 - 15). Binary numbers start with a B followed by digits of 0 or 1.

With all numerical inputs, leading zeros may be omitted. But you must be careful not to exceed the permissible range possible with 16 bit numbers. Otherwise, erroneous numbers are placed on the stack. The largest permissible numbers are:

| -32768                                 | to | 32767                                |

|----------------------------------------|----|--------------------------------------|

| #0000                                  | to | #FFFF                                |

| B0000000000000000000000000000000000000 | to | B111111111111111 (16 digits after B) |

The format of the stack display on the TV-screen depends on the number last entered. For example:

**15 B111 #15** results in the display:

```

#000F #0007 #0015 (the last entry was in hexadecimal)

```

If you enter now **-40** you get:

15 7 21 -40 (the last entry was in decimal)

If the last entry was binary, the stack is displayed in hexadecimal; there is no binary display.

#### 2.2.3 Arithmetic operations

The basic arithmetic operations are effected by the words:

+ - \* / /MOD

If you use the above stack content ( 15, 7, 21, -40 ) and enter the "word" + you obtain: 15 7 -19

The upper two numbers of the stack were removed, added and the result was placed on the stack.

Entering a - now results in: 15 26 Now entering a \* results in: 390

All arithmetic operations are modulo  $2^{16}$ . There is no diagnostic at overflow; it is the programmer's responsibility to ensure that the number range is not exceeded.

The division and /MOD are defined for positive numbers only, but these may extend up to #FFFF. /MOD is a division leaving a quotient and on top of it the remainder.

#### 2.2.4 Logical operators

In addition to the arithmetic operations IPS enables logical operations; there are three operators ( words ):

AND OR XOR

These operations expect two numbers on the stack just like the arithmetic operators; the operation takes place bit by bit and the result is left on the stack.

With AND the bits have to be pairwise 1 in order to have the corresponding bit in the result to be 1.

With OR at least one of the bits has to be 1 to have a 1 in corresponding bit in the result.

With XOR a 1 in the result is obtained, if the two corresponding bits are different.

e.g.: **B1010 B1100 XOR** results in #0006 (i.e. B0110)

So far we have seen only operations using two numbers. There are also operations using a single number.

The word INV replaces all bits of a number by the opposite.

The word BIT takes a number from the stack and discards all bits except the four least significant ones. This resulting number (it may range from 0 to 15 or #0 to #F) is taken as a number identifying a specific single bit in a 16-bit number. (The 16 bits of a number may be identified as bits 0 through 15, bit 0 being the least significant. ) BIT now places a number on the stack in which all bits are 0 except the one identified by the original four least significant bits.

e.g.: **#7** BIT results in #0080 equal B000000010000000

Bit-number: 15 7 0

This function is useful, if you want to test large numbers of bits in loops.

#### 2.3 Stack manipulations

#### 2.3.1 Parameter Stack Operations

So far you can see that the stack is the source and destination of all operations involving numbers or logical quantities. In order to give you more freedom in dealing with these quantities, IPS provides some stack manipulation operators. You have already learned one; the word DEL. This is the complete list:

| DEL  | DELetes the top entry                                             |

|------|-------------------------------------------------------------------|

| PDEL | DELetes the two top entries ( a Pair )                            |

| DUP  | DUPlicates the top entry                                          |

| PDUP | DUPlicates the two top entries ( a Pair )                         |

| SWAP | interchanges the two top-entries                                  |

| RTU  | Rotates the Three top entry Up, the old topmost entry becomes the |

|      | third-lowest                                                      |

| RTD  | Rotates the Three top entries Down, the old third-lowest          |

|      | becomes the top entry                                             |

| SOT  | duplicates the Second entry On Top of the stack                   |

SOT duplicates the Second entry On Top of the stack.

The following table demonstrates these operations:

|      | Befe | ore | ope | ration |   | Afte | r o | pera | ition |    |   |

|------|------|-----|-----|--------|---|------|-----|------|-------|----|---|

| SWAP | 5    | 8   |     |        |   | 8    | 5   |      |       |    |   |

| DUP  | 8    | 5   |     |        |   | 8    | 5   | 5    |       |    |   |

| DEL  | 8    | 5   | 5   |        |   | 8    | 5   |      |       |    |   |

| RTU  | 8    | 5   | 12  |        |   | 12   | 8   | 5    |       |    |   |

| RTD  | 12   | 8   | 5   |        |   | 8    | 5   | 12   |       |    |   |

| SOT  | 8    | 5   | 12  |        |   | 8    | 5   | 12   | 5     |    |   |

| PDUP | 8    | 5   | 12  | 5      |   | 8    | 5   | 12   | 5     | 12 | 5 |

| PDEL | 8    | 5   | 12  | 5 12   | 5 | 8    | 5   | 12   | 5     |    |   |

#### 2.3.2 Return Stack Operations

In addition to the normal stack ( the operand or parameter stack ) there is another stack IPS uses internally. This stack is called the *return stack* for reasons explained later; the return stack may also be used by the programmer. There are some restrictions to be observed though, that will be explained in the section describing loops, ( Sect. 3.1.2 ).

The return stack often represents a welcome intermediate storage area, if you wish to access deeper layers of the stack.

#### Sect. 2 - Keyboard Operations

These three operations are available:

- S>R takes a number off the stack and places it on the return stack

- R>S takes a number off the return stack and places it on the stack

- I (called Index, see Sect. 3.1.2) duplicates the content of the return stack onto the stack without changing the return stack.

This table demonstrates the actions:

|     |            | Before operation | After operation |

|-----|------------|------------------|-----------------|

| S>R | <b>S</b> : | 5 7              | 5               |

|     | R:         | empty            | 7               |

| Ι   | <b>S</b> : | 5                | 5 7             |

|     | R:         | 7                | 7               |

| R>S | <b>S</b> : | 5                | 5 7             |

|     | R:         | 7                | empty           |

Note: Do not remove numbers from the return stack that you did not place there previously !

#### 2.4 Named constants and variables

The stack is very practical for short term storage and for the manipulation of numbers, but it is not very suitable for the permanent storage of numbers. IPS offers two possibilities to store numbers under a name: constants and variables.

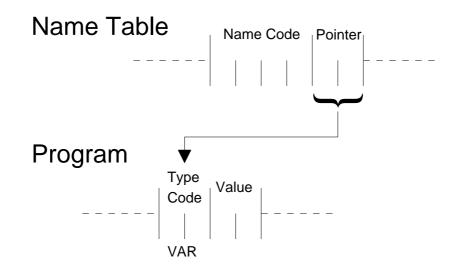

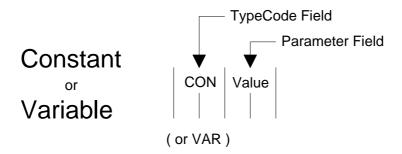

To accomplish this, IPS creates an entry in the dictionary consisting of a compressed form of the name (namecode, 4 bytes), a pointer to code (2 bytes), an identifier of the code type (typecode, 2 bytes) and the value of the entry (2 bytes). This structure is fully described in Chapter III. See also Sect. 2.5.

*Constant* entries are produced for those numbers which are not changed during the course of the program.

To create a constant entry you enter the value the constant is to have, the word CON and the name the constant is to have.

e.g.: **510 CON LIMIT** produces a constant-entry named LIMIT containing a value of 510.

If you now type the word LIMIT, the constant 510 is placed on the stack. (It also continues to exist in LIMIT, of course.)

You may use any string of arbitrary characters for the names of dictionary entries - that includes special and control characters. For example or >>> are perfectly valid names. Only blanks and round brackets are not permissible. (See Sect. 3.1)

Because changing the value of constants is a bit involved, there is a second type of number-entry called *variable*.

e.g.: **745 VAR AUTO** creates a variable entry.

Typing AUTO does not deliver the value of AUTO, but the memory position where AUTO is stored. Variables thus are not named numbers, but named locations (addresses) in which numbers may be stored.

In order to obtain the contents of such a location the word @ is used. It replaces an address on the stack by the actual data residing at that address.

e.g.: AUTO @ results in 745 to be placed on the stack ( Please remember that words are separated by one or more blanks. )

Because the variables deliver the address on the stack, it is simple to change their value. The word ! ( store ) expects two numbers on the stack; a number that is to be stored and on top of it the address where it is to be stored. When performing storage, the ! removes both numbers.

e.g.: LIMIT AUTO ! calls the constant LIMIT (510), calls the address of AUTO; then stores the 510 into AUTO. Now entering AUTO @ delivers 510 to the stack.

It is also possible to change the value of a constant; it is recommended that this option be used during program development only, however. (Some IPS versions store constants in ROM).

In order to store a new value into a constant, you need the address of that constant. The word ? followed by the name of the constant delivers this address to the stack.

e.g.: **45** ? **LIMIT** ! puts a 45 on the stack, then the address of LIMIT is placed on the stack and finally ! stores the 45 into the address of LIMIT .

Some IPS versions do not allow use of the ? in programs. It is good practice to create variable entries if the value of that entry changes during the program.

#### 2.5 Fields

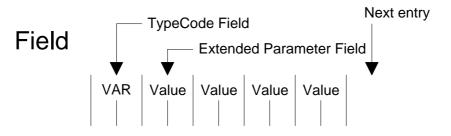

Often a set of numbers set required, which are stored under a single name and which differs only by an index. Such structures are called *fields*. Such fields may be defined by the use of an extension of the variable concept. In order to understand this, let us take a closer look at how variables are stored in memory. All entries in the dictionary (nametable) are very similar.

The nametable contains the "name" coded into 4 bytes. The first byte contains the number of characters in the name (truncated to 63, if necessary). The following three bytes contain a 24-bit number computed from all the ASCII

characters of the name. All entries into the IPS dictionary utilize this name coding; each name has a unique code and may thus be identified later.

In the nametable each namecode is followed by a pointer which indicates the dictionary position containing the typecode of the entry. A variable entry in the dictionary consists of a 2 bytes typecode for variable followed by 2 bytes containing the actual numerical value of this particular variable. For full details see Chapter III, Sect. 5.3.

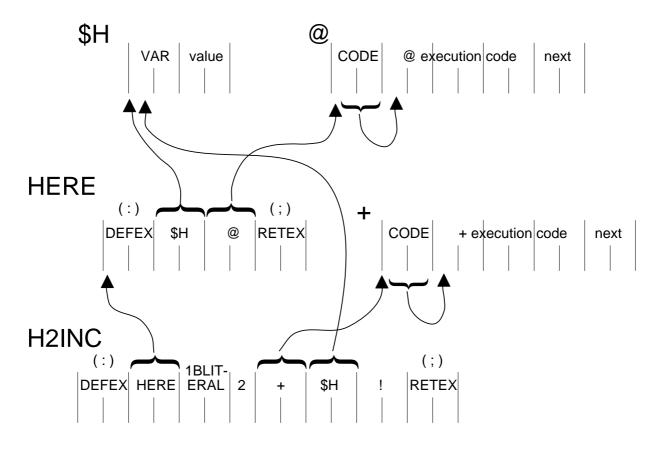

IPS has a system-variable named \$H, which contains a pointer to the next free position in the dictionary. Thus IPS keeps track of where the next entry in the dictionary is to go.

If you increment this pointer after creating a variable-entry, you make room in the variable to contain more than two bytes. If you want to create a field for 10 numbers, for example, you must increase \$H by 9 number positions (18 bytes total, since you will recall that each number entry consists of two bytes.)

e.g.: 0 VAR GROUP produces a variable GROUP

If you want to be able to store into it 10 numbers, you must increase \$H by 18 ( bytes ).

**\$H @ 18 + \$H !** ( instead of writing \$H @ you may also write HERE ; it has the same effect )

To now store a value of 15 into component number 4 of the field ( counting: 0  $1 2 3 \dots$  ), you type:

**15 GROUP 8 + !** The 8 + increases the address by 8 bytes, that is by four numbers, before the storage takes place. Similarly, component 3 is accessed by:

GROUP 6 + @

#### 2.5.1 Field Operations

To simplify the creation and manipulation of fields, IPS offers five words;

FIELD !FC >>> L>>> and F-COMP

To create a field you may write:

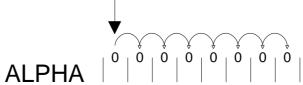

**8 FIELD ALPHA** This creates a field named ALPHA being 8 bytes wide. In this field all numbers are initially undefined. To preset them to specific values, you type:

5 9 -123 17 ALPHA 4 !FC ( store field components )

This operation stores the 4 numbers 5 9 -123 17 (in this order) into the field ALPHA; the number of components must always be specified.

With the operation !FC, as with all other IPS operations expecting numbers on the stack, the following principle is always observed: first the "source", then the "destination" and finally additional information is expected on the stack in this order.

To move components of a field into another field, you could accomplish this component by component using @ and ! . With a large set of data this would be clumsy and slow. To simplify and speed up this activity, a special word is available.

Using the two fields GROUP and ALPHA of 20 and 8 bytes, respectively, you might move ALPHA into GROUP say, beginning at position 10:

ALPHA GROUP 10 + 8 >>>

source destination no of bytes field transport Graphically:

ALPHA  $| \stackrel{0}{|} \stackrel{1}{|} \stackrel{2}{|} \stackrel{3}{|} \stackrel{4}{|} \stackrel{5}{|} \stackrel{6}{|} \stackrel{7}{|}$ Solution Solution

This transport takes place directly (not via the stack) and thus is much faster than transporting individual components. The transport takes place byte by byte starting at the lower addresses. The addresses may overlap. This enables the following useful function:

Assume you wish to set a total field to zero, you type:

0 ALPHA ! (clears the first two bytes) ALPHA ALPHA 1 + 7 >>> Graphically:

The word >>> transports 1 - 256 bytes. If you wish to transport a larger number of bytes, you may use the word L>>> . This word transports between 0 and 32767 bytes. If the number of bytes to be transported is negative, no transport takes place.

The word L>>> takes slightly longer to execute than >>>. For short transports the word >>> thus is the preferred one.

In this context note that there is also an instruction which compares two fields, byte by byte ( length: 1 - 256 bytes ).

| Write:  |         |              |                  |

|---------|---------|--------------|------------------|

| GROUP   | ALPHA   | 8            | F-COMP           |

| field 1 | field 2 | no. of bytes | field comparison |

This operation compares the first 8 bytes of the two fields. If these field contents are identical, F-COMP leaves a 1 on the stack. If GROUP is numerically smaller than ALPHA, the result is 0; if GROUP is larger, the result is 2. The bytes having the higher addresses are also treated as the more significant ones.

#### 2.6 Byte manipulations

Numbers are stored in two bytes, and the numerical or logical operations always operate on 16-bit (2-byte) quantities. Often it is desirable though, to access single bytes (8 bits) particularly if you wish to manipulate text strings. There are two words enabling byte accesses:

@B expects an address on the stack; it removes it and replaces it with the content of the byte at that address. This number may have values between 0 and 255 (#00 to #FF) and is the least significant byte on the stack. The most significant byte on that stack entry is set to 0 (#00).

!B stores a single byte into an address. The operation is analogous to the !; the most significant byte of the number to be stored is discarded.

In variables and constants, the byte having the lower address is also the least significant one. Numbers on the stack always are held and handled as two bytes - there is no single byte access to the stack.

#### 2.7 Error messages

If IPS does not recognize a word or a number, an error indication is produced. IPS at first checks whether the input word is already in the dictionary. If so, the word is executed. Else IPS checks whether the input word is a valid number. In this case the number is placed on the stack. If both of these tests fail, IPS writes in front of the unidentified word, an inverted ? and stops processing the input. You may now correct ( starting after the ?) your text. If you enter CR again, IPS continues to read after the ?.

There are a few activities, in which the instruction is followed by a name (e.g. VAR). If there is an error in such an operation, both words must be repeated.

Often there is a longer text following the error ? . Make sure that you place the cursor after the last word of your entry before pressing CR. IPS reads only to the position of the cursor prior to entering CR.

There are only a few error messages beyond the ? mentioned; they are written into the seventh line:

| STACK EMPTY !    | You removed a number from the empty stack; the stack had to be restored. |

|------------------|--------------------------------------------------------------------------|

| MEMORY FULL !    | The dictionary cannot accept further entries.                            |

|                  | This will rarely be encountered.                                         |

| DUPLICATE NAME ! | The name is already in use by you or the                                 |

|                  | system; select a different one.                                          |

| TEXT-ERROR !     | )                                                                        |

| STRUCTURE ERROR! | ) These will be explained in Section 3.                                  |

| NAME MISSING !   | )                                                                        |

The error messages remain on the screen until they are acknowledged by typing OK. This will clear the message and also re-enable cassette reading. (An error will stop it, see Sect. 3.3, Tape Operations)

## 3 Programming

### **3.1 Definitions**

So far, methods have been introduced which allow the computer to perform mathematical or logical operations. The main strength of a computer though, lies in its ability the "remember" a sequence of actions and to perform them at a later time as dictated by other events, e.g. at a certain time or after certain external events.

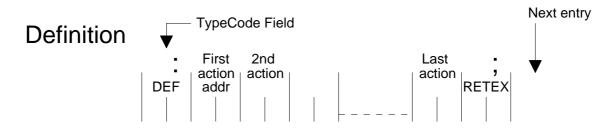

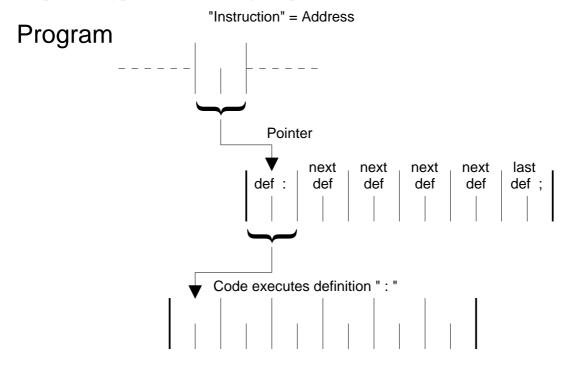

To enable the computer to remember a set of actions, select a name and then enter the actions required. To be precise, type:

: name word word ... word ;

The colon produces an entry identified by the name which follows the colon. The following words are not executed, but stored in the entry for later execution (coded internally as addresses). The semicolon terminates the entry. Again: words are separated by blanks; the semicolon is a word, too.

In order to make such definitions of actions more readable, you may insert arbitrary comments - simply enclose these comments by parentheses. IPS will ignore these comments, but later they may help you to understand your programs.

Example of a definition:

: 4NUMBERS 10 DUP ( PUTS 10 ON THE STACK TWICE ) 15 DUP ( PUTS 15 ON THE STACK TWICE ) ;

If you now type **4NUMBERS**, the stack will display:

```

10 10 15 15

```

You may see something new from this example beyond the creation of definitions: within definitions numbers are also not executed ( put on the stack ), but "compiled" into the definition in such a way that they will be put on the stack at the time of actual execution of the definition.

The only rule which must be observed is that you can put into definitions only items as are defined within IPS itself, or those which you have defined previously. Of course you may put into definitions other definitions you created before; thus you may create arbitrary hierarchies of definitions.

#### 3.1.1 Branches

One of the most important properties of computers is their ability to make decisions based on the result of calculations or other events. IPS offers several possibilities towards this end. They assume that you have left a number on the stack. This number is to govern the further actions of the computer. For the time being, let us assume that there is a 0 or a 1 on the stack. You may then use the following words:

| YES? word word word | ( actions to be performed, if a 1 was |

|---------------------|---------------------------------------|

|                     | on the stack )                        |

| NO: word word word  | ( actions to be performed, if a 0 was |

|                     | on the stack )                        |

| THEN word word      | ( continuing action in both cases )   |

The word YES? removes a number from the stack and checks it. If it is a 1, the words following the YES? are executed and then the words following the THEN. If there was a 0 on the stack, the words following the NO: are executed and the program continues after the THEN.

*Rule:* Each YES? must be followed by a corresponding THEN The NO: may be omitted; if the number on the stack is 0, the program continues after the THEN.

Generally there is not a 0 or 1 on the stack to base a decision on, it rather has to be calculated or produced by a comparison.

Strictly, only the least significant bit of the number is checked. An odd number leads to the YES? action, an even number results in the NO: action.

IPS offers the following standard comparisons:

| >0         | ) These compare a number on the stack against 0. They     |

|------------|-----------------------------------------------------------|

| <0         | ) remove the number and replace it by a 1, if the         |

| =0         | ) condition is true, else they put a 0 on the stack.      |

|            |                                                           |

| >          | )                                                         |

| <          | ) These compare two numbers on the stack and remove them. |

| =          | ) They put a 1 on the stack, if the condition is          |

| >=         | ) true, else they put a 0 on the stack.                   |

| <=         | )                                                         |

| =/         | )                                                         |

| $\diamond$ | ) Equivalent to $=/$ in some versions of IPS.             |

|            |                                                           |

F-COMP Compares two fields, as explained earlier.

In addition to these standard comparisons, you may also use the logical operations. In this case you utilize only their effect on the least significant bit.

e.g.: A @ B @ > C @ D @ < AND YES? ... NO: ... THEN ...

These words will test, if A > B and C < D. Only if both are true, the words following YES? are executed. It is a good exercise to write down the state of the stack after each word.

The "aligned" method of writing the YES? NO: THEN of course is not mandatory, but it helps to improve the readability of programs and is an insurance against trivial errors (like forgetting the THEN).

#### 3.1.2 Loops

Many problems require a repetition of actions before you may continue with other instructions. IPS has four ways of effecting repetitions.

1. Instruction sequences requiring an initially unknown number of repetitions are written between the words LBEGIN and LEND? . LEND? expects a number on the stack and removes it. If it was 1, the loop terminates and the computer proceeds with the activities following the LEND? . If the number found by LEND? was 0, the instructions following the LBEGIN are repeated again. This repetition continues until the LEND? finally finds a 1. (Again, as with the YES?, only the least significant bit is tested; the loop terminates with an odd number.)

The following program demonstrates this concept.

```

: PICTURE TV4 ( THIS IS THE ADDRESS OF THE 4TH LINE )

LBEGIN #40 ( ASCII FOR @ )

SOT ( GETS ADDRESS, INITIALLY TV4 )

!B ( DEPOSITS @ INTO THE ADDRESS )

1 + ( INCREMENTS ADDRESS )

DUP TV4 64 + = ( ADR. = TV4 + 64 ? )

LEND? DEL ( ADDRESS ) ;

```

This program may now be executed by typing PICTURE . It will fill line 4 of the TV with @-characters.

Note: IPS has the constants TV0, TV4 and TV8 containing the addresses of the start of line 0, 4, 8 of the TV-screen. The constant TVE is the address of the last character on the TV.

2. With the LBEGIN ... LEND? construct the loop is executed at least once, because the termination test is at the end. If you need a loop with the test at the beginning, use this construct:

| LBEGIN      | words for the test                        |

|-------------|-------------------------------------------|

| YES?        | words to be executed, if test delivered 1 |

| THEN/REPEAT |                                           |

The THEN/REPEAT always transfers control back to LBEGIN. The loop terminates if the test prior to YES? delivers a 0.

Again a small sample program:

```

: A-LINE TV4 LBEGIN

```

DUP TV4 64 + < ( LINE NOT YET COMPLETE ) YES? #41 ( ASCII FOR A ) SOT !B 1 + THEN/REPEAT DEL ;

This program will fill line 4 with As.

In the LBEGIN ... YES? ... THEN/REPEAT construct the word NO: is not permissible. Logically the same result will be obtained, if the NO: action follows the THEN/REPEAT.

*3.* Actions to be performed a specific number of times, are placed between the words EACH ... NOW. This construct has an iteration counter ( also called index ). The word EACH expects two numbers on the stack, the loop begin ( the initial value of the iteration counter ) and the loop limit. The loop is executed for each consecutive number of the iteration counter until it exceeds the loop limit. You may simplify the sample program of above by writing:

: CLEAR TV4 TV4 63 + EACH #20 ( ASCII BLANK ) I ( GETS THE INDEX, IN THIS CASE THE ADDRESS ) !B NOW ; CLEAD will show line 4

CLEAR will clear line 4.

The EACH takes the two parameters off the stack and puts them on the return stack. The NOW increments the iteration counter and then checks whether

it exceeds the loop limit. If not, the loop ( between EACH and NOW ) repeats. Else, the NOW discards the two parameters on the return stack and the loop is terminated. Inside the loop the loop limit and the iteration counter are on the return stack; the later on top. You may thus use the word I to access the iteration counter. If the initial value of the iteration counter exceeds the limit, the loop action is not executed at all.

4. If you desire another increment than one with the loop index, you may use the word +NOW instead of NOW. +NOW expects a number on the stack and removes it. The iteration counter is incremented by this number. e.g.

#### : PATTERN TV4 TV4 63 + EACH #5F ( ASCII FOR \_ ) I !B 3 +NOW ;

will write an "\_" into each third position when you type PATTERN.

The return stack first belongs to IPS; if you wish to use it, you must comply with these restrictions:

*a*. If you place something on the return stack within a definition you must remove it again in the same definition. IPS uses the return stack to remember where it is to return after executing a definition.

*b*. The EACH ... NOW construct also uses the return stack. If you place a number on the return stack within the EACH ... NOW loop, you also must remove it inside the loop. If you call a definition from within the loop, note that this definition puts a number on the return stack. Thus you cannot call I within this definition. If you need I within the definition, put it on the stack prior to calling the definition. (These rules may be circumvented by appropriate stack manipulations. But programs become difficult to read this way and this practice is therefore not recommended. )

#### 3.1.3 Nesting rules

Constructs using the YES? NO: THEN and loops may be arbitrarily nested. If you nest EACH ... NOW loops note that only the loop index of the inner loop is available by I. If you need the loop index of an outer loop, you have three options; you may "unpack" the return stack, you may put the index in the outer loop on the stack or you may store the index in the outer loop into a variable. Which of the solutions is optimum depends on the particular problem. Usually the last one is the most straightforward solution. Make sure that each YES? has a corresponding THEN, each EACH has a corresponding NOW or +NOW and each LBEGIN has a corresponding LEND? or THEN/REPEAT. If you violate this rule, IPS will write STRUCTURE ERROR! and the definition is not deposited into the dictionary.

STRUCTURE ERROR! with a residual number on the stack indicates a missing THEN, NOW or LEND? . If you also get the message STACK EMPTY !, there is an excessive THEN, NOW or LEND? . It is good practice to define definition entries with an empty stack, only in this way are you guaranteed that a structuring error will not result in additional damage to your program. After a structuring error therefore, remove residual numbers from the stack with DEL .

Entries expecting a name (e.g. VAR) must receive the name during the same input. Otherwise you will get the message NAME MISSING and the action is not executed. Apart from this rule, definition entries may extend over multiple inputs. In this case there will appear numbers on the stack, which you may ignore. The first number is always the same on your system and you may consider it an indicator for the definition mode of IPS.

#### 3.2 Text handling

Besides handling numerical or logical quantities, IPS also must be able to communicate with humans. Therefore, there are a few words to allow the handling of text, particularly for output to the TV-screen. Basically text is treated similarly to numbers, that is; you may include your text output in definitions or you may put it into fields. Each character occupies one byte. There are no basic differences between variables, fields containing numbers, or fields containing text strings except for the length of the parameter field. With variables it is two bytes, with fields you must define the length.

Numbers you put into a definition are placed on the stack when you execute the definition. Text strings, on the other hand, will be written on the TV-screen. There is a variable SP ( screen pointer ) whose content points to the position on the TV, where the next writing is to go. After writing, SP points to the first position following your writing. Text strings are marked as such by quotation marks, e.g.

: TEST " THIS IS A TEST " ;

will create a definition, whose sole purpose is to write THIS IS A TEST . If you type now TEST, IPS will write into line 4 THIS IS A TEST . (SP is initialized to TV4.)

Entering TEST once more will append this text to the old one, and so on.

Since the TV-screen must be reused, there is a clear-word: BLANKS. This word expects a number on the stack and writes this number of blanks beginning at SP. SP is not changed.

You may set SP again to line 4 and clear the screen by typing:

#### TV4 SP ! 256 BLANKS

If now you call TEST, the game starts all over again.

If a text string is used by different program parts, it is more economical memory-wise to place it into a text array. If you are not in the definition-mode, a text string as input ( in quotation marks ) will leave on the stack the position of the first character on the screen and the number of characters in the string. (Blanks are characters too, of course ). You may then store a text string into a field using !T e.g.:

#### " MOTOR DEFECT " GROUP !T

implies that there is a field named GROUP having a length of at least 12 bytes. MOTOR DEFECT will be stored into these 12 bytes, the rest remains unchanged. If GROUP is 20 bytes long, and you want to fill the rest by blanks, you may write:

" MOTOR DEFECT " GROUP !T

*Caution*: If the text contains more characters than the field has bytes, IPS will be destroyed. The number of characters of a text-string is the number of positions between the quotation marks minus two.

You may create the field in conjunction with the text input.

#### " COLD " 4 FIELD CD CD !T

Instead of writing 4 you might also have written DUP, but the length of the array would not be documented that way.

Text strings may have a length between 1 and 256 characters. If you forget the closing " or if the string is too long, you will get the diagnostic message TEXT-ERROR ! and the stack indicates the length of the erroneous string. Within a definition this also will result in a structuring error.

Outside definitions, the text string and the words connected with the further processing of the text must be within the same input, since the screen will be cleared after the input and thus the text will not available beyond the input.

Text stored in fields is transported to the screen using the word WRITE . WRITE expects on the stack the address of the field containing the string and on top the number of characters to be written. Again SP is used as pointer, and after writing, SP points to the next free position.

#### CD 4 WRITE

will write COLD on the screen. (See previous example).

To write numbers on the screen, you may use the word CONV. It takes a number from the stack, converts it into an ASCII string and then writes it at SP. SP again is updated to the next free position. The format of this writing is identical to the stack display.

The presentation ( decimal or hexadecimal ) depends on the last input. If you want to make certain, that the display is either decimal or hexadecimal, you must store ( prior to calling CONV ) a 10 or a 16 into the variable BASE .

e.g.: **10 BASE !** before calling CONV will guarantee a decimal display. CONV may produce up to six characters.

Text strings of course also may be transported to the screen using >>> . In this case SP, if you use it, is not updated. Also you may produce text on the screen by explicitly storing the numerical representation of the ASCII characters as was demonstrated in the loop sample-programs. All techniques together give you the choice to create the display handling best suited for your application.

#### **3.3 Tape cassette operations**

Programs ( definitions ) so far were only entered manually. But you may store your typing on cassettes. The recording technique uses low-cost cassette recorders and tape cassettes. The technical details are described in appendix B. Each recording operation records a "block" of 512 bytes at a time ( exactly one half TV-screen, 8 lines ). The recorder should be modified in such a way that the computer can start and stop the recorder motor. This feature allows automation of the more important tape operations.

To create a text recording, you first put IPS into the text editing mode by entering the word TEXT. Then you have a number of additional editing keys at your disposal.

1. CTRL P ( DLE ) clears the rest of the screen after the cursor. The cursor then is positioned at the beginning of the screen. Hitting DLE twice thus will clear the whole screen.

2. CR (Return) will not turn the text over to IPS, rather it positions the cursor at the beginning of the next line.

3. CTRL  $^{(RS)}$  initiates the recording of the upper half of the screen (8 lines). The 8 lower lines of the screen move into the position of the upper 8 lines, the lower 8 lines will be cleared and the cursor will be at the beginning of line 8.

Before you can do a recording you must wind the tape cassette manually until the brown oxide coated layer is visible in the center window of the cassette. ( Only with cassettes having a leader and trailer tape ). You then put the cassette into the recorder and press the "start" and the "record" button. The computer will start and stop the recorder after pressing RS. Playing back your recordings will place them on the screen again starting at the position of the cursor. Do not stop the recorder while the "block" lamp is on. If the space following the cursor is fewer than 8 lines, the rest of the block is lost.

Most IPS-versions incorporate additional editing keys.

1. DEL moves the cursor 1 line up, it thus is the opposite of LINEFEED.

2. CTRL O (SI) deletes one character under the cursor, the rest of the line moves one position left and the last character of the line becomes a blank.

3. CTRL N ( SO ) inserts a blank at the cursor. The character under the cursor and the rest of the line moves one position to the right, the last character of the line is lost.

4. CTRL R ( DC2 ) ( delete line ) replaces the rest of the line starting at the cursor by the corresponding part of the next line. The following lines move one line up, the last line is being filled by blanks.

5. CTRL Q ( DC1 ) inserts a line filled with blanks starting at the cursor; the rest of the line following the cursor and all lines below move one line down. The last line is lost.

6. CTRL X (CAN) resets the block counter to one. The block counter is incremented with each recorded block and written after RS into the last position of the screen. After count 5 it starts with 1 again. The purpose of this counter is to simplify editing large amounts of text. This concept assumes that your text material will be printed with a hard-copy device onto pages. If 5 blocks constitute one page (40 lines), block number 5 signals the last block on a page. The block counter thus enables you to keep track of the page format.

If you have completed your text editing, you may leave the edit mode again by pressing CTRL D ( EOT ). IPS once again expects IPS words starting at line 8.

Instead of manual entries, you may now also play back text recordings. Make sure the cursor is at the beginning of line 8 . Since CR is not recorded, IPS will recognize only complete blocks of 512 bytes. Entering such a block is equivalent to the CR. IPS will stop the recorder while it is processing the block. After completion it restarts the recorder. If there are further blocks, it will process them one after another.

Because the cassettes contain no inherent file identification, you must write appropriate notes on the cassettes to maintain order in your recordings; there is no automatic file search available due to the limited control the computer has over the recorder.

During program development it is a good idea to not record too many blocks on a cassette, modifications of text are much faster this way. You may overwrite individual blocks on the cassette without problems; you merely have to position the tape to the block gap before the block to be overwritten. If you listen to the recording, the block gap easily can be identified by a momentary increase in pitch. You may also record spoken comments on the cassette between blocks; the system will ignore this voice recording.

Later on it will be explained, how you may record data or complete translated programs and how you may enter them again.

#### 3.4 Process control programming

#### 3.4.1 Inputs and outputs

IPS primarily was created to allow for controlling of technical processes. For this purpose there are some fields representing the "outside world". The length of these fields depends on the hardware of your installation, particularly on the number of I/O ports.

The field OUTPUT usually will have four or more bytes. Numbers you store into these field components will appear, bit by bit, on the corresponding output lines of the output-ports.

The field INPUT (generally three or more bytes) works in the opposite direction. Signals to the input ports appear in the field INPUT and may be evaluated by reading these bytes. For example:

INPUT 2 + @B fetches the byte at input port 2 and places it on the stack.

#55 DUP OUTPUT !B OUTPUT 3 + !B stores #55 (B01010101) into output-ports 0 and 3 and thus forces the output lines to the pattern 01010101 on each port.

The approach of handling I/O ports by fields corresponds to the so-called memory mapped I/O hardware concept. Although all processors may employ this I/O philosophy, processors having special CPU I/O instructions usually lack the supporting hardware of this technique. If your processor has special I/O instructions (COSMAC or 8080), and your hardware does not support mapped I/O, IPS simulates this mode by transporting the contents of the field every 20 ms to the corresponding I/O ports and vice versa. In most applications the resulting delay may be neglected (e.g. a power relay pulls in about 40 ms). If you cannot tolerate this delay, chapter II will explain how you may design custom I/O without delay.

If your computer contains an A/D converter, there is another field for this input called A/D-CONV. The converter is assumed to convert one analog input voltage (typically 0 - 2 Volts) into a number the computer "understands". With an 8-bit converter these numbers range from 0 - 255 (one byte, #00 - #FF). The converters used by AMSAT maintain #FF with overranging and #00 with underranging. Normally there is a commutating switch (multiplexer), which scans a number of analog lines and thus their values are sequentially converted into numbers. These numbers are then placed into the field A/D-CONV. Each analog input line thus corresponds to a byte in the field and may be inspected by the program. The IPS operating system controls the multiplexer and puts the

conversion results into the field. The converters used by AMSAT convert one level every 20 ms. If there is a large number of analog voltages, say 32, every value in the field is updated every 0.64 seconds. Chapter III contains information for customisation of the A/D converter.

#### 3.4.2 Clock

To simplify programming time-dependent problems, IPS contains a clock supplying the time, day and 4 stopwatches. The field CLOCK supplies time in 6 bytes. (The operating system keeps the time).

CLOCK byte 0 contains 1/100 seconds. It is updated every 20 ms up to 98, then it is reset and there is

a carry into byte 1.

- byte 1 contains seconds (0 59)

- byte 2 contains minutes (0 59)

- byte 3 contains hours (0-23)

- byte 4 and

byte 5 contain days, continuous counting without special limit or reset (16-bit number)

You must set the clock after loading IPS, if you wish to use it. For this purpose you may enter the definition:

```

: SET 0 CLOCK ! CLOCK 2 + DUP 2 +

EACH I !B

NOW 0 CLOCK 5 + !B ;

You then may enter 15 12 24 SET and the clock is set to date 15, time

```

12:24 hours.

If your program needs to check the time for a limit, it is recommended to proceed backwards from date to hours and so on. You thus avoid problems if the time changes during your checking. The following definition checks if a certain time has been reached or exceeded. If not, it will deliver 0, else 1 onto the stack.

```

: YET SWAP CLOCK 4 + @B > ( HOURS NOT YET REACHED )

YES? DEL 0

NO: CLOCK 3 + @B > ( MINUTES NOT YET REACHED )

YES? 0

NO: 1

THEN

THEN;

```

e.g. **12 30 YET** delivers 0 before 12:30 and and 1 afterwards.

A more simple test is possible, if your time limit is available in a field. In this case you may use F-COMP to compare the clock against your limit and immediately get the result of the comparison. (During F-COMP and >>> the clock does not change).

#### 3.4.3 Stopwatches

In addition to the clock there are four stopwatches. They are fields, 4 bytes each, and are named SW0 , SW1 , SW2 and SW3 .

| SW0, 1, 2, 3 | byte 0 | contains 1/100 seconds ( 98 - 0 )    |

|--------------|--------|--------------------------------------|

|              | byte 1 | contains seconds (59 - 0)            |

|              | byte 2 | and                                  |

|              | byte 3 | contain minutes (16 bits, 32767 max) |

Byte 0 is reduced by 2 every 20 ms by the operating system. If byte 0 contains an odd number, the stopwatch is stopped. You may thus stop it momentarily by incrementing byte 0. You may later restart the watch by reducing byte 0 again by 1. If the time of the stopwatch has expired, all bytes are 0 except byte 0; it is 1. To test whether the stopwatch has expired, you only need to test byte 0. While the watch is running, this byte is even and thus will fail the YES? test.

e.g.: SW1 @B YES? ... ( WATCH EXPIRED ) NO: ... ( WATCH STILL RUNNING ) THEN

In setting the stopwatches to a particular time, byte 0 should be the last byte set; the watch will start only then. ( Or you may use >>> to set all four bytes at a time ).

e.g.: (SW2 is to run for five minutes)

5 SW2 2 + ! 0 SW2 ! (byte 0 and 1 are set together, which is OK)

If you are interested whether a stopwatch is below a certain value, you again may use F-COMP . The stopwatch is not updated while F-COMP is being executed.

# 3.5 Repeated execution and multiprogramming

# 3.5.1 The chain

So far we learned only how to execute a definition once by typing its name. Many technical problems require a continuous repetition of a program. A routine checking a machine for example, is to perform this check periodically; in case of problems it then is to perform the appropriate actions.

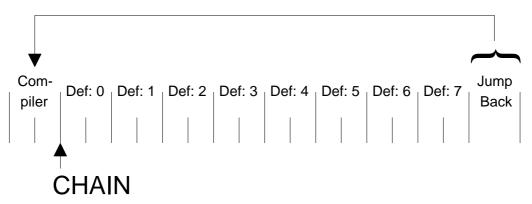

In the general situation of the computer controlling outside activities, there are usually a few more or less independent processes the computer is to look after. This multiprogramming and the repeated execution is solved with IPS by the concept of a *chain*. This is a field containing not numbers, but programs that are to be performed in sequence. IPS executes these programs one after the other, and at the end of the chain starts again at the beginning.

The chain has eight positions in which to put programs. A ninth position in front of the chain positions contains the COMPILER, the program processing keyboard and tape inputs. Position 0 contains the program displaying the stack contents; all other positions are preset with no-ops, words resulting in no action of the computer. You may add further programs to the chain which then are also periodically executed. Experience shows that even with large programs it seldom takes longer than 100 or 200 ms to run once through the complete chain. For many technical applications this is fast enough and eliminates the need of interrupts and their associated problems typical with real-time programming. To put or remove programs from the chain is very easy; it may take place by keyboard or by definitions. In particular, a definition may remove itself from the chain.

It later may be put into the chain again by another definition. With these operations the rule always holds that a definition in the chain is always executed to the end. Its removal from the chain means only that during the *next* pass through the chain the definition no longer exists in the chain.

Before you put definitions into the chain, you have to make sure that they leave the stack as they find it upon entry. A definition leaving a number on the stack will leave this number upon each pass of the chain; thus the stack will overflow or underflow resulting in a program crash. (While executing definitions in the chain, the stack is not checked.)

To put a program into the chain, you first specify the chain position (0 - 7), followed by the word ICHN and the name of the program to be put into the chain. e.g.:

| 4 ICHN TEST | puts the definition TEST into position 4 for      |

|-------------|---------------------------------------------------|

|             | periodic execution.                               |

| 4 DCHN      | removes the definition at position 4 and replaces |

|             | it by a no-op.                                    |

In particular, 0 DCHN removes the stack display from the chain. This may be useful if you have other ideas on the use of the display. To switch it on, you may type 0 ICHN STACKDISPLAY.

Of course you might have put the stack display into position 5 as well, the net result would have been the same.

If you design programs in- and de-chaining each other make sure that there are no states from which there does not exist an exit. It is a good idea to prepare a list of the use of the chain positions and the conditions under which definitions are put there and removed.

Although the chain is a simple tool to allow multiprogramming, there may exist situations where this concept is not fast enough. In chapter III another concept is presented allowing high-level interrupts ( so-called pseudo-interrupts ) to exist in parallel to the chain. Where even this is not fast enough, the assembler of chapter II will enable you to use machine interrupts. The two later techniques are slightly more complex to use, thus the chain is the preferred mode if the timing is not critical.

The following table relates the applicability and response time requirements of the three techniques.

| a. Chain:             | Up to a few 100 milliseconds until service       |  |  |  |  |

|-----------------------|--------------------------------------------------|--|--|--|--|

|                       | depending on rest of chain.                      |  |  |  |  |

| b. Pseudo-interrupt:  | Up to 18 ms until service with single user-      |  |  |  |  |

|                       | pseudo-interrupt. With more, add duration        |  |  |  |  |

|                       | of higher priority routines.                     |  |  |  |  |