# This Asynchronous World

Essays dedicated to Alex Yakovlev on the occasion of his 60th birthday

Editor:

Andrey Mokhov Newcastle University School of Electrical and Electronic Engineering Newcastle upon Tyne, NE1 7RU, UK Email: andrey.mokhov@ncl.ac.uk

Cover art by:

Ashur Rafiev Newcastle University School of Computing Science Newcastle upon Tyne, NE1 7RU, UK Email: ashur.rafiev@ncl.ac.uk

Book production:

Ghaith Tarawneh Newcastle University Institute of Neuroscience Newcastle upon Tyne, NE1 7RU, UK Email: ghaith.tarawneh@ncl.ac.uk

Publisher:

Newcastle University Newcastle upon Tyne, NE1 7RU, UK Website: www.ncl.ac.uk

ISBN: 978-0-7017-0257-1

Publication date: 20 July 2016

# Preface

The world was in a very unstable state before this Festschrift. It waited, impatiently, for a lightest touch to explode with thousands of messages flown across the globe. The messages have turned into stories, and the stories have turned into this book.

As the reader is undoubtedly aware, this book is dedicated to Alex Yakovlev on the occasion of his  $60^{th}$  birthday, but let us not confuse the occasion with the underlying cause, which is: *everybody loves Alex!* His open mind, infectious enthusiasm, and positive thinking are driving the community, and we – his students, colleagues and friends – thank him here, in writing.

It is important to note that not everyone was able to complete their writing in time to be included into the first edition of the book. But fear not: as a selfappointed editor I declare this book fully asynchronous and unbounded. Let us celebrate the variability of the contributions with respect to their completion time (which is likely to follow Alex's favourite long-tail distribution), as well as their topic and length, and welcome new contributors, who will become part of future editions of the book<sup>1</sup>.

One of the many lessons I learned from Alex is that 'when' is just as important as 'what' and 'why'. We present our stories to Alex on his  $60^{th}$  anniversary; at best, I can only half understand the magnitude of this number in my 30s, therefore let me delegate the task of arguing that "60 is not just a number" to a philosopher in our community:

Professor Alex Yakovlev.

The days of our years are threescore years and ten. Respect our forefathers, as you become one. Marvel at their wise words and institutions; the giant shoulders to our improbable but superlative technical edifice. The next 40yrs will be as exciting as the last, but you will not lead its charge. Time now to set aside personal aspiration and firm the shoulder for those who follow. As life takes you to this new and scary place, remember you are not alone in the dark.

Though ships that pass, I am very pleased to have known, shared and laughed with you o'er years beyond number. And equally pleased to count you friend and colleague.

60 is not just a number; it's the end of childhood.

#### Ian Phillips (ARM)

I would like to thank everyone who contributed to this book, sent their words of encouragement and support, and helped with the editing. And with no further ado, ladies and gentlemen, I invite you to join Alex and turn this page.

> Andrey Mokhov July 2016, Newcastle

<sup>&</sup>lt;sup>1</sup> Please contact me by email andrey.mokhov@ncl.ac.uk if you would like to contribute a paper or for any other queries.

# Table of Contents

| Resilient bundled-data design: motivation, results to date, and remaining<br>challenges                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| From an extended study of asynchronous controllers to system level design: application to the design of digital and analog interfaces 15 Edith Beigne, Pascal Vivet and Marc Renaudin |

| A community of asynchronauts: 20+ years of the ASYNC conference $\ldots \ldots 22$ $Erik\ Brunvand$                                                                                   |

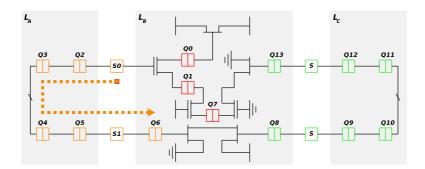

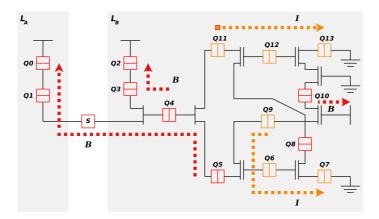

| Investigating the side-effects of synchronisers on GALS circuits 59<br>Frank Burns                                                                                                    |

| Analytical derivation of the reliability metric for digital circuits                                                                                                                  |

| From digital timing diagrams to natural language and back 82 Josep Carmona                                                                                                            |

| Are asynchronous ideas useful in FPGAs?                                                                                                                                               |

| Event splitting: the way to survive when regions fail                                                                                                                                 |

| The scientific craftsperson: beauty, engineering and the Bohemian<br>researcher                                                                                                       |

| Every accomplishment starts with the decision to try 118<br>Sohini Dasgupta and Praneet Bhatnagar                                                                                     |

| The story of the Amulet: a brief history of asynchronous events in<br>Manchester                                                                                                      |

| Partially-ordered event-triggered systems (POETS) 131<br>Steve Furber and Andrew Brown                                                                                                |

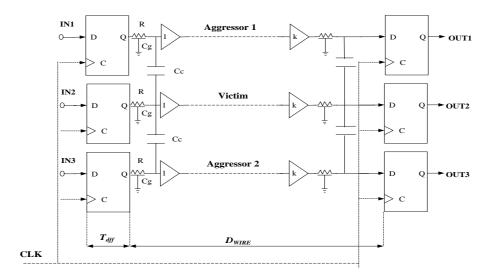

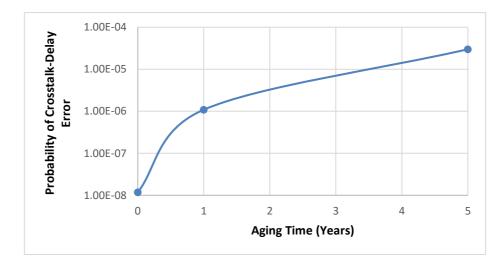

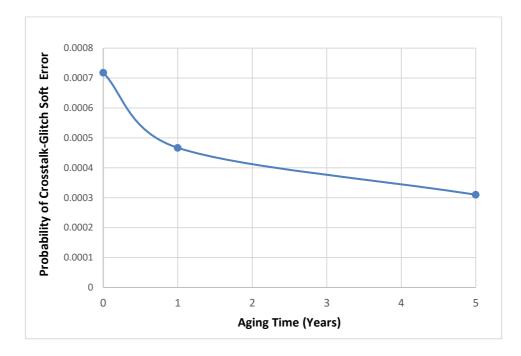

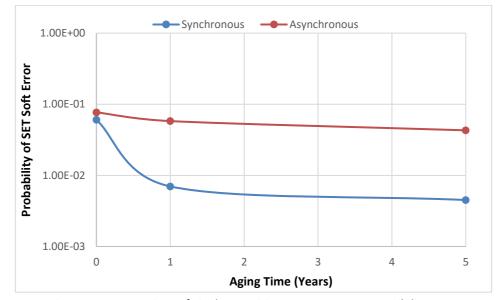

| The effects of BTI aging on the susceptibility of on-chip communication schemes to soft errors in nano-scale CMOS technologies | 150 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| Proving timing properties with the Leibnizian time model                                                                       | 166 |

| Regions of affine nets<br>Jetty Kleijn, Maciej Koutny and Marta Pietkiewicz-Koutny                                             | 182 |

| Asynchronous design methods for dark silicon chips                                                                             | 192 |

| State recovery of coarse-grained TMR circuits based on scan chains<br>and clock gating                                         | 197 |

| Where the light is coming from                                                                                                 | 202 |

| Reassessing the causes of asynchronous systems performance                                                                     | 205 |

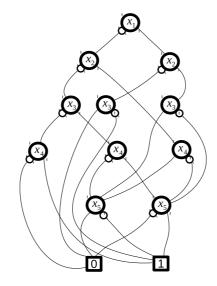

| Asynchronous BDD-like structures<br>Oleg Mayevsky, Andrey Mokhov and Danil Sokolov                                             | 208 |

| Asynchronous clocks                                                                                                            | 227 |

| Asynchronous circuit design and beyond                                                                                         | 236 |

| Beyond carrying coal to Newcastle: dual citizen circuits                                                                       | 241 |

| Significance-driven computing for big data applications: from Buttery discussions to serious research                          | 262 |

| Workcraft: ten years later                                                                                                     | 269 |

| Fifty shades of synchrony                                                                                                      | 294 |

| Can metastable states be trapped?<br>Ghaith Tarawneh                             | 301 |

|----------------------------------------------------------------------------------|-----|

| Quantitative modelling of asynchronous variables<br>Fei Xia and Ian Clark        | 305 |

| Working with Petri nets and asynchronous circuits<br>Tomohiro Yoneda             | 320 |

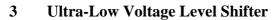

| Opportunities and challenges for ultra-low voltage digital IC design<br>Jun Zhou | 327 |

# Resilient Bundled-Data Design: Motivation, Results to Date, and Remaining Challenges<sup>\*</sup>

Peter A. Beerel<sup>1</sup> and Ney L. V. Calazans<sup>2</sup>

<sup>1</sup> University of Southern California - Los Angeles, California, USA, pabeerel@usc.edu

<sup>2</sup> Pontifícia Universidade Católica do Rio Grande do Sul - Porto Alegre, Brazil, ney.calazans@pucrs.br

Abstract. The periodic nature of the global clock in traditional synchronous designs forces circuits to be margined for the worst possible case of process, voltage, temperature, and data conditions. This constrains the silicon to operate at worst-case frequencies and at conservative supply voltages. Resilient architectures promise to remove these margins, by detecting and correcting timing errors when they occur, thereby creating the potential to achieve real average-case operation. However, synchronous resilient schemes previously proposed can suffer from multiple issues, including being susceptible to metastability and requiring often complex changes to the architecture to support replay-based recovery from timing errors. These problems respectively lead to circuit failures and/or incur high timing penalties when errors occur. This paper reviews a recently proposed resilient bundled-data template called Blade that is robust to metastability issues, requires no replay-based logic, and has low timing error penalties. It also describes some open issues and new research opportunities this template presents, including automation problems to target average-case operation, specific circuit optimizations to minimize resiliency overhead, and the need for new test procedures to tune delay lines and screen out bad chips.

# 1 Introduction and Related Work

Traditional synchronous designs must incorporate timing guardbands to ensure correct operation under worst-case delays caused by process, voltage, and temperature (PVT) variations as well as data-dependency [6]. This is particularly important in low-power low-voltage designs, as performance uncertainty due to PVT variations grows from around 50% at nominal supply to around 2,000% in the near-threshold domain [14]. To address this problem, many synchronous design techniques for resilient circuits have been proposed that address delay variations. For example, canary FFs predict when the design is close to a setup timing failure (see e.g., [41]). Designs can then adjust their supply voltage or clock frequency either statically or dynamically to ensure correct operation at

$<sup>^{\</sup>star}$  This is an extended and updated version of an ECCTD 2015 invited paper on the same topic.

#### 2 Peter Beerel and Ney Calazans

the edge of failure. The adverse impact of variations on hold margins are significantly more challenging to manage because changing the clock frequency and voltage does not typically resolve hold problems and thus these must be very conservatively managed. Hold constraints are typically resolved by preemptively adding hold buffers to all "short" paths in the design. Unfortunately, at low voltages, the number of hold buffers needed can be much larger than at nominal voltages, because the increased delay variation causes: (1) clock uncertainty to grow; (2) a larger fraction of paths to be identified as potentially short, due to the possible decrease in delays resulting from variability; and (3) the hold buffers themselves possibly being unexpectedly fast. All these margins translate into considerable increases in energy consumption.

Several research groups have explored adding a degree of *timing resiliency* into the design to detect and then recover from setup violations [9, 12, 25, 27]. There are two general approaches: architecturally dependent, or "replay-based" approaches, and architecturally independent. The former includes Razor II [12] and the Intel approach described in [6]. The problem with these approaches is that they work much like pulsed latch circuits: the wider the pulse, the more resiliency is obtained, at the cost of worsening hold time margins [15]. Moreover they require synchronizers in the control path, incurring long delays to identify whether an error occurred, and demand complex replay and recovery mechanisms [6, 12, 27]. Granted, the area overhead of these can be amortized by reusing existing recovery logic (e.g., for resuming after a mispredicted branch), but the techniques remain architecturally invasive and thus a design challenge. In contrast, architecturally independent approaches like Bubble Razor [15] and TIMBER [9] require no architectural changes and can be automatically generated from standard RTL specifications. The flow involves replacing flip-flops with retimed latches that have non-overlapping clocks, mitigating hold time problems. Bubble Razor, for example, avoids replay and recovery by immediately stalling neighboring stages via clock gating, and solves timing errors on the fly and locally. However, the template assumes that metastability can be resolved within one clock period, which is often unrealistic and leads to poor mean-time-betweenfailures rates [3]. More recent work [25] proposes to borrow time only from the following stage by quickly boosting its supply voltage to accommodate for the borrowed time. Unfortunately, this approach requires fast error detection and dynamically adjustable supply voltages which limits its applicability.

Different asynchronous templates have also been proposed to address the excessive margining problem (e.g., [42]). Quasi-delay-insensitive (QDI) templates use completion signal logic which makes them robust to delay variations at the cost of increased area (often 4x larger than synchronous counterparts or even more) and high switching activity due to a return to zero paradigm (e.g., [16, 38]). Bundled-data templates (e.g., micropipelines [39]) use delay lines matched to single-rail combinational logic, providing a low area, low switching activity asynchronous solution (e.g., [10]). However, the delay lines must be implemented with sufficiently large margins in the presence of on-chip variations [11], reducing the advantages of this approach. Researchers have proposed different solutions to mitigate these margins, such as duplicating the bundled-data delay lines [8],

constraining the design to regular structures such as PLAs [24] and using soft latches [28]. Others have suggested current-based completion sensing techniques (e.g., [1, 29]) that rely on analog current sensors, which can be prohibitively power hungry.

This work focuses on a recently proposed asynchronous design template that couples the architectural benefits of resilient techniques with the flexibility of asynchronous bundled-data pipelines. The template, called Blade, minimizes hold time issues, requires no replay-based logic, and is supported by an automatic translation flow from synchronous RTL specifications. It is not only safe from metastability issues but also takes advantage of the low *average* metastability resolution times, which leads to low timing error penalties compared to synchronous alternatives. It thus provides significantly higher potential performance and voltage scaling power benefits.

The paper reviews Blade principles and operation, comparing and contrasting the approach to synchronous alternatives. Its recent application to the design of a MIPS OpenCore processor illustrates techniques to reduce overheads and maximize performance and power benefits. The paper also discusses the range of designs for which this design style is likely to provide the biggest overall benefit, as well as some of the open problems that must be solved to maximize the opportunity to use Blade and make the method commercially attractive.

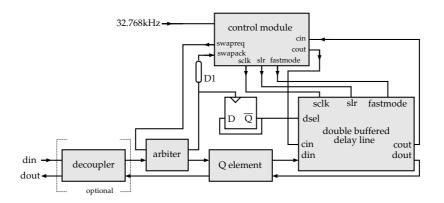

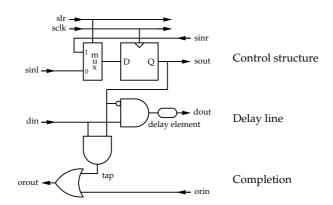

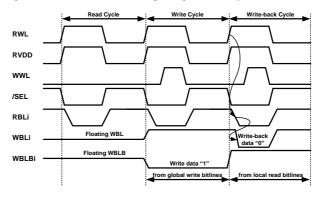

# 2 The Blade Bundled-Data Architecture

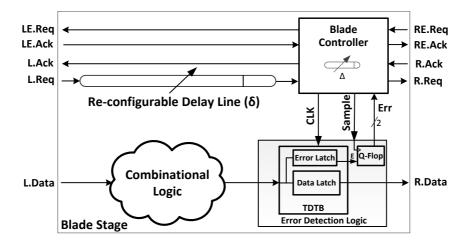

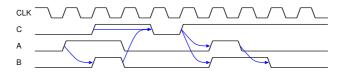

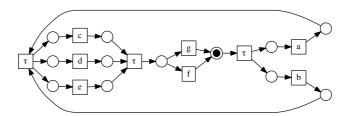

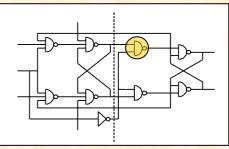

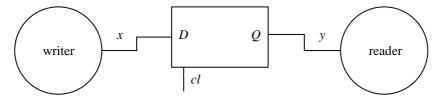

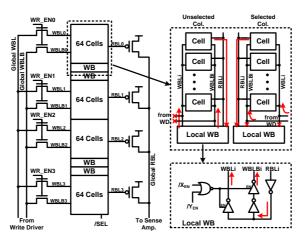

As Figure 1 shows, pipeline stages in Blade use single-rail logic followed by Transition Detector with Time Borrowing (TDTB) error detecting latches (EDLs) [6,32], Q-Flops [35], and two reconfigurable delay lines. The stage-to-stage delay line is of duration  $\delta$  and controls when the TDTB goes transparent and begins to propagate data at the output of the combinational logic to the next stage. According to the timing diagram depicted in Figure 2, the asynchronous controller speculatively assumes data at the output of the TDTB latch is stable and triggers the request to the next stage via the standard bundled data request channel consisting of *R.req* and *R.ack*. The second delay line is of duration  $\Delta$  and defines a time window during which late transitions that violate this assumption (i.e. timing errors) are allowed, which is called the *timing resiliency window* (TRW). While  $\Delta$  is elapsing, CLK is high (i.e. the Data Latch is transparent).

Error detecting latches are responsible for triggering an error if a timing violation occurs during the TRW. While there are several EDL implementations (e.g., [6,9,15,32]), Blade employs a custom design [32] based on TDTB latches [6]. The basic design requirement is this component triggers an error on its E output in response to any transition or glitch during the TRW that is significant enough to also propagate to its data output [32]. In this way, no timing violation is missed.

In addition to the push data channel L, Blade uses a second pull *error channel* formed by signals RE.req and RE.ack to manage potential timing violations. Near the end of the TRW, after receiving a request on the RE.req signal, the controller will trigger a signal that directs the Q-Flop to sample the E signal,

Fig. 1. The Blade architecture typical stage structure.

determining whether or not a timing error occurred during the TRW. If an error did not occur RE.ack is immediately asserted, else  $\Delta$  is triggered and only after that RE.ack is asserted. Because the setup time of the TDTB Error Latch may be violated, the E signal may be metastable during sampling. To cope with this, the Q-Flop has a built-in metastability filter that guarantees metastability does not propagate to its Err output. In fact, this output is intentionally made a dual-rail signal that only becomes valid after the Q-Flop has safely determined if an error occurred or not. The controller simply waits for this to happen before acknowledging the error channel request via the RE.ack signal. This ensures that metastability, while possibly causing an instantaneous cycle slowdown, does not propagate to the main control path. This is in stark contrast to synchronous schemes, which must wait for a fixed, larger metastability resolution time set to guarantee a sufficiently large mean time between failures (MTBF).

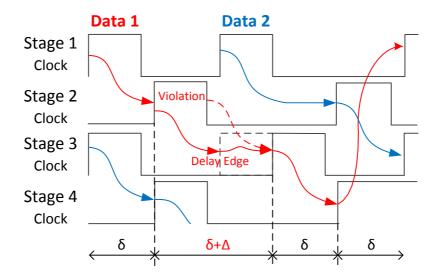

There are two main delay lines that affect the performance of Blade,  $\delta$  and  $\Delta$ . Compared to a traditional synchronous circuit, with clock period C, we set  $C = \delta + \Delta$ . The TRW (defined by  $\Delta$ ) must be large enough to capture even the worst-case datapath delay. However, a trade off in setting these values emerges, as increasing  $\Delta$  allows  $\delta$  to be smaller and the system to operate faster if no timing violations (errors) occur; on the other hand, the shorter stage-to-stage delay means that more transitions will occur while the latch is transparent, thereby increasing the frequency of errors that force subsequent pipeline stages to be delayed by the now larger  $\Delta$  value. The optimal  $\Delta$  depends greatly upon the amount of total variation (due to data and PVT variations) that can be expected in the design, and can range from 20% to over 60% [18] of the stage total delay. This is in contrast to Bubble Razor whose optimal error rate is less than 5% percent [15] and synchronous replay-based Razor schemes whose optimal error rate is less than 1% [7].

When  $\Delta$  is sufficiently smaller than  $\delta$ , the next stage has time to check whether the previous stage has an error before it makes its own latch transpar-

Fig. 2. Typical timing diagram for the Blade template.

ent, delaying the transparency phase if the previous stage had an error. Stage clocks will thus remain non-overlapping, as illustrated in Figure 2, making it easy to satisfy hold times. This is again in contrast to most synchronous resiliency schemes that make meeting hold time margins harder. Supporting larger values of  $\Delta$  (w.r.t.  $\delta$ ) is also possible and is beneficial when data/process yield high variability. However, the result is that the transparency phases of neighboring stages clocks will overlap, and this may cause hold time issues similar to those seen in synchronous approaches (see [15] for an encompassing analysis). Managing these hold time issues in synchronous resiliency approaches is particularly challenging, as they cannot be fixed by slowing down the clock. Accordingly, hold times need to margined to a higher degree than setup times. As mentioned earlier, these hold margins are typically satisfied by adding hold buffers to the datapath, but the higher margins may make the number of added buffers impractically large for designs with high variability. In contrast, an asynchronous solution like Blade can easily add an additional programmable delay line to the backward control path, actively managing the degree of transparency overlap, which makes such extra margins unnecessary. In both cases the flexibility of the asynchronous solution makes managing hold time issues far more practical.

Lastly, note that Blade also uses programmable delay lines, because under significant PVT variations it may be difficult to achieve the optimal TRW, which captures the delay of all worst-case paths via static design analysis and optimization. Programmable delay lines allow customizing the actual delay post-silicon. In particular, the authors expect that during chip characterization delay lines are analyzed and optimally configured for every chip produced, subject to some quantization error. In particular, quantization errors in  $\delta$  may lead to a nonoptimal expected error rate, but the overall performance will remain close to

#### 6 Peter Beerel and Ney Calazans

optimal [18]. Any additional margin needed to account for worst-case paths under PVT variations can be added only to the  $\Delta$  delay line. Given the average frequency of timing violations can be in the range of 20%-40%, the impact of the added margin is only experienced 20-40% of the time, greatly reducing the percentage drop in performance. This is in contrast to non-resilient bundled-data designs (e.g., [10]) in which the added margin affects performance 100% of the time. As an example, a 10% increase in variation due to PVT can result in up to 30% margin penalty in synchronous designs; however, even considering a 40% rate of timing violations, the computed performance impact on Blade is less than 13% [19].

# 3 Preliminary CAD Flow

The authors' teams developed a preliminary flow to automatically convert single CLK domain, synchronous RTL designs to the Blade template using industry standard synthesis tools. The flow consists of various Tcl and shell scripts that drive the tools and a library of custom cells (e.g., the TDTB error latch), needed to make the template efficient.

In addition, to further reduce area and power overheads of the error detection logic, two microarchitectural optimizations are used. First, not every pipeline stage need be error-detecting, and non error-detecting stages can time borrow. Time-borrowing stages permit data to pass through the latch during the entire time it is transparent without flagging violations. The authors found that alternating between error-detecting and time-borrowing stages can work well as this effectively halves the overhead of error detection logic while still providing sufficient resiliency. Secondly, only latches that terminate near-critical paths [19] need to be error detecting, further reducing the number of EDLs in the entire design.

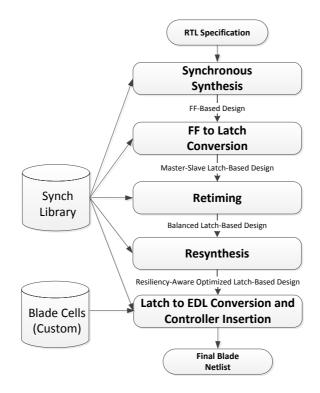

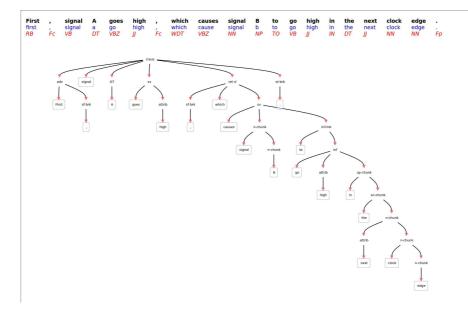

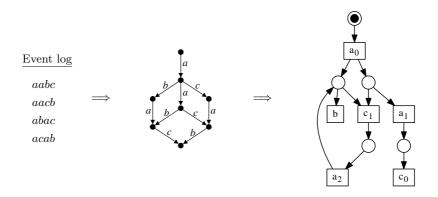

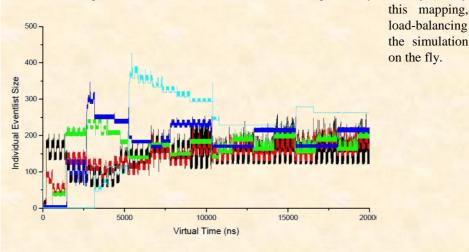

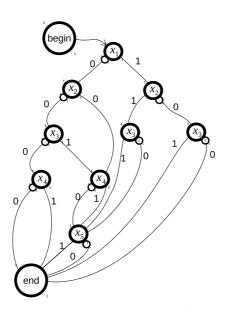

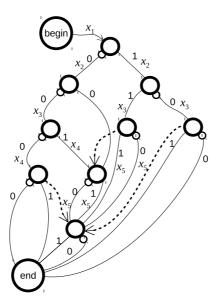

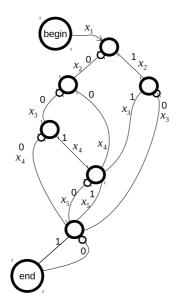

As Figure 3 illustrates, the flow has five main steps:

- 1) Synchronous Synthesis: The synchronous RTL is synthesized to a flip-flop (FF-based) design for given clock.

- 2) FF to Latch Conversion: FFs are converted to master-slave latches by synthesizing the design using a fake library of standardized D flip-flops (DFFs) that can be easily mapped to standard cell latches.

- 3) Latch Retiming: The latch-based netlist is retimed using a target TRW, where the combined path delay constraint of any two stages equals the given clock period. The purpose is to split the critical path in two parts, which enables hiding inter-stage Blade handshaking overheads.

- 4) Resynthesis: The retimed netlist is then resynthesized to reduce the number of TDTBs and increase performance of the final resilient netlist. In particular, re-synthesizing the logic happens such that the delay to a subset of latches is sufficiently fast to guarantee that data is stable before the latches go transparent (i.e., is not near-critical). This means that the latches do not need to be error-detecting, reducing the EDL overhead, and potentially reduces the error rate at the expense of increasing the datapath logic area.

#### Resilient Bundled-Data Design 7

Fig. 3. The Blade design flow.

Targeting latches that cause the most errors in typical applications can lead to significant reductions in error rates with marginal increase in area. In [19] the authors employ a simple brute-force search, but more powerful means of identifying which subset of latches to speed up is an interesting area of future work.

5) Blade Conversion: The resynthesized latch-based netlist is then converted to the Blade template, by removing clock trees and replacing these with Blade controllers. The control logic, delay lines, and error detection logic are also inserted to create a final Blade netlist. There are many ways to implement the control logic [5]; using burst-mode specifications was explored in [19].

The authors' preliminary pre-P&R flow was tested and evaluated on a 3-stage version of Plasma [33], a MIPS OpenCore CPU, targeting a 28nm FD-SOI technology. The gate-level Blade design was compared to the equivalent synchronous design, and post-synthesis results demonstrate that for an area overhead of 8.4%, the Blade version of Plasma achieves a 19% average performance boost with a timing resiliency window of 30%. Out of the 8.4% area overhead, 32% is due to the use of EDLs and to the FF to latch conversion. With the removal of synchronous PVT margins, it led to an estimated 30%-40% improvement in performance [19].

#### 8 Peter Beerel and Ney Calazans

## 4 Recent Developments and Open Research Problems

The technology is being commercialized by Reduced Energy Microsystems [34], a semi-conductor start-up company co-founded by William Koven, Dylan Hand, and Eleazar Vega-Gonzalez. They recently designed and fabricated a Blade-based design for light-weight encryption cyphers [20] and have plans on using Blade to build energy-efficient processors for the Internet of Things market. The success of the commercialization of Blade, however, will likely require solving several research challenges which we outline here.

#### 4.1 Scope and Scale of Design

REM's recent work involved extending the flow illustrated in Figure 3 to start from a synthesizable-subset of SystemVerilogCSP [36] and include back-end place-and-route. In particular, they leveraged the USC-developed tool CSP2RTL to automatically decompose CSP designs into blocks of synthesized unconditional logic surrounded by efficient SEND/RECEIVE primitives. This tool allows asynchronous designers to couple the benefits of hierarchical decomposition and conditional communication with resilient pipelined designs and is based on a similar framework used for industrial-scale QDI designs [4].

Interestingly, the work in [20] represents just the beginning of what is possible when the scope of synthesizable CSP specifications is expanded. For example, we envision supporting arbitration in CSP where the CSP2RTL tool would automatically insert arbitrated merge blocks to enable the automatic design of complex routers and NoC designs. Moreover, we believe we can support mixed-timing interfaces in SystemVerilogCSP for which the tool will automatically insert clock-domain-crossing circuits. This will enable seamless integration of resilient bundled-data blocks within otherwise synchronous designs.

# 4.2 Area and Energy Efficiency

A CSP-based resilient design flow can support energy-efficient hardware design for a large variety of applications, but the added complexity associated with hierarchical design and conditional communication must be managed. In particular, over-decomposition can lead to increased overheads in terms of extra pipeline stages, excess error-detecting logic, and more delay lines and control logic. To properly navigate this increased design space, high-level energy and power estimation tools that guide decomposition will be important. In addition, the use of slack-less controllers such as in [20] can often provide much of the benefits of conditionality without the area overhead of a distinct pipeline stage. This design exploration should be guided by a notion of average-performance and average-energy consumption that considers the probabilities implicit in the conditional communication and the probabilities associated with error-rates at each error-detecting pipeline stage. In particular, understanding the implication of clustering latches into pipeline stages will likely be critical for a comprehensive flow that can accommodate industry-scale applications. Too few pipeline stages and the design would loose the benefits of average-case data whereas too many pipeline stages would lead to too high overhead. Finding the right balance is likely design and use-case specific and will demand new tools to guide the design.

Even for simple RTL-based resilient bundled-data designs, numerous advances in area and power efficiency will likely be essential to the success of the technology. In particular, the design of the delay line and error-detecting logic is critical to efficiency. We expect one of the significant advantages of this design style is its ability to naturally support dynamic voltage scaling [21, 40]. Unlike a synchronous design in which adjusting voltages often requires stalling the pipeline for many clock cycles while the clock source is reconfigured, bundleddata circuits can be designed to automatically adapt to voltage scaling. If the delay line tracks the delay of the combinational logic, it need not be re-programmed when the supply voltage is changed. To support this strategy, we recently proposed a framework for delay line design [40] in which we minimize average energy subject to two-sided voltage scaling constraints. In fact, we anticipate we will need to build a library of delay elements and a CAD tool that chooses which delay elements to use based on an analysis of the likely critical path of a pipeline stage and its voltage scaling properties.

Minimizing the cost of error-detecting logic latches is also important. There are two distinct approaches to this problem. The first approach is re-synthesis in which new constraints are added to the logic synthesis / physical design to make certain latches non-critical, thereby saving the overhead of making them errordetecting. In [23], we developed a geometric programming based mathematical algorithm that guides re-synthesis to minimize the total area of the design. We have found that this often reduces error rates, but explicitly modeling and considering average-case performance is interesting future work. Moreover, we are exploring resilient-aware, latch-based retiming. Recall that the Blade CAD flow described above involves replacing FFs with a pair of latches and retiming of the slave latches to create a balanced latch based design. This balance aids in hiding the performance overhead of the asynchronous control and mitigating hold-time problems. Commercial tools support retiming of sequential elements, including latches, but the results are often sub-optimal for resilient designs as their retiming algorithm does not understand the inherent trade-off associated with near-critical paths and the error-detecting/non-error-detecting latch at which the path ends. The second approach is to design efficient multi-bit error-detecting latches. Amortizing the cost of memorizing whether an error occurs can lead to significant benefits in terms of area and power [22].

While most of the circuit design research has focused on super and nearthreshold design, another important domain for Blade designs may be subthreshold operation, particularly for the sub-set of the market in which performance is not important. Sub-threshold design, however, introduces new challenges in guaranteeing reasonable static noise margins and minimizing leakage currents. Fortunately, techniques to achieve efficient sub-threshold designs for synchronous circuits are well-known [2]. Using these techniques to design efficient efficient asynchronous control circuits, delay lines, and error-detecting

#### 10 Peter Beerel and Ney Calazans

latches for the sub-threshold operation is an interesting and important area of research.

Finally, numerous researchers have developed bundled-data design flows using commercially-supported physical design tools [11, 16, 17] and REM has developed a prototype flow for Blade circuits [20]. To extend these to complex Blade designs, however, a few more enhancements will be necessary. First, new standard-cells must be designed, including efficient error-detecting latches and mutual exclusion elements. In addition, supporting the non-standard timing constraints and trade-offs associated with the introduction of programmable delay lines in complex Blade designs is novel and challenging. A naïve implementation can lead to a quadratic explosion of delay lines between interacting Blade stages. Instead, an intelligent sharing of delay lines is needed to guarantee using only a linear number of delay lines and this sharing should be guided by a variety of factors.

#### 4.3 Design for Test, Debug, and Manufacturability

Traditional synchronous testing methodologies are based on an implicit assumption of statically controlled voltages and clocks and that the associated control logic is minimal (an on-chip PLL and off-chip voltage regulator). Traditional test methodologies have thus focused on the max-delay constraints in the core digital logic and relied on functional tests to cover the control logic. However, bundleddata resilient designs are more complex as they have programmable delay lines in every pipeline stage and have error-detecting logic that indicates when setup failures occur. One recent study explored the testability of the Blade template and found while many faults were implicitly testable by the error-detecting logic, other faults led to excessive errors or disabled the error-detecting capability of the circuit [26]. The complex nature of testing these circuits warrants the study of a holistic test methodology that encompasses new resiliency-aware fault models, test coverage, test generation, and design for test. This will include test methods for optimally tuning the programmable delay lines based perhaps on *in* situ error rate monitoring, as well as means to identify and discard chips with delay variations too large to correct.

## 5 Discussion and Conclusions

Asynchronous design has become an increasingly attractive alternative to synchronous design in several applications for a variety of reasons. For example, Intel showed that high-performance quasi-delay-insensitive (QDI) design is sufficiently robust and effective for high performance networking chips [13]. Moreover, the challenges of managing a global clock in large neuromorphic chips, have driven IBM [31] and Stanford [30] to adopt an asynchronous mostly QDI interconnect. Other academic researchers have found that built-in flow-control in bundleddata network-on-chips lead to significant benefits in terms of latency and area compared to synchronous counterparts [16]. However, efforts to commercialize bundled-data pipelines for processors demonstrated only marginal performance benefits [10]. We hope that adding resiliency opens the door for much larger performance advantages to a broader range of applications.

Generally speaking, the range of architectures and applications for which resiliency adds value depends on two factors: the overhead one can expect from the error-detecting latches and the variance of the data and PVT dependent delays [37]. The benefits of a resilient design are higher when the fraction of combinational to sequential area is large, because the relative overheads of the TDTBs is smaller. Thus, resilient design favors less pipelined designs. Moreover, an architecture where the difference between average and worst-case delay is large will likely benefit more than a well balanced architecture and even more likely if the worst-case paths are rarely executed [37]. For example, architectures that involve complex logic with rarely executed long carry chains will benefit more than balanced designs consisting of many regular structures (e.g., memories). Fortunately, there are many architectural decisions that can be made to favor timing resilient templates [37].

Lastly, it is important to emphasize that the advantages of asynchronous resilient designs are difficult to approximate in synchronous architectures. In particular, asynchronous resilient designs adapt to the quite low average-case time it takes for metastability to resolve, which in principle can be unbounded. In contrast, the periodic nature of the clock forces synchronous alternatives to be designed for a much larger fixed resolution time, set by an acceptable MTBF. This difference enables our solution to be architecturally-independent, whereas existing robust synchronous solutions are forced to be based on recover and replay logic to obtain reasonable MTBF.

Thus, we believe asynchronous resiliency is a promising research direction to obtain efficient designs which adapt to the combination of PVT and data variations and naturally supports voltage scaling. We believe that a good initial market for this technology is the Internet of Things market, but the higher energy efficiency may very well be attractive to more general computing domains.

# References

- Akgun, O., Leblebici, Y., Vittoz, E.: Current Sensing Completion Detection for Subthreshold Asynchronous Circuits. In: European Conference on Circuit Theory and Design (ECCTD). pp. 376–379 (Aug 2007)

- Alioto, M.: Ultra-low power VLSI circuit design demystified and explained: A tutorial. IEEE Transactions on Circuits and Systems - I: Regular Papers 59(1), 3–29 (Jan 2012)

- Beer, S., Cannizzaro, M., Cortadella, J., Ginosar, R., Lavagno, L.: Metastability in Better-Than-Worst-Case Designs. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). pp. 101–102 (Apr 2014), (Fresh Ideas Workshop)

- Beerel, P.A., Dimou, G.D., Lines, A.M.: Proteus: An ASIC flow for GHz asynchronous designs. IEEE Design & Test of Computers 28(5), 36–51 (2011)

- 5. Beerel, P., Ozdag, R., Ferreti, M.: A Designer's Guide to Asynchronous VLSI. Cambridge University Press (2010)

#### 12 Peter Beerel and Ney Calazans

- Bowman, K., Tschanz, J., Kim, N., Lee, J., Wilkerson, C., Lu, S., Karnik, T., De, V.: Energy-Efficient and Metastability-Immune Resilient Circuits for Dynamic Variation Tolerance. IEEE Journal of Solid State Circuits 44(1), 49–63 (Jan 2009)

- Bowman, K., Tschanz, J., Lu, S., Aseron, P., Khellah, M., Raychowdhury, A., Geuskens, B., Tokunaga, C., Wilkerson, C., Karnik, T., De, V.: A 45 nm resilient microprocessor core for dynamic variation tolerance. IEEE JSSC 46(1), 194–208 (Jan 2011)

- Chang, I.J., Park, S.P., Roy, K.: Exploring Asynchronous Design Techniques for Process-Tolerant and Energy-Efficient Subthreshold Operation. IEEE Journal of Solid State Circuits 45(2), 401–410 (Feb 2010)

- Choudhury, M., Chandra, V., Aitken, R., Mohanram, K.: Time-Borrowing Circuit Designs and Hardware Prototyping for Timing Error Resilience. IEEE Transactions on Computers 63(2), 497–509 (Feb 2014)

- Cortadella, J., Kondratyev, A., Lavagno, L., Sotiriou, C.: Desynchronization: Synthesis of Asynchronous Circuits From Synchronous Specifications. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 25(10), 1904–1921 (Oct 2006)

- Cortadella, J., Lupon, M., Moreno, A., Roca, A., Sapatnekar, S.: Ring Oscillator Clocks and Margins. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). pp. 19–26 (May 2016)

- Das, S., Tokunaga, C., Pant, S., Wei-Hsiang, M., Kalaiselvan, S., Lai, K., Bull, D., Blaauw, D.: Razor II: In Situ Error Detection and Correction for PVT and SER Tolerance. IEEE Journal of Solid State Circuits 44(1), 32–48 (Jan 2009)

- Davies, M., Lines, A., Dama, J., Gravel, A., Southworth, R., Dimou, G., Beerel, P.: A 72-Port 10G Ethernet Switch/Router using Quasi-Delay-Insensitive Asynchronous Design. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). pp. 103–104 (May 2014), (Industrial Track)

- Dreslinski, R., Wieckowski, M., Blaauw, D., Sylvester, D., Mudge, T.: Near-Threshold Computing: Reclaiming Moore's Law Through Energy Efficient Integrated Circuits. Proceedings of the IEEE 98(2), 253–266 (Feb 2010)

- Fojtik, M., Fick, D., Kim, Y., Pinckney, N., Harris, D., Blaauw, D., Sylvester, D.: Bubble Razor: Eliminating Timing Margins in an ARM Cortex-M3 Processor in 45 nm CMOS Using Architecturally Independent Error Detection and Correction. IEEE Journal of Solid State Circuits 48(1), 66–81 (Jan 2013)

- Ghiribaldi, A., Bertozzi, D., Nowick, S.: A Transition-signaling Bundled Data NoC Switch Architecture for Cost-effective GALS Multicore Systems. In: Design & Test in Europe (DATE). pp. 332–337 (Mar 2013)

- Gibiluka, M., Moreira, M.T., Calazans, N.L.V.: A Bundled-Data Asynchronous Circuit Synthesis Flow Using a Commercial EDA Framework. In: Euromicro Conference on Digital System Design (DSD). pp. 79–86 (2015)

- Hand, D., Huang, H., Cheng, B., Zhang, Y., Moreira, M.T., Breuer, M., Calazans, N.L.V., Beerel, P.A.: Performance Optimization and Analysis of Blade Designs under Delay Variability. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). pp. 61–68 (May 2015)

- Hand, D., Moreira, M., Huang, H., Chen, D., Butzke, F., Li, Z., Gibiluka, M., M., B., Calazans, N.L.V., Beerel, P.A.: Blade - A Timing Violation Resilient Asynchronous Template. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). pp. 21–28 (May 2015)

- Hand, D., Katzin, A., Koven, W.: Adding Conditionality to Resilient Bundled-Data Designs. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC) (May 2016), (Industrial Track)

- Heck, G., Heck, L.S., Singhvi, A., Moreira, M.T., Beerel, P.A., Calazans, N.L.V.: Analysis and Optimization of Programmable Delay Elements for 2-Phase Bundled-Data Circuits. In: International Conference on VLSI Design (VLSI). pp. 321–326 (Jan 2015)

- 22. Hua, W., Tadros, R., Beerel, P.: Low area, low power, robust, highly sensitive error detecting latch for resilient architectures. In: International Symposium on Low Power Electronics and Design (ISLPED) (Aug 2016)

- Huang, H.H.H., Cheng, H., Chu, C.C., Beerel, P.A.: Area optimization of resilient designs guided by a mixed integer geometric program. In: Design Automation Conference (DAC) (Jun 2016)

- Jayakuma, N., Garg, R., Gamache, B., Khatri, S.: A PLA based Asynchronous Micropipelining Approach for Subthreshold Circuit Design. In: Design Automation Conference (DAC). pp. 419–424 (Jun 2006)

- 25. Kim, S., Seok, M.: Variation-Tolerant, Ultra-Low-Voltage μP With a Low-Overhead, Within-a-Cycle In-Situ Timing-Error Detection and Correction Technique. IEEE Journal of Solid State Circuits 50(6), 1478–1490 (Jun 2015)

- Kuentzer, F., Amory, A.: Fault classification of the error detection logic in the blade resilient templates. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). pp. 37–42 (May 2016)

- 27. Kulkarni, J.P., Tokunaga, C., Aseron, P.A., Nguyen, T., Augustine, C., Tschanz, J.W., De, V.: A 409 GOPS/W Adaptive and Resilient Domino Register File in 22 nm Tri-Gate CMOS Featuring In-Situ Timing Margin and Error Detection for Tolerance to Within-Die Variation, Voltage Droop, Temperature and Aging. IEEE Journal of Solid State Circuits 51(1), 117–129 (Jan 2016)

- Liu, J., Nowick, S., Seok, M.: Soft MOUSETRAP: A Bundled-Data Asynchronous Pipeline Scheme Tolerant to Random Variations at Ultra-Low Supply Voltages. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). pp. 1–7 (May 2013)

- Liu, T.T., Alarcon, L., Pierson, M., Rabaey, J.: Asynchronous Computing in Sense Amplifier-Based Pass Transistor Logic. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC). pp. 105–115 (Apr 2008)

- Merolla, P., Arthur, J., Alvarez, R., Bussat, J.M., Boahen, K.: A Multicast Tree Router for Multichip Neuromorphic Systems. IEEE Transactions on Circuits and Systems - I: Regular Papers 61(3), 820–833 (Mar 2014)

- Merolla, P., et al.: A Million Spiking-neuron Integrated Circuit with a Scalable Communication Network and Interface. Science 345(6197), 668–673 (2014)

- 32. Moreira, M.T., Hand, D., Calazans, N.L.V., Beerel, P.A.: TDTB Error Detecting Latches: Timing Violation Sensitivity Analysis and Optimization. In: International Symposium on Quality Electronic Design (ISQED). pp. 379–383 (Mar 2015)

- 33. Plasma CPU, 2014. Available: http://opencores.org/project,plasma

- 34. Reduced Energy Microsystems. http://www.remicro.com, Accessed: March, 2016

- Rosenberger, F., Molnar, C., Chaney, T., Fang, T.P.: Q-modules: Internally Clocked Delay-insensitive Modules. IEEE Transactions on Computers 37(9), 1005– 1018 (Sep 1988)

- Saifhashemi, A., Beerel, P.A.: SystemVerilogCSP: Modeling digital asynchronous circuits using systemverilog interfaces. In: Proceedings of Communicating Process Architectures - WoTUG-33 (Jun 2011)

- Sartori, J., Kumar, R.: Exploiting Timing Error Resilience in Processor Architecture. ACM Transactions on Embedded Computing Systems 12(2), 89:1–89:25 (May 2013)

#### 14 Peter Beerel and Ney Calazans

- Stevens, K.S., Gebhardt, D., You, J., Xu, Y., Vij, V., Das, S., Desai, K.: The Future of Formal Methods and GALS Design. Electronic Notes in Theoretical Computer Science 245(0), 115–134 (2009)

- Sutherland, I.E.: Micropipelines. Communications of the ACM 32(6), 720–738 (Jun 1989)

- 40. Tadros, R., Hua, W., Gibiluka, M., Moreira, M.T., Calazans, N.L.V., Beerel, P.A.: Analysis and design of delay lines for dynamic voltage scaling applications. In: IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC) (May 2016)

- Tschanz, J., Bowman, K., Walstra, S., Agostinelli, M., Karnik, T., De, V.: Tunable Replica Circuits and Adaptive Voltage-Frequency Techniques for Dynamic Voltage, Temperature, and Aging Variation Tolerance. In: Symposium on VLSI Circuits. pp. 112–113 (2009)

- 42. Yakovlev, A., Vivet, P., Renaudin, M.: Advances in Asynchronous Logic: From Principles to GALS & NoC, Recent Industry Applications, and Commercial CAD Tools. In: Design & Test in Europe (DATE). pp. 1715–1724 (Mar 2013)

# From an extended study of asynchronous controllers to system level design: application to the design of digital and analog interfaces

E. Beigne\*, P. Vivet\* and M. Renaudin\*\*

\* CEA LETI, Minatec Campus, 38054 Grenoble, France \*\* Tiempo, 38330 Montbonnnot, France Grenoble, France edith.beigne@cea.fr, pascal.vivet@cea.fr, marc.renaudin@tiempo-ic.com

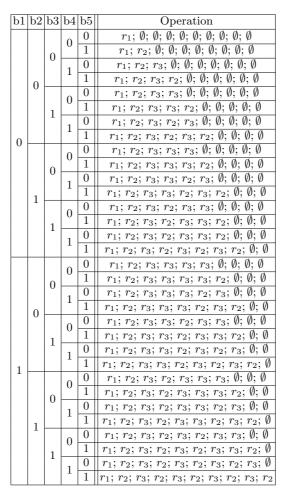

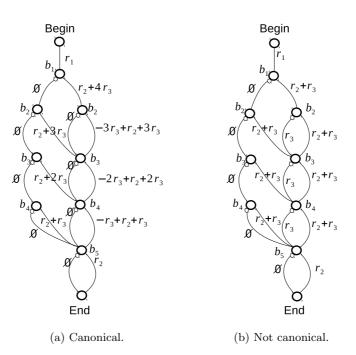

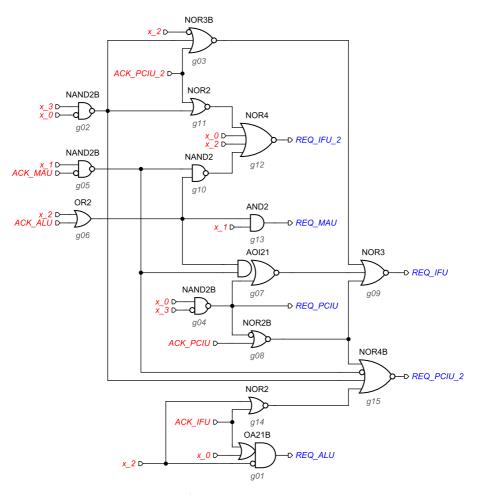

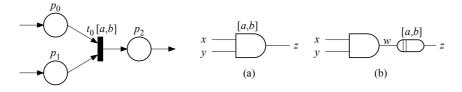

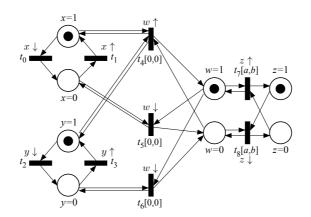

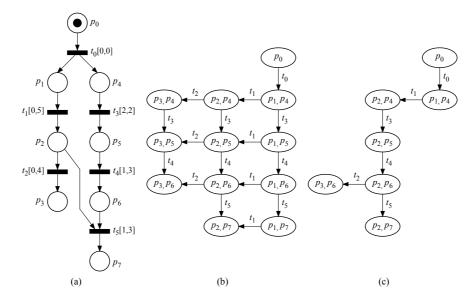

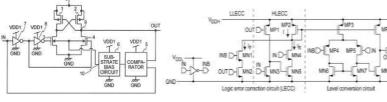

**Abstract.** Asynchronous circuits have been proposed for many years and have successfully shown their robustness to delay variations making them a key solution for digital and mixed-signal circuits. More specifically, asynchronous circuits have demonstrated their efficiency in solving control, arbiter and interfaces issues. In order to make them more widely adopted, modeling and synthesis of asynchronous circuits have been proposed through different methodologies that we will firstly detail and discuss in this paper. We will then demonstrate the use of these specific methodologies for the synthesis and design of digital and analog-to-digital interfaces. The overall paper aims at providing a study and analysis of specific interfaces and their dedicated controllers for synchronization and energy management applications while discussing the asynchronous community positioning accordingly.

**Keywords:** Asynchronous circuits, controllers, interfaces, digital, analog, modelling, synthesis, verification, STGs, Petri Nets.

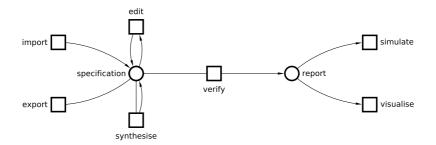

# 1 INTRODUCTION: TOOLS TO SOLVE INTERFACES ISSUES

This is now a cliché to say that there is a lack of tools for the design and verification of asynchronous circuits. But is that true? Not really, if we consider how challenging it is to enumerate all the tools that were developed and/or are still in use: Sis, Assassin, Forcage, Meat, Verdect, Syn, Versify, Tangram, Balsa, Teak, Cast, NCL, Ack, Tast, Pipefitter, Chp2Vhdl, Verilog2Stg, Desynch, Class, Haste, Tiempo-Tools, Petrify, Minimalist, Proteus, 3D...

So, why are there so many of them, and why people are complaining about a lack of tool? This is probably because there is still no consensus, neither about a modelinglanguage nor about a circuit-style. Therefore, many modeling languages and many asynchronous circuit styles are in use, not giving the opportunity of visible ones to emerge.

#### 16 Edith Beigne, Pascal Vivet and Marc Renaudin

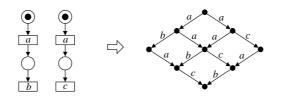

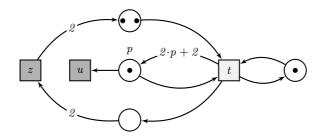

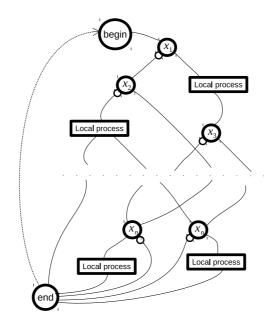

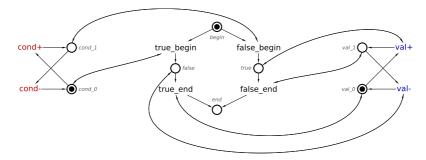

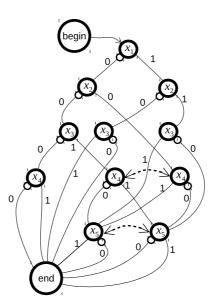

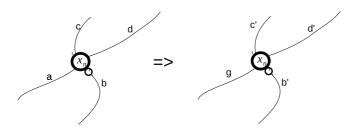

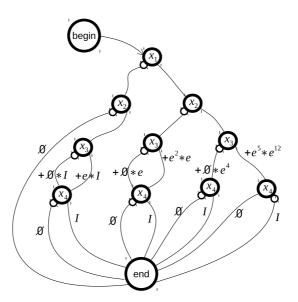

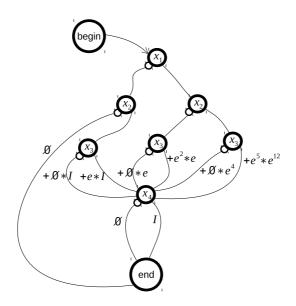

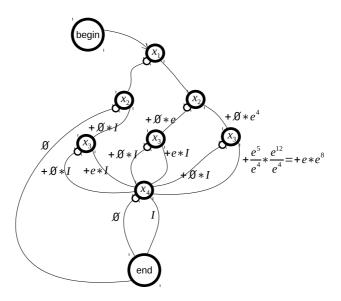

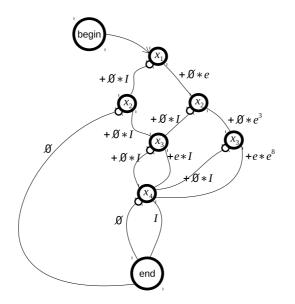

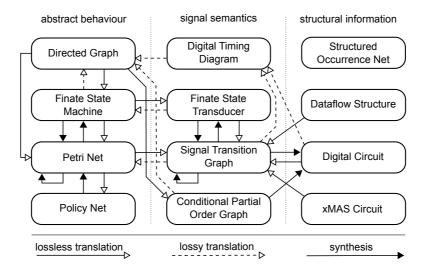

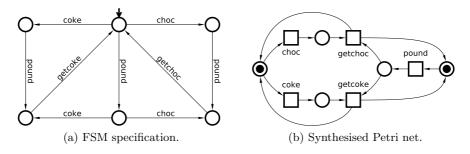

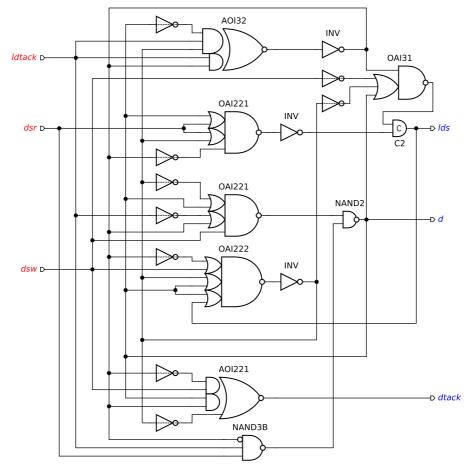

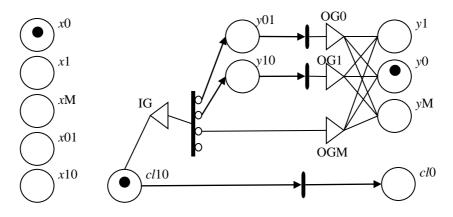

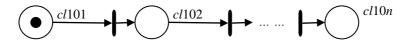

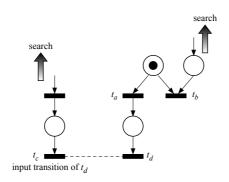

Prof. Yakovlev vision is focused, the language has to be suited to model, verify and synthesize asynchronous controllers, i.e. control circuits that are reactive to their input signals and able to drive their output signals, following a formal specification of concurrency, causality and choice. With this respect, a high level language is not necessary, there's no need for communicating processes, nor channels, but instead there is the need for modeling signals' behavior formally using concurrency and choice at a very fine grain. Exit Tangram, Balsa, CHP, HDLs, etc. and welcome Petri Nets [1] [2], STGs [3], or FSMs, even if there might be some links between them [4]. The spectrum of formalisms being narrowed, what is the appropriate graph based methodology and the supporting modeling language? PN, STGs, FSMs all target speed independent circuits which are robust enough to accommodate the variations the controllers have to resist, but they are not equivalent with respect to their ability to efficiently model and synthesize controllers.

Prof. Yakovlev and his team contributed to a major evolution of these graph-based approaches with the introduction of CPOG [5], because it prevents the designer from explicitly enumerating all the signal events and their traces together with their causal relations. CPOG is based on a description of the scenarios, i.e. the events traces, using a compact functional form. The signal encodings are specified apart, thus simplifying the controller's behavioral specification, and at the same time enabling synthesizing the controller with different encodings but keeping the same structural specification. Both aspects brought significant improvements to the modeling and design of asynchronous controllers.

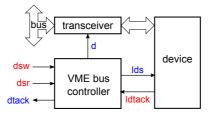

So, now it's fine, let's develop design tools using all the concurrency theory, the computer science and electrical engineering knowledge and skills underneath, in order to apply and prove that all this research is solving relevant real and physical problems. With this respect Prof. Yakovlev vision is very wide, especially in the domain of interfaces we want to focus on in this paper. He proposed the specification, implementation and verification of many arbiters, synchronizers and controllers for the communication between digital circuits both synchronous and asynchronous, or between digital and analog circuits, and also controllers dedicated to phase encodings and analog circuits, etc...

Prof. Yakovlev scientific contribution is significant and well recognized; it was used and continues to inspire many works in different domains, such as the design of interfaces we choose to briefly address in this paper, because it illustrates very well the broad scientific knowledges involved.

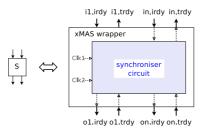

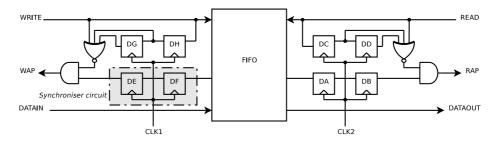

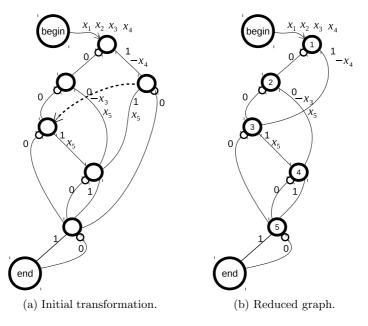

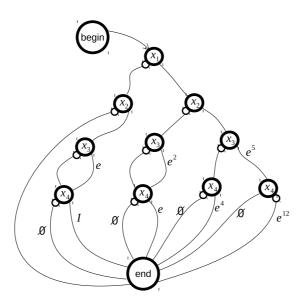

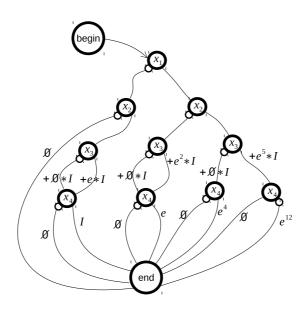

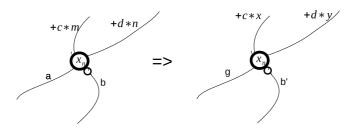

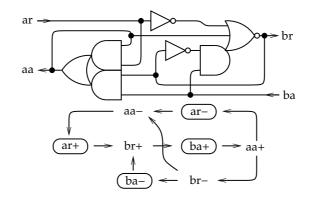

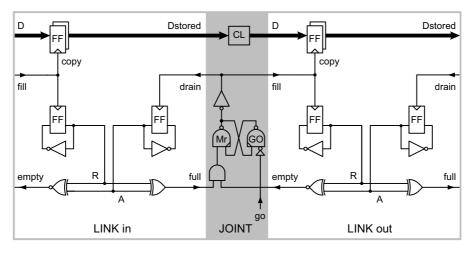

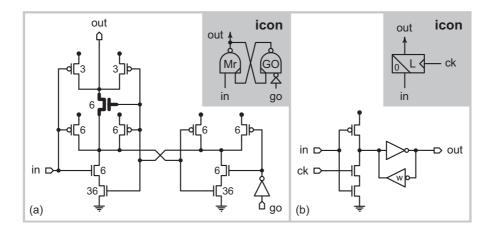

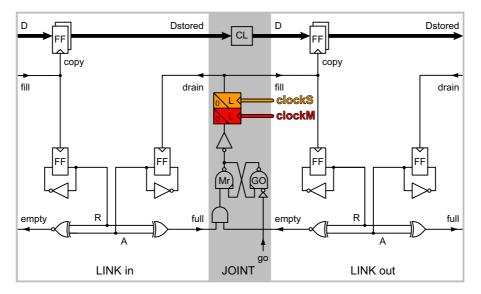

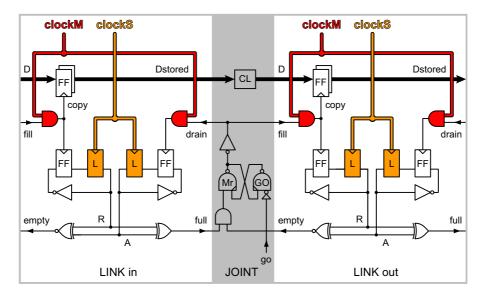

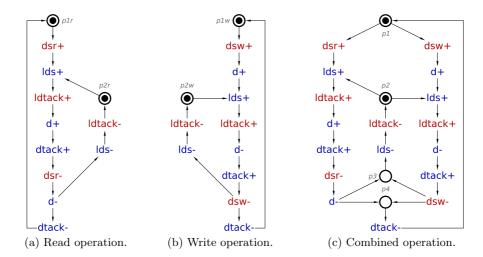

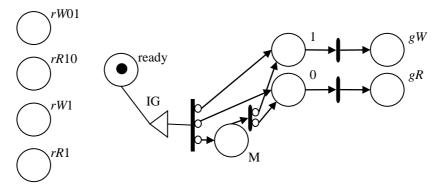

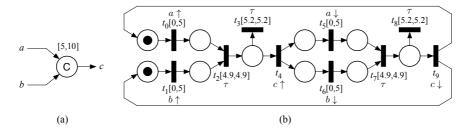

# 2 DIGITAL INTERFACES FOR SYNCHRONIZATION

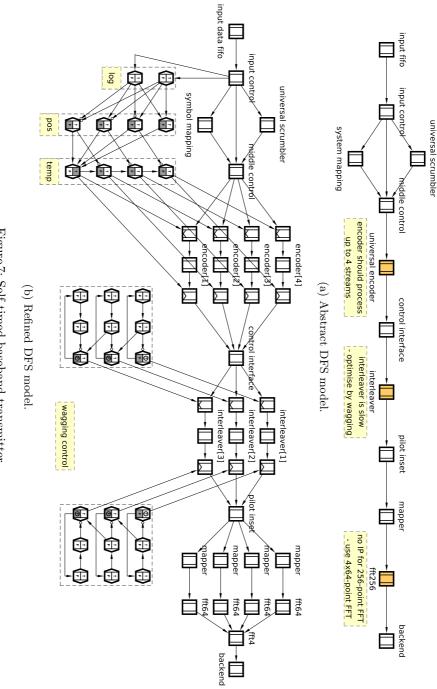

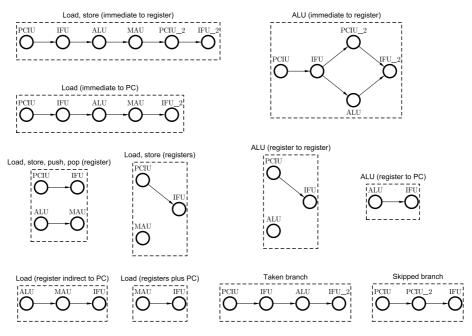

In advanced digital systems with nowadays large System-on-Chips and multicore architectures, one of the primary concern is the interconnect infrastructure, and how to implement efficient system communication for on-chip or off-chip communication. With tens of cores, hundreds of different clocks, and due to the always larger delay in wires compared to delay in gates, communication architecture and its clean implementation is a great challenge. Deep pipelining must be implemented to transport information from one die side to its other side. It is more costly to exchange data than performing computation.

In this context, Prof. Yakovlev was a precursor and very early applied his knowledge of asynchronous controller design to the design of generic and abstract interfaces to implement system interfaces. In [6], he early proposed the model and design of controllers to implement system communication of arbitrary protocols. It was applied to a simple fifo interface but claimed to be generic for application to any kind of interfaces: "a unified solution to the problem of synthesizing logic implementations from abstract specifications. Although easily applied to control circuits, it is suitable for all types of interfaces implemented in asynchronous logic. Prof. Yakovlev studied many kind of interfaces, such as [7] proposing system communication using STG, allowing reader & writer to indefinitely wait for an answer, compared to earlier work using fundamental mode : such interfaces was then latency insensitive (at protocol and system level) and Speed Independent or QDI at signal level. In [8], the proposed asynchronous interfaces could cope with various timing and protocol interfaces.

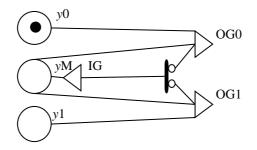

One of the primary aspects of system communication is obviously synchronization: a clean synchronization of low level signals must be performed to ensure robust communication. On this domain, Alex Yakovlev has made on the long time a very wide study of synchronization and its formalization, both at electrical level with the study of synchronizer cell elements, and at logical level with the design of a full range of asynchronous arbiters, using various specification methods and proposing different services. He proposed for instance flat arbiters [9], priority arbiters [10], and parallel multi-resource arbiters [11], among many other ones. More recently, he also proposed opportunistic merge elements, as a way to efficiently control asynchronous events within a switch cap converter. One can notice that smart digital interface implementing synchronization may also be required for efficient control of the analog domain, as it will be presented in section III.

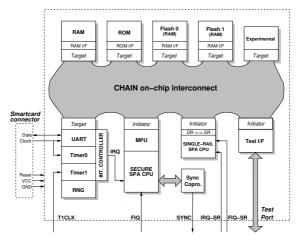

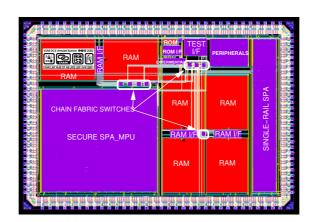

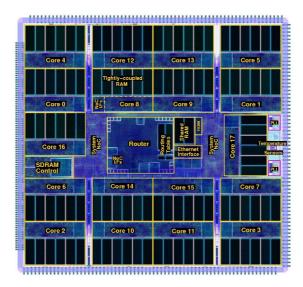

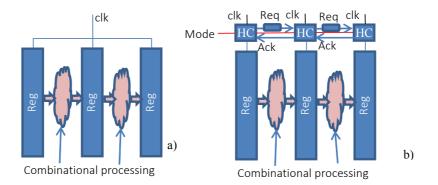

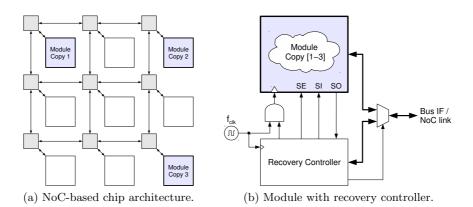

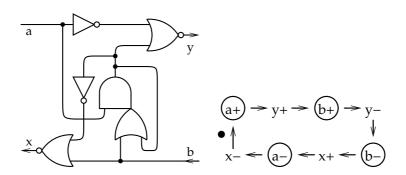

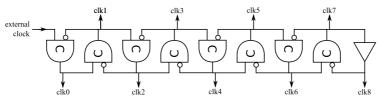

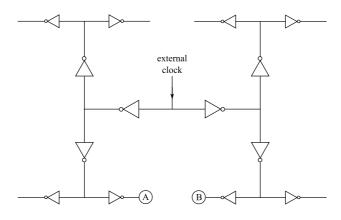

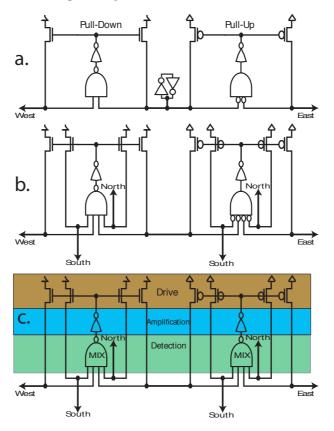

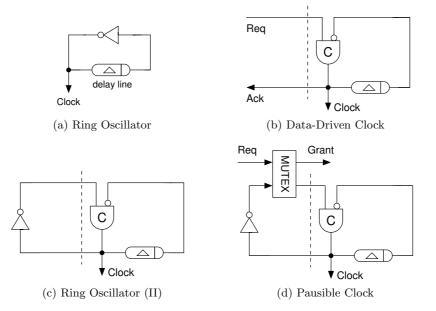

These contributions on interface synchronization and arbiter design have been a regular source of inspiration for the design of large scale system level interconnects. In the 2000's, the Network-on-Chip paradigm has been introduced and many flavors where proposed, in conjunction with the Globally Asynchronous Locally Synchronous (GALS) paradigm as early introduced by D. Chapiro. The NoC architecture offers first of all a clear separation of computation and communication, compared to previous bus-based topologies, and NoC perfectly fits the GALS paradigm, where computations (core, accelerators, etc...) are implemented using synchronous methods. Many flavors of GALS NoCs are then possible: either multi-synchronous, or meso-chronous, or fully asynchronous Network-on-Chip have been introduced and implemented, such as Chain, QNoC, Mango, ANOC, Hermes-A and more recently a 2-phase bundle-data NoC.

For the CEA-LETI ANOC architecture, the proposal is based on wormhole packet switching, it includes virtual channels for Quality of Service, while routers and links

#### 18 Edith Beigne, Pascal Vivet and Marc Renaudin

are implemented using Quasi Delay Insensitive logic with 4-phase / 4-rail protocol for robust system communications. The early arbiters design within the ANOC router were initiated by early works from Marc Renaudin and by priority arbiters [9] from Prof. Yakovlev proposal. Within CEA-LETI, a full series of circuit demonstrators have been developed using ANOC protocol, which was continuously improved by adding new features, such as on-chip and off-chip NoC interfaces, Design-for-Test wrapper, automatic router power down using activity detection, integration of DVFS scheme within NoC units, and with an automated flow for timing analysis and physical implementation. An extensive comparative study showed a clear benefit of ANOC versus its synchronous counterparts with a gain in power consumption by a ratio of 5.

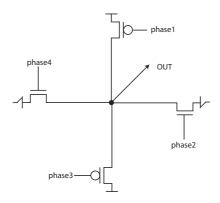

For NoC topologies, a challenge is the design of efficient and robust NoC links using dense encodings. Alex Yakovlev proposed original contributions on protocol signaling for system communication. For instance in [12], he proposed a novel selftimed communication protocol based upon phase-modulation of a reference signal. The reference and the data are sent on the same transmission lines and the data can be recovered observing the sequence of events on the same lines phase, offering a compact code, while being robust to faults. In the same period, for system communication, people tried also to extend and optimize the existing 2-phase protocol (for reduced number of transitions compared to 4-phase), but using denser codes. For examples, the LETS code offers a generic solution for 2-phase multi-rail codes, their protocols and their associated protocol converters. More recently, a 1-of-T multi-rail code was proposed for 2phase signaling with efficient 2-phase/4-phase protocol converters.

These few examples of asynchronous protocols and corresponding protocol converters can be applied to 3D architecture. 3D technology using so-called Through-Silicon-Via (TSV) offer a new paradigm for further system integration, with strong benefits in terms of yield and system partitioning, power reduction due to shorter connections, and a full spectrum of new architecture by using heterogeneous technologies (logic, memory, NVM, MEMs, etc). Again, in such 3D architecture, scalable and modular system communication is a challenge, and it can be elegantly implemented as an asynchronous 3D Network-on-Chip, by offering power efficient and robust 3D asynchronous communications without any global 3D clocking.

To conclude this section, asynchronous logic offers an efficient way to implement digital interfaces at system level. GALS has still a long story to play. The main design challenges are still the same: synchronization, arbitration, protocol communication and signaling. Detailed modeling of the interfaces is mandatory to ensure reliability and robust design. More automation would help but due to the large spectrum of all these interfaces, it will be difficult [16]. Even if mature solutions exist, research can always be carried-on on these complex topics to continue innovation on protocol signaling and associated control schemes!

# 3 MIXED-SIGNAL AND ANALOG INTERFACES

Interfaces issues are more and more problematic today with the advent of power management circuit techniques and mixed-signal systems of the Internet-of-Things (IoT). In the first case, voltage and frequency generators are analog circuits, integrated onchip, but controlling digital circuits. They require internal control loops and also need to be efficiently interfaced with digital blocks. IoT systems, on their side, are mixedsignal circuits in which many different interfaces are managed. In that kind of circuit, analog information is coming from sensors, wireless transfer or even energy harvesters. In that context, Prof. Yakovlev proposed many novel solutions from mixed-signal circuit workflow using asynchronous control [13] to Buck-boost DC-DC converters controls [14] and specific efficient IT controller called opportunistic merge element [15]. In the following we will discuss some of these works and put in perspective our current works using energy efficient asynchronous design.

#### 3.1 The advent of mixed-signal circuits

To start with, it is obvious to say that, today, most of our circuits are mixed-signal. We use to call mixed-signal, a circuit which contains an analog and a digital part, interfaced with Analog-to-Digital or Digital-to-Analog converters. The reality is more complex: small digital circuits are necessary to control analog blocks. It can be implemented as control loops or finite-state-machines. Prof. Yakovlev proposed a framework for the design of mixed-signal systems with asynchronous control [13]. It enables formal verification of AMS systems with asynchronous control and the workflow is efficiently demonstrated on a buck-boost converter. In our lab, we implemented in 2007 an integrated micro battery charger which can be charged by a thermogenerator's DC/DC output or by an HF converter. The power supply manager consisted in a specific unit along with an asynchronous finite state machine to manage priority between the two different sources. Electrical simulations were performed but no framework was available at that time to formally verify our circuit's functionality. This could have been solved by Prof. Yakovlev work and the proposed AMS methodology [13] and would have improved a lot our verification step.

#### 3.2 Power management circuits and limitations

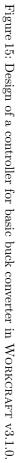

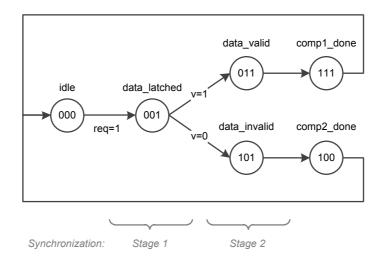

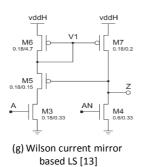

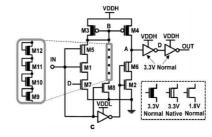

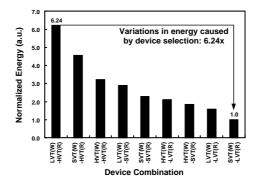

One of the main mixed-signal components in today's circuits is related to power management and more precisely to voltage generation. Prof. Yakovlev demonstrated that power control can significantly benefit from the use of asynchronous logic [14]. They demonstrated how to design and verify a speed-independent multi-phase buck-boost converter. It has been shown to be extremely robust to the changes in power demand. In the same topic, in our lab, we first tried to get rid of classical synchronous DC-DC converter by proposing a Vdd-Hopping solution based on voltage dithering. In this scheme, two or three supply voltages are available on chip and delivered through power switches to the digital block. The main advantage is very high power efficiency as it only consumes during transitions. To avoid any undershoots and overshoots on

#### 20 Edith Beigne, Pascal Vivet and Marc Renaudin

the digital block power supply, a local control loop is implemented. It was originally designed using synchronous logic, but we finally realized that an asynchronous loop would have probably been more robust to voltage changes as demonstrated by Prof. Yakovlev in a paper entitled "Design and Verification of Speed-Independent Multiphase Buck Controller". Another interesting application of asynchronous circuits at the interface of power supply and energy harvesters is presented in our lab in 2010. An asynchronous state-machine controls the energy levels between different energy sources (Photo-voltaic, Thermoelectric, etc.). The control is based on voltage level crossings on capacitances representing the energy level of the sources. We are still working on this topic today as, ideally; it could bring infinite energy autonomy to IoT circuits and systems making them fully energy-driven (similarly to asynchronous data-driven circuits).

#### 3.3 Low power IoT circuits and systems

We have just discussed interfaces and control for mixed-signal circuits related to power management issues. In addition, in emerging IoT systems, many analog sensors have to interface with digital controllers. Events coming from these sensors are purely asynchronous and it would be inefficient in terms of energy to continuously sample them as they can occur in very different time scales. An efficient solution is to handle these events as asynchronous Interrupts (ITs) computed by an asynchronous IT controller (IT-Ctrl) as shown in our very recent works. An asynchronous IT-Ctrl manages all the peripherals events and sends the priority number to a decoder. Interruptions are sorted by interruption numbers with the highest priority on interrupt number 0 and weakest priority on interrupt number 31. This scheme is interesting in terms of wake-up as, due to its asynchronous implementation, it immediately reacts on an incoming interrupt. However, the priority could be treated in a different way to improve this controller's energy efficiency. Indeed, Prof. Yakovlev's work proposes an element named opportunistic merge element which could greatly improve our IT controller performances. This innovative asynchronous component merges two or more request-acknowledge channels into one and is allowed to opportunistically send requests if they arrive close to each other. Our future works aim at improving our current IT controller with the help of an opportunistic scheme as described [15] by Prof. Yakovlev work.

# 4 CONCLUSION

We have discussed in this paper interfaces issues in digital and mixed-signal circuits. These interfaces can be implemented between synchronous domains or between analog to digital and digital to analog parts of circuits. They are also seen as a key issue between synchronous and asynchronous timing domains. We have shown how Prof Yakovlev's work has been focused, in part, to solve these issues by proposing many different methodologies and innovative implementation schemes. Our aim has been to put in perspective our own work with respect to his research all along the paper and to show that most of our proposals are complementary or could have been even greatly improved by Prof Yakovlev's proposals.

# References

- A. Yakovlev, A. Koelmans, A. Semenov, D. Kinniment, "Modelling, analysis and synthesis of asynchronous control circuits using Petri Nets", Integration: the VLSI Journal, 1996, Vol. 21, N°. 3, pp. 143-170.

- A. Yakovlev, A. Koelmans, "Petri Nets and Digital Hardware design", in W. Reisig, G. Rosenberg ed., Lectures on Petri Nets II: Applications, Advances in Petri Nets, Berlin, New York, Springer-Verlag, 1998, 154-236.

- D. Sokolov, A. Bystrov, A. Yakovlev, "STG optimization in the direct mapping of asynchronous circuits", Design Automation and Test in Europe (DATE), 2003, Munich, Germany.

- M. Renaudin, A. Yakovlev, "From Hardware Processes to Asynchronous Circuits via Petri Nets: an Application to Arbiter Design", Workshop on Token Based Computing (ToBa-Co), part of the 25th International Conference on Applications and Theory of Petri Nets (ICATPN'04), 2004.

- A. Mokhov, A. Yakovlev, "Conditional Partial Orders Graphs: Models, Synthesis, and Application", IEEE Transactions on Computers, 2010, Vol. 59, N°. 11, 1480-1493.

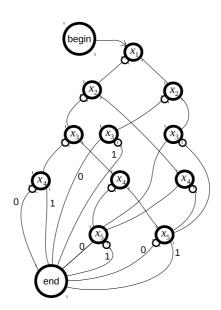

- A. Yakovlev, A. Koelmans, L. Lavagno, "High-level modeling and design of asynchronous interface logic", IEEE Design & Test of Computers, 1995, vol. 12, issue 1, pp. 32-40.

- F. Xia, A. Yakovlev, D. Shang, A. Bystrov, A. Koelmans, D. Kinniment, "Asynchronous communication mechanisms using self-timed circuits", Sixth International Symposium on Advanced Research in Asynchronous Circuits and Systems, 2000, pp. 150-159.

- F. Xia, A. Yakovlev, I. G. Clark, D. Shang, "Data communication in systems with heterogeneous timing", IEEE Micro, 2002, Vol. 22, Issue 6, pp. 58-69.

- 9. A. Mokhov, V. Khomenko, A. Yakovlev, "Flat Arbiters", Fundamenta Informaticae, 2011, 108(1-2), pp. 63-90.

- A. Bystrov, D. Kinniment, A. Yakovlev, "Priority Arbiters", International Symposium on Advanced Research in Asynchronous Circuits, April 2000, pp. 128-137.

- D. Shang, F. Xia, A. Yakovlev, "Highly parallel multi-resource arbiters", Proceedings of 2010 IEEE International Symposium on Circuits and Systems, 2010, pp. 4117-4120.

- C. D'Alessandro, Delong Shang, A. Bystrov, A. Yakovlev, O. Maevsky, "Multiple-rail phase-encoding for NoC", 12th IEEE International Symposium on Asynchronous Circuits and Systems, 2006, pp.110-116.

- 13. V. Dubikhin, C. J. Myers, A. Yakovlev, D. Sokolov, "Design of Mixed-signal Systems with Asynchronous Control", IEEE Design & Test, 2016, 10.1109/MDAT.2016.2555916.

- D. Sokolov, V. Khomenko, A. Mokhov, A. Yakovlev and D. Lloyd, "Design and Verification of Speed-Independent Multiphase Buck Controller," Asynchronous Circuits and Systems (ASYNC), IEEE International Symposium on, Mountain View, CA, 2015, pp. 29-36.

- A. Mokhov, V. Khomenko, D. Sokolov and A. Yakovlev, "Opportunistic Merge Element," Asynchronous Circuits and Systems (ASYNC), 2015 21st IEEE International Symposium on, Mountain View, CA, 2015, pp. 116-123.

- A. Yakovlev, P. Vivet, M. Renaudin, "Advances in Asynchronous Logic: from Principles to GALS & NoC, Recent industry Applications, and Commercial CAD Tools", in Conference on Design, Automation and Test in Europe (DATE'13), 2013, Grenoble, France.

# A Community of Asynchronauts: 20+ Years of the ASYNC Conference

Erik Brunvand

School of Computing University of Utah Salt Lake City, UT 84112

**Abstract.** Since its founding in 1994, the IEEE Symposium on Asynchronous Circuits and Systems has been a premiere venue for publishing results from the asynchronous research community. Perhaps more importantly, it has also been an annual meeting where people gather, form and renew friendships, and build a strong sense of community. In this paper I will give a brief history of the ASYNC Symposium with a special focus on the social events that have contributed so much to the tremendous sense of community we enjoy among asynchronous researchers.

## 1 Introduction

Researchers interested in asynchronous circuits and systems have always been a bit on the fringe of the computer engineering world. Although there were interesting examples of asynchronous approaches in the early days of computer design, the codification of a synchronous design style, and the subsequent support for that design style in computer-aided design tools, resulted in the vast majority of digital systems using a synchronous timing regime. In spite of that inertia, an intrepid group of researchers has continued to be intrigued by the possibilities of asynchronous approaches, both in terms of design (at circuit and system levels) and analysis/theory.

Like researchers in many "niche" areas, their results were sometimes not appreciated by the larger research community, and often had to struggle to be recognized at the larger conferences and journals. As sometimes happens, when the critical mass of research becomes great enough in an area, this spawns a new conference series devoted more specifically to that area of study.

In the case of asynchronous design, this critical mass was reached in the early 1990's. Leading up to this point researchers such as Chuck Seitz at Caltech [36, 39, 38], Charles Molnar, Tom Chaney and Wes Clark at Washington University in Saint Louis [13, 12, 14, 25], Steven Unger at Columbia [49, 50], and Victor Varshavsky at the St. Petersburg Electrical Engineering Institute [51–53] were doing foundational work from the late 1960's to the early 1980's, without the benefit of a specific conference venue.

One standout conference series that included a nice set of early asynchronous and self timed papers was the Caltech Conference on VLSI which would become the Advanced Research in VLSI (ARVLSI) conference series. The very first Caltech Conference in 1979, for example, had three seminal papers on asynchronous subjects [45, 48, 37] and the 1983 version of that conference included another set of important papers on asynchronous circuits and systems [16, 17, 40].

In the 1980's researchers such as Alain Martin at Caltech [19–21], Bob Sproull and Ivan Sutherland at Caltech and Carnegie Mellon University [41, 47, 15], and Theresa Meng at Stanford [23, 22, 24] were extending the work of earlier pioneers, and they, along with the pioneers, were producing a new generation of asynchronous researchers including Peter Beerel [2, 3, 1], Erik Brunvand [10, 7– 9], Chris Myers [27, 28, 26], Steven Nowick [29–31], and Ken Stevens [44, 42, 43], Kees van Berkel [4–6], Alex Yakovlev [54, 18, 55], and many others (note that references chosen in this section are specifically the early works from these selected researchers).

With the backdrop of the expanding world of asynchronous and self-timed research, the time was right for a conference devoted to this research area.

# 2 Pre-history: HICSS 1993

The first foray into thinking about a discipline-specific conference was to propose and organize a special session on Asynchronous and Self-Timed Circuits and Systems at an existing conference. Erik Brunvand and Ganesh Gopalakrishnan from the University of Utah took up the challenge and organized just such a special session at the 1993 Hawaiian International Conference on System Sciences (HICSS) (see Figure 1). This conference had the double benefit of being open to such a special session on a niche topic, and also being held in Maui, Hawaii in January. The conference "mini-track" was a huge success with 14 papers accepted and presented by most of the leading researchers in the area. In fact, the Hawaiian conference organizers were apparently not prepared for the success of the minitrack, and for the avid nature of the asynchronous research community. The conference session was held in a tiny room that was overflowing with attendees anxious to participate in the session and hear about the research. The organizers of the conference were apparently thinking that people would be at the beach rather than listen to papers on such a topic! But the interest and enthusiasm was clear. That session was enough to encourage the organizers to think in grander terms and organize a whole conference dedicated to the subnect of asynchronous and self-timed circuits and systems research.

# 3 Async 1994: Salt Lake City, UT, USA

The first official IEEE Symposium on Advanced Research in Asynchronous Circuits and Systems was organized and held in November 1994 in Salt Lake City at the University of Utah. The conference was primarily organized by: General Chairs Erik Brunvand (University of Utah), Al Davis (University of Utah), and Program Chairs Ganesh Golpalakrishnan (University of Utah) and Steven Now-ick (Columbia University). The name for the conference was a bit of a mouthful,

#### 24 Erik Brunvand

**Fig. 1.** The proceedings cover, and the session contents, for the Special Session on Asynchronous and Self-Timed Circuits and Systems at the 1993 Hawaiian International Conference on Systems Science held on Maui, Hawaii.

but chosen to echo the name of the premiere VLSI conference of the day, the conference on Advanced Research in VLSI (ARVLSI). The Async conference name was eventually shortened to remove the "Advanced Research in" portion of the name.

The conference was organized with support from the IEEE Technical Committee on VLSI - support that it continues to have to this day. It was also started with a small grant from the National Science Foundation to support student attendance at the conference, and also non-monetary support from IFIP Working Groups 10.2 and 10.5. The November time frame of the original conference was designed to be loosely compatible with the International Conference on Computer Aided Design (ICCAD) so that attendees could plausibly come to both conferences one after the other, ICCAD being held in November 1994 in Santa Clara, California.

The program committee for the first Async conference in 1994 reads like a "who's who" of asynchronous and self-timed researchers at the time: Graham Birtwistle, Steven Burns, Raul Camposano, Tam-Anh Chu, David Dill, Steven Furber, Luciano Lavagno, Bill Lin, Alain Martin, Teresa H.-Y. Meng, Charles Molnar, Martin Rem, Jens Sparsø, Robert Sproull, Pasupathi (Subra) Subramanyam, Jan Tijmen Udding, Steven Unger, Kees van Berkel, Peter Vanbekbergen, and Alex Yakovlev. The conference registration fee for IEEE members was \$225, and students could register for \$65. The conference included 25 refereed papers and one invited paper. The keynote speaker was Ivan Sutherland (Sun Microsystems).

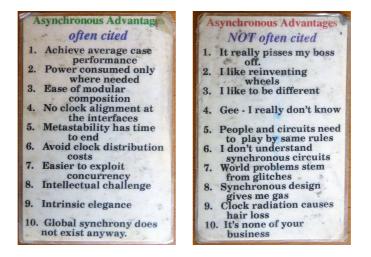

Perhaps the most memorable keepsake from this first Async conference was the "Async wallet card" (see Figure 2). This card, given to all conference atten-

Fig. 2. The front and back sides of the wallet card given to Async 1994 attendees. This card was designed and produced by Al Davis and Erik Brunvand.

dees, was designed and produced by Al Davis and Erik Brunvand back in the day when color printing and laminating had to happen at a commercial printing shop. The card featured a list of the most common asynchronous advantages that we had seen repeated in virtually every paper, along with humorous "advantages" not often cited in papers. For many years afterwards at future Async conferences a challenge was given by Ivan Sutherland to hold up your Async wallet card if you still had it with you.

Although there was no organized outing at this first Async conference, it was definitely a starting point for the community of Asynchronauts. Friendships and research collaborations initiated at this very first Async conference persist to this day. From my clearly biased perspective, it was a rousing success!

#### 4 Async 1996: Aizu, Japan