Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lay bed ON Semiconductor and its officers, employees, ween if such claim alleges that ON Semiconductor was negligent regarding the d

# DC Noise Immunity of **CMOS Logic Gates**

#### Introduction

The immunity of a CMOS logic gate to noise signals is a function of many variables, such as individual chip differences, fan-in and fan-out, stray inductance and capacitance, supply voltage, location of the noise, shape of the noise signal, and temperature. Moreover, the immunity of a system of gates usually differs from that of any individual gate; thus a generalized analysis of the noise immunity of a logic circuit becomes a very complex process when one takes all the above parameters into consideration.

The complementary structure of the inverter results in a near-ideal input-output characteristic with switching point midway (45%-55%) between the "0" and "1" output logic levels. The result is a high noise immunity (defined as the maximum noise voltage which can appear on the input without switching an inverter from one state to another). Fairchild's CMOS circuits have a typical noise immunity of 0.45  $\rm V_{\rm CC}.$ This means that a spurious input which is 45% of the power supply voltage typically will not propagate through the circuit. However, the standard guaranteed value through the industry is 30%.

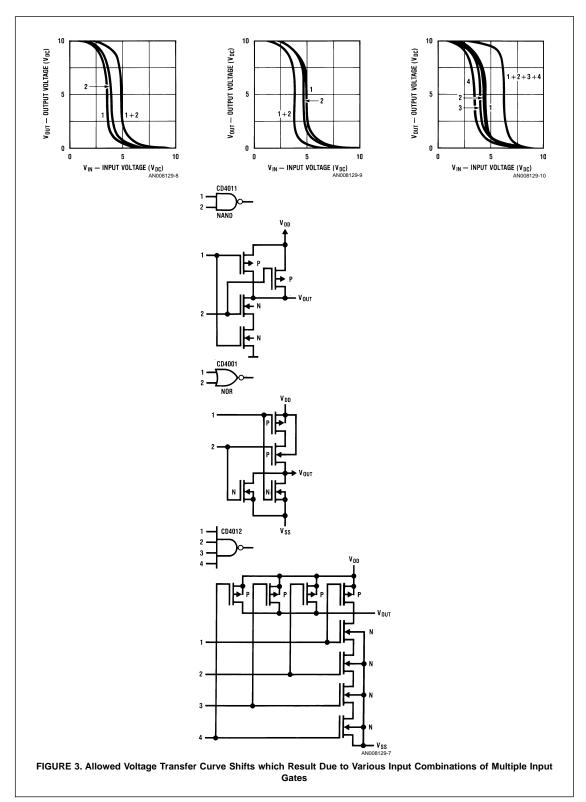

This note describes the variation of the transfer region (or DC noise immunity) of a multiple-input gate in conjunction with the gate configuration-a consideration important in the system design.

#### **Transfer Characteristics**

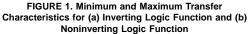

Figure 1 illustrates minimum and maximum transfer characteristics useful for defining noise immunity for an inverter and a non-inverter. Some definitions are as follows:

Fairchild Semiconductor Application Note 377 July 1984

VIH min=the minimum input voltage high-level input for which the output logic level does not change state. Then:

- V<sub>NL</sub>=V<sub>ILmax</sub>="low level" noise immunity

- V<sub>NH</sub>=V<sub>DD</sub>-V<sub>IH</sub>="high level" noise immunity

- V<sub>OHmin</sub>=minimum high level output voltage for rated V<sub>NL</sub>-[for inverting function as in Figure 1 (a)]

Table 1 shows the UB and B series noise immunity and noise margin ratings determined by the Joint Electron Devices Engineering Council (JEDEC). B series ratings are slightly higher than the UB series because of the buffered nature of these gates.

| TABLE 1. UB and | <b>B</b> Series | DC  | Noise | Immunity | and |

|-----------------|-----------------|-----|-------|----------|-----|

| Nois            | e Margin        | (T_ | =25°C | )        |     |

| Characteristics     |          | Test<br>Conditio | Input<br>Voltage |      |

|---------------------|----------|------------------|------------------|------|

|                     |          | V <sub>o</sub>   | V <sub>DD</sub>  | (V)  |

|                     |          | (V)              | (V)              |      |

| Input Low Vo        | oltage   |                  |                  |      |

| V <sub>IL</sub> max |          |                  |                  |      |

|                     | B types  | 0.5/4.5          | 5                | 1.5  |

|                     |          | 1/9              | 10               | 3    |

|                     |          | 1.5/13.5         | 15               | 4    |

|                     | UB types | 0.5/4.5          | 5                | 1    |

|                     |          | 1/9              | 10               | 2    |

|                     |          | 1.5/13.5         | 15               | 2.5  |

| Input High V        | oltage   |                  |                  |      |

| V <sub>IH</sub> min |          |                  |                  |      |

|                     | B types  | 0.5/4.5          | 5                | 3.5  |

|                     |          | 1/9              | 10               | 7    |

|                     |          | 1.5/13.5         | 15               | 11   |

|                     | UB types | 0.5/4.5          | 5                | 4    |

|                     |          | 1/9              | 10               | 8    |

|                     |          | 1.5/13.5         | 15               | 12.5 |

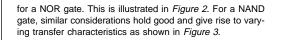

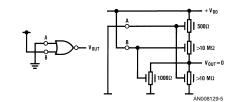

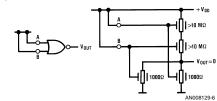

Since the MOS transistors are voltage-controlled resistors, the transfer characteristics and consequently the DC noise immunity are determined by the parallel series combination of the transistor impedances in conjunction with the input voltages, the number of inputs, and the gate circuit configuration. This consideration becomes more important for a system designer who has harsh-noise-prone applications.

The value of the standard transistor ON resistance may vary from 10 M $\Omega$  down to almost 30 $\Omega$  (depending on the dimensions of the MOS-FET and applied voltages). For different input conditions, different combinations of the impedances of the N-channel transistors connected in parallel and the P-channel transistors connected in series will come into play

© 1998 Fairchild Semiconductor Corporation AN008129 AN-377

A=1, B=0

A=0, B=1

A=B=1

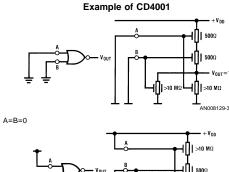

FIGURE 2. Typical Transfer ON/OFF Resistances for Various Input Combinations for CD4001

#### Analysis

The DC transfer characteristics of the CMOS inverter can be calculated from the simplified DC current-voltage characteristics of the N- and P-channel MOS devices.

In the transfer region, where both transistors are in saturation, the following relationships can be used for an inverter. N-channel drain current will be:

$$I_{dsn} = \frac{K_n}{2} (V_{IN} - V_{TN})^2$$

(1)

P-channel drain current will be:

$$-I_{dsp} = \frac{K_p}{2} (V_{IN} - V_{DD} - V_{TP})^2$$

(2)

where:

$$K_{n} = \frac{\mu n C_{ox} W_{n}}{L_{n}}, K_{p} = \frac{\mu p C_{ox} W_{p}}{L_{p}}$$

Taking the ratio of Equation (2) and Equation (1):

$$\frac{|I_{dsp}|}{I_{dsn}} = \frac{K_p}{K_n} \cdot \frac{(V_{IN} - V_{DD} - V_{TP})^2}{(V_{IN} - V_{TN})^2}$$

$$\frac{K_p}{K_n} = \frac{|Idsp|}{I_{dsn}} \cdot \frac{(V_{IN} - V_{TN})^2}{(V_{IN} - V_{DD} - V_{TP})^2}$$

(3)

Studies made at Fairchild show good correlations between the process monitor pattern and actual device on a wafer for drive currents. Thus the ratio  $K_p/K_n$  can be calculated for the actual device if one knows drive currents for the test pattern, widths of N- and P-channel devices and threshold voltages from a given process.

The transition voltage is calculated from basic current equations and from the fact that some current has to flow through P- and N-channel devices. Equating saturation currents and rearranging terms, one can obtain<sup>1</sup>:

Transition Voltage=V<sub>IN</sub>\*

$$=\frac{V_{TN}+\sqrt{\frac{K_{p}}{K_{n}}(V_{DD}-|V_{TP}|)}}{\sqrt{1+K_{p}/K_{n}}}$$

(4)

www.fairchildsemi.com

www.fairchildsemi.com

By selecting  $|V_{TP}|=V_{TN}$  and  $K_p=K_n$ , transition voltage can be designed to fall midway between 0V and  $V_{DD}$ —an ideal situation for obtaining excellent noise immunity. However, it is not always possible to obtain equal threshold voltages because of process variations. Also, W/L ratio for a P-channel device must be made 2 or 3 times larger than W/L ratio for an N-channel device to take into account mobility variations. The designer should consider these factors when designing for the best noise immunity characteristics.

In *Equation (4)*, the value of K<sub>p</sub>/K<sub>n</sub> substituted is obtained from *Equation (3)*. With different gate configurations, effective W<sub>p</sub> and W<sub>n</sub> values change; also, K<sub>p</sub>/K<sub>n</sub> ratio changes and a shift in transfer characteristics results.

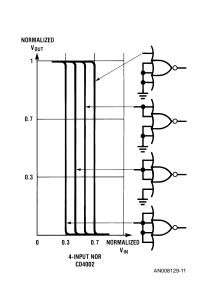

For the 4-input NOR gate like CD4002, an empirical relation for the low noise margin  $\rm V_{\rm NL}$  has been obtained, which is as follows:

$V_{NL} \approx V_{DD} \Bigg[ \frac{1}{1.5 + \frac{N_i}{N_m}} - 0.1 \Bigg]$

where:

Ni=number of used inputs/gate

N<sub>m</sub>=total number of inputs/gate

The input voltage high noise margin  $V_{\rm NH}$  can be calculated by:

$$V_{\text{NH}} \approx V_{\text{DD}} \Bigg[ 0.9 - \frac{1}{1.5 + \frac{N_i}{N_m}} \Bigg] \tag{6}$$

Similar equations can be derived for a NAND gate.

From Equation (5) and Equation (6), one can see that the low noise margin  $V_{\rm NL}$  will *decrease* as a function of the number of controlled inputs, while it will increase for a NAND gate. The input HIGH noise margin will *increase* as a function of the number of controlled inputs for the NOR gate; for the NAND gate it will decrease.

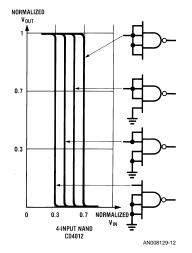

Figure 4 depicts  $V_{OUT}$ =f ( $V_{IN}$ ) for different configurations for NOR and NAND gates. The system designer can thus use these facts effectively in his design and obtain the best possible configuration for the desired noise immunity with Fairchild's logic family.

FIGURE 4. Example of Transfer Voltage Variation for NOR and NAND Gates for Various Input Combinations

(5)

1. Carr, W.N., and Mize, J.P., MOS/LSI Design and Application, Texas Instruments Electronic Series, 1972

www.fairchildsemi.com

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMI-CONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

| Fairchild Semiconductor<br>Corporation | Fairchild Semiconductor<br>Europe   | Fairchild Semiconductor<br>Hong Kong Ltd. | National Semiconduct<br>Japan Ltd. |

|----------------------------------------|-------------------------------------|-------------------------------------------|------------------------------------|

| Americas                               | Fax: +49 (0) 1 80-530 85 86         | 13th Floor, Straight Block,               | Tel: 81-3-5620-6175                |

| Customer Response Center               | Email: europe.support@nsc.com       | Ocean Centre, 5 Canton Rd.                | Fax: 81-3-5620-6179                |

| Tel: 1-888-522-5372                    | Deutsch Tel: +49 (0) 8 141-35-0     | Tsimshatsui, Kowloon                      |                                    |

|                                        | English Tel: +44 (0) 1 793-85-68-56 | Hong Kong                                 |                                    |

|                                        | Italy Tel: +39 (0) 2 57 5631        | Tel: +852 2737-7200                       |                                    |

| www.fairchildsemi.com                  |                                     | Fax: +852 2314-0061                       |                                    |

Fairchild does not assume any responsibility for use of any circuity described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

## PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC