DRAFT INTERNATIONAL STANDARD ISO/DIS 26262-5

ISO/TC 22/SC 3

Secretariat: DIN

Voting begins on: 2009-07-08

Voting terminates on: 2009-12-08

INTERNATIONAL ORGANIZATION FOR STANDARDIZATION • MEXCHAPODHAS OPPAHUSALUNS NO CTAHDAPTUSALUN • ORGANISATION INTERNATIONALE DE NORMALISATION

# Road vehicles — Functional safety —

# Part 5: Product development: hardware level

Véhicules routiers — Sécurité fonctionnelle — Partie 5: Développement du produit : niveau matériel

ICS 43.040.10

In accordance with the provisions of Council Resolution 15/1993 this document is circulated in the English language only.

Conformément aux dispositions de la Résolution du Conseil 15/1993, ce document est distribué en version anglaise seulement.

To expedite distribution, this document is circulated as received from the committee secretariat. ISO Central Secretariat work of editing and text composition will be undertaken at publication stage.

Pour accélérer la distribution, le présent document est distribué tel qu'il est parvenu du secrétariat du comité. Le travail de rédaction et de composition de texte sera effectué au Secrétariat central de l'ISO au stade de publication.

THIS DOCUMENT IS A DRAFT CIRCULATED FOR COMMENT AND APPROVAL. IT IS THEREFORE SUBJECT TO CHANGE AND MAY NOT BE REFERRED TO AS AN INTERNATIONAL STANDARD UNTIL PUBLISHED AS SUCH.

IN ADDITION TO THEIR EVALUATION AS BEING ACCEPTABLE FOR INDUSTRIAL, TECHNOLOGICAL, COMMERCIAL AND USER PURPOSES, DRAFT INTERNATIONAL STANDARDS MAY ON OCCASION HAVE TO BE CONSIDERED IN THE LIGHT OF THEIR POTENTIAL TO BECOME STANDARDS TO WHICH REFERENCE MAY BE MADE IN NATIONAL REGULATIONS.

RECIPIENTS OF THIS DRAFT ARE INVITED TO SUBMIT, WITH THEIR COMMENTS, NOTIFICATION OF ANY RELEVANT PATENT RIGHTS OF WHICH THEY ARE AWARE AND TO PROVIDE SUPPORTING DOCUMENTATION.

#### PDF disclaimer

This PDF file may contain embedded typefaces. In accordance with Adobe's licensing policy, this file may be printed or viewed but shall not be edited unless the typefaces which are embedded are licensed to and installed on the computer performing the editing. In downloading this file, parties accept therein the responsibility of not infringing Adobe's licensing policy. The ISO Central Secretariat accepts no liability in this area.

Adobe is a trademark of Adobe Systems Incorporated.

Details of the software products used to create this PDF file can be found in the General Info relative to the file; the PDF-creation parameters were optimized for printing. Every care has been taken to ensure that the file is suitable for use by ISO member bodies. In the unlikely event that a problem relating to it is found, please inform the Central Secretariat at the address given below.

#### **Copyright notice**

This ISO document is a Draft International Standard and is copyright-protected by ISO. Except as permitted under the applicable laws of the user's country, neither this ISO draft nor any extract from it may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, photocopying, recording or otherwise, without prior written permission being secured.

Requests for permission to reproduce should be addressed to either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Case postale 56 • CH-1211 Geneva 20 Tel. + 41 22 749 01 11 Fax + 41 22 749 09 47 E-mail copyright@iso.org Web www.iso.org

Reproduction may be subject to royalty payments or a licensing agreement.

Violators may be prosecuted.

# Contents

| Forewo  | ord                                                                  | v   |

|---------|----------------------------------------------------------------------|-----|

| Introdu | uction                                                               | vi  |

| 1       | Scope                                                                | 1   |

| 2       | Normative references                                                 | 1   |

| 3       | Terms and definitions                                                | 2   |

| 4       | Requirements for compliance                                          | 2   |

| 4.1     | General requirements                                                 | 2   |

| 4.2     | Interpretations of tables                                            | 2   |

| 4.3     | ASIL dependent requirements and recommendations                      | 2   |

| 5       | Initiation of product development at the hardware level              | 3   |

| 5.1     | Objectives                                                           | 3   |

| 5.2     | General                                                              | 3   |

| 5.3     | Inputs to this clause                                                | 4   |

| 5.4     | Requirements and recommendations                                     | 5   |

| 5.5     | Work products                                                        | 5   |

| 6       | Specification of hardware safety requirements                        | 5   |

| 6.1     | Objectives                                                           | 5   |

| 6.2     | General                                                              | 5   |

| 6.3     | Inputs to this clause                                                | 5   |

| 6.4     | Requirements and recommendations                                     | 6   |

| 6.5     | Work products                                                        | 8   |

| 7       | Hardware design                                                      | 8   |

| 7.1     | Objectives                                                           | 8   |

| 7.2     | General                                                              | 8   |

| 7.3     | Inputs to this clause                                                | 8   |

| 7.4     | Requirements and recommendations                                     | 9   |

| 7.5     | Work products                                                        | .13 |

| 8       | Hardware architectural metrics                                       | .13 |

| 8.1     | Objectives                                                           | .13 |

| 8.2     | General                                                              | .13 |

| 8.3     | Inputs of this clause                                                | .14 |

| 8.4     | Requirements and recommendations                                     | .14 |

| 8.5     | Work products                                                        | .16 |

| 9       | Evaluation of violation of the safety goal due to random HW failures | .16 |

| 9.1     | Objectives                                                           | .16 |

| 9.2 General 1                                                                                       | 6                          |

|-----------------------------------------------------------------------------------------------------|----------------------------|

| 9.3 Inputs to this clause 1                                                                         | 7                          |

| 9.4 Requirements and recommendations 1                                                              | 7                          |

| 9.5 Work products 2                                                                                 | :5                         |

| 10 Hardware integration and testing 2                                                               | :5                         |

| 10.1 Objectives                                                                                     | :5                         |

| 10.2 General 2                                                                                      | :5                         |

| 10.3 Inputs of this clause                                                                          | :6                         |

| 10.4 Requirements and recommendations 2                                                             | :6                         |

| 10.5 Work products 2                                                                                | :9                         |

|                                                                                                     |                            |

| Annex A (informative) Overview on and document flow of product development at the hardware level    | :0                         |

|                                                                                                     |                            |

| level                                                                                               | 32                         |

| Ievel       3         Annex B (informative)       Failure mode classification of a hardware element | 82<br>84                   |

| Ievel       3         Annex B (informative)       Failure mode classification of a hardware element | 32<br>34<br>38             |

| Ievel       3         Annex B (informative) Failure mode classification of a hardware element       | 32<br>34<br>38<br>33       |

| Ievel       3         Annex B (informative) Failure mode classification of a hardware element       | 32<br>34<br>38<br>33<br>34 |

# Foreword

ISO (the International Organization for Standardization) is a worldwide federation of national standards bodies (ISO member bodies). The work of preparing International Standards is normally carried out through ISO technical committees. Each member body interested in a subject for which a technical committee has been established has the right to be represented on that committee. International organizations, governmental and non-governmental, in liaison with ISO, also take part in the work. ISO collaborates closely with the International Electrotechnical Commission (IEC) on all matters of electrotechnical standardization.

International Standards are drafted in accordance with the rules given in the ISO/IEC Directives, Part 2.

The main task of technical committees is to prepare International Standards. Draft International Standards adopted by the technical committees are circulated to the member bodies for voting. Publication as an International Standard requires approval by at least 75 % of the member bodies casting a vote.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO shall not be held responsible for identifying any or all such patent rights.

ISO 26262-5 was prepared by Technical Committee ISO/TC 22, *Road vehicles*, Subcommittee SC 3, *Electrical and electronic equipment*.

ISO 26262 consists of the following parts, under the general title *Road vehicles — Functional safety*:

- Part 1: Vocabulary

- Part 2: Management of functional safety

- Part 3: Concept phase

- Part 4: Product development: system level

- Part 5: Product development: hardware level

- Part 6: Product development: software level

- Part 7: Production and operation

- Part 8: Supporting processes

- Part 9: ASIL-oriented and safety-oriented analyses

- Part 10: Guideline on ISO 26262

# Introduction

ISO 26262 is the adaptation of IEC 61508 to comply with needs specific to the application sector of E/E systems within road vehicles.

This adaptation applies to all activities during the safety lifecycle of safety-related systems comprised of electrical, electronic, and software elements that provide safety-related functions.

Safety is one of the key issues of future automobile development. New functionality not only in the area of driver assistance but also in vehicle dynamics control and active and passive safety systems increasingly touches the domain of safety engineering. Future development and integration of these functionalities will even strengthen the need of safe system development processes and the possibility to provide evidence that all reasonable safety objectives are satisfied.

With the trend of increasing complexity, software content and mechatronic implementation, there are increasing risks from systematic failures and random hardware failures. ISO 26262 includes guidance to avoid these risks by providing feasible requirements and processes.

System safety is achieved through a number of safety measures, which are implemented in a variety of technologies (for example: mechanical, hydraulic, pneumatic, electrical, electronic, programmable electronic etc). Although ISO 26262 is concerned with E/E systems, it provides a framework within which safety-related systems based on other technologies can be considered.

ISO 26262:

- provides an automotive safety lifecycle (management, development, production, operation, service, decommissioning) and supports tailoring the necessary activities during these lifecycle phases;

- provides an automotive specific risk-based approach for determining risk classes (Automotive Safety Integrity Levels, ASILs);

- uses ASILs for specifying the item's necessary safety requirements for achieving an acceptable residual risk; and

- provides requirements for validation and confirmation measures to ensure a sufficient and acceptable level of safety being achieved.

Functional safety is influenced by the development process (including such activities as requirements specification, design, implementation, integration, verification, validation and configuration), the production and service processes and by the management processes.

Safety issues are intertwined with common function-oriented and quality-oriented development activities and work products. ISO 26262 addresses the safety-related aspects of the development activities and work products.

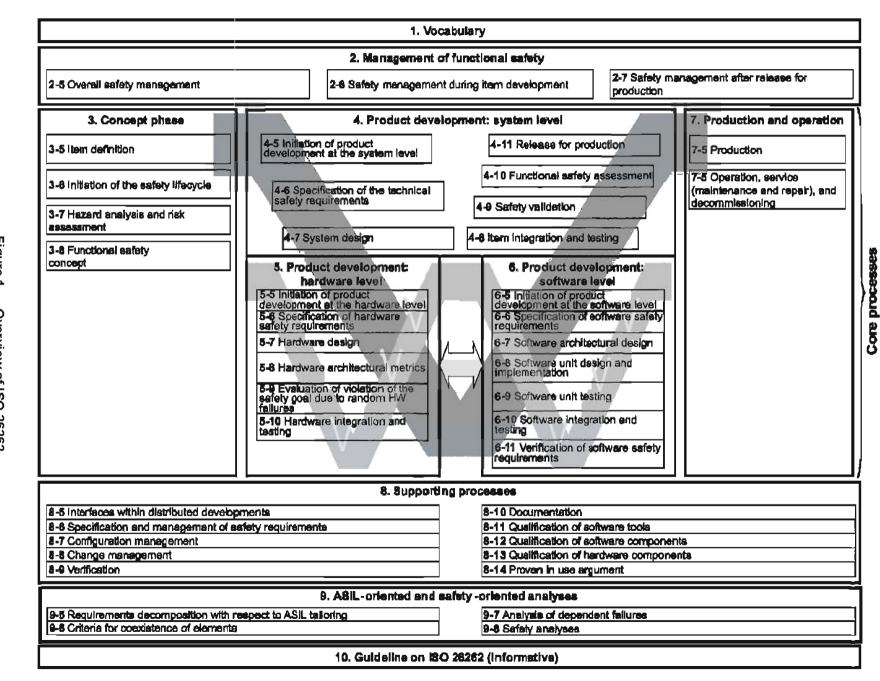

Figure 1 shows the overall structure of ISO 26262. ISO 26262 is based upon a V-Model as a reference process model for the different phases of product development. The shaded "V"s represents the relations between ISO 26262-3, ISO 26262-4, ISO 26262-5, ISO 26262-6 and ISO 26262-7.

elektronische Auslegestelle-Beuth-SNV shop Schweizer.Normen-Vereinigung ein Joint Venture

Externe ‼∧

Externe elektronische Auslegestelle Beuth-SNV shop Schweizer.Nc

# Road vehicles — Functional safety — Part 5: Product development: hardware level

# 1 Scope

ISO 26262 is intended to be applied to safety-related systems that include one or more E/E systems and that are installed in series production passenger cars with a max gross weight up to 3,5 t. ISO 26262 does not address unique E/E systems in special purpose vehicles such as vehicles designed for drivers with disabilities. Systems developed prior to the publication date of ISO 26262 are exempted from the scope.

ISO 26262 addresses possible hazards caused by malfunctioning behaviour of E/E safety-related systems including interaction of these systems. It does not address hazards as electric shock, fire, smoke, heat, radiation, toxicity, flammability, reactivity, corrosion, release of energy, and similar hazards unless directly caused by malfunctioning behaviour of E/E safety-related systems.

ISO 26262 does not address the nominal performance of E/E systems, even if dedicated functional performance standards exist for these systems (for example active and passive safety systems, brake systems, ACC).

This part of ISO26262 specifies the requirements on product development at the hardware level. These include requirements on the initiation of product development at the hardware level, the specification of the hardware safety requirements, hardware design, hardware architectural metrics, and evaluation of violation of the safety goal due to random hardware failures and hardware integration and testing.

# 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

| ISO 26262-1: — <sup>1</sup> Road vehicles – Functional Safety — Part 1: Vocabulary                                 |  |

|--------------------------------------------------------------------------------------------------------------------|--|

| ISO 26262-2: — <sup>1</sup> Road vehicles – Functional Safety — Part 2: Management of functional safety            |  |

| ISO 26262-4: — <sup>1</sup> Road vehicles – Functional Safety — Part 4: Product development: system level          |  |

| ISO 26262-6: — <sup>1</sup> Road vehicles – Functional Safety — Part 6: Product development: software level        |  |

| ISO 26262-8: — <sup>1</sup> Road vehicles – Functional Safety — Part 8: Supporting processes                       |  |

| ISO 26262-9: — <sup>1</sup> Road vehicles – Functional Safety — Part 9: ASIL-oriented and safety-oriented analyses |  |

|                                                                                                                    |  |

<sup>1</sup> To be published

# 3 Terms and definitions

For the purposes of this document, the terms, definitions and abbreviated terms given in ISO 26262-1 apply.

# **4** Requirements for compliance

#### 4.1 General requirements

When claiming compliance with ISO 26262, each requirement shall be complied with, unless one of the following applies:

- 1) Tailoring in accordance with ISO 26262-2 has been planned and shows that the requirement does not apply.

- 2) A rationale is available that the non-compliance is acceptable and the rationale has been assessed in accordance with ISO 26262-2.

Information marked as a "NOTE" is only for guidance in understanding, or for clarification of, the associated requirement and shall not be interpreted as a requirement itself.

#### 4.2 Interpretations of tables

Tables may be normative or informative depending on their context.

The different methods listed in a table contribute to the level of confidence that the corresponding requirement shall apply.

Each method in a table is either a consecutive entry (marked by a sequence number in the leftmost column, e.g. 1, 2, 3) or an alternative entry (marked by a number followed by a letter in leftmost column, e.g., 2a, 2b, 2c).

For consecutive entries all methods are recommended in accordance with the ASIL. If methods other than those listed are to be applied a rationale shall be given that they comply with the corresponding requirement.

For alternative entries an appropriate combination of methods shall be applied in accordance with the ASIL, independently of whether they are listed in the table or not. If methods are listed with different degrees of recombination for an ASIL the higher one should be preferred. A rationale shall be given that the selected combination of methods complies with the corresponding requirement. If all highly recommended methods listed for a particular ASIL are selected a rationale needs not to be given.

For each method, the degree of recommendation to use the corresponding method depends on the ASIL and is categorized as follows:

"++" The method is highly recommended for this ASIL.

"+" The method is recommended for this ASIL.

"o" The method has no recommendation for or against its usage for this ASIL.

#### 4.3 ASIL dependent requirements and recommendations

The requirements or recommendations of each subclause shall apply to ASIL A, B, C and D, if not stated otherwise. These requirements and recommendations refer to the ASIL of the safety goal. If ASIL decomposition has been performed at an earlier stage of development in accordance with ISO 26262-9:— Clause 54 the ASIL resulting from the decomposition will apply.

If an ASIL is given in parentheses, the corresponding subclause shall be read as a recommendation rather than a requirement for this ASIL.

#### 5 Initiation of product development at the hardware level

#### 5.1 Objectives

The objective of the initiation of the product development for the hardware is to determine and plan the functional safety activities during the individual sub-phases of hardware development. This also includes the necessary supporting processes described in ISO 26262-8.

This planning of hardware-specific safety activities is included in the safety plan.

#### 5.2 General

Integration of the following activities is crucial for the product development at hardware level:

- Hardware implementation of the technical safety concept;

- Analysis of potential faults and their effects; and

- Coordination with software development.

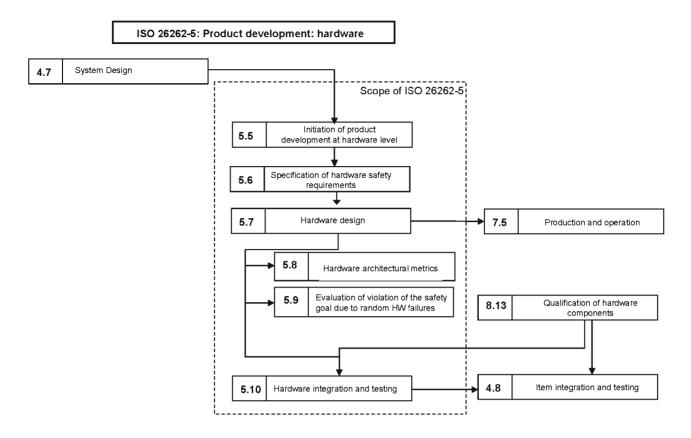

The necessary activities and processes are planned. Figure 2 illustrates how the different activities are carried out in order to comply with the requirements of this part, and how these activities are integrated in the whole ISO 26262 frameworks.

NOTE Requirements of this part on hardware are applicable both to non-programmable and programmable elements such as ASIC, FPGA, PLD. Furthermore, for programmable electronic elements, requirements in ISO 26262-6:—, ISO 26262-8:—, Clause 11 and ISO 26262-8:—, Clause 12 are applicable.

#### Figure 2 — Informative reference phase model for the development of a safety-related item

#### 5.3 Inputs to this clause

#### 5.3.1 Prerequisites

The following information shall be available:

- Overall project plan (refined) (see ISO 26262-4:—, 5.5.1)

- Safety plan (refined) (see ISO 26262-4:—, 5.5.2)

- Item integration and testing plan (refined) (see ISO 26262-4:—, 7.5.4)

#### 5.3.2 Further supporting information

None

#### 5.4 Requirements and recommendations

**5.4.1** The activities for the product development of the hardware elements of the item described in Clause 6 to Clause 10 shall be planned and included in the safety plan consistently with the planning of activities in ISO 26262-6.

NOTE The project plan and safety plan as work products of ISO 26262-2:—, Clause 6 and ISO 26262-4:—, Clause 5 and ISO 26262-4:—, Clause 6 are detailed in this Clause 5.

**5.4.2** The safety plan shall specify the activities to determine appropriate methods and measures to be used during the design to ensure the functional safety of the hardware elements of the item.

**5.4.3** The hardware development process for the hardware of the item, including lifecycle phases, methods, and tools, shall be consistent across all subphases of the hardware lifecycle and compatible with system and software lifecycles, such that required data can be transformed correctly.

#### 5.5 Work products

**5.5.1** Overall project plan (refined) resulting from requirements 5.4.1 to 5.4.3.

**5.5.2** Safety plan (refined) resulting from requirements 5.4.1 to 5.4.3.

#### 6 Specification of hardware safety requirements

#### 6.1 Objectives

The first objective of this clause is to make available a consistent and complete hardware specification that will be applied to the hardware of the item or element under consideration. The requirements of this specification are hardware safety requirements.

The second objective is to verify that the hardware safety requirements are consistent with the technical safety concept.

A further objective of this phase is to detail the hardware-software interface (HSI) requirements initiated in ISO 26262-4:—, Clause 7.

#### 6.2 General

The hardware safety requirements to be defined can be derived from several sources:

- Technical safety concept specified in ISO 26262-4:—, Clause 7 (including relevant environmental conditions and conditions of operation)

- Software safety requirements specified in ISO 26262-6:—, Clauses 6 and 7.

#### 6.3 Inputs to this clause

#### 6.3.1 Prerequisites

The following information shall be available:

- Overall project plan (refined) (see 5.5.1)

- Safety plan (refined) (see 5.5.2)

- Technical safety concept (see ISO 26262-4:—, 7.5.1)

- System design specification (see ISO 26262-4:—, 7.5.2)

- Hardware software interface specification (see ISO 26262-4:—, 7.5.6)

#### 6.3.2 Further supporting information

The following information may be considered:

— Software safety requirements specification (see ISO 26262-6:—, 6.5.1)

#### 6.4 Requirements and recommendations

**6.4.1** A consistent and complete hardware safety requirements specification for the hardware of the element under consideration shall be derived from the technical safety requirements allocated to hardware.

**6.4.2** The hardware safety requirements specification shall include each hardware requirement that relates to safety including:

b) The hardware safety requirements of safety mechanisms to control internal failures of the hardware of the element, with their relevant attributes;

EXAMPLE 1 These attributes can be for instance the timing and detection abilities of a watchdog.

c) The hardware safety requirements of safety mechanisms to make the element under consideration tolerant to failures external to the element, with their relevant attributes

EXAMPLE 2 This includes, for instance, the functional behaviour required for an ECU in the event of an external failure, such as an open-circuit in the input of the ECU.

d) The hardware safety requirements of safety mechanisms to comply with the safety requirements of other elements

EXAMPLE 3 diagnoses of sensors or actuators.

e) The hardware safety requirements of safety mechanisms to detect and signal internal or external failures

NOTE 1 The hardware safety requirements described in bullet d) include safety mechanisms to prevent faults from being latent.

NOTE 2 The hardware safety requirements, described in each bullet, include the characteristics needed to ensure the effectiveness of the above safety mechanisms.

EXAMPLE 4 This includes for instance the specified fault reaction time for the hardware part of a safety mechanism, so as to be consistent with the fault tolerant time interval.

NOTE 3 The hardware safety requirements include requirements on the target values as given by requirements 6.4.3 and 6.4.4, as well as requirements for avoidance of specific behaviour. An example of an avoidance requirement is that a particular sensor shall not produce wrong output, with an ASIL attached to this requirement.

**6.4.3** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3: The target values specified in ISO 26262-4:—, Clause 7 for the metrics of Clause 8 shall be considered when showing compliance of the hardware of the item.

NOTE This activity can include a split of target values in the case of a distributed development in accordance with ISO 26262-8:—, Clause 5.

**6.4.4** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3: The target values specified in ISO 26262-4:—, Clause 7 for the procedures of Clause 9 shall be considered when showing compliance of the hardware of the item.

NOTE This activity can include a split of target values in the case of a distributed development in accordance with ISO 26262-8:—, Clause 5.

6.4.5 The hardware safety requirements shall be specified in accordance with ISO 26262-8:--, Clause 6.

**6.4.6** The criteria for qualification and testing of the hardware of the item or element shall be specified in accordance with Clause 10, and ISO 26262-8:—, Clause 13. This shall include environmental conditions (temperature, vibration, EMC, etc), specific operational environment and component specific requirements.

**6.4.7** The hardware safety requirements shall ensure compliance with the fault tolerant time interval for safety mechanisms as specified in ISO 26262-4:—, 6.4.9.

**6.4.8** The hardware safety requirements shall ensure compliance with the multiple point fault detection interval as specified in ISO 26262-4:—, 6.4.10.2.

NOTE 1 For ASILC and D safety goals: if the corresponding safety concept does not prescribe specific values, the multiple point fault detection intervals can be specified to be equal or lower than the item's "power-up to power-down" cycle.

NOTE 2 Appropriate multiple point fault detection intervals can also be justified by the quantitative analysis of occurrence of random hardware failures, if they are considered in the calculation model (see Clause 9).

6.4.9 The hardware safety requirements shall be verified in accordance with Table 1 in order to show:

- a) Consistency with the technical safety concept, the system design specification and the hardware specifications;

- b) Completeness with respect to the technical safety requirements allocated to the hardware element under consideration,

- c) Correctness and accuracy;

- d) Compliance with the requirements of this Clause.

| Methods |                                             |    | ASIL |    |    |  |  |

|---------|---------------------------------------------|----|------|----|----|--|--|

|         | methods                                     |    |      | С  | D  |  |  |

| 1a      | Walkthrough of hardware safety requirements | ++ | +    | 0  | 0  |  |  |

| 1b      | Inspection of hardware safety requirements  | +  | ++   | ++ | ++ |  |  |

#### Table 1 — Verification of the hardware safety requirements

#### 6.4.10 Hardware-software interface (HSI) specification

**6.4.10.1** The hardware-software interface specification initiated in ISO 26262-4:—, Clause 7 shall be detailed down to a level allowing correct control and usage by software.

**6.4.10.2** The persons responsible for hardware and software development shall jointly verify the adequacy of the refined HSI specification.

#### 6.5 Work products

**6.5.1** Hardware safety requirements specification (including test and qualification criteria) resulting from requirements 6.4.1, 6.4.2 and 6.4.6.

- **6.5.2** Hardware architectural metrics requirements resulting from requirement 6.4.3.

- 6.5.3 Random hardware failure requirements resulting from requirement 6.4.4.

- 6.5.4 Hardware-software interface specification (refined) resulting from requirements 6.4.10.1, 6.4.10.2.

- 6.5.5 Hardware safety requirements verification report resulting from requirement 6.4.9.

#### 7 Hardware design

#### 7.1 Objectives

The first objective of this clause is to design the hardware with respect to the system design specification and the hardware safety requirements.

The second objective of this clause is to verify the hardware design against the system design specification and the hardware safety requirements.

# 7.2 General

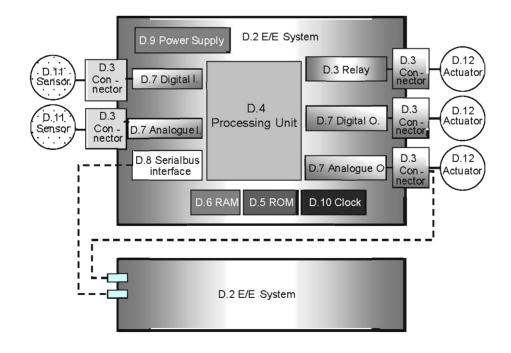

Hardware design includes hardware architectural design and hardware detailed design. Hardware architectural design represents all hardware components and their interactions with one another. Hardware detailed design is at the level of electrical schematics representing the interconnections between hardware parts composing the hardware components.

In order to develop a single hardware design, the design complies with both hardware safety requirements as well as non-safety-related requirements, i.e. in this phase safety-related and non safety-related requirements are handled within one development process.

#### 7.3 Inputs to this clause

#### 7.3.1 Prerequisites

The following information shall be available:

- Hardware safety requirements specification (see 6.5.1)

- Hardware software interface specification (refined) (see 6.5.5)

- System design specification (ISO 26262-4:—, 7.5.2)

- Overall project plan (refined) (see 5.5.1)

- Safety plan (refined) (see 5.5.2)

#### 7.3.2 Further supporting information

The following information may be considered:

— Software safety requirements specification (ISO 26262-6:—, 6.5.1)

#### 7.4 Requirements and recommendations

#### 7.4.1 Requirements for hardware architectural design

7.4.1.1 The hardware architecture shall implement the hardware safety requirements defined in Clause 6.

**7.4.1.2** Each hardware element shall inherit the highest ASIL from the hardware safety requirements that it implements.

**7.4.1.3** If ASIL decomposition is applied to the hardware architecture, it shall be applied in accordance with ISO 26262-9:—, Clause 5.

**7.4.1.4** If a hardware element is made of sub-elements with different ASILs assigned, or of non-safety-related sub-elements and safety-related sub-elements, then each of these shall be treated in accordance with the highest ASIL, unless the criteria for coexistence, in accordance with ISO 26262-9:—, Clause 6, are met.

**7.4.1.5** The traceability between the hardware safety requirements and their implementation shall be maintained down to hardware components.

NOTE This means that the traceability is not required down to hardware detailed design and no ASILs are assigned to hardware parts.

**7.4.1.6** In order to achieve an adequate level of granularity and to avoid failures resulting from high complexity, the following modular design properties shall be considered:

- 1) This requirement applies to ASIL (A, B, C, and D), in accordance with 4.3: Hierarchical design;

- 2) This requirement applies to ASIL A, B, C, and D, in accordance with 4.3: Precisely defined interfaces of safety-related hardware components;

- 3) This requirement applies to ASIL (A, B, C), and D, in accordance with 4.3: Avoidance of unnecessary complexity of interfaces;

- 4) This requirement applies to ASIL (A, B), C, and D, in accordance with 4.3: Avoidance of unnecessary complexity of hardware components;

- 5) This requirement applies to ASIL (A, B, C, and D), in accordance with 4.3: Maintainability (service);

- 6) This requirement applies to ASIL (A, B), C, and D, in accordance with 4.3: Testability.

- NOTE Testability includes testability during development and operation.

**7.4.1.7** Well-trusted hardware components should be considered for re-use, in accordance with ISO 26262-4:---, 7.4.3.4.

NOTE The aim of the use of well-trusted hardware components is to avoid unknown and first time failures. However, it is not intended to limit the application of new technology where there is a benefit and the safety properties of the new technology have been analysed to a level of detail appropriate for the assigned ASIL.

**7.4.1.8** Non-functional causes for failure of a safety-related hardware component shall be considered during hardware architectural design, including the following influences, if applicable: temperature, vibrations, water, dust, EMI, cross-talks originating either from other hardware components of the hardware architecture or from its environment.

#### 7.4.2 Hardware detailed design

7.4.2.1 In order to avoid common design faults, lessons learned, if applicable, shall be used.

**7.4.2.2** Non-functional causes for failure of a safety-related hardware part shall be considered during hardware detailed design, including the following influences, if applicable: temperature, vibrations, water, dust, EMI, noise factor, cross-talks originating either from other hardware parts of the hardware component or from its environment.

**7.4.2.3** The hardware detailed design shall ensure that hardware parts are used within their environmental and operational specifications.

7.4.2.4 Robust design principles shall be considered.

#### 7.4.3 Safety Analyses

**7.4.3.1** Safety analysis of hardware architectural and detailed design to determine effects and causes of faults shall be applied in accordance with Table 2 and ISO 26262-9:—, Clause 8.

NOTE 1 The purpose of these analyses is first to support the specification of the hardware architectural and detailed design. The same analyses can then be used for verification of the hardware design (see 7.4.4).

NOTE 2 At this stage, qualitative analyses might be appropriate and sufficient.

|                                                          | Methods                                                   | ASIL |    |    |    |  |  |  |

|----------------------------------------------------------|-----------------------------------------------------------|------|----|----|----|--|--|--|

|                                                          | Methods                                                   |      | В  | С  | D  |  |  |  |

| 1                                                        | Deductive analysis <sup>a</sup>                           | 0    | +  | ++ | ++ |  |  |  |

| 2                                                        | Inductive analysis <sup>b</sup>                           | ++   | ++ | ++ | ++ |  |  |  |

| <sup>a</sup> A typical deductive analysis method is FTA. |                                                           |      |    |    |    |  |  |  |

| b                                                        | <sup>b</sup> A typical inductive analysis method is FMEA. |      |    |    |    |  |  |  |

#### Table 2 — Hardware design safety analysis

NOTE The level of detail of the analysis is chosen in an appropriate manner.

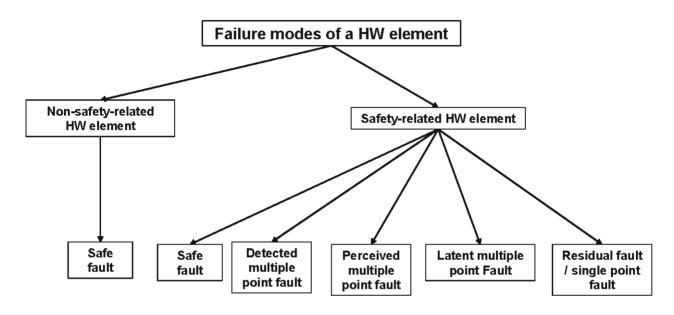

**7.4.3.2** This requirement applies to ASIL (B,) C, D of the safety goal, in accordance with 4.3: For each safety-related hardware element the safety analyses shall identify the following for the safety goal under consideration:

a) Safe faults;

- b) Single point faults or residual faults;

- c) Dual point faults (either perceived, detected or latent).

NOTE 1 Multiple point faults of higher order than two are considered if shown relevant in the safety concept.

NOTE 2 The safety analysis is done at a feasible level with respect to the type of element.

NOTE 3 The intention of the identification of dual point faults is not to require a systematic analysis of every possible combination of 2 hardware faults but at least to consider combinations that derives from the safety concept (for instance the combination of 2 faults where one fault affects a safety-related element and another fault affects the corresponding safety mechanism intended to achieve or maintain a safe state).

**7.4.3.3** This requirement applies to ASIL (B,) C, D of the safety goal, in accordance with 4.3. Evidence of effectiveness of the safety mechanisms to avoid single point faults shall be made available.

For that purpose:

- a) Evidence of the ability of the safety mechanisms to maintain a safe state or to switch safely into a safe state shall be made available (in particular, appropriate failure mitigation ability within fault tolerant time interval); and

- b) Diagnostic coverage shall be evaluated.

NOTE 1 A fault cannot be considered covered if its diagnostic test interval plus the fault reaction time of the associated safety mechanism is higher than the relevant fault tolerant time interval.

NOTE 2 A FMEA can be used to structure the justification.

**7.4.3.4** This requirement applies to ASIL (B,) C, D of the safety goal, in accordance with 4.3. Evidence of effectiveness of the safety mechanisms to avoid multiple point faults remaining latent shall be made available.

For that purpose:

- a) Evidence of the failure detection and the ability to signal to the driver within the acceptable multiple point fault interval for latent faults shall be made available in order to determine which faults remain latent and which faults are not latent; and

- b) Diagnostic coverage with regard to latent multiple point faults shall be evaluated.

NOTE 1 A fault cannot be considered covered if its diagnostic test interval plus the fault reaction time of the associated safety mechanism is higher than the relevant multiple point fault interval for latent faults.

NOTE 2 A FMEA can be used to structure the justification.

**7.4.3.5** In the case of independence requirements, evidence of the compliance of the hardware design shall be made available by an analysis of dependent failures in accordance with ISO 26262-9:—, Clause 7 applied on the hardware design.

**7.4.3.6** If new hazards introduced by the hardware design are identified, they shall be introduced and evaluated in the hazard analysis and risk assessment in accordance with the change management process in ISO 26262-8:—, Clause 8.

NOTE Newly identified hazards, not already reflected in a safety goal, are usually non-functional hazards. If those non-functional hazards are outside the scope of ISO 26262 then it is recommended that they are annotated in the hazard analysis and risk assessment with the following statement "No ASIL is assigned to this hazard as it is not within the scope of ISO 26262". However, an ASIL is allowed for reference purposes.

#### 7.4.4 Verification of hardware design

**7.4.4.1** The hardware design shall be verified for compliance and completeness with regard to the hardware safety requirements. To achieve this, the methods listed in Table 3 shall be considered:

|                                                                                                                                                        | Methods                                                                                                                                                                   | ASIL      |           |         |         |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|---------|---------|--|

|                                                                                                                                                        | Methods                                                                                                                                                                   | A         | В         | С       | D       |  |

| 1a                                                                                                                                                     | Hardware design inspection <sup>a</sup>                                                                                                                                   | +         | +         | ++      | ++      |  |

| 1b                                                                                                                                                     | Hardware design walkthrough <sup>a</sup>                                                                                                                                  | ++ ++ 0   |           | 0       |         |  |

| 2                                                                                                                                                      | Safety analyses                                                                                                                                                           | See 7.4.3 |           |         |         |  |

| 3a                                                                                                                                                     | Emulation by simulation <sup>b</sup>                                                                                                                                      | 0         | +         | +       | +       |  |

| 3b                                                                                                                                                     | Development by prototype hardware                                                                                                                                         | 0         | +         | +       | +       |  |

| <sup>a</sup> Methods 1a and 1b serve as a check of the complete and correct implementation of the technical safety requirements in the hardware design |                                                                                                                                                                           |           |           |         |         |  |

|                                                                                                                                                        | Nethods 3a and 3b serve as a check of particular points of hardware design for wh<br>ot considered sufficient. It can be used among other as a fault injection technique. | nich ana  | lytical m | nethods | 1 and 2 |  |

| Table 3 — Hardware o | design | verification |

|----------------------|--------|--------------|

|----------------------|--------|--------------|

**7.4.4.2** If it is revealed, during hardware design, that the implementation of any hardware safety requirement is not feasible, request for changes shall be issued in accordance with the change management process in ISO 26262-8:—, Clause 8.

#### 7.4.5 Requirements for production and operation

**7.4.5.1** Safety-related special characteristics shall be specified if safety analyses have shown them to be relevant. Attributes of safety-related special characteristics shall include:

a) The verification measures for production and operation

b) The acceptance criteria for the measures.

**7.4.5.2** Instructions for assembly, disassembly and decommissioning of safety-related hardware elements shall be issued, if these operations can impact the safety concept.

**7.4.5.3** The traceability of safety-related hardware elements shall be ensured.

NOTE This can include adequate labelling.

**7.4.5.4** Instructions for maintenance of safety-related hardware elements shall be issued, if maintenance can impact the safety concept.

#### 7.5 Work products

- 7.5.1 Hardware design specification resulting from requirements 7.4.1, 7.4.2.

- **7.5.2** Hardware safety analysis report resulting from requirement 7.4.3.

- **7.5.3** Hardware design verification report resulting from requirement 7.4.4.

- 7.5.4 Requirements for production and operation resulting from requirement 7.4.5.

#### 8 Hardware architectural metrics

#### 8.1 Objectives

The objective of this clause is to evaluate the hardware architecture of the item against the requirements for fault handling as represented by the hardware architectural metrics.

#### 8.2 General

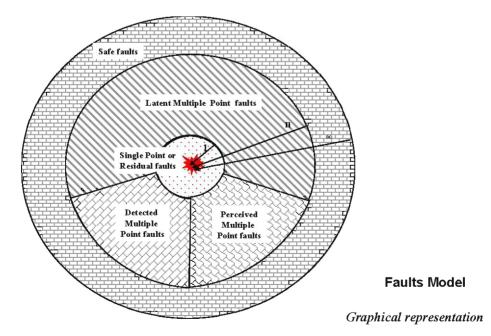

This clause describes two hardware architectural metrics for assessment of the effectiveness of the system architecture to cope with hardware random failures.

These metrics and associated target values apply to the overall hardware architecture of the item and are complementary to the residual risk assessment described in Clause 9.

The scope of this clause is limited to random hardware failures of the item. The parts considered in the analyses are the electrical and electronic parts. For electromechanical parts, only the electrical failure modes and failure rate are considered.

Compliance with the target figures prescribed for the hardware architectural metrics is achieved for each safety goal in which the item is involved.

Some or all of the applicable safety goals can be considered together for the determination of the metrics; but in this case the metrics' targets to be considered are those of the safety goal with the highest ASIL. These hardware architectural metrics are defined to achieve the following objectives:

- Be objectively assessable: metrics are verifiable, unambiguous, reproducible and precise enough to differentiate between different architectures;

- Support evaluation of the final design (the precise calculations are done with the detailed hardware design);

- Make available ASIL dependent pass/fail criteria;

- Reveal whether or not the coverage of the safety mechanisms, to control hardware faults in the E/E architecture, is sufficient;

- Reveal if the coverage of the safety mechanisms to prevent risk from latent multiple point faults in the hardware E/E architecture is sufficient;

- Address single point faults, residual faults and latent multiple point faults;

- Be robust concerning uncertainty of hardware failures rates;

- Be limited to safety-related elements; and

Be usable on different elements levels, e.g. target values can be assigned at supplier's perimeter level for supplier's interfaces.

#### 8.3 Inputs of this clause

#### 8.3.1 Prerequisites

The following information shall be available:

- Hardware safety requirements specification (see 6.5.1)

- Hardware architectural metrics requirements (see 6.5.2)

- Hardware design specification (see 7.5.1)

- Hardware safety analysis report (see 7.5.2)

#### 8.3.2 Further supporting information

The following information may be considered:

- Technical safety concept (ISO 26262-4:—, 7.5.1)

- System design specification (ISO 26262-4:—, 7.5.2)

#### 8.4 Requirements and recommendations

#### 8.4.1 General

The requirements of this Clause refer only to the ASIL of the safety goal.

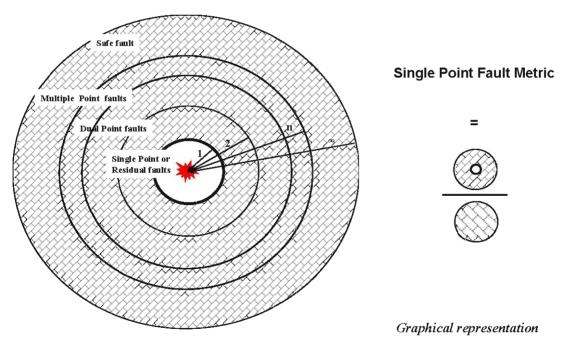

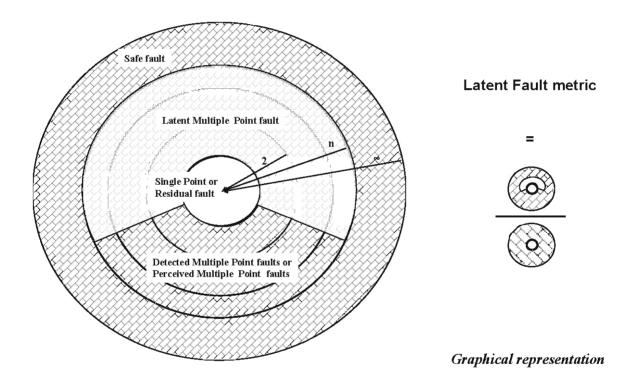

**8.4.2** This requirement applies to ASIL (B), C, and D of the safety goal, in accordance with 4.3: The concepts of diagnostic coverage, single point faults metric and latent fault metric, as defined in Annex C, shall be considered for the following requirements (8.4.3 to 8.4.9).

**8.4.3** This requirement applies to ASIL (B), C, and D of the safety goal, in accordance with 4.3: The coverage of safety-related hardware elements by safety mechanisms shall be estimated with regard to residual faults and with regard to latent multiple point faults.

NOTE For this purpose, the Tables D.1 to D.12 can be used.

**8.4.4** This requirement applies to ASIL (B), C, and D of the safety goal, in accordance with 4.3: The failure rates of safety-related hardware parts shall be estimated in accordance with 9.4.3.6.

**8.4.5** If sufficient evidence of the failure rate used in the calculation of a single point fault or latent multiple point fault cannot be made available, alternative means should be proposed (e.g. add safety mechanisms to detect and control this fault).

**8.4.6** This requirement applies to ASIL (B), C, and D of the safety goal, in accordance with 4.3. For each safety goal, numerical target values for "single point faults metric" and "latent faults metric" shall be based on one of the following sources of reference target values:

a) Derived from the safety hardware architectural metrics calculation applied on similar well-trusted designs; or

NOTE Two similar designs have similar functionalities and similar safety goals with the same associated ASIL.

b) Derived from Annex E.

These numerical targets are intended to:

- Make available design guidance as described in 8.2.

- Make available evidence that the design satisfies the safety goals.

**8.4.7** This requirement applies to ASIL (B), C, and D of the safety goal, in accordance with 4.3. For each safety goal, the overall hardware architecture of the item shall meet the target values of the "single point faults metric.

NOTE 1 The compliance with requirement 8.4.7 can be achieved with the following procedure:

- 1) Prescribe at the hardware element level, appropriate targets sufficient to comply with the metrics' target values given in requirement 8.4.4 assigned to the overall hardware architecture, and

- 2) Make available a rationale for compliance with these targets at the hardware element level.

NOTE 2 If an item contains different kinds of hardware elements with significantly different failure rate levels, compliance with the hardware architectural metrics could only focus on the kind of hardware elements with the highest magnitude of failure rates. (One example where this can be used is for the single point faults metric for which compliance could be achieved by considering the failure rates for failures of wires / fuses / connectors, while disregarding the failure rates of hardware parts with significantly lower failure rates.) The prescription of appropriate metric target values for each kind of hardware helps to avoid this side effect.

NOTE 3 Some or all of the applicable safety goals can be considered together for the determination of the metrics; but in this case the metrics' targets to be considered are those of the safety goal with the highest ASIL.

NOTE 4 If the target is not met, the rationale for how the safety goal is achieved will be available in the safety case.

EXAMPLE A rationale can be the compliance with the state of the art.

**8.4.8** This requirement applies to ASIL (B), C, and D of the safety goal, in accordance with 4.3. For each safety goal, the overall hardware architecture of the item shall meet one of the following targets:

- a) target values of the "latent faults metric";

- b) when each safety mechanism of the item is based on fault detection, DC with regard to Latent Multiple Point Faults of each hardware element with fault(s) that could lead to the unavailability of a safety mechanism (to prevent a fault from violating the safety goal) compliant with the target value given in requirement 8.4.6 for the "latent faults metric" (treated as a diagnostic coverage).

NOTE 1 Approach b) can only be considered when each safety mechanism is based on fault detection. If this condition is not met then approach a) is the only possibility.

NOTE 2 In the case b), a metric is not calculated, only the coverage of the hardware elements by safety mechanisms with regard to latent multiple point faults is evaluated.

NOTE 3 The compliance with requirement 8.4.8 can be achieved with the following procedure:

- 1) Prescribe at the hardware element level, appropriate targets sufficient to comply with the metrics' target values given in requirement 8.4.4 assigned to the overall hardware architecture, and

- 2) Make available a rationale for compliance with these targets at the hardware element level.

NOTE 4 If an item contains different kinds of hardware elements with significantly different failure rate levels, compliance with the hardware architectural metrics could only focus on the kind of hardware elements with the highest magnitude of failure rates. (One example where this can be used is for the single point fault metric for which compliance could be achieved by considering the failure rates for failures of wires / fuses / connectors, while disregarding the failure rates of hardware parts with significantly lower failure rates.) The prescription of appropriate metric target values for each kind of hardware helps to avoid this side effect.

NOTE 5 Some or all of the applicable safety goals can be considered together for the determination of the metrics; but in this case the metrics' targets to be considered are those of the safety goal with the highest ASIL.

NOTE 6 If the target is not met, the rationale for how the safety goal is achieved will be available in the safety case

EXAMPLE A rationale can be the compliance with the state of the art.

**8.4.9** This requirement applies to ASIL (B), C, and D of the safety goal, in accordance with 4.3: A review of the result of the applied methods in 8.4.7 and 8.4.8 shall be performed.

NOTE The careful verification of the denominator for the single point faults metric is to ensure that failure rates of safety-related hardware elements, without any single point fault and residual fault, do not falsify the metric.

#### 8.5 Work products

**8.5.1** Assessment of the effectiveness of the system architecture to cope with the hardware random failures resulting from requirements 8.4.2 to 8.4.9.

**8.5.2** Review report of assessment of the effectiveness of the system architecture to cope with the hardware random failures resulting from requirement 8.4.9.

# 9 Evaluation of violation of the safety goal due to random HW failures

#### 9.1 Objectives

The objective of the requirements in this clause is to make available criteria that can be used in a rationale that the residual risk of safety goal violation, due to random hardware failures of the item, is sufficiently low.

NOTE 'Sufficiently low' means "comparable to accepted risks on similar items already in use".

#### 9.2 General

Two alternative methods are proposed to evaluate whether the residual risk of violation of safety goals is acceptable.

Both methods evaluate the residual risk of violating a safety goal due to single point faults, residual faults, and plausible dual point faults. In this analysis, coverage of safety mechanisms and exposure duration in case of a dual point fault will be considered.

The first method consists of using a probabilistic metric to evaluate violation of the considered safety goal (using for instance quantified FTA) and compares the result of this quantification with a target value.

The second method consists of the individual evaluation of each residual and single point fault and of each dual point failure leading to the violation of the considered safety goal. This analysis method can also be considered to be a cut-set analysis.

The scope of this clause is limited to the random hardware failures of the item. The parts considered in the analyses are the electrical and electronic parts. For electromechanical parts, only the electrical failure modes and failure rate are considered.

#### 9.3 Inputs to this clause

#### 9.3.1 Prerequisites

The following information shall be available:

- Random hardware failure requirements (see 6.5.3);

- Hardware design specification (see 7.5.1);

- Hardware safety analysis report (see 7.5.2).

#### 9.3.2 Further supporting information

The following information may be considered:

- Technical safety concept (ISO 26262-4:—, 7.5.1);

- System design specification (ISO 26262-4:—, 7.5.2);

- Hardware safety requirements specification (see 6.5.1).

#### 9.4 Requirements and recommendations

#### 9.4.1 General

The requirements of this Clause apply to the ASIL of the safety goal.

**9.4.2** This requirement applies to ASIL (B), C and D of the safety goal, in accordance with 4.3: The item shall comply with one of the following sets of requirements:

- a) Requirements 9.4.3;

- b) Requirements 9.4.4.

#### 9.4.3 Probabilistic metric for random hardware failures

**9.4.3.1** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3. Quantitative target values for maximum probability of violation of each safety goal due to hardware random failures as required in ISO 26262-4:—, 7.4.4.3 shall be defined using one of the following sources of reference target values:

a) Derived from quantitative analysis techniques applied on similar well-trusted designs using well known failure rate databases;

NOTE 1 Two similar designs have similar functionalities and similar safety goals with the same associated ASIL.

NOTE 2 The numbers do not have any absolute significance and are only useful to compare a new design with existing ones.

- b) Derived from field data of similar well-trusted designs;

- NOTE 3 In this case, the quantitative values can have an absolute significance.

- c) Derived from Annex G.

These numerical targets are intended to:

- Make available design guidance as described in 9.1.

- Make available evidence that the design satisfies the safety goals.

NOTE 4 These target values described in Annex G might be adapted to fit specific uses of the item (for instance if the item is able to violate the safety goal for durations longer than the typical use of a passenger car).

**9.4.3.2** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3. Target values of requirement 9.4.3.1 shall be expressed in terms of average probability per hour over the operational lifetime of the item.

**9.4.3.3** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3. A quantitative analysis of the hardware architecture shall provide evidence that target values of requirement 9.4.3.1 are achieved. This quantitative analysis shall consider:

- a) Single point faults, residual faults and dual point faults;

- b) The architecture of the item;

- c) The estimated failure rate of each hardware part in any failure modes which would cause a single point fault of the item;

- d) The estimated failure rate of each hardware part with respect to its dual point faults;

- e) The diagnostic coverage of safety-related hardware elements by safety mechanisms;

- f) The exposure duration in case of multiple point faults; and

- g) The remaining dependent failures due to random hardware faults.

NOTE 1 For safety mechanisms using integrated diagnostics Tables D.1 to D.12 can be used to evaluate the coverage rate of these safety mechanisms.

- NOTE 2 Exposure duration starts as soon as the fault can occur and includes:

- The multiple point fault interval associated with each safety mechanism, or the lifetime of the vehicle if the fault is not indicated to the driver (latent multiple point fault);

- The maximum duration of a trip (driver requested to stop in a safe way);

- The average duration until the vehicle is at the workshop for repair (driver alerted to have the vehicle repaired);

So exposure duration depends on the type of monitoring involved (continuous monitoring, periodic self-tests, driver monitoring, no monitoring) and the kind of reaction when the fault has been detected. It can be as short as a few milliseconds in the case of a continuous monitoring triggering a transition to a safe state. It can be as long as the car lifetime when there is no monitoring.

Example of assumptions that the driver will have his (or her) vehicle repaired in the following average vehicle trips:

- 200 vehicle trips for reduction of comfort features;

- 50 vehicle trips for reduction of driving support features;

- 20 vehicle trips for amber warning lights or driving disturbing behaviour;

- One vehicle trip for red warning lights.

Time taken to repair is usually not considered (except to evaluate hazards that can expose maintenance personnel).

The mean duration of a vehicle trip can be considered as being equal to 1h.

NOTE 3 Dependent failures analysis as described in ISO 26262-9:—, Clause 7 is basically a qualitative analysis leading to the suppression or reduction of harmful dependencies.

NOTE 4 Multiple point faults of higher order than two are considered if shown relevant in the safety concept.

NOTE 5 Situations when the item is in power down mode are not included in the calculation of the average probability per hour.

NOTE 6 If the target is not met, the rationale for how the safety goal is achieved will be available in the safety case.

EXAMPLE A rationale can be the compliance with the state of the art.

**9.4.3.4** This requirement applies to ASIL C and D of the safety goal of the safety goal, in accordance with 4.3: A single point fault occurring in a hardware part, shall only be considered acceptable if dedicated measures are taken to ensure the accuracy of its estimated failure rate used in the analysis of 9.4.3.3.

NOTE Dedicated measures can be among others:

- a) Design features such as hardware part over design (e.g. electrical or thermal stress rating) or physical separation (e.g. spacing of contacts on a printed circuit board);

- b) A special sample test of incoming material to reduce the risk of occurrence of this failure mode;

- c) A burn-in test;

- d) A dedicated control plan.

**9.4.3.5** This requirement applies to ASIL C and D of the safety goal, in accordance with 4.3. A residual fault occurring in a hardware part with a diagnostic coverage (with regard to residual faults) lower than 90 %, shall be considered as acceptable only if the corresponding hardware part is dealt with dedicated measures (the note in 9.4.3.4 gives examples of dedicated measures) to justify the failure rate claimed in the analysis of 9.4.3.3.

**9.4.3.6** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3. The estimated failure rates for hardware parts used in the analyses shall be determined either:

a) Using hardware part failure rates data from a recognised industry source;

EXAMPLE Commonly recognised industry sources to determine hardware part failure rate and failure mode distribution are IEC 62380, IEC 61709, MIL HDBK 217 F notice 2, RAC HDBK 217 Plus, NPRD95, EN50129 Annex C, EN 62061 Annex D, RAC FMD97 and MIL HDBK 338.

NOTE 1 The failure rate values given in these databases are generally considered to be pessimistic.

- b) Using statistics based on field returns or tests. In this case, the estimated failure rate should have an adequate confidence level; or

- c) Using expert judgement founded on engineering approach based quantitative and qualitative arguments. Expert judgement is to be exercised in accordance with structured criteria as a basis for this judgement. The criteria are to be set before the estimation of failure rates is made.

NOTE 2 These criteria can consider field experience, testing, reliability analysis, and novelty of design.

NOTE 3 Different sources of failure rates (a, b or c) can be used for the different hardware parts involved in an analysis.

**9.4.3.7** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3. In order to avoid bias in the quantification, if failure rates from multiple sources are combined, they shall be scaled to

be consistent. Scaling is possible if a rationale for the factor between two failure rates sources is available, for instance if sufficient data exists about a "predecessor" system whose failure rate can be considered representative of that expected for the item under consideration.

For the three failure rate sources in 9.4.3.1, a, b and c, let  $T \in \{a, b, c\}$  be the source of failure rate data for the target and let  $\lambda_{representative.T}$  be the calculated overall failure rate for the representative system using T as the data source. For the three failure rate sources in 9.4.3.1, a, b and c, let  $\lambda_{representative.A}$  be the calculated overall failure rate for the representative system using an alternative source of data  $A \in \{a, b, c\}$ . Then A can be employed as a source of failure rate data to calculate targets for an item under consideration based on

*T* if each failure rate using A is multiplied by the scaling factor  $\pi_{T,A} = \frac{\lambda_{representative.T}}{\lambda_{representative.A}}$ , that is,

if  $\lambda_{i,A}$  is a component failure rate obtained from data source A, then  $\pi_{T,A} \times \lambda_{i,A}$  can be used as a component failure rate to calculate a target value based on T.

Combining failure rates from multiple sources is only allowed if the rates can be made consistent.

EXAMPLE From a previous design, calculated failure rates from a data handbook and warrantee data have been obtained. We then know that  $\lambda_{handbook} / \lambda_{warrantee} = \pi$

where  $\lambda_{handbook}$  is the calculated failure rates from a data handbook,

$\lambda_{warrantee}$  is the calculated failure rates from warrantee data and

$\pi$  is the resulting scaling factor.

For instance, an hardware element with  $\lambda_{handbook} = 10^{-8} / h$ , has  $\lambda_{warrantee} = 2 \cdot 10^{-9} / h$ . In this case  $\pi = 10^{-8} / 2 \cdot 10^{-9}$ .

If in a new design, we use the handbook data to determine the failure rates except for one hardware element (hardware element 1) for which we have warrantee data,  $\lambda_{1(handbook)} = \lambda_{1(warrantee)} * \pi$

Where  $\lambda_{1(handbook)}$  is the failure rate of the hardware element 1 using handbook data and

$\lambda_{1(\textit{warrantee})}$  is the failure rate of the hardware element 1 using warrantee data.

For instance, if  $\lambda_{1(warrantee)} = 9 \cdot 10^{-9} / h$ , then  $\lambda_{1(handbook)}$  can be calculated as  $9 \cdot 10^{-9} * (10^{-8}/2 \cdot 10^{-9}) = 4,5 \cdot 10^{-9} / h$

Using this  $\lambda_{1(handbook)}$ , a consistent evaluation of the violation of the safety goal due to random hardware failures can be done.

**9.4.3.8** Table 4 shows an example of combinations of target values and failure rates.

NOTE 1 If the source of data for the target and the new component failure rates is similar, then no scaling is necessary.

NOTE 2 The targets of Annex G are similar to handbook data.

# Table 4 — Example showing combinations of sources of target values and failure rates to produce consistent failure rates for use in calculations.

|                                                                                                                                                            |                              | Data source for Target Value  |                                                 |                                 |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------|-------------------------------------------------|---------------------------------|--|--|

|                                                                                                                                                            |                              | Calculated value<br>9.4.3.1 a | Field data<br>9.4.3.1 b                         | Annex G<br>9.4.3.1 c            |  |  |

| Data source                                                                                                                                                | Std. Database<br>9.4.3.6 a   | (1)                           | $oldsymbol{\pi}_{_{b,a}}	imes \lambda_{_{l,b}}$ | $\lambda_{i,a}$                 |  |  |

| for failure<br>rates of<br>hardware                                                                                                                        | Statistics<br>9.4.3.6 b      | (1)                           | $\lambda_{i,b}$                                 | $\pi_{a,b} 	imes \lambda_{i,b}$ |  |  |

| parts                                                                                                                                                      | Expert judgment<br>9.4.3.6 c | (1)                           | $\pi_{b,c} 	imes \lambda_{b,c}$                 | $\pi_{a,c} 	imes \lambda_{i,c}$ |  |  |

| (1) Failure rates                                                                                                                                          | s should have the sam        | e origin as those used        | to calculate the target va                      | alue                            |  |  |

| NOTE 1 $\pi_{T,A} = \frac{\lambda_{representative.T}}{\lambda_{representative.A}}$ where $\lambda_{representative.X}$ is the collective failure rate for a |                              |                               |                                                 |                                 |  |  |

| system whose data source is X and $\pi_{T,A}$ is the scaling factor between data source T and data source A.                                               |                              |                               |                                                 |                                 |  |  |

| NOTE 2 $\lambda_{i,X}$ is the failure rate of component <i>i</i> using X as a data source                                                                  |                              |                               |                                                 |                                 |  |  |

#### 9.4.4 Evaluation of each remaining cause of violation of safety goals

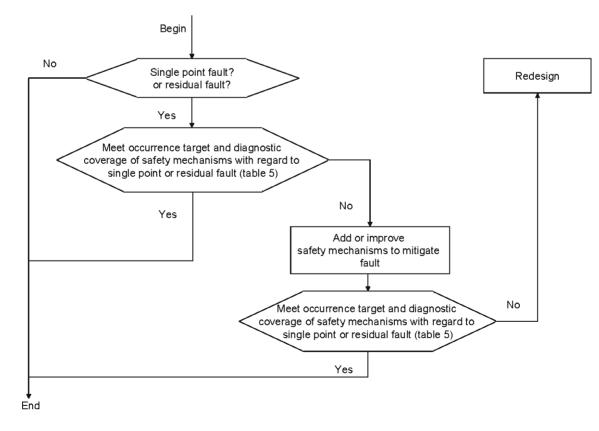

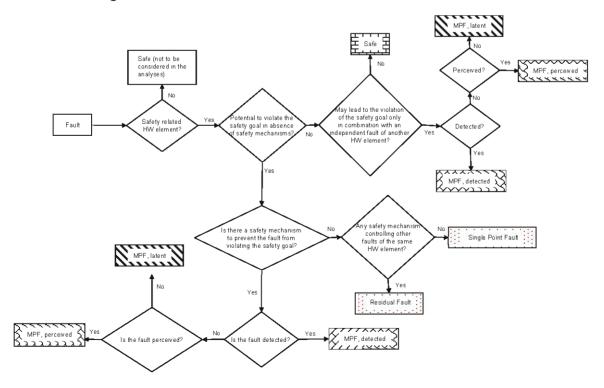

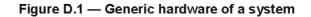

**9.4.4.1** This second method is illustrated by flowchart in Figure 3. Each single point fault is evaluated using criteria on occurrence of the fault. Each residual fault is evaluated using criteria combining occurrence of the fault and efficiency of the safety mechanism.

#### Figure 3 — Evaluation procedure for single point and residual faults

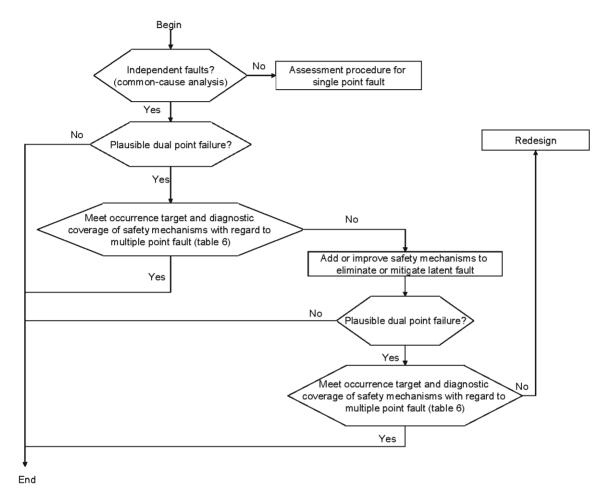

The procedure to be applied for dual point failures is illustrated by flowchart in Figure 4. Each dual point failure is first evaluated regarding its plausibility. A dual point failure is considered not plausible if both faults leading to the failure are detected or perceived in a sufficiently short time with sufficient coverage. If the dual point failure is plausible, the faults causing it are then evaluated using criteria combining occurrence of the fault and coverage of the safety mechanisms.

The evaluation procedures described in Figures 3 and 4 apply to the hardware parts (transistors, integrated circuits, etc) level.

Figure 4 — Evaluation procedure for dual point failures

**9.4.4.2** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3. An individual evaluation of each single point fault, residual fault and dual point failure violating the considered safety goal shall be performed at the hardware part level. This evaluation shall show that each single point fault, residual fault and dual point failure violating the considered safety goal is acceptable in accordance with requirements 9.4.4.3 to 9.4.4.12.

NOTE This analysis can be viewed as review of cut sets where imperfect coverage is treated as a fault.

NOTE 2 Multiple point failures of higher order than two are considered if shown relevant in the safety concept.

**9.4.4.3** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3. The failure rate class ranking for a hardware part failure rate shall be determined as follows:

a) The failure rate corresponding to failure rate class 1 shall be less than the target for ASIL D divided by 100;

NOTE 1 The target values given in Annex G can be used.

NOTE 2 If it can be justified that the number of cut sets is lower than 100, the failure rate class ranking can be adapted – the ASILD target not being divided by 100 anymore. In this case, it is necessary to pay attention in order to keep proper ranking considering the single point faults, residual faults and higher degree cutsets together.

- b) The failure rate corresponding to failure rate class 2 shall be less than ten times the failure rate corresponding to failure rate class 1;

- c) The failure rate corresponding to failure rate class 3 shall be less than a hundred times the failure rate corresponding to failure rate class 1.

NOTE 3 Failure rate class 1, respectively 2 and 3 could be considered to be equivalent to occurrence level 1, respectively 2 and 3 in a FMEA.

- d) The failure rate corresponding to failure rate class *i*, i > 3 shall be less than  $10^{(i-1)}$  times the failure rate corresponding to failure rate class 1.

- NOTE 4 The failure rate class assignment is based upon the hardware part failure rate.

NOTE 5 For the case where a small number of components have failure rates slightly higher than failure rate class i, then the failure rate for failure rate class i can be assigned higher so as to include these components in failure rate class i if the resulting average failure rate corresponds to failure rate class i. A failure rate slightly higher than failure rate class i cannot be equal to or higher than failure rate class i+1.

**9.4.4.4** This requirement applies to ASIL D of the safety goal, in accordance with 4.3. A single point fault occurring in a hardware part shall only be considered as acceptable, if the corresponding hardware part failure rate is ranked failure rate class 1 and dedicated measures are taken to ensure this occurrence level.

NOTE The note under 9.4.3.4 gives examples of dedicated measures.

**9.4.4.5** This requirement applies to ASIL C of the safety goal, in accordance with 4.3: A single point fault occurring in a hardware part shall be considered as acceptable, if the corresponding hardware part failure rate is either:

a) Ranked failure rate class 2 and dedicated measures shall be taken to ensure this failure rate; or

b) Ranked failure rate class 1.

NOTE The note under 9.4.3.4 gives examples of dedicated measures.

**9.4.4.6** This requirement applies to ASIL (B) of the safety goal, in accordance with 4.3: A single point fault occurring in a hardware part shall be considered as acceptable, if the corresponding hardware part failure rate is ranked failure rate class 2 or failure rate class 1.

**9.4.4.7** This requirement applies to ASIL (B,) C, and D of the safety goal, in accordance with 4.3: A residual fault occurring in a hardware part shall be considered as acceptable if the failure rate class ranking and the diagnostic coverage (with regard to residual faults) of the corresponding hardware part comply with the targets given in Table 5. For failure rate classes i, i > 3, a residual fault shall be considered as acceptable if the diagnostic coverage is equal to  $(100\% - 10^{(3-i)})$ .

NOTE 1 Failure rate to be considered is the unmitigated occurrence of the hardware part failure. Therefore, it does not consider effectiveness of safety mechanisms.

NOTE 2 Table 5 specifies the maximum failure rate class allowed given the target ASIL level and the level of diagnostic coverage achieved. Lower failure rate classes are acceptable but not required.

|                                                                                   |   | Diagno                     | Diagnostic Coverage wrt. residual faults |                                                                 |  |  |  |