# High-Definition Multimedia Interface

# Compliance Test Specification Version 1.0

Hitachi, Ltd.

Matsushita Electric Industrial Co., Ltd.

Philips Consumer Electronics, International B.V.

Silicon Image, Inc.

Sony Corporation

Thomson Inc.

**Toshiba Corporation**

# CONFIDENTIAL

# Preface

## <u>Notice</u>

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, NO WARRANTIES OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION, OR SAMPLE.

Hitachi, Ltd., Matsushita Electric Industrial Co., Ltd., Philips Consumer Electronics International B.V., Silicon Image, Inc., Sony Corporation, Thomson Inc., Toshiba Corporation and HDMI Licensing, LLC. disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification.

Copyright © 2001-2002 by Hitachi, Ltd., Matsushita Electric Industrial Co., Ltd., Philips Consumer Electronics International, B.V., Silicon Image, Inc., Sony Corporation, Thomson Inc., and Toshiba Corporation. All rights reserved. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein. Unauthorized use or duplication prohibited. "HDMI" and all associated logos are trademarks of HDMI Licensing, LLC. Third-party trademarks and servicemarks are property of their respective owners.

# **Document Revision History**

- 0.9 2003/06/26 0.9 Release

- 1.0 2003/07/18 1.0 Release

# Table of Contents

| Р | REFA | CE       |                                                    | II   |

|---|------|----------|----------------------------------------------------|------|

|   | Noti | СЕ       |                                                    | . II |

|   | Doci | JMENT F  | Revision History                                   | . II |

| 1 | IN   | TROD     | UCTION                                             | . 1  |

|   | 1.1  | PURP     | OSE AND SCOPE                                      | . 1  |

|   | 1.2  | Norm     | 1ATIVE REFERENCES                                  | . 1  |

|   | 1.3  | ORGA     | NIZATION OF THIS DOCUMENT                          | . 1  |

| 2 | DE   | FINIT    | IONS                                               | . 3  |

|   | 2.1  | Conf     | ORMANCE LEVELS                                     | . 3  |

|   | 2.2  | USAG     | es and Conventions                                 | . 3  |

|   | 2.3  | GLOS     | SARY OF TERMS                                      | . 4  |

|   | 2.4  | ACRO     | NYMS AND ABBREVIATIONS                             | . 5  |

| 3 | 01   | /ERVII   | EW                                                 | . 6  |

| 4 | ТЕ   | ST EO    | UIPMENT                                            | . 7  |

|   | 4.1  | -        | EQUIPMENT OVERVIEW                                 |      |

|   | 4.1  | .1 1     | Required Capabilities versus Recommended Equipment | . 7  |

|   | 4.1  |          | Analyzers and Generators                           |      |

|   | 4.1  | .3       | Simultaneous Test Case Execution                   | . 7  |

|   | 4.2  | Test     | Equipment Requirements                             | . 7  |

|   | 4.2  | 2.1 1    | Electrical Testing                                 | . 7  |

|   | 2    | 4.2.1.1  | Test Point Access Boards                           | . 7  |

|   | 2    | 4.2.1.2  | Jitter/Eye Analyzer                                | 12   |

|   | 2    | 4.2.1.3  | 4GHz Digital Oscilloscope                          | 14   |

|   | 2    | 4.2.1.4  | Differential Probe                                 | 15   |

|   | 2    | 4.2.1.5  | Single-Ended Probe                                 | 15   |

|   | 2    | 4.2.1.6  | SMA Cables                                         | 15   |

|   | 2    | 4.2.1.7  | 50 Ohm SMA Terminators                             | 16   |

|   | 2    | 4.2.1.8  | TMDS Signal Generator                              | 16   |

|   | 2    | 4.2.1.9  | Network Analyzer                                   | 17   |

|   | 2    | 4.2.1.10 |                                                    |      |

|   | 4    | 4.2.1.11 | Digital Multi-Meter and Probe                      | 18   |

|   | 2    | 4.2.1.12 | Voltage Meter                                      | 19   |

|                                        | 4.2.1.13                                                                                                                                   | Resistor for HPD Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 19                                                                                                                                 |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                                        | 4.2.1.14                                                                                                                                   | DC power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 19                                                                                                                                 |

|                                        | 4.2.1.15                                                                                                                                   | LCR Meter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 19                                                                                                                                 |

|                                        | 4.2.1.16                                                                                                                                   | HDMI Cable Emulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 20                                                                                                                                 |

| 4                                      | .2.2 (                                                                                                                                     | Connector Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                                                                                                   |

| 4                                      | .2.3 1                                                                                                                                     | EDID Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20                                                                                                                                   |

|                                        | 4.2.3.1                                                                                                                                    | EDID Reader/Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 20                                                                                                                                 |

|                                        | 4.2.3.2                                                                                                                                    | EDID Emulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 21                                                                                                                                 |

|                                        | 4.2.3.3                                                                                                                                    | I <sup>2</sup> C Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 22                                                                                                                                 |

| 4                                      | .2.4 1                                                                                                                                     | Protocol Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                                                                   |

|                                        | 4.2.4.1                                                                                                                                    | Encoding Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 22                                                                                                                                 |

|                                        | 4.2.4.2                                                                                                                                    | Protocol Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 24                                                                                                                                 |

|                                        | 4.2.4.3                                                                                                                                    | TMDS Protocol Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 24                                                                                                                                 |

| 4                                      | .2.5                                                                                                                                       | Iudio/Video Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25                                                                                                                                   |

|                                        | 4.2.5.1                                                                                                                                    | Video Timing Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 25                                                                                                                                 |

|                                        | 4.2.5.2                                                                                                                                    | Video Picture Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 25                                                                                                                                 |

|                                        | 4.2.5.3                                                                                                                                    | Audio Timing Analyzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 26                                                                                                                                 |

|                                        | 4.2.5.4                                                                                                                                    | Audio/Video Protocol Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 27                                                                                                                                 |

|                                        |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                      |

| 5 Т                                    | TESTS – (                                                                                                                                  | CABLE ASSEMBLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 29                                                                                                                                 |

| 5 T<br>5.1                             |                                                                                                                                            | CABLE ASSEMBLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                      |

|                                        | CABL                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 30                                                                                                                                 |

|                                        | CABL<br>Test ID                                                                                                                            | E – MECHANICAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 30<br>. 30                                                                                                                         |

| 5.1                                    | CABL<br>Test ID<br>CABL                                                                                                                    | e – MECHANICAL<br>5-1: Connector Minimum Envelope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30<br>30<br>31                                                                                                                       |

| 5.1                                    | CABL<br>Test ID<br>CABL<br>Test ID                                                                                                         | e – Mechanical<br>5-1: Connector Minimum Envelope<br>e – Electrical : Required Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 30<br>. 30<br>. 31<br>. 31                                                                                                         |

| 5.1                                    | CABL<br>Test ID<br>CABL<br>Test ID<br>Test ID                                                                                              | E – MECHANICAL<br>5-1: Connector Minimum Envelope<br>E – ELECTRICAL : REQUIRED TESTS<br>5-2: Wire Assignment                                                                                                                                                                                                                                                                                                                                                                                                                               | . 30<br>. 30<br>. 31<br>. 31<br>. 33                                                                                                 |

| 5.1<br>5.2                             | CABL<br>Test ID<br>CABL<br>Test ID<br>Test ID<br>CABL                                                                                      | E – MECHANICAL<br>5-1: Connector Minimum Envelope<br>E – ELECTRICAL : REQUIRED TESTS<br>5-2: Wire Assignment<br>5-3: TMDS Data Eye Diagram                                                                                                                                                                                                                                                                                                                                                                                                 | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36                                                                                         |

| 5.1<br>5.2                             | CABL<br>Test ID<br>Test ID<br>Test ID<br>CABL<br>Test ID                                                                                   | E – MECHANICAL<br>5-1: Connector Minimum Envelope<br>E – ELECTRICAL : REQUIRED TESTS<br>5-2: Wire Assignment<br>5-3: TMDS Data Eye Diagram<br>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS                                                                                                                                                                                                                                                                                                                                                 | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36<br>. 36                                                                                 |

| 5.1<br>5.2                             | CABL<br>Test ID<br>Test ID<br>Test ID<br>CABL<br>Test ID<br>Test ID                                                                        | E – MECHANICAL<br>5-1: Connector Minimum Envelope<br>E – ELECTRICAL : REQUIRED TESTS<br>5-2: Wire Assignment<br>5-3: TMDS Data Eye Diagram<br>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS<br>5-4: Intra-Pair Skew                                                                                                                                                                                                                                                                                                                         | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36<br>. 36<br>. 39                                                                         |

| 5.1<br>5.2                             | CABL<br>Test ID<br>Test ID<br>Test ID<br>CABL<br>Test ID<br>Test ID<br>Test ID                                                             | E – MECHANICAL<br>5-1: Connector Minimum Envelope<br>E – ELECTRICAL : REQUIRED TESTS<br>5-2: Wire Assignment<br>5-3: TMDS Data Eye Diagram<br>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS<br>5-4: Intra-Pair Skew<br>5-5: Inter-Pair Skew                                                                                                                                                                                                                                                                                                 | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36<br>. 36<br>. 39<br>. 42                                                                 |

| 5.1<br>5.2                             | CABL<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID                                                          | <ul> <li>E – MECHANICAL</li> <li>5-1: Connector Minimum Envelope</li> <li>E – ELECTRICAL : REQUIRED TESTS</li> <li>5-2: Wire Assignment</li> <li>5-3: TMDS Data Eye Diagram</li> <li>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS</li> <li>5-4: Intra-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-6: Far End Crosstalk</li> </ul>                                                                                                                                                                                                   | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36<br>. 36<br>. 36<br>. 39<br>. 42<br>. 45                                                 |

| 5.1<br>5.2<br>5.3                      | CABL<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID                                               | <ul> <li>E – MECHANICAL</li> <li>5-1: Connector Minimum Envelope</li> <li>E – ELECTRICAL : REQUIRED TESTS</li> <li>5-2: Wire Assignment</li> <li>5-3: TMDS Data Eye Diagram</li> <li>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS</li> <li>5-4: Intra-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-6: Far End Crosstalk</li> <li>5-7: Attenuation</li> <li>5-8: Differential Impedance</li> </ul>                                                                                                                                    | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36<br>. 36<br>. 36<br>. 39<br>. 42<br>. 45<br>. 48                                         |

| 5.1<br>5.2<br>5.3                      | CABL<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID                                    | <ul> <li>E – MECHANICAL</li> <li>5-1: Connector Minimum Envelope</li> <li>E – ELECTRICAL : REQUIRED TESTS</li> <li>5-2: Wire Assignment.</li> <li>5-3: TMDS Data Eye Diagram</li> <li>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS</li> <li>5-4: Intra-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-6: Far End Crosstalk</li> <li>5-7: Attenuation</li> <li>5-8: Differential Impedance</li> </ul>                                                                                                     | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36<br>. 36<br>. 36<br>. 39<br>. 42<br>. 45<br>. 48<br>. 51                                 |

| 5.1<br>5.2<br>5.3                      | CABL<br>Test ID<br>CABL<br>Test ID<br>CABL<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID                    | <ul> <li>E – MECHANICAL</li> <li>5-1: Connector Minimum Envelope</li> <li>E – ELECTRICAL : REQUIRED TESTS</li> <li>5-2: Wire Assignment</li> <li>5-3: TMDS Data Eye Diagram</li> <li>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS</li> <li>5-4: Intra-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-6: Far End Crosstalk</li> <li>5-7: Attenuation</li> <li>5-8: Differential Impedance</li> <li>PLUG AND RECEPTACLE</li> <li>IANICAL TESTS</li> </ul>                                                                                | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36<br>. 36<br>. 36<br>. 36<br>. 36<br>. 42<br>. 48<br>. 48<br>. 51                         |

| 5.1<br>5.2<br>5.3                      | CABL<br>Test ID<br>CABL<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID                            | <ul> <li>E – MECHANICAL</li> <li>5-1: Connector Minimum Envelope</li> <li>E – ELECTRICAL : REQUIRED TESTS</li> <li>5-2: Wire Assignment.</li> <li>5-3: TMDS Data Eye Diagram</li> <li>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS</li> <li>5-4: Intra-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-6: Far End Crosstalk</li> <li>5-7: Attenuation</li> <li>5-8: Differential Impedance</li> </ul>                                                                                                     | . 30<br>. 30<br>. 31<br>. 33<br>. 36<br>. 36<br>. 39<br>. 42<br>. 45<br>. 45<br>. 48<br>. 51<br>. 51                                 |

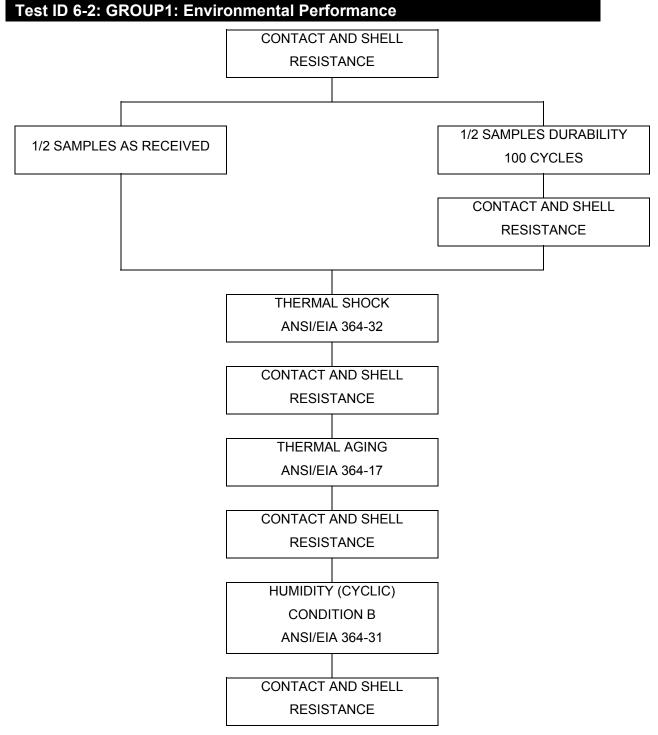

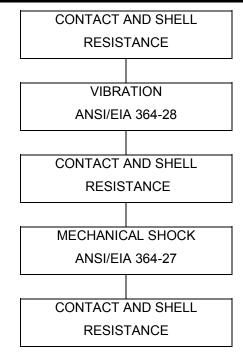

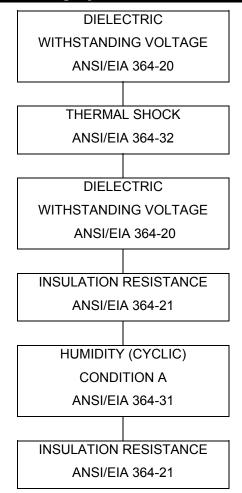

| 5.1<br>5.2<br>5.3<br><b>6 1</b><br>6.1 | CABL<br>Test ID<br>CABL<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br>Test ID<br><b>ESTS –</b> I<br>MECH<br>Test ID | <ul> <li>E – MECHANICAL</li> <li>5-1: Connector Minimum Envelope</li> <li>E – ELECTRICAL : REQUIRED TESTS</li> <li>5-2: Wire Assignment</li> <li>5-3: TMDS Data Eye Diagram</li> <li>E – ELECTRICAL : OPTIONAL (PARAMETRIC) TESTS</li> <li>5-4: Intra-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-5: Inter-Pair Skew</li> <li>5-6: Far End Crosstalk</li> <li>5-7: Attenuation</li> <li>5-8: Differential Impedance</li> <li>PLUG AND RECEPTACLE</li> <li>IANICAL TESTS</li> <li>6-1: Connector Mechanical Specification</li> </ul> | . 30<br>. 30<br>. 31<br>. 31<br>. 33<br>. 36<br>. 36<br>. 36<br>. 39<br>. 42<br>. 45<br>. 45<br>. 45<br>. 45<br>. 51<br>. 51<br>. 52 |

|   |     | Test ID 6-4: GROUP 3 Insulator Integrity                  | 55   |

|---|-----|-----------------------------------------------------------|------|

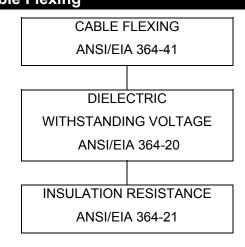

|   |     | Test ID 6-5: GROUP 4 Cable Flexing                        | . 56 |

|   |     | Test ID 6-6: GROUP 5 Electrostatic Discharge              | 56   |

| 7 | Т   | 'ESTS – SOURCE                                            | . 57 |

|   | 7.1 | Source Products Overview                                  | . 57 |

|   | 7.2 | Source – EDID / E-DDC / HPD                               | 58   |

|   |     | Test ID 7-1: EDID-Related Behavior                        |      |

|   | 7.3 | Source – Electrical                                       | 61   |

|   |     | Test ID 7-2: TMDS –V <sub>L</sub>                         | 61   |

|   |     | Test ID 7-3: TMDS – I <sub>OFF</sub>                      | . 64 |

|   |     | Test ID 7-4: TMDS – T <sub>RISE</sub> , T <sub>FALL</sub> | . 66 |

|   |     | Test ID 7-5: TMDS – Over/Undershoot                       | . 69 |

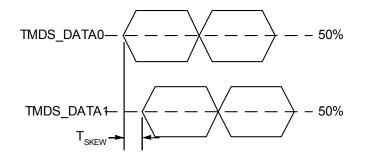

|   |     | Test ID 7-6: TMDS – Inter-Pair Skew                       | . 72 |

|   |     | Test ID 7-7: TMDS – Intra-Pair Skew                       | . 74 |

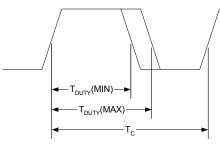

|   |     | Test ID 7-8: TMDS – Clock Duty Cycle                      | . 76 |

|   |     | Test ID 7-9: TMDS – Clock Jitter                          | . 78 |

|   |     | Test ID 7-10: TMDS – Data Eye Diagram                     | . 81 |

|   |     | Test ID 7-11: +5V Power                                   | . 84 |

|   |     | Test ID 7-12: Hot Plug Detect                             | . 86 |

|   |     | Test ID 7-13: DDC/CEC Capacitance                         | . 88 |

|   |     | Test ID 7-14: CEC Line Connectivity                       | . 90 |

|   |     | Test ID 7-15: CEC Line Degradation                        | . 93 |

|   | 7.4 | Source – Protocol                                         | . 95 |

|   | 7.  | 4.1 Required Test Method Setup for Protocol Tests         | 95   |

|   | 7.  | .4.2 Tests                                                | 96   |

|   |     | Test ID 7-16: Legal Codes                                 | . 96 |

|   |     | Test ID 7-17: Basic Protocol                              | . 98 |

|   |     | Test ID 7-18: Extended Control Period                     | 100  |

|   |     | Test ID 7-19: Packet Types 1                              | 101  |

|   | 7.5 | Source – Video 1                                          | 103  |

|   |     | Test ID 7-20: Type A Connector Usage                      | 103  |

|   |     | Test ID 7-21: Minimum Format Support                      | 104  |

|   |     | Test ID 7-22: Additional Format Support                   | 106  |

|   |     | Test ID 7-23: Pixel Encoding – RGB to RGB-only Sink       | 109  |

|   |     | Test ID 7-24: Pixel Encoding– $YC_BC_R$ to $YC_BC_R$ Sink | 111  |

|   |     | Test ID 7-25: Video Format Timing                         | 112  |

|   |     | Test ID 7-26: Pixel Repetition                            | 117  |

|     | Test ID 7-27: AVI InfoFrame                          | 120 |

|-----|------------------------------------------------------|-----|

| 7.6 | Source – Audio                                       | 124 |

| 7   | 2.6.1 Combinations of Audio and Video Formats        | 124 |

| 7   | <i>1.6.2 Tests</i>                                   | 125 |

|     | Test ID 7-28: IEC 60958/IEC 61937                    | 125 |

|     | Test ID 7-29: ACR                                    | 126 |

|     | Test ID 7-30: Audio Sample Packet Jitter             | 128 |

|     | Test ID 7-31: Audio InfoFrame                        | 129 |

|     | Test ID 7-32: Audio Sample Packet Layout             | 131 |

| 7.7 | Source – Interoperability With DVI                   | 133 |

|     | Test ID 7-33: Interoperability With DVI              | 133 |

| 8 Т | TESTS – SINK                                         |     |

| 8.1 | Sink Products Overview                               |     |

| 8   | 1.1 Television and Other Display Products            |     |

| 8   | 1.2 Audio Rendering Products                         |     |

| 8   | 2.1.3 Non-Display Devices                            |     |

| 8.2 | Sink – EDID / E-DDC                                  |     |

|     | Test ID 8-1: EDID Readable                           | 135 |

|     | Test ID 8-2: EDID VESA Structure                     |     |

|     | Test ID 8-3: CEA Timing Extension Structure          |     |

| 8.3 | Sink – Electrical                                    | 143 |

|     | Test ID 8-4: TMDS – Termination Voltage              |     |

|     | Test ID 8-5: TMDS – Minimum Differential Sensitivity |     |

|     | Test ID 8-6: TMDS – Intra-Pair Skew                  |     |

|     | Test ID 8-7: TMDS – Jitter Tolerance                 | 151 |

|     | Test ID 8-8: TMDS – Differential Impedance           |     |

|     | Test ID 8-9: DDC/CEC Line Capacitance                |     |

|     | Test ID 8-10: HPD Output Voltage                     |     |

|     | Test ID 8-11: HPD Output Resistance                  |     |

|     | Test ID 8-12: +5V Power Max Current                  | 167 |

|     | Test ID 8-13: CEC Line Connectivity                  | 169 |

|     | Test ID 8-14: CEC Line Degradation                   |     |

| 8.4 | SINK – PROTOCOL                                      |     |

|     | Test ID 8-15: Character Synchronization              |     |

|     | Test ID 8-16: Acceptance of All Valid Packet Types   | 176 |

| 8.5 | SINK – VIDEO                                         | 177 |

|     | Test ID 8-17: 861B Format Support Requirements       | 177 |

| Test ID 8-18: HDMI Format Support Requirements                 |     |

|----------------------------------------------------------------|-----|

| Test ID 8-19: Pixel Encoding Requirements                      |     |

| Test ID 8-20: Video Format Timing                              |     |

| 8.6 SINK – AUDIO                                               |     |

| 8.6.1 Audio Test A/V Formats                                   |     |

| 8.6.2 Tests                                                    |     |

| Test ID 8-21: Audio Clock Regeneration                         |     |

| Test ID 8-22: Audio Sample Packet Jitter                       |     |

| Test ID 8-23: Audio Formats                                    |     |

| 8.7 SINK – INTEROPERABILITY WITH DVI                           |     |

| Test ID 8-24: Interoperability With DVI                        |     |

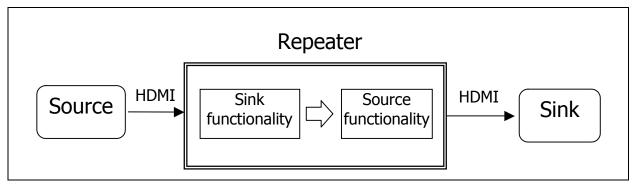

| 9 TESTS – REPEATER                                             | 193 |

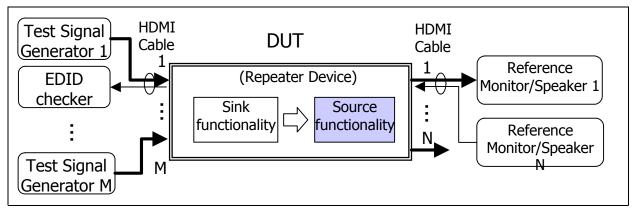

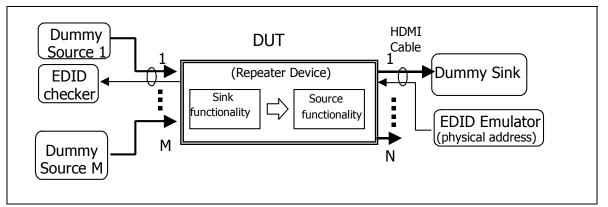

| 9.1 REPEATER PRODUCTS OVERVIEW                                 |     |

| 9.2 INTERNAL FUNCTIONAL BLOCK CATEGORIZATION                   |     |

| 9.2.1 Input/Output Categories                                  |     |

| 9.2.2 Processing Categories                                    |     |

| 9.2.3 Combinations                                             |     |

| 9.2.4 Non-HDMI I/O                                             |     |

| 9.2.5 Source / Sink / Repeater Functionality                   |     |

| 9.3 TESTS OF OUTPUT PORTS                                      |     |

| Test ID 9-1: Repeated Output Port                              |     |

| Test ID 9-2: Sink Functionality                                |     |

| 9.4 Tests of Input Ports                                       |     |

| Test ID 9-3: Repeated Input Port                               |     |

| Test ID 9-4: Source Functionality                              |     |

| 9.5 TESTS FOR PHYSICAL ADDRESS HANDLING                        |     |

| Test ID 9-5: Physical Address                                  |     |

| APPENDIX 1 – AUTHORIZED TESTING CENTER – TEST EQUIPMENT LIST . |     |

| APPENDIX 2 – SOFTWARE CRU TECHNOLOGY                           |     |

| APPENDIX 3 – CAPABILITIES DECLARATION FORM (CDF)               |     |

| PRODUCT CATEGORY                                               |     |

| Source Capabilities                                            |     |

| SINK CAPABILITIES                                              |     |

| Repeater Capabilities                                          |     |

| CABLE ASSEMBLY CAPABILITIES                                    |     |

| APPENDIX 4 – TEST RESULTS FORM         | 221 |

|----------------------------------------|-----|

| Test Results Form – Source DUT         | 222 |

| Test Results Form – Sink DUT           | 225 |

| Test Results Form – Repeater DUT       |     |

| Test Results Form – Cable Assembly DUT | 229 |

| Test Results Form – Plug & Receptacle  |     |

1

# Introduction

## 1.1 <u>Purpose and Scope</u>

This document constitutes the specification of procedures, tools and criteria for testing the compliance of devices with the High-Definition Multimedia Interface Specification Version 1.0.

Each individual test is designed to ensure compliance with one or more requirements in the HDMI Specification or in one of its normative (required) specifications. No amount of testing can guarantee 100% interoperability among all passing devices when operated in all possible modes but, properly executed, the tests described in this document should give a very high level of confidence in the ability of the device to interoperate with other HDMI devices.

Due to the nature of testing a closed-box system such as a TV or DVD player, there are a variety of requirements in the HDMI Specification which are very difficult or impossible to directly verify. Compliance testing for these items will depend upon alternative methods which may not have 100% correlation with the HDMI-required behavior but will achieve the objective of generating confidence in the interoperability of the device.

Consumer Electronics Control (CEC) test methods are given in the HDMI Compliance Test Specification Supplement 1. Version 1.0 of Supplement 1 will be available shortly.

Type B and dual-link functionality is not fully covered by this test specification. Such details will be included in a future version.

## 1.2 <u>Normative References</u>

HDMI Licensing, LLC., "High-Definition Multimedia Interface, Specification Version 1.0", December 9, 2002

Note that the HDMI Specification includes normative references affecting the required operation of HDMI devices.

## 1.3 Organization of this document

This specification is organized as follows:

- Chapter 1 describes the Purpose and Scope of the document, references, usages and conventions.

- Chapter 2 defines terms and acronyms used within the document.

- Chapter 3 provides an Overview to HDMI compliance testing.

- Chapter 4 describes the Required Capabilities for the defined test equipment as well as certain Recommended Test Equipment that has been proven to meet those requirements.

- Chapter 5 describes the tests for a Cable Assembly. For each test, a Required Test Method is described that defines the minimum requirements for accurate and valid testing and a Recommended Test Method that describes the specific procedure for the use of specific test equipment known to adequately test for the required condition.

- Chapter 6 describes the tests for Plug and Receptacles used on any HDMI product.

- Chapter 7 describes the tests for a Source.

- Chapter 8 describes the tests for a Sink

- Chapter 9 describes the tests for a Repeater.

- Appendix 1 lists the initial test equipment used by the Authorized Testing Centers.

- Appendix 2 describes the Software CRU technology used during TMDS electrical testing.

- Appendix 3 defines the Capabilities Declaration Form, which is filled out and submitted by the product manufacturer whenever a product is sent for testing at an Authorized Testing Center (ATC) or when the results of ATC or self-testing are sent to the HDMI Licensing, LLC.

- Appendix 4 defines the Test Results Form, which is completed by the test operator and submitted as the results of ATC or self-testing to the HDMI Licensing, LLC.

- Supplement 1: CEC, defines the tests for the optional Consumer Electronics Control protocol.

# Definitions

2

## 2.1 <u>Conformance Levels</u>

| expected | A key word used to describe the behavior of the hardware or software in the design models <i>assumed</i> by this specification. Other hardware and software design models may also be implemented. |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| may      | A key word that indicates flexibility of choice with no implied preference.                                                                                                                        |

| shall    | A key word indicating a mandatory requirement. Designers are <i>required</i> to implement all such mandatory requirements.                                                                         |

| should   | A key word indicating flexibility of choice with a strongly preferred alternative. Equivalent to the phrase <i>is recommended</i> .                                                                |

# 2.2 Usages and Conventions

Note that the HDMI Specification should be referenced for definitions of all usages and conventions that are not defined below.

| bit N         | Bits are numbered in little-endian format, i.e. the least-significant bit of a byte or word is referred to as bit 0.                                                                            |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[X:Y]        | Bit field representation covering bit X to bit Y (inclusive) of value or field D.                                                                                                               |

| 0xNN          | Hexadecimal representation of base-16 numbers are represented using 'C' language notation, preceded by '0x'.                                                                                    |

| 0bNN          | Binary (base-2) numbers are represented using 'C' language notation, preceded by '0b'.                                                                                                          |

| NN            | Decimal (base-10) numbers are represented using no additional prefixes or suffixes.                                                                                                             |

| !=            | Does not equal ('C' notation).                                                                                                                                                                  |

| ==            | Is Equal to ('C' notation). Used to test for a specific value (e.g. if bit 3 == 1, or, verify that byte SB0 == 0).                                                                              |

| =             | Equals ('C' notation). Used to assign a value to a variable (e.g. number of packets = number of pixels / 32) or is used in the specification of a required value (e.g. AVcc = $3.3V \pm 5\%$ ). |

| [HDMI: X.Y.Z] | Shorthand notation indicating a reference to the HDMI Specification.<br>Examples: [HDMI: 3.2] denotes a reference to the HDMI Specification, section 3.2.                                       |

| [CEC: X.Y.Z]  | Denotes a reference to the HDMI Specification, Supplement 1,<br>"Consumer Electronics Control", section CEC X.Y.Z.                                                                              |

| HDMI Compliance Test Specification |                                                                                                                                                                                                                                                                                                                                                      | Version 1.0                          |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Section 2                          | Definitions                                                                                                                                                                                                                                                                                                                                          |                                      |

| [861B: X.Y.Z]                      | Denotes a reference to the EIA/CEA-861B specification. E<br>[861B: 3.2] denotes a reference to the EIA/CEA-861B species<br>section 3.2.                                                                                                                                                                                                              |                                      |

| TMDS_DATA0                         | Equivalent to the differential signal pair TMDS Data0. Whe single-ended signal within this pair, TMDS_DAT0+ or TMD used. Same applies to TMDS_DATA1, TMDS_DATA2 and TMDS_CLOCK.                                                                                                                                                                      | S_DATA0– is                          |

| FAIL, "xxx"                        | Indicates a directive to the test operator to fail this test and<br>"FAIL" in the "Pass/Fail" field of the Test Results form, and<br>"xxx" in the Comments field. It is permitted and frequently to<br>remainder of the test to be performed to provide additional<br>about the failure.                                                             | the comment<br>useful for the        |

| PASS, "xxx"                        | Indicates a directive to the test operator to pass this test ar<br>"PASS" in the "Pass/Fail" field of the Test Results form, an<br>comment "xxx" in the Comments field. The PASS directive<br>the test is complete unless indicated otherwise. There is an<br>PASS directive at the end of every test method, causing su<br>completed tests to PASS. | d the<br>indicates that<br>n implied |

# 2.3 Glossary of Terms

Note that the HDMI Specification should be referenced for definitions of any terms that are not defined below.

| test coupon        | A test trace, that emulates the signal traces, present on a test fixture PCB. The test coupon is used to measure and compensate for process variations during PCB manufacture.                                                                                                                                                                                                                                                                                               |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| support            | The ability for a device to perform the appropriate action (for that device) with the specified format or option. For display devices, a video format is supported if such a signal is displayed in a manner comparable to other video formats or video from other inputs. For source devices, a video format is supported if the device is capable, after appropriate user input or delivery of appropriate content to the device, of outputting a signal with that format. |

| T <sub>BIT</sub>   | One bit time at the specified pixel clock frequency (= $T_{PIXEL}/10$ ). If no pixel clock frequency is specified, it is assumed to be the current (tested) pixel clock frequency.                                                                                                                                                                                                                                                                                           |

| T <sub>PIXEL</sub> | One pixel time at the specified pixel (TMDS) clock frequency. If no pixel clock frequency is specified, it is assumed to be the current (tested) pixel clock frequency. If a video format is pixel-repeated, $T_{PIXEL}$ continues to be defined as 10* $T_{BIT}$ .                                                                                                                                                                                                          |

## 2.4 Acronyms and Abbreviations

Note that the HDMI Specification should be referenced for definitions of any terms that are not defined below.

| ATC  | Authorized Testing Center                                                      |

|------|--------------------------------------------------------------------------------|

| CDF  | Capabilities Declaration Form                                                  |

| DTD  | Detailed Timing Descriptor (also called "18-byte timing descriptor)            |

| DUT  | Device Under Test                                                              |

| ISVM | I (current) Source Voltage Measurements                                        |

| SVD  | Short Video Descriptor (in Data Block collection of CEA EDID Timing Extension) |

| TDR  | Time Domain Reflectometer/Reflectometry                                        |

| TDT  | Time Domain Transmission                                                       |

| TE   | Test Equipment                                                                 |

| TPA  | Test Point Access                                                              |

| VSIM | Voltage Source I (current) measurements                                        |

# 3 Overview

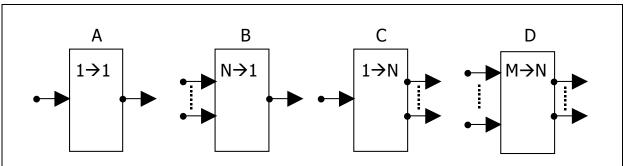

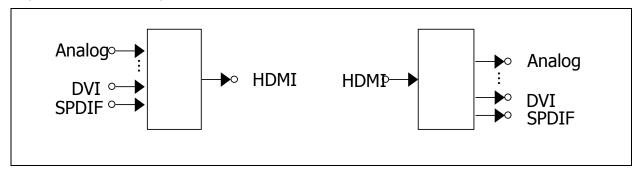

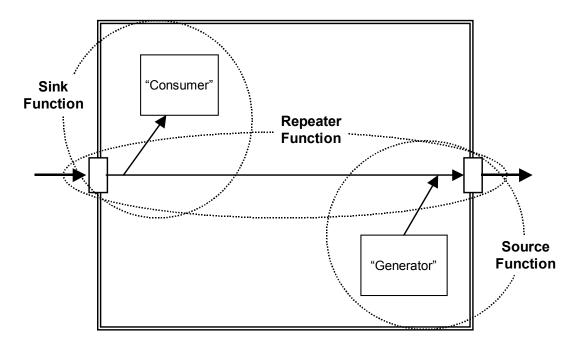

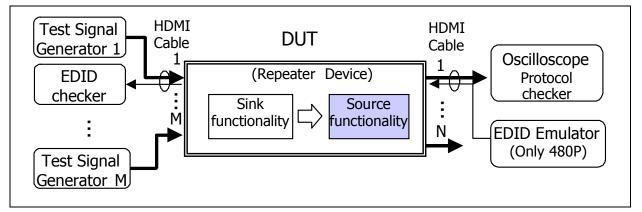

HDMI system architecture is defined to consist of Sources, Sinks, Repeaters and Cable Assemblies. A given device may have one or more HDMI inputs and one or more HDMI outputs. Each HDMI input on a device shall follow all of the rules for an HDMI Sink and each HDMI output shall follow all of the rules for an HDMI Source. Consequently, each HDMI input shall be fully tested for compliance using the tests specified for Sink devices and each HDMI output shall be fully tested against the full set of tests specified for Source devices.

Any device with at least one HDMI input and at least one HDMI output is defined to be a Repeater. In addition to the Source and Sink tests required for each of the inputs and outputs, additional Repeater tests may be required.

In addition to the tests described for Sources, Sinks, Repeaters and Cable Assemblies, there are tests described for connectors present on these devices. The manufacturer of the device is required to verify the compliance of the connector in all cases, whether the product is ATC-tested or self-tested.

In order to provide the best coverage possible, it is necessary to perform many of the tests herein for each relevant operational mode of the Device Under Test (DUT). For instance, it is necessary to perform some of the video tests for each supported video format.

The primary purpose of the testing is to reveal whether the product passes all test cases. A failure of a single test item within a test case constitutes a failure of the product to meet the overall compliance testing requirement. However, even if an intermediate test step within a test case reveals a failure, it is permitted and frequently useful for the remainder of that test case and other test cases to be performed in order to provide additional information about the failure.

# 4 Test Equipment

## 4.1 <u>Test Equipment Overview</u>

## 4.1.1 Required Capabilities versus Recommended Equipment

Each piece of test equipment referenced by the individual test cases in the Source, Sink, Repeater and Cable Assembly sections is listed below. For each of these, the "Required Test Equipment Capabilities" are described. All equipment used for testing the related attributes shall comply with the requirements listed for that equipment.

In addition, for each of the defined pieces of equipment, specific commercial or custom "Recommended Test Equipment" is described. This is the equipment that is used in the initial HDMI Authorized Test Center and should also, if possible, be used for any self-testing of the related functions. Other configurations and equipment may be used for self-testing, as long as that equipment and the processes used meet all of the stated and implied requirements and permit an equivalent level of testing. It is the Adopter's responsibility to verify that the substituted equipment and processes are sufficient.

## 4.1.2 Analyzers and Generators

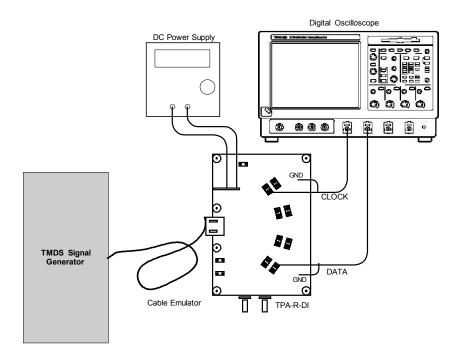

In general, Source devices are tested using various Sink emulators with measurement functions, typically called "Analyzers". These Sink emulators may have a variety of EDID structures used to encourage certain behavior by the Source DUT and they are capable of measuring a variety of parameters or attributes of the HDMI signals delivered by the Source DUT. The measurement may be performed using the facilities of the Sink emulator itself or using standard test equipment such as digital oscilloscopes, logic analyzers or network analyzers.

Likewise, Sink devices are tested using a variety of Source emulators or "Generators" capable of generating a variety of test signals. These generators may consist of custom hardware designed for HDMI compliance testing or may consist of standard waveform and pattern generators or some combination thereof.

## 4.1.3 Simultaneous Test Case Execution

Some test tools can be used for a variety of test cases. These tests can sometimes be executed simultaneously so that, with one running of the tool, several tests can be passed or failed without re-running the tool.

## 4.2 <u>Test Equipment Requirements</u>

All test equipment requiring calibration in order to ensure accurate and repeatable results shall be calibrated prior to and, if necessary, during the test procedure.

## 4.2.1 Electrical Testing

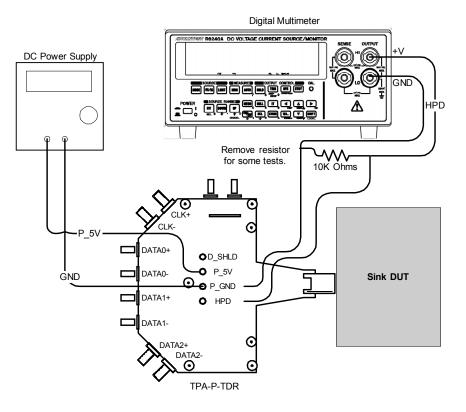

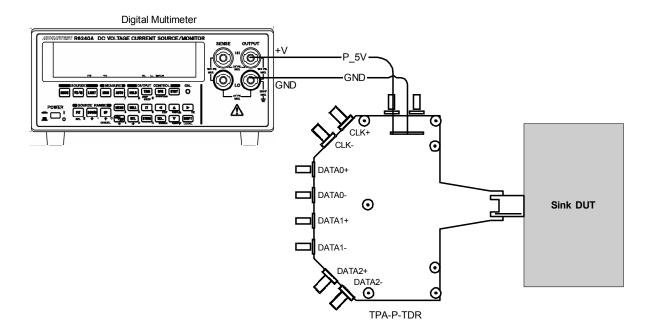

#### 4.2.1.1 Test Point Access Boards

### 4.2.1.1.1 Overview

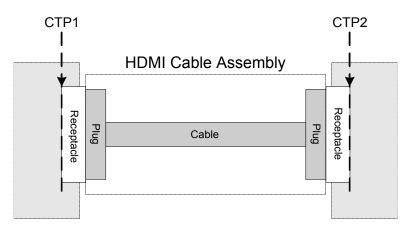

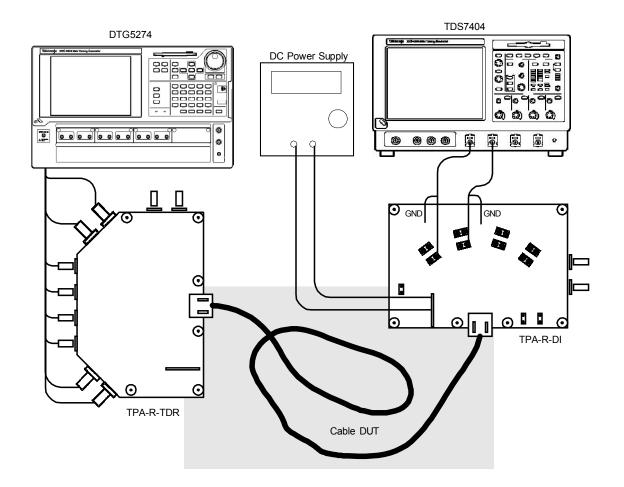

In order to gain access to the required signals, Test Point Access boards are required. TPA boards provide test points for all of the pins on the HDMI connector, including no-connect pins.

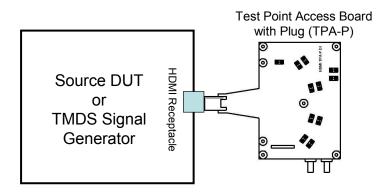

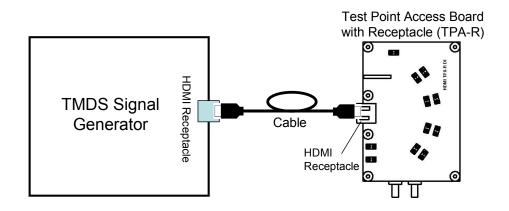

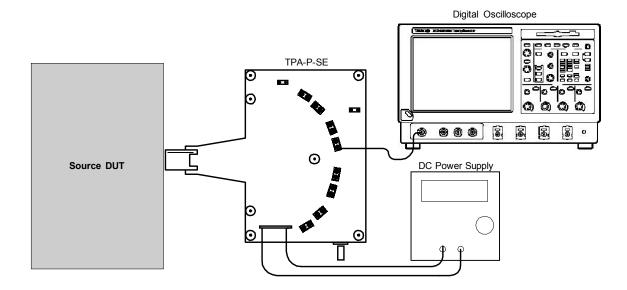

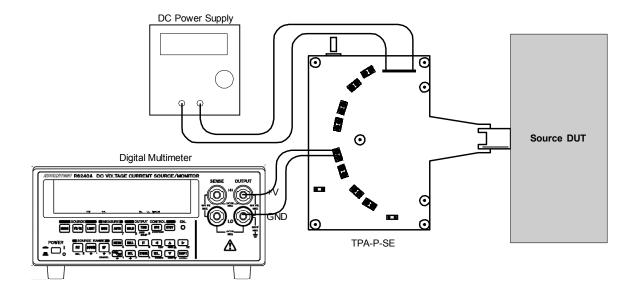

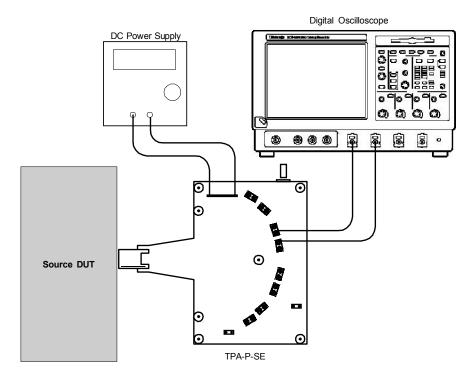

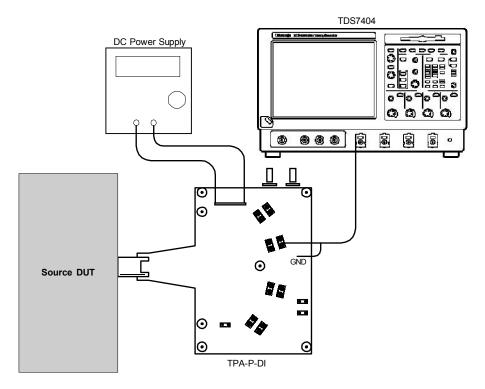

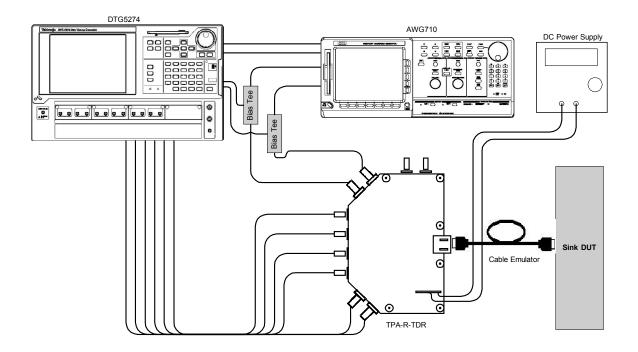

For each of the two different connector types (Type A and Type B) there are two different TPA board configurations. These are the Receptacle TPA (TPA-R) and Plug TPA (TPA-P) and are shown in Figure 4-1 and Figure 4-2. These boards permit direct access to all TMDS, DDC and CEC signals. Due to differences in the measurements taken (e.g. skew, jitter) and the types of probes used, there are a variety of TPA boards available of each type (Plug and Receptacle).

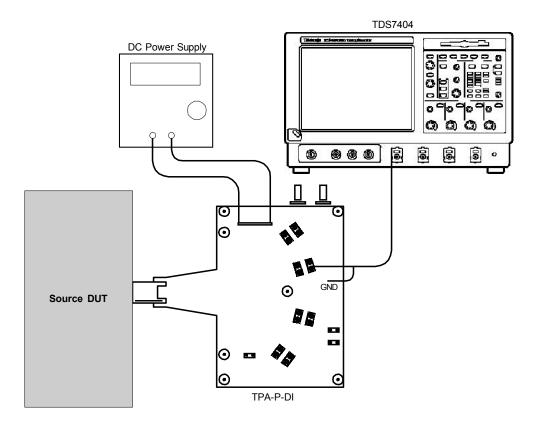

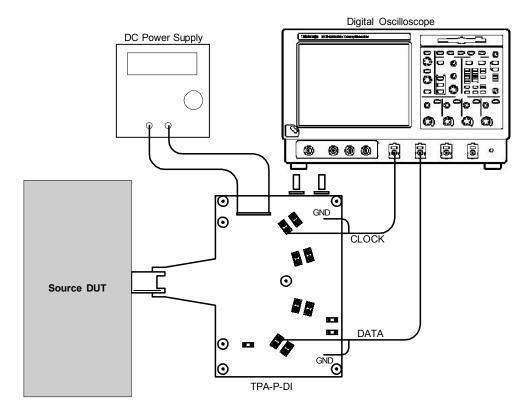

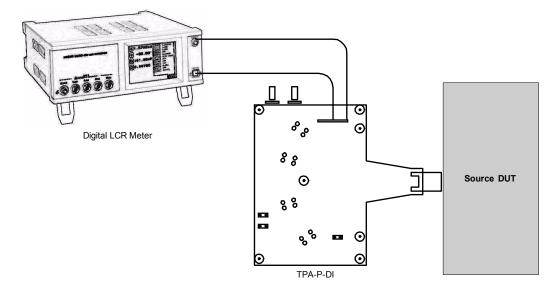

Figure 4-1 TPA-P, used for Source and Cable test calibration

Figure 4-2 TPA-R, used for Sink and Sink test calibration

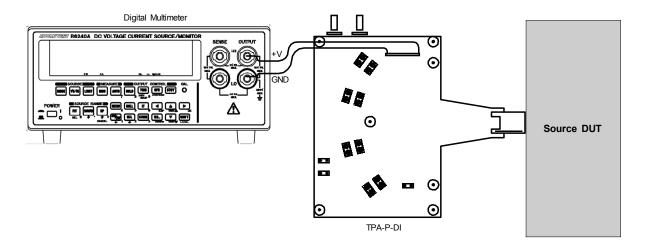

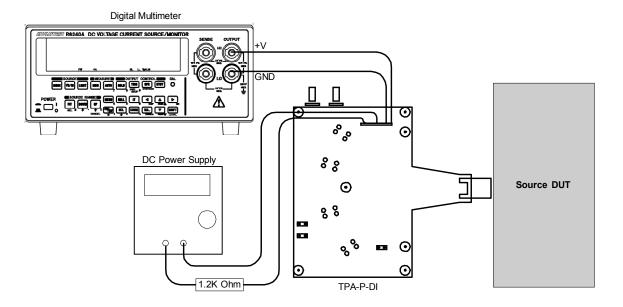

When a TPA board is acting as a Sink (for Source DUT testing), additional functionality is required. Termination resistors are connected between each TMDS signal and a (typically) 3.3V supply. In addition, a variety of EDID images may be required in order to get the Source to create the required signal. For this reason, an EDID Emulator may be attached to the TPA board. Lastly, as a Sink, the TPA is typically operated with the Hot Plug Detect signal connected to the +5V Power signal through a 1kohm resistor.

#### Required Test Equipment Capabilities

Following are the capabilities common among all of the TPA boards:

• HDMI plug or receptacle is mounted in such a way to enable direct connection to a Source, Sink or Cable Assembly.

- Termination: On any TPA that is used to emulate the behavior of a Sink, termination resistors are provided on each of the TMDS signal lines. In this case:

- Connector is provided allowing input of external DC 3.3V source to +3.3V power rail used for TMDS termination.

- Test point is provided on 3.3V rail.

- Each single-ended TMDS signal is pulled up to +3.3V power rail through a 50 ohm resistor with less than ± 1% tolerance.

- Test coupon test ports (see below) are pulled up to the +3.3V rail through a 50 ohm resistor with less than ± 1% tolerance. At least 1 GND pin is mounted near the test port (closer than 15mm).

- All TMDS signals have the following characteristics:

- Test port shall be appropriate to the type of probe used and is located at an equivalent trace length from the HDMI connector as all other test ports.

- Characteristic differential impedance of the connector, for each differential TMDS pair is 100 ohms ± 15%.

- Characteristic differential impedance of the traces, for each differential TMDS pair, is 100 ohms ± 5% as a average over the entire trace. Peak impedance of up to 100 ohms ±10% is also permitted.

- Intra-pair skew is less than 15psec.

- Inter-pair skew is less than 40psec.

- At least 1 GND pin is mounted near each TMDS test port. This pin is connected to the PCB ground plane as well as to all of the TMDS shields.

- Non-TMDS pins (if required for test):

- These pins have testing ports that can be used to measure or drive each of the signals.

- Connector is provided to allow input of DC 5V to the HDMI +5V Power pin.

- HDMI HPD signal may be connected to HDMI +5V Power through a removable 1kohm resistor.

- Test coupon is recommended to be provided to measure and compensate for process variation of PCB manufacture:

- Test coupon consists of one or two traces meant to emulate the traces of a single-ended TMDS signal or a differential pair of TMDS signals.

- Each of the traces is located on the same layer of the PCB as the trace that it is emulating.

- Trace length and characteristics are equivalent to that of the emulated trace on this board.

- To enable easy and accurate attachment of testing equipment, each trace is terminated at one end to an SMA connector (or other connector of sufficient quality) and at the other with a Test port, which is identical to the Test ports for the TMDS signals and designed to match the probes used for the measurement.

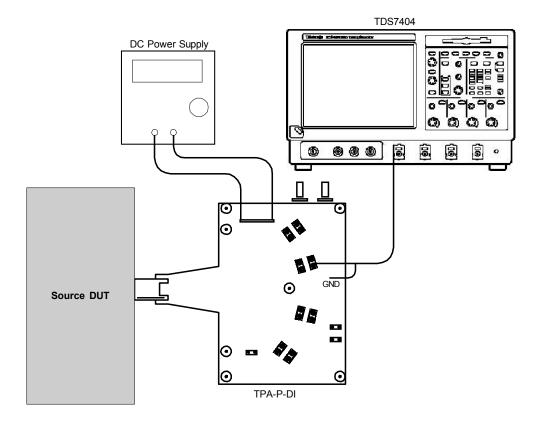

## 4.2.1.1.2 TPA-P for Differential measurement

Access points are provided for differential probes to measure each of the four TMDS differential pairs.

#### Required Test Equipment Capabilities

- All standard TPA capabilities described above in Section 4.2.1.1.1.

- Type A plug connector is mounted to enable direct connection to a Source or Sink.

- TMDS test ports consist of two pins (for each TMDS differential pair) designed to allow direct and reliable connection of a differential probe.

- Test coupon consists of two traces as described in Section 4.2.1.1.1 with test ports identical to those on the TMDS traces.

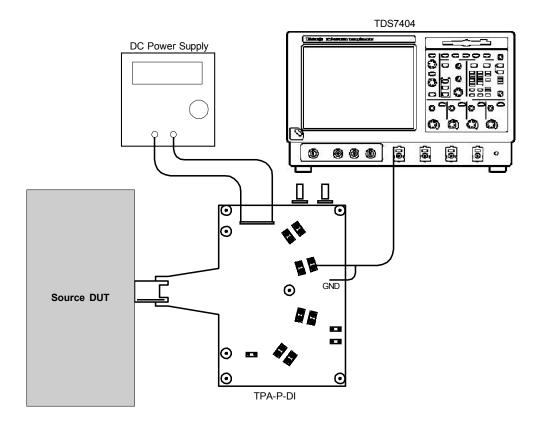

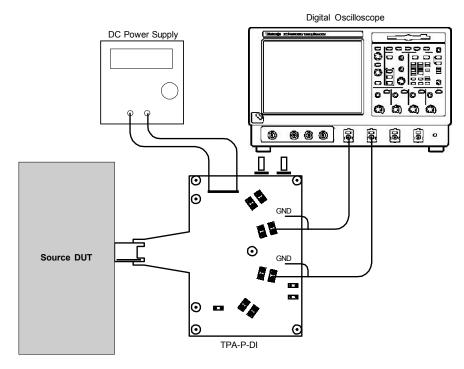

#### Recommended Test Equipment

• Tektronix TPA-P-DI, available as one component in Tektronix 013-A013-50

## 4.2.1.1.3 TPA-R for Differential measurement

Access points for differential probes to measure across each of the four TMDS differential pairs.

#### Required Test Equipment Capabilities

- All standard TPA capabilities described above in Section 4.2.1.1.1.

- Type A receptacle connector is mounted to allow direct connection to a Cable Assembly.

- TMDS test ports consist of two pins (for each TMDS differential pair) designed to allow direct and reliable connection of a differential probe.

- Test coupon consists of two traces as described in Section 4.2.1.1.1 with test ports identical to those on the TMDS traces.

#### Recommended Test Equipment

• Tektronix TPA-R-DI, available as one component in Tektronix 013-A012-50

## 4.2.1.1.4 TPA-P for Single Ended measurement

Access points for single-ended probes to measure each of the TMDS single-ended signals.

#### Required Test Equipment Capabilities

- All standard TPA capabilities described above in Section 4.2.1.1.1.

- Type A plug connector is mounted to allow direct connection to a Source or Sink.

- TMDS test ports consist of two pins (for each TMDS single-ended signal) designed to allow direct and reliable connection of a single-ended probe with corresponding ground connection.

- Test coupon consists of one trace as described in Section 4.2.1.1.1 with test port identical to those on the TMDS traces.

### Recommended Test Equipment

• Tektronix TPA-P-SE, available as one component in Tektronix 013-A013-50

## 4.2.1.1.5 TPA-R for Single Ended measurement

Access points for single-ended probes to measure each of the TMDS single-ended signals.

#### Required Test Equipment Capabilities

- All standard TPA capabilities described above in Section 4.2.1.1.1.

- Type A receptacle connector is mounted to allow direct connection to a Cable Assembly.

- TMDS test ports consist of two pins (for each TMDS single-ended signal) designed to allow direct and reliable connection of a single-ended probe with corresponding ground connection.

- Test coupon consists of one trace as described in Section 4.2.1.1.1 with test port identical to those on the TMDS traces.

#### Recommended Test Equipment

• Tektronix TPA-R-SE, available as one component in Tektronix 013-A012-50

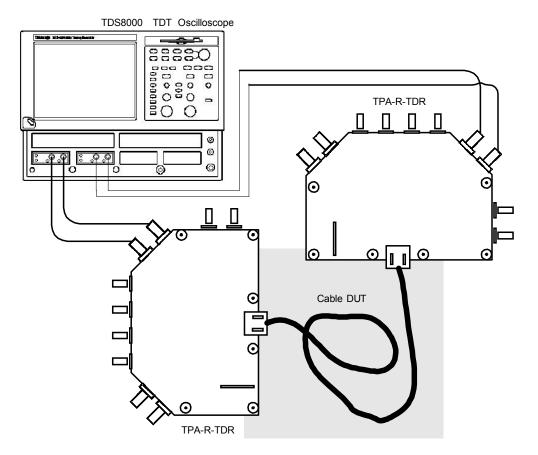

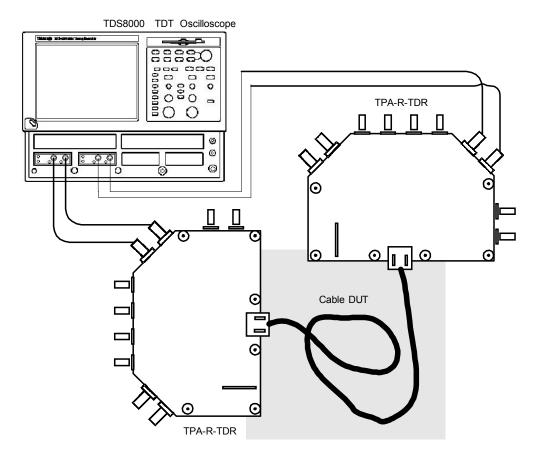

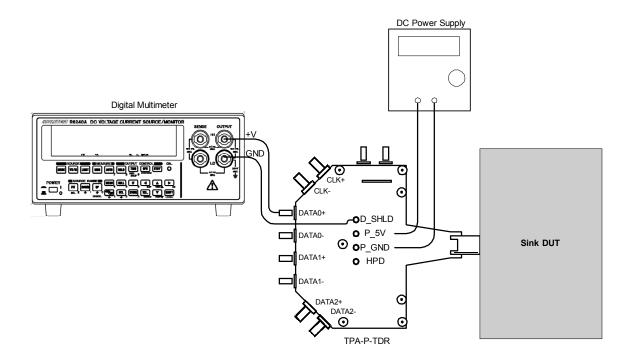

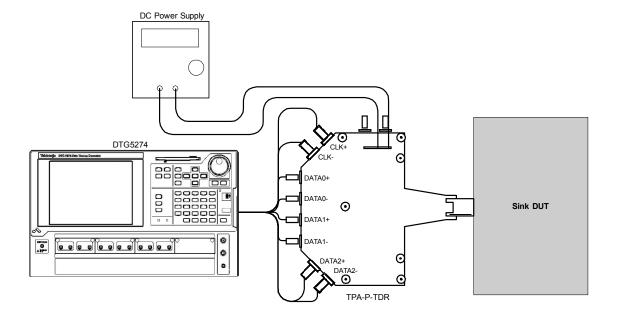

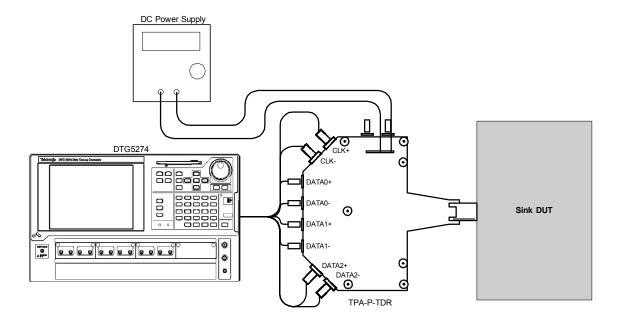

## 4.2.1.1.6 TPA-P for TDR measurement

This TPA is typically used in a manner that emulates a Source device, rather than a Sink device.

#### Required Test Equipment Capabilities

- All standard TPA capabilities described above in Section 4.2.1.1.1.

- Type A plug connector is mounted to allow direct connection to a Source or Sink.

- TMDS test ports consist of one SMA connector for each TMDS signal and are designed to allow easy connection of a TDR oscilloscope.

- There are no TMDS pull-up resistors installed.

- Rise time of less than 200psec (10-90%), when connected to the TDR oscilloscope is possible.

- Test coupon consists of one trace as described in Section 4.2.1.1.1 with test port identical to those on the TMDS traces (SMA).

#### Recommended Test Equipment

• Tektronix TPA-P-TDR, available as one component in Tektronix 013-A013-50

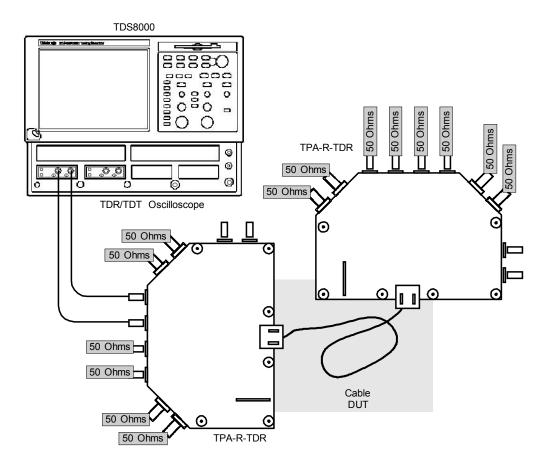

## 4.2.1.1.7 TPA-R for TDR measurement

#### Required Test Equipment Capabilities

• All standard TPA capabilities described above in Section 4.2.1.1.1.

- Type A receptacle connector is mounted to allow direct connection to a Cable Assembly.

- TMDS test ports consist of one SMA connector for each TMDS signal and are designed to allow easy connection of a TDR oscilloscope.

- There are no TMDS pull-up resistors installed.

- Rise time of less than 200psec (10-90%), when connected to the TDR oscilloscope is possible.

- Test coupon consists of one trace as described in Section 4.2.1.1.1 with test port identical to those on the TMDS traces (SMA).

#### Recommended Test Equipment

• Tektronix TPA-R-TDR, available as one component in Tektronix 013-A012-50

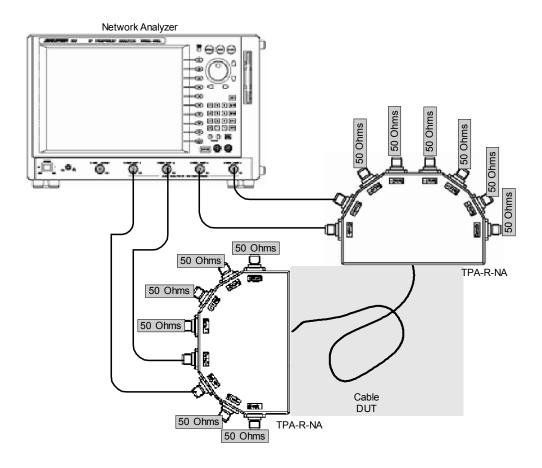

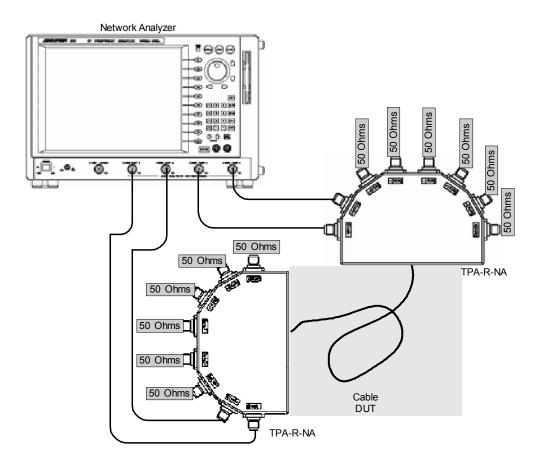

## 4.2.1.1.8 TPA-R for Network Analyzer measurement (TPA-R-NA)

#### Required Test Equipment Capabilities

- All standard TPA capabilities described above in Section 4.2.1.1.1.

- Type A receptacle connector is mounted to allow direct connection to a Cable Assembly.

- TMDS test ports consist of one SMA connector for each TMDS signal and are designed to allow easy connection of a Network Analyzer.

- Measurement bandwidth is 300kHz 4.125GHz

- Rise time of less than 200psec, when connected to the TDR oscilloscope is possible.

- Test coupon is preferred but not required.

#### Recommended Test Equipment

• ADVANTEST CAX-ATI013

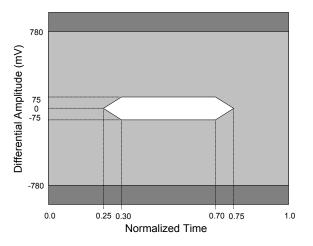

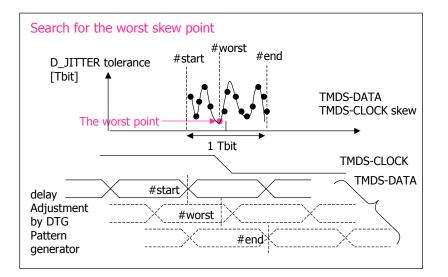

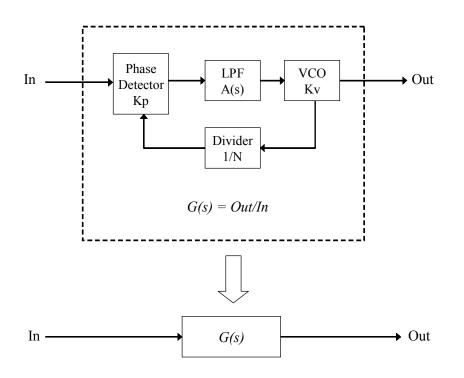

#### 4.2.1.2 Jitter/Eye Analyzer

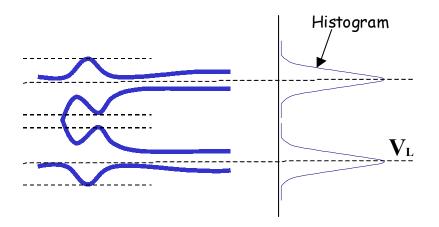

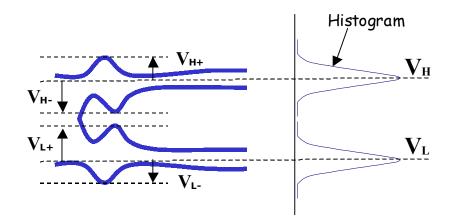

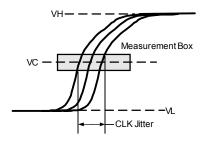

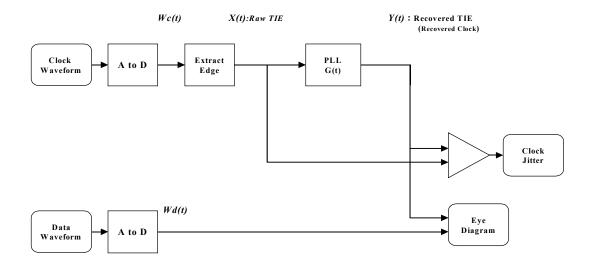

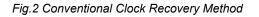

All jitter and eye measurements are taken relative to a Recovered Clock which is generated by a Clock Recovery Unit (CRU). This recovered clock is meant to approximate the Ideal Recovery Clock specified in the HDMI Specification. This Recovered Clock, rather than the real TMDS differential clock, is used as the trigger for measurement of the TMDS clock jitter and TMDS data eye diagram.

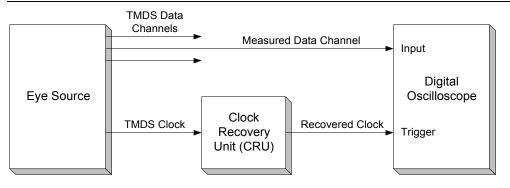

Figure 4-3 shows *functionally* how the CRU is used to measure an eye diagram. Clock jitter is measured using a very similar approach, shown in Figure 4-4. Effectively, the CRU generates the trigger which the oscilloscope uses to capture and display the data eye.

#### HDMI Compliance Test Specification

#### Section 4

Figure 4-3 TMDS Eye Diagram Measurement: 10x clock output from CRU(bit time)

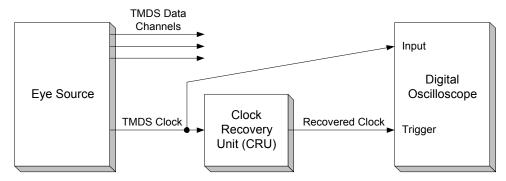

Figure 4-4 shows how the CRU is used to measure the jitter on a transmitted TMDS clock.

Figure 4-4 TMDS Clock Jitter Measurement: 1x clock output from CRU (pixel time)

In actuality, the recommended CRU consists of software which digitally processes captured data. Following the capture, the software CRU processes the captured TMDS\_CLOCK waveform according to the mathematical definition of the Ideal Recovery Clock, specified in [HDMI: 4.2.3]. The eye diagram is then drawn as if a series of captures had occurred, each triggered by a Recovered Clock edge.

This type of approach can be made to work with any analog data capture device with sufficient resolution, speed, memory depth and jitter-free capture clock. Following the capture, the software CRU algorithm could process and display data on any computer. A digital oscilloscope may be used to provide the data capture, software processing and/or display capabilities required.

This software approach is recommended, due to the high correlation between the software implementation and the mathematical definition of the Ideal Recovery Clock.

Jitter and eye measurements are used for Source, Sink, and Cable Assembly compliance testing. For Source testing, the Jitter/Eye Analyzer is used to verify the compliance of the output eye and TMDS clock jitter directly. For Sinks, the Jitter/Eye Analyzer is used during the calibration of a worst-case eye from a TMDS Signal Generator. The worst-case eye is input to the Sink to determine its data recovery capabilities. For cables, generation of a worst-case input eye as well as analysis of the cable's output eye are performed.

#### Required Test Equipment Capabilities

The Jitter/Eye Analyzer must be capable of accurately indicating the amount of jitter or the actual eye diagram on the tested TMDS differential signal.

The transfer function for an Ideal Recovery Clock is shown in Equation 4-1 below. An ideal CRU would perfectly match this function.

Across the tested clock frequency range, the Jitter/Eye Analyzer's CRU shall have a jitter transfer amplitude that differs, from the ideal transfer function, by no more than  $\pm 0.2dB$  from DC to 10MHz. At 20MHz the difference must be less than  $\pm 1dB$  and at 50MHz, less than  $\pm 2/-6dB$ . From DC to 20MHz, the jitter transfer phase response must be within  $\pm 1.8$  degrees of the phase response of the ideal recovery clock.

$H(j\omega) = 1 / (1 + j\omega/\omega_0)$  Where  $\omega_0 = 2\pi F_0$ ,  $F_0 = 4.0 MHz$

Equation 4-1 Jitter Transfer Function of PLL for Ideal Recovery Clock Definition

#### Recommended Test Equipment

The Recommended Jitter/Eye Analyzer uses a high-speed digital oscilloscope to perform the data capture operation and a PC to perform the software CRU processing and display:

- Tektronix TDS7404 4GHz Digital Oscilloscope, with 32 mega-samples total (16 megasamples on each of two active channels).

- Two (2) Tektronix P7330 Differential Probes

- PC running 32-bit Windows OS (may be integrated into oscilloscope)

- Tektronix SoftCRU software, running on the Windows PC, designed to be used with the data captured from the Tektronix TDS7404 digital oscilloscope. (See Appendix 2 for details.)

## 4.2.1.3 4GHz Digital Oscilloscope

Required Test Equipment Capabilities

- DC to 4GHz, -3dB bandwidth or greater

- Input configurations:

- 1 or 2 Differential Probes

- 1 or 2 Single-Ended probes

- Sampling rate >= 10GSample/sec, sampling 2 channels simultaneously.

- Sample memory: >=32 mega-samples total (>=16 mega-samples on each of two active channels).

#### Recommended Test Equipment

• Tektronix TDS7404 4GHz Digital Oscilloscope with large memory option (#4M)

## 4.2.1.4 Differential Probe

#### Required Test Equipment Capabilities

- DC 3.5GHz bandwidth (or greater) when connected to the oscilloscope

- Can connect directly and reliably to the TPA-P-DI or TPA-R-DIfixtures

- Length of Ground Lead is less than 7cm

#### Recommended Test Equipment

- Tektronix P7330 Differential Probe

- Tektronix 016-1884-00 Square Pin Adapter

- Tektronix 196-3469-00 Ground Lead

## 4.2.1.5 Single-Ended Probe

Required Test Equipment Capabilities

- DC 4GHz bandwidth (or greater) when connected to the oscilloscope .

- Can connect directly and reliably to the TPA-P-SE or TPA-R-SE fixtures

#### Recommended Test Equipment

- Tektronix P7240

- Tektronix 016-1773-00 Square pin socket

## 4.2.1.6 SMA Cables

Required Test Equipment Capabilities

- Less than 2 meters, preferably less than 1 meter.

- Bandwidth: 9GHz or greater

- 50 ohms impedance

#### Recommended Test Equipment

Any of the following are sufficient:

- Tektronix 174-1428-00 (1.5 meter)

- Tektronix 174-1341-00 (1 meter)

## 4.2.1.7 50 Ohm SMA Terminators

Required Test Equipment Capabilities

- 50 ohms impedance ± 1% or better

- Connects directly to SMA female.

## Recommended Test Equipment

Any lab-quality terminator which meets requirements above is sufficient.

## 4.2.1.8 TMDS Signal Generator

Generates HDMI signal with a variety of patterns, clock jitter, data waveform (eye diagram) and amplitude characteristics.

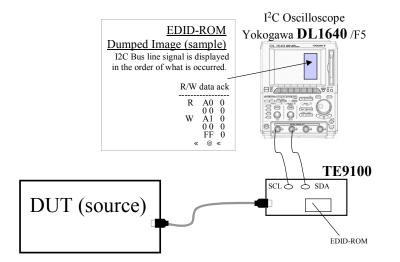

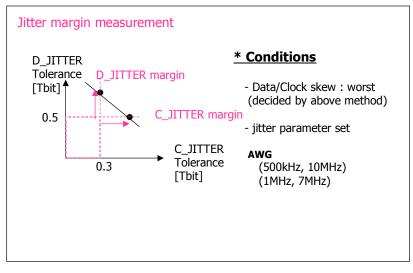

### Required Test Equipment Capabilities