# **Aalborg Universitet**

# Coordinated Control Based on Bus-Signaling and Virtual Inertia for Islanded DC

Wu, Dan; Tang, Fen; Dragicevic, Tomislav; Guerrero, Josep M.; Quintero, Juan Carlos Vasquez

Published in:

I E E E Transactions on Smart Grid

DOI (link to publication from Publisher): 10.1109/TSG.2014.2387357

Publication date:

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Wu, D., Tang, F., Dragicevic, T., Guerrero, J. M., & Vasquez, J. C. (2015). Coordinated Control Based on Bus-Signaling and Virtual Inertia for Islanded DC Microgrids. I E E E Transactions on Smart Grid, 6(6), 2627 - 2638. DŎI: 10.1109/TSG.2014.2387357

## **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

# Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Coordinated Control Based on Bus-Signaling and Virtual Inertia for DC Islanded Microgrids

Dan Wu, Fen Tang, Tomislav Dragicevic, Josep M. Guerrero, Juan C. Vasquez

Abstract-- A low-voltage DC islanded microgrid contains a number of renewable energy sources (RES), local loads, and energy storage systems (ESS). To avoid the over-charging and over-discharging situations of ESS, a coordinated control strategy should be used in DC islanded microgrids. In this paper, a novel bus-signaling method (BSM) is proposed to achieve autonomous coordinated performance of system according to different state of charge (SoC) conditions. Additionally, a secondary coordinated control is introduced to restore the voltage deviation produced by primary control level without decaying coordinated performance. The proposed control algorithm and controller implementation based on BSM are also presented. Finally, real-time simulation results show the feasibility of the proposed approach by presenting the operation of a DC islanded microgrid in different testing scenarios.

Index Terms-- Coordinated control, primary control, secondary control, bus-signaling method, DC islanded microgrids.

#### Nomenclature

| ${V_{dc}}^st$       | Nominal value of bus voltage                              |

|---------------------|-----------------------------------------------------------|

| $V_{dc}$            | DC bus voltage                                            |

| $SoC_0$             | Lower-threshold of SoC                                    |

| $SoC_1$             | Upper-threshold of SoC                                    |

| $m_1$               | Boosting slope of bus voltage                             |

| $m_0$               | Descending slope of bus voltage                           |

| $V_{ m max}$        | Maximum value of bus voltage                              |

| $V_{ m min}$        | Minimum value of bus voltage                              |

| $P_{ m L}$          | Total power rating of loads                               |

| $P_{ m L1}$         | Power rating of load when one step is shed                |

| $P_{ m L2}$         | Power rating of load when two steps are shed              |

| $SoC_e$             | Steady-state SoC in high SoC case                         |

| $V_{dce}$           | Steady-state bus voltage in high SoC case                 |

| $P_{RES}$           | Power generated from RES                                  |

| $P_e$               | Steady-state power of RES with power                      |

|                     | curtailment                                               |

| $P_{MPP}$           | Maximum power generated from RES                          |

| $V_{meas}$          | Measured bus voltage by RES                               |

| n                   | Virtual inertia coefficient of RES                        |

| au                  | Time constant of low pass filter measuring $V_{meas}$     |

| $G_{ m vi}({ m s})$ | Closed-loop system inertia of RES                         |

| $V_{L1\_OFF}$       | Bus voltage threshold when shedding Load <sub>1</sub>     |

| $V_{LI\_ON}^{}$     | Bus voltage threshold when reconnecting Load <sub>1</sub> |

Dan Wu, Tomislav Dragicevic, Josep M. Guerrero, Juan C. Vasquez are with Department of Energy Technology, Aalborg University, 9220 Aalborg (e-mail: dwu@et.aau.dk; tdr@et.aau.dk, joz@et.aau.dk, juq@et.aau.dk).

Fen Tang is with National Active Distribution Network Technology Research Center (NANTEC), Beijing Jiaotong University, Haidian District, Beijing 100044, China (e-mail: ftang\_nego@126.com).

| $V_{L2\_OFF}$        | Bus voltage threshold when shedding Load <sub>2</sub>     |

|----------------------|-----------------------------------------------------------|

| $V_{L2\_ON}$         | Bus voltage threshold when reconnecting Load <sub>2</sub> |

| $\Delta V$           | Steady-state voltage deviation in high SoC case           |

| $\delta V$           | Shifting-voltage term of secondary control                |

| $k_{p m sec}$        | Proportional term of secondary control                    |

| $k_{i 	ext{sec}}_*$  | Integral term of secondary control                        |

| ${V_{ m sec}}^*$     | Secondary bus voltage reference                           |

| $V_{meas2}$          | Measured bus voltage by secondary control                 |

| $G_{ m sec}({ m s})$ | Secondary controller                                      |

| $	au_2$              | Time constant of low pass filter measuring $V_{meas2}$    |

| $I_{ref}$            | Current reference of RES inner loop controller            |

| $SoC_{sI}$           | SoC threshold for shedding Load <sub>1</sub>              |

| $SoC_{rI}$           | SoC threshold for reconnecting Load <sub>1</sub>          |

| $SoC_{s2}$           | SoC threshold for shedding Load <sub>2</sub>              |

| $SoC_{r2}$           | SoC threshold for reconnecting Load <sub>2</sub>          |

#### I. INTRODUCTION

ICROGRID is a local grid with a number of renewable energy sources (RES), energy storage systems (ESS), and local loads, which can be seen as an independent system with capability to operate in either grid-connected or islanded mode [1], [2]. Nowadays, DC microgrids or nanogrids have drawn great attention. Compared to AC microgrids which require multiple AC/DC and DC/AC conversions, DC microgrids can provide higher efficiency and reliability [3]. Therefore, they have great potential in applications such as future building electrical systems, datacom centers and plug-in hybrid electric vehicles [4]-[6].

In islanded DC microgrids, the power generation and load consumption by dispersed units should not be conceived separately, but in a coordinated way to achieve the energy management. Furthermore, the power fluctuation of both power generation and load consumption will result in charging or discharging of ESS. Then the state of charge (SoC) of ESS should also be taken into account when controlling the system, so that to avoid over-charging and over-discharging situations. Usually this coordinated function is achieved by a microgrid central controller at upper level [7]-[9], which is classified as tertiary level of hierarchical structure described in [10] and [11]. Detailed illustrations of this kind of control structure are presented in [12] and [13], where the islanded microgrid operation is classified into different control modes. The central controllers are making decisions based on the SoC conditions of the ESS collected from primary level, and then sending back control mode signals to the distributed units. However, this conventional control structure may result in single point of

failure, which means that the islanded microgrid loses coordination performance when the central controller or communication link fails. In previous studies, droop control is famous and widely used in both AC and DC microgrids in order to realize autonomous coordinated control among distributed units [14]-[16]. In [17], an overview of distributed control strategies of power converters is given. And in [18], an advanced parameters design procedure is shown in order to optimize the power sharing performance with droop controlled components. While the modeling of microgrid with droop control is presented in [19], targeting at improving islanding process response. However, in terms of coordinated performance, these control strategies based on droop method meet the limitations: i) droop control is usually implemented on voltage control mode (VCM) converters, while most RES units embrace current control mode (CCM) converters [20], [21]; ii) the conditions of SoC are not taken into account when developing decentralized power control strategies.

In this sense, power line communication methods are proposed in [22]-[25], which inject a range of high frequency components over AC or DC power lines as communication signals to achieve power management among converters. They attract much attention since the coordinated signals (i.e. SoC of ESS, power generation of RES) can be exchanged depend on power lines instead of using external fast communication links. However, these methods intensively introduce a series of high frequency noise to the power cables. Another similar technique employs bus voltage levels as communication signals, which is presented in [26], [27]. Based on these bus voltage signals, ESS and RES units change output power or operation modes. However, this control law needs the mode changing actions, which makes the parameters of each mode hard to be designed and even may cause system instabilities during the dynamic switching process. In addition, few of them discuss the full scenario considering both power generation and demand side management (DSM).

In this paper, a novel coordinated control for islanded DC microgrids is proposed, which consists of two levels: a primary local control and centralized secondary control. The primary control is based on bus-signaling method (BSM), where the bus voltage is regulated as a function of SoC and acts as a coordination signal to control power generation/consumption from RES/distributed loads. In addition, a higher secondary level is presented to restore bus voltage for the applications that require strict bus voltage regulation. Comparing with aforementioned existing studies, the proposed coordinated control in this paper takes the following advantages: i) the coordinated performance of DC islanded microgrid based on SoC conditions is independent from the central controller at upper level, which makes the control of overall microgrid toward more decentralized. ii) the design of primary loop takes into account the inherent difference of VCM and CCM inner loops and therefore can be applied on both VCM and CCM units. iii) the proposed coordinated control can be easily implemented on top of the conventional inner loop algorithms without altering operational modes.

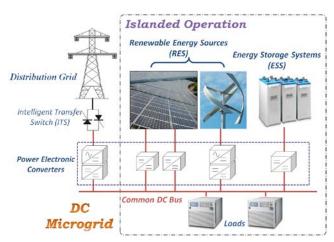

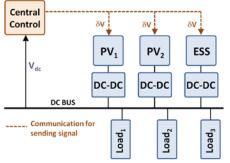

Fig. 1. Typical configuration of a DC microgrid.

This paper is organized as follows. Section II gives a general description of coordinated operation of DC microgrids. Section III illustrates fundamentals of the proposed BSM to achieve autonomous coordinated operation. Section IV introduces the secondary coordinated control for restoring the bus voltage. Section V explains the control algorithms implementation. Finally, Section VI shows the real-time hardware-in-the-loop (HiL) results that verify the proposed coordinated control based on BSM.

#### II. COORDINATED OPERATION OF DC MICROGRIDS

In a DC microgrid as shown in Fig. 1, RES units (such as photovoltaic and wind turbine systems) are used to provide clean energy, while ESS unit is utilized to compensate power fluctuation between power generation and consumption. In grid-connected operation, the power balance between the power generation and load consumption is managed by both main grid and ESS, depending on SoC conditions of ESS and time of use of the electricity from main grid [28]. However, in islanded operation, ESS has to take the main role as energy buffer to compensate unbalanced power. When the ESS is not fully charged, the RESs should operate at the maximum power point (MPP) to make an efficient utilization of renewable energy. When the ESS is approaching to be full of charged so that its SoC is very high, then ESS should limit its input power according to SoC conditions. Coordinately, RES units should decrease power to balance the energy of generated and demanded. Once RESs with curtailed power are not able to supply load consumption, then ESS should start to discharge and RESs restore their MPP operation. On the contrary, if SoC of ESS is too low, ESS should limit its discharging power to avoid system collapse. In this situation, non-critical loads should be disconnected from DC microgrids to decrease power consumption. Therefore, the coordinated operation of DC islanded microgrid system is achieved by managing power flow from all RES, ESS and loads depending on different SoC scenarios.

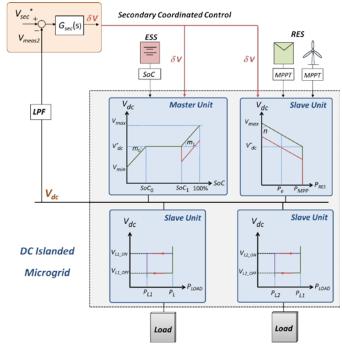

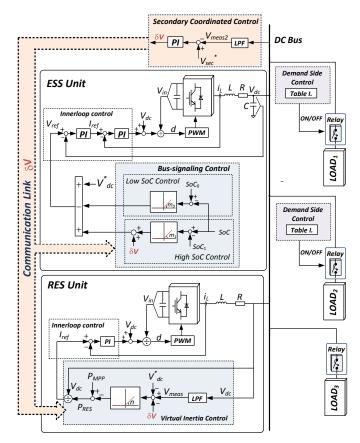

The proposed coordinated control is shown in Fig. 2. The ESS unit is defined as a master unit and controlled in VCM based on BSM in order to regulate DC bus voltages. The BSM

Fig. 2. Proposed coordinated operation of system based on master-slave control.

makes the ESS change bus voltage values depending on SoC conditions, while RES units and loads are defined as slave units to regulate their power according to bus voltage. It is worth noticing that the proposed DC-BSM is applied for islanded operation of DC microgrids. In this case the ESS unit has ability to regulate DC bus voltage to perform signaling actions to slave units. When the DC islanded microgrid is required to transfer into grid-connected mode, the corresponding coordinated control strategy in grid-connected operation can be referred to [28], [29], and is not considered within the scope of this paper.

#### III. PROPOSED BUS-SIGNALING CONTROL STRATEGY

The BSM for the autonomous coordinated control of DC islanded microgrid is classified as ESS master control, RES virtual inertia control and demand side control. These control strategies can be combined together in order to target at different SoC scenarios of ESS in a decentralized way.

#### A. ESS Master Control: Bus-Signaling Control.

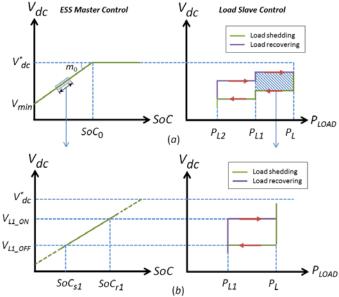

The ESS master control aims at controlling bus voltage based on SoC conditions. According to different SoC scenarios, the ESS bus-signaling control can be classified into high SoC control and low SoC control. When applying the BSM to AC microgrids, the signaling variable should be changed to AC bus frequency in order to regulate power generation from RES units [30]. The corresponding application in AC microgrids can be found in [31].

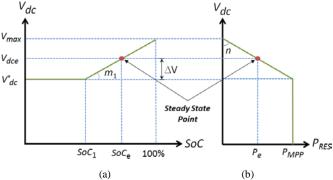

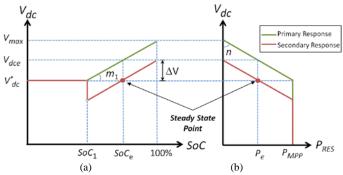

The high SoC control, also called primary coordinated control, is obtained by coordination of ESS and RES units as shown in Fig. 3. There are three ranges of SoC determining bus voltage signaling behavior of ESS that can be expressed as

Fig. 3. Primary coordinated control of ESS and RES. (a) ESS master control with BSM and (b) RES virtual inertial control.

Fig. 4. Demand side control of ESS master control with BSM and load slave control.(a) two steps of load triping proceedures and (b) zoom in on one step of load actions.

$$\begin{cases} V_{dc} = V_{dc}^{*} & \text{if } SoC_{0} \leq SoC \leq SoC_{1} \\ V_{dc} = V_{dc}^{*} + m_{1} \cdot (SoC - SoC_{1}) & \text{if } SoC > SoC_{1} \\ V_{dc} = V_{dc}^{*} - m_{0} \cdot (SoC_{0} - SoC) & \text{if } SoC < SoC_{0} \end{cases}$$

(1a)

The boosting and descending coefficients  $m_1$  and  $m_0$  can be defined as

$$m_1 = \frac{V_{\text{max}} - V_{dc}^*}{100\% - SoC_1} \tag{1b}$$

$$m_0 = \frac{V_{dc}^* - V_{\min}}{SoC_0} \tag{1c}$$

As shown in Fig. 3, when SoC is lower than  $SoC_1$  but higher than  $SoC_0$ , the ESS operates as ideal VCM which regulates its output voltage as nominal value. When SoC is higher than the upper-threshold, the ESS controls its output voltage gradually increasing with slope of  $m_1$  to inform RES units to decrease power generation. When SoC is below lower-threshold, the ESS controls its output voltage decreasing gradually with the slope of  $m_0$ , so that the bus voltage acts as a signal to enable load shedding procedures, as shown in Fig. 4(a). In this paper, noticing that the microgrid coordination performance targets at

using one ESS as master unit with multiple RES units as slave units connected to single bus. When more ESS units are added to the system, additional droop control with virtual resistance should be incorporated in order to achieve power sharing performance and energy management inside storage systems [32]. The voltage references of distributed units can be set in a coordinated way in order to control the current flow between DC buses. Detailed illustrations in this case can be found in [33].

## B. RES Slave Control: Virtual Inertia Control.

In high-SoC scenario, the performance of RES should be coordinated with the bus voltage values, as Fig. 3(b) shows. When bus voltage is kept at nominal value, each RES unit controls its output power at MPP with conventional current control mode. When the bus voltage is continuously increasing, the charging power of ESS should be limited. In this case, each RES unit decreases power from MPP, and this power curtailment of RES units is achieved by adding virtual inertia. The virtual inertia performance of RES units is shown in Fig. 3(b). Here virtual inertia is not presented as in AC system using the variation of the power with respect to the frequency, but with respect to the voltage. As the feedback bus voltage reflects the SoC conditions of ESS, the higher value the bus voltage is, the lower the power generated from RES units. Finally, when the power absorbed by the ESS is low enough to maintain SoC at  $SoC_e$ , the bus voltage level will be stable at  $V_{dce}$ , and power from RES units will be decreased to  $P_e$ . The generated power of each RES can be expressed as follows

$$\begin{cases} P_{RES} = P_{MPP} & \text{if } V_{meas} \leq V_{dc}^* \\ P_{RES} = P_{MPP} - n \cdot (V_{meas} - V_{dc}^*) & \text{if } V_{meas} > V_{dc}^* \end{cases}$$

(2a)

The virtual inertia coefficient n is defined as

$$n = \frac{P_{MPP}}{V_{\text{max}} - V_{dc}^*}$$

(2b)

While the  $V_{meas}$  is obtained with a first order low pass filter, which can be expressed as:

$$V_{meas} = \frac{1}{\tau s + 1} V_{dc} \tag{3}$$

Considering that the ESS is operating in the range of  $SoC_1 < SoC < 100\%$ , taking (3) into (2a) we have

$$P_{RES} = P_{MPP} - \frac{n}{\tau_{S} + 1} \cdot V_{dc} + n \cdot V_{dc}^{*}$$

(4)

Then combing (1a) and (4), the RES output power in high SoC scenario can be written as

$$P_{RES} = P_{MPP} + \frac{n\tau s}{\tau s + 1} \cdot V_{dc} - nm_1 \cdot (SoC - SoC_1)$$

(5)

As different from the conventional RES system that the output power is independent of the bus voltage, the RES units under coordinated control have inertia response with respect to the bus voltage. Consequently, the closed-loop system inertia can be calculated by using small-signal analysis

$$G_{vi}(s) = \frac{\Delta P_{RES}(s)}{s\Delta V_{dc}(s)} = \frac{n\tau}{\tau s + 1}$$

(6)

Fig. 5. Secondary coordinated control of ESS and RES. (a) ESS bussignaling control and (b) RES virtual inertial control.

The  $G_{vi}(s)$  of RES is a virtual value that is determined by the slope coefficient n and time constant  $\tau$ . Usually n is constrained by the allowable bus voltage deviation, then by designing different time constants  $\tau$ , the inertia response of the RES units can be changed.

# C. Demand Side Control.

The demand side control is also obtained by detecting the DC bus voltage to perform the load shedding and recovering procedures as shown in Fig. 4, where Fig. 4(b) is one step of load action zoomed in from Fig. 4(a). It can be observed that a relay action with different voltage levels  $V_{LI\_OFF}$  and  $V_{LI\_ON}$  are assigned to the contactor of loads for tripping and recovering actions, in order to avoid the chattering phenomenon. In addition, if multiple load shedding steps are required, different pre-set bus voltage levels should be applied on different load steps respectively. Based on these voltage levels, the priorities are assigned to these loads with critical and non-critical property respectively, in order to realize a series of load shedding procedures. For example, the non-critical loads assigned with lowest priority can be cut-off when the bus voltage firstly decreases to the specific level. With bus voltage continuously decreasing to a lower level which means that less energy is stored in ESS, another part of loads with a higher priority should be then cut-off. Some candidates for those loads can be disconnected for demand side management includes domestic appliance, plug-in vehicles etc. according to [34]. While some most critical loads such as power supply for data centers or emergency systems should be remained as long as possible. When recovering tripped loads, the reconnected action is in the reverse order that the loads with the higher priority are firstly recovered and those with the lower priority are later connected.

# IV. SECONDARY COORDINATED CONTROL

As previously shown in Fig. 3, with only primary coordinated control of ESS and RES, no communication link is needed between units for coordination performance based on SoC. However, bus voltage deviation  $\Delta V$  is generated in steady state as a result of BSM. This voltage deviation can be designed within an allowable range according to (1), but in the applications that strict voltage regulation is required, additional secondary controller with communication

technology should be implemented in order to regulate the bus voltage at the required value, e.g. the nominal value. Although the communication link between the secondary control and primary control is of low bandwidth, this central secondary control is still optional in the proposed BSM since the coordination performance is already achieved in primary level. This tradeoff between the investment of communication link and high quality of power supply should be decided by customer with respect to different applications.

Fig. 5 shows the secondary coordinated control of ESS and RES units based on BSM. Fig. 5(a) shows the secondary response of ESS. When  $SoC \leq SoC_1$ , which means the ESS is not approaching to be fully charged, the DC bus voltage regulation remains the same as primary control. While in the range of  $SoC > SoC_1$ ,  $V_{dc} - SoC$  curve of the ESS which is determined by primary response shifts downwards, in order to regulate the microgrid DC bus voltage as nominal value. Then, we can modify the control strategy (1a) by adding  $\delta V$ , thus when  $SoC > SoC_1$  (1a) can be rewritten as

$$V_{dc} = V_{dc}^* + m_1 \cdot (SoC - SoC_1) + \delta V$$

if  $SoC > SoC_1$  (7)

This  $\delta V$  generated by secondary control is regulated by the following centralized PI controller

$$\delta V = G_{\text{sec}}(s) \cdot (V_{\text{sec}}^* - V_{meas2}) = \left(k_{p \text{sec}} + \frac{k_{i \text{sec}}}{s}\right) \cdot (V_{\text{sec}}^* - V_{meas2})$$

(8)

Same as (3) presented,  $V_{meas2}$  can be expressed as

$$V_{meas2} = \frac{1}{\tau_2 s + 1} V_{dc} \tag{9}$$

For the secondary control of RES units, if the DC bus voltage is restored as nominal value, the effect of the RES inertia control will be cancelled since they cannot receive the signal of boosting bus voltage to decrease output power. Therefore, to maintain coordinated control, the signaling DC bus voltage value in RES units to regulate output power should also be modified coordinately as Fig. 5(b) shows. The output power generated by RES units in terms of DC bus voltage in (2a) is modified as following

$$\begin{cases} P_{RES} = P_{MPP} & \text{if } V_{meas} \leq V_{dc}^* + \delta V \\ P_{RES} = P_{MPP} - n \cdot (V_{meas} - V_{dc}^* - \delta V) & \text{if } V_{meas} > V_{dc}^* + \delta V \end{cases}$$

$$(10)$$

Notice that instead of using  $V_{dc}^*$  as DC bus voltage threshold, now the  $\delta V$  is also incorporated with  $V_{dc}^*$  to determine the regulation of output power of RES units. In this way, after shifting downward both curves of ESS and RES, the DC bus voltage can be controlled at nominal value in steady state in the range of  $SoC > SoC_1$ , and at the same time ensuring the output power of RES units decreases to constrain the power injecting to ESS.

For coherency, the secondary voltage reference is selected as  $V_{\rm sec}^* = V_{\rm dc}^*$ . By combining (7) and (10), the dynamics of RESs output power and closed-loop system inertia will be the same as (5) and (6). This indicates that the utilization of secondary coordinated control will not change the dynamics and the inertia of RES units which is performed in the primary level.

Fig. 6. Control algorithm for BSM coordinated operation.

# V. CONTROLLER IMPLEMENTATION

The coordinated control implementation is realized through hierarchical control levels where the lower control level receives commands from the higher control level to take actions. The proposed control algorithm of DC islanded microgrids is shown in Fig. 6.

# A. Inner loop Control.

The inner control loops are designed to obtain the desired voltages and currents of each unit. The ESS operates as a grid-forming unit in VCM and regulates the output voltage according to primary control commands. Considering the grid side converter as a buck converter, the inner loop control of ESS with VCM utilizes the voltage-current double loop control over the capacitor voltage and inductor current with two proportional integral (PI) controllers. On the other hand, RESs are controlled in CCM with a single loop PI controller to regulate its output current according to primary level commands. The calculation of inner loop PI controller parameters depends on symmetrical optimum that tuning the cross over frequency and phase margin which can be referred to [35].

#### B. ESS Master Control in Primary Level.

The objective of primary ESS master control is to regulate the DC bus voltage reference in different SoC scenarios, according to Fig. 3 and Fig. 4. In practical applications the SoC estimation error can be incorporated by setting the upper

TABLE I

BUS-SIGNALING OF LOAD SLAVE CONTROL

| Estimated SoC | DC Bus<br>thresholds | Load <sub>1</sub> status | Load <sub>2</sub> status |  |

|---------------|----------------------|--------------------------|--------------------------|--|

| $SoC_{rl}$    | $V_{LI\_ON}$         | ON                       | NC                       |  |

| $SoC_{r2}$    | $V_{L2\_ON}$         | NC                       | ON                       |  |

| $SoC_{sI}$    | $V_{L1\_OFF}$        | OFF                      | NC                       |  |

| $SoC_{s2}$    | $V_{L2\_OFF}$        | NC                       | OFF                      |  |

Note: NC indicates no changing action.

and lower thresholds of SoC in order to reduce the effect of SoC estimation error on the coordination accuracy, e.g. giving 5% of the SoC margin according to [36]. In high SoC control, the bus voltage steadily increases based on (1a), and slope  $m_1$ is designed according to allowable maximum bus voltage  $V_{\rm max}$ as (1b). In low SoC scenario, the bus voltage is decreased based on slope of  $m_0$  which is set according to allowable minimum bus voltage  $V_{\min}$  to enable loads shedding procedure. The bus voltage deviation in emergency and standby power systems should be limited within [-13%, +6%] as demanded in [37]. And this paper adopts power supply systems for communication equipment as an example of DC islanded microgrids in which the nominal value is kept at 48V. The specific technical requirement for this application can be found in [38], in which the DC bus voltage is required to be kept between 43 and 53V. Then  $V_{\min}$  and  $V_{\max}$  are selected as 44V and 50.4V respectively in this paper to meet both technical requirements above.

# C. RES Slave Control in Primary Level.

The primary RES control aims to control the output power of each RES unit according to the bus voltage signaling from ESS, as shown in Fig. 3(b). When the bus voltage is detected above the nominal value, the output power of RES is controlled by using (2a). Also, the inertias of RESs are designed with respect to different time constants of low pass filter and slope n as depicted in (2b). Since the relation of primary RES control is  $P_{RES}$ - $V_{dc}$ , the power reference of RES should be converted to current reference as

$$I_{ref} = \frac{P_{RES}}{V_{dc}} \tag{11}$$

Then this current reference can be sent to the CCM inner control loop. In primary control of RES, the time constant  $\tau$  used in the low pass filter should be much larger than the inner loop regulation time, so that the control performance of these two levels are not interacted with each other and can be tuned independently.

# D. Demand Side Control.

In the demand side control, the process of load shedding and recovering based on two load steps can be referred to Table I, where the SoC thresholds for load shedding and recovering are corresponding to specific voltage levels. Then with relay actions presented in Fig. 4, the bus voltage levels  $V_{L1\ OFF}$  and  $V_{L1\ ON}$  are applied with  $Load_1$  for tripping and

TABLE II

POWER STAGE AND CONTROL PARAMETERS

| POWER STAGE AND C                               |                         |            | TT                 |  |  |  |  |

|-------------------------------------------------|-------------------------|------------|--------------------|--|--|--|--|

| Parameter                                       | Symbol                  | Value      | Unit               |  |  |  |  |

| Power Stage                                     |                         |            |                    |  |  |  |  |

| Nominal DC Bus Voltage                          | ${V_{ m dc}}^*$         | 48         | V                  |  |  |  |  |

| Filter Inductance                               | L                       | 1.8        | mH                 |  |  |  |  |

| Filter Capacitance                              | C                       | 2200       | μF                 |  |  |  |  |

| Inner loop Control                              |                         |            |                    |  |  |  |  |

| ESS Voltage Controller                          | $k_{pV}, k_{iV}$        | 5, 50      | -, s <sup>-1</sup> |  |  |  |  |

| ESS Current Controller                          | $k_{pl}, k_{il}$        | 10,300     | -, s <sup>-1</sup> |  |  |  |  |

| RES Current Controller                          | $k_{pR}, k_{iR}$        | 10,300     | -, s <sup>-1</sup> |  |  |  |  |

| Primary Coordinated Control                     |                         |            |                    |  |  |  |  |

| SoC Upper-threshold                             | $SoC_1$                 | 95         | %                  |  |  |  |  |

| SoC Lower-threshold                             | $SoC_0$                 | 40         | %                  |  |  |  |  |

| Boosting Slope of Bus<br>Voltage                | $m_1$                   | 0.48       | V/%                |  |  |  |  |

| Descending Slope of Bus<br>Voltage              | $m_0$                   | 0.1        | V/%                |  |  |  |  |

| Virtual Inertia Coefficient of RES <sub>1</sub> | $n_1$                   | 83         | W/V                |  |  |  |  |

| Virtual Inertia Coefficient of RES <sub>2</sub> | $n_2$                   | 42         | W/V                |  |  |  |  |

| Secondary Coordinated Control                   |                         |            |                    |  |  |  |  |

| Secondary Bus Voltage<br>Reference              | $V_{sec}$               | 48         | V                  |  |  |  |  |

| Proportional Term                               | $k_{psec}$              | 0.001      | -                  |  |  |  |  |

| Integral Term                                   | $k_{isec}$              | 1          | s <sup>-1</sup>    |  |  |  |  |

| Demand Side Control                             |                         |            |                    |  |  |  |  |

| SoC Thresholds of Load                          | $SoC_{s1}$ ,            | 20,        | 0/                 |  |  |  |  |

| Shedding                                        | $SoC_{s2}$              | 12         | %                  |  |  |  |  |

| SoC Thresholds of Load                          | $SoC_{r1}$ ,            | 31,        | %                  |  |  |  |  |

| Recovering                                      | $SoC_{r2}$              | 23         | 70                 |  |  |  |  |

| Bus Voltage Thresholds of<br>Load Shedding      | $V_{\rm s1},V_{\rm s2}$ | 46, 45.2   | V                  |  |  |  |  |

| Bus Voltage Thresholds of<br>Load Recovering    | $V_{\rm r1},V_{\rm r2}$ | 47.1, 46.3 | V                  |  |  |  |  |

recovering respectively, while  $V_{L2\_OFF}$  and  $V_{L2\_ON}$  are adopted by  $Load_2$  respectively.

## E. Secondary Coordinated Control.

The secondary controller includes a PI controller in  $G_{\rm sec}(s)$  expressed by (8). Then the voltage adjusting term  $\delta V$  is sent to the ESS and RES units at the lower control level in order to maintain the coordinated performance. The modified primary control is achieved by using (7) and (10). In this design procedure of different loops for coordinated control, the bandwidth of control loops is also following a hierarchical manner (decreasing from the lower level to the higher level) [10], so that the time constant in (3) and (9) for primary and secondary control should be designed as  $\tau_2 \gg \tau$ .

# VI. HARDWARE-IN-THE-LOOP RESULTS

In order to verify the proposed control strategy, the hardware-in-the-loop (HiL) real-time simulation is carried out based on dSPACE 1006 platform. Under this test system, the DC islanded microgrid consists of one ESS, two RES units modeling as photovoltaic (PV) generation, and two load

Fig. 7. HiL simulation diagram with proposed coordinated control strategy.

Fig. 8. HiL simulation diagram with conventional coordinated control strategy.

tripping and recovering steps are taken into consideration, in which the power stage and control parameters are shown in Table II.

Fig. 7 shows the overall system diagram under the proposed control structure with bus-signaling method. In power stage part, DC-DC converters are utilized to connect prime sources with common DC bus. ESS and PV generation units are consistently controlled under VCM and CCM respectively over the full range of SoC scenario. The central controller shown in the diagram sends out shifting voltage commands to distributed units through communication link in order to restore bus voltage by measuring DC bus voltage. Since the proposed control system uses electrical DC bus to carry the information of SoC of ESS and power generated from PV units, there is no need to collect these signals by means of communication link and send it to the central controller for data process.

Moreover, the proposed control strategy is compared with the traditional coordinated control method that is described in [12], [13] with numerical simulation results. In this case, the central controller takes the role as energy management system, so that it is necessary to use communication link to collect information of distributed units like SoC and  $P_{RES}$ , and then send it to the central controller for processing, as shown in Fig. 8. When the ESS is not fully charged, the overall system operates in normal case where the ESS and PV units are controlled in VCM and CCM respectively. When detecting that the SoC is above upper-threshold, the central controller sends out mode changing signal to distributed units and makes ESS change to idle mode, while PV units are switched from CCM to VCM mode under off-MPP situation to support loads. The proper operation of PV units in this scenario is ensured by using droop control with proportional virtual impedance that

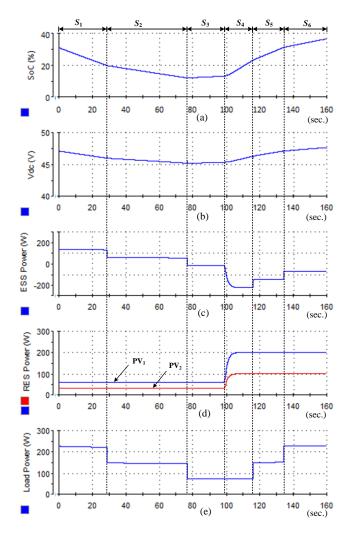

Fig. 9. Simulation results for high SoC case of ESS with proposed control.

has been shown in [13]. The detailed description of this conventional testing scenario for coordinated control can be referred to [12].

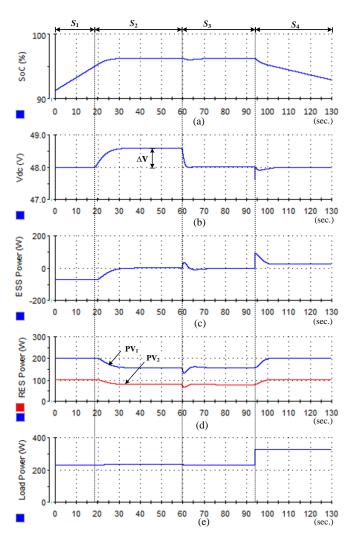

Fig. 9 shows the simulation results for high SoC scenario of ESS with the proposed control. For simplicity, constant irradiation is utilized for two PV generation units in order to compare microgrid performance with and without secondary control. The response of microgrid during different scenarios is summarized as follows:

- Scenario S<sub>1</sub>: The SoC of ESS (Fig. 9(a)) is lower than the upper-threshold 95%. Therefore, overall system operates in normal case which the PV units are operating at MPP with output power of 100 and 200W respectively (Fig. 9(d)) while the ESS is charging the surplus power (Fig. 9(c)) at 70W. In this normal scenario, the bus voltage is fixed at nominal value 48V (Fig. 9(b)).

- Scenario S<sub>2</sub>: The SoC of ESS reaches the upper-threshold 95%, and the primary coordinated control is taking effect. The bus voltage is boosting gradually to 48.6V by ESS with the increase of SoC. It can be seen that due to the autonomous performance of coordinated control, the power of PV units are able to decrease gradually, meanwhile the charging power of ESS is able to reduce

Fig. 10. Simulation results for low SoC case of ESS with proposed control.

to zero. However, the results show that the bus voltage deviation is  $\Delta V{=}0.6V$  due to the solely primary coordinated control.

- Scenario  $S_3$ : The secondary coordinated control is activated. It can be seen that the bus voltage deviation can be restored effectively to the nominal value 48V, without degrading primary coordinated control performance.

- Scenario S<sub>4</sub>: The load consumption increases from 230W to 325W, then the ESS starts to discharge power and SoC decreases from upper-threshold. It can be seen that the instantaneous power increase is absorbed by the ESS, after that PV units gradually restore to MPP, which finally support load consumption together with the ESS, and the overall system comes back to normal operation.

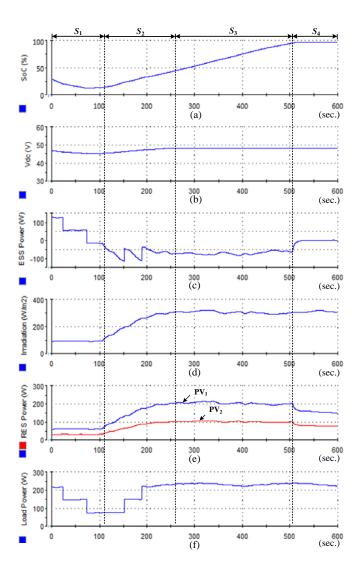

Fig. 10 shows the low SoC case of ESS. There are two steps of load shedding in the simulation. The bus voltage thresholds for disconnecting and reconnecting loads are based on Table II. The load shedding process is described as follows:

Scenario S<sub>1</sub>: The demand side consumes power at 230W in total (Fig. 10(e)) and PV units generate power at 30 and 60W respectively (Fig. 10(d)). In this period, the ESS is discharging power (Fig. 10(c)) and SoC is

Fig. 11. Simulation results in full SoC scenario of ESS.

decreasing accordingly (Fig. 10(a)).

- Scenario  $S_2$ : The SoC of ESS (Fig. 10(a)) reaches the first load shedding threshold at 20%, meanwhile the DC bus voltage drifts from nominal value 48V to 46V (Fig. 10(b)) with the slope 0.1V/%. By detecting this voltage threshold defined in Table I and Table II, the load is shed automatically to 154W with tripping Load<sub>1</sub>. Then the SoC of ESS continues to decrease since the total power consumption is still higher than total power generation. It should be noted if RES units increase power generation to keep SoC increasing before SoC decreases to the load shedding threshold, this load shedding procedure can be then avoided.

- Scenario S<sub>3</sub>: The SoC of ESS reaches the second load shedding threshold at 12%, corresponding to the bus voltage at 45.2V. As the same mechanism shown in Scenario S<sub>2</sub>, the load is shed to 77W by tripping Load<sub>2</sub>.

- Scenario S<sub>4</sub>: The generation of PV units increases to 100 and 200W respectively and then ESS is charging power of 223W. In this period, the SoC is increasing steadily.

- Scenario  $S_5$ : The SoC of ESS reaches the first load recovering threshold at 23%, corresponding to bus

Fig. 12. Simulation results of system performance using conventional control with central control action (Case I) and without central control action (Case II).

Fig. 13. Simulation results of system performance using proposed control with central control action (Case I) and without central control action (CaseII).

voltage 46.3V. By detecting this voltage threshold, Load<sub>2</sub> is reconnected with the relay control shown in Fig. 4.

Scenario S<sub>6</sub>: The SoC of ESS reaches the second load recovering threshold at 31%, corresponding to bus voltage 47.1V. In this case as the same mechanism shown in Scenario S<sub>5</sub>, Load<sub>1</sub> is reconnected finally.

Fig.11 shows the full range of SoC scenario of ESS, taking into account of both intermittent characteristics of PV generation (Fig. 11(d)), and the load fluctuation in demand side (Fig. 11(f)), which is described as follows:

• Scenario  $S_1$ : The power generated from PV units (Fig.

- 11(e)) is continuously lower than the power consumed from demand side, which results in low SoC scenario (Fig. 11(a)). Then bus voltage  $V_{dc}$  is decreased steadily with slope of 0.1V/% based on DC bus-signaling control (Fig. 11(b)). In this case two steps of loads shedding procedures are enabled to cut off non-critical loads (Fig. 11(f)).

- Scenario  $S_2$ : The PV units gradually increase power generation due to the increase of solar irradiance (Fig. 11(d)), while the ESS keeps charging power (Fig. 11(c)). And then two steps of load reconnection are enabled.

- Scenario S<sub>3</sub>: The overall system operates in normal condition, while the DC bus voltage is kept at nominal value 48V.

- Scenario S<sub>4</sub>: The overall system operates in high scenario

of operation when SoC reaches the upper-threshold 95%.

Then both primary and secondary coordinated controllers

are taking effect automatically. It can be seen that due to

coordinated control, the PV power generation can be

decreased gradually to suppress charging power into

ESS, which keeps the SoC from continuously increasing

effectively.

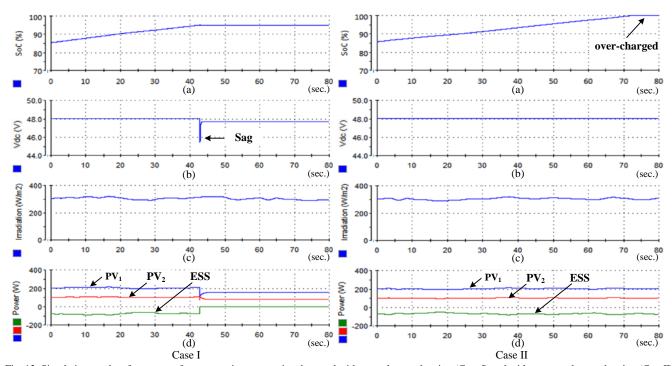

In order to further highlight the advantages and effectiveness of the proposed control strategy, comparison study is carried out which is shown in Fig. 12 and Fig. 13. Fig. 12 is based on conventional central control as Fig. 8 shows. When SoC is not above upper-threshold 95%, the overall system operates in normal condition that ESS is controlled in VCM to support DC bus voltage and PV units operate in CCM following MPP. Under the condition that SoC above upperthreshold 95%, the central controller sends out mode changing signal to all units so that the ESS is in idle mode, and both PV units operate in VCM while sharing the load together by using droop control. Case I and Case II of Fig. 12 show the simulation results of conventional control algorithm with and without central control actions respectively. It can be seen from Fig. 12(d) in Case I that the coordinated control can be achieved well by switching PV units to VCM mode when SoC reaches upper-threshold. In this case the ESS can be effectively kept from over-charging scenario as shown in Fig. 12(a). However there is large transient bus voltage decay when the overall system switching control mode to prevent the overcharging scenario by using conventional control algorithm. Moreover, Case II in Fig. 12 shows the scenario of conventional coordinated algorithm when the central control action fails. This situation can happen when either the central controller or communication link fails. In case II, Fig. 12(a) shows that ESS reaches fully charged however PV units are not able to decrease power to limit charging power to ESS (Fig. 12(d)). Which means, in this case, over-charged situation can happen.

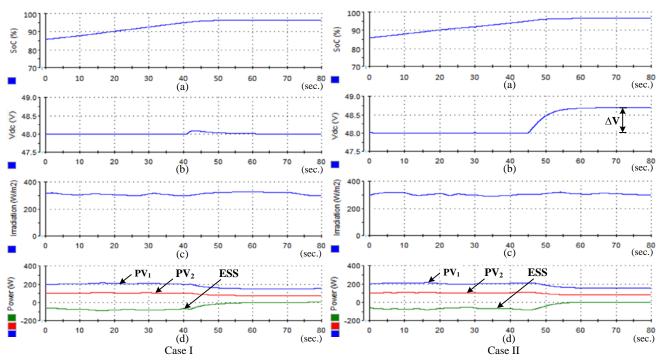

In contrast, Fig. 13 shows the simulation results using the proposed coordinated control strategy under the situation with (Case I) and without (Case II) the central control action. By comparing Case I in both Fig. 12(b) and Fig. 13(b), it can be seen that with the proposed control strategy the islanded DC microgrid is able to achieve a more smooth bus voltage regulation when SoC is approaching to be fully charged. In addition, by contrasting Case II in Fig. 12 and Fig. 13, the simulation results show that with the proposed control strategy, the coordinated performance can be well achieved by regulating power among ESS and PV units (Fig. 13(a)) to keep SoC in a safe range (Fig. 13(d)), even without the interference of the central controller from upper level.

# VII. CONCLUSION

This paper proposed a coordinated control strategy among

RES, ESS and loads based on a novel bus-signaling method. In the primary control level, ESS unit performs the bus-signaling by controlling the bus voltage at different thresholds. Reacting to these bus voltage deviations, the RES units and loads implement virtual inertia control and demand side control respectively. In this way, the autonomous coordinated performance of DC islanded microgrid is achieved in full range of SoC of ESS. Then additional secondary control is implemented to eliminate steady state bus voltage deviation. Finally, the real-time hardware-in-the-loop simulation results verified the proposed coordinated control strategy by presenting the coordinated operation of DC islanded microgrid system under different SoC scenarios.

## REFERENCES

- [1] J. M. Guerrero, M. Chandorkar, T. Lee, P. C. Loh, "Advanced Control Architectures for Intelligent Microgrids—Part I: Decentralized and Hierarchical Control," *IEEE Trans. Ind. Electron*, vol.60, no.4, pp.1254-1262, April 2013

- [2] R. H. Lasseter, "Microgrids," in Proc. IEEE Power Eng. Soc. Winter Meet., 2002, pp. 305–308.

- [3] S. Anand, B. G. Fernandes, M. Guerrero, "Distributed Control to Ensure Proportional Load Sharing and Improve Voltage Regulation in Low-Voltage DC Microgrids," *IEEE Trans. Power Electron.*, vol.28, no.4, pp.1900-1913, April 2013.

- [4] Y. Liu, A. Pratt, P. Kumar, M. Xu, and F. C. Lee, "390V Input VRM for High Efficiency Server Power Architecture," in Proc. 22<sup>nd</sup> Annu. Appl. Power Electron. Conf. Expo., 2007, pp. 1619-1624.

- [5] W. Schulz, "ETSI standards and guides for efficient powering of telecommunication and datacom," in *Proc.29th INTELEC* 2007. pp. 168-173.

- [6] D. Yu, Z. Xiaohu, B. Sanzhong, S. Lukic, and A. Huang, "Review of non-isolated bi-directional DC-DC converters for plug-in hybrid electric vehicle charge station application at municipal parking decks," in Proc. Applied Power Electronics Conference and Exposition, APEC 2010, Twenty-Fifth Annual IEEE, 2010, pp. 1145-1151.

- [7] K. Jong-Yul, K. Seul-Ki, J. Jin-Hong, "Coordinated state-of-charge control strategy for microgrid during islanded operation," in *Proc. IEEE Power Electronics for Distributed Generation Systems (PEDG)*, 2012 3rd IEEE International Symposium on, pp.133-139, June 2012.

- [8] H. Kanchev, L. Di, F. Colas, V. Lazarov, B. Francois, "Energy Management and Operational Planning of a Microgrid With a PV-Based Active Generator for Smart Grid Applications," *IEEE Trans. Ind. Electron*, vol.58, no.10, pp.4583-4592, Oct. 2011.

- [9] K. Jong-Yul, J. Jin-Hong, K. Seul-Ki, C. Changhee, P. June-Ho; K. Hak-Man, N. Kee-Young, "Cooperative Control Strategy of Energy Storage System and Microsources for Stabilizing the Microgrid during Islanded Operation," *IEEE Trans. Power Electron.*, vol.25, no.12, pp.3037,3048, Dec. 2010.

- [10] J. M. Guerrero, J.C. Vasquez, J. Matas, L. G. de Vicuña, M. Castilla, "Hierarchical Control of Droop-Controlled AC and DC Microgrids—A General Approach Toward Standardization," *IEEE Trans. Ind. Electron*, vol.58, no.1, pp.158-172, Jan. 2011.

- [11] J. C. Vasquez, J. M. Guerrero, J. Miret, M. Castilla, L. G. de Vicuña, "Hierarchical Control of Intelligent Microgrids," *IEEE Magazine Ind. Electron*, vol.4, no.4, pp.23-29, Dec. 2010.

- [12] Xiong Liu, Peng Wang, and Poh Chiang Loh, "A Hybrid AC/DC Microgrid and Its Coordination Control," *IEEE Trans. Smart Grid*, vol. 2, no. 2, pp. 278–286, Jun. 2011.

- [13] T. Dragicevic, J. M. Guerrero, J. C. Vasquez, and D. Skrlec, "Supervisory Control of an Adaptive-Droop Regulated DC Microgrid with Battery Management Capability," *Power Electron. IEEE Trans.*, vol. PP, no. 99, p. 1, 2013.

- [14] L. Xu and D. Chen, "Control and Operation of a DC Microgrid With Variable Generation and Energy Storage," *IEEE Trans. Power Deliv.*, vol. 26, no. 4, pp. 2513–2522, Oct. 2011.

- [15] T. M. Haileselassie and K. Uhlen, "Impact of DC Line Voltage Drops on Power Flow of MTDC Using Droop Control," *IEEE Trans. Power Syst.*, vol. 27, no. 3, pp. 1441–1449, Aug. 2012.

- [16] P. Karlsson, J. Svensson, "DC bus voltage control for a distributed power system," *IEEE Trans. Power Electron.*, vol.18, no.6, pp.1405-1412, Nov. 2003.

- [17] J. Rocabert, A. Luna, F. Blaabjerg, and P. Rodríguez, "Control of Power Converters in AC Microgrids," *IEEE Trans. Power Electron.*, vol. 27, no. 11, pp. 4734–4749, Nov. 2012.

- [18] I. Y. Chung, W. Liu, D. A. Cartes and E. G. Collins, "Control Methods of Inverter-Interfaced Distributed Generators in a Microgrid System," *IEEE Trans. Ind. Appl.*, vol. 46, no. 3, pp. 1078–1088, 2010.

- [19] F. Katiraei, M. R. Iravani, and P. W. Lehn, "Micro-Grid Autonomous Operation During and Subsequent to Islanding Process," *IEEE Trans. Power Deliv.*, vol. 20, no. 1, pp. 248–257, Jan. 2005.

- [20] F. Blaabjerg, R. Teodorescu, M. Liserre, A. V. Timbus, "Overview of Control and Grid Synchronization for Distributed Power Generation Systems," *IEEE Trans. Ind. Electron*, vol.53, no.5, pp.1398-1409, Oct. 2006.

- [21] S. B. Kjaer, J. K. Pedersen, F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Trans. Ind. Appl.*, vol.41, no.5, pp.1292-1306, Sept.-Oct. 2005.

- [22] T. Dragicevic, J. M. Guerrero, and J. C. Vasquez, "A Distributed Control Strategy for Coordination of an Autonomous LVDC Microgrid Based on Power-Line Signaling," *Ind. Electron. IEEE Trans.*, vol. 61, no. 7, pp. 3313–3326, 2014.

- [23] D. Hirata, N. Kuwabara, Y. Akiyama, H. Yamane, "Influence of appliance state on transmission characteristics of indoor AC mains lines in frequency range used power line communication," in *Proc. Int. EMC* 2005. pp.715-720, Vol. 3, Aug. 2005.

- [24] W. Stefanutti, S. Saggini, P. Mattavelli, M. Ghioni, "Power Line Communication in Digitally Controlled DC–DC Converters Using Switching Frequency Modulation," *IEEE Trans. Ind. Electron*, vol.55, no.4, pp.1509-1518, April 2008.

- [25] A. Pinomaa, J. Ahola, and A. Kosonen, "Power-line communication-based network architecture for LVDC distribution system," in *Proc. IEEE Int.* Symp. Power Line Commun. Appl., Apr. 2011, pp. 358–363.

- [26] D. Boroyevich, I. Cvetkovic, D. Dong, R. Burgos, F. Wang, F. Lee, "Future electronic power distribution systems a contemplative view," in *Proc. Int.* 12<sup>th</sup> Optimization of Electrical and Electronic Equipment (OPTIM), pp.1369-1380, May 2010.

- [27] J. Schonberger, R. Duke, S. D. Round, "DC-Bus Signaling: A Distributed Control Strategy for a Hybrid Renewable Nanogrid," *IEEE Trans. Ind. Electron*, vol.53, no.5, pp.1453,1460, Oct. 2006.

- [28] K. T. Tan, P. L. So, Y. C. Chu, and M. Z. Q. Chen, "Coordinated Control and Energy Management of Distributed Generation Inverters in a Microgrid," *IEEE Trans. Power Deliv.*, vol. 28, no. 2, pp. 704–713, Apr. 2013.

- [29] L. Xu and D. Chen, "Control and Operation of a DC Microgrid With Variable Generation and Energy Storage," *IEEE Trans. Power Deliv.*, vol. 26, no. 4, pp. 2513–2522, Oct. 2011.

- [30] SMA Technologies AG: "Sunny Island 5048 Installation & Instruction Manual," 2006.

- [31] Z. Yang, Y. Che, and C. Wang, "Construction, operation and control of a laboratory-scale microgrid," in 2009 International Conference on Sustainable Power Generation and Supply, 2009, pp. 1–5.

- [32] X. Lu, K. Sun, J. M. Guerrero, J. C. Vasquez, and L. Huang, "State-of-Charge Balance Using Adaptive Droop Control for Distributed Energy Storage Systems in DC Microgrid Applications," *IEEE Trans. Ind. Electron.*, vol. 61, no. 6, pp. 2804–2815, Jun. 2014.

- [33] T. Dragicevic, J. C. Vasquez, J. M. Guerrero, and D. Skrlec, "Advanced LVDC Electrical Power Architectures and Microgrids: A step toward a new generation of power distribution networks.," *IEEE Electrif. Mag.*, vol. 2, no. 1, pp. 54–65, Mar. 2014.

- [34] A. Brooks, E. Lu, D. Reicher, C. Spirakis, and B.Weihl, "Demand dispatch, using real-time control of demand to help balance generation and load," *IEEE Power & Energy Magazine*, May/June 2010, vol. 8, no. 3, pp. 20–29.

- [35] V. Blasko and V. Kaura, "A new mathematical model and control of a three-phase AC-DC voltage source converter," *IEEE Trans. Power Electron.*, vol. 12, no. 1, pp. 116–123, 1997.

- [36] B. Xiao, Y. Shi, and L. He, "A universal state-of-charge algorithm for batteries," *Design Automation Conference (DAC)*, 2010 47th ACM/IEEE, vol., no., pp.687,692, 13-18 June 2010.

- [37] IEEE Recommended Practice for Emergency and Standby Power Systems for Industrial and Commercial Applications. IEEE Standard 446-1995.

- [38] Nippon Telegraph and Telephone Corporation, "Technical Requirements for Power-Supply Interface of Communications Equipment," 2008.

Dan Wu received the B.S. degree and M.S. degree in Electrical Engineering from Beijing Institute of Technology, Beijing, China, in 2009 and 2012 respectively. Currently, she is working towards her Ph.D. degree at the department of Energy Technology, Aalborg University, Denmark. She is member of the Microgrid Research Group at Aalborg University. Her areas of interest include microgrids, distributed generation systems.

Fen Tang received the B.S. degree in Electrical Engineering and the Ph.D. degree in Power Electronics & Electric Drives from Beijing Jiaotong University, Beijing, China, in 2006 and 2013, respectively. She is currently a Postdoc in Beijing Jiaotong University. From Jan. 2013 to Jan. 2014 she was a guest Postdoc at Department of Energy Technology, Aalborg University, Denmark.

Her research interests include microgrid, wind power generation system, power converter for

renewable generation systems, power quality, and motor control.

**Tomislav Dragicevic** (S'09-M'13) received the M.E.E. and the Ph.D. degree from the Faculty of Electrical Engineering, Zagreb, Croatia, in 2009 and 2013, respectively. Since 2010, he has been actively cooperating in an industrial project related with design of electrical power supply for remote telecommunication stations. Since 2013 he has been a fulltime Post-Doc at Aalborg University in Denmark. His fields of interest include modeling,

control and energy management of intelligent electric vehicle charging stations and other types of microgrids based on renewable energy sources and energy storage technologies.

Josep M. Guerrero (S'01-M'04-SM'08-F'14) received the B.S. degree in telecommunications engineering, the M.S. degree in electronics engineering, and the Ph.D. degree in power electronics from the Technical University of Catalonia, Barcelona, in 1997, 2000 and 2003, respectively. Since 2011, he has been a Full Professor with the Department of Energy Technology, Aalborg University, Denmark, where he is responsible for the Microgrid Research Program. From 2012 he is a guest Professor at the

Chinese Academy of Science and the Nanjing University of Aeronautics and Astronautics; and from 2014 he is chair Professor in Shandong University. His research interests is oriented to different microgrid aspects, including power electronics, distributed energy-storage systems, hierarchical and

cooperative control, energy management systems, and optimization of microgrids and islanded minigrids. Prof. Guerrero is an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, and the IEEE Industrial Electronics Magazine, and an Editor for the IEEE TRANSACTIONS on SMART GRID. He has been Guest Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS Special Issues: Power Electronics for Wind Energy Conversion and Power Electronics for Microgrids; the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS Special Sections: Uninterruptible Power Supplies systems, Renewable Energy Systems, Distributed Generation and Microgrids, and Industrial Applications and Implementation Issues of the Kalman Filter; and the IEEE TRANSACTIONS on SMART GRID Special Issue on Smart DC Distribution Systems. He was the chair of the Renewable Energy Systems Technical Committee of the IEEE Industrial Electronics Society. In 2014 he was awarded by Thomson Reuters as Highly Cited Researcher. The same year he was elevated to IEEE Fellow for contributions to distributed power systems and microgrids.

Juan C. Vasquez (M'12) received the B.S. degree in Electronics Engineering from Autonomous University of Manizales, Colombia in 2004 where he has been teaching courses on digital circuits, servo systems and flexible manufacturing systems. In 2009, He received his Ph.D degree from the Technical University of Catalonia, Barcelona, Spain in 2009 at the Department of Automatic Control Systems and Computer Engineering, from Technical University of Catalonia, Barcelona (Spain), where he worked as

Post-doc Assistant and also teaching courses based on renewable energy systems. Since 2011, he has been an Assistant Professor in microgrids at the Institute of Energy Technology, Aalborg University, Aalborg, Denmark, where he is the co-responsible of the microgrids research program. His current research interests include operation, power management, hierarchical control and optimization applied to Distributed Generation in AC/DC microgrids. He is currently member of the Technical Committee on Renewable Energy Systems TC-RES.