2/16/06

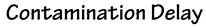

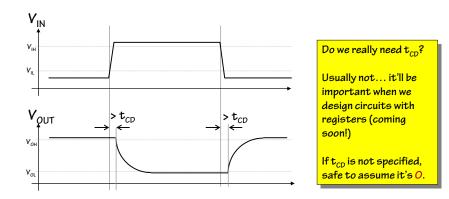

an optional, additional timing spec

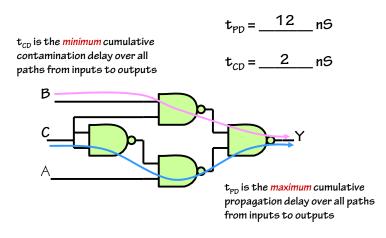

### INVALID inputs take time to propagate, too...

CONTAMINATION DELAY, t<sub>CD</sub> A LOWER BOUND on the delay from any invalid input to an invalid output

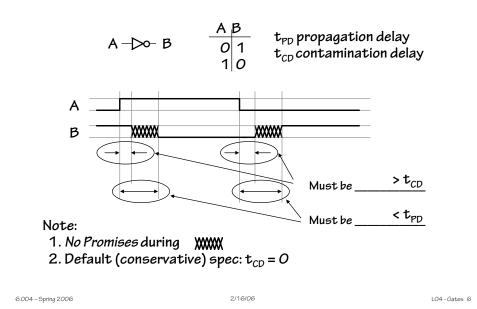

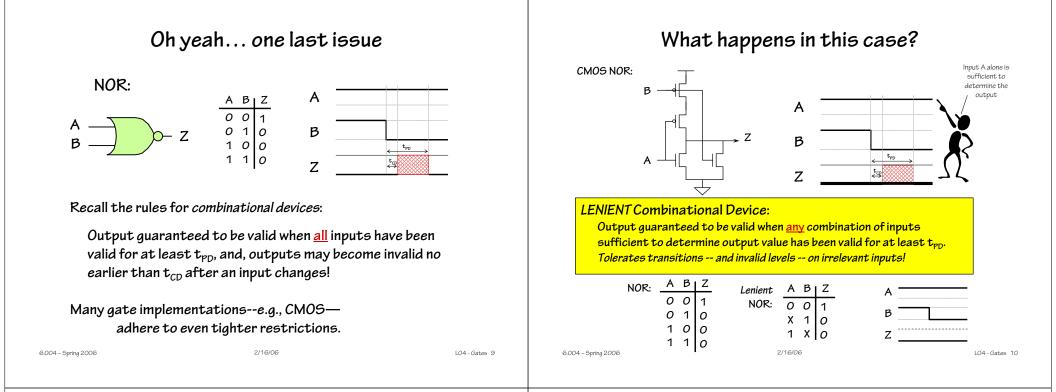

# The Combinational Contract

### Acyclic Combinational Circuits

2/16/06

If NAND gates have a  $t_{PD}$  = 4nS and  $t_{CD}$  = 1nS

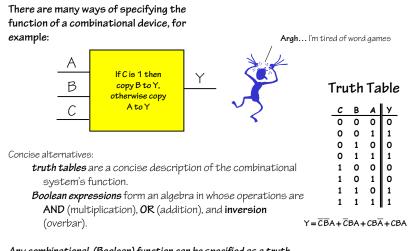

# Functional Specifications

Any combinational (Boolean) function can be specified as a truth table or an equivalent <u>sum-of-products</u> Boolean expression!

6.004 - Spring 2006

LO4-Gates 5

# **Basic Gate Repertoire**

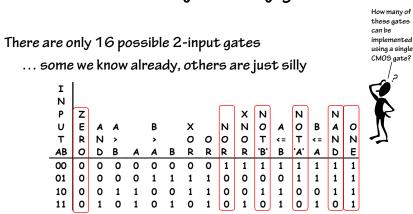

Are we sure we have all the gates we need? Just how many two-input gates are there?

| AND |   |    | OR |    | NAND |    | NOR |  |

|-----|---|----|----|----|------|----|-----|--|

| AB  | У | AB | У  | AB | У    | AB | У   |  |

| 00  |   | 00 | 0  | 00 | 1    | 00 |     |  |

| 01  | 0 | 01 | 1  | 01 | 1    | -  | 0   |  |

| 10  | 0 | 10 | 1  | 10 | 1    | 10 | 0   |  |

| 11  | 1 | 11 | 1  | 11 | 0    | 11 | 0   |  |

Hmmmm... all of these have 2-inputs (no surprise) ... each with 4 combinations, giving  $2^2$  output cases  $2^2 = 2^4 = 16$

How many ways are there of assigning 4 outputs?

### There are only so many gates

CMOS gates are inverting; we can always respond positively to positive transitions by cascaded gates. But suppose our logic yielded cheap *positive* functions, while inverters were expensive...

### Logic Geek Party Games

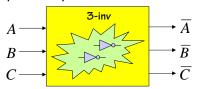

You have plenty of ANDs and ORs, but only 2 inverters. Can you invert more than 2 independent inputs?

$\label{eq:CHALLENGE:Come up with a combinational circuit using ANDs, ORs, and at most 2 inverters that inverts A, B, and C !$

Such a circuit exists. What does that mean?

- If we can invert 3 signals using 2 inverters, can we use 2 of the pseudoinverters to invert 3 more signals?

- Do we need only 2 inverters to make ANY combinational circuit?

- Hint: there's a subtle difference between our 3-inv device and three combinational inverters!

#### Is our 3-inv device LENIENT?

2/16/06

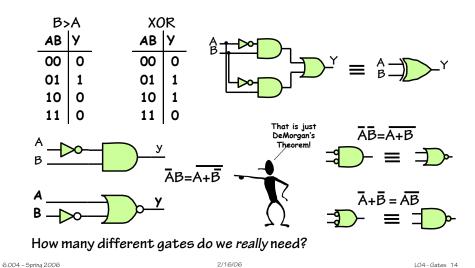

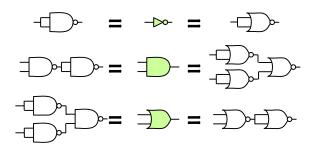

Fortunately, we can get by with a few basic gates...

AND, OR, and NOT are sufficient... (cf Boolean Expressions):

LO4-Gates 13

### One will do!

### NANDs and NORs are universal:

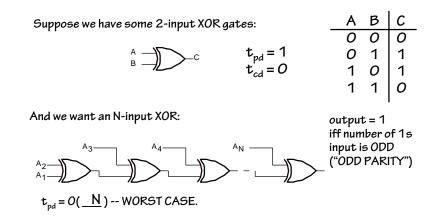

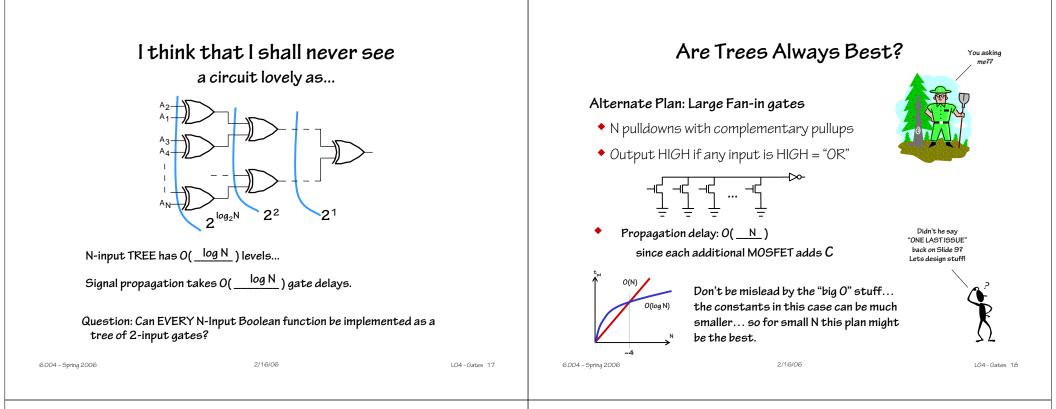

### Ah!, but what if we want more than 2-inputs

# Stupid Gate Tricks

#### Can we compute N-input XOR faster?

# Here's a Design Approach

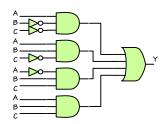

| Truth Table                                      |             |   | ele | 1) Write out our functional spec as a truth table                        |

|--------------------------------------------------|-------------|---|-----|--------------------------------------------------------------------------|

| С                                                | В           | A | У   | 2) Write down a Boolean expression with                                  |

| 0                                                | 0<br>0<br>1 | 0 | 0   | terms covering each '1' in the output:                                   |

| 0                                                | 0           | 1 | 1   |                                                                          |

| 0                                                | 1           | 0 | 0   | $Y = \overline{C}\overline{B}A + \overline{C}BA + CB\overline{A} + CBA$  |

| 0                                                | 1           | 1 | 1   |                                                                          |

| 1                                                | 0           | 0 | 0   |                                                                          |

| 1                                                | 0<br>1<br>1 | 1 | 0   | 3) Wire up the gates, call it a day, and                                 |

| 1                                                | 1           | 0 | 1   | declare success!                                                         |

| 1                                                | 1           | 1 | 1   | ueciai e success:                                                        |

| -it's systematic!<br>-it works!<br>▼ -it's easy! |             |   |     | This approach will always give us<br>Boolean expressions in a particular |

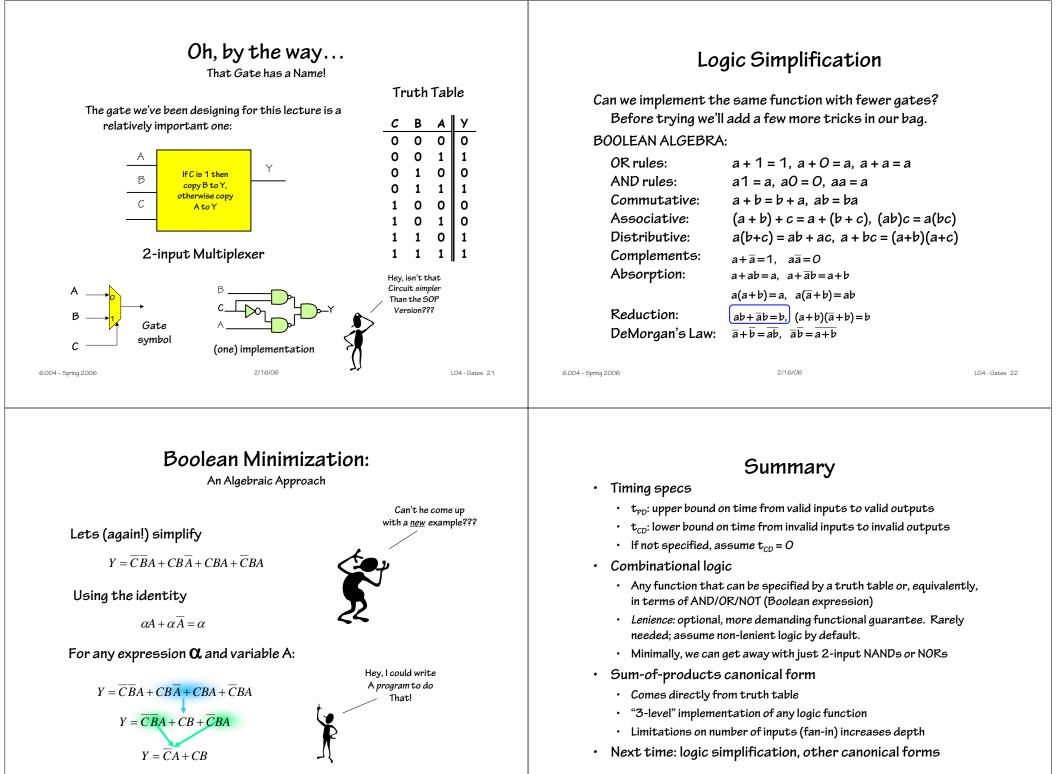

# Straightforward Synthesis

We can implement SUM-OF-PRODUCTS with just three levels of logic.

#### INVERTERS/AND/OR

Propagation delay --No more than 3 gate delays (ignoring fan-in)

·it's easy! ·are we done vet???

form: SUM-OF-PRODUCTS

LO4*-Ga*tes 23