# Cache-Oblivious Algorithms

by Harald Prokop

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY.

June 1999

© Massachusetts Institute of Technology 1999. All rights reserved.

| Author       |                                                                                            |

|--------------|--------------------------------------------------------------------------------------------|

|              | Department of Electrical Engineering and Computer Science<br>May 21, 1999                  |

| Certified by |                                                                                            |

| certified by | Charles E. Leiserson<br>Professor of Computer Science and Engineering<br>Thesis Supervisor |

| Accepted by  |                                                                                            |

|              | Arthur C. Smith<br>Chairman, Departmental Committee on Graduate Students                   |

## Cache-Oblivious Algorithms

by Harald Prokop

Submitted to the Department of Electrical Engineering and Computer Science on May 21, 1999 in partial fulfillment of the requirements for the degree of Master of Science.

#### Abstract

This thesis presents "cache-oblivious" algorithms that use asymptotically optimal amounts of work, and move data asymptotically optimally among multiple levels of cache. An algorithm is *cache oblivious* if no program variables dependent on hardware configuration parameters, such as cache size and cache-line length need to be tuned to minimize the number of cache misses.

We show that the ordinary algorithms for matrix transposition, matrix multiplication, sorting, and Jacobi-style multipass filtering are not cache optimal. We present algorithms for rectangular matrix transposition, FFT, sorting, and multipass filters, which are asymptotically optimal on computers with multiple levels of caches. For a cache with size Z and cache-line length L, where  $Z = \Omega(L^2)$ , the number of cache misses for an  $m \times n$  matrix transpose is  $\Theta(1 + mn/L)$ . The number of cache misses for either an n-point FFT or the sorting of n numbers is  $\Theta(1 + (n/L)(1 + \log_Z n))$ . The cache complexity of computing n time steps of a Jacobi-style multipass filter on an array of size n is  $\Theta(1 + n/L + n^2/ZL)$ . We also give an  $\Theta(mnp)$ -work algorithm to multiply an  $m \times n$  matrix by an  $n \times p$  matrix that incurs  $\Theta(m + n + p + (mn + np + mp)/L + mnp/L\sqrt{Z})$  cache misses.

We introduce an "ideal-cache" model to analyze our algorithms, and we prove that an optimal cache-oblivious algorithm designed for two levels of memory is also optimal for multiple levels. We further prove that any optimal cache-oblivious algorithm is also optimal in the previously studied HMM and SUMH models. Algorithms developed for these earlier models are perforce *cache-aware*: their behavior varies as a function of hardware-dependent parameters which must be tuned to attain optimality. Our cache-oblivious algorithms achieve the same asymptotic optimality on all these models, but without any tuning.

Thesis Supervisor: Charles E. Leiserson

Title: Professor of Computer Science and Engineering

# Acknowledgments

I am extremely grateful to my advisor Charles E. Leiserson. He has greatly helped me both in technical and nontechnical matters. Without his insight, suggestions, and excitement, this work would have never taken place. Charles also helped with the write-up of the paper on which this thesis is based. It is amazing how patiently Charles can rewrite a section until it has the quality he expects.

Most of the work presented in this thesis has been a team effort. I would like to thank those with whom I collaborated: Matteo Frigo, Charles E. Leiserson, and Sridhar Ramachandran. Special thanks to Sridhar who patiently listened to all my (broken) attempts to prove that cache-oblivious sorting is impossible.

I am privileged to be part of the stimulating and friendly environment of the Supercomputing Technologies research group of the MIT Laboratory of Computer Science. I would like to thank all the members of the group, both past and present, for making it a great place to work. Many thanks to Don Dailey, Phil Lisiecki, Dimitris Mitsouras, Alberto Medina, Bin Song, and Volker Strumpen.

The research in this thesis was supported in part by the Defense Advanced Research Projects Agency (DARPA) under Grant F30602-97-1-0270 and by a fellowship from the Cusanuswerk, Bonn, Germany.

Finally, I want to thank my family for their love, encouragement, and help, which kept me going during the more difficult times.

HARALD PROKOP Cambridge, Massachusetts May 21, 1999

## **Contents**

| 1                         | Intr                         | roduction                               | 9              |

|---------------------------|------------------------------|-----------------------------------------|----------------|

| 2                         | Matrix multiplication        |                                         |                |

| 3                         | Matrix transposition and FFT |                                         |                |

| 4                         | Funnelsort                   |                                         |                |

| 5                         | Distribution sort            |                                         | 29             |

| 6 Jacobi multipass filter |                              |                                         | 35             |

|                           | 6.1<br>6.2<br>6.3            | Iterative algorithm                     | 36<br>37<br>41 |

|                           | 6.4                          | Experimental results                    | 43             |

| 7                         | Cacl                         | ne complexity of ordinary algorithms    | 45             |

|                           | 7.1                          | Matrix multiplication                   | 47             |

|                           | 7.2                          | Matrix transposition                    | 48             |

|                           | 7.3                          | Mergesort                               | 49             |

| 8 Other cache models      |                              |                                         | 51             |

|                           | 8.1                          | Two-level models                        | 51             |

|                           | 8.2                          | Multilevel ideal caches                 | 52             |

|                           | 8.3                          | The SUMH model                          | 53             |

|                           | 8.4                          | The HMM model                           | 54             |

| 9                         | Rela                         | ted work                                | 57             |

| 10                        | Con                          | clusion                                 | 59             |

|                           | 10.1                         | Engineering cache-oblivious algorithms  | 60             |

|                           |                              | Cache-oblivious data structures         | 61             |

|                           | 10.3                         | Complexity of cache obliviousness       | 62             |

|                           |                              | Compiler support for divide-and-conquer | 63             |

|                           | 10.5                         | The future of divide-and-conquer        | 64             |

| Α                         | Bibl                         | iograpy                                 | 67             |

### **SECTION 1**

## Introduction

Resource-oblivious algorithms that nevertheless use resources efficiently offer advantages of simplicity and portability over resource-aware algorithms whose resource usage must be programmed explicitly. In this thesis, we study cache resources, specifically, the hierarchy of memories in modern computers. We exhibit several "cache-oblivious" algorithms that use cache as effectively as "cache-aware" algorithms.

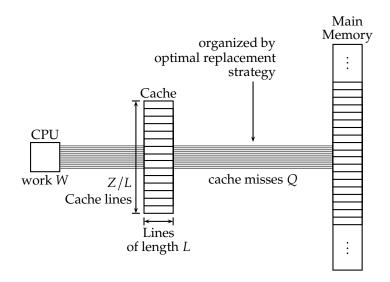

Before discussing the notion of cache obliviousness, we introduce the  $(\mathbf{Z}, \mathbf{L})$  *ideal-cache model* to study the cache complexity of algorithms. This model, which is illustrated in Figure 1-1, consists of a computer with a two-level memory hierarchy consisting of an ideal (data) cache of Z words and an arbitrarily large main memory. Because the actual size of words in a computer is typically a small, fixed size (4 bytes, 8 bytes, etc.), we shall assume that word size is constant; the particular constant does not affect our asymptotic analyses. The cache is partitioned into *cache lines*, each consisting of L consecutive words that are always moved together between cache and main memory. Cache designers typically use L > 1, banking on spatial locality to amortize the overhead of moving the cache line. We shall generally assume in this thesis that the cache is *tall*:

$$Z = \Omega(L^2) , \qquad (1.1)$$

which is usually true in practice.

The processor can only reference words that reside in the cache. If the referenced word belongs to a line already in cache, a *cache hit* occurs, and the word is

Figure 1-1: The ideal-cache model

delivered to the processor. Otherwise, a *cache miss* occurs, and the line is fetched into the cache. The ideal cache is *fully associative* [24, Ch. 5]: Cache lines can be stored anywhere in the cache. If the cache is full, a cache line must be evicted. The ideal cache uses the optimal off-line strategy of replacing the cache line whose next access is farthest in the future [7], and thus it exploits temporal locality perfectly.

An algorithm with an input of size n is measured in the ideal-cache model in terms of its *work complexity* W(n)—its conventional running time in a RAM model [4]—and its *cache complexity* Q(n; Z, L)—the number of cache misses it incurs as a function of the size Z and line length L of the ideal cache. When Z and L are clear from context, we denote the cache complexity as simply Q(n) to ease notation.

We define an algorithm to be *cache aware* if it contains parameters (set at either compile-time or runtime) that can be tuned to optimize the cache complexity for the particular cache size and line length. Otherwise, the algorithm is *cache oblivious*. Historically, good performance has been obtained using cache-aware algorithms, but we shall exhibit several cache-oblivious algorithms for fundamental problems that are asymptotically as efficient as their cache-aware counterparts.

To illustrate the notion of cache awareness, consider the problem of multiplying two  $n \times n$  matrices A and B to produce their  $n \times n$  product C. We assume that the three matrices are stored in row-major order, as shown in Figure 2-1(a). We further assume that n is "big," i.e., n > L, in order to simplify the analysis. The conventional way to multiply matrices on a computer with caches is to use a **blocked** algorithm [22, p. 45]. The idea is to view each matrix M as consist-

ing of  $(n/s) \times (n/s)$  submatrices  $M_{ij}$  (the blocks), each of which has size  $s \times s$ , where s is a tuning parameter. The following algorithm implements this strategy:

```

BLOCK-MULT (A, B, C, n)

1 for i \leftarrow 1 to n/s

2 do for j \leftarrow 1 to n/s

3 do for k \leftarrow 1 to n/s

4 do ORD-MULT (A_{ik}, B_{kj}, C_{ij}, s)

```

where ORD-MULT (A, B, C, s) is a subroutine that computes  $C \leftarrow C + AB$  on  $s \times s$  matrices using the ordinary  $O(s^3)$  algorithm (see Section 7.1). (This algorithm assumes for simplicity that s evenly divides n. In practice, s and n need have no special relationship, which yields more complicated code in the same spirit.)

Depending on the cache size of the machine on which BLOCK-MULT is run, the parameter s can be tuned to make the algorithm run fast, and thus BLOCK-MULT is a cache-aware algorithm. To minimize the cache complexity, we choose s as large as possible such that the three  $s \times s$  submatrices simultaneously fit in cache. An  $s \times s$  submatrix is stored on  $\Theta(s+s^2/L)$  cache lines. From the tall-cache assumption (1.1), we can see that  $s = \Theta(\sqrt{Z})$ . Thus, each of the calls to ORD-MULT runs with at most  $Z/L = \Theta(s+s^2/L)$  cache misses needed to bring the three matrices into the cache. Consequently, the cache complexity of the entire algorithm is  $\Theta(n+n^2/L+(n/\sqrt{Z})^3(Z/L)) = \Theta(n+n^2/L+n^3/L\sqrt{Z})$ , since the algorithm must read  $n^2$  elements, which reside on  $\lfloor n^2/L \rfloor$  cache lines.

The same bound can be achieved using a simple cache-oblivious algorithm that requires no tuning parameters such as the *s* in BLOCK-MULT. We present such an algorithm, which works on general rectangular matrices, in Section 2. The problems of computing a matrix transpose and of performing an FFT also succumb to remarkably simple algorithms, which are described in Section 3. Cache-oblivious sorting poses a more formidable challenge. In Sections 4 and 5, we present two sorting algorithms, one based on mergesort and the other on distribution sort, both of which are optimal. Section 6 compares an optimal recursive algorithm with an "ordinary" iterative algorithm, both of which compute a multipass filter over one-dimensional data. It also provides some brief empirical results for this problem. In Section 7, we show that the ordinary algorithms for matrix transposition, matrix multiplication, and sorting are not cache optimal.

The ideal-cache model makes the perhaps-questionable assumption that memory is managed automatically by an optimal cache replacement strategy. Although the current trend in architecture does favor automatic caching over programmer-specified data movement, Section 8 addresses this concern theoretically. We show

that the assumptions of two hierarchical memory models in the literature, in which memory movement is programmed explicitly, are actually no weaker than ours. Specifically, we prove (with only minor assumptions) that optimal cache-oblivious algorithms in the ideal-cache model are also optimal in the hierarchical memory model (HMM) [1] and in the serial uniform memory hierarchy (SUMH) model [5, 42]. Section 9 discusses related work, and Section 10 offers some concluding remarks.

Many of the results in this thesis are based on a joint paper [21] coauthored by Matteo Frigo, Charles E. Leiserson, and Sridhar Ramachandran.

# Matrix multiplication

This section describes and analyzes an algorithm for multiplying an  $m \times n$  matrix by an  $n \times p$  matrix cache-obliviously using  $\Theta(mnp)$  work and incurring  $\Theta(m+n+p+mn+np+mp)/L+mnp/L\sqrt{Z})$  cache misses. These results require the tall-cache assumption (1.1) for matrices stored in row-major layout format, but the assumption can be relaxed for certain other layouts. We also show that Strassen's algorithm [38] for multiplying  $n \times n$  matrices, which uses  $\Theta(n^{\log_2 7})$  work, incurs  $\Theta(1+n^2/L+n^{\log_2 7}/L\sqrt{Z})$  cache misses.

The following algorithm extends the optimal divide-and-conquer algorithm for square matrices described in [9] to rectangular matrices. To multiply an  $m \times n$  matrix A by an  $n \times p$  matrix B, the algorithm halves the largest of the three dimensions and recurs according to one of the following three cases:

$$AB = \begin{pmatrix} A_1 \\ A_2 \end{pmatrix} B = \begin{pmatrix} A_1 B \\ A_2 B \end{pmatrix} , \qquad (2.1)$$

$$AB = (A_1 \ A_2) \begin{pmatrix} B_1 \\ B_2 \end{pmatrix} = A_1 B_1 + A_2 B_2 ,$$

(2.2)

$$AB = A (B_1 \ B_2) = (AB_1 \ AB_2) .$$

(2.3)

In case (2.1), we have  $m \ge \max\{n, p\}$ . Matrix A is split horizontally, and both halves are multiplied by matrix B. In case (2.2), we have  $n \ge \max\{m, p\}$ . Both matrices are split, and the two halves are multiplied. In case (2.3), we have  $p \ge \max\{m, n\}$ . Matrix B is split vertically, and each half is multiplied by A. For square matrices, these three cases together are equivalent to the recursive multiplication

```

(a) 1 2 3 4 5 6 7 8

(b) 1

9 10 11 12 13 14 15 16

17 18 19 20 21 22 23 24

11 19 27 35 43 51 59

12/20/28/36/44/52/60

25 26 27 28 29 30 31 32

13 21 29 37 45 53

3<del>3 34 35 36 37 38 39 4</del>0

14 22 30 38 46 54

41 42 43 44 45 46 47 48

15 23 31 39 47 55

49 50 51 52 53 54 55 56

57 58 59 60 61 62 63 64

(c) 1 2 3 4 1<del>7 18 19 2</del>0

5 6 7 8 2<del>1 22 23 2</del>4

9 10 11 12 25 26 27 28

13 14 15 16 29 30 31 32

3<del>3 34 35 3</del>6 49 50 51 52

3<del>3 3</del>4 37 38 49 50 53 54

3<del>5 3</del>6 3<del>9 4</del>0 5<del>1 5</del>2 5<del>5 5</del>6

3<del>7 38 39 4</del>0 <del>53 54 55 5</del>6

41 42 43 44 57 58 59 60

4<del>1 4</del>2 4<del>5 4</del>6 5<del>7 5</del>8 6<del>1 6</del>2

45 46 47 48 61 62 63 64

```

**Figure 2-1:** Layout of a  $16 \times 16$  matrix in (a) row major, (b) column major, (c)  $4 \times 4$ -blocked, and (d) bit-interleaved layouts.

algorithm described in [9]. The base case occurs when m = n = p = 1, in which case the two elements are multiplied and added into the result matrix.

Although this straightforward divide-and-conquer algorithm contains no tuning parameters, it uses cache optimally. To analyze the algorithm, we assume that the three matrices are stored in row-major order, as shown in Figure 2-1(a). Intuitively, the cache-oblivious divide-and-conquer algorithm uses the cache effectively, because once a subproblem fits into the cache, its smaller subproblems can be solved in cache with no further cache misses.

**Theorem 1** The cache-oblivious matrix multiplication algorithm uses  $\Theta(mnp)$  work and incurs  $\Theta(m+n+p+(mn+np+mp)/L+mnp/L\sqrt{Z})$  cache misses when multiplying an  $m \times n$  by an  $n \times p$  matrix.

*Proof.* It can be shown by induction that the work of this algorithm is  $\Theta(mnp)$ . To analyze the cache misses, let  $\alpha$  be a constant sufficiently small that three submatrices of size  $m' \times n'$ ,  $n' \times p'$ , and  $m' \times p'$ , where  $\max\{m', n', p'\} \leq \alpha \sqrt{Z}$ , all fit completely in the cache. We distinguish the following four cases cases depending on the initial size of the matrices.

**Case I:**

$$m, n, p > \alpha \sqrt{Z}$$

.

This case is the most intuitive. The matrices do not fit in cache, since all dimensions are "big enough." The cache complexity of matrix multiplication can be described by the recurrence

$$Q(m,n,p) \leq \begin{cases} \Theta((mn+np+mp)/L) & \text{if } (mn+np+mp) \leq \alpha Z, \\ 2Q(m/2,n,p) + O(1) & \text{otherwise and if } m \geq n \text{ and } m \geq p, \\ 2Q(m,n/2,p) + O(1) & \text{otherwise and if } n > m \text{ and } n \geq p, \\ 2Q(m,n,p/2) + O(1) & \text{otherwise}. \end{cases}$$

(2.4)

The base case arises as soon as all three submatrices fit in cache. The total number of lines used by the three submatrices is  $\Theta((mn+np+mp)/L)$ . The only cache misses that occur during the remainder of the recursion are the  $\Theta((mn+np+mp)/L)$  cache misses required to bring the matrices into cache. In the recursive cases, when the matrices do not fit in cache, we pay for the cache misses of the recursive calls, which depend on the dimensions of the matrices, plus O(1) cache misses for the overhead of manipulating submatrices. The solution to this recurrence is  $Q(m,n,p) = \Theta(mnp/L\sqrt{Z})$ .

**Case II:**

$$(m \le \alpha \sqrt{Z} \text{ and } n, p > \alpha \sqrt{Z}) \text{ OR } (m \le \alpha \sqrt{Z} \text{ and } n, p > \alpha \sqrt{Z}) \text{ OR } (p \le \alpha \sqrt{Z} \text{ and } m, n > \alpha \sqrt{Z}).$$

Here, we shall present the case where  $m \le \alpha \sqrt{Z}$  and  $n, p > \alpha \sqrt{Z}$ . The proofs for the other cases are only small variations of this proof. The multiplication algorithm always divides n or p by 2 according to cases (2.2) and (2.3). At some point in the recursion, both are small enough that the whole problem fits into cache. The number of cache misses can be described by the recurrence

$$Q(m,n,p) \le \begin{cases} \Theta(1+n+np/L+m) & \text{if } n,p \in [\alpha\sqrt{Z}/2,\alpha\sqrt{Z}] \text{,} \\ 2Q(m,n/2,p) + O(1) & \text{otherwise and if } n \ge p \text{,} \\ 2Q(m,n,p/2) + O(1) & \text{otherwise .} \end{cases}$$

The solution to this recurrence is  $\Theta(np/L + mnp/L\sqrt{Z})$ .

**Case III:**

$$(n, p \le \alpha \sqrt{Z} \text{ and } m > \alpha \sqrt{Z}) \text{ OR } (m, p \le \alpha \sqrt{Z} \text{ and } n > \alpha \sqrt{Z}) \text{ OR } (m, n \le \alpha \sqrt{Z} \text{ and } p > \alpha \sqrt{Z}).$$

In each of these cases, one of the matrices fits into cache, and the others do not. Here, we shall present the case where  $n, p \le \alpha \sqrt{Z}$  and  $m > \alpha \sqrt{Z}$ . The other cases can be proven similarly. The multiplication algorithm always

divides m by 2 according to case (2.1). At some point in the recursion, m is in the range  $\alpha\sqrt{Z}/2 \le m \le \alpha\sqrt{Z}$ , and the whole problem fits in cache. The number cache misses can be described by the recurrence

$$Q(m,n) \le \begin{cases} \Theta(1+m) & \text{if } m \in [\alpha\sqrt{Z}/2, \alpha\sqrt{Z}] \\ 2Q(m/2, n, p) + O(1) & \text{otherwise} \end{cases}$$

whose solution is  $Q(m, n, p) = \Theta(m + mnp/L\sqrt{Z})$ .

**Case IV:**  $m, n, p \le \alpha \sqrt{Z}$ .

From the choice of  $\alpha$ , all three matrices fit into cache. The matrices are stored on  $\Theta(1 + mn/L + np/L + mp/L)$  cache lines. Therefore, we have  $Q(m, n, p) = \Theta(1 + (mn + np + mp)/L)$ .

We require the tall-cache assumption (1.1) in these analyses, because the matrices are stored in row-major order. Tall caches are also needed if matrices are stored in column-major order (Figure 2-1(b)), but the assumption that  $Z=\Omega(L^2)$  can be relaxed for certain other matrix layouts. The  $s\times s$ -blocked layout (Figure 2-1(c)), for some tuning parameter s, can be used to achieve the same bounds with the weaker assumption that the cache holds at least some sufficiently large constant number of lines. The cache-oblivious bit-interleaved layout (Figure 2-1(d)) has the same advantage as the blocked layout, but no tuning parameter need be set, since submatrices of size  $\Theta(\sqrt{L}\times\sqrt{L})$  are cache-obliviously stored on one cache line. The advantages of bit-interleaved and related layouts have been studied in [18] and [12, 13]. One of the practical disadvantages of bit-interleaved layouts is that index calculations on conventional microprocessors can be costly.

For square matrices, the cache complexity  $Q(n) = \Theta(n + n^2/L + n^3/L\sqrt{Z})$  of the cache-oblivious matrix multiplication algorithm is the same as the cache complexity of the cache-aware BLOCK-MULT algorithm and also matches the lower bound by Hong and Kung [25]. This lower bound holds for all algorithms that execute the  $\Theta(n^3)$  operations given by the definition of matrix multiplication

$$c_{ij} = \sum_{k=1}^n a_{ik} b_{kj} .$$

No tight lower bounds for the general problem of matrix multiplication are known. By using an asymptotically faster algorithm, such as Strassen's algorithm [38] or one of its variants [45], both the work and cache complexity can be reduced. When multiplying  $n \times n$  matrices, Strassen's algorithm, which is cache oblivious,

requires only 7 recursive multiplications of  $n/2 \times n/2$  matrices and a constant number of matrix additions, yielding the recurrence

$$Q(n) \le \begin{cases} \Theta(1+n+n^2/L) & \text{if } n^2 \le \alpha Z, \\ 7Q(n/2) + O(n^2/L) & \text{otherwise}; \end{cases}$$

(2.5)

where  $\alpha$  is a sufficiently small constant. The solution to this recurrence is  $\Theta(n + n^2/L + n^{\log_2 7}/L\sqrt{Z})$ .

### Summary

In this section we have used the ideal-cache model to analyze two algorithms for matrix multiplication. We have described an efficient cache-oblivious algorithm for rectangular matrix multiplication and analyzed the cache complexity of Strassen's algorithm.

# Matrix transposition and FFT

This section describes an optimal cache-oblivious algorithm for transposing an  $m \times n$  matrix. The algorithm uses  $\Theta(mn)$  work and incurs  $\Theta(1+mn/L)$  cache misses. Using matrix transposition as a subroutine, we convert a variant [44] of the "six-step" fast Fourier transform (FFT) algorithm [6] into an optimal cache-oblivious algorithm. This FFT algorithm uses  $O(n \lg n)$  work and incurs  $O(1+(n/L)(1+\log_2 n))$  cache misses.

The problem of matrix transposition is defined as follows. Given an  $m \times n$  matrix stored in a row-major layout, compute and store  $A^T$  into an  $n \times m$  matrix B also stored in a row-major layout. The straightforward algorithm for transposition that employs doubly nested loops incurs  $\Theta(mn)$  cache misses on one of the matrices when  $mn \gg Z$ , which is suboptimal.

Optimal work and cache complexities can be obtained with a divide-and-conquer strategy, however. If  $n \ge m$ , we partition

$$A = (A_1 A_2)$$

,  $B = \begin{pmatrix} B_1 \\ B_2 \end{pmatrix}$ .

Then, we recursively execute  $\mathsf{TRANSPOSE}(A_1, B_1)$  and  $\mathsf{TRANSPOSE}(A_2, B_2)$ . Alternatively, if m > n, we divide matrix A horizontally and matrix B vertically and likewise perform two transpositions recursively. The next two theorems provide upper and lower bounds on the performance of this algorithm.

**Theorem 2** The cache-oblivious matrix-transpose algorithm involves  $\Theta(mn)$  work and incurs  $\Theta(1 + mn/L)$  cache misses for an  $m \times n$  matrix.

*Proof.* That the algorithm uses  $\Theta(mn)$  work can be shown by induction. For the cache analysis, let Q(m,n) be the cache complexity of transposing an  $m \times n$  matrix. We assume that the matrices are stored in row-major order, the column-major case having a similar analysis.

Let  $\alpha$  be a constant sufficiently small that two submatrices of size  $m' \times n'$  and  $n' \times m'$ , where  $\max\{m', n'\} \leq \alpha L$ , fit completely in the cache. We distinguish the following three cases.

**Case I:**  $\max\{m,n\} \leq \alpha L$ .

Both the matrices fit in O(1) + 2mn/L lines. From the choice of  $\alpha$ , the number of lines required is at most Z/L, which implies  $Q(m, n) = \Theta(1 + mn/L)$ .

**Case II:**  $m < \alpha L < n \text{ OR } n < \alpha L < m$ .

For this case, we assume without loss of generality that  $m \le \alpha L < n$ . The case  $n \le \alpha L < m$  is analogous. The transposition algorithm divides the greater dimension n by 2 and performs divide-and-conquer. At some point in the recursion, n is in the range  $\alpha L/2 \le n \le \alpha L$ , and the whole problem fits in cache. Because the layout is row-major, at this point the input array has n rows, m columns, and it is laid out in contiguous locations, thus requiring at most O(1 + nm/L) cache misses to be read. The output array consists of nm elements in m rows, where in the worst case every row lies on a different cache line. Consequently, we incur at most O(m + nm/L) for writing the output array. Since  $n \ge \alpha L/2$ , the total cache complexity for this base case is O(1 + m).

These observations yield the recurrence

$$Q(m,n) \le \begin{cases} \Theta(1+m) & \text{if } n \in [\alpha L/2, \alpha L], \\ 2Q(m,n/2) + O(1) & \text{otherwise}; \end{cases}$$

whose solution is  $Q(m, n) = \Theta(1 + mn/L)$ .

**Case III:**  $m, n > \alpha L$ .

As in Case II, at some point in the recursion, both n and m fall in the interval  $[\alpha L/2, \alpha L]$ . The whole problem then fits into cache, and it can be solved with at most O(m + n + mn/L) cache misses.

The cache complexity thus satisfies the recurrence

$$Q(m,n) \leq \left\{ \begin{array}{ll} \Theta(m+n+mn/L) & \text{if } m,n \in [\alpha L/2,\alpha L] \text{ ,} \\ 2Q(m/2,n) + O(1) & \text{if } m \geq n \text{ ,} \\ 2Q(m,n/2) + O(1) & \text{otherwise ;} \end{array} \right.$$

whose solution is  $Q(m, n) = \Theta(1 + mn/L)$ .

**Theorem 3** *The cache-oblivious matrix-transpose algorithm is asymptotically optimal.*

*Proof.* For an  $m \times n$  matrix, the matrix-transposition algorithm must write to mn distinct elements, which occupy at least  $\lceil mn/L \rceil = \Omega(1 + mn/L)$  cache lines.  $\square$

As an example application of the cache-oblivious transposition algorithm, the rest of this section describes and analyzes a cache-oblivious algorithm for computing the discrete Fourier transform of a complex array of n elements, where n is an exact power of 2. The basic algorithm is the well-known "six-step" variant [6, 44] of the Cooley-Tukey FFT algorithm [15]. By using the cache-oblivious transposition algorithm, however, we can make the FFT cache oblivious, and its performance matches the lower bound by Hong and Kung [25].

Recall that the *discrete Fourier transform (DFT)* of an array X of n complex numbers is the array Y given by

$$Y[i] = \sum_{j=0}^{n-1} X[j] \omega_n^{-ij} , \qquad (3.1)$$

where  $\omega_n = e^{2\pi\sqrt{-1}/n}$  is a primitive nth root of unity, and  $0 \le i < n$ .

Many known algorithms evaluate Equation (3.1) in time  $O(n \lg n)$  for all integers n [17]. In this thesis, however, we assume that n is an exact power of 2, and compute Equation (3.1) according to the Cooley-Tukey algorithm, which works recursively as follows. In the base case where n = O(1), we compute Equation (3.1) directly. Otherwise, for any factorization  $n = n_1 n_2$  of n, we have

$$Y[i_1 + i_2 n_1] = \sum_{j_2=0}^{n_2-1} \left[ \left( \sum_{j_1=0}^{n_1-1} X[j_1 n_2 + j_2] \omega_{n_1}^{-i_1 j_1} \right) \omega_n^{-i_1 j_2} \right] \omega_{n_2}^{-i_2 j_2}.$$

(3.2)

Observe that both the inner and outer summations in Equation (3.2) are DFT's. Operationally, the computation specified by Equation (3.2) can be performed by computing  $n_2$  transforms of size  $n_1$  (the inner sum), multiplying the result by the factors  $\omega_n^{-i_1j_2}$  (called the *twiddle factors* [17]), and finally computing  $n_1$  transforms of size  $n_2$  (the outer sum).

We choose  $n_1$  to be  $2^{\lceil (\lg n)/2 \rceil}$  and  $n_2$  to be  $2^{\lfloor (\lg n)/2 \rfloor}$ . The recursive step then operates as follows:

1. Pretend that the input is a row-major  $n_1 \times n_2$  matrix A. Transpose A in place, i.e., use the cache-oblivious algorithm to transpose A onto an auxiliary array B, and copy B back onto A. (If  $n_1 = 2n_2$ , consider the matrix to be made up of records containing two elements.)

- 2. At this stage, the inner sum corresponds to a DFT of the  $n_2$  rows of the transposed matrix. Compute these  $n_2$  DFT's of size  $n_1$  recursively. Observe that, because of the previous transposition, we are transforming a contiguous array of elements.

- 3. Multiply *A* by the twiddle factors, which can be computed on the fly with no extra cache misses.

- 4. Transpose *A* in-place, so that the inputs to the next stage are arranged in contiguous locations.

- 5. Compute  $n_1$  DFT's of the rows of the matrix, recursively.

- 6. Transpose *A* in-place so as to produce the correct output order.

It can be proven by induction that the work complexity of this FFT algorithm is  $O(n \lg n)$ . We now analyze its cache complexity. The algorithm always operates on contiguous data, by construction. In order to simplify the analysis of the cache complexity, we assume a tall cache, in which case each transposition operation and the multiplication by the twiddle factors require at most O(1 + n/L) cache misses. Thus, the cache complexity satisfies the recurrence

$$Q(n) \le \begin{cases} O(1 + n/L), & \text{if } n \le \alpha Z, \\ n_1 Q(n_2) + n_2 Q(n_1) + O(1 + n/L) & \text{otherwise}; \end{cases}$$

(3.3)

for a sufficiently small constant  $\alpha$  chosen such that a subproblem of size  $\alpha Z$  fits in cache. This recurrence has solution

$$Q(n) = O\left(1 + (n/L)\left(1 + \log_{Z} n\right)\right) ,$$

which is asymptotically optimal for a Cooley-Tukey algorithm, matching the lower bound by Hong and Kung [25] when n is an exact power of 2. As with matrix multiplication, no tight lower bounds for cache complexity are known for the general problem of computing the DFT.

### Summary

In this section, we have described an optimal cache-oblivious algorithm for FFT. The basic algorithm is the well-known "six-step" variant [6, 44] of the Cooley-Tukey FFT algorithm [15]. By using an optimal cache-oblivious transposition algorithm, however, we can make the FFT cache oblivious, and its performance matches the lower bound by Hong and Kung [25].

### **SECTION 4**

## **Funnelsort**

Although it is cache oblivious, algorithms like familiar two-way merge sort (see Section 7.3) are not asymptotically optimal with respect to cache misses. The *Z*-way mergesort mentioned by Aggarwal and Vitter [3] is optimal in terms of cache complexity, but it is cache aware. This section describes a cache-oblivious sorting algorithm called "funnelsort." This algorithm has an asymptotically optimal work complexity  $\Theta(n \lg n)$ , as well as an optimal cache complexity  $\Theta(1 + (n/L)(1 + \log_Z n))$  if the cache is tall. In Section 5, we shall present another cache-oblivious sorting algorithm based on distribution sort.

Funnelsort is similar to mergesort. In order to sort a (contiguous) array of n elements, funnelsort performs the following two steps:

- 1. Split the input into  $n^{1/3}$  contiguous arrays of size  $n^{2/3}$ , and sort these arrays recursively.

- 2. Merge the  $n^{1/3}$  sorted sequences using a  $n^{1/3}$ -merger, which is described below.

Funnelsort differs from mergesort in the way the merge operation works. Merging is performed by a device called a *k-merger*, which inputs *k* sorted sequences and merges them. A *k*-merger operates by recursively merging sorted sequences that become progressively longer as the algorithm proceeds. Unlike mergesort, however, a *k*-merger stops working on a merging subproblem when the merged output sequence becomes "long enough," and it resumes working on another merging subproblem.

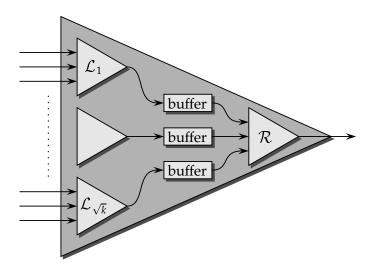

**Figure 4-1:** Illustration of a k-merger. A k-merger is built recursively out of  $\sqrt{k}$  left  $\sqrt{k}$ -mergers  $\mathcal{L}_1, \mathcal{L}_2, \dots, \mathcal{L}_{\sqrt{k}}$ , a series of buffers, and one right  $\sqrt{k}$ -merger  $\mathcal{R}$ .

Since this complicated flow of control makes a k-merger a bit tricky to describe, we explain the operation of the k-merger pictorially. Figure 4-1 shows a representation of a k-merger, which has k sorted sequences as inputs. Throughout its execution, the k-merger maintains the following invariant.

**Invariant** The invocation of a k-merger outputs the first  $k^3$  elements of the sorted sequence obtained by merging the k input sequences.

A k-merger is built recursively out of  $\sqrt{k}$ -mergers in the following way. The k inputs are partitioned into  $\sqrt{k}$  sets of  $\sqrt{k}$  elements, and these sets form the input to the  $\sqrt{k}$  left  $\sqrt{k}$ -mergers  $\mathcal{L}_1, \mathcal{L}_2, \ldots, \mathcal{L}_{\sqrt{k}}$  in the left part of the figure. The outputs of these mergers are connected to the inputs of  $\sqrt{k}$  buffers. Each buffer is a FIFO queue that can hold  $2k^{3/2}$  elements. Finally, the outputs of the buffers are connected to the  $\sqrt{k}$  inputs of the right  $\sqrt{k}$ -merger  $\mathcal{R}$  in the right part of the figure. The output of this final  $\sqrt{k}$ -merger becomes the output of the whole k-merger. The reader should notice that the intermediate buffers are overdimensioned. In fact, each buffer can hold  $2k^{3/2}$  elements, which is twice the number  $k^{3/2}$  of elements output by a  $\sqrt{k}$ -merger. This additional buffer space is necessary for the correct behavior of the algorithm, as will be explained below. The base case of the recursion is a k-merger with k=2, which produces  $k^3=8$  elements whenever invoked.

A k-merger operates recursively in the following way. In order to output  $k^3$  elements, the k-merger invokes  $\mathcal{R}$   $k^{3/2}$  times. Before each invocation, however, the k-merger fills all buffers that are less than half full, i.e., all buffers that contain less than  $k^{3/2}$  elements. In order to fill buffer i, the algorithm invokes the corresponding

left merger  $\mathcal{L}_i$  once. Since  $\mathcal{L}_i$  outputs  $k^{3/2}$  elements, the buffer contains at least  $k^{3/2}$  elements after  $\mathcal{L}_i$  finishes.

In order to prove this result, we need three auxiliary lemmata. The first lemma bounds the space required by a *k*-merger.

**Lemma 4** A k-merger can be laid out in  $O(k^2)$  contiguous memory locations.

*Proof.* A *k*-merger requires  $O(k^2)$  memory locations for the buffers, plus the space required by the  $\sqrt{k}$ -mergers. The space S(k) thus satisfies the recurrence

$$S(k) \leq (\sqrt{k} + 1)S(\sqrt{k}) + O(k^2),$$

whose solution is  $S(k) = O(k^2)$ .

It follows from Lemma 4, that a problem of size  $\alpha\sqrt{Z}$  can be solved in cache with no further cache misses, where  $\alpha$  is a sufficiently small constant.

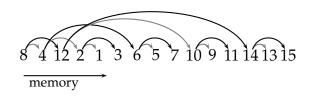

In order to achieve the bound on the number Q(n) of cache misses, it is important that the buffers in a k-merger be maintained as circular queues of size k. This requirement guarantees that we can manage the queue cache-efficiently, in the sense stated by the next lemma.

**Lemma 5** Performing r insert and remove operations on a circular queue causes O(1 + r/L) cache misses if four cache lines are available for the buffer.

*Proof.* Associate the two cache lines with the head and tail of the circular queue. The head- and tail-pointers are kept on two seperate lines. Since the replacement strategy is optimal, it will keep the frequently accessed pointers in cache. If a new cache line is read during an insert (delete) operation, the next L-1 insert (delete) operations do not cause a cache miss. The result follows.

Define  $Q_{\rm M}$  to be the number of cache misses incurred by a k-merger. The next lemma bounds the number of cache misses incurred by a k-merger.

**Lemma 6** On a tall cache, one invocation of a k-merger incurs

$$Q_{\rm M}(k) = O\left(k + k^3/L + k^3 \log_Z k/L\right)$$

cache misses.

*Proof.* There are two cases: either  $k \le \alpha \sqrt{Z}$  or  $k > \alpha \sqrt{Z}$ .

Assume first that  $k \le \alpha \sqrt{Z}$ . By Lemma 4, the data structure associated with the k-merger requires at most  $O(k^2) = O(Z)$  contiguous memory locations. By the choice of  $\alpha$  the k-merger fits into cache. The k-merger has k input queues, from

which it loads  $O(k^3)$  elements. Let  $r_i$  be the number of elements extracted from the ith input queue. Since  $k \le \alpha \sqrt{Z}$  and  $L = O(\sqrt{Z})$ , there are at least  $Z/L = \Omega(k)$  cache lines available for the input buffers. Lemma 5 applies, whence the total number of cache misses for accessing the input queues is

$$\sum_{i=1}^{k} O(1 + r_i/L) = O(k + k^3/L) .$$

Similarly by Lemma 5, the cache complexity of writing the output queue is at most  $O(1+k^3/L)$ . Finally, for touching the  $O(k^2)$  contiguous memory locations used by the internal data structures, the algorithm incurs at most  $O(1+k^2/L)$  cache misses. The total cache complexity is therefore

$$Q_{M}(k) = O(k + k^{3}/L) + O(1 + k^{2}/L) + O(1 + k^{3}/L)$$

=  $O(k + k^{3}/L)$

completing the proof of the first case.

Assume now that  $k > \alpha \sqrt{Z}$ . In this second case, we prove by induction on k that whenever  $k > \alpha \sqrt{Z}$ , we have

$$Q_{\rm M}(k) \le (ck^3\log_2 k)/L - A(k)$$

, (4.1)

for some constant c>0, where  $A(k)=k(1+(2c\log_Z k)/L)=o(k^3)$ . The lower-order term A(k) does not affect the asymptotic behavior, but it makes the induction go through. This particular value of A(k) will be justified later in the analysis.

The base case of the induction consists of values of k such that  $\sqrt{\alpha}Z^{1/4} < k \le \alpha\sqrt{Z}$ . (It is not sufficient to just consider  $k = \Theta(\sqrt{Z})$ , since k can become as small as  $\Theta(Z^{1/4})$  in the recursive calls.) The analysis of the first case applies, yielding  $Q_{\rm M}(k) = O\left(k + k^3/L\right)$ . Because  $k^2 > \alpha\sqrt{Z} = \Omega(L)$  and  $k = \Omega(1)$ , the last term dominates, and  $Q_{\rm M}(k) = O\left(k^3/L\right)$  holds. Consequently, a large enough value of c can be found that satisfies Inequality (4.1).

For the inductive case, let  $k > \alpha \sqrt{Z}$ . The k-merger invokes the  $\sqrt{k}$ -mergers recursively. Since  $\sqrt{\alpha}Z^{1/4} < \sqrt{k} < k$ , the inductive hypothesis can be used to bound the number  $Q_{\rm M}(\sqrt{k})$  of cache misses incurred by the submergers. The right merger  $\mathcal R$  is invoked exactly  $k^{3/2}$  times. The total number l of invocations of left mergers is bounded by  $l < k^{3/2} + 2\sqrt{k}$ . To see why, consider that every invocation of a left merger puts  $k^{3/2}$  elements into some buffer. Since  $k^3$  elements are output and the buffer space is  $2k^2$ , the bound  $l < k^{3/2} + 2\sqrt{k}$  follows.

Before invoking  $\mathcal{R}$ , the algorithm must check every buffer to see whether it is empty. One such check requires at most  $\sqrt{k}$  cache misses, since there are  $\sqrt{k}$

buffers. This check is repeated exactly  $k^{3/2}$  times, leading to at most  $k^2$  cache misses for all checks.

These considerations lead to the recurrence

$$Q_{\rm M}(k) \le \left(2k^{3/2} + 2\sqrt{k}\right) Q_{\rm M}(\sqrt{k}) + k^2$$

.

Application of the inductive hypothesis yields the desired bound Inequality (4.1), as follows.

$$\begin{split} Q_{\mathrm{M}}(k) & \leq \left(2k^{3/2} + 2\sqrt{k}\right) Q_{\mathrm{M}}(\sqrt{k}) + k^{2} \\ & \leq 2\left(k^{3/2} + \sqrt{k}\right) \left[\frac{ck^{3/2}\mathrm{log}_{Z}k}{2L} - A(\sqrt{k})\right] + k^{2} \\ & \leq \left(ck^{3}\mathrm{log}_{Z}k\right)/L + k^{2}\left(1 + (c\mathrm{log}_{Z}k)/L\right) \\ & - \left(2k^{3/2} + 2\sqrt{k}\right)A(\sqrt{k}) \; . \end{split}$$

If  $A(k) = k(1 + (2c\log_2 k)/L)$  (for example), we get

$$\begin{array}{rcl} Q_{\rm M}(k) & \leq & (ck^3{\rm log}_Z k)/L + k^2 \left(1 + (c{\rm log}_Z k)/L\right) \\ & & - \left(2k^{3/2} + 2\sqrt{k}\right)\sqrt{k}\left(1 + (2c{\rm log}_Z\sqrt{k})/L\right) \\ & \leq & (ck^3{\rm log}_Z k)/L + k^2 \left(1 + (c{\rm log}_Z k)/L\right) \\ & & - \left(2k^2 + 2k\right)\left(1 + (c{\rm log}_Z k)/L\right) \\ & \leq & (ck^3{\rm log}_Z k)/L - (k^2 + 2k)\left(1 + (c{\rm log}_Z k)/L\right) \\ & \leq & (ck^3{\rm log}_Z k)/L - A(k) \end{array}$$

and Inequality (4.1) follows.

It can be proven by induction that the work complexity of funnelsort is  $O(n \lg n)$ . The next theorem gives the cache complexity of funnelsort.

**Theorem 7** Funnelsort sorts n elements incurring at most Q(n) cache misses, where

$$Q(n) = O(1 + (n/L)(1 + \log_{z} n))$$

.

*Proof.* If  $n \le \alpha Z$  for a small enough constant  $\alpha$ , then the funnelsort data structures fit into cache. To see why, observe that only one k-merger is active at any time. The biggest k-merger is the top-level  $n^{1/3}$ -merger, which requires  $O(n^{2/3}) < O(n)$  space. The algorithm thus can operate in O(1+n/L) cache misses.

If  $n > \alpha Z$ , we have the recurrence

$$Q(n) = n^{1/3}Q(n^{2/3}) + Q_{\rm M}(n^{1/3})$$

.

By Lemma 6, we have  $Q_{\rm M}(n^{1/3}) = O(n^{1/3} + n/L + (n\log_Z n)/L)$ .

With the hypothesis  $Z = \Omega(L^2)$ , we have  $n/L = \Omega(n^{1/3})$ . Moreover, we also have  $n^{1/3} = \Omega(1)$  and  $\lg n = \Omega(\lg Z)$ . Consequently,  $Q_{\rm M}(n^{1/3}) = O\left((n\log_Z n)/L\right)$  holds, and the recurrence simplifies to

$$Q(n) = n^{1/3}Q(n^{2/3}) + O((n\log_{\mathbb{Z}} n)/L) .$$

The result follows by induction on n.

This upper bound matches the lower bound stated by the next theorem, proving that funnelsort is cache-optimal.

**Theorem 8** *The cache complexity of any sorting algorithm is*

$$Q(n) = \Omega \left( 1 + (n/L) \left( 1 + \log_Z n \right) \right) .$$

*Proof.* Aggarwal and Vitter [3] show that there is an  $\Omega\left((n/L)\log_{Z/L}(n/Z)\right)$  bound on the number of cache misses made by any sorting algorithm on their "out-of-core" memory model, a bound that extends to the ideal-cache model. By applying the tall-cache assumption  $Z=\Omega(L^2)$ , we have

$$\begin{split} Q(n) & \geq & a(n/L) \log_{Z/L}(n/Z) \\ & \geq & a(n/L) \lg(n/Z)/(\lg Z - \lg L) \\ & \geq & a(n/L) \lg(n/Z)/\lg Z \\ & \geq & a(n/L) \lg n/\lg Z - a(n/L) \;. \end{split}$$

It follows that  $Q(n) = \Omega((n/L)\log_Z n)$ . The theorem can be proven by combining this result with the trivial lower bounds of  $Q(n) = \Omega(1)$  and  $Q(n) = \Omega(n/L)$ .

**Corollary 9** *The cache-oblivious Funnelsort is asymptotically optimal.*

*Proof.* Follows from Theorems 8 and 7.  $\Box$

### Summary

In this section we have presented an optimal cache-oblivious algorithm based on mergesort. Funnelsort uses a device called a k-merger, which inputs k sorted sequences and merges them in "chunks". It stops when the merged output becomes "long enough" to resume work on another subproblem. Further, we have shown that any sorting algorithm incurs at least  $\Omega\left(1+(n/L)\left(1+\log_Z n\right)\right)$  cache misses. This lower bound is matched by both our algorithms.

#### **SECTION 5**

## Distribution sort

In this section, we describe a cache-oblivious optimal sorting algorithm based on distribution sort. Like the funnelsort algorithm from Section 4, the distribution-sorting algorithm uses  $O(n \lg n)$  work to sort n elements, and it incurs

$$\Theta\left(1+\left(n/L\right)\left(1+\log_{Z}n\right)\right)$$

cache misses if the cache is tall. Unlike previous cache-efficient distribution-sorting algorithms [1, 3, 30, 42, 44], which use sampling or other techniques to find the partitioning elements before the distribution step, our algorithm uses a "bucket-splitting" technique to select pivots incrementally during the distribution.

Given an array A (stored in contiguous locations) of length n, the cache-oblivious distribution sort sorts A as follows:

- 1. Partition *A* into  $\sqrt{n}$  contiguous subarrays of size  $\sqrt{n}$ . Recursively sort each subarray.

- 2. Distribute the sorted subarrays into  $q \le \sqrt{n}$  buckets  $B_1, B_2, \ldots, B_q$  of size  $n_1, n_2, \ldots, n_q$ , respectively, such that for  $i = 1, 2, \ldots, q 1$ , we have

- 1.  $\max\{x \mid x \in B_i\} \le \min\{x \mid x \in B_{i+1}\}\$ ,

- $2. \ n_i \leq 2\sqrt{n} \ .$

(See below for details.)

- 3. Recursively sort each bucket.

- 4. Copy the sorted buckets back to array *A*.

A stack-based memory allocator is used to exploit spatial locality. A nice property of stack based allocation is that memory is not fragmented for problems of small size. So if the space complexity of a procedure is S, only O(1 + S/L) cache misses are made when  $S \leq Z$ , provided the procedure accesses only its local variables.

### Distribution step

The goal of Step 2 is to distribute the sorted subarrays of A into q buckets  $B_1$ ,  $B_2, \ldots, B_q$ . The algorithm maintains two invariants. First, each bucket holds at most  $2\sqrt{n}$  elements at any time, and any element in bucket  $B_i$  is smaller than any element in bucket  $B_{i+1}$ . Second, every bucket has an associated *pivot*, a value which is greater than all elements in the bucket. Initially, only one empty bucket exists with pivot  $\infty$ . At the end of Step 2, all elements will be in the buckets and the two conditions (a) and (b) stated in Step 2 will hold.

The idea is to copy all elements from the subarrays into the buckets cache efficiently while maintaining the invariants. We keep state information for each subarray and for each bucket. The state of a subarray consists of an index *next* of the next element to be read from the subarray and a bucket number *bnum* indicating where this element should be copied. By convention,  $bnum = \infty$  if all elements in a subarray have been copied. The state of a bucket consists of the bucket's pivot and the number of elements currently in the bucket.

We would like to copy the element at position *next* of a subarray to bucket *bnum*. If this element is greater than the pivot of bucket *bnum*, we would increment *bnum* until we find a bucket for which the element is smaller than the pivot. Unfortunately, this basic strategy has poor caching behavior, which calls for a more complicated procedure.

The distribution step is accomplished by the recursive procedure DISTRIBUTE. DISTRIBUTE (i, j, m) distributes elements from the ith through (i + m - 1)th subarrays into buckets starting from  $B_j$ . Given the precondition that each subarray  $r = i, i + 1, \ldots, i + m - 1$  has its  $bnum[r] \geq j$ , the execution of DISTRIBUTE (i, j, m) enforces the postcondition that  $bnum[r] \geq j + m$ . Step 2 of the distribution sort invokes DISTRIBUTE  $(1, 1, \sqrt{n})$ . The following is a recursive implementation of DISTRIBUTE:

```

DISTRIBUTE (i, j, m)

1 if m = 1

2 then COPYELEMS (i, j)

3 else DISTRIBUTE (i, j, m/2)

4 DISTRIBUTE (i + m/2, j, m/2)

5 DISTRIBUTE (i, j + m/2, m/2)

6 DISTRIBUTE (i + m/2, j + m/2, m/2)

```

In the base case (line 1), the subroutine COPYELEMS(i,j) copies all elements from subarray i that belong to bucket j. If bucket j has more than  $2\sqrt{n}$  elements after the insertion, it can be split into two buckets of size at least  $\sqrt{n}$ . For the splitting operation, we use the deterministic median-finding algorithm [16, p. 189] followed by a partition. The next lemma shows that the median-finding algorithm uses O(m) work and incurs O(1+m/L) cache misses to find the median of an array of size m. (In our case, we have  $m \geq 2\sqrt{n} + 1$ .) In addition, when a bucket splits, all subarrays whose bnum is greater than the bnum of the split bucket must have their bnum's incremented. The analysis of DISTRIBUTE is given by the following two lemmata.

**Lemma 10** *The median of m elements can be found cache-obliviously using* O(m) *work and incurring* O(1 + m/L) *cache misses.*

*Proof.* See [16, p. 189] for the linear-time median finding algorithm and the work analysis. The cache complexity is given by the same recurrence as the work complexity with a different base case.

$$Q(m) = \begin{cases} O(1+m/L) & \text{if } m \le \alpha Z, \\ Q(\lceil m/5 \rceil) + Q(7m/10+6) + O(1+m/L) & \text{otherwise,} \end{cases}$$

where  $\alpha$  is a sufficiently small constant. The result follows.

**Lemma 11** *Step 2 uses* O(n) *work, incurs* O(1 + n/L) *cache misses, and uses* O(n) *stack space to distribute n elements.*

*Proof.* In order to simplify the analysis of the work used by DISTRIBUTE, assume that COPYELEMS uses O(1) work. We account for the work due to copying elements and splitting of buckets separately. The work of DISTRIBUTE on m subarrays is described by the recurrence

$$T(m) = 4T(m/2) + O(1)$$

.

It follows that  $T(m) = O(m^2)$ , where  $m = \sqrt{n}$  initially.

We now analyze the work used for copying and bucket splitting. The number of copied elements is O(n). Each element is copied exactly once and therefore the work due to copying elements is also O(n). The total number of bucket splits is at most  $\sqrt{n}$ . To see why, observe that there are at most  $\sqrt{n}$  buckets at the end of the distribution step, since each bucket contains at least  $\sqrt{n}$  elements. Each split operation involves  $O(\sqrt{n})$  work and so the net contribution to the work is O(n). Thus, the total work used by DISTRIBUTE is  $W(n) = O(T(\sqrt{n})) + O(n) + O(n) = O(n)$ .

For the cache analysis, we distinguish two cases. Let  $\alpha$  be a sufficiently small constant such that the stack space used by sorting a problem of size  $\alpha Z$ , including the input array, fits completely into cache.

#### **Case I:** $n \leq \alpha Z$ .

The input and the auxiliary space of size O(n) fit into cache using O(1 + n/L) cache lines. Consequently, the cache complexity is O(1 + n/L).

#### Case II: $n > \alpha Z$ .

Let R(m,d) denote the cache misses incurred by an invocation of the subroutine DISTRIBUTE (i,j,m) that copies d elements from m subarrays to m buckets. We again account for the splitting of buckets separately. We first prove that R satisfies the following recurrence:

$$R(m,d) \le \begin{cases} O(L+d/L) & \text{if } m \le \alpha L, \\ \sum_{1 \le i \le 4} R(m/2, d_i) & \text{otherwise,} \end{cases}$$

(5.1)

where  $\sum_{1 \le i \le 4} d_i = d$ .

First, consider the base case  $m \leq \alpha L$ . An invocation of DISTRIBUTE(i,j,m) operates with m subarrays and m buckets. Since there are  $\Omega(L)$  cache lines, the cache can hold all the auxiliary storage involved and the currently accessed element in each subarray and bucket. In this case there are O(L+d/L) cache misses. The initial access to each subarray and bucket causes O(m) = O(L) cache misses. The cache complexity for copying the d elements from one set of contiguous locations to another set of contiguous locations is O(1+d/L), which completes the proof of the base case. The recursive case, when  $m > \alpha L$ , follows immediately from the algorithm. The solution for Recurrence 5.1 is  $R(m,d) = O(L+m^2/L+d/L)$ .

We still need to account for the cache misses caused by the splitting of buckets. Each split causes  $O(1+\sqrt{n}/L)$  cache misses due to median finding

(Lemma 10) and partitioning of  $\sqrt{n}$  contiguous elements. An additional  $O(1+\sqrt{n}/L)$  misses are incurred by restoring the cache. As proven in the work analysis, there are at most  $\sqrt{n}$  split operations.

By adding  $R(\sqrt{n}, n)$  to the complexity of splitting, we conclude that the total cache complexity of the distribution step is  $O(L + n/L + \sqrt{n}(1 + \sqrt{n}/L)) = O(n/L)$ .

**Theorem 12** Distribution sort uses  $O(n \lg n)$  work and incurs  $O(1 + (n/L)(1 + \log_Z n))$  cache misses to sort n elements.

*Proof.* The work done by the algorithm is given by

$$W(n) = \sqrt{n}W(\sqrt{n}) + \sum_{i=1}^{q} W(n_i) + O(n)$$

,

where  $q \le \sqrt{n}$ , each  $n_i \le 2\sqrt{n}$ , and  $\sum_{i=1}^q n_i = n$ . The solution to this recurrence is  $W(n) = O(n \lg n)$ .

The space complexity of the algorithm is given by

$$S(n) \leq S(2\sqrt{n}) + O(n) .$$

Each bucket has at most  $2\sqrt{n}$  elements, thus the recursive call uses at  $S(2\sqrt{n})$  space and the O(n) term comes from Step 2. The solution to this recurrence is S(n) = O(n).

The cache complexity of distribution sort is described by the recurrence

$$Q(n) \le \begin{cases} O(1+n/L) & \text{if } n \le \alpha Z, \\ \sqrt{n}Q(\sqrt{n}) + \sum_{i=1}^{q} Q(n_i) + O(1+n/L) & \text{otherwise,} \end{cases}$$

where  $\alpha$  is a sufficiently small constant such that the stack space used by a sorting problem of size  $\alpha Z$ , including the input array, fits completely in cache. The base case  $n \leq \alpha Z$  arises when both the input array A and the contiguous stack space of size S(n) = O(n) fit in O(1 + n/L) cache lines of the cache. In this case, the algorithm incurs O(1 + n/L) cache misses to touch all involved memory locations once. In the case where  $n > \alpha Z$ , the recursive calls in Steps 1 and 3 cause  $Q(\sqrt{n}) + \sum_{i=1}^q Q(n_i)$  cache misses and O(1 + n/L) is the cache complexity of Steps 2 and 4, as shown by Lemma 11. The theorem now follows by solving the recurrence.

**Corollary 13** *The cache-oblivious distribution sort algorithm is asymptotically optimal.*

*Proof.* Follows from Theorems 8 and 12.

### Summary

In this section, we have presented another optimal cache-oblivious sorting algorithm, which is based on distribution sort. All previous cache-efficient distribution sort algorithms [1, 3, 30, 42, 44] are cache aware, since they are designed for caching models where the data is moved explicitly. They usually use a sampling processes to find the partitioning elements before the distribution step. Our algorithm finds the pivots incrementally during the distribution.

#### **SECTION 6**

# Jacobi multipass filter

This section compares an optimal recursive algorithm with a more straightforward iterative algorithm, both which compute a multipass filter over one-dimensional data. When computing n generations on n elements, both algorithms use  $\Theta(n^2)$  work. The iterative incurs  $\Theta(n^2/L)$  cache misses, if the data does not fit into the cache, where the recursive algorithm incurs only  $\Theta(1+n/L+n^2/ZL)$  cache misses which we prove to be cache optimal. We also provide some brief empirical results for this problem. The recursive algorithm executes in less than 70% of the time of the iterative algorithm for problem sizes that do not fit in L2-cache

Consider the problem of a computing a multipass filter on an array A of size n, where a new value  $A_i^{(\tau+1)}$  at generation  $\tau+1$  is computed from values at the previous step  $\tau$  according to some update rule. A typical update function is

$$A_i^{(\tau+1)} \leftarrow \left(A_{i-1}^{(\tau)} + A_i^{(\tau)} + A_{i+1}^{(\tau)}\right)/3$$

(6.1)

Applications of multipass filtering include the Jacobi iteration for solving heat-diffusion equations [31, p. 673] and the simulation of lattice gases with cellular automata. These applications usually deal with multidimensional data, but here, we shall explore the one-dimensional case for simplicity, even though caching effects are often more pronounced with multidimensional data.

```

JACOBI-ITER(A)

1 n \leftarrow \text{length of } A

2 \mathbf{for } i \leftarrow 1 \mathbf{to } n/2

3 \mathbf{do for } j \leftarrow 1 \mathbf{to } n \Rightarrow \text{Generation } 2i

4 \mathbf{do } tmp[j] \leftarrow \left(A[(j-1) \bmod n] + A[j] + A[(j+1) \bmod n]\right)/3

5 \mathbf{for } j \leftarrow 1 \mathbf{to } n \Rightarrow \text{Generation } 2i + 1

6 \mathbf{do } A[j] \leftarrow \left(tmp[(j-1) \bmod n] + tmp[j] + tmp[(j+1) \bmod n]\right)/3

```

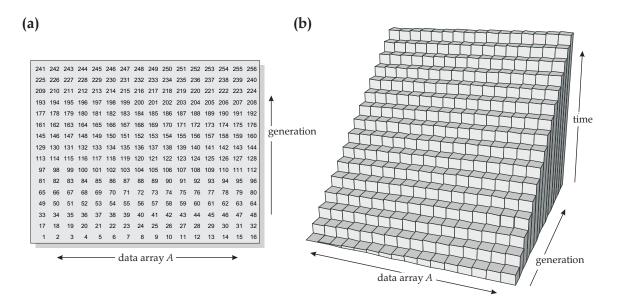

**Figure 6-1:** Iterative implementation of n-pass Jacobi update on array A with n elements.

### 6.1 Iterative algorithm

We first analyze the cache complexity of the straightforward implementation JA-COBI-ITER of the update rule given in Equation (6.1). We show that this algorithm, shown in Figure 6-1, uses  $\Theta(n)$  temporary storage and performs  $\Theta(n^2)$  memory accesses for an array of size n. If the array of size n does not fit into cache, the total number of cache misses is  $\Theta(n^2/L)$ .

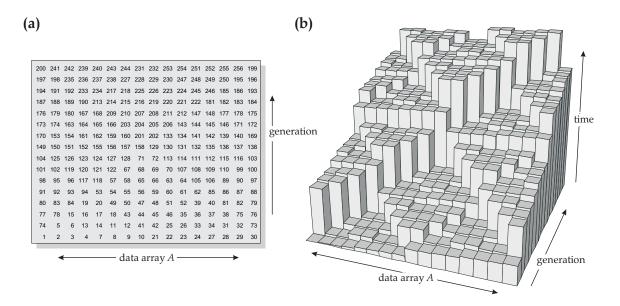

To illustrate the order of updates of JACOBI-ITER on input A of size n, we view the computation of n generations of the multipass as a two-dimensional trace matrix T of size  $n \times n$ . One dimension of T is the offset in the input array and the other dimension is the "generation" of the filtered result. The value of element  $T_{4,2}$  is the value of array element A[2] at the 4th generation of the iterative algorithm. One row in the matrix represents the updates on one element in the array. The trace matrix of the iterative algorithm on a data array of size 16 is shown in Figure 6-2. The height of a bar represents the ordering of the updates, where the higher bars are updated later. The bigger the difference in the height of two bars, the further apart in time are their updates. If the height of a bar is not much bigger than the height of the bar directly in front of it, it is likely that the element is still in cache and a hit occurs. The height differences between two updates to the same element in the iterative algorithm are all equal. Either the updates are close enough together that all updates are cache hits, or they are too far apart, and all updates are cache misses.

**Theorem 14** The JACOBI-ITER algorithm uses  $\Theta(n^2)$  work when computing n generations on an array of size n. JACOBI-ITER incurs  $\Theta(1 + n/L)$  cache misses if the data fits into cache, and it incurs  $\Theta(n^2/L)$  cache misses if the array does not fit into cache.

*Proof.* Since there are two nested loops, each of which performs n iterations, the work is  $\Theta(n^2)$ .

**Figure 6-2:** Ordering of updates of JACOBI-ITER on an array with 16 elements. **(a)** The trace matrix with the order of updates from 1 to 256. **(b)** A bar-graph illustrating the updates, where the height of a bar represents the ordering of updates and the smallest bar is updated first.

We now analyze the cache misses of JACOBI-ITER on a (Z, L) ideal cache. Let  $\alpha$  be a constant sufficiently small that  $\alpha Z$  elements fit into a cache of size Z. As long as the array and the temporary storage fit into cache, e.g.,  $n \leq \alpha Z$ , the algorithm performs well. The cache complexity is only  $\Theta(1 + n/L)$  since the O(n) elements are read (in order) only once.

If the array has size  $n \ge \alpha Z$ , however, then it does not all fit in cache at one time. The optimal replacement strategy can keep at most O(Z) elements in cache. Thus, per iteration we have  $\Omega(n/L-Z)$  updates which are cache misses. Consequently, the total number of cache misses is  $\Theta(n)\Omega(n/L-Z) = \Omega(n^2/L)$  for the n iterations.

The algorithm can be optimized to use only O(1) temporary storage and avoid the modulo computation, but the number of cache misses remains at  $\Theta(n^2/L)$ .

## 6.2 Recursive algorithm

In this section, we present an optimal recursive algorithm to compute an n-pass Jacobi filter. This cache-oblivious algorithm JACOBI-REC is sketched in Figure 6-3, where the input size is a power of  $2.^1$  We prove that the work used by JACOBI-

<sup>&</sup>lt;sup>1</sup>The algorithm for the general case is slightly more complicated.

```

JACOBI\Delta(A, n, s, w, \tau)

1 if w > 2

2

then JACOBI\triangle(A, n, s, w/2, \tau)

3

JACOBI\triangle(A, n, (s+w/2), w/2, \tau)

JACOBI\nabla(A, n, (s + w/4) + 1, w/2, \tau)

4

5

JACOBI\triangle(A, n, (s+w/4), w/2, \tau+w/4)

6

else p \leftarrow \tau \mod 2

7

q \leftarrow (\tau + 1) \mod 2

8

A[p][s \bmod n] \leftarrow

9

(A[q][(s-1) \bmod n] + A[q][s \bmod n] + A[q][(s+1) \bmod n])/3

A[p][(s+1) \bmod n] \leftarrow

10

(A[q][s \bmod n] + A[q][(s+1) \bmod n] + A[q][(s+2) \bmod n])/3

11

JACOBI\nabla(A, n, s, w, \tau)

1 if w > 2

2

then JACOBI \nabla (A, n, s + w/4, w/2, \tau)

JACOBI\triangle(A, n, s + w/4, w/2, \tau + w/4)

3

JACOBI\nabla(A, n, s, w/2, \tau + w/4)

4

5

JACOBI \nabla (A, n, s + w/2, w/2, \tau + w/4)

JACOBI-REC(A)

1 n \leftarrow \text{length of } A

2 JACOBI\triangle(A, n, 0, n, 0)

3 JACOBI\nabla(A, n, n/2, n, 0)

4 JACOBI\triangle(A, n, n/2, n, n/2)

5 JACOBI\nabla(A, n, 0, n, n/2)

```

**Figure 6-3:** The recursive implementation of the multipass filter on array A of size n, where n is a power of 2. The algorithm uses two auxiliary subroutines  $JACOBI\triangle(A,n,s,w,\tau)$  and  $JACOBI\nabla(A,n,s,w,\tau)$ . The input is in A[0] and A[1] is the O(n) auxiliary space. The parameters s and w specify the position and size of the computed triangle and  $\tau$  is the generation of the lowest level of the triangle. JACOBI-REC(A) is the initial call.

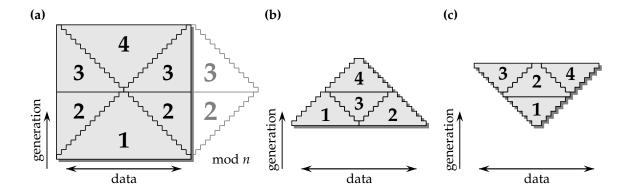

**Figure 6-4: (a)** Decomposition of trace matrix in four triangles by JACOBI-REC. Triangles 2 and 3 "wrap around" since array positions are computed modulo n. **(b)** shows the decomposition used by JACOBI $\triangle$  and **(c)** shows the decomposition used by JACOBI $\nabla$ .

REC is  $\Theta(n^2)$  and the cache complexity is  $O(1 + n/L + n^2/ZL)$ , even if the problem does not fit into cache, which is a factor of Z fewer cache misses than the iterative method.

In order to simplify the description, we describe the recursive algorithm as if the whole trace matrix would be computed. It turns out that in practice one auxiliary array of size n suffices to compute the n steps on an array of size n.

The divide-and-conquer algorithm divides the trace matrix into 4 triangles, which are recursively divided into smaller triangles, as shown in Figure 6-4(a). Two auxiliary functions JACOBI $\triangle$  and JACOBI $\nabla$  are used to implement the recursion. JACOBI $\triangle$ ( $A, n, s, w, \tau$ ) computes an "upper triangle" of the trace matrix A of size n, where the base of the triangle has size w and starts at s with generation  $\tau$ . It recursively computes up to w/2 generations ahead as shown in Figure 6-4(b). Analogously, JACOBI $\nabla$  computes a lower triangle recursively as shown in Figure 6-4(c). The resulting trace matrix for an array of size 16 is shown in Figure 6-5. It illustrates the locality of the recursive algorithms. The triangles of the decomposition are clearly visible. Depending on the cache size, triangles of different size fit entirely into cache, which are then computed without any further cache misses. Although JACOBI-REC computes the elements in different order than JACOBI-ITER, it computes exactly the same values as JACOBI-ITER.

**Figure 6-5:** Ordering of updates of JACOBI-REC on an array with 16 elements. **(a)** The trace matrix with the order of updates from 1 to 256. **(b)** A bar-graph illustrating the updates, where the height of a bar represents the ordering of updates and the smallest bar is updated first.

**Theorem 15** The recursive JACOBI-REC algorithm involves  $\Theta(n^2)$  work and incurs  $\Theta(1 + n/L + n^2/ZL)$  cache misses when computing n generations on n elements.

*Proof.* To simplify the analysis, we assume that n is an exact power of 2.<sup>2</sup> The work of JACOBI-REC can be described by three recurrences:

$$\begin{split} W(n) &= 2W_{\triangle}(n/2) + 2W_{\nabla}(n/2) + O(1) \;, \\ W_{\triangle}(n) &= 3W_{\triangle}(n/2) + W_{\nabla}(n/2) + O(1) \;, \\ W_{\nabla}(n) &= 3W_{\nabla}(n/2) + W_{\triangle}(n/2) + O(1) \;; \end{split}$$

where  $W_{\triangle}$  and  $W_{\nabla}$  are the work used by the recursive procedures JACOBI $\triangle$  and JACOBI $\nabla$ . The solution for the total work is  $W(n) = \Theta(n^2)$ , which is the same as the work of the iterative algorithm.

The number Q(n) of cache misses incurred by a subproblem of size n is described by three recurrences:

$$\begin{array}{lcl} Q(n) & = & 2Q_{\triangle}(n/2) + 2Q_{\nabla}(n/2) + O(1) \; ; \\ \\ Q_{\triangle}(n) & \leq & \left\{ \begin{array}{ll} \Theta(1 + n/L) & \text{if } n \leq \alpha Z \; , \\ 3Q_{\triangle}(n/2) + Q_{\nabla}(n/2) + O(1) & \text{otherwise} \; ; \end{array} \right. \end{array}$$

<sup>&</sup>lt;sup>2</sup>The results can be extended, but the analysis is somewhat more complicated.

**Figure 6-6:** Computational dag of JACOBI-ITER. **(a)** complete subgraph of size  $9 \times 9$ , **(b)** its decomposition into lines, and **(c)** diamond-shaped subdag of width  $\Omega(d)$  that is enclosed by two nodes u and v of distance d=4.

$$Q_{\nabla}(n) \leq \begin{cases} \Theta(1+n/L) & \text{if } n \leq \alpha Z, \\ 3Q_{\nabla}(n/2) + Q_{\triangle}(n/2) + O(1) & \text{otherwise;} \end{cases}$$

where  $Q_{\triangle}$  and  $Q_{\triangle}$  are the cache misses of the two recursive procedures JACOBI $\triangle$  and JACOBI $\nabla$ , and  $\alpha$  is a sufficiently small constant. The base case occurs when the two arrays fit into the cache. Solving these recurrences, we obtain  $Q(n) = \Theta(1 + n/L + n^2/ZL)$  cache misses.

#### 6.3 Lower bound

Finally, we prove that the number of cache misses for this problem is lower bounded by  $\Omega(1 + n/L + n^2/ZL)$ , which implies that the recursive algorithm JACOBI-REC is indeed optimal.

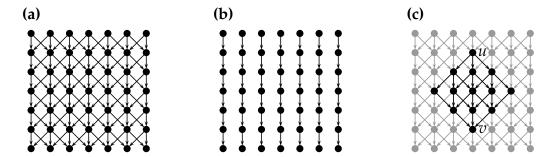

We can use the red-blue pebble game technique described by Hong and Kung [25] to lower-bound the number of cache misses incurred by any algorithm computing n generations of an Jacobi-multipass filter on n elements. Hong and Kung use properties of the *computation dag* (directed acyclic graph) G given by a computation to lower-bound the number of cache misses on a two-level memory. Nodes in a computation dag represent operations, and edges, the data-flow of the algorithm. Nodes with no incoming edges are input and nodes with no outgoing edges are output. Figure 6.3(a) shows a subgraph of the computation dag given by JA-COBI-ITER. A vertex-disjoint path from inputs to outputs will be called *lines*. The decomposition of Figure 6.3(a) into lines is shown in Figure 6.3(b). The number of cache misses can be lower-bounded by the *information speed function*  $F_G(d)$  of a dag G, which is defined as follows.

For any two vertices u and v on the same line that are at least d apart, there are  $F_G(d)$  vertices in the dag G satisfying two properties:

- 1. None of these vertices belongs to the same line.

- 2. Each of these vertices belongs to a path connecting u and v.

In the dag given by JACOBI-ITER, for example, two nodes u and v enclose a diamond-shaped subdag of width  $\Omega(d)$ , where d is the distance of u and v, as shown in Figure 6.3(c).

We can obtain lower bounds on the cache complexity *Q* using the following lemma which is proven in [25].

**Lemma 16** Suppose G is a computation dag where all inputs can reach all outputs through vertex-disjoint paths, and its information speed function is  $\Omega(F_G(d))$ . If  $F_G(d)$  is monotonically increasing, and  $F_G^{-1}(d)$  exists, then the number of cache misses required to execute G is

$$Q = \Omega(K/F_G^{-1}(Z)),$$

where K is the total number of vertices on the vertex-disjoint paths or lines.

We use Lemma 16 to prove a lower bound on the cache complexity of any algorithm computing n generations of a Jacobi multipass filter on n elements by finding an upper bound on  $F_G^{-1}$ .

**Theorem 17** Any scheduling of the computation dag induced by the JACOBI-ITER algorithm on an array of size n incurs  $\Omega(1 + n/L + n^2/LZ)$  cache misses.

*Proof.* This theorem can be proven by applying three lower bounds:

1. Suppose that L=1. We can lower-bound the cache complexity using Lemma 16. Consider the subnetwork of the dag of JACOBI-ITER that includes only one third of the edges, as shown in Figure 6.3(b). The subnetwork has n lines with  $K=\Theta(n^2)$  vertices. The information speed function is  $F(d)=\Omega(d)$ , since a diamond-shaped subdag of width  $\Omega(d-2)$  is enclosed by two nodes as illustrated in Figure 6.3(c) for d=4. Therefore  $F^{-1}(d)=O(d)$  and the resulting lower bound for Q is  $Q(n)=\Omega(n^2/Z)$ .

At most L data items are moved into cache when a cache miss occurs. Thus, a first lower bound for L > 1 is

$$Q(n) = \Omega(n^2/ZL) .$$

**Figure 6-7:** Plot of update time per element per generation for optimized iterative and recursive implementations of a multipass filter on a 167-MHz UltraSparc with 16kB L1-cache and 512kB L2-cache.

- 2. The algorithm must read all  $\Theta(n)$  inputs, which reside on  $\Omega(n/L)$  cache lines. This yields the second lower bound of  $\Omega(n/L)$ .

- 3. The third lower bound is the trivial lower bound of  $Q(n) = \Omega(1)$ .

By combining these lower bounds we get  $Q(n) = \Omega(1 + n/L + n^2/LZ)$ .

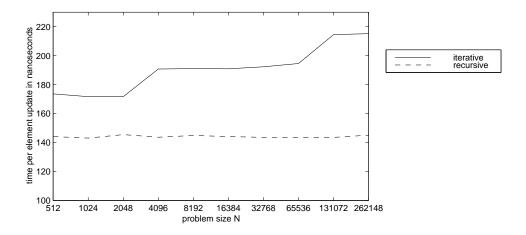

## 6.4 Experimental results

We now compare optimized implementations of the iterative and the recursive algorithms for the simple update rule given in Equation (6.1). (The iterative algorithm uses only 2 temporary variables, and the recursive implementation uses a "unfolded" [18] base case.) Figure 6-7 shows a plot of the update time per element per generation for the two versions on a 167-MHz Sun UltraSparc with 16kB L1-cache and 512kB L2-cache. The update time for the recursive algorithm is not only faster than the iterative algorithm, it is also nearly constant, whereas the iterative implementation slows down with every new level of the memory hierarchy. For arrays that do not fit in L2-cache, the recursive implementation executes in less than 70% of the time of the iterative version. The gain can be even higher for out-of-core algorithms, because disk bandwidth is considerably less than memory or cache bandwidths.

## Summary

In this section, we have presented an optimal recursive algorithm to compute a multipass filter over one-dimensional data. We compared its cache complexity to a iterative algorithm and gave some brief empirical results for this problem. The recursive algorithm executes in less than 70% of the time of the iterative algorithm on problems that do not fit in *L*2-cache. The technique presented here can be extended to multidimensional stencil-filters. I expect that the advantage of the cache-oblivious algorithm on the multidimensional data will prove to be even greater.

# Cache complexity of ordinary algorithms

This section analyzes the cache complexity of the "ordinary" algorithms for matrix transposition, matrix multiplication, and sorting. Although optimal in the random-access machine model [4] and cache oblivious, these algorithms are not asymptotically optimal with respect to cache misses. We first prove that the number of cache misses of algorithms with a "regular" complexity bound (as defined later) is asymptotically the same even if least-recently-used (LRU) is used instead of optimal replacement. We then show that the standard iterative algorithm to transpose a matrix incurs  $\Omega(n^2)$  cache misses on a  $n \times n$  matrix matching the trivial upper bound of one cache miss per time step. The ordinary iterative algorithm to multiply two  $n \times n$  matrices incurs  $\Omega(n^3)$  cache misses, which is also the worst possible asymptotic behavior for an  $O(n^3)$ -work algorithm. Many "ordinary" algorithms for sorting exit. We pick mergesort and prove that its cache complexity is  $\Omega((n/L) \lg (n/Z))$  when sorting an array of n elements, which is a factor of  $\Theta(\lg Z)$  away from optimal.

The ideal-cache model is well suited for algorithm design and upper-bound analyses. This comes in part from the optimal replacement strategy employed by the ideal-cache.

Lower-bounding the cache complexity of an algorithm with optimal replacement is somewhat hard, since it must be proven that the optimal replacement strategy will do. For upper bounds, we can pick any replacement strategy we

want and the optimal replacement will perform as least as well as our arbitrary strategy. However, for lower bounds we must be more careful. We usually do not know which line the optimal replacement strategy would replace. The following analysis shows that the optimal and omniscient replacement strategy used by an ideal cache can be simulated efficiently by the LRU replacement strategy. The LRU strategy replaces the cache line whose most recent access was earliest among all lines in the associativity set. In fact, for algorithms with a "regular" complexity bound, LRU and optimal replacement yield the same asymptotic bounds. We define a cache complexity bound Q(n; Z, L) to be *regular* if

$$Q(n; Z, L) = O(Q(n; 2Z, L)). (7.1)$$

**Lemma 18** Consider an algorithm that causes  $Q^*(n; Z, L)$  cache misses on a problem of size n using a (Z, L) ideal cache. Then, the same algorithm incurs  $Q(n; Z, L) \leq 2Q^*(n; Z/2, L)$  cache misses on a (Z, L) cache that uses LRU replacement.

*Proof.* Sleator and Tarjan [37] have shown that the cache misses on a (Z, L) cache using LRU replacement is  $(Z/(Z-Z^*+1))$ -competitive with optimal replacement on a  $(Z^*, L)$  ideal if both caches start with an empty cache. It follows that the number of misses on a (Z, L) LRU-cache is at most twice the number of misses on a (Z/2, L) ideal-cache.

**Corollary 19** For algorithms with regular cache complexity bounds, the asymptotic number of cache misses is the same for LRU and optimal replacement.

*Proof.* This corollary follows directly from Lemma 18 and the regularity condition.  $\Box$

The same argument extends to a variety of other replacement strategies [11], including:

**flush when full:** Whenever there is a cache miss and there is no space left in the cache, evict all lines currently in the cache (call this action a "flush").

**clock replacement:** An approximation to LRU in which a single "use bit" replaces the implicit (time of last access) timestamp of LRU.

**first-in, first-out:** Replace the line that has been in the fast memory longest.

**random:** Whenever a cache miss occurs, evict a page chosen randomly and uniformly among all fast memory pages.

We shall use Corollary 19 in the following lower-bound proofs and assume that the cache is handled by LRU to simplify our analyses. If an algorithm analyzed with LRU is regular, then the optimal strategy must also be regular. Therfore, according to Corollary 19 the bound derived with the LRU analysis applies to the ideal cache model as well.

#### 7.1 Matrix multiplication

In this section, we analyze the straightforward iterative algorithm for matrix multiplication. We prove that it causes  $\Omega(n^3)$  cache misses when the  $n \times n$  matrices are stored in row-major order and do not fit in cache. We further show that even if the matrices are stored in the order in which they are used and do not fit in cache, the number of cache misses is at least  $\Omega(n^3/L)$ , compared to  $\Theta(n^3/L\sqrt{Z})$  for an the cache-optimal  $\Theta(n^3)$ -work algorithm presented in Section 2.

The simplest way to compute the product of two matrices is to evaluate the formula