# SiFive Core Designer From Custom CPU to Hello World in 30 Minutes

# Silicon at the speed of software.

Design RISC-V CPUs in an hour. Get custom SoCs in weeks, not months. Impossible? Not anymore.

Start Designing

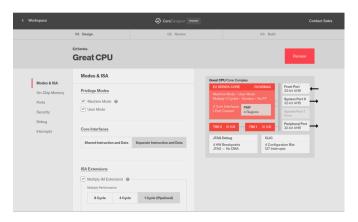

#### SiFive Core Designer

| <ul> <li>C</li> <li>https</li> <li>K</li> <li>Workspace</li> </ul>                                                                     | s://scs.sitive.com/core-designer/4                                                                                               | customize/4822849d-ef63-4776-aea |                          |                                                 |                                 | ☆ () ⓒ   ③<br>Contact Sales                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------|-------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------|

| 01.                                                                                                                                    | Design                                                                                                                           | 02. Review                       |                          |                                                 | 03. Bui                         | ld                                                                               |

|                                                                                                                                        | E2 Series<br>Great CPU                                                                                                           |                                  |                          | Review                                          |                                 |                                                                                  |

| Modes & ISA                                                                                                                            | Modes & ISA                                                                                                                      |                                  | Great CPU Cor            |                                                 | _                               |                                                                                  |

| On-Chip Memory     Privile       Ports     Image: Chip Memory       Security     Image: Chip Memory       Debug     Image: Chip Memory | Privilege Modes          Image: Machine Mode         Image: Machine Mode         Image: Machine Mode         Image: Machine Mode |                                  |                          | de • User Mode<br>elined) • Atomics<br>aces PMP |                                 | Front Port<br>32-bit AHB<br>System Port 0<br>32-bit AHB<br>System Port 1<br>None |

|                                                                                                                                        | Core Interfaces                                                                                                                  |                                  | <b>TIM O</b> 16 K        |                                                 |                                 | Peripheral Port<br>32-bit AHB                                                    |

|                                                                                                                                        | Shared Instruction and<br>Data                                                                                                   | Separate Instruction and<br>Data | JTAG Debug<br>4 HW Break |                                                 | CLIC<br>4 Configu<br>127 Intern | ration Bits<br>upts                                                              |

|                                                                                                                                        | ISA Extensions<br>Multiply (M Extension)                                                                                         | 0                                |                          |                                                 |                                 |                                                                                  |

|                                                                                                                                        | Multiply (M Extension)                                                                                                           | •                                |                          |                                                 |                                 |                                                                                  |

- All SiFive Core IP is configured and delivered via the SiFive Core Designer Web Portal

- Simple, Easy to Use, Web Interface

- Variants are generated with click of a button and available from the Workspace

#### Variants contain

•

- RTL matching the configuration, including a testbench, and other collateral needed to realize the design

- Documentation specific to the design

- Customized bare-metal BSP for easy integration into SiFive's SDKs

- FPGA bitstreams for common FPGA development boards for easy software benchmarking of the RC

#### In-house IP: SiFive RISC-V Core IP Product Offering

|                                                                                 | ECores 32-bit embedded cores<br>MCU, edge computing,<br>AI, IoT                                                                                                                                                         | <b>SCores</b><br><b>64-bit embedded cores</b><br>Storage, AR/VR, machine<br>learning                                                | <b>UCORES</b><br><b>64-bit application cores</b><br>Linux, datacenter, network<br>baseband                                                                             |

|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 Series                                                                        | E7 Series                                                                                                                                                                                                               | S7 Series                                                                                                                           | U7 Series                                                                                                                                                              |

| Highest<br>performance:<br>8-stage, dual-issue<br>superscalar pipeline          | <ul> <li>&gt; E76-MC<br/>Quad-core 32-bit embedded processor</li> <li>&gt; E76<br/>High performance 32-bit embedded core</li> </ul>                                                                                     | <ul> <li>&gt; S76-MC<br/>Quad-core 64-bit embedded processor</li> <li>&gt; S76<br/>High-performance 64-bit embedded core</li> </ul> | <ul> <li>&gt; U74-MC<br/>Multicore: four U74 cores and one S76 core</li> <li>&gt; U74<br/>High performance LInux-capable processor</li> </ul>                          |

| 3/5 Series                                                                      | E3 Series                                                                                                                                                                                                               | S5 Series                                                                                                                           | U5 Series                                                                                                                                                              |

| <b>Efficient</b><br><b>performance:</b><br>5–6-stage, single-<br>issue pipeline | <ul> <li>&gt; E34<br/>E31 features + single-precision floating point</li> <li>&gt; E31<br/>Balanced performance and efficiency</li> </ul>                                                                               | <ul> <li>&gt; S54<br/>S51 features + single-precision floating point</li> <li>&gt; S51<br/>Low-power 64-bit MCU core</li> </ul>     | <ul> <li>&gt; U54-MC<br/>Multicore application processor with four<br/>U54 cores and one S76 core</li> <li>&gt; U54<br/>Linux-capable application processor</li> </ul> |

| 2 Series                                                                        | E2 Series                                                                                                                                                                                                               | S2 Series                                                                                                                           |                                                                                                                                                                        |

| Power & area<br>optimized:<br>2–3-stage, single-<br>issue pipeline              | <ul> <li>&gt; E24         E21 + single-precision floating point     </li> <li>&gt; E21         E20 + User Mode, Atomics, Multiply, TIM     </li> <li>&gt; E20         Our smallest, most efficient core     </li> </ul> | > <b>S21</b><br>Area-efficient 64-bit MCU core                                                                                      |                                                                                                                                                                        |

| RIGHT 2019 SIFIVE. ALL RIGHTS RESERVED.                                         |                                                                                                                                                                                                                         |                                                                                                                                     |                                                                                                                                                                        |

- 4

**Si**Five

#### From Custom CPU to Hello World in 30 minutes

Step 1

Configure a custom SiFive RISC-V Core using SiFive Core Designer

#### Step 2

Use the FPGA bitstream from Step 1 to program a Digilent Arty FPGA board with the configured CPU

#### Step 3

Use Freedom Studio and the SiFive SDK to program and run Hello World

# **Step 1 - Configure the Core using SiFive Core Designer**

https://www.sifive.com/core-designer

# Vastly customizable core IP.

Get best-in-class core IP developed by the inventors of RISC-V and customize it to your exact specifications.

**Design Core**

## **Configure a SiFive RISC-V CPU**

# **SiFive Core Designer**

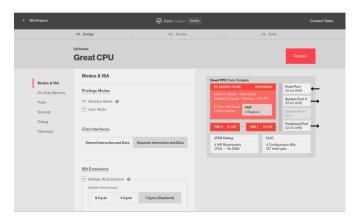

#### Web Interface to Configure SiFive Core IP

- No Complex EDA tools or scripting languages to learn

- What is configurable

- ISA, Performance levels, Modes, Ports, Interrupts, Security, Debug, and much more!

#### What is the output

Verilog RTL and supporting collateral, an FPGA bitstream, software, and documentation

| < Workspace                                                               | 01. Design                                                                                                                              | CoreDesigner PREVNEW          |                                                                                                                                                                                                                                        | Contact Sales                       |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|                                                                           | E2 Series<br>Great CPU                                                                                                                  | U.L. ITEVIEW                  |                                                                                                                                                                                                                                        | Review                              |

| Modes & ISA<br>On-Chip Memory<br>Ports<br>Security<br>Debug<br>Interrupts | Modes & ISA  Privilege Modes  Machine Mode  Machine Mode  Core Interfaces  Shared Instruction and Data                                  | Separate Instruction and Data | reat CPU Core Complex<br>E2 SERIES CORE RV32<br>Machine Mode - User Mode<br>Multiply (1 Cycle) - Atomics - No<br>2 Core Interfaces<br>1 Perf Counter 4 Regions<br>TIM 0 16 KB TIM 1<br>JTAG Debug<br>4 HW Breakpoints<br>JTAG – No DMA | 32-bit AHB<br>System Port 1<br>None |

|                                                                           | ISA Extensions          ISA Extensions         Image: Multiply (M Extension)         Multiply Performance         8 Cycle       4 Cycle |                               |                                                                                                                                                                                                                                        |                                     |

## **Core Designer UI Walkthrough**

Go to the SiFive website and click "Start Designing"

• <u>https://www.sifive.com/</u>

#### Choose a Core Series to start from

- Start from a pre-configured Standard Core

- Or start from scratch

#### Name the Design and Start Clicking!

• Change performance levels, memory maps, Privilege modes, Instructions Sets, Security, Debug, etc...

#### **Click Review and then Build**

• Launches SiFive's cloud based infrastructure to render and verify the design

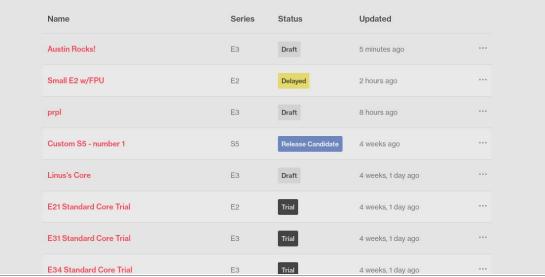

#### Download from your SiFive Workspace

| Home - SiFive × +                                                      |                                | ٠                         |

|------------------------------------------------------------------------|--------------------------------|---------------------------|

| SiFive – Design × +                                                    |                                |                           |

| ← → C. A https://scs.sifive.com/core_designer/                         |                                | + <u>0</u> e o e :        |

| SiFive — Core Designer × +                                             |                                | •                         |

| ← → C <u>e</u> https://scs.sifive.com/core-designer/customize/f09d&d92 | 2-fabr-40f1-a7r9-e4b2b1239br7/ |                           |

| ← → C                                                                  |                                | ☆ <b>0 @ 0</b> 🔇 :        |

| SiFive Chip Designer Core Designer                                     | Boards & Software Why SIFive   | Contact Sales Workspace D |

| Workspace                                                              |                                |                           |

| Core Designs                                                           | You have 3 builds remaining.   | New Core Design           |

| Name                                                                   | Series Status Updated          |                           |

## $\overline{\clubsuit}$

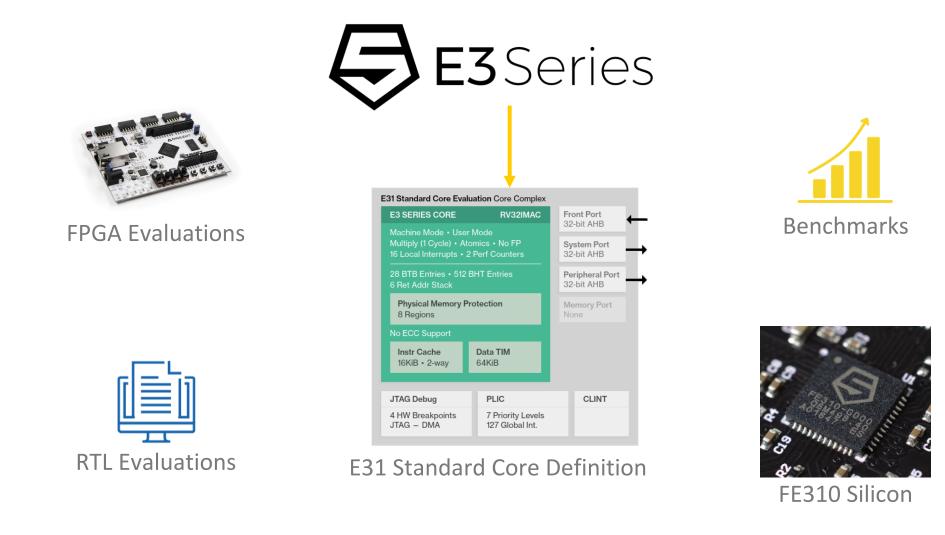

#### **Too Many Choices? Start with a Standard Core**

Standard Core RTL and FPGA Evaluations are Available with a clickthrough License

# Step 2 - Download the Deliverables and Program the FPGA

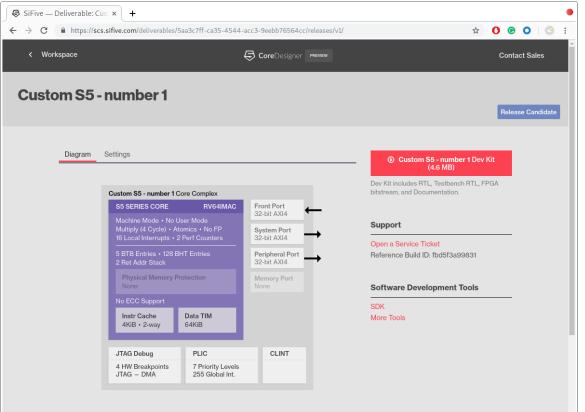

#### **Download the Deliverables from your SCD Workspace**

SiFive — Dashboard × + ☆ () () () () () SiFive Contact Sales Workspace D Workspace **Core Designs** You have 3 builds remaining. New Core Design Name Series Status Updated Small E2 w/FPU E2 a minute ago E3 Draft prpl 6 hours ago Release Candida 4 weeks ago Custom S5 - number 1 S5 Linus's Core Draft E3 4 weeks, 1 day ago Trial E21 Standard Core Trial E2 4 weeks, 1 day ago E31 Standard Core Trial E3 Trial 4 weeks, 1 day ago E34 Standard Core Trial E3 Trial 4 weeks, 1 day ago

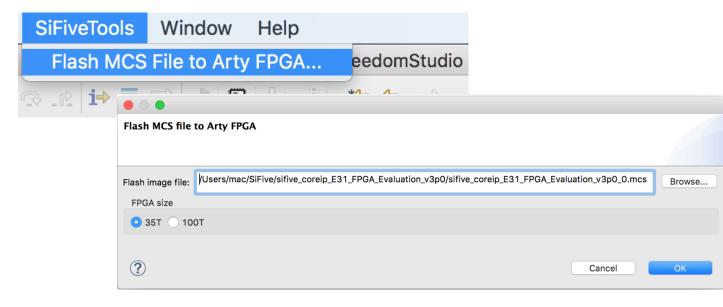

## Deploy the bitstream to the FPGA

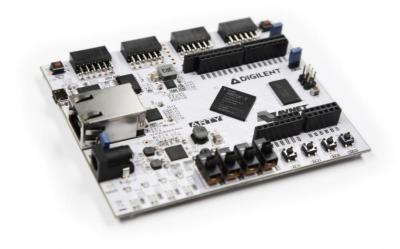

**1. Purchase a Digilent Arty**

https://store.digilentinc.com/arty-a7-artix-7-fpga-development-board-for-makers-and-hobbyists/

2. Download Freedom Studio

https://www.sifive.com/boards

3. Use Freedom Studio's Integrated Arty Flashing utility

# **Step 3 - Hello World!**

COPYRIGHT 2019 SIFIVE. ALL RIGHTS RESERVED.

#### **Download Freedom Studio**

| SiFive         | Products Why SIFive? |                                                                                                                                                                                   | Contact Sales N             | Workspace D |  |  |  |

|----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------|--|--|--|

|                | •                    | Software                                                                                                                                                                          |                             |             |  |  |  |

|                |                      | Dream it.                                                                                                                                                                         |                             |             |  |  |  |

|                |                      | Build it.                                                                                                                                                                         |                             |             |  |  |  |

|                |                      | Dulla It.                                                                                                                                                                         |                             |             |  |  |  |

|                |                      |                                                                                                                                                                                   |                             |             |  |  |  |

| Freedom Studio |                      | Freedom Studio is the fastest way to get started                                                                                                                                  | programming with your SiFiv | /e          |  |  |  |

|                |                      | hardware. Freedom Studio is built on top of the popular Eclipse IDE and                                                                                                           |                             |             |  |  |  |

|                |                      | packaged with a prebuilt toolchain and example<br>SDK. Freedom Studio is compatible with all SiFiv                                                                                |                             |             |  |  |  |

|                |                      |                                                                                                                                                                                   |                             |             |  |  |  |

|                |                      |                                                                                                                                                                                   |                             |             |  |  |  |

|                |                      |                                                                                                                                                                                   | Freedom Studio              |             |  |  |  |

|                |                      | • • •                                                                                                                                                                             | Windows                     | 0           |  |  |  |

|                |                      | 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1                                                                                                                                          |                             |             |  |  |  |

|                |                      | ▼ Clocal_interrupts Debug (GDB OpenOCD Debugging)<br>▼ Plocal_interrupts.elf                                                                                                      | macOS                       | 0           |  |  |  |

|                |                      | ♥ g9 Thread #1 (Suspended : Breakpoint)<br>■ button2_Jsrt] at local_interrupts.c:115 0x4040<br>■ handle_trap() at init:c:75 0x404001da<br>■ trap_entry() at entry:S:50 0x40400280 | CentOS                      | Θ           |  |  |  |

|                |                      | j≣ openood<br>j≣ riscv64-unknown-elf-gdb                                                                                                                                          | Ubuntu                      | 0           |  |  |  |

|                |                      |                                                                                                                                                                                   |                             |             |  |  |  |

|                |                      |                                                                                                                                                                                   |                             |             |  |  |  |

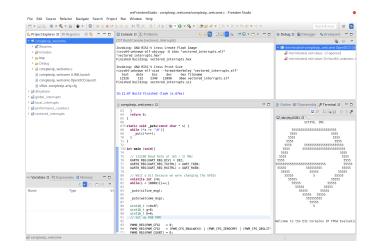

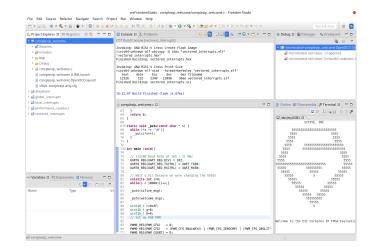

#### • Freedom Studio is an Eclipse based IDE with

- pre-built GCC and OpenOCD

- Bundled examples for SiFive targets

# Download Freedom Studio <u>https://www.sifive.com/boards</u>

Unzip to the desired installation directory

#### • Or... Skip the IDE

- Download pre-built binaries of GCC and OpenOCD from the same webpage

- Use Freedom-E-SDK to build and debug your software using a makefile CLI based flow <u>https://github.com/sifive/freedom-e-sdk</u>

#### **Build and Run the Software**

- File New C Project

- Select the Freedom E SDK Makefile Project

- Select the desired device and example and click Finish

- The program will automatically build and launch the debugger!

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3. 3. £ i> 3, 2 ≥ 4 = 4 = 0 - 4                                                                                                                                                                                                                                                                                                                                                                               | ★ ● ●                                                                               | $(\neg \diamond \bullet $ | Quick Access 🛛 🖻 🥃                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| ြဲ Project Explorer 🛿 🏭 Registers 📄 🔹 🔻 🗖 🗖                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 📮 Console 🛛 🔝 Problems                                                                                                                                                                                                                                                                                                                                                                                        | - 🕂 🗘 🔁 📰 🖬 📑 🛼 🖃                                                                   | ⊑ - 📬 - 🗆 🗆                                                                                                                                                       | 💠 Debug 🛿 🙀 Debugger 🔹 Breakpoint 🗖 🗖    |

| r 😂 coreplexip_welcome                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CDT Build Console [vectored_interrupts]                                                                                                                                                                                                                                                                                                                                                                       |                                                                                     |                                                                                                                                                                   | 🍇 i⇒ 🤝                                   |

| <ul> <li>↓ Binaries</li> <li>↓ Complexip_welcome.c</li> <li>↓ Coreplexip_welcome JLINK.launch</li> <li>↓ Coreplexip_welcome OpenOCD.launch</li> <li>↓ Sifive-coreplexip-arty.cfg</li> </ul> | Invoking: GNU RISC-V Cross Create Flash Im<br>riscv64-unknown-elf-objcopy -0 ihex "vecto<br>"vectored interrupts.hex"<br>Finished Building: vectored_interrupts.hex<br>Invoking: GNU RISC-V Cross Print Size<br>riscv64-unknown-elf-size -format=berkeley<br>text data bss dec hex fi<br>11526 132 2340 13998 36ae ve<br>Finished building: vectored_interrupts.siz<br>15:21:07 Build Finished (took 1s.67ms) | rèd_interrupts.elf"<br>"vectored_interrupts.elf"<br>lename<br>ctored_interrupts.elf |                                                                                                                                                                   |                                          |

| ▶ Global_interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                     |                                                                                                                                                                   | 😢 Outline 📟 Disassembly 🖉 Terminal 🕱 🖳 🗖 |

| Seperformance_counters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C coreplexip_welcome.c ⊠                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |                                                                                                                                                                   |                                          |

| • Variables ☎ 🕂 Expressions 🚺 Memory 🖓 🗖<br>الله الله الله الله الله الله الله الله                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <pre>85 86 _puts(welcome_msg); 87 88 uint16 t r=0x3F; 89 uint16 t g=0; 90 uint16 t b=0; 91 // Set up RGB PWM 92 93 PWM0 REG(PWM_CFG) = 0; </pre>                                                                                                                                                                                                                                                              | TXEN;<br>RXEN;                                                                      |                                                                                                                                                                   |                                          |

# **Si**Five

#### **Demo - From Custom CPU to Hello World in 30 minutes**

Step 1

Configure a custom SiFive RISC-V Core using SiFive Core Designer

#### Step 2

Use the FPGA bitstream from Step 1 to program a Digilent Arty FPGA board with the configured CPU

#### Step 3

Use Freedom Studio and the SiFive SDK to program and run Hello World

# Silicon verified. Market proven.

The most advanced configurable core IP and silicon solutions from the inventors of RISC-V.

Microcontrollers

Embedded

Linux

Multicore

Networking Storage Computing AI Industrial IoT Consumer Automotive

www.sifive.com