### A composable and predictable on-chip interconnect

Citation for published version (APA):

Hansson, M. A. (2009). A composable and predictable on-chip interconnect. Eindhoven: Technische Universiteit Eindhoven. https://doi.org/10.6100/IR642929

DOI:

10.6100/IR642929

Document status and date:

Published: 01/01/2009

**Document Version:**

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 07. Feb. 2020

# A Composable and Predictable On-Chip Interconnect

#### **PROEFSCHRIFT**

ter verkrijging van de graad van doctor aan de Technische Universiteit Eindhoven, op gezag van de rector magnificus, prof.dr.ir. C.J. van Duijn, voor een commissie aangewezen door het College voor Promoties in het openbaar te verdedigen op woensdag 17 juni 2009 om 16.00 uur

door

Andreas Hansson

geboren te Svedala, Zweden

Dit proefschrift is goedgekeurd door de promotoren:

prof.dr. H. Corporaal en prof.dr. K.G.W. Goossens

This work was carried out at Philips Electronics & NXP Semiconductors.

All product and company names mentioned in this work are trademarks of their respective holders.

#### ©Copyright 2009 Andreas Hansson

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission from the copyright owner.

#### CIP-DATA LIBRARY TECHNISCHE UNIVERSITEIT EINDHOVEN

Hansson, Andreas

A Composable and Predictable On-Chip Interconnect / by Andreas Hansson.

- Eindhoven: Technische Universiteit Eindhoven, 2009.

Proefschrift. - ISBN 978-90-386-1871-5

**NUR 959**

Trefw.: ingebedde systemen / multiprocessoren / ware-tijdssystemen / systeem-op-chip / netwerk-op-chip.

Subject headings: embedded systems / multiprocessors / real-time systems / system on chip / network on chip.

Making the simple complicated is commonplace. Making the complicated simple, awesomely simple, that's creativity.

Charles Mingus, 1922 - 1979

## **Acknowledgements**

This thesis is the result of many years of hard work and creative thinking that started long before my PhD studies, involved many bright minds, and a productive collaboration with many parties.

My foremost thank goes to my thesis promoter Prof. Kees Goossens. I thank him for his encouragement, and for his insights and suggestions that helped to shape my research and engineering skills. His valuable feedback contributed greatly to my work and to this thesis. I also wish to thank my promoter Prof. Henk Corporaal for his involvement in the work behind this thesis, and especially for all the lively discussions we have had throughout the years. Although he was not my promoter during the finalisation of the work, I want to thank Prof. Jef van Meerbergen for always asking the right questions. His insightful thoughts were sometimes so profound that they took me months or even years to fully understand. In addition to my promoters, I thank my thesis committee members for their valuable feedback. Together with the reviewers of numerous conferences and journals their criticisms have helped me improve this thesis in many ways.

During the past years I have enjoyed the hospitality of several universities and companies, and I have had the opportunity to work with a large number of people. I am especially grateful to Prof. Lambert (Ben) Spaanenburg for laying the first stone by arranging a trip to Eindhoven. I would like to thank all my colleagues at Philips and NXP, in particular Andrei Rădulescu, Martijn Coenen, Marco Bekooij and Maarten Wiggers. I also want to thank Jos Huisken and Menno Lindwer for all help (and intellectual property) they have provided. I thank the members of the Electronic Systems group at Eindhoven University of Technology, especially Prof. Ralph Otten, Marja de Mol-Regels and Rian van Gaalen. I am grateful to Prof. Li-Shiuan Peh for offering me the opportunity to take part in her research group at Princeton University, and for giving me an idea of what academic research looks like on the other side of the pond. Many thanks go to the students that helped in my work, in particular Alok Sharma, Marc van Hintum, Nikolaos Gkotsis, Mahesh Subburaman, Marcus Ekerhult and Andrew Nelson. In addition I thank all the students of the embedded systems laboratory, both in Eindhoven and Delft, that have used (and abused) the results of this thesis.

With many long days and weekends spent in the office, I am especially thankful to friends and family for being there outside working hours. Thank you all for sharing so many great experiences, whether travelling to distant countries, enjoying a drink (only one) at the pub, or upholding Scandinavian culinary traditions. I am especially grateful to Benny, my brother in arms, whom I have had the fortune of sharing both home and office with. May the force be with you. I would also like to thank my mother for always being there, never further than a phone call away, and for supporting me through all these years. Last but not least, thank you Marie Claire for enlightening my world and for being an amazing partner on the journey of life.

Thank you. Dank u. Dankie. Tack.

### **Abstract**

#### A Composable and Predictable On-Chip Interconnect

A growing number of independent applications, often with firm or soft real-time requirements, are integrated on the same *System on Chip* (SoC), in the form of either hardware or software *Intellectual Property* (IP). The applications are started and stopped at run time, creating different use-cases. Resources, such as the on-chip interconnect, are shared between different applications, both within and between use-cases, to reduce silicon cost and power consumption.

The functional and temporal behaviour of the applications is verified by simulation and formal methods. Traditionally, designers resort to monolithic verification of the system as whole, as the applications interfere in shared resources, and thus affect each other's behaviour. Due to interference between applications, the integration and verification complexity grows exponentially in the number of applications, and the task to verify correct behaviour of concurrent applications is on the system designer rather than the application designers.

The problem we aim to solve in this work is to provide an on-chip interconnect that enables the design of a SoC with multiple real-time applications with reasonable design effort and cost, even as the number of applications grows. We believe that the challenges introduced require an interconnect that offers scalability on the physical and architectural level, allowing a large number of applications and IPs to be integrated in the SoC. The interconnect must also support application diversity, in terms of behaviours, real-time requirements, communication paradigms, and IP interfaces. To reduce the integration effort, composability of applications is required, thus enabling application-level design and verification. For real-time applications, predictability with lower bounds on performance, is key in enabling bounds on the end-to-end temporal behaviour. To accommodate dynamic starting and stopping of applications, reconfigurability of the hardware platform is required. Lastly, automation of interconnect mapping and synthesis, is essential in helping the designer to quickly turn high-level requirements to an implementation.

As the main contributions of this work, we propose a complete on-chip interconnect architecture that fulfils the aforementioned requirements. We show how the associated design flow enables dimensioning, resource allocation, instantiation of the interconnect hardware and software, and verification of application-level performance requirements. We demonstrate the applicability of the proposed interconnect by constructing an example multi-processor system instance and mapping it to an FPGA. On this instance we demonstrate how multiple *diverse* applications, with soft and firm real-time requirements are independently analysed, using different methodologies. In the analysis we do not consider any of the other applications in the system. This is made possible by the *composability* of our interconnect, and is a major qualitative difference with existing SoC platforms. We demonstrate how the *predictability* of our interconnect enables us to derive bounds on the end-to-end temporal behaviour of a firm real-time audio post-processing application. Similarly, for a soft real-time image decoder, we derive conservative bounds on performance for specific input images. *Reconfigurability* is demonstrated by starting and stopping applications at run time. In contrast to other SoCs, reconfiguration is performed without affecting the other applications of the system, and with upper bounds on the time required. Finally, thanks to the *automation* the entire system is generated in a matter of hours, based on high-level specifications and requirements.

# **Table of Contents**

| 1 | Intr | oduction 1             |

|---|------|------------------------|

|   | 1.1  | Trends                 |

|   | 1.2  | Problem statement      |

|   | 1.3  | Requirements           |

|   | 1.4  | Contributions          |

|   | 1.5  | Organisation           |

| 2 | Pro  | posed solution19       |

|   | 2.1  | Architecture overview  |

|   | 2.2  | Scalability            |

|   | 2.3  | Diversity              |

|   | 2.4  | Composability          |

|   | 2.5  | Predictability         |

|   | 2.6  | Reconfigurability      |

|   | 2.7  | Automation             |

|   | 2.8  | Conclusions            |

| 3 | Dim  | ensioning 39           |

| • | 3.1  | Local buses            |

|   | 3.2  | Atomisers              |

|   | 3.3  | Protocol shells        |

|   | 3.4  | Clock domain crossings |

|   | 3.5  | Network interfaces     |

|   | 3.6  | Routers                |

|   | 3.7  | Mesochronous links     |

|   | 3.8  | Control infrastructure |

|   | 3.9  | Conclusions            |

| 4 | ΔIIo | cation67               |

| • | 4.1  | Sharing slots          |

|   | 4.2  | Problem formulation    |

|   | 4.3  | Allocation algorithm   |

|   | 4.4  | Experimental results   |

|   | 4.5  | Conclusions            |

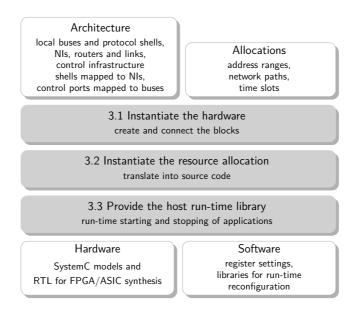

| 5 | Inst | antiation103           |

| • | 5.1  | Hardware               |

|   | 5.2  | Allocations            |

|   | 5.3  | Run-time library       |

|   | 5.4  | Experimental results   |

|   | 5.5  | Conclusions 120        |

| 6                | Veri       | fication                            | 123  |  |  |  |  |  |

|------------------|------------|-------------------------------------|------|--|--|--|--|--|

| •                | 6.1        | Problem formulation                 |      |  |  |  |  |  |

|                  | 6.2        | Network requirements                | 130  |  |  |  |  |  |

|                  | 6.3        | Network behaviour                   | 131  |  |  |  |  |  |

|                  | 6.4        | Channel model                       | 134  |  |  |  |  |  |

|                  | 6.5        | Buffer sizing                       |      |  |  |  |  |  |

|                  | 6.6        | Conservative simulation             |      |  |  |  |  |  |

|                  | 6.7        | Conclusions                         |      |  |  |  |  |  |

| 7                | Case       | o study                             | _145 |  |  |  |  |  |

| •                | 7.1        | e <b>study</b><br>Hardware platform |      |  |  |  |  |  |

|                  | 7.2        | •                                   |      |  |  |  |  |  |

|                  | 7.3        | Software platform                   | _    |  |  |  |  |  |

|                  | 7.4        | Application mapping                 |      |  |  |  |  |  |

|                  | 7.4<br>7.5 | Performance verification            |      |  |  |  |  |  |

|                  | 7.5        | Conclusions                         | 156  |  |  |  |  |  |

| 8                |            | Related work                        |      |  |  |  |  |  |

|                  | 8.1        | Scalability                         | 159  |  |  |  |  |  |

|                  | 8.2        | Diversity                           | 161  |  |  |  |  |  |

|                  | 8.3        | Composability                       | 162  |  |  |  |  |  |

|                  | 8.4        | Predictability                      | 165  |  |  |  |  |  |

|                  | 8.5        | Reconfigurability                   | 166  |  |  |  |  |  |

|                  | 8.6        | Automation                          | 167  |  |  |  |  |  |

| 9                | Con        | clusions and future work            | _169 |  |  |  |  |  |

|                  | 9.1        | Conclusions                         | 169  |  |  |  |  |  |

|                  | 9.2        | Tangible results                    | 171  |  |  |  |  |  |

|                  | 9.3        | Future work                         | 172  |  |  |  |  |  |

| Α                | Exai       | Example specification               |      |  |  |  |  |  |

|                  | A.1        | Architecture                        | 176  |  |  |  |  |  |

|                  | A.2        | Communication                       |      |  |  |  |  |  |

| Bil              | oliogi     | aphy                                | _181 |  |  |  |  |  |

| Glo              | ossarı     | y                                   | _195 |  |  |  |  |  |

| Curriculum Vitae |            |                                     |      |  |  |  |  |  |

I'm reconstructing the story from the back to the front so that I know where the front is.

John Irving, 1942 -

# Introduction

Embedded systems are rapidly growing in numbers and importance as we crowd our living rooms with digital televisions, game consoles and set-top boxes, and our pockets (or maybe handbags) with mobile phones, digital cameras, and personal digital assistants. Even traditional PC and IT companies are making an effort to enter the *consumer-electronics* business [4] with a mobile phone market that is four times larger than the PC market (1.12 billion compared to 271 million PCs and laptops in 2007) [168]. Embedded systems routinely offer a rich set of features, do so at a unit price of a few US dollars, and have an energy consumption low enough to keep portable devices alive for days. To achieve these goals all components of the system are integrated on a single circuit, a System on Chip (SoC). As we shall see, one of the critical parts in such a SoC, and the focus of this work, is the on-chip interconnect that enables different components to communicate with each other.

In this chapter, we start by looking at trends in the design and implementation of SoCs in Section 1.1. We also introduce our example system that serves to demonstrate the trends and is the running example throughout this work. This is followed by the problem statement in Section 1.2, accompanied by an overview of the key requirements in Section 1.3. Finally, Section 1.4 lists the key contributions of this work and Section 1.5 provides an overview of the remaining chapters.

#### 1.1 Trends

SoCs grow in complexity as an increasing number of independent *applications* are integrated on a single chip [9, 45, 49, 136, 168]. In the area of portable consumer systems, such as mobile phones, the number of applications doubles roughly every two years, and the introduction of new technology solutions is increasingly driven by applications [72, 80]. With increasing application heterogeneity, system-level constraints become increasingly complex and *application requirements*, as discussed next, become more multifaceted [142].

2 1.1. Trends

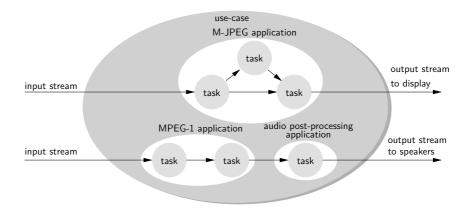

Figure 1.1: Application model.

#### 1.1.1 Application requirements

Applications can be broadly classified into control-oriented and signal-processing (streaming) applications. For the former, the reaction time is often critical [134]. Performance gains mainly come from higher clock rates, more deeply pipelined architectures and instruction-level parallelism. Control-oriented applications fall outside the scope of this work and are not discussed further. Signal-processing applications often have real-time requirements related to user perception [134], e.g. video and audio codecs, or requirements dictated by standards like DVB, DAB and UMTS [79, 122]. For signal-processing applications, an increasing amount of data must be processed due to growing data sets, i.e. higher video resolutions, and increasing work for the data sets, i.e. more elaborate and computationally intensive coding schemes [134]. As a result, the required processing power is expected to increase by 1000 times in the next ten years [181] and the gap between the processing requirement and the available processing performance of a single processor is growing super-linearly [80].

Delivering a certain performance is, however, not enough. It must also be performed in a timely manner. The individual applications have different real-time requirements [29]. For *firm real-time* applications, e.g. a Software-Defined Radio [122] or the audio post-processing filter, illustrated in Figure 1.1, deadline misses are highly undesirable. This is typically due to standardisation, e.g. upper bounds on the response latency in the aforementioned wireless standards [79], or perception, e.g. steep quality reduction in the case of misses. Note that firm real-time only differs from *hard real-time*, a term widely used in the automotive and aerospace domain, in that it does not involve safety aspects. *Soft real-time* applications, e.g. a video decoder, can tolerate occasional deadline misses with only a modest quality degradation. In addition, *non real-time* applications have no requirements on their temporal behaviour, and must only be functionally correct.

Each application has its own set of requirements, but the SoC typically executes

many applications *concurrently*, as exemplified by Figure 1.1. Furthermore, applications are started and stopped at run time by the user, thus creating many different *use-cases*, i.e. combinations of concurrent applications [63, 125]. The number of use-cases grows roughly exponentially in the number of applications, and for every use-case, the requirements of the individual applications must be fulfilled. Moreover, applications often span multiple use-cases and should not have their requirements violated when other applications are started or stopped [63, 146]. Going from the trends in application requirements, we now continue by looking at how the *implementation and design* of SoCs is affected.

#### 1.1.2 Implementation and design

As exemplified in Figure 1.1, applications are often split into multiple *tasks* running concurrently, either to improve the power dissipation [156] or to exploit task-level parallelism to meet real-time requirements that supersede what can be provided by a single processor [162]. The tasks are realised by hardware and software Intellectual Property (IP), e.g. accelerators, processors and application code. For an optimum balance between performance, power consumption, flexibility and efficiency, a *heterogeneous mix* of processing elements that can be tuned to the application domain of the system is required [181]. This leads to systems with a combination of general-purpose processors, digital-signal processors, application-specific processors, and dedicated hardware for static parts [134]. Different IP components (hardware and software) in the same system are often developed by *unrelated design teams* [81], either in-house or by independent IP vendors [46]. The diversity in origin and requirements lead to applications using a diverse set of programming models and communication paradigms [108].

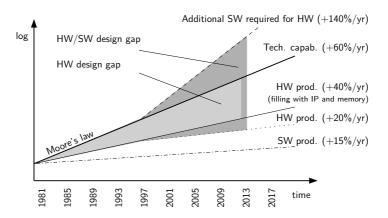

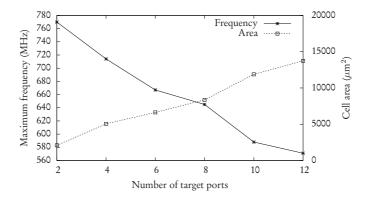

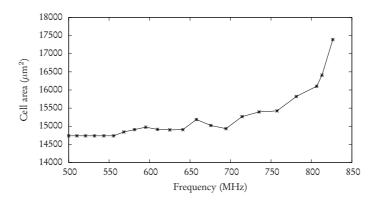

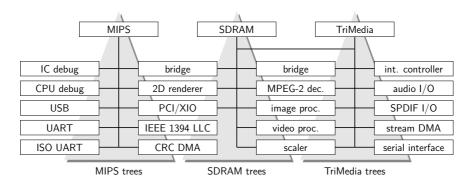

The rising number of applications and growing need for processing power lead to an increased demand for hardware and software. Figure 1.2 shows the well-known hardware design gap, with capability of technology doubling every 18 months (+60% annually), and hardware productivity growing more slowly, doubling every 24 months (+40% annually). The hardware design productivity relies heavily on *reuse* of IP and *platform-based design* [80], and improved over the last couple of years by filling the silicon with regular hardware structures, e.g. memory. Still, systems are not fully exploiting the number of transistors per chip possible with today's technology, and the gap continues to grow [72].

The increasing number of transistors on a SoC offers more integration possibilities, but the diminishing feature size complicates modularity and scalability at the physical level [94]. Global synchronisation is becoming prohibitively costly, due to process variability and power dissipation, and the distribution of low-skew clock signals already accounts for a considerable share of power consumption and die area [81, 129]. Moreover, with a growing chip size and diminishing feature size, signal delay is becoming a larger fraction of the clock-cycle time [31], and cross-chip signalling can no longer be achieved in a single clock cycle [81, 152].

In addition to the consequences at the physical level, the growing number of IPs also has large effects at the architectural level. The introduction of more IP promises

4 1.1. Trends

Figure 1.2: Hardware (HW) and software (SW) design gaps [81].

more parallelism in computational and storage resources. This, however, places additional requirements on the resources involved in communication that have to offer more parallelism as well.

While the hardware design gap is an important issue, the hardware/software design gap is far more alarming. This gap is quickly growing as the demand for software is currently doubling every 10 months (+140%/year), with recent SoC designs featuring more than a million lines of code [72]. The large amount of software is a response to evolving standards and changing market requirements, requiring flexible and thus programmable platforms. Despite much reuse of software too [180], the productivity for hardware-dependent software lags far behind hardware productivity and only doubles every 5 years (+15%/year).

A dominant part of their overall design time is spent in verification, thus limiting productivity. New designs greatly complicate the verification process by increasing the level of concurrency and by introducing additional application requirements [81]. Already, many of the bugs that elude verification relate to timing and concurrency issues [180]. The problem is further worsened by a growing sharing of resources. As a result of the sharing, applications cannot be verified in isolation, but must first be integrated and then verified together. The *monolithic* analysis leads to an explosion of the behaviours to cover, with negative impact on verification time [156], whether done by simulation of formal analysis. Furthermore, the dependencies between applications severely complicate the protection and concurrent engineering of IP, which negatively affects the *time and cost* of design.

#### 1.1.3 Time and cost

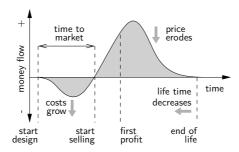

In addition to the problems related to the ability to design current and future systems, these systems must also be designed with a low cost and a low *Time To Market (TTM)*, as illustrated in Figure 1.3. Portable consumer SoCs have *as-soon-as-possible requirements*

Figure 1.3: Product life cycle.

on TTM [81]. The requirement is largely a response to a diminishing *product life time*, where consumers replace old products much more frequently due to rapid technology changes [81]. Mobile phone manufacturers, for example, release two major product lines per year compared with one just a few years ago [72]. Furthermore, as the product life time decreases, the units sold must still generate enough profit to cover the *rising costs* of manufacturing and design.

Profit is a major concern, as the manufacturing Non-Recurring Engineering (NRE) cost for a contemporary SoC is in the order of \$1M, and design NRE cost routinely reaches \$10M to \$100M [103]. Traditionally, the rising costs are mitigated by high volumes and a high degree of system integration of heterogeneous technologies [80]. However, an increasing portion of the NRE cost is going into design and test and in 2007, for the first time in the history of SoC design, software design cost exceeded hardware design cost, and now accounts for 80% or more of the embedded systems development cost [81]. Thus, we see a steep increase in NRE cost for SoC designs which is not compensated for by higher volumes or higher margins. On the contrary, volumes are increasingly dependent on a low TTM, and margins decrease as prices erode quicker over time. The International Technology Roadmap for Semiconductors (ITRS) [81] goes as far as saying that the cost of designing the SoC is the greatest threat to continuation of the semiconductor road map.

#### 1.1.4 Summary

To summarise the trends, we see growing needs for functionality and performance, coupled with increasingly diverse requirements for different applications. Additionally, applications are becoming more dynamic, and are started and stopped at run time by the user. The diversity in functionality and requirements is also reflected in the architecture, as the applications are implemented by heterogeneous hardware and software IP, typically from multiple independent design teams. The increasing number of applications and resources also lead to an increased amount of resource sharing, both within and between use-cases. We illustrate all these trends in the following section, where we introduce an example system that we refer to throughout this work.

6 **1.1. Trends**

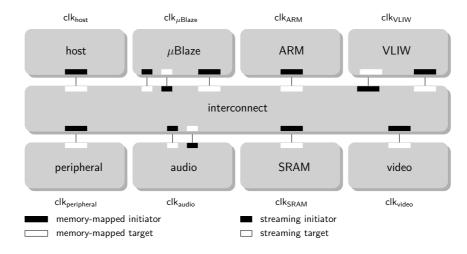

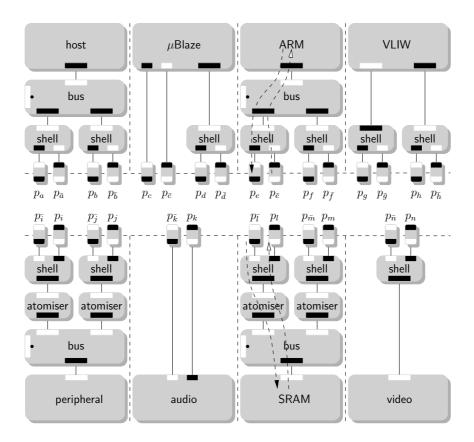

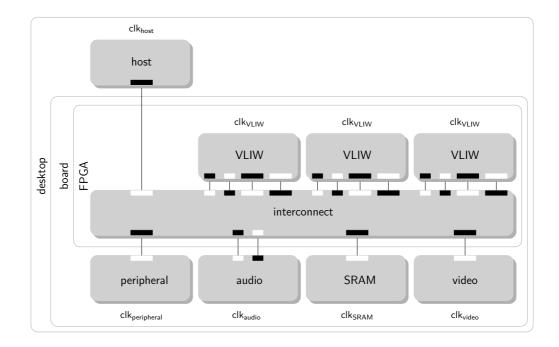

Figure 1.4: Example system.

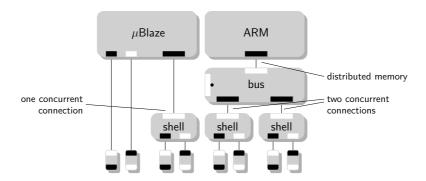

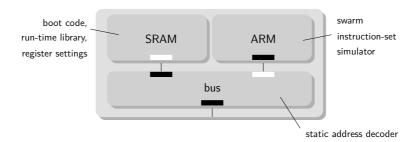

#### 1.1.5 Example system

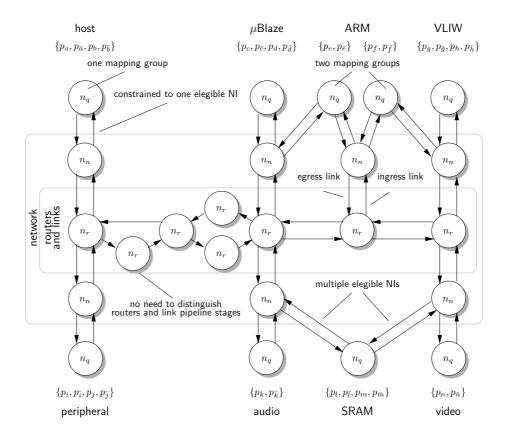

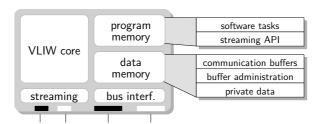

The system in Figure 1.4 serves as our design example. Despite its limited size, this system is an example of a software-programmable, highly-parallel Multi-Processor SoC (MPSoC), as envisioned by e.g. [72, 80, 103]. The system comprises a host processor, a number of heterogeneous processing engines, peripherals, and memories. Three processors, a Very Long Instruction Word (VLIW), an ARM and a  $\mu$ Blaze, are connected to a memory-mapped video subsystem, an embedded SRAM, an audio codec, and a peripheral tile with a character display, push buttons, and a touch-screen controller. The host controls all the IPs and the *interconnect*, which binds them all together.

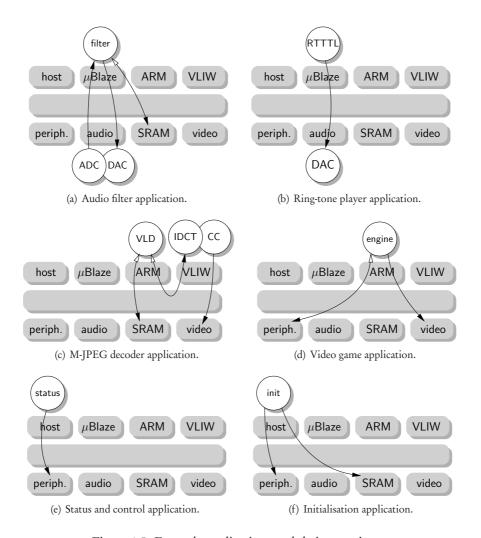

For our example we assume a static set of applications, defined at design time, with tasks already statically mapped onto hardware IPs. This assumption is in line with the design flow proposed in this work. We consider six applications running on this system, as illustrated in Figure 1.5. First, the two audio applications, both with firm real-time requirements as failure to consume and produce samples at 48 kHz causes noticeable clicks and sound distortion. Second, a Motion-JPEG (M-JPEG) decoder and a video game. These applications both have soft real-time requirements, as they have a frame rate that is desirable, but not critical, for the user-perceived quality. Lastly, the two applications that run on the host. In contrast to the previous applications, they have no real-time constraints and only need to be functionally correct. In Figure 1.5, the individual tasks of the applications are shown above and below the IPs to which they are mapped, and the communication between IPs is indicated by arrows. The solid- and open- headed arrows denote requests and responses, respectively. We now

<sup>&</sup>lt;sup>1</sup>The names are merely used to distinguish the three processors. Their actual architecture is of no relevance for the example. The three processor families have, however, been demonstrated together with the interconnect proposed in this work.

Figure 1.5: Example applications and their mappings.

8 1.1. Trends

discus the different applications in-depth.

The audio filter task runs on the  $\mu$ Blaze.<sup>2</sup> Input samples are read from the audio line-in Analog to Digital Converter (ADC) and a reverb effect is applied by adding attenuated past output samples that are read back from the SRAM. The output is written back to the line-out Digital to Analog Converter (DAC) and stored in the SRAM for future use. The Ring Tone Text Transfer Language (RTTTL) player, running on the same  $\mu$ Blaze, interprets and generates the waveforms corresponding to ring-tone character strings and sends the output to the audio line-out.

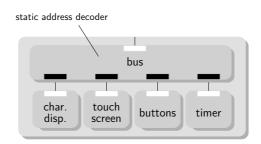

The software M-JPEG decoder is mapped to the ARM and VLIW. The ARM reads input from SRAM and performs the Variable Length Decoding (VLD), including the inverse zig-zag and quantisation, before it writes its output to the local memory of the VLIW. The VLIW then carries out the Inverse Discrete Cosine Transform (IDCT) and Colour Conversion (CC) before writing the decoded pictures to the video output, eventually to be presented to the display controller. Both the ARM and the VLIW make use of distributed shared memory for all communication, and rely on memory consistency models to implement synchronisation primitives used in inter-processor communication. The other soft real-time application in our system is a video game. The ARM is responsible for rendering the on-screen contents and updating the screen based on user input. Memory-mapped buttons and timers in the peripheral tile are used to provide input and calibrate the update intervals, respectively.

Lastly, there are two non real-time applications that both involve the host. The initialisation application supplies input data for the decoder into the shared SRAM, and initialises sampling rates for the audio. When the system is running, the status and control application is responsible for updating the character display with status information and setting the appropriate gain for the audio input and output.

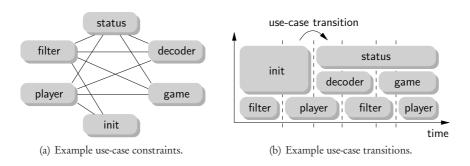

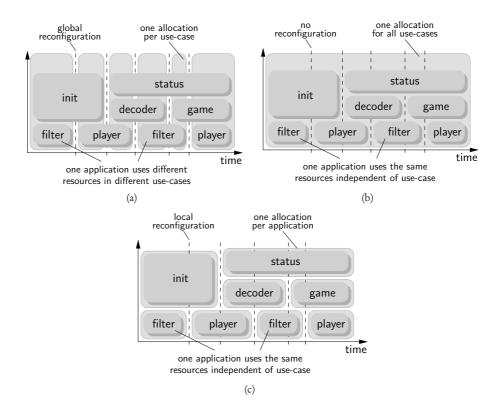

The individual *applications* are combined into *use-cases*, based on constraints as shown in Figure 1.6(a). An edge between two applications means that they may run concurrently. From these constraints we get a set of use-cases, determined by the cliques (every subgraph that is a complete graph) formed by the applications. The number of use-cases thus depends on the constraints, and is typically much larger than the number of applications. Figure 1.6(b) exemplifies how the user could start and stop applications dynamically at run time, creating six different use-cases. Traditionally, use-cases are optimised independently. However, as seen in the figure, applications typically span multiple use-cases, e.g. the filter application continues to run as the decoder is stopped and the game started. Even during such changes, the real-time requirements of the filter application must not be violated.

Already in this small system, we have multiple concurrent applications, and a mix of firm-, soft- and non real-time requirements. The tasks of the applications are distributed across multiple heterogeneous resources (as in the case of the decoder application), and the resources in turn (in this case the interconnect, SRAM and peripheral tile) are shared between applications. The hardware IPs make use of both bi-directional

<sup>&</sup>lt;sup>2</sup>For brevity, we assume that the processors have local instruction memories and leave out the loading of these memories. In Chapter 7 we demonstrate how loading of instructions is taken into account.

Figure 1.6: Example use-cases.

address-based memory-mapped protocols like DTL [149], AXI [6], OCP [137], AHB [5], PLB [199], Avalon-MM [3] (on the VLIW, ARM,  $\mu$ Blaze, video, SRAM and peripheral), and uni-directional streaming protocols like DTL PPSD [149], Avalon-ST [3] and FSL [200] (on the  $\mu$ Blaze and audio). Additionally, the system has multiple clock domains, as every IP (and also the interconnect) resides in a clock domain of its own.

Having introduced and exemplified the trends in embedded systems, we continue by looking at the consequences on the system design and implementation.

#### 1.2 Problem statement

The trends have repercussions on all parts of the system, but are especially important for the design and implementation of the interconnect. The interconnect is a major contributor to the time required to reach timing closure on the system [81]. On the architectural level, the increasing number of IPs translates directly to a rapidly growing parallelism that has to be delivered by the interconnect in order for performance to scale. The interconnect is also the location where the diverse IP interfaces must interoperate. Concerning the increasing integration and verification complexity, the interconnect plays an important role, as it is the primary locus of the interactions between applications. The interconnect is also central in enabling real-time guarantees for applications where the tasks are distributed across multiples IPs. The impact the interconnect has makes it a key component of the MPSoC design [103, 152]. The problem we aim to solve in this work is:

Provide an on-chip interconnect that enables the design of a SoC with multiple heterogeneous real-time applications with reasonable design effort and implementation cost.

#### 1.3 Requirements

We cannot change the applications or the innovation speed, and instead look at simplifying the design and verification process through the introduction of a new on-chip

interconnect. We believe that the challenges introduced require an platform template that offers:

- *scalability* at the physical and architectural level (Section 1.3.1), allowing a large number of applications and IPs to be integrated on the SoC,

- diversity in IP interfaces and application communication paradigms (Section 1.3.2), to accommodate a variety of application behaviours implemented using heterogeneous IP from multiple vendors,

- *composability* of applications (Section 1.3.3), enabling independent design and verification of individual applications and applications as a unit of reuse,

- *predictability* with lower bounds on performance (Section 1.3.4), enabling formal analysis of the end-to-end application behaviour for real-time applications,

- *reconfigurability* of the hardware platform (Section 1.3.5), accommodating all usecases by enabling dynamic starting and stopping of applications,

- automation of platform mapping and synthesis (Section 1.3.6), to help the designer go from high-level requirements to an implementation.

We now explain each of the requirements in more detail before detailing how this work contributes to address them.

#### 1.3.1 Scalability

The growing number of applications leads to a growing number and larger heterogeneity of IPs, introducing difficulties in timing validation and in connecting blocks running at different speeds [13]. This calls for *scalability at the physical level*, i.e. the ability to grow the chip size without negatively affecting the performance.

To enable components which are externally delay insensitive [31], Globally Asynchronous Locally Synchronous (GALS) design methods are used to decouple the clocks of the interconnect and the IPs [25, 55, 144], thus facilitating system integration [94]. Active rather than combinational interconnects are thus needed [195] to decouple computation and communication [88, 163], i.e. through the introduction of delay-tolerant protocols for the communication between IPs.

GALS at the level of IPs is, however, not enough. The interconnect typically spans the entire chip, and existing bus-based interconnects have many global wires and tight constraints on clock skew. With the increasing die sizes, it also becomes necessary to relax the requirements on synchronicity within the interconnect [144]. Networks on Chip (NoC) alleviate those requirements by moving from synchronous to mesochronous [26, 69, 144] or even asynchronous [13, 25, 155] communication. To achieve scalability at the physical level we require GALS design at the level of independent IPs, and a mesochronous (or asynchronous) interconnect.

Physical scalability is of no use unless the platform is scalable at the architectural level, i.e. supports a growing number of IPs and logical interconnections without

negatively affecting the performance. Existing bus-based solutions address the problem by introducing more parallelism with outstanding transactions, and improvements like bridges and crossbars [152]. NoCs extend on these concepts with their modular design, re-use, homogeneity and regularity [19, 39], offering high throughput and good power efficiency [13]. For architectural scalability we require a modular interconnect without inherent bottlenecks.

Scalability at the physical and architectural levels is necessary but not enough. The growing number of IPs and applications leads to a growing *diversity* in interfaces and programming models that the interconnect must accommodate.

#### 1.3.2 Diversity

As we have seen, applications have diverse behaviours and requirements. Applications like the filter in our example system have firm real-time requirements, but also a fairly static behaviour. The M-JPEG player on the other hand, is highly dynamic due to the input-dependent behaviour. This is also reflected in its more relaxed soft real-time requirements. To facilitate application diversity, we require that applications are not forced to fit in a specific formal model, e.g. have design-time schedules.

To facilitate the increased parallelism, diversity is also growing in the programming models and communication paradigms used by different IPs. SoCs are evolving in the direction of distributed-memory architectures, where the processor tiles have local memories, thus offering high throughput and low latency [130, 171], coupled with a low power consumption [131]. As the distributed nature of the interconnect leads to increased latencies, it is also important that the programming model is *latency tolerant*, i.e. enables maximal concurrency. In addition to memory-mapped communication, *streaming communication* (message passing) between IPs is growing in importance to alleviate contention for shared memories and is becoming a key aspect in achieving efficient parallel processing [103]. Hence, we require that the interconnect offers both streaming (message passing) and distributed shared memory communication, and an established memory consistency model.

The hardware IPs from different vendors use different interfaces, e.g. AHB [5] or AXI [6] for processors from ARM, PLB [199] for the  $\mu$ Blaze family from Xilinx, and DTL [149] for IP from Philips and NXP. To enable the use of existing IP, we require that the interconnect supports one or more industry-standard interfaces, and that it is easy to extend to future interfaces.

Lastly, there is also diversity in how the interconnect hardware and software is used by the system designer. That is, the tools used for e.g. compilation, elaboration, simulation and synthesis differ between users, locations and target platforms. As a consequence, we require that the interconnect uses standard hardware-description languages and programming languages for the interconnect hardware and software, respectively.

Not only are applications diverse, they also share resources. Hence, for verification of their requirements, there is a need to decouple their behaviours as described next.

#### 1.3.3 Composability

With more applications and more resources, the level of resource sharing is increasing. The increased sharing causes more application interference [133, 156], causing systems to behave in what has been described as mysterious ways [49]. In the presence of functional and non-functional application requirements the interference has severe implications on the effort involved in verifying the requirements, and increasing dynamism within and between applications exacerbates the problem [142]. Although individual IPs are pre-verified, the verification is usually done in a limited context, with assumptions that may not hold after integration. As a result, the complexity of system verification and integration grows exponentially with the number of applications, far outgrowing the incremental productivity improvement of IP design and verification [156], and making system-level simulation untenable [142]. Higher levels of abstraction, e.g. transactionlevel modelling, mitigate the problem but may cause bugs to disappear or give inaccurate performance measures. The high-levels models are thus not able to guarantee that the application requirements are met. Instead, we need to develop the technology that allows applications to be easily *composed* into working systems, independent other applications in the system [9, 65, 82, 136].

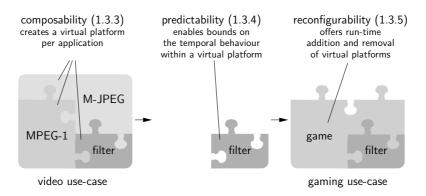

Composability is a well-established concept in systems used in the automotive and aerospace domains [8, 159]. In a composable platform one application cannot change the behaviour of another application.<sup>3</sup> Since application interference is eliminated, the resources available before and after integration can only be different due to the intrinsic platform uncertainty, caused by e.g. clock domain crossings. Composability enables design and debugging of applications to be done in isolation, with higher simulation speed and reduced debugging scope [65]. This is possible as only the resources assigned to the application in question have to be included in the simulation. Everything that is not part of the application can be safely excluded. As a result, probabilistic analysis, e.g. average-case performance or deadline miss rate, during the application design gives a good indication of the performance that is to be expected after integration. Application composability also improves IP protection, as the functional and temporal behaviour before and after integration is independent of other applications. Consequently, there is never a reason blame other applications for problems, e.g. violated requirements in the form of bugs of deadline misses. As a result, the IP of different Independent Software Vendors (ISV) do not have to be shared, nor the input stimuli.

Application composability places stringent requirements on the management of all resources that are shared by multiple applications, in our case the interconnect.<sup>4</sup> Composable sharing of resources requires *admission control* coupled with *non work-conserving arbitration* [201] between applications, where the amount of resources and time resources are available, is not influenced by other applications. For a shared memory controller, for example, the exact number of cycles required to finish a request must depend only on the platform and the cycle in which the request is made

<sup>&</sup>lt;sup>3</sup>We return to discuss other aspects of composability in Chapter 8, when reviewing related work.

<sup>&</sup>lt;sup>4</sup>Sharing of *processors* between applications is outside the scope of this work, a reasonable limitation that is elaborated on in Chapter 7 when discussing our example system.

(and previous requests from the same application), and not the behaviour of other applications [100].

With application composability, the quality of service, e.g. the deadline miss rate, and bugs, e.g. due to races, are unaffected by other applications. We already expect this type of composable behaviour on the level of individual transistors, gates, arithmetic logic units and processors [156]. Taking it one step further, in this work we require that applications can be viewed as design artifacts, implemented and verified independently, and composed into systems.

Composability addresses the productivity and verification challenge by a divideand-conquer strategy. It does, however, not offer any help in the verification of the realtime requirements of the individual applications. For this purpose, we need temporal predictability [14].

#### 1.3.4 Predictability

We refer to an architectural component as *predictable* when it is able to guarantee (useful) *lower bounds* on performance, i.e. minimum throughput and maximum latency [56, 82], given to an application. Predictability is needed to be able to guarantee that real-time requirements are met for firm real-time applications, thus delivering for example a desired user-perceived quality or living up to the latency requirements in wireless standards.

Note that predictability and composability are *orthogonal* properties [65]. For an illustrative example, consider our example system, and then in particular the filter and decoder applications. If the interconnect and SRAM use composable arbitration, as later described in Chapter 3, but the  $\mu$ Blaze and ARM are running a non real-time operating system, then the platform is *composable and not predictable*, because the applications do not influence each other, but the operating system makes it difficult, if not impossible, to derive *useful bounds* on the worst-case behaviour. In contrast, if the  $\mu$ Blaze and ARM are used without any caches and operating systems, but the SRAM is shared round robin, then the platform is *predictable and not composable*. This is due to the fact that the applications influence each other in the shared resource, but lower bounds on the provided service can be computed.

Predictable resources are, however, not enough. To determine bounds on the temporal behaviour of an application, the architecture and resource allocations must be modelled conservatively according to a specific *Model of Computation* (MoC). Moreover, also the application (or rather its tasks) must fit in a MoC that allows analytical reasoning about relevant metrics. Using predictability for application-level analysis thus *places limitations* on the application. In addition, the MoC must be *monotonic* [151], i.e. a reduced task execution time cannot result in a reduction of the throughput or increased latency of the application [151]. Without monotonicity, a *decrease* of the execution time at the task level may cause an *increase* at the application level [57]. To benefit from the bounds provided by a predictable platform, the MoC (but not the implementation itself) must be free of these types of scheduling anomalies. For application-level predictability *we require that the interconnect guaran-*

Figure 1.7: Reconfigurable composability and predictability.

tees a minimum throughput bound and maximum latency bound and that the temporal behaviour of the interconnect can be conservatively captured in a monotonic MoC.

To enable composability and predictability in the presence of multiple use-cases, the allocations of resources to applications must be *reconfigurable* as applications are started and stopped.

#### 1.3.5 Reconfigurability

As already illustrated in Figure 1.6, applications are started and stopped at run time, creating many different use-cases. Reconfigurability is thus required to allow dynamic behaviour between applications, i.e. to modify the set of running applications as illustrated in Figure 1.7. Moreover, applications must be started and stopped independently of one another [63, 91] to maintain composability (and predictability if implemented by the application in question) during reconfiguration. Consequently, we require that one application can be started and stopped without affecting the other applications of the system.

The problem of reconfigurability does, however, does not entail only the allocation of resources. The allocations must also be instantiated at run time in a safe manner. Internally, programming the interconnect involves modifications of the registers in individual components [23, 42]. To mitigate the complexity of reconfiguration, the abstraction level must be raised and provide an interface between the platform and the applications [102, 106]. Moreover, it is crucial that the changes are applied in such a way as to leave the system in a consistent state, that is, a state from which the system can continue processing normally rather than progressing towards an error state [93]. Simply updating the interconnect registers could cause out-of-order delivery or even no delivery, with an erroneous behaviour, e.g. deadlock as the outcome. In addition to correctness, some application transitions require an upper bound on the time needed for reconfiguration. Consider for example the filter and ring-tone player in our example system where a maximum period of silence is allowed in the transition between the

two applications. To accommodate these applications, we require a run-time library that hides the details of the architecture and provides correct and timely reconfiguration of the interconnect.

As we have seen, a scalable, diverse, composable, predictable and reconfigurable onchip interconnect addresses many problems, but also pushes decisions to design time. However, the design effort cannot be increased, and must remain at current levels for the foreseeable future [80]. Already today, meeting schedules is the number one concern for embedded developers [180]. As a consequence, the degree of *automation*, particularly in verification and implementation, must be increased.

#### 1.3.6 Automation

Within the scope of this work, automation is primarily needed in three areas. First, in platform *dimensioning* and resource *allocation*. That is, going from high-level requirements and constraints, formulated by the application designers to a specification of interconnect architecture and allocations. Second, in *instantiation* of the interconnect hardware and software, e.g. going from the specification to a functional system realisation in the form of SystemC or RTL HDL. Third, in the *evaluation* of the system by automating performance analysis and cost assessment. Throughout these steps, it is important that the automated flow allows user interaction at any point.

Deferring decisions to run time typically enables higher performance,<sup>5</sup> but also makes real-time analysis more difficult, if not impossible [100]. Compare, for example, the compile-time scheduling of a VLIW with that of a super-scalar out-of-order processor. Similar to the VLIW, the predictability and composability in our platform is based on hard resource reservations made at design and compile time. Therefore, platform mapping, essential for all SoCs [81], is even more prominent in our system. As part of the interconnect design flow, we require a clear unambiguous way to express the application requirements. Furthermore, we require that the design flow is able to automatically turn the requirements into an interconnect specification by performing the resource dimensioning and resource allocation.

Once we have a specification of the hardware and software that together constitute the platform, it must be instantiated. This involves turning the hardware specification into executable models or industry-standard hardware description languages, to be used by e.g. Field-Programmable Gate Array (FPGA) or Application-Specific Integrated Circuit (ASIC) synthesis tools. Additionally, the hardware must be accompanied by the software libraries required to program and control the hardware, and a translation of the allocation into a format useful to these libraries. Furthermore, this software must be portable to a wide range of host implementations, e.g. different processors and compilers, and be available for simulation as well as actual platform instances. Thus, we require that the design flow instantiates a complete hardware and software platform, using industry-standard languages.

<sup>&</sup>lt;sup>5</sup>More (accurate) information is available, but with smaller scope (local). Run-time processing is also usually (much) more constrained than design-time processing in terms of compute power.

16 1.4. Contributions

Lastly, automation is required to help in the evaluation of the interconnect instance. The design flow must make it possible to evaluate application-level performance, either through simulation or formal analysis, and do so at multiple levels, ranging from transaction-level to gate-level. It is also essential that the tools enable the designer to assess the cost of the system, for example by providing early area estimates. To enable the efficient design, use and verification of tomorrow's billion-transistor chips, we require that the interconnect offers both (conservative) formal models and simulation models, and that the latter enable a trade-off between speed and accuracy.

#### 1.4 Contributions

As the main contributions of this work, we:

- Identify the *requirements for composability and predictability* in multi-application SoCs [65] (this chapter).

- Propose a complete on-chip *interconnect architecture* with local buses, protocol shells, clock bridges, network interfaces (NI), routers and links [69], together with a control infrastructure for run-time reconfiguration [64] (Chapter 3).

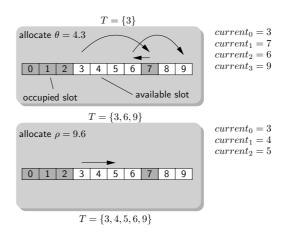

- Provide a *resource allocation algorithm* for composability and predictability [66, 68] across multiple use-cases [63], coupled with sharing of time slots [62] within a use-case (Chapter 4).

- Deliver *run-time libraries for the run-time instantiation* of the resource allocations [64], ensuring correctness and giving temporal bounds on reconfiguration operations (Chapter 5).

- Present *formal models of a network channel*, and show how to use them for buffer sizing [70], and for application-level performance guarantees [71] (Chapter 6).

- Demonstrate the applicability of this work by constructing an example multiprocessor system instance, with a diverse set of applications and computational cores, and map it to an FPGA [65] (Chapter 7).

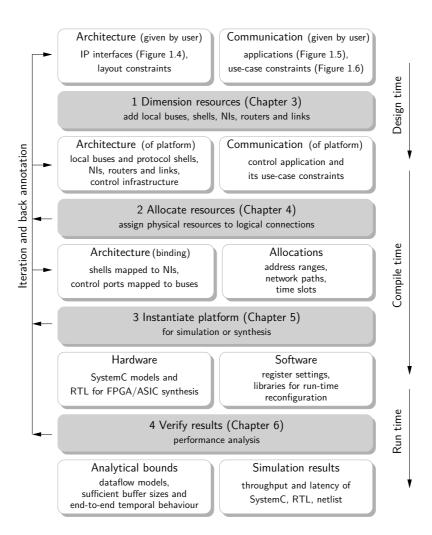

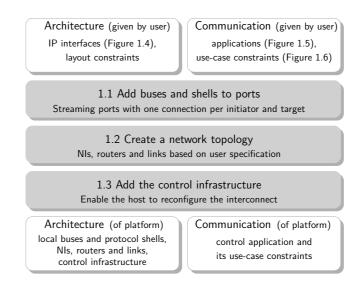

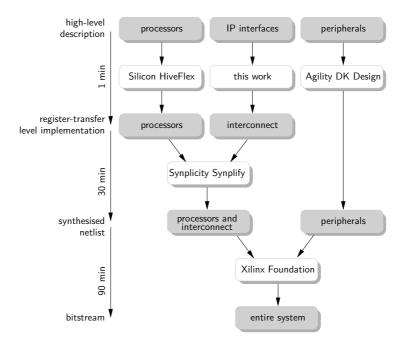

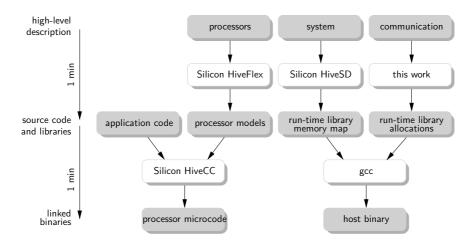

The final contribution of this work is the design flow depicted in Figure 1.8. As shown in the figure, this work takes as its starting point the specification of the physical interfaces that are used by the IPs. The aforementioned architecture description is complemented by the communication requirements of the applications, specified per application as a set of logical interconnections between IP ports, each with bounds on the maximum latency and minimum throughput. The architecture and communication specification also allows the user of the design flow to constrains how the physical IPs are placed and how the applications are combined temporally. These specifications are assumed to be given by the application and system designer, referred to as the user in Figure 1.8. The interface specifications follow directly from the choice of IPs, and the use-case constraints are part of the early system design. It is less obvious, however,

where the requirements on the interconnect stem from. Depending on the application, the desired throughput and latency may be analytically computed, the outcome of high-level simulation models of the application, or simply guesstimates based on back-of-the-envelope calculations or earlier designs. Automation of this step is outside the scope of this work, but we refer to related work that address the issue, and present a number of design examples that illustrate possible approaches.

The outcome of the proposed design flow is a complete SoC interconnect architecture and a set of resource allocations that together implement the requirements specified by the user. The resulting platform is instantiated (in synthesisable HDL or SystemC), together with the software libraries required to configure and orchestrate use-case switches (in Tcl or ANSI C). Verification of the result is performed per application, either by means of simulation or by using conservative models of the interconnect. At this point, it is also important to note that the actual applications, whether run on an FPGA or analytically modelled are evaluated together with the interconnect.

Throughout the design flow, there are many opportunities for successive refinement, as indicated by the iteration in Figure 1.8. Iteration is either a result of failure to deliver on requirements or a result of cost assessment, e.g. silicon area or power consumption. It is also possible that the specification of requirements changes as a result of the final evaluation.

#### 1.5 Organisation

The remainder of this work is organised as follows. We start by introducing the key concepts of the proposed solution in Chapter 2. Thereafter, Chapter 3 begins our bottom-up description of the solution, introducing the design-time dimensioning of the interconnect. This is followed by a discussion on the compile-time allocation of resources in Chapter 4. Chapter 5 shows how the resources and allocations come together in an instantiation at run time. Next, Chapter 6 shows how to capture the interconnect hardware and software in an analysis model, and how it is applied in formal verification of the end-to-end application behaviour. All the ingredients come together in Chapter 7, where a complete example multi-processor system is designed, instantiated and verified. Finally, we review related work in Chapter 8, and end with conclusions and directions for future work in Chapter 9.

Figure 1.8: Design-flow overview.

That is what learning is. You suddenly understand something you've understood all your life, but in a new way.

Doris Lessing, 1919 -

# 2

# **Proposed solution**

In this chapter we give a high-level view of the building blocks of the interconnect and discus the rationale behind their partitioning and functionalities. We start by introducing the blocks by exemplifying their use (Section 2.1). This is followed by a discussion of how the interconnect delivers scalability at the physical and architectural level (Section 2.2). Next, we introduce the protocol stack and show how it enables diversity, both in the application programming models and in the IP interfaces (Section 2.3). We continue by explaining how we provide temporal composability when applications share resources (Section 2.4). Thereafter, we detail how our interconnect enables predictability on the application level by providing dataflow models of individual connections (Section 2.5). Next we show how we implement reconfigurability to enable applications to be independently started and stopped at run time (Section 2.6). Lastly, we describe the rationale behind the central role of automation in our proposed interconnect (Section 2.7), and end this chapter with conclusions (Section 2.8).

#### 2.1 Architecture overview

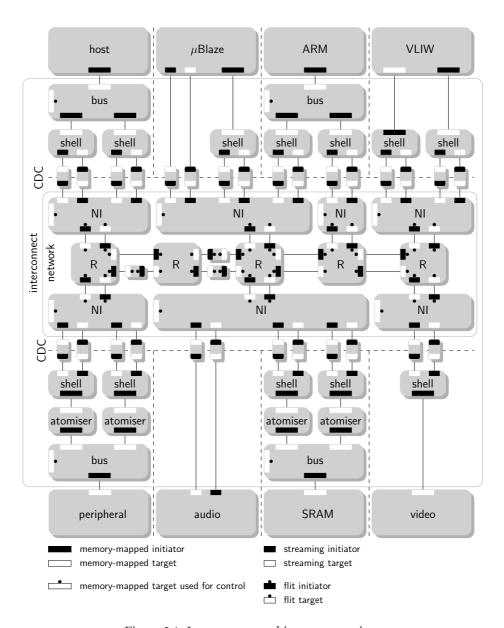

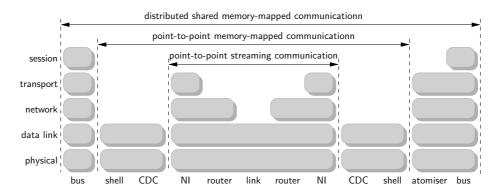

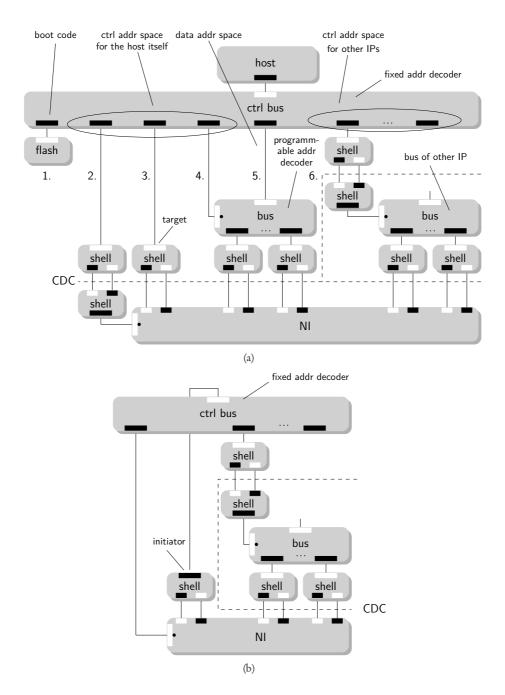

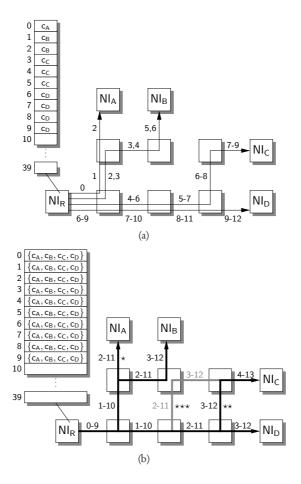

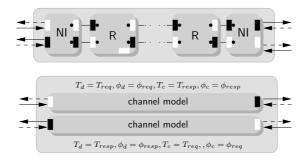

The blocks of the interconnect are all shown in Figure 2.1, which illustrates the same system as Figure 1.4, but now with an expanded view of the interconnect, dimensioned for the applications in Figure 1.5 and use-cases in Figure 1.6.

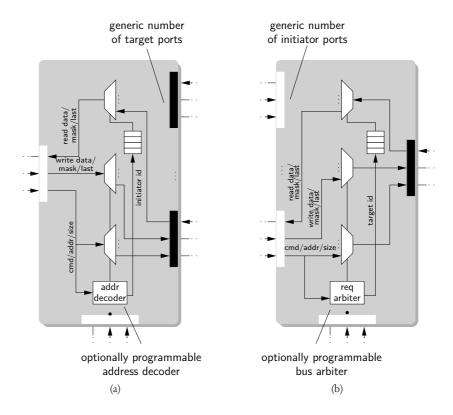

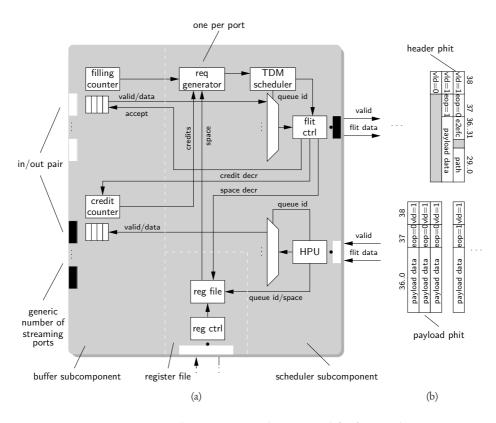

To illustrate the functions of the different blocks, consider a load instruction that is executed on the ARM. The instruction causes a bus transaction, in this case a read transaction, to be initiated on the data port of the processor, i.e. the memory-mapped initiator port. Since the ARM uses distributed memory, a target bus with a reconfigurable address decoder forwards the read request message to the appropriate initiator port of the bus, based on the address. The elements that constitute the request message, e.g. the address and command flags in the case of a read request, are then serialised by a target shell into individual words of streaming data, as elaborated on in Section 2.3. The streaming data is fed via a Clock Domain Crossing (CDC) into the NI input queue corresponding to a specific connection. The data items reside in that input queue until the reconfigurable NI arbiter schedules the connection. The streaming data is packetised

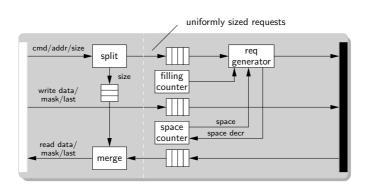

Figure 2.1: Interconnect architecture overview.

and injected into the router network, as flow control digits (flits). Based on a path in the packet header, the flits are forwarded through the router network, possibly also encountering pipeline stages on the links, until they reach their destination NI. In the network, the flits are forwarded without arbitration, as discussed further in Section 2.1.1. Once the flits reach the destination NI, their payload, i.e. the streaming data, is put in the NI output queue of the connection and passes through a clock domain crossing into an initiator shell. The shell represents the ARM as a memory-mapped initiator by reassembling the request message. If the destination target port is not shared by multiple initiators, the shell is directly connected to it, e.g. the video tile in Figure 2.1. For a shared target, the request message passes through an atomiser. By splitting the request, the atomiser ensures that transactions, from the perspective of the shared target, are of a fixed size. As further discussed in Section 2.4, the atomiser also provides buffering to ensure that atomised transaction can complete in their entirety without blocking. Each atomised request message is then forwarded to an *initiator bus* that *arbitrates* between different initiator ports. Once granted, the request message is forwarded to the target, in this case the SRAM, and a response message is generated. The elements that constitute the response message are sent back through the bus. Each atomised response message is buffered in the atomiser that reconstructs the entire response message. After the atomiser, the response message is presented to the initiator shell that issued the corresponding request. The shell adds a message header and serialises the response message into streaming data that is sent back through the network, hereafter denoting the NIs, routers and link pipeline stages. On the other side of the network, the response message is reassembled by the target shell and forwarded to the bus. The target bus implements the transaction ordering corresponding to the IP port protocol. Depending on the protocol, the response message may have to wait until transactions issued by the ARM before this one finish. The bus then forwards the response message to the ARM, completing the read transaction and the load instruction. In addition to response ordering, the target bus also implements mechanisms such as tagging [149] to enable programmers to choose a specific memory-consistency model.

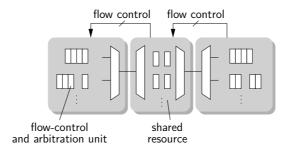

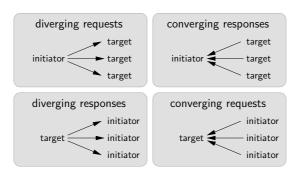

In the proposed interconnect architecture, the applications share the network and possibly also the memory-mapped targets.<sup>1</sup> Arbitration thus takes place in the NIs and the initiator buses. Inside the network, however, *contention-free routing* [154] removes the need for any additional arbitration. We now discus the concepts of contention-free routing in more detail.

#### 2.1.1 Contention-free routing

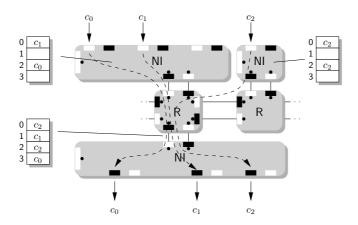

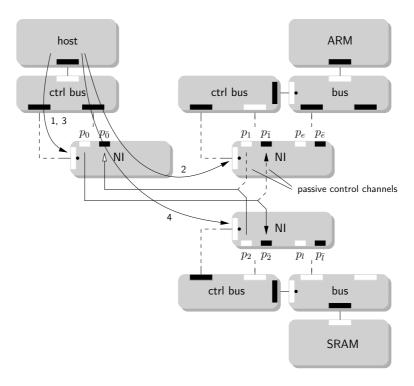

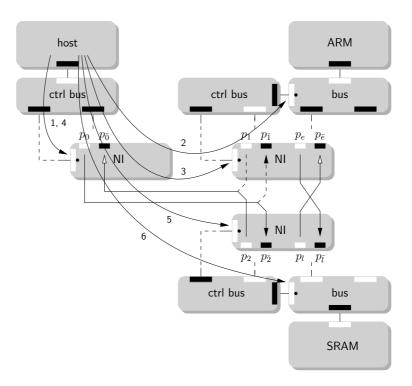

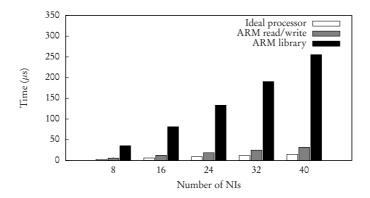

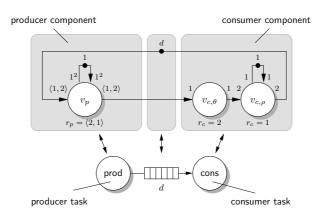

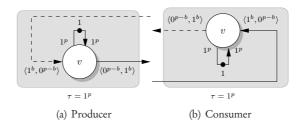

Arbitration in the network is done at the level of flits. The injection of flits is regulated by TDM tables in the NIs such that no two flits ever arrive at the same link at the same time. Network *contention and congestion* is thus avoided. This is illustrated in Figure 2.2, where a small part of the network from our example system is shown.

<sup>&</sup>lt;sup>1</sup>Memory-mapped initiator ports and target buses are not shared in the current instance, and is something we consider future work.

22 **2.2. Scalability**

Figure 2.2: Contention-free routing.

In the figure, we see three *channels*, denoted  $c_0$ ,  $c_1$ , and  $c_2$ , respectively. These three channels correspond to the connections from the streaming port on the  $\mu$ Blaze to the DAC, the request channel from the memory-mapped port on the  $\mu$ Blaze to the SRAM, and the request channel from the ARM to the SRAM. Channels  $c_0$  and  $c_1$  have the same source NI and have slots 2 and 0 reserved, respectively. Channel  $c_2$  originates from a different NI and also has slots 0 and 2 reserved. The TDM table size is the same throughout the network, in this case 4, and every slot corresponds to a flit of fixed size, assumed to be three words throughout this work.

For every hop along the path, the reservation is shifted by one slot, also denoted a *flit cycle*. For example, in Figure 2.2, on the last link before the destination NI,  $c_0$  uses slot 3 (one hop),  $c_1$  slot 1 (one hop), and  $c_2$  slots 0 and 2 (two hops). The notion of a flit cycle is a result of the alignment between the scheduling interval of the NI, the flit size, and the forwarding delay of a router and link pipeline stage. As we shall see in Chapter 4, this alignment is crucial for the resource allocation.

With contention-free routing, the router network behaves as a non-blocking pipelined multi-stage switch, with a global schedule implied by all the slot tables. Arbitration takes place once, at the source NI, and not at the routers. As a result each channel is like an independent FIFO, thus offering composability. Moreover, contention-free routing enables predictability by giving per-channel bounds on latency and throughput. We return to discus composability and predictability in Sections 2.4 and 2.5, respectively. We now discus the consequences on the scalability.

#### 2.2 Scalability

Scalability is required both at the physical and architectural level, i.e. the interconnect must enable both large die sizes, and a large number of IPs. We divide the discussion of our proposed interconnect accordingly, and start by looking at the physical level.

#### 2.2.1 Physical scalability

To enable the IPs to run on independent clocks, i.e. GALS at the level of IPs, the NIs interface with the shells (IPs) through clock domain crossings. We choose to implement the clock domain crossings using bi-synchronous FIFOs. This offers a clearly defined, standardised interface and a simple protocol between synchronous modules, as suggested in [94, 107]. Furthermore, a clock domain crossing based on bi-synchronous FIFOs is robust with regards to metastability, and allows each locally synchronous module's frequency and voltage to be set independently [94]. The rationale behind the placement of the clock domain crossings between the NIs and shells is that all complications involved in bridging between clock domains are placed on a single component, namely the bi-synchronous FIFO. Even though the IPs have their own clock domains (and possibly voltage islands), normal test approaches are applicable as the test equipment can access independent scan chains per synchronous block of the system [94], potentially reusing the functional interconnect as a test access mechanism [183].

In addition to individual clock domains of the IPs, the link pipeline stages enable *mesochronous clocking* inside the network [69]. The entire network thus uses the same clock (frequency), but a phase difference is allowed between neighbouring routers and NIs. Thus, in contrast to a synchronous network, restrictions on the phase differences are relaxed, easing the module placement and the clock distribution. As the constraints on the maximum phase difference are only between neighbours, the clock distribution scales with the network size, as demonstrated in [75]. The rationale behind choosing a mesochronous rather than an asynchronous interconnect implementation is that can be conceived as globally synchronous on the outside [26]. Thereby, the system designer does not need to consider its mesochronous nature. Furthermore, besides the clock domain crossings and link pipeline stages, all other (sub-)components of the interconnect are synchronous and consequently designed, implemented and tested independently.

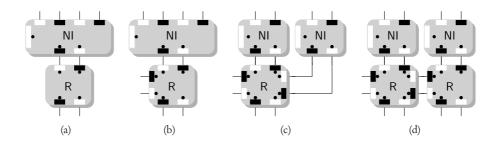

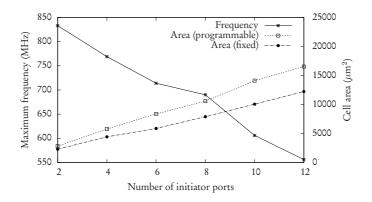

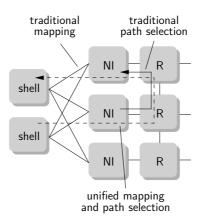

#### 2.2.2 Architectural scalability

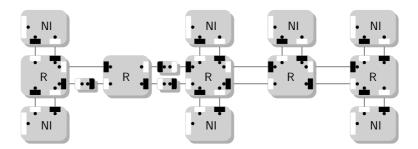

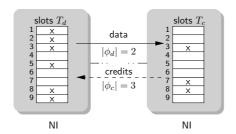

The physical scalability of the interconnect is necessary but not sufficient. The distributed nature of the interconnect enables architectural scalability by avoiding central bottlenecks [19, 39]. More applications and IPs are easily added by expanding the interconnect with more links, routers, NIs, shells and buses. Furthermore, the latency and throughput that can be offered to different applications is a direct result of the amount of contention in the interconnect. In the network, the contention can be made arbitrarily low, and links (router ports), NIs and routers can be added up to the level where each connection has its own resources, as exemplified in Figure 2.3. In Figure 2.3(a), we start with two connections sharing an NI. We then add a two links (router ports) in Figure 2.3(b) (to an already existing router), thus reducing the level of contention. Figure 2.3(c) continues by giving each connection a dedicated NI. Lastly, Figure 2.3(d) distributes the connections across multiple routers, thus reducing the contention to a minimum (but increasing the cost of the interconnect). As we shall see in Section 2.4 the proposed interconnect also contributes to architectural scalability by

24 2.3. Diversity

Figure 2.3: Architecture scaling by adding links (b), NIs (c), and routers (d).

having a router network that does not grow with the number of connections.

Outside the network, the contention for a shared target port, such as an off-chip memory controller, cannot be mitigated by the interconnect as it is inherent in the applications. This problem has to be addressed at the level of the programming model, which we discus in depth in the following section.

#### 2.3 Diversity

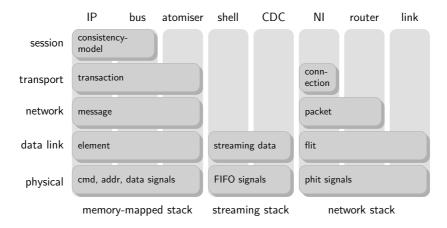

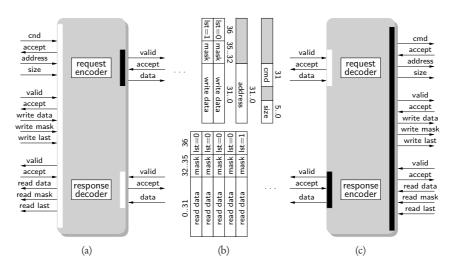

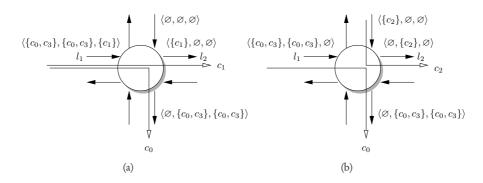

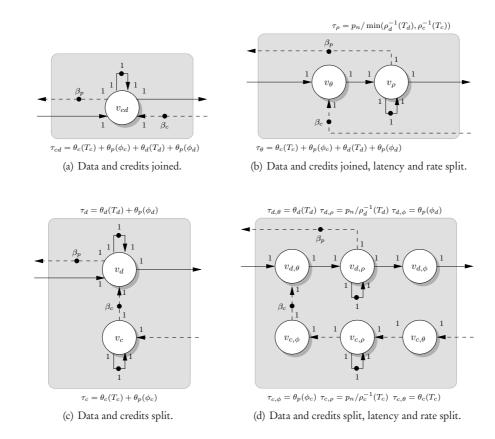

Diversity in interfaces and programming models is addressed by the protocol stack shown in Figure 2.4. The stack is divided into five layers according to the seven-layer Open Systems Interconnection (OSI) reference model [41]. As seen in the figure, the memory-mapped protocol, the streaming protocol and the network protocol each have their own stack, bridged by the shell and the NI. We discus the three stacks in turn.

#### 2.3.1 Network stack

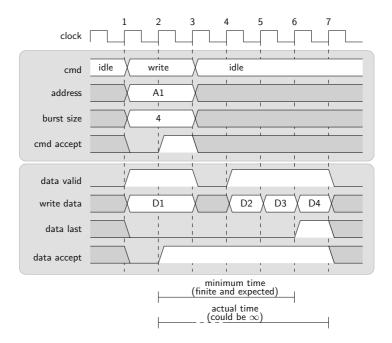

The network stack is similar to what is proposed in [18, 22, 109, 114]. The NI is on the transport level as it maintains end-to-end (from the perspective of the network stack) connections and guarantees ordering within, but not between connections [158]. A connection is a bidirectional point-to-point inter-connection, between two pairs of initiator and target streaming ports on the NIs. Two uni-directional channels, one in each direction, connect the two pairs of ports. Due to the bidirectional nature of a connection, streaming ports always appear in pairs, with one initiator and one target port. As we shall see in Section 2.4, the way in which connections are buffered and arbitrated is central to the ability to provide composable and predictable services in the network, and has a major impact on the NI and router architecture. As seen in Figure 2.4, the router is at the network level and performs switching of packets. The last element of the network, the link pipeline stage, is at the data link level and is responsible for the (synchronous or mesochronous) clock synchronisation and flow control involved in the transport of flits. The physical layer, i.e. timing, bus width, and pulse shape, is governed by the phit (physical digit) format.

Figure 2.4: Interconnect protocol stack.

From the perspective of the IPs, the network behaves as a collection of distributed and independent FIFOs (or virtual wires), with data entering at a streaming target port, and at a later point appearing at a corresponding streaming initiator port (determined by the allocation). Thus, the network stack is completely hidden from the IPs, and only used by means of the streaming stack.

#### 2.3.2 Streaming stack

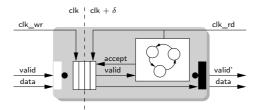

The streaming stack is far simpler than the network stack, and only covers the two lowest layers. The NI, clock domain crossing, shell, and IPs with streaming ports (like the  $\mu$ Blaze in our example system or the video blocks in [174]) all make direct use of this stack. The data-link level governs the flow control of individual words of *streaming data*. The streaming ports make use of a simple FIFO interface with a valid and accept handshake of the data. The physical level concerns the FIFO signal interface. For robustness, the streaming interfaces use *blocking flow control* by means of back pressure. That is, writing to a streaming target port that is not ready to accept data (e.g. due to a full FIFO) or reading from a streaming target port that has no valid data (e.g. due to an empty FIFO) causes a process to stall. We return to discus the blocking flow control and its implications in Section 2.4.

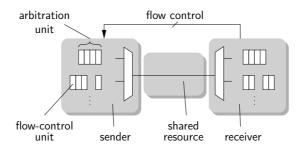

As illustrated in Figure 2.5, the NI bridges between the streaming stack and network stack by establishing connections between streaming ports and embedding streaming data in network packets. The connections are thus, via the streaming stack, offering bi-directional point-to-point streaming communication, without any interpretation or assumptions on the time or value of the individual words of streaming data. Moreover, with FIFO ordering inside a network channel, it is up to the users of the network, e.g. IPs and buses to implement a specific inter-channel ordering. Both the aforementioned properties are key in enabling diversity in communication paradigms and program-

26 **2.3. Diversity**

Figure 2.5: Bridging the protocol stacks.

ming models, as described next.

The most basic use of the streaming stack is exemplified in Figure 2.1 by the  $\mu$ Blaze that communicates with the audio directly via the streaming ports of the NI. One connection is sufficient to interconnect the two blocks, with one channel carrying data from the ADC to the  $\mu$ Blaze, and the other channel from the  $\mu$ Blaze to the DAC. Only raw data is communicated across both channels that are completely homogeneous [65].

## 2.3.3 Memory-mapped stack

In contrast to the simple FIFO interface of the streaming ports, memory-mapped protocols are based on a request-response transaction model and typically have interfaces with dedicated groups of wires for command, address, write data, and read data [3, 5, 6, 137, 149, 199]. Many protocols also support features like byte enables and burst transactions (single request multiple data elements). The block that bridges between the memory-mapped ports of the IPs and the streaming ports of the NIs is a shell, that (independently) serialises the memory-mapped request and response messages. As illustrated in Figure 2.5, the shells enable point-to-point memory-mapped communication by bridging between the elements of a bus-protocol message, e.g. the address, command flags or individual words of write data, and words of streaming data by implementing the data link protocol of both the bus stack and the streaming stack. As already mentioned, the network places no assumptions on the time and value of individual words of streaming data, and also not on the size, syntax, semantics or synchronisation granularity of messages. Consequently, the shells enable streaming communication and memory-mapped communication to co-exist in the interconnect. Moreover, different pairs of memory-mapped initiators and targets may communicate using different protocols, thus enabling multiple memory-mapped protocols.

The shells work on the granularity of a single memory-mapped initiator or target port. However, a memory-mapped initiator port often uses distributed memory [157], and accesses multiple targets, based on e.g. the address, the type of transaction (e.g.

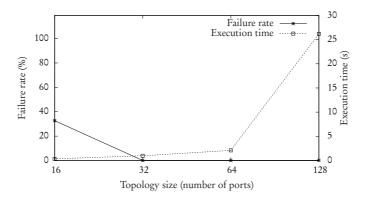

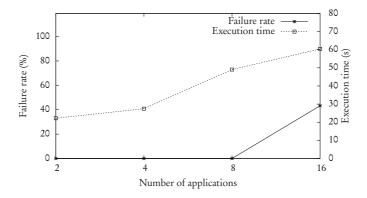

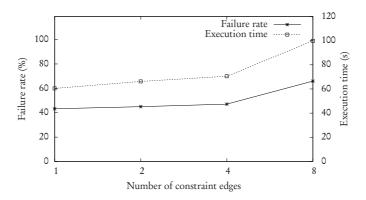

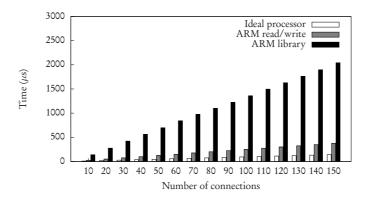

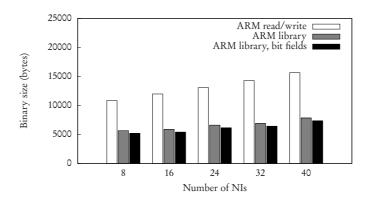

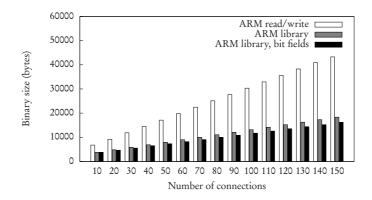

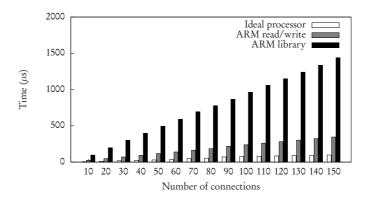

read or write) or dedicated identifier signals in the port interface [137]. The use of distributed memory is demonstrated by the host and ARM in Figure 2.1. As the ARM accesses more than one target port, the outgoing requests have to be directed to the appropriate target, and the incoming responses *ordered* and presented to the initiator according to the protocol. In addition to the use of distributed memory at the initiator ports, memory-mapped target ports are often shared by multiple initiators, as illustrated by the SRAM in Figure 2.1. A shared target must hence be *arbitrated*, and the initiators' transactions multiplexed according to the protocol of the target port. Next, we show how distributed and shared memory-mapped communication, as shown in Figure 2.5, is enabled by the target buses and initiator buses, respectively.