# SiFive Freedom SoCs: Industry's First Open-Source RISC-V Chips

$\diamond$

ŝ

ψ

S

Yunsup Lee Co-Founder and CTO

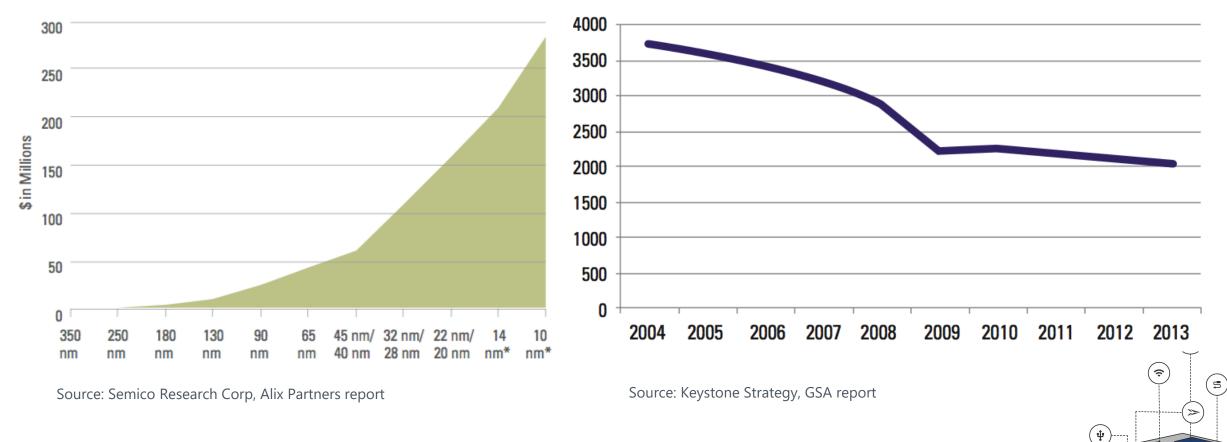

### High Upfront Cost Has Killed Innovation

Our industry needs a fundamental change

Total SoC Development Cost

# DesignShare

Proposing new, industry-wide movement to bring innovation back

- Make IP available at free/reduced upfront cost

- Open-source AND Proprietary IP

- Lower upfront fee in exchange for \$\$ later (e.g., mass production milestone, royalties)

- Enable quick, easy, predictable access to silicon utilizing DesignShare IP

- Create new companies who innovate without having to invest in full design and IP negotiation teams

- Just like how the foundry model created an entirely new class of fabless semiconductor companies who didn't have to invest in a fab

#### **Democratize Access. Share the Risk, Share the Rewards**

ŝ

( 5)

RISC-V

RISC-V is a high-quality, license-free, royalty-free ISA

- 5<sup>th</sup> Generation RISC design from UC Berkeley (started in 2010)

- Experiencing rapid uptake in both industry and academia

- Standard maintained by non-profit RISC-V Foundation

- Multiple proprietary and open-source core implementations

- Supported by growing software ecosystem

- binutils/gcc/FreeBSD mainlined, Linux/glibc submitted to upstream

- Appropriate for all levels of computing system, from microcontrollers to supercomputers

s

#### It's Not Just RISC-V

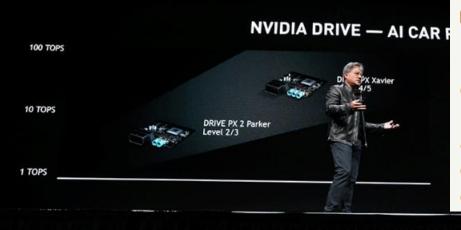

#### NVIDIA Open Sources their Deep Learning Accelerator (DLA)

#### 5/10/2017

It's so incredibly hard to put it together, why don't we accelerate the adoption, democratize deep learning for the trillions of devices that will use deep learning, Jensen says.

So, we're open sourcing the Xavier DLA. The best engineers in the world are working on this. We're going to take this, which some people call the TPU and we're going to open source it. Early access in July. Full access in September, "Our goal is proliferation," Jensen says.

#### 8/10/2017

#### BARRON'S

Huang was enthusiastic about Nvidia's decision to give technology to the **open-source** effort:

We designed a deep learning accelerator, the "DLA," and it's probably the best anyone has ever designed, and we open-sourced it. RISC V is an open source company, and they asked us if we might work with them to put our DLA into it, and so we are going to give it to the community. How it benefits Nvidia is that the more people who receive deep learning computing, the more demand there will be for deep learning. And two, the DLA is supported by our Tensor RT, and so that's how we extend the reach of our platform

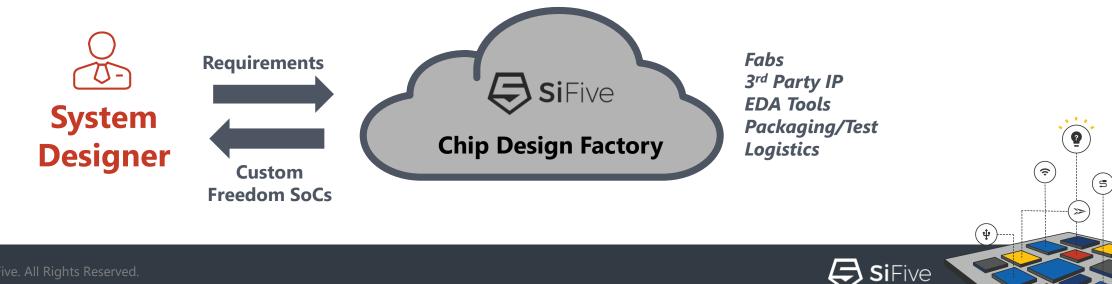

Founded by the inventors of RISC-V

- We contribute to the open-source Freedom SoC platform based on RISC-V

- We build customized Freedom SoCs quickly, easily, predictably at low upfront cost

### SiFive Products: RISC-V SoCs and RISC-V IPs

Tailored RISC-V Solutions for both Chip and System Designers

| SiFive Freedom SoCs                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                         | SiFive Coreplex IP                                                                                                                                                                                        |                                                                                                                                                                                                           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <section-header><section-header><section-header><section-header><section-header><list-item><list-item><list-item><list-item></list-item></list-item></list-item></list-item></section-header></section-header></section-header></section-header></section-header> | <section-header><section-header><section-header><section-header><list-item><list-item><list-item><list-item><list-item></list-item></list-item></list-item></list-item></list-item></section-header></section-header></section-header></section-header> | <section-header><section-header><section-header><section-header><list-item><list-item><list-item></list-item></list-item></list-item></section-header></section-header></section-header></section-header> | <section-header><section-header><section-header><section-header><list-item><list-item><list-item></list-item></list-item></list-item></section-header></section-header></section-header></section-header> |  |

|                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                         |                                                                                                                                                                                                           | (\psi)                                                                                                                                                                                                    |  |

s

# **Freedom Everywhere SoCs**

Low power, 32-bit microcontrollers

? Ŷ 5 >ψ

.

::

### Freedom E310

- First RISC-V based SoC based on the Freedom Everywhere SoC platform

- Target markets: IoT, Wearables, Embedded

- Low-power, low-cost, high-performance

- Open-source software and tools support

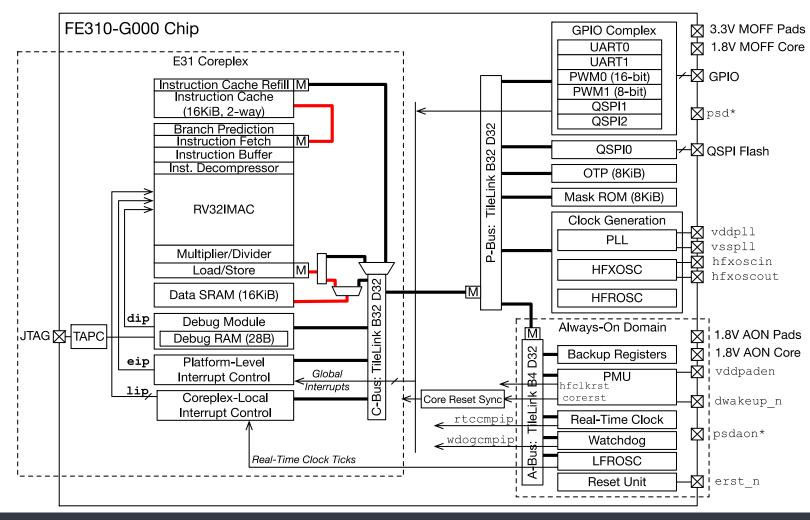

# Freedom E310 Chip Block Diagram

First RISC-V SoC based on the Freedom Everywhere SoC platform

- 320+ MHz SiFive E31 CPU

- 1.61 DMIPS/MHz

- 16KB L1 I\$

- 16KB Data Scratchpad

- Hardware Multiply/Divide

- Debug Module

- Multiple Power Domains

- Low Power Standby

- Wide Range of Clock Inputs

- TSMC180G

- 6mmx6mm 48-Pin QFN

?

(5)

`ج)

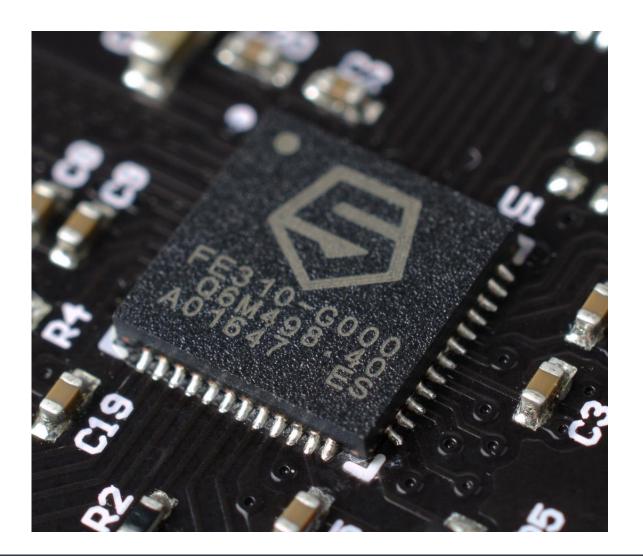

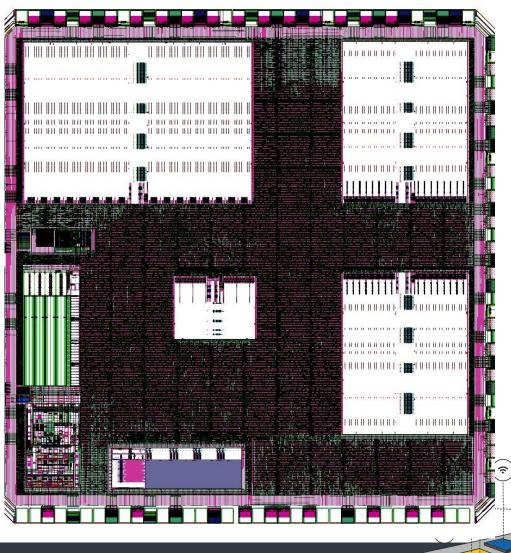

#### Freedom E310 Chip

#### ~6mm<sup>2</sup> in TSMC 180nm

SiFive

**`**@`

(5)

### Freedom E310 Perf/Power Comparison

| Microcontroller    | CPU Core       | CPU ISA            | CPU Speed                   | DMIPS/MHz | Total<br>Dhrystones | DMIPS/mW* |

|--------------------|----------------|--------------------|-----------------------------|-----------|---------------------|-----------|

| Intel Curie Module | Intel Quark SE | x86                | 32 MHz                      | 1.3       | 41.6                | 0.35*     |

| ATSAMD21G18        | ARM Cortex M0+ | ARMv6-M            | 48 MHz                      | 0.93      | 44.6                |           |

| Nordic NRF51       | ARM Cortex M0  | ARMv6-M            | 16 MHz                      | 0.93      | 14.9                | 1.88*     |

| Freedom E310       | SiFive E31     | RISC-V<br>RV32IMAC | 200 MHz<br>320 MHz<br>(max) | 1.61      | 320.4               | 3.16*     |

\*All Power Comparisons are in same 180nm Process Technology

**Si**Five

ŝ

໌ 🖻

- 10x Faster Clock than Intel's Arduino 101 uController

- 11x More Dhrystones than ARM's Arduino Zero (ATSAMD21G18)

- 9x More Power Efficient than Intel Quark

- 2x More Power Efficient than ARM Cortex M0+

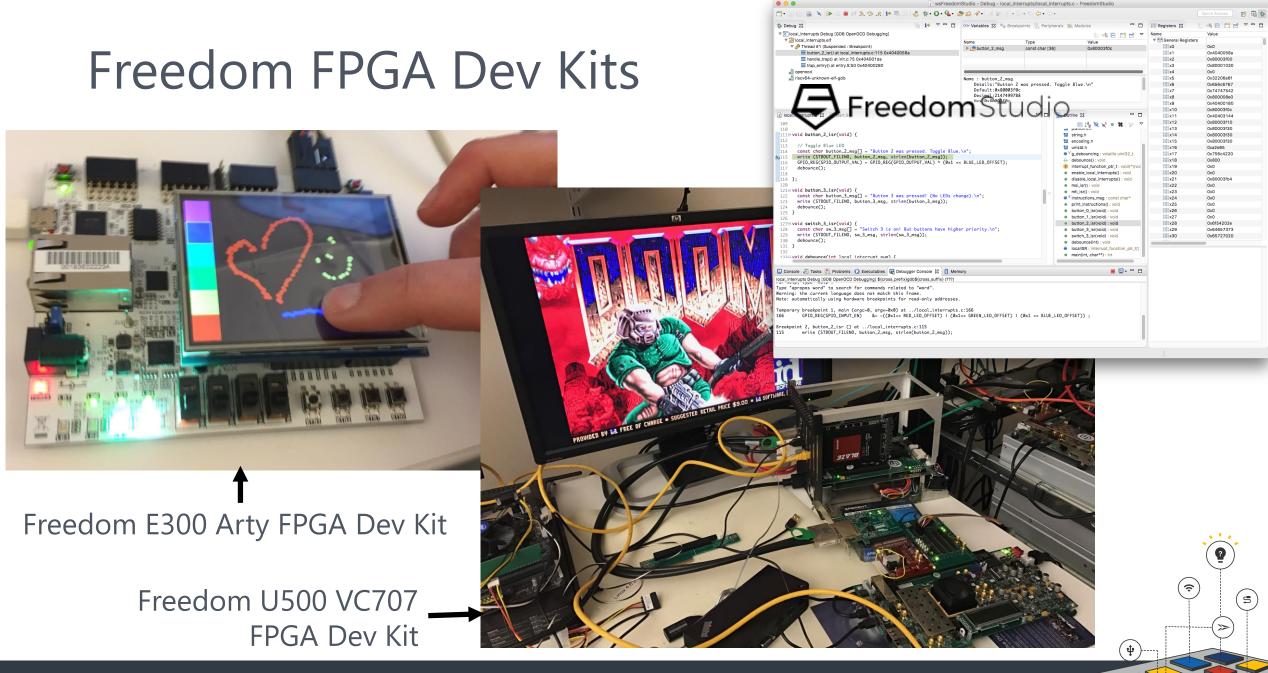

# HiFive1: Arduino-Compatible RISC-V Dev Kit

Powered by the Freedom E310 chip

\$59, https://www.crowdsupply.com/sifive/hifive1

- Operating Voltage: 3.3 V and 1.8 V

- Input Voltage: 5 V USB or 7-12 VDC Jack

- **IO Voltages:** Both 3.3 V or 5 V supported

- Digital I/O Pins: 19

- **PWM Pins:** 9

- SPI Controllers/HW CS Pins: 1/3

- External Interrupt Pins: 19

- External Wakeup Pins: 1

- **Flash Memory:** 128 Mbit Off-Chip (ISSI SPI Flash)

- Host Interface (microUSB): Program, Debug, and Serial Communication

(3)

# **Freedom Unleashed SoCs**

64-bit multi-core SoCs for embedded computing

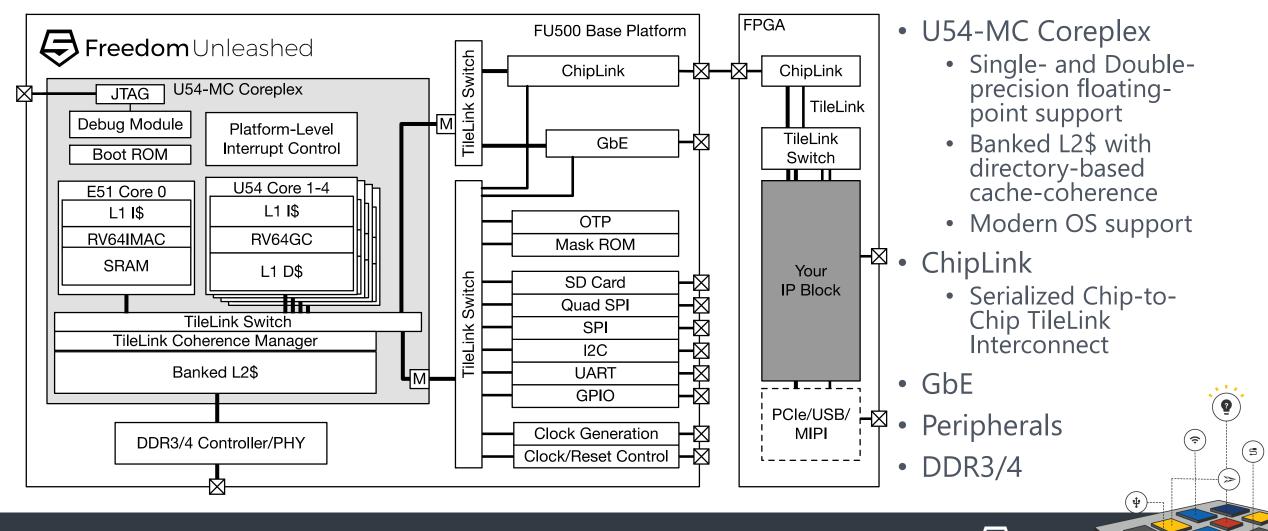

# Freedom U500 Base Platform Block Diagram

TSMC 28nm Chip for Rapid Customization of the Freedom Unleashed Platform

**Si**Five

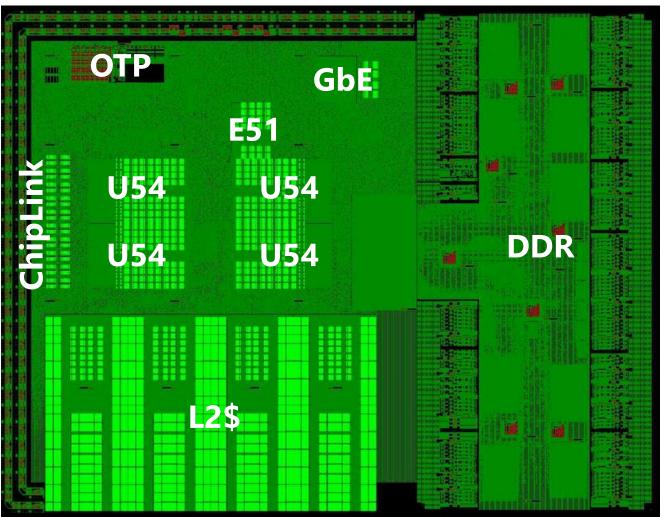

# Freedom U500 Base Platform Chip

- ~30mm<sup>2</sup> in TSMC 28nm

- 250M transistors

- 1.5 GHz+ SiFive E51/U54 CPU

- 1x E51: 16KB L1I\$ and 8KB DTIM

- 4x U54: 32KB L1I\$ and 32KB L1D\$

- ECC support

- Banked 2MB L2\$

- ECC support

- TSMC 28HPC

- FCBGA package

- Development board available Q1 2018

(s)

# **Open-Source Freedom SoCs**

### We Open-Sourced the Freedom Platform!

Including the RTL, FPGA Scripts, BSPs, Tools, Documentation, and Schematics

- RISC-V CPU (Rocket)

- TileLink, a free and open coherent SoC interconnect

- Low-speed Peripherals: SPI, UART, PWM, GPIO, PMU

- High-speed Xilinx FPGA Peripheral Wrappers: DDR, PCIe blocks

- Certain 3<sup>rd</sup>-party IPs such as pads, PLL, OTP, and ROM are not open-sourced

- Checkout <u>https://dev.sifive.com</u>, <u>https://github.com/sifive</u>, and <u>https://github.com/freechipsproject</u>

ŝ

(=)

# Why Open-Source the Freedom Platform?

Look at how open-source software changed the world

- Open-source platform allows for more innovation, promotes reuse, and attracts developers

- Developers and IP providers can focus on their value-added innovation

5

- Enables both open-source developers and for-profit IP companies

- Leverage the collective effort of the community and industry

- System designers can easily customize their chip and software with full view of the system

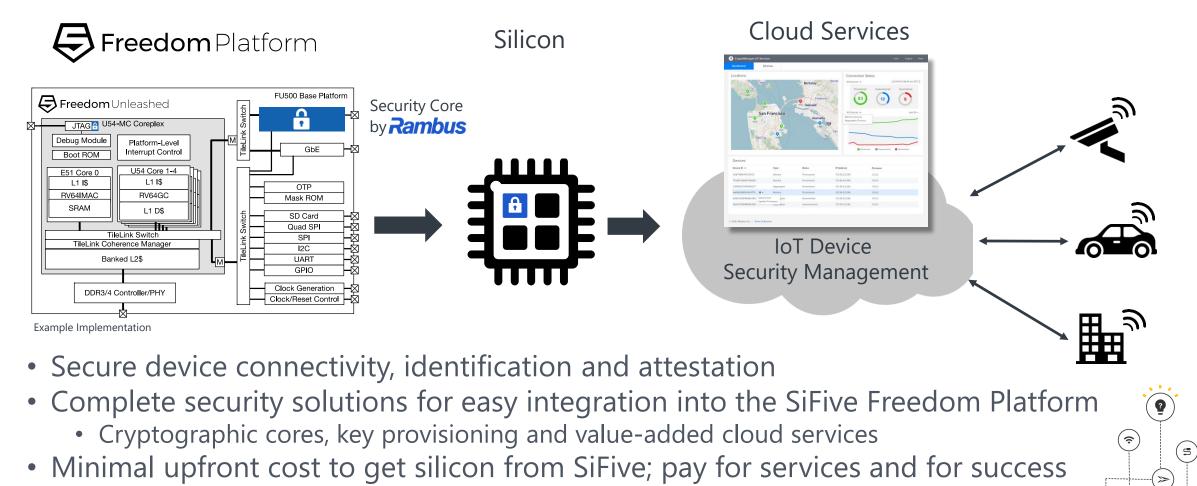

## SiFive & Rambus: A Shared Vision

Partnering for end-to-end security solutions

(‡)

**Si**Five

Rambus

#### Join the DesignShare Revolution!

- For IP designers, who have great technology

- Work with us to bring your technology to the Freedom SoC platform

- We will find new customers and markets together

- For system designers

- You can afford a custom chip from SiFive

- Start customizing the SiFive Freedom SoC platform

- Innovate at both the hardware and software level

- Let's lower the upfront cost and increase design starts together

ŝ

ີ ສີ

Start today at https://sifive.com