Microcontrollers

#### CAN

| Revision History: Previous Version: |            | 2004-02                                                               | V 1.0 |

|-------------------------------------|------------|-----------------------------------------------------------------------|-------|

|                                     |            | -                                                                     |       |

| Page                                | Subjects ( | major changes since last revision)                                    |       |

| All                                 |            | ayout to Infineon Corporate Design, updated release to 1.0, nchanged! |       |

|                                     |            |                                                                       |       |

|                                     |            |                                                                       |       |

|                                     |            |                                                                       |       |

Controller Area Network (CAN): License of Robert Bosch GmbH

### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

## **Table of Contents**

| Table of Contents                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 1                                                                                                                                                                     | Abbreviations and Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2                                         |

| 2                                                                                                                                                                     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2                                         |

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.2<br>3.3.2.1<br>3.3.2.2<br>3.3.3<br>3.3.3.1<br>3.3.3.2<br>3.3.3.3<br>3.4<br>3.5<br>3.6<br>3.6.1<br>3.6.2 | The Controller Area Network (CAN)  CAN Basics  Addressing and Bus Arbitration  The different CAN Frames and their Formats  Data Frame  Standard CAN Data Frame  Extended CAN Data Frame  Remote Frame  Standard CAN Remote Frame  Extended CAN Remote Frame  Extended CAN Remote Frame  Error Frames, Overload Frame, Interframe Space  Error Frames  Overload Frame  Interframe Space  The Nominal Bit Time  Error Detection and Error Handling  Different CAN Implementations  Standard CAN, Extended CAN  Basic CAN, Full CAN | 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |

| 4<br>4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                        | The Infineon CAN Devices C167CR, C515C and SAE 81C90/91 The Microcontroller Families C500 and C166 at a Glance The CAN Module on the C167CR / C515C The Functional Blocks of the CAN Module Control Registers of the CAN Controller The Message Objects Initialization of the CAN Controller SAE 81C90/91 Important Features of the SAE 81C90/91 Functional blocks of the SAE 81C90/91 The most important Control Registers of the SAE 81C90/91 Initialization of the SAE 81C90/91 and Bus Access                                | 2<br>2<br>2<br>2<br>2                     |

| 5<br>5.1<br>5.2                                                                                                                                                       | Examples for the Connection of Infineon Microcontrollers to CAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2                                         |

## **Table of Contents**

| 5.3   | Connecting the C511 / C513 to CAN using the serial interface of the SAE 81C <u>91</u> | . 2 |

|-------|---------------------------------------------------------------------------------------|-----|

| 5.4   | A proposal for the CAN Bus Cables                                                     | . 2 |

| 6     | Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR C515C              |     |

| 6.1   | Notes on the following Sections                                                       | . 2 |

| 6.2   | Accessing the Registers of the CAN Module and the SAE 81C90/91                        | . 2 |

| 6.3   | Configuration of the Bit Timing                                                       | . 2 |

| 6.4   | Ways of Handling the CAN Module                                                       | . 2 |

| 6.4.1 | The Initialization of the CAN Module on the C167CR / C515C                            | . 2 |

| 6.4.2 | The Transmission of a Data Frame with the CAN Module                                  | . 2 |

| 6.4.3 | The Transmission of a Remote Frame with the CAN Module                                | . 2 |

| 6.4.4 | Evaluation of a received Message with the CAN Module                                  | . 2 |

| 6.5   | Ways of Handling the SAE 81C90/91                                                     | . 2 |

| 6.5.1 | The Initialization of the SAE 81C90/91                                                | . 2 |

| 6.5.2 | The Transmission of a Data Frame / Remote Frame with the                              |     |

|       | SAE 81C90/91                                                                          | . 2 |

| 6.5.3 | Evaluation of a received Message with the SAE 81C90/91                                | . 2 |

| 6.6   | How to use the Basic CAN Features of the CAN Module and the SAE                       |     |

|       | 81C90/91                                                                              | . 2 |

| 6.6.1 | The Basic-CAN Feature of the CAN Module                                               | . 2 |

| 6.6.2 | The Monitor Mode of the SAE 81C90/91                                                  | . 2 |

|       |                                                                                       |     |

### **Abbreviations and Symbols**

## 1 Abbreviations and Symbols

The following abbreviations and symbols are used throughout this application note:

ABUS "Allgemeine Bitserielle Universelle Schnittstelle" (VW protocol)

BL1, BL2 Bit timing registers of the SAE 81C90/91

BRP Baudrate Prescaler

BSP Bit Stream Processor

BTL Bit Timing Logic

CAN Controller Area Network (Bosch)

CAN H, CAN L Names of the CAN bus lines

CCE Bit in the Control Register of the CAN module

CiA CAN in Automation (CAN User Group)

CIL CPU Interface Logic

CPU Central Processing Unit

CRC Cyclic Redundancy Check

CSMA/CD Carrier Sense Multiple Access / Collision Detection

CTRL Control Register of the SAE 81C90/91

EML Error Management Logic

IC Integrated Circuit

IM Bit in the MOD Register of the SAE 81C90/91

INIT Bit in the Control Register of the CAN module

INT Interrupt Register of the SAE 81C90/91

J1850 Protocol from Chrysler, GM, Ford

MOD Status- and Control Register of the SAE 81C90/91

NDA Non-Destructive Arbitration

NRZ Non-Return-to-Zero

PEC Peripheral Event Controller

PLCC Plastic Leaded Chip Carrier

PWM Pulse Width Modulation

RAM Random Access Memory

REC Receive Error Counter

RES Bit in the MOD Register of the SAE 81C90/91

ROM Read Only Memory

RTR Remote Transmission Request Rx0, Rx1 Receive Inputs of the SAE 81C90/91

SJW Synchronisation Jump Width

TCEC Transmit Check Error Counter

TCL Transceiver Control Logic

TEC Transmit Error Counter

TSEG1, TSEG2 Segments of the CAN bit cell

Tx0, Tx1 Transmit Outputs of the SAE 81C90/91

## **Abbreviations and Symbols**

USART Universal Synchronous/Asynchronous Receiver/Transmitter

VAN Vehicle Area Network (Peugeot, Renault)

XBUS Chip-internal bus on the C167CR

This application note describes the CAN¹ Protocol, Infineon CAN devices and different options for connecting devices of the Infineon C166 and C500 microcontroller families to the Controller Area Network (CAN). It replaces the German application note "CAN-Anschluß für die Mikrocontrollerfamilien C166 and C500".

After the introduction (Section 1), Section 2 introduces the reader to the Controller Area Network (CAN). Section 3 describes the Infineon CAN devices, the 16-bit microcontroller C167CR, the 8-bit microcontroller C515C, and the Stand-Alone Full-CAN Controller SAE 81C90/91. Section 4 gives hardware examples for connection of Infineon microcontrollers to CAN. Finally, in Section 5, ways of handling the SAE 81C90/91 and the CAN module on the C167CR and the C515C are given.

Whilst every effort has been made to ensure the accuracy of information contained in this application note, the authors cannot be held responsible for any consequences arising from its use.

Application Note 6 V 1.0, 2004-02

<sup>&</sup>lt;sup>1</sup> Controller Area Network (CAN): License of Robert Bosch GmbH

Introduction

## 2 Introduction

Ever increasing quantities of electronic devices are fitted to modern motor vehicles. Examples of such devices include engine management systems, active suspension, ABS, gear control, lighting control, air conditioning, airbags and central locking. All this means more safety and more comfort for the driver and of course a reduction of fuel consumption and exhaust emissions. To improve the behaviour of the vehicle even further, it is necessary for the different control systems (and their sensors) to exchange information. At present, this is usually done by discrete interconnection of the different systems (i.e. point to point wiring). The requirement for information exchange has now grown to such an extent that a cable network with a length of up to several kilometers and many connectors is required. This produces growing problems concerning material cost, production time and reliability.

The solution to this problem is the connection of the control systems via a serial bus system. This bus has to fulfill some special requirements due to its usage in a vehicle:

#### **Data Rate**

Much of the data that is exchanged by the control systems (or by sensors) has to be processed in real time which requires very fast transmission. Data items may differ in transmission priority (e.g. Airbag data is likely to be high priority, Air Conditioning data is likely to be low priority). For very high priority data the latency period between the transmission request and the actual start of the transmission is very important and must be minimized. The serial bus therefore must provide very fast transmission, short message length and bus access prioritisation.

### **Data Integrity**

The bus must have a high resistance to Electromagnetic Interference. Erroneous messages must be detected and repeated. To ensure valid data across the sytem, every bus node has to be informed about an error. Bus communication must not be disturbed if one (or more) bus nodes malfunction. Faulty nodes must withdraw from bus communication on their own. The bus must therefore have a linear structure with equal bus nodes (multimaster concept).

## **Data Sharing**

All control systems needing a common data item should be able to simultaneously receive this data item from the bus (e.g. vehicle speed might be used by the engine management system, active suspension ABS and gear control) The bus must therefore have multicast capability.

#### Introduction

Several different serial bus systems have been developed for the use in motor vehicles, each of them trying, as far as possible, to fulfill the above requirements. Examples are ABUS from Volkswagen, VAN (Vehicle Area Network) developed by Peugeot and Renault, the J1850 protocol from Chrysler, General Motors and Ford and, of course, the Controller Area Network (CAN) from Robert Bosch GmbH in Germany. These protocols mostly differ in transfer rate, signal coding, message format, error detection, and error handling.

The CAN protocol was defined by Bosch in the mid-eighties. For some time Infineon have also offered CAN devices such as the stand-alone Full-CAN controller SAE 81C90/91 and the C167CR and the C515C microcontrollers (high-end 16-bit or 8-bit microcontrollers respectively with an on-chip CAN module).

CAN has now clearly established a market leading position and indeed a number of vehicle manufacturers have abandoned their proprietry protocols and have chosen the CAN protocol. More than 15 Million CAN nodes are in use worldwide.

The Controller Area Network (CAN)

## 3 The Controller Area Network (CAN)

#### 3.1 CAN Basics

CAN is an asynchronous serial bus system with one logical bus line. It has an open, linear bus structure with equal bus nodes. A CAN bus consists of two or more nodes. The number of nodes on the bus may be changed dynamically without disturbing the communication of other nodes. This allows easy connection and disconnection of bus nodes (e.g. for addition of system function, error recovery or bus monitoring).

The bus logic corresponds to a "wired-AND" mechanism, "recessive" bits (mostly, but not necessarily equivalent to the logic level "1") are overwritten by "dominant" bits (logic level mostly "0"). As long as no bus node is sending a dominant bit, the bus line is in the recessive state, but a dominant bit from any bus node generates the dominant bus state. Therefore, for the CAN bus line, a medium must be chosen that is able to transmit the two possible bit states (dominant and recessive). One of the most common and cheapest ways is to use a twisted wire pair. The bus lines are then called "CAN H" and "CAN L" and may be connected directly to the nodes or via a connector. There's no standard defined by CAN regarding the connector to be used. The twisted wire pair is terminated by terminating resistors at each end of the bus line. The maximum bus speed is 1 MBaud, which can be achieved with a bus length of up to 40 m. For bus lengths longer than 40 m the bus speed must be reduced (a 1000 m bus can be realised with a 40 KBaud bus speed). For a bus length above 1000 m special drivers should be used. At least 30 nodes may be connected without additional equipment. Due to the differential nature of transmission CAN is insensitive to EMI. because both bus lines are affected in the same way which leaves the differential signal unaffected. The bus lines can also be shielded to reduce the electromagnetic emission of the bus itself, especially at high baudrates.

The binary data is coded corresponding to the NRZ code (Non-Return-to-Zero; low level = dominant state; high level = recessive state). To ensure exact synchronization of all bus nodes bit stuffing is used. This means that during the transmission of a message a maximum of five consecutive bits may have the same polarity. Whenever five consecutive bits of the same polarity have been transmitted the transmitter will insert one additional bit of the opposite polarity into the bit stream before transmitting further bits. The receiver also checks the number of bits with the same polarity and removes the stuff bits from the bit stream (= destuffing).

The Controller Area Network (CAN)

## 3.2 Addressing and Bus Arbitration

In the CAN protocol it is not bus nodes that are addressed, but the address information is contained in the messages that are transmitted. This is done via an identifier (part of each message) which identifies the message content (e.g. engine speed, oil temperature etc.) The identifier additionally indicates the priority of the message. The lower the binary value of the identifier the higher is the priority of the message.

For bus arbitration, CSMA/CD with NDA is used (Carrier Sense Multiple Access / Collision Detection with Non-Destructive Arbitration). If bus node A wants to transmit a message across the network, it at first checks that the bus is in the idle state ("Carrier Sense") i.e. no node is currently transmitting. If this is the case (and no other node wishes to start a transmission at the same moment) node A becomes the bus master and sends its message. All other nodes switch to receive mode during the first transmitted bit (Start Of Frame bit). After correct reception of the message (which is acknowledged by each node) each bus node checks the message identifier and stores the message, if required. Otherwise, the message is discarded.

If two or more bus nodes start their transmission at the same time ("Multiple Access"), collision of the messages is avoided by bitwise arbitration ("Collision Detection / Non-Destructive Arbitration" together with the "Wired-AND" mechanism, "dominant" bits override "recessive" bits). Each node sends the bits of its message identifier (MSB first) and monitors the bus level. A node that sends a recessive identifier bit but reads back a dominant one loses bus arbitration and switches to receive mode. This condition occurs when the message identifier of a competing node has a lower binary value (dominant state = logic 0) and therefore the competing node is sending a message with a higher priority. In this way, the bus node with the highest priority message wins arbitration without losing time by having to repeat the message. All other nodes automatically try to repeat their transmission once the bus returns to the idle state. It is not permitted for different nodes to send messages with the same identifier as arbitration could fail leading to collisions and errors.

The original CAN specifications (Versions 1.0, 1.2 and 2.0A) defined the message identifier as having a length of 11 bits giving a possible 2048 message identifiers. The specification has since been updated (to version 2.0B) to remove this possible limitation. CAN specification Version 2.0B allows message identifier lengths of 11 and/or 29 bits to be used (an identifier length of 29 bits allows over 536 Million message identifiers). Version 2.0B CAN is often referred to as "Extended CAN", the versions below (1.0, 1.2 and 2.0A) being referred to as "Standard CAN" (see section 2.6.1 for further details).

The Controller Area Network (CAN)

## 3.3 The different CAN Frames and their Formats

#### 3.3.1 Data Frame

#### 3.3.1.1 Standard CAN Data Frame

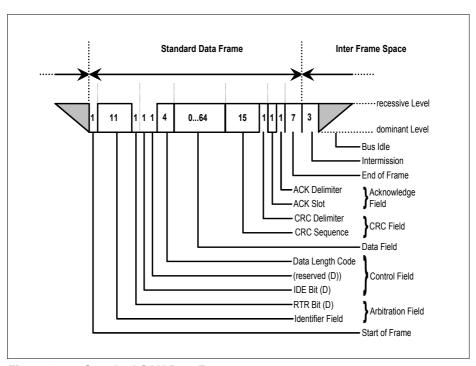

Figure 1 Standard CAN Data Frame

A "Data Frame" is generated by a node when the node wishes to transmit data. The Standard CAN Data Frame is shown in figure 1. In common with all other frames, the frame begins with a Start Of Frame bit (SOF = dominant state) for hard synchronization of all nodes.

## The Controller Area Network (CAN)

The SOF is followed by the Arbitration Field consisting of 12 bits, the 11-bit Identifier (reflecting the contents and priority of the message) and the RTR bit (Remote Transmission Request bit). The RTR bit is used to distinguish a Data Frame (RTR = dominant) from a Remote Frame (see section 2.3.2).

The next field is the Control Field, consisting of 6 bits. The first bit of this field is called the IDE bit (Identifier Extension) and is at dominant state to specify that the frame is a Standard Frame. The following bit is reserved and defined as a dominant bit. The remaining 4 bits of the Control Field are the Data Length Code (DLC) and specify the number of bytes of data contained in the message (0 - 8 bytes).

The data being sent follows in the Data Field which is of the length defined by the DLC above (0, 8, 16, ...., 56 or 64 bits).

The Cyclic Redundancy Field (CRC) follows and is used to detect possible transmission errors. The CRC Field consists of a 15 bit CRC sequence, completed by the recessive CRC Delimiter bit.

The final field is the Acknowledge Field. During the ACK Slot bit the transmitting node sends out a recessive bit. Any node that has received an error free frame acknowledges the correct reception of the frame by sending back a dominant bit (regardless of whether the node is configured to accept that specific message or not). From this it can be seen that CAN belongs to the "in-bit-response" group of protocols. The recessive Acknowledge Delimiter completes the Acknowledge Slot and may not be overwritten by a dominant bit.

Seven recessive bits (End of Frame) end the Data Frame. Between any two frames the bus must remain in the recessive state for at least a further 3 bit times (called Intermission). If, following the frame, no nodes wish to transmit then the bus stays in the recessive state (Bus Idle).

The Controller Area Network (CAN)

#### 3.3.1.2 Extended CAN Data Frame

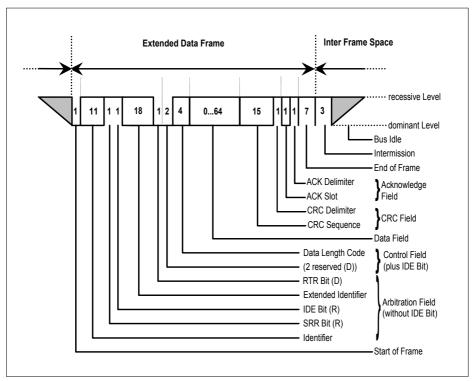

Figure 2 Extended CAN Data Frame

The Extended CAN Data Frame is shown in figure 2.

It should be noted above, that to enable standard and extended frames to be sent across a shared network it is necessary to split the 29 bit extended message identifier into 11bit (most significant) and 18 bit (least significant) sections. This split ensures that the Identifier Extension bit (IDE) can remain at the same bit position in both standard and extended frames (see below).

## The Controller Area Network (CAN)

In the Extended CAN Data Frame the Start Of Frame bit (SOF) is followed by the Arbitration Field consisting of 32 bits. The first 11 bits are the 11 most significant bits of the 29-bit Identifier ("Base-ID"). These 11 bits are followed by the Substitute Remote Request bit (SRR) which is transmitted as recessive. The SRR is followed by the IDE bit which is recessive to denote that the frame is an Extended CAN frame. It should be noted from this, that if arbitration remains unresolved after transmission of the first 11 bits of the identifier, and one of the nodes involved in arbitration is sending a Standard CAN frame (11 bit identifier), then the Standard CAN frame will win arbitration due to the assertion of a dominant IDE bit. Further to this the SRR bit in an Extended CAN frame must be recessive to allow the assertion of a dominant RTR bit by a node that is sending a Standard CAN Remote Frame (see section 2.3.2.1). The SRR and IDE bits are followed by the remaining 18 bits of the identifier ("ID-Extension") and the Remote Transmission Request bit (again RTR = dominant for a Data Frame).

The next field is the Control Field, consisting of 6 bits. The first 2 bits of this field are reserved and are at dominant state. The remaining 4 bits of the Control Field are the Data Length Code (DLC) and specify the number of data bytes (as for the Standard Data Frame).

The remaining portion of the frame (Data Field, CRC Field, Acknowledge Field, End Of Frame and Intermission) is constructed in the same way as for a Standard Data Frame.

#### 3.3.2 Remote Frame

#### 3.3.2.1 Standard CAN Remote Frame

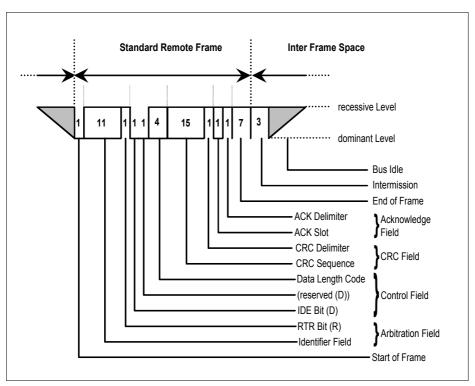

Normally data transmission is performed on an autonomous basis with the data source node (e.g. a sensor) sending out a Data Frame. It is also possible, however, for a destination node (or nodes) to request the data from the source. For this purpose the destination node sends a "Remote Frame" with an identifier that matches the identifier of the required Data Frame. The appropriate data source node will then send a Data Frame as a response to this remote request.

There are 2 differences between a Remote Frame and a Data Frame. Firstly the RTR-bit is at the recessive state and secondly there is no Data Field. In the very unlikely event of a Data Frame and a Remote Frame with the same identifier being transmitted at the same time, the Data Frame wins arbitration due to the dominant RTR bit following the identifier. In this way, the node that transmitted the Remote Frame receives the desired data immediately.

The format of a Standard Remote Frame is shown in figure 3 below.

## The Controller Area Network (CAN)

Figure 3 Standard CAN Remote Frame

### 3.3.2.2 Extended CAN Remote Frame

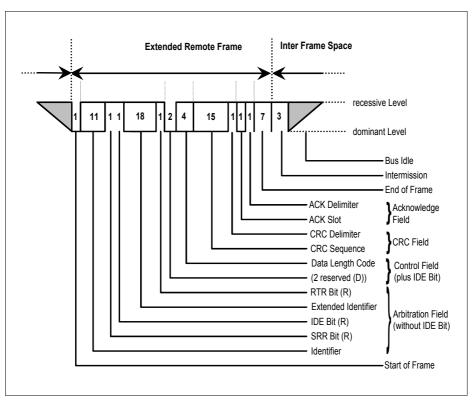

The format of an Extended CAN Remote Frame is shown in figure 4 below.

### The Controller Area Network (CAN)

Figure 4 Extended CAN Remote Frame

## 3.3.3 Error Frames, Overload Frame, Interframe Space

#### 3.3.3.1 Error Frames

An Error Frame is generated by any node that detects a bus error. An error frame consists of 2 fields, an Error Flag field followed by an Error Delimiter field. The Error Delimiter consists of 8 recessive bits and allows the bus nodes to restart bus communications cleanly after an error. There are, however, two forms of Error Flag fields. The form of the Error Flag field depends on the "error status" of the node that detects the error (see section 2.5 for details of "error status").

## The Controller Area Network (CAN)

If an "error-active" node detects a bus error then the node interrupts transmission of the current message by generating an "active error flag". The "active error flag" is composed of six consecutive dominant bits. This bit sequence actively violates the bit stuffing rule. All other stations recognize the resulting bit stuffing error and in turn generate Error Frames themselves. The Error Flag field therefore consists of between six and twelve consecutive dominant bits (generated by one or more nodes). The Error Delimiter field completes the Error Frame. After completion of the Error Frame bus activity returns to normal and the interrupted node attempts to resend the aborted message.

if an "error passive" node detects a bus error then the node transmits an "error passive flag" followed, again, by the Error Delimiter field. The "error passive flag" consists of six consequtive recessive bits, and therefore the Error Frame (for an "error passive" node) consists of 14 recessive bits (i.e. no dominant bits). From this it follows that, unless the bus error is detected by the node that is actually transmitting (i.e. is the bus master), the transmission of an Error Frame by an "error passive" node will not affect any other node on the network. If the bus master node generates an "error passive flag" then this may cause other nodes to generate error frames due to the resulting bit stuffing violation. After transmission of an Error Frame an "error passive" node must wait for 6 consecutive recessive bits on the bus before attempting to rejoin bus communications.

#### 3.3.3.2 Overload Frame

An Overload Frame has the same format as an "active" Error Frame (i.e. that generated by an "error active" node). An Overload Frame, however can only be generated during Interframe Space. This is the way then an Overload Frame can be differentiated from an Error Frame (an Error Frame is sent during the transmission of a message). The Overload Frame consists of 2 fields, an Overload Flag followed by an Overload Delimiter. The Overload Flag consists of six dominant bits followed by Overload Flags generated by other nodes (as for "active error flag", again giving a maximum of twelve dominant bits). The Overload Delimiter consists of eight recessive bits. An *Overload Frame* can be generated by a node as a result of 2 conditions, a) if the node detects a dominant bit during Interframe Space (illegal see section 2.5), or b) if due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential Overload Frames to delay the start of the next message.

The Controller Area Network (CAN)

## 3.3.3.3 Interframe Space

Interframe Space separates a preceeding frame (of whatever type) from a following Data or Remote Frame. Interframe space is composed of at least 3 recessive bits, these bits are termed the Intermission. This time is provided to allow nodes time for internal processing before the start of the next message frame. After the Intermission, the bus line remains in the recessive state (Bus Idle) until the next transmission starts.

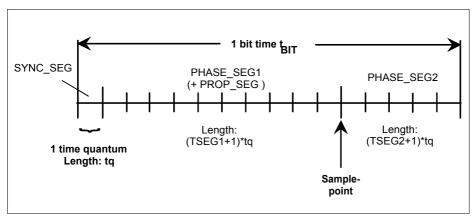

### 3.4 The Nominal Bit Time

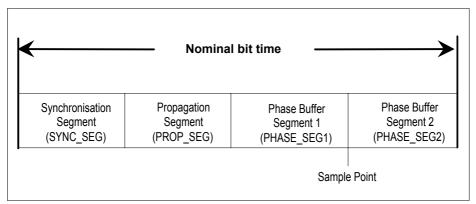

One bit cell (i.e. one high or low pulse of the NRZ code) is constructed from four segments. Each segment is in turn constructed from an integer multiple of Time Quanta. The Time Quantum is the smallest discrete timing resolution used by a CAN node. A bit time, and therefore by definition also the bit rate, is selected by programming the Bit Timing Logic (BTL) to select the width of the Time Quanta and the number of Time Quanta in the various segments. The nominal bit time with its segments (according to CAN Spec ISO11898, 1993) is shown in figure 5.

Figure 5 Partition of bit time

The SYNC\_SEG (Synchronisation Segment) is used to synchronise the various bus nodes. If there is a bit state change between the previous bit and the current bit then the bus state change is expected to occur within this segment. The length of this segment is always 1 Time Quantum (1 BTL cycle).

### The Controller Area Network (CAN)

The PROP\_SEG (Propagation Segment) is used to compensate for signal delays across the network. These delays are caused by signal propagation delay on the bus line and through the electronic interface circuits of the bus nodes. PROP\_SEG may be 1, 2, 3, ..., 8 or more Time Quanta long. For many CAN module implementations the PROP\_SEG and PHASE\_SEG1 segments are combined for ease of programming.

The PHASE\_SEG1 and PHASE\_SEG2 segments are used to compensate for edge phase errors. These segments may be lengthened or shortened by resynchronization. PHASE\_SEG1 may be 1, 2, 3, ..., 8 or more Time Quanta long. PHASE\_SEG2 is the maximum of PHASE\_SEG1 and the information processing time, which is the time segment starting with the sample point reserved for calculation of the subsequent bit level and is less than or equal to two Time Quanta long. The sample point is the point of time at which the bus level is read and interpreted as the value of that respective bit. Its location is at the end of PHASE\_SEG1.

The total number of Time Quanta in a bit time must be between 8 and 25.

As a result of resynchronization, PHASE\_SEG1 may be lengthened or PHASE\_SEG2 may be shortened. The amount of lengthening or shortening the phase buffer segments has an upper limit given by the resynchronization jump width. The resynchronization jump width may be between 1 and 4 Time Quanta, but it may not be longer than PHASE\_SEG1.

## 3.5 Error Detection and Error Handling

The CAN protocol provides sophisticated error detection mechanisms. The following errors can be detected:

## Cyclic Redundancy Check (CRC) Error

With the Cyclic Redundancy Check the transmitter calculates special check bits for the bit sequence from the start of a frame until the end of the Data Field. This CRC sequence is transmitted in the CRC Field. The receiving node also calculates the CRC sequence using the same formula and performs a comparison to the received sequence. If a mismatch is detected, a CRC error has occured and an Error Frame is generated. The message is repeated.

### Acknowledge Error

In the Acknowledge Field of a message the transmitter checks if the Acknowledge Slot (which it has sent out as a recessive bit) contains a dominant bit. If not, no other node has received the frame correctly, an Acknowledge Error has occured and the message has to be repeated. No Error Frame is generated, though.

The Controller Area Network (CAN)

#### Form Error

If a transmitter detects a dominant bit in one of the four segments End of Frame, Interframe Space, Acknowledge Delimiter or CRC Delimiter then a Form Error has occured and an Error Frame is generated. The message is repeated.

#### Bit Error

A Bit Error occurs if a) a transmitter sends a dominant bit and detects a recessive bit or b) if it sends a recessive bit and detects a dominant bit when monitoring the actual bus level and comparing it to the just transmitted bit. In case b) no error occurs during the Arbitration Field and the Acknowledge Slot.

#### Stuff Error

If between Start of Frame and CRC Delimiter 6 consecutive bits with the same polarity are detected, the bit stuffing rule has been violated. A stuff error occurs and an Error Frame is generated. The message is repeated.

Detected errors are made public to all other nodes via Error Frames. The transmission of the erroneous message is aborted and the frame is repeated as soon as possible. Furthermore, each CAN node is in one of the three error states "error active", "error passive" oder "bus off" according to the value of the internal error counters. The error-active state is the usual state where the bus node can transmit messages and active Error Frames (made of dominant bits) without any restrictions. In the error-passive state, messages and passive Error Frames (made of recessive bits) may be transmitted. The bus-off state makes it temporarily impossible for the station to participate in the bus communication. During this state, messages can neither be received nor transmitted.

## 3.6 Different CAN Implementations

## 3.6.1 Standard CAN, Extended CAN

Those Data Frames and Remote Frames, which only contain the 11-bit identifier, are called Standard Frames according to CAN specification V2.0 part A. With these frames, 2<sup>11</sup> (=2048) different messages can be identified (identifiers 0-2047). However, the 16 messages with the lowest priority (2032-2047) are reserved. Extended Frames according to CAN specification V2.0 part B own a 29-bit identifier. As already mentioned, this 29-bit identifier is made up of the 11-bit identifier ("Base ID") and the 18-bit Extended Identifier ("ID Extension"). So 2<sup>29</sup> different identifiers are possible.

## The Controller Area Network (CAN)

CAN modules specified after CAN V2.0 part A are only able to transmit and receive Standard Frames according to the Standard CAN protocol. Messages using the 29-bit identifier cause errors. If a device is specified after CAN V2.0 part B, there's one more distinction. Modules named "Part B Passive" can transmit and receive Standard Frames but tolerate Extended Frames without generating Error Frames. "Part B Active" devices are able to transmit and receive both Standard and Extended Frames.

### 3.6.2 Basic CAN, Full CAN

There is one more CAN characteristic concerning the interface between the CAN module and the host CPU, dividing CAN chips into "Basic CAN" and "Full CAN" devices. This has nothing to do with the used protocol though (Standard or Extended CAN), which makes it possible to use both Basic and Full CAN devices in the same network.

In the Basic CAN devices, only basic functions of the protocol are implemented in hardware, e.g. the generation and the check of the bit steam. The decision, if a received message has to be stored or not (acceptance filtering) and the whole message management has to be done by software, i.e. by the host CPU. Mostly the CAN chip also only provides one transmit buffer and one or two receive buffers. So the host CPU load is quite high using Basic CAN modules, therefore these devices should only be used at low baudrates and low bus loads with only a few different messages. The advantages of Basic CAN are the small chip size leading to low costs of these devices.

Full CAN devices do the whole bus protocol in hardware including the acceptance filtering and the message management. They contain several so called message objects which handle the identifier, the data, the direction (receive or transmit) and the information Standard CAN / Extended CAN. During the initialisation of the device, the host CPU defines which messages are to be sent and which are to be received. The host CPU is informed by interrupt if the identifier of a received message matches with one of the programmed (receive-) message objects. In this way, the CPU load is strongly reduced. Using Full CAN devices, high baudrates and high bus loads with many messages can be handled. These chips are more expensive than the Basic CAN devices, though.

Many Full CAN chips provide a "Basic-CAN-Feature": One of their message objects can be programmed in a way that every message is stored there that does not match with one of the other message objects. This can be very helpful in a number of applications.

The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

# 4 The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

#### 4.1 The Microcontroller Families C500 and C166 at a Glance

The history of the 8-bit microcontrollers from Infineon is founded on 8051-compatible derivatives like the SAB 80C515 or the SAB 80C517. The improvement of these controllers lead to the C500 family whose C500 core is still fully compatible to the old 8051 core but provides more performance and a more flexible design methodology for further integration. An actual high-performance member of the C500 family is the C515C. It is based on the well-known SAB 80C515A, but has some additional features like an SPI-compatible, synchronous serial interface (SSC) and a CAN module which will be described in detail in section 3.2.

To meet the requirements of today's and future embedded control applications Infineon developed the SAB 80C166 in 1990 being the first member of the 16-bit microcontroller family C166. The controllers own a registerbank-oriented CPU with a four-stage pipeline being able to process most of the instructions in just one machine cycle of 80 ns @ 25 MHz CPU clock. The freely programmable interrupt system has response times of typically 400 ns and can handle a large number of independent internal and external interrupt sources at 16 priority levels. The family members SAB 80C166, C167, C165 and C163 are equipped with a well-balanced mix of modular, autonomous peripherals like a 10-bit ADC with up to 16 channels, Capture/Compare units, serial interfaces, a PWM unit, complex timer units and also a CAN module. The implemented XBUS makes it easy to extend the standard derivatives by further application specific peripheral functions. The controllers contain up to 4 Kbytes internal RAM and up to 128 Kbytes ROM or Flash-EPROM, respectively. The whole C166 architecture is made for fast instruction execution and minimum response time to external events. This combination, however, provides highest real-time performance.

### 4.2 The CAN Module on the C167CR / C515C

### 4.2.1 The Functional Blocks of the CAN Module

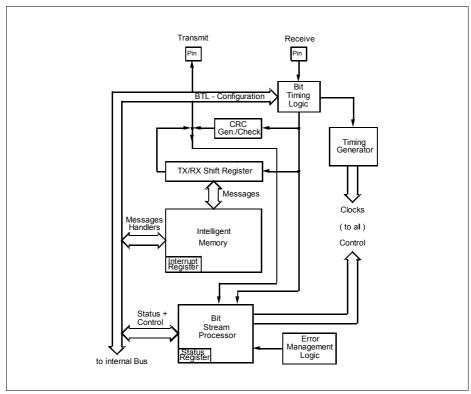

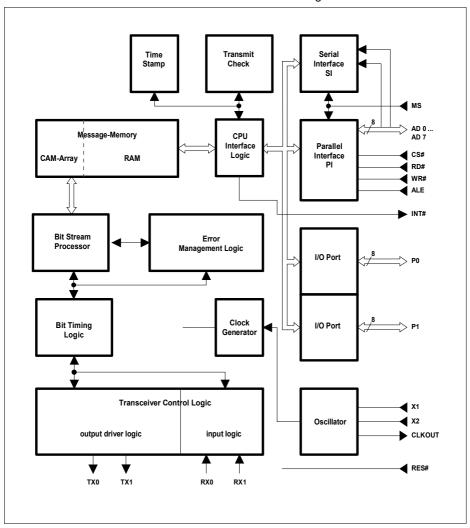

The CAN modules on the C167CR and the C515C are fully compatible concerning the CAN functionality. There are only differences in the interface to the CPU, the module clock generation, the internal registers (8 bit wide on the C515C, 16-bit wide on the C167CR), and the interrupt functionality. A block diagram of the CAN module is shown in figure 3.2-1 (connected to the C167CR here).

Application Note 22 V 1.0, 2004-02

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

Figure 6 Block Diagram of the CAN module (connected to the C167CR here)

The CAN module is made of two major blocks. One of them represents the interface to the CPU.

In the C167CR, the CAN module is connected to the bus controller (and therefore to the CPU) via the XBUS. From a user's point of view, this XBUS can be regarded as an internal representation of the external bus. Connecting the CAN module to the XBUS in 16-bit demultiplexed bus mode offers the fastest possible accesses. All registers of the CAN module are organized as 16-bit registers, located on word addresses. However, all registers may be accessed bytewise in order to select special actions without affecting other mechanisms. These registers reside in a special CAN address area of 256 bytes, which is mapped into segment 0 and uses addresses EF00h through EFFFh.

In the C515C, the CAN module is connected to the internal bus. Again, the registers are mapped into a special address area of 256 bytes using addresses F700h through F7FFh. The registers can be accessed with MOVX-instructions. An access to this special memory space requires the modification of the XPAGE register to the value F7h. Furthermore, the bits XMAP0 and XMAP1 in the SYSCON register must be set to "0".

Application Note 23 V 1.0, 2004-02

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

The second block of the CAN module on the C167CR and the C515C is the CAN controller itself, which is derived from the stand-alone component AN 82527. The CAN controller provides all resources that are required to run the Standard CAN protocol (11-bit identifiers) as well as the Extended CAN protocol (29-bit identifiers). It provides a sophisticated object layer to relieve the CPU of as much overhead as possible when controlling many different message objects (up to 15). This includes bus arbitration, resending of garbled messages, error handling, interrupt generation, etc. In order to implement the physical layer, external CAN transceiver components have to be connected to the C167CR / C515C.

The CAN controller combines several functional blocks (see figure 3.2-2) that work in parallel and contribute to the controller's performance. These units and the functions they provide are described below.

- The *Transmit / Receive Shift Register* holds the destuffed bit stream from the bus line to allow the parallel access to the whole data or Remote Frame for the acceptance match test and the parallel transfer of the frame to and from the Intelligent Memory.

- The *Bit Stream Processor (BSP)* is a sequencer controlling the sequential data stream between the Tx/Rx Shift Register, the CRC Register, and the bus line. The BSP also controls the Error Management Logic (EML) and the parallel data stream between the Tx/Rx Shift Register and the Intelligent Memory such that the processes of reception, arbitration, transmission, and error signalling are performed according to the CAN protocol. Note that the automatic retransmission of messages which have been corrupted by noise or other external error conditions on the bus line is handled by the BSP.

- The Cyclic Redundancy Check Register generates the Cyclic Redundancy Check (CRC) code to be transmitted after the data bytes and checks the CRC code of incoming messages. This is done by dividing the data stream by the code generator polynomial.

- The Error Management Logic (EML) is responsible for the fault confinement of the CAN device. Its counters, the Receive Error Counter and the Transmit Error Counter, are incremented and decremented by commands from the Bit Stream Processor. According to the values of the error counters, the CAN controller is set into the states error active, error passive or busoff.

- The CAN controller is *error active*, if both error counters are below the *error passive* limit of 128. It is *error passive*, if at least one of the error counters equals or exceeds 128. It goes *busoff*, if the Transmit Error Counter equals or exceeds the *busoff* limit of 256. The device remains in this state, until the *busoff* recovery sequence is finished. Additionally, there is the bit EWRN in the Status Register, which is set, if at least one of the error counters equals or exceeds the error warning limit of 96. EWRN is reset if both error counters are less than the error warning limit.

Application Note 24 V 1.0, 2004-02

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

- The Bit Timing Logic (BTL) monitors the busline input CAN\_RxD and handles the busline related bit timing according to the CAN protocol. The BTL synchronises on a recessive to dominant busline transition at Start of Frame (hard synchronisation) and on any further recessive to dominant busline transition, if the CAN controller itself does not transmit a dominant bit (resynchronisation). The BTL also provides programmable time segments to compensate for the propagation delay time and for phase shifts and to define the position of the Sample Point in the bit time. The programming of the BTL depends on the baudrate and on external physical delay times.

- The Intelligent Memory (CAM/RAM Array) provides storage for up to 15 message objects of maximum 8 data bytes length. Each of these objects has a unique identifier and its own set of control and status bits. After the initial configuration, the Intelligent Memory can handle the reception and transmission of data without further CPU actions.

Figure 7 Block Diagram of the CAN Controller on the C167CR / C515C

Application Note 25 V 1.0, 2004-02

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

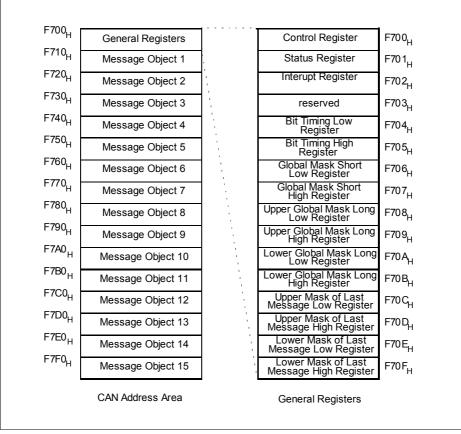

## 4.2.2 Control Registers of the CAN Controller

All registers reside in the already mentioned 256-byte wide CAN address areas (shown in figure 8) together with the message objects. The most important registers are now described.

The *Control Register* and the *Status Register* contain important status- and control bits e.g. used for initialisation and interrupt control. The cause for a pending interrupt can be read from the *Interrupt-Register*. In the *Bit-Timing-Register*, the desired baudrate on the CAN bus and the length of the time segments described in section 2.4 are defined.

Figure 8 CAN addressing area on the C515C

Application Note 26 V 1.0, 2004-02

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

Figure 9 CAN addressing area on the C167CR

There are three mask registers in the CAN controller, called "Global Mask Short", "Global Mask Long" and "Mask of Last Message". Incoming frames are masked with their appropriate global mask. Therefore incoming Standard Frames are masked with the standard 11-bit mask in Global Mask Short, while incoming Extended Frames are masked with the extended 29-bit identifier in Global Mask Long. A bit in the mask registers holding a "0" means "don't care", i.e. the respective bit position of the message's identifier is not relevant during the acceptance filtering. In this way a message object accepts not only one specific message but all messages only differing in the previously masked bits. The last message object (MO 15) is used for the "Basic CAN" feature.

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

It has an additional individually programmable acceptance mask for the complete Arbitration Field called Mask of Last Message which is ANDed with the global mask that corresponds to the incoming message. This allows classes of messages to be especially received in this message object by masking some (or all) bits of the identifier.

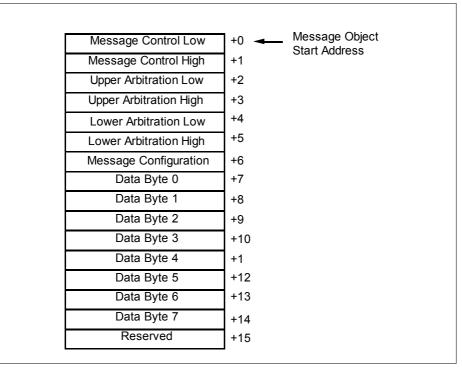

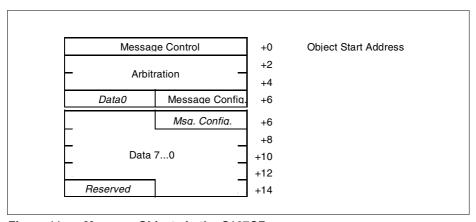

## 4.2.3 The Message Objects

The CAN controller provides storage for up to 15 message objects of maximum 8 bytes data length. Each of these objects has a unique identifier and its own set of control and status bits (see figure 3.2-4a and 3.2-4b). Each object can be configured with its direction as either transmit or receive, except the last message which is only a receive buffer with a special mask register.

An object with its direction set as transmit can be configured to be automatically sent whenever a Remote Frame with a matching identifier (taking into account the respective global mask register) is received over the CAN bus. By requesting the transmission of a message with the direction set as receive, a Remote Frame can be sent to request that the appropriate object be sent by some other node. Each object has separate transmit and receive interrupts and status bits, allowing the CPU full flexibility in detecting when a Remote/Data Frame has been sent or received.

For general purpose two masks for acceptance filtering can be programmed, one for identifiers of 11 bits and one for identifiers of 29 bits. However the CPU must configure bit XTD (Normal or Extended Frame Identifier) for each valid message to determine whether a standard or extended frame will be accepted.

The last message object has its own programmable mask for acceptance filtering, allowing a large number of infrequent objects to be handled by the system.

Application Note 28 V 1.0, 2004-02

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

Figure 10 Message Objects in the C515C

Figure 11 Message Objects in the C167CR

Application Note 29 V 1.0, 2004-02

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

#### 4.2.4 Initialization of the CAN Controller

To initialize the CAN controller, two bits in the control register (INIT and CCE) have to be set first. Then the register concerning the bit timing and the global mask registers must be configured. Afterwards each message object is to be initialized or is to be declared as not valid if it is not needed. The procedure is finished when bits INIT and CCE in the control register are reset. Now the CAN controller synchronizes to the data transfer on the CAN bus by waiting for 11 consecutive recessive bits. Finally it can participate in the CAN bus communication. Please also read section 5.4.1 for more information about the initialization of this device.

Further information about the CAN module can be found in section 5 or in the Infineon literature "Description of the On-Chip CAN-Module" and the manuals of the C167CR and the C515C.

#### 4.3 The Stand-Alone Full-CAN Controller SAE 81C90/91

## 4.3.1 Important Features of the SAE 81C90/91

The CAN controllers SAE 81C90 (P-LCC-44-package, with two 8-bit I/O-Ports, and SAE 81C91 (P-LCC-28-package; without I/O-Ports) can be operated with up to 20 MHz. They support the CAN spezification V2.0A (B passive), i.e. the controllers can handle messages with the 11-bit standard identifier. Frames with the 29-bit extended identifier are not stored, but tolerated. Via a flexible, programmable interface the connection to different implementations of the physical layer (ISO/OSI layer 1) is possible. The connection to the host controller can be set up either in parallel via a multiplexed 8-bit address-/ data bus compatible to Infineon 8- and 16-bit microcontrollers or via a fast synchronous serial interface (up to 5 MBit/s). With the 8 bit wide registers all functions of the device are controlled from the host CPU. There are software drivers available for the SAE 81C90/91 from different CAN tool suppliers.

The SAE 81C90/91 can handle 16 CAN message objects. Each of these comprises eight data bytes and two descriptor bytes containing important information about the configuration of the relevant object. Message objects 0-7 are additionally equipped with two time-stamp bytes, from which the currency of the data in the data bytes can be inferred. For message object 0, a so called "monitor mode" is available with which this message object can be configured to receive all messages that are not covered by other memory locations. This device, too, thus offers basic CAN functionality.

Application Note 30 V 1.0, 2004-02

## The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

### 4.3.2 Functional blocks of the SAE 81C90/91

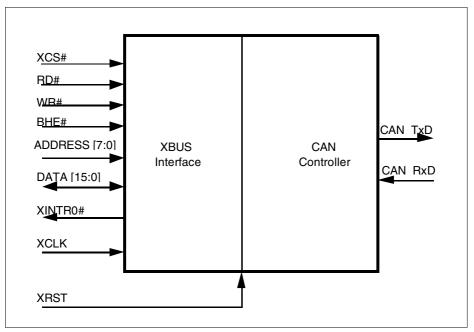

The functional blocks of the SAE 81C90/91 are shown in figure 12.

Figure 12 Block Diagram of the SAE 81C90/91 (I/O Ports only available for SAE 81C90)

Application Note 31 V 1.0, 2004-02

### The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

The *Message Memory* contains the 16 message objects. The SAE 81C90/91 as well owns a *Bit-Stream-Prozessor (BSP)*, which controls the complete CAN protocol, handles the different CAN frames (Data Frame, Remote Frame), and performs the frame check. The BSP reports errors to the *Error Management Logic* which returns information about the error rate back to the BSP and to the *CPU Interface Logic* (CIL). The CIL controls the accesses of the host CPU via the parallel or serial interface and interprets the included instructions.

The task of the *Bit Timing Logic* is again the synchronization to the bit stream and the bus timing. The *Transceiver Control Logic (TCL)* contains the output driver and the input comparator. The *Transmit Check Unit* is a special feature of the SAE 81C90/91. When transmitting a message, each bit is read back via the normal receive path and compared with the bit just sent. If a mismatch occurs, the Transmit Check Error Counter (TCEC) is incremented by one and the actual message is invalidated by an Error Frame. In this way also the chip-internal conversion of the data stored in parallel to the serial bit stream (which is not covered by the CAN protocol itself) is monitored. If the TCEC reaches 4, the device enters the bus-off state.

## 4.3.3 The most important Control Registers of the SAE 81C90/91

Via the host CPU and the 8-bit control registers all functions of the SAE 81C90/91 are controlled. The most important registers are described in the following section.

The register MOD contains the two bits IM and RES, which are necessary for the initialization of the device, and some status bits. In the control register CTRL the Monitor Mode of message object 1 and the Transmit Check Unit can be enabled. The interrupt register INT shows occured interrupts which can be individually enabled / disabled in the interrupt mask register IMSK. In the bit length registers BL1 and BL2 the bit timing segments TSEG1, TSEG2 and SJW are configured. The desired baudrate is controlled via the baudrate prescaler register BRPR. Different physical layers can be connected to the SAE 81C90/91 by programming the output control register OC. The descriptor registers are filled with the 11 bits of the respective identifier, the RTR bit (which distinguishes between Data- and Remote Frames), and the data length code.

#### 4.3.4 Initialization of the SAE 81C90/91 and Bus Access

Similar to the C167CR / C515C two special bits have to be set to be able to initialize the device. These bits are IM and RES in the register MOD. Afterwards the registers concerning the bit timing can be written and the message objects must be configured. Resetting bits RES and IM ends the initialization phase and the controller can participate in the CAN bus activities. Please also read section 5.5.1 for more information about the initialization of this device.

Application Note 32 V 1.0, 2004-02

## The Infineon CAN Devices C167CR, C515C and SAE 81C90/91

The SAE 81C90/91 contains no implementation of the physical layer, which again requires a CAN transceiver.

Further information about the SAE 81C90/91 Stand Alone Full CAN Controller can be found in section 5 or in the corresponding Data Sheet.

**Examples for the Connection of Infineon Microcontrollers to CAN**

# 5 Examples for the Connection of Infineon Microcontrollers to CAN

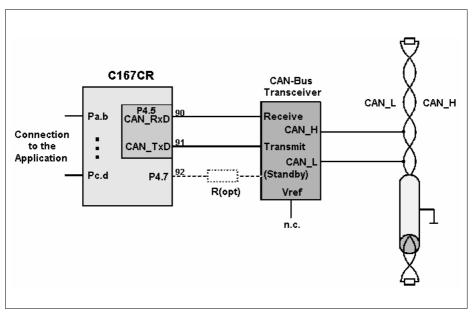

## 5.1 Connecting the C167CR / C515C to CAN

Figure 13 shows the connection between the C167CR and the CAN bus. The CAN module is connected to the outside world via two pins, CAN\_RxD (P4.5) and CAN\_TxD, of port 4. CAN\_RxD receives data from the physical layer of the CAN bus, while CAN\_TxD transfers data to the physical layer. The physical layer is not implemented in the CAN module, so the C167CR is likewise connected via an external transceiver to the CAN bus lines CAN\_H and CAN\_L. In this example, the CAN bus is a shielded, twisted wire pair with termination resistors at both ends of the bus lines. If the transceiver has an input pin for slope control or "stand-by", it can be driven via a port pin of the C167CR (pin P4.7 in this case).

#### Notes:

- If the CAN module is used, port 4 may not be programmed to output all eight segment address lines. A maximum of four segment address lines is possible in this case. The address range that can be accessed via the address lines is then reduced to 1 MByte.

- P4.5 (CAN\_RxD) has to be configured as input by the user. (If the CAN module is not used, P4.5 can be used as general purpose I/O).

- In some versions / production steps of the C167CR, CAN\_TxD is configured as output by hardware and therefore cannot be used as general purpose I/O pin P4.6.

Please contact your distributor or your local Infineon office if you need further information about this subject.

Application Note 34 V 1.0, 2004-02

### **Examples for the Connection of Infineon Microcontrollers to CAN**

Figure 13 Connection of the C167CR to CAN

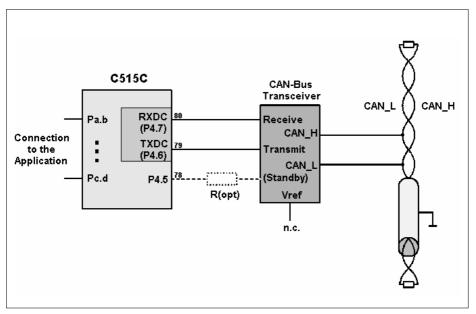

Figure 14 shows the connection between the C515C and the CAN bus. This time the CAN module is connected to the CAN transceiver via the port pins "RXDC" and "TXDC" of port 4. For the control of a slope control or "stand-by" pin, portpin P4.5 was chosen in this example.

Application Note 35 V 1.0, 2004-02

### **Examples for the Connection of Infineon Microcontrollers to CAN**

Figure 14 Connection of a C515C to CAN

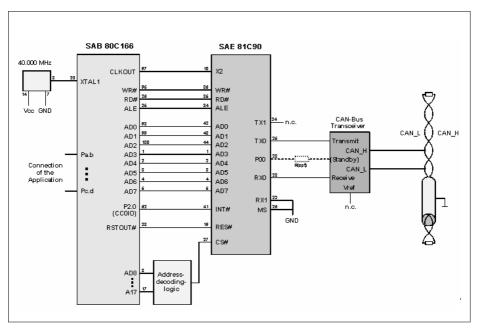

# 5.2 Connecting the SAB 80C166 to CAN using the parallel interface of the SAE 81C90

Of course not all members of the C500- and C166 family own an integrated CAN module. But also these controllers can be used in a Controller Area Network. In figure 15, the connection between a SAB 80C166 and a SAE 81C90 (P-LCC 44, with I/O ports) is shown. Both controllers are connected via the multiplexed 8-bit bus (address/data lines AD0 to AD7, signals WR#, RD#, ALE). This parallel connection is selected by applying a low logic level to pin MS (a high level would activate the serial interface). With the aid of the remaining address lines AD8 to AD17, the chip-select signal for the CAN controller (active low) can be generated via decoding logic, depending on the external memory configuration. The SAB 80C166 can use the multiplexed 8-bit bus for the corresponding memory range, and one of the other bus modes, for example the faster non-multiplexed 16-bit bus (with individual bus timing in each case), for the accesses to the remaining address space.

Application Note 36 V 1.0, 2004-02

#### **Examples for the Connection of Infineon Microcontrollers to CAN**

Figure 15 Connection of a SAB 80C166 to CAN via the SAE 81C90 (parallel)

The SAE 81C90 obtains its defined reset via the RSTOUT# pin of the SAB 80C166. The interrupt output INT# of the CAN controller is routed to a capture input of the host controller (P2.0 in this case). Via this line, the CAN controller can report incoming messages. A 40 MHz quartz oscillator feeds the SAB 80C166, whose CLKOUT pin (which must be enabled in the SYSCON register) in turn supplies the CAN controller with 20 MHz clock information.

Like the C167CR / C515C, the SAE 81C90 contains no implementation of the physical layer and therefore a transceiver must be used. This driver module is connectd to the SAE 81C90 via pins TX0 (Transmitter Output 0, set as a push/pull output by software here) and RX0 (Comparator Input 0 / Digital input). Neither the second transmit pin TX1 nor the analog input RX1 is required here. RX1 is at 0V because the signal shall be evaluated digitally. Two of the transceiver pins are again directly connected to the CAN\_H and CAN\_L lines of the CAN bus. If the transceiver has a pin for slope control or standby, this can be driven by a pin of the two 8-bit I/O ports of the SAE 81C90 (e.g. pin P00). The application driven by the SAB 80C166, e.g. a robot controller, can now interchange data with other nodes in the same Controller Area Network.

Application Note 37 V 1.0, 2004-02

#### **Examples for the Connection of Infineon Microcontrollers to CAN**

Note: If a complete external CAN transceiver chip is used, the best way is to evaluate the signal digitally as shown in this application note. But the SAE 81C90/91 also has an input comparator implemented on-chip in case no such transceiver IC is used. However, if the bus lines work according to the ISO specification, additional circuitry is necessary for the interconnection of the input comparator to the bus lines.

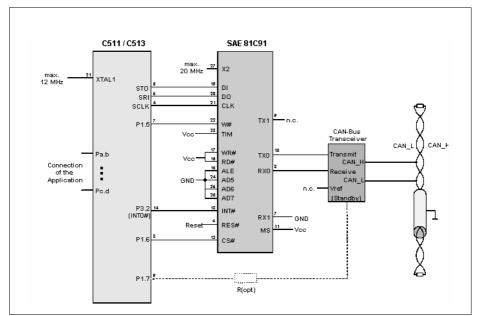

# 5.3 Connecting the C511 / C513 to CAN using the serial interface of the SAE 81C<u>91</u>

The 8-bit microcontrollers C511 / C513 are new low-cost members of the C500 family. The SAE 81C90/91 is an obvious choice for using one of these devices in a Controller Area Network, just as it is for the SAB 80C166. In contrast to the the example shown in figure 16, however, the SAE 81C91 (P-LCC 28, without I/O ports) was selected in the circuit shown in figure 4.3-1. It is connected to the C511 / C513 and its Synchronous Serial Channel (SSC) via the Serial Synchronous Interface (SI), which is selected by applying a high level to the MS pin. In this example, the SSC should be configured as follows: master mode, clock idle level = low, first edge of clock (= rising edge) = data shift, second edge (= trailing edge) = data shift. The data width is 8 bits, MSB is sent / received first.

Figure 16 Connection of a C511 / C513 to CAN via the SAE 81C91 (serial)

Application Note 38 V 1.0, 2004-02

#### **Examples for the Connection of Infineon Microcontrollers to CAN**

Every access to the SAE 81C91 is started by activating the device (CS# = 0), performed by a port pin (e.g. P1.6). Pin P1.5 of the C511 / C513 then selects a read (W# = 1) or a write (W# = 0) operation via the W# input of the CAN controller. Then the address of the register to be read or written is sent to the SAE 81C91 via the line connecting pin STO (SSC Transmit Output) with pin DI (Data Input). Depending on the operation, one or more (if the automatic decrementing of the address is activated in the CAN controller by setting bit ADE in the MOD register) data bytes can be written to the SAE 81C91 or can be read via the line between pin SRI (SSC Receive Input) and pin DO (Data Output). Finally, the CAN controller has to be deactivated again (CS# = 1).

The synchronization of the controllers is done via the line SCLK - CLK. Data from pin DI are always transferred into the internal shift register with the rising edge of the clock. The level applied to the timing pin (TIM) of the CAN controller decides whether data is output at the DO pin with the rising edge (TIM = 0) or with the falling edge (TIM = 1, see figure 4.3-1) of the CLK signal. Pin P1.7 of the C511 / C513 controls the slope control pin of the CAN transceiver, when available. On the CAN controller side, an inactive level is applied to pins WR#, RD#, and ALE, and to pins AD5 to AD7, which are not required when the serial connection between the SAE 81C91 and the host controller is used.

## 5.4 A proposal for the CAN Bus Cables

The CAN standard does not include the connectors with which an application is connected to the bus lines. A proposal of the CAN user group "CAN in Automation" (CiA) uses 9-pole SUB-D connectors with the following pin usage:

Table 1

| Pin | Signal | Description       |

|-----|--------|-------------------|

| 1   | _      | (reserved)        |

| 2   | CAN_L  | CAN_L bus line    |

| 3   | GND    | ground            |

| 4   | _      | (reserved)        |

| 5   | _      | (reserved)        |

| 6   | (GND)  | optional ground   |

| 7   | CAN_H  | CAN_H bus line    |

| 8   | _      | (reserved)        |

| 9   | (V+)   | opt. power supply |

Application Note 39 V 1.0, 2004-02

Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR / C515C

# Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR / C515C

### 6.1 Notes on the following Sections

The following sections contain important hints necessary for establishing a communication via the CAN bus using the devices described above. The program parts are mainly written in "C". They show just *one* way to solve a certain problem and they don't claim for optimized code. For better understanding the reader should also refer to the Infineon information "Description of the On-Chip CAN-Module", the SAE 81C90/91 Data Sheet, and the C515C User's Manual.

# 6.2 Accessing the Registers of the CAN Module and the SAE 81C90/91

To access the registers of the CAN module and the SAE 81C90/91, the registers have been given names that show the task of the respective register. Via pointer these names have been connected with the respective address in three include files. Therefore, in the software hints, not "address EF04h of the C167CR" is accessed but "directly" the register "BTR" (the Bit Timing Register). Those registers, which appear more than once (e.g. in each message object) are given the name adder "\_M1", "\_M2" etc. for message object 1, 2 etc. Another possibility would be to define the message objects as "structures" ("MOBJ1", "MOBJ2",...) to then access for example the Message Control Register of message object 5 with "MOBJ5.MCR".

#### Extract from the include file for the C167CR:

| /*      | Registe | r       | Address */ |        |        |

|---------|---------|---------|------------|--------|--------|

| #define |         | CSR     | *(unsigned | int *) | 0xef00 |

| #define |         | IR      | *(unsigned | char*) | 0xef02 |

| #define |         | BTR     | *(unsigned | int *) | 0xef04 |

| #define |         | GMS     | *(unsigned | int *) | 0xef06 |

| #define |         | UGML    | *(unsigned | int *) | 0xef08 |

| #define |         | LGML    | *(unsigned | int *) | 0xef0a |

| #define |         | UMLM    | *(unsigned | int *) | 0xef0c |

| #define |         | LMLM    | *(unsigned | int *) | 0xef0e |

| #define |         | MCR_M1  | *(unsigned | int *) | 0xef10 |

| #define |         | UAR_M1  | *(unsigned | int *) | 0xef12 |

| #define |         | LAR_M1  | *(unsigned | int *) | 0xef14 |

| #define |         | MCFG_M1 | *(unsigned | char*) | 0xef16 |

| #define |         | DB0_M1  | *(unsigned | char*) | 0xef17 |

| #define |         | DB1_M1  | *(unsigned | char*) | 0xef18 |

| #define |         | DB2_M1  | *(unsigned | char*) | 0xef19 |

Application Note 40 V 1.0, 2004-02

### Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR / C515C

```

#define

DB3 M1 *(unsigned char*)

0xef1a

DB4_M1 *(unsigned char*)

#define

0xef1b

#define

DB5_M1 *(unsigned char*)

0xef1c

#define

DB6_M1 *(unsigned char*)

0xef1d

DB7_M1 *(unsigned char*)

#define

0xef1e

#define

MCR_M2 *(unsigned char *)

0xef20

#define ...

```

#### . . .

#### Extract from the include file for the C515C:

| /*      | Registe: | r       | Ado        | dress */ |        |

|---------|----------|---------|------------|----------|--------|

| #define |          | CR      | *(unsigned | char*)   | 0xf700 |

| #define |          | SR      | *(unsigned | char*)   | 0xf701 |

| #define |          | IR      | *(unsigned | char*)   | 0xf702 |

| #define |          | BTR0    | *(unsigned | char*)   | 0xf704 |

| #define |          | BTR1    | *(unsigned | char*)   | 0xf705 |

| #define |          | GMS0    | *(unsigned | char*)   | 0xf706 |

| #define |          | GMS1    | *(unsigned | char*)   | 0xf707 |

| #define |          | UGML0   | *(unsigned | char*)   | 0xf708 |

| #define |          | UGML1   | *(unsigned | char*)   | 0xf709 |

| #define |          | LGML0   | *(unsigned | char*)   | 0xf70a |

| #define |          | LGML1   | *(unsigned | char*)   | 0xf70b |

| #define |          | UMLM0   | *(unsigned | char*)   | 0xf70c |

| #define |          | UMLM1   | *(unsigned | char*)   | 0xf70d |

| #define |          | LMLM0   | *(unsigned | char*)   | 0xf70e |

| #define |          | LMLM1   | *(unsigned | char*)   | 0xf70f |

|         |          |         |            |          |        |

| #define |          | MCR0_M1 | *(unsigned | char*)   | 0xf710 |

| #define |          | MCR1_M1 | *(unsigned | char*)   | 0xf711 |

| #define |          | UAR0_M1 | *(unsigned | char*)   | 0xf712 |

| #define |          | UAR1_M1 | *(unsigned | char*)   | 0xf713 |

| #define |          | LAR0_M1 | *(unsigned | char*)   | 0xf714 |

| #define |          | LAR1_M1 | *(unsigned | char*)   | 0xf715 |

| #define |          | MCFG_M1 | *(unsigned | char*)   | 0xf716 |

| #define |          | DB0_M1  | *(unsigned | char*)   | 0xf717 |

| #define |          | DB1_M1  | *(unsigned | char*)   | 0xf718 |

| #define |          | DB2_M1  | *(unsigned | char*)   | 0xf719 |

| #define |          | DB3_M1  | *(unsigned | char*)   | 0xf71a |

| #define |          | DB4_M1  | *(unsigned | char*)   | 0xf71b |

| #define |          | DB5_M1  | *(unsigned | char*)   | 0xf71c |

| #define |          | DB6_M1  | *(unsigned | char*)   | 0xf71d |

| #define |          | DB7_M1  | *(unsigned | char*)   | 0xf71e |

|         |          |         |            |          |        |

| #define |          | MCR0_M2 | *(unsigned | char*)   | 0xf720 |

| #define |          |         |            |          |        |

|         |          |         |            |          |        |

Application Note 41 V 1.0, 2004-02

## Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR / C515C

Extract from the include file for the SAE 81C90/91 (according to the specification 01/97):

```

/*

Register

Addresse */

*(unsigned char far*) 0x...00

#define

BL1

#define

BL2

*(unsigned char far*) 0x...01

#define

OC

*(unsigned char far*) 0x...02

#define

*(unsigned char far*) 0x...03

BRPR

#define

RRR1

*(unsigned char far*) 0x...04

#define

RRR2

*(unsigned char far*) 0x...05

#define

RIMR1

*(unsigned char far*) 0x...06

#define

*(unsigned char far*) 0x...07

RIMR2

#define

*(unsigned char far*) 0x...08

TRSR1

#define

*(unsigned char far*) 0x...09

TRSR2

#define

IMSK

*(unsigned char far*) 0x...0a

#define

*(unsigned char far*) 0x...10

MOD

#define

*(unsigned char far*) 0x...11

INT

#define

*(unsigned char far*) 0x...12

CTRL

#define

*(unsigned char far*) 0x...40

DR0H

#define

*(unsigned char far*) 0x...41

DR0L

#define

*(unsigned char far*) 0x...42

DR1H

#define

DR1L

*(unsigned char far*) 0x...43

#define

BYTE0MSG0

*(unsigned char far*) 0x...80

#define

BYTE1MSG0

*(unsigned char far*) 0x...81

#define

BYTE2MSG0

*(unsigned char far*) 0x...82

#define

BYTE3MSG0

*(unsigned char far*) 0x...83

#define

*(unsigned char far*) 0x...84

BYTE4MSG0

#define

*(unsigned char far*) 0x...85

BYTE5MSG0

#define

BYTE6MSG0

*(unsigned char far*) 0x...86

#define

BYTE7MSG0

*(unsigned char far*) 0x...87

#define

BYTE0MSG1

*(unsigned char far*) 0x...88

```

The absolute addresses have to be chosen according to the address range the controller is supposed to be located in.

Application Note 42 V 1.0, 2004-02

### Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR / C515C

## 6.3 Configuration of the Bit Timing

Before initializing the CAN controllers, one has to think about the internal frequencies of the devices as well as the baudrate of the CAN bus. The registers that are responsible for the bit timing contain the parameters TSEG1, TSEG2, SJW and BRP which have to be programmed accordingly.

In the following section, a way to determine these parameters for a special controller frequency (e.g. 20 MHz) and a certain CAN baudrate (e.g. 125 kbit/s) shall be presented. The calculations are based on the following (rough) structure of one bit time (figure 17):

Figure 17 Rough Structure of one Bit Cell in the CAN Module of the C167CR / C515C and in the SAE 81C90/91

The following equations apply to figure 17:

Application Note 43 V 1.0, 2004-02

### Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR / C515C

Please note that TSEG1, TSEG2, BRP and SJW are the numerical values of the respective fields to be programmed in the respective registers of the controllers,  $t_{\rm G}$  represents one BTL cycle (see section 2.4).

The following equation applies to the C167CR:

$$t_{CAN\_CLOCK} = 2 * t_{XCLK} = \frac{2}{f_{CPU}}$$

The following equation applies to the C515C:

$$t_{CAN\_CLOCK} = 1 CLP = \frac{1}{f_{CPU}}$$

The following equation applies to SAE 81C90/91:

$$t_{CAN\_CLOCK} = 2 * t_{OSC} = \frac{2}{f_{OSC}}$$

Equations (2), (3) and (4) inserted into (1) results in:

$$t_{BIT} = 1 * t_{q} + (TSEG1 + 1) * t_{q} + (TSEG2 + 1) * t_{q}$$

which is equal to

$$t_{BIT} = 3 * t_{q} + (TSEG1 + TSEG2) * t_{q}$$

This equation solved to (TSEG1 + TSEG2) results in:

$$(TSEG1 + TSEG2) = \frac{t_{BIT} - 3 * t_{q}}{t_{q}}$$

Inserting (5) results in

$$(TSEG1 + TSEG2) = \frac{t_{BIT}}{(BRP + 1) * t_{CAN\_CLOCK}} - 3$$

The following applies to (TSEG1 + TSEG2):

$$1 \le (TSEG1 + TSEG2) \le 22$$

and  $(TSEG1 + TSEG2) \ge N$

because the possible values for TSEG1 are between 0 and 15 and for TSEG2 are between 0 and 7 and both parameters have to be integer. Now certain values of  $t_{\text{BIT}}$ ,  $t_{\text{CAN\_CLOCK}}$ , and BRP (possible values for BRP are 0 to 63) result in different possible values for (TSEG1 + TSEG2).

Application Note 44 V 1.0, 2004-02

#### Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR / C515C

Example: C167CR CPU clock: 20 MHz  $\Rightarrow$  t<sub>can clock</sub> = 100 ns

Desired CAN baudrate: 125 kBit/s  $\Rightarrow$  t<sub>BIT</sub> = 1 / baudrate = 8  $\mu$ s

Using equation (7) results in the following table with the valid values of (TSEG1 + TSEG2). Additionally,  $t_{\alpha}$  is calculated using equation (5).

#### Table 2

| BRP<br>(0 ≤ BRP ≤ 63)         | <br>3   | 4   | <br>7   | <br>9    |  |

|-------------------------------|---------|-----|---------|----------|--|

| TSEG1 + TSEG2<br>(1 ≤ x ≤ 22) | <br>17  | 13  | <br>7   | <br>5    |  |

| t <sub>q</sub> [ns]           | <br>400 | 500 | <br>800 | <br>1000 |  |

When choosing one possibility for BRP, TSEG1, and TSEG2, some rules have to be obeyed so that the CAN specification is fulfilled. Signal delays by the bus lines, input comparators and output drivers have to be taken into account. General rules for TSEG1 and TSEG2 depending on BRP:

#### Table 3

| if BRP = 0: | if BRP ≥ 1: |

|-------------|-------------|

| TSEG1 ≥ 2   | TSEG1 ≥ 1   |

| TSEG2 ≥ 1   | TSEG2 ≥ 0   |

As a general rule, the sampling of the bit should take place at about 60-70% of the total bit time. Nevertheless, for each system the delays of bus drivers, transmitter / receiver circuits and the bus lines have to be taken into account when configuring the sample point. Examples can be found in the "Description of the on-chip CAN Module", page N-32 / N33.

If BRP is chosen to be 4, then TSEG1 + TSEG2 = 13 and  $t_q$  is 500 ns. Therefore the total bit time of 8  $\mu$ s is devided into 16  $t_q$ . One  $t_q$  is needed for the Synchronization Segment which leaves 15  $t_q$  left for Phase Buffer Segment 1 and Phase Buffer Segment 2 (see figure 17 again).

60% of 16 t<sub>a</sub> are about 10 t<sub>a</sub> which results in the following configuration:

- 1 t<sub>a</sub> for the Synchronization Segment

- 9 t for Phase Buffer Segment 1

- 6 t<sub>a</sub> for Phase Buffer Segment 2.

Application Note 45 V 1.0, 2004-02

### Ways of handling the SAE 81C90/91 and the CAN Module on the C167CR / C515C

This means that TSEG1 and TSEG2 should be programmed to the following values:

$$TSEG1 = 8;$$

$TSEG2 = 5.$

General rules for the SJW:

$$0 \le SJW \le 3;$$

$SJW \le TSEG2.$

This means that SJW could be programmed to the maximum value of 3. But normally such a big SJW is only necessary when the clock generation of the different nodes is quite inaccurate, e.g. if ceramic resonators are used. So a SJW of 1 should be enough.