# Variability analysis of Graded Channel Dual Material-Double Gate Strained-Silicon MOSFET with fixed charges

Subba Rao Suddapalli · Bheema Rao Nistala

Received: 07 April 2021 / Accepted:

Abstract In this paper, variability analysis of graded channel dual material (GCDM) double gate (DG) strainedsilicon (s-Si) MOSFET with fixed charges is analyzed with the help of Sentaurus TCAD. By varying the different device parameters, the variability analysis of the proposed GCDM-DG s-Si MOSFET is performed with respect to variations in threshold voltage and drain current as the line edge roughness and fluctuations in random dopant, contact resistance, and oxide thickness are considered. The results confirm that the effect of process variations is severe when the device has fixed charges at oxide interface. Moreover, the proposed GCDM-DG s-Si p-MOSFET has less vulnerable to the effects of line edge roughness, fluctuations in oxide thickness and random dopants in comparison with the proposed GCDM-DG s-Si n-MOSFET.

Keywords Contact resistance fluctuations  $\cdot$  Line edge roughness  $\cdot$  Oxide thickness fluctuations  $\cdot$  Random dopant fluctuations  $\cdot$  Strained-Silicon  $\cdot$  Threshold voltage.

#### 1 Introduction

In recent times, numerous studies have been dedicated to the strained-silicon (s-Si) MOSFETs owing to their compatibility with traditional silicon fabrication processing and the capability for obtaining higher performance because of the enhanced carrier transport properties, i.e., improved mobility and high-field velocity [1]-

Department of ECE, NIT Warangal, Telangana, India, 506004

E-mail: subbarao.s29@gmail.com, nbr.rao@gmail.com

[6]. With the help of layer transfer method [7], the strain is introduced in the silicon material. In this technique, the biaxial-tensile strain is developed in silicon layer by growing a silicon layer on the relaxed  $Si_{(1-X)}Ge_{(X)}$  layer, which is developed on silicon on insulator (SOI) material. In nano scaled MOSFETs, interface traps are generated at s-Si/Oxide (s-Si/SiO<sub>2</sub>) interface due to the electric field in s-Si devices [8]-[10]. Hence, the performance of s-Si MOSFET deteriorates in terms of threshold voltage and short channel effects (SCEs).

To reduce the hot carrier effects (HCEs), the dual metal gate (DMG) engineering is incorporated in double gate (DG) s-Si MOSFET [11]-[13]. Since control gate in DMG structure has higher work function than screen gate, a step like profile in channel potential and an increased average electric-field in channel are achieved. Consequently, the performance of DG s-Si device is enhanced by incorporating the DMG structure. Furthermore, when graded channel (GC) engineering is included in DG s-Si MOSFET, lower electric field is obtained at drain side, thus resulting in reduced HCEs [14]-[16]. Therefore, better performance of DG s-Si MOSFET is acquired by employing both gate and channel engineering.

The analytical threshold voltage model of FD-SOI MOSFET with random dopant fluctuations was demonstrated in [17]. Moreover, The dependence of different device parameters, such as channel length, thicknesses of gate oxide and silicon film on deviation of threshold voltage is studied. In [18], the effect of random dopant fluctuation in undoped channel silicon Gate All Around Nanowire was demonstrated. Besides, it is noticed that the random dopant fluctuation in the source/drain extension and channel regions disturbs the carrier potential and initiates random variations in electrical characteristics of Nanowire. In [19], the impact of random

dopant variation in source and drain on the performance of DG MOSFETs was presented. Also, the effect of high doping clusters on the charge injection has been examined in detail using quantum simulation based on non-equilibrium Green function coupled self consistently to the Poissons equation. In [20], a study on the impact of random dopant variations of the source/drain extension (SDE) of Strained SiGe FinFETs was presented. Moreover, increasing SDE's length and decreasing SDE's doping concentration reduce the variations in threshold voltage, on-current, and off-current. The variability analysis of Graded Channel Dual Material (GCDM) DG s-Si MOSFET with fixed charges has not been presented so far in the literature. By employing GC with gate engineering structure, reduced variability performance of s-Si DG MOSFET is achieved.

This paper illustrates the analysis of the effect of fluctuations in doping (RDF), oxide thickness (OTF), contact resistance (CRF), and line edge roughness (LER) on the performance of GCDM-DG s-Si device with fixed charges. The electrical characteristics of the device strongly depend on doping profiles and the physical dimensions, so the responsiveness of the device to the deviations of RDF and LER becomes more. Thus, we need to calculate the standard deviations of the threshold voltage and ON current of the device due to the perturbations of RDF, LER, OTF, and CRF. Also, the variations in the characteristics of the MOSFET can be reduced by carefully choosing the device's dimensions. Besides, the proposed GCDM-DG s-Si p-MOSFET has less deviations when compared to proposed GCDM-DG s-Si n-MOSFET.

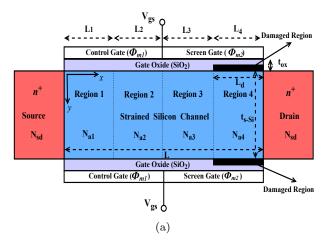

# 2 Proposed MOSFET structure and TCAD setup

The simulated schematic view of the GCDM-DG s-Si MOSFET with fixed charges is shown in Fig. 1(a). The channel region is doped with four different uniform doping concentrations (i.e.,  $N_{a1}$ ,  $N_{a2}$ ,  $N_{a3}$ , and  $N_{a4}$ ). The top and bottom gates of the proposed device consist of control gate and screen gate. It is considered that the control gate has higher work function than screen gate (i.e.,  $\phi_{m1} > \phi_{m2}$ ). However, the gates of GC-DG s-Si MOSFET has a single gate material whose work function is an average of  $\phi_{m1}$  and  $\phi_{m2}$ . Owing to HCEs in nano-scaled proposed s-Si MOSFET, fixed charges are created at oxide/channel interface in damaged region of length  $L_d$ , as shown in Fig. 1(a). The transfer characteristics of the s-Si MOSFET simulated in TCAD are calibrated with the experimental results of the transfer characteristics of [21], as demonstrated in Fig. 1(b). It is apparent from Fig. 1(b) that the TCAD simulation

data of s-Si device is in good agreement with the experimental data illustrated in [21]. The different device parameters and dimensions of the proposed MOSFET used in the simulation are listed in Table 1.

Because of the introduced strain into the silicon layer, the energy band structure of silicon is affected because of the biaxial tension. Hence, the energy-band gap of the silicon material and effective mass of carriers decrease, whereas electron affinity of an atom  $(\chi_{Si})$  increases. The variations in energy band gap of silicon, electron affinity of atom, and effective masses of carrier are expressed as shown below [22,23]

$$(\Delta E_c)_{s-Si} = 0.57X, \qquad (\Delta E_g)_{s-Si} = 0.4X$$

$$V_T \ln \left( \frac{N_{V,Si}}{N_{V,s-Si}} \right) = V_T \ln \left( \frac{m_{h,Si}^*}{m_{h,s-Si}^*} \right)^{\frac{3}{2}} \approx 0.075X$$

where X represents the Germanium mole fraction in silicon layer and  $V_T$  indicates thermal voltage.  $N_{V,Si}$  and  $N_{V,s-Si}$  demonstrate the density of states in valence-band of silicon and strained-silicon material, respectively.  $m_{h,Si}^*$  and  $m_{h,s-Si}^*$  denote the effective masses of hole in silicon and strained-silicon material, respectively. It is obvious from the equations given below that the both flat band potential and barrier potential of the source (drain) to channel decrease simultaneously [24].

$$\Delta V_{fb} = -\frac{E_c}{q} + \frac{E_g}{q} - V_T \ln \left( \frac{N_{V,Si}}{N_{V,s-Si}} \right)$$

$$\Delta V_{bi} = V_T \ln \left( \frac{N_{V,Si}}{N_{V,s-Si}} \right) - \frac{E_g}{q}$$

where  $\Delta V_{fb}$  and  $\Delta V_{bi}$  are the variations in flat-band voltage and built-in barrier, respectively.

The variability analysis of the proposed GCDM-DG s-Si device with fixed charges is simulated with the help of the statistical impedance field method (sIFM) in Sentaurus TCAD [25]. The sIFM creates a huge number of randomized fluctuations of the parameters that are under investigation (dopant concentrations) and evaluates the changes in the device performance in linear response. In device simulation, the following physical models are employed. The carrier transport mechanism is evaluated with the aid of drift diffusion model and recombination of the carriers are estimated by using Auger and SRH recombination models. Moreover, the mobility of carriers is interpreted by using the highfield saturation and Enormal mobility model. Besides, energy band gap narrowing effects are estimated by OldSlotboom model and strained-silicon properties are considered by the MoleFraction model. And also, effect of the fixed charges at oxide/channel interface of MOS-FET are assessed by using the Traps model. As the thicknesses of channel and oxide are considered to be 10 nm and  $\geq$  1 nm, respectively, quantum-mechanical effects are neglected [26].

Fig. 1: Symmetrical GCDM-DG s-Si MOSFET fixed charges a. Proposed MOSFET structure b. Calibration of transfer characteristics of the s-Si device with experimental results of [21].

Table 1: Dimensions and parameters are used in device simulation of the GCDM-DG s-Si MOSFET

| S. No. | Parameter                 | Symbol                           | Values                                                                 |  |  |

|--------|---------------------------|----------------------------------|------------------------------------------------------------------------|--|--|

| 1      | Channel length            | L                                | 20 - 40 nm                                                             |  |  |

| 2      | Channel doping            | $N_{a1}, N_{a2}, N_{a3}, N_{a4}$ | $10^{17}, 7 \times 10^{16}, 4 \times 10^{16}, 10^{16} \text{ cm}^{-3}$ |  |  |

| 3      | Source and Drain doping   | $N_{sd}$                         | $10^{20} \text{ cm}^{-3}$                                              |  |  |

| 4      | Channel thickness         | $t_{s-Si}$                       | 10 nm                                                                  |  |  |

| 5      | Oxide thickness           | $t_{ox}$                         | 1 - 2 nm                                                               |  |  |

| 6      | Work functions of control | $\phi_{m1},\phi_{m2}$            | 4.8, 4.6 eV                                                            |  |  |

| U      | and screen gates          | $  \varphi_{m1}, \varphi_{m2}  $ | 1.0, 1.0 0 1                                                           |  |  |

| 7      | Gate-source voltage       | $V_{gs}$                         | 0 - 1 V                                                                |  |  |

| 8      | Drain-source voltage      | $V_{ds}$                         | 0 - 1 V                                                                |  |  |

| 9      | Germanium mole fraction   | m                                | 0.2 - 0.3                                                              |  |  |

| 10     | Fixed charge density      | $N_f$                            | $-4 \times 10^{12}, 4 \times 10^{12} \text{ cm}^{-2}$                  |  |  |

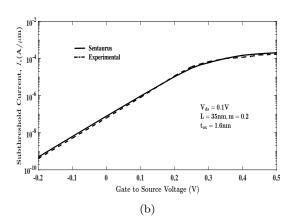

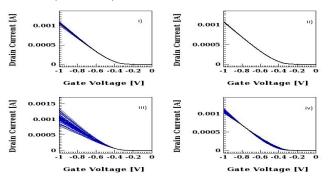

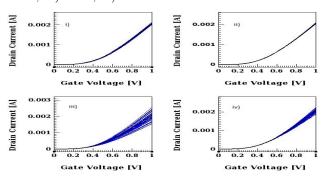

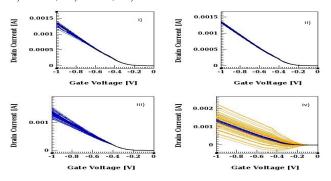

Fig. 2: Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with L=20 nm due to i) RDF, ii) OTF, iii) CRF, iv) LER.

# 3 Result analysis

This section illustrates the variability analysis of the GCDM-DG s-Si MOSFET with fixed charges. The effects of RDF, OTF, CRF, and LER are considered individually to perform variability analysis of the proposed device, and each case is simulated with an ensemble size of 150. Fig. 2 depicts the effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG

s-Si n-MOSFET at L=20 nm,  $t_{ox}=1$  nm, and m=0.2. It is evident from Fig. 2 that the CRF has more effect on ON current  $(I_{ON})$  and LER has moderate effect on threshold voltage  $(V_{th})$  of the device when compared to other fluctuations, as listed in Table 2. Moreover, the standard deviation of  $V_{th}$  ( $\sigma V_{th}$ ) of the proposed device is estimated for different values of  $V_{th}$  and extracted from the transfer characteristics at a  $V_{DS}$  of 0.05 V. Therefore, standard deviations of  $I_{ON}$  ( $\sigma I_{ON}$ ) and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve ( $V_{th}=0.262$  V and  $I_{ON}=7.3\times10^{-4}$ ), as seen in Table 2.

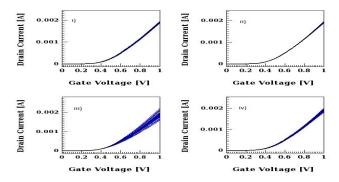

The effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si n-MOSFET at L=40 nm,  $t_{ox}=1$  nm, and m=0.2 are shown in Fig. 3. It is noticed from Fig. 2 and Fig. 3 that the effect of variations are less at a channel length of 40 nm as compared to a channel length of 20 nm due to reduced short channel effects. However, CRF has considerable effect on  $I_{ON}$  of the device than other process variations, as listed in Table 2. Moreover, in this case,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve ( $V_{th}=0.369$  V and  $I_{ON}=4.21\times10^{-4}$ ), as illustrated in Table 2.

Fig. 3: Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with L=40 nm due to i) RDF, ii) OTF, iii) CRF, iv) LER.

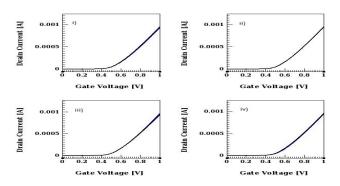

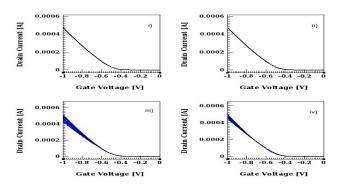

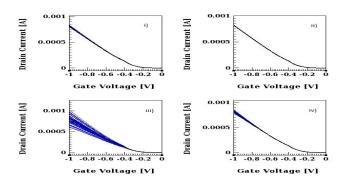

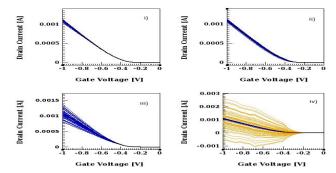

Fig. 4: Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with L= 20 nm due to i) RDF, ii) OTF, iii) CRF, iv) LER.

Fig. 4 depicts the effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si p-MOSFET at L=20 nm,  $t_{ox}=1$  nm, and m=0.2. It is evident from Fig. 4 that the CRF has more effect on  $I_{ON}$  and LER has moderate effect on threshold voltage of the device as compared to the other fluctuations, as listed in Table 3. Moreover,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve ( $V_{th}=-0.348$  V and  $I_{ON}=3.19\times10^{-4}$ ), as demonstrated in Table 3. It is observed from Table 2 and Table 3 that the effects of RDF, OTF, CRF, and LER on the transfer characteristics of the proposed p-MOSFET are less than the proposed n-MOSFET because of the higher threshold voltage of proposed p-MOSFET.

The effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si p-MOSFET at L=40 nm,  $t_{ox}=1$  nm, and m=0.2 are shown in Fig. 5. It is observed from Fig. 4 and Fig. 5 that the effect of variations are less for channel length L=40 nm as compared to L=20 nm due to reduced short channel effects. However, CRF has some effect on  $I_{ON}$  of the proposed device when compared to the other variations, as listed in Table 3. Moreover, in this case,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer character-

Fig. 5: Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with L= 40 nm due to i) RDF, ii) OTF, iii) CRF, iv) LER.

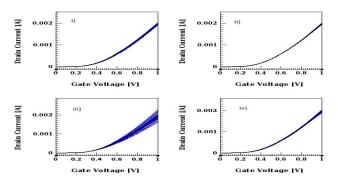

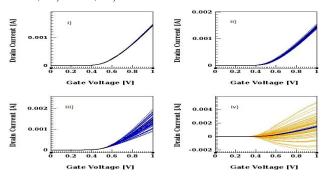

Fig. 6: Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with m=0.3 due to i) RDF, ii) OTF, iii) CRF, iv) LER.

istic curve ( $V_{th}$ = -0.428 V and  $I_{ON}$ = 1.41×10<sup>-4</sup>), as shown in Table 3.

The effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si n-MOSFET at L=20 nm,  $t_{ox}=1$  nm, and m=0.3 are illustrated in Fig. 6. It is evident from Fig. 6 that as strain increases in silicon channel, the impact of RDF, OTF, CRF, and LER on the transfer characteristics slightly decreases due to decrease in threshold voltage of proposed n-MOSFET. Moreover,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve  $(V_{th}=0.196 \text{ V} \text{ and } I_{ON}=4.12\times10^{-4})$ , as illustrated in Table 2.

Fig. 7 illustrates the effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si p-MOSFET at L=20 nm,  $t_{ox}$ = 1 nm, and m= 0.3. The variations of RDF, OTF, CRF, and LER on the transfer characteristics slightly decreases due to the increase in the threshold voltage of the proposed MOSFET as strain increases in silicon channel. Moreover,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve ( $V_{th}$ = -0.382 V and  $I_{ON}$ = 2.72×10<sup>-4</sup>), as listed in Table 3.

Fig. 7: Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with m=0.3 due to i) RDF, ii) OTF, iii) CRF, iv) LER.

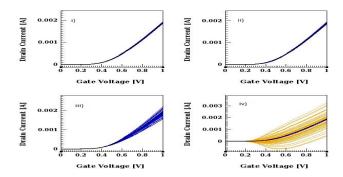

Fig. 8: Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with  $t_{ox}$ = 2 nm due to i) RDF, ii) OTF, iii) CRF, iv) LER.

The effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si n-MOSFET at L=20 nm,  $t_{ox}=2$  nm, and m=0.2 are depicted in Fig. 8. As  $t_{ox}$  increases in the GCDM-DG s-Si n-MOSFET, variations of ON current decrease due to less gate control over the channel than drain and variations of threshold voltage increase because of decrease in threshold voltage of proposed n-MOSFET. Besides,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve ( $V_{th}=0.172$  V and  $I_{ON}=5.96\times10^{-4}$ ), as shown in Table 2.

Fig. 9 plots the effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si p-MOSFET at L=20 nm,  $t_{ox}$ = 2 nm, and m=0.2. As  $t_{ox}$  increases in the GCDM-DG s-Si p-MOSFET, variations of both ON current and threshold voltage decrease due to the less gate control over channel than drain. Besides,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve ( $V_{th}$ =-0.293 V and  $I_{ON}$ =  $2.354 \times 10^{-4}$ ), as illustrated in Table 3.

The effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si n-MOSFET along with negative fixed charge density  $(N_f)$  at L=20 nm,  $t_{ox}=1$  nm, and m=0.2 are shown in Fig. 10.

Fig. 9: Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with  $t_{ox}$ = 2 nm due to i) RDF, ii) OTF, iii) CRF, iv) LER.

Fig. 10: Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with  $N_f = -4 \times 10^{12}$  due to i) RDF, ii) OTF, iii) CRF, iv) LER.

As negative  $N_f$  is considered at oxide/channel interface, the effects of OTF and LER on both  $I_{ON}$  and  $V_{th}$  are more severe compared to the other effects. Due to the fixed charges at oxide/channel interface, the minimum channel potential and its position of the device are varied according to the polarity and magnitude of the fixed charges and length of damaged region [13]. As negative  $N_f$  increases, threshold voltage of the device increases because of the decrement of minimum channel potential, and vice-versa for positive  $N_f$ . Besides,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve ( $V_{th}$ =0.449 V and  $I_{ON}$ =5.86×10<sup>-4</sup>), as listed in Table 2.

Fig. 11 shows the effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si n-MOSFET along with positive  $N_f$  at L=20 nm,  $t_{ox}=1$  nm, and m=0.2 are shown in Fig. 11. As positive  $N_f$  is considered at oxide/channel interface, the effects of OTF and LER on both  $I_{ON}$  and  $V_{th}$  are more severe compared to the other effects. However, in case of the proposed device with positive  $N_f$ , the impacts of OTF and LER are less on both  $I_{ON}$  and  $V_{th}$  compared to the device that has negative  $N_f$  at oxide/channel interface. Moreover,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect

|                            | RDF                  |                       | OTF                  |                       | CRF                  |                       | LER                  |                       |

|----------------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|

|                            | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   |

| L= 20 nm                   | 2.3                  | $1.82 \times 10^{-5}$ | 1.1                  | $1.24 \times 10^{-6}$ | 0.1                  | $4.66 \times 10^{-3}$ | 8.6                  | $2.77 \times 10^{-5}$ |

| L= 40 nm                   | 1.1                  | $6.35 \times 10^{-6}$ | 0.2                  | $6.82 \times 10^{-7}$ | 0.0                  | $1.47 \times 10^{-3}$ | 5.5                  | $1.25 \times 10^{-5}$ |

| m = 0.3                    | 2.6                  | $1.55 \times 10^{-5}$ | 1.1                  | $1.1 \times 10^{-6}$  | 0.1                  | $1.62 \times 10^{-3}$ | 8.6                  | $4.5 \times 10^{-5}$  |

| $t_{ox} = 2nm$             | 2.8                  | $9.75 \times 10^{-6}$ | 0.9                  | $1.25 \times 10^{-6}$ | 0.2                  | $2.93 \times 10^{-3}$ | 9.7                  | $2.46 \times 10^{-5}$ |

| $N_f = 4 \times 10^{-12}$  | 2.2                  | $1.74 \times 10^{-5}$ | 8.3                  | $5.78 \times 10^{-6}$ |                      | $4.6 \times 10^{-3}$  | 267.4                | $1.17 \times 10^{-4}$ |

| $N_f = -4 \times 10^{-12}$ | 1.5                  | $1.26 \times 10^{-5}$ | 15.6                 | $1.34 \times 10^{-5}$ | 0.1                  | $2.71 \times 10^{-3}$ | 442                  | $5.02 \times 10^{-4}$ |

Table 2: Variability analysis of proposed GCDM-DG s-Si n-MOSFET with  $V_{ds} = 0.05 \text{ V}$

Table 3: Variability analysis of proposed GCDM-DG s-Si p-MOSFET with  $V_{ds} = 0.05~V$

|                            | RDF                  |                       | OTF                  |                       | CRF                  |                       | LER                  |                       |

|----------------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|

|                            | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   |

| L= 20 nm                   | 1.1                  | $5.48 \times 10^{-6}$ |                      | $9.86 \times 10^{-7}$ | 0.2                  | $7.52 \times 10^{-4}$ | 8.8                  | $1.62 \times 10^{-5}$ |

| L= 40 nm                   | 0.8                  | $1.13 \times 10^{-6}$ | 0.1                  | $2.2 \times 10^{-7}$  | 0.1                  | $1.53 \times 10^{-4}$ | 1.9                  | $4.06 \times 10^{-6}$ |

| m = 0.3                    | 1.1                  | $5.11 \times 10^{-6}$ | 0.3                  | $8.84 \times 10^{-7}$ | 0.2                  | $5.25 \times 10^{-4}$ | 8.4                  | $1.59 \times 10^{-5}$ |

| $t_{ox} = 2nm$             | 0.9                  | $1.7 \times 10^{-6}$  | 0.2                  | $4.9 \times 10^{-7}$  | 0.3                  | $3.9 \times 10^{-4}$  | 3.7                  | $6.77 \times 10^{-6}$ |

| $N_f = 4 \times 10^{-12}$  | 1.1                  | $5.41 \times 10^{-6}$ | 16.3                 | $5.11 \times 10^{-6}$ | 0.2                  | $7.78 \times 10^{-4}$ | 481.3                | $2.03 \times 10^{-4}$ |

| $N_f = -4 \times 10^{-12}$ | 1.4                  | $7.04 \times 10^{-6}$ | 7.3                  | $3.58 \times 10^{-6}$ | 0.1                  | $1.2 \times 10^{-3}$  | 229.2                | $8.53 \times 10^{-5}$ |

Fig. 11: Variation of transfer characteristics of GCDM-DG s-Si n-MOSFET with  $N_f = 4 \times 10^{12}$  due to i) RDF, ii) OTF, iii) CRF, iv) LER.

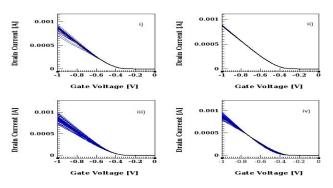

Fig. 12: Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with  $N_f = -4 \times 10^{12}$  due to i) RDF, ii) OTF, iii) CRF, iv) LER.

to reference transfer characteristic curve ( $V_{th}$ = 0.271 V and  $I_{ON}$ = 7.26×10<sup>-4</sup>), as listed in Table 2.

Fig. 12 demonstrates the effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si p-MOSFET along with negative  $N_f$  at L=20 nm,

Fig. 13: Variation of transfer characteristics of GCDM-DG s-Si p-MOSFET with  $N_f = 4 \times 10^{12}$  due to i) RDF, ii) OTF, iii) CRF, iv) LER.

$t_{ox}=1$  nm, and m=0.2. As negative  $N_f$  is considered at oxide/channel interface, the effects of OTF and LER on both  $I_{ON}$  and  $V_{th}$  are more severe compared to the other effects. As positive  $N_f$  increases, threshold voltage of the device increases because of the decrement of minimum channel potential, and vice-versa for negative  $N_f$ . However, the impacts of OTF and LER on transfer characteristics of the proposed p-MOSFET with negative  $N_f$  is less compared to the proposed n-MOSFET that has negative  $N_f$ . Besides,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve  $(V_{th}=-0.159~{\rm V}$  and  $I_{ON}=3.92\times10^{-4})$ , as shown in Table 3.

Fig. 13 illustrates the effects of RDF, OTF, CRF, and LER on the transfer characteristics of GCDM-DG s-Si p-MOSFET along with positive  $N_f$  at L=20 nm,  $t_{ox}=1$  nm, and m=0.2. As positive  $N_f$  is considered at oxide/channel interface, the effects of OTF and LER on both  $I_{ON}$  and  $V_{th}$  are more severe compared to other

|                            | RDF                  |                       | OTF                  |                       | CRF                  |                       | LER                  |                       |

|----------------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|

|                            | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   |

| L= 20 nm                   | 3.8                  | $2.0 \times 10^{-5}$  | 1.7                  | $1.31 \times 10^{-5}$ | 0.0                  | $1.71 \times 10^{-4}$ | 5.7                  | $4.09 \times 10^{-5}$ |

| L= 40 nm                   | 1.1                  | $5.6 \times 10^{-6}$  | 0.3                  | $3.4 \times 10^{-6}$  | 0.0                  | $1.28 \times 10^{-5}$ | 5.4                  | $6.6 \times 10^{-6}$  |

| m = 0.3                    | 4.3                  | $2.29 \times 10^{-5}$ | 1.7                  | $1.32 \times 10^{-5}$ | 0.1                  | $1.81 \times 10^{-4}$ | 5.5                  | $3.12 \times 10^{-5}$ |

| $t_{ox} = 2nm$             | 4.1                  | $1.66 \times 10^{-5}$ | 1.7                  | $4.98 \times 10^{-6}$ | 0.1                  | $2.04 \times 10^{-4}$ | 11.3                 | $2.6 \times 10^{-5}$  |

| $N_f = 4 \times 10^{-12}$  | 3.0                  | $1.94 \times 10^{-5}$ | 6.7                  | $2.53 \times 10^{-5}$ | 0.0                  | $1.72 \times 10^{-4}$ | 247.7                | $5.93 \times 10^{-4}$ |

| $N_f = -4 \times 10^{-12}$ | 2.1                  | $1.16 \times 10^{-5}$ | 11.1                 | $4.53 \times 10^{-5}$ | 0.1                  | $2.85 \times 10^{-4}$ | 287.2                | $1.48 \times 10^{-3}$ |

Table 4: Variability analysis of proposed GCDM-DG s-Si n-MOSFET with  $V_{ds} = 0.9 \text{ V}$

Table 5: Variability analysis of proposed GCDM-DG s-Si p-MOSFET with  $V_{ds}$ = 0.9 V

|                            | RDF                  |                       | OTF                  |                       | CRF                  |                       | LER                  |                       |

|----------------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|----------------------|-----------------------|

|                            | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   | $\sigma V_{th}$ , mV | $\sigma I_{ON}$ , A   |

| L= 20 nm                   | 1.2                  | $1.67 \times 10^{-5}$ | 0.6                  | $5.75 \times 10^{-6}$ | 0.1                  | $1.55 \times 10^{-4}$ | 10.8                 | $2.81 \times 10^{-5}$ |

| L= 40 nm                   | 0.9                  | $1.76 \times 10^{-6}$ | 0.2                  | $1.0 \times 10^{-6}$  | 0.0                  | $2.6 \times 10^{-5}$  | 4.9                  | $1.15 \times 10^{-5}$ |

| m = 0.3                    | 1.2                  | $5.07 \times 10^{-5}$ | 0.6                  | $7.06 \times 10^{-6}$ | 0.1                  | $7.97 \times 10^{-5}$ | 10.5                 | $3.89 \times 10^{-5}$ |

| $t_{ox} = 2nm$             | 1.6                  | $8.01 \times 10^{-6}$ | 0.8                  | $2.89 \times 10^{-6}$ | 0.1                  | $1.13 \times 10^{-4}$ | 1.3                  | $1.43 \times 10^{-5}$ |

| $N_f = 4 \times 10^{-12}$  | 1.3                  | $1.73 \times 10^{-5}$ | 9.8                  | $2.07 \times 10^{-5}$ | 0.1                  | $1.56 \times 10^{-4}$ | 261.2                | $6.67 \times 10^{-4}$ |

| $N_f = -4 \times 10^{-12}$ | 2.0                  | $4.21 \times 10^{-5}$ | 5.9                  | $1.56 \times 10^{-5}$ | 0.0                  | $1.18 \times 10^{-4}$ | 208.5                | $3.76 \times 10^{-4}$ |

effects. However, in case of the proposed device with negative  $N_f$ , the impacts of OTF and LER are less on both  $I_{ON}$  and  $V_{th}$  compared to the device that has positive  $N_f$  at oxide/channel interface. Also, the impacts of OTF and LER on transfer characteristics of the proposed n-MOSFET with positive  $N_f$  is less compared to the proposed p-MOSFET that has positive  $N_f$ . Moreover,  $\sigma I_{ON}$  and  $\sigma V_{th}$  are calculated with respect to reference transfer characteristic curve ( $V_{th}$ = -0.336 V and  $I_{ON}$ = 3.24×10<sup>-4</sup>), as listed in Table 3.

The effects of RDF, OTF, CRF, and LER on the transfer characteristics of the GCDM-DG s-Si MOS-FET at  $V_{ds}$ =0.9 V are given in Table 4 and Table 5. As shown in Table 4 and Table 5, there is a slight increase in  $\sigma I_{ON}$  and slight decrease in  $\sigma V_{th}$  when  $V_{ds}$  changes from 0.05 V to 0.9V.

#### 4 Conclusion

The variability analysis of proposed GCDM-DG s-Si MOSFET with fixed charge density has been evaluated using the TCAD tool. The variability of GCDM-DG s-Si MOSFET is reduced by employing the DMG structure and the GC engineering. A detailed variability analysis has been done to investigate the different effects, such as RDF, OTF, CRF, and LER by varying parameters of the GCDM-DG s-Si MOSFET. Decrements of  $\sigma I_{ON}$  and  $\sigma V_{th}$  of proposed GCDM-DG s-Si MOSFET have been obtained by increasing the channel length. Moreover, it is concluded from the results that the effects of OTF and LER on the device characteristics are severe when device has fixed charge density at oxide/channel interface. Besides, the impact of RDF, OTF, CRF, and LER on ON current and threshold voltage of proposed GCDM-DG s-Si p-MOSFET

is less compared to the proposed GCDM-DG s-Si n-MOSFET.

#### **Declarations**

Funding The authors declare that Suddapalli Subba Rao has received research support from National Institute of Technology Warangal. Further, authors have no other relevant funding or financial support to disclose in relevance to the work shown in this paper.

Conflicts of interest The authors declare that there is no conflict of interests.

Availability of data and material The data that support the findings of this study are available from the corresponding author, upon reasonable request.

Author Contributions All the authors contributed to study conception and conceptualization. TCAD simulation, analysis, and first draft were performed by Suddapalli Subba Rao and edited by Nistala Bheema Rao.

## Consent to Participate Not Applicable

Consent for Publication All the authors declare their consent to transfer the publication rights to the journal in which this manuscript is submitted.

### References

1. J. B. Roldán and F. Gámiz, "Simulation and modelling of transport properties in strained-Si and strained-Si/SiGe-

- on-insulator MOSFETs," *Solid-State Electronics*, vol. 48, no. 8, pp. 1347–1355, 2004.

- T. Vogelsang and K. R. Hofmann, "Electron mobilities and high-field drift velocities in strained silicon on silicongermanium substrates," *IEEE Transactions on Electron Devices*, vol. 39, no. 11, pp. 2641–2642, Nov 1992.

- S. Barraud, L. Clavelier, and T. Ernst, "Electron transport in thin SOI, strained-SOI and GeOI MOSFET by Monte-Carlo simulation," Solid-State Electronics, vol. 49, no. 7, pp. 1090 – 1097, 2005.

- K. Chandrasekaran, X. Zhou, S. B. Chiah, W. Shangguan, and G. H. See, "Physics-based single-piece charge model for strained-Si MOSFETs," *IEEE Transactions on Electron Devices*, vol. 52, no. 7, pp. 1555–1562, July 2005.

- C. Nguyen, A. Pham, C. Jungemann, and B. Meinerzhagen, "Study of charge carrier quantization in strained SinMOSFETs," *Materials Science in Semiconductor Processing*, vol. 8, no. 1, pp. 363 366, 2005.

- C. H. Ko, C. H. Ge, C. C. Huang, C. Y. Fu, C. P. Hsu, C. H. Chen, C. H. Chang, J. C. Lu, Y. C. Yeo, W. C. Lee, and M. H. Chi, "A novel process-induced strained silicon (PSS) CMOS technology for high-performance applications," in *IEEE VLSI-TSA International Symposium on VLSI Technology*, 2005. (VLSI-TSA-Tech)., April 2005, pp. 25–26.

- T. Langdo, M. T. Currie, A. Lochtefeld, R. Hammond, J. Carlin, M. Erdtmann, G. Braithwaite, V. K. Yang, C. Vineis, H. Badawi, and M. Bulsara, "SiGe-free strained Si on insulator by wafer bonding and layer transfer," Applied Physics Letters, vol. 82, pp. 4256–4258, 06 2003.

- 8. S. R. Suddapalli and B. R. Nistala, "Analytical modeling of subthreshold current and swing of strained-Si graded channel dual material double gate MOSFET with interface charges and analysis of circuit performance," *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields*, Vol. 34, Issue 1, 2021.

- S. R. Suddapalli and B. R. Nistala, "Analog/RF Performance of Graded Channel Gate Stack Triple Material Double Gate Strained-Si MOSFET with Fixed Charges," Silicon, 2021, DOI:10.1007/s12633-021-01028-0.

- K. K. Ng and G. W. Taylor, "Effects of hot-carrier trapping in n- and p-channel MOSFET's," *IEEE Transactions on Electron Devices*, vol. 30, no. 8, pp. 871–876, Aug 1983.

- S. R. Suddapalli and B. R. Nistala, "The analog/RF performance of a strained-Si graded-channel dual-material double-gate MOSFET with interface charges," *Journal of Computational Electronics*, Vol. 20, Issue 1, pp. 492-502, 2021.

- S. Baishya, A. Mallik, and C. K. Sarkar, "A pseudo twodimensional subthreshold surface potential model for dualmaterial gate MOSFETs," *IEEE Transactions on Electron Devices*, vol. 54, no. 9, pp. 2520–2525, 2007.

- B. Sanjay Prasad and Anil Vohra, "Dual Material Gate Engineering to Reduce DIBL in Cylindrical Gate All Around Si Nanowire MOSFET for 7-nm Gate," Semiconductors, vol. 54, no. 11, pp. 1490–1495, 2020.

- 14. S. R. Suddapalli and B. R. Nistala, "A center-potential-based threshold voltage model for a graded-channel dual-material double-gate strained-Si MOSFET with interface charges," *Journal of Computational Electronics*, vol. 18, no. 4, pp. 1173–1181, Dec 2019.

- E. Goel, S. Kumar, B. Singh, K. Singh, and S. Jit, "Two-dimensional model for subthreshold current and subthreshold swing of graded-channel dual-material double-gate (GCDMDG) MOSFETs," Superlattices and Microstructures, vol. 106, pp. 147 155, 2017.

- R. K. Sharma, M. Gupta, and R. S. Gupta, "Two-dimensional analytical subthreshold model of graded channel DG FD SOI n-MOSFET with gate misalignment effect," Superlattices and Microstructures, vol. 45, no. 3, pp. 91–104, 2009.

- R. Rao, N. DasGupta and A. DasGupta, "Study of Random Dopant Fluctuation Effects in FD-SOI MOSFET Using Analytical Threshold Voltage Model," *IEEE Transactions on Device and Materials Reliability*, vol. 10, no. 2, pp. 247-253, June 2010.

- K. Nayak, S. Agarwal, M. Bajaj, K. V. R. M. Murali and V. R. Rao, "Random Dopant Fluctuation Induced Variability in Undoped Channel Si Gate all Around Nanowire n-MOSFET," *IEEE Transactions on Electron Devices*, vol. 62, no. 2, pp. 685-688, Feb. 2015.

- A. Martinez, J. R. Barker, A. Svizhenko, M. P. Anantram and A. Asenov, "The Impact of Random Dopant Aggregation in Source and Drain on the Performance of Ballistic DG Nano-MOSFETs: A NEGF Study," *IEEE Transactions on Nanotechnology*, vol. 6, no. 4, pp. 438-445, July 2007.

- K. Liu and E. Chen, "Investigation of the Effects and the Random-Dopant-Induced Variations of Source/Drain Extension of 7-nm Strained SiGe n-Type FinFETs," *IEEE Transactions on Electron Devices*, vol. 66, no. 2, pp. 847-854, Feb. 2019.

- 21. Qi Xiang, Jung-Suk Goo, J. Pan, Bin Yu, S. Ahmed, John Zhang, and Ming-Ren Lin, "Strained silicon NMOS with nickel-silicide metal gate," in 2003 Symposium on VLSI Technology. Digest of Technical Papers (IEEE Cat. No.03CH37407), June 2003, pp. 101–102.

- 22. J.-S. Lim, S. E. Thompson, and J. G. Fossum, "Comparison of threshold-voltage shifts for uniaxial and biaxial tensile-stressed n-MOSFETs," *IEEE Electron Device Letters*, vol. 25, no. 11, pp. 731–733, Nov 2004.

- 23. W. Zhang and J. G. Fossum, "On the threshold voltage of strained-Si-Si1-xGex MOSFETs," *IEEE Transactions on Electron Devices*, vol. 52, pp. 263 268, 03 2005.

- M. J. Kumar, V. Venkataraman, and S. Nawal, "A Simple Analytical Threshold Voltage Model of Nanoscale Single-Layer Fully Depleted Strained-Silicon-on-Insulator MOS-FETs," *IEEE Transactions on Electron Devices*, vol. 53, no. 10, pp. 2500–2506, 2006.

- Sentaurus Device User Guide, Synopsys, Inc., Mountain View, CA, USA, 2020.

- 26. Y. Omura, S. Horiguchi, M. Tabe, and K. Kishi, "Quantum-mechanical effects on the threshold voltage of ultrathin-SOI nMOSFETs," *IEEE Electron Device Letters*, vol. 14, no. 12, pp. 569–571, Dec 1993.