# $\begin{array}{c} INTERNATIONAL \\ ROADMAP \\ FOR \\ DEVICES \ AND \ SYSTEMS^{^{TM}} \end{array}$

**2021 UPDATE**

MORE MOORE

THE IRDS IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

| © 2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                 |

# **Table of Contents**

| Ack | nowl  | edgments                                 | iii |

|-----|-------|------------------------------------------|-----|

| 1.  | Intro | oduction                                 | 1   |

| 1.  | .1.   | Current State of Technology              | 2   |

| 1.  | .2.   | Drivers and Technology Targets           | 2   |

| 2.  | Sum   | nmary and Key Points                     | 3   |

| 3.  | Cha   | llenges                                  | 4   |

| 3.  | .1.   | Near-term Challenges                     | 4   |

| 3.  | 2.    | Long-term Challenges                     | 5   |

| 4.  | Tech  | nnology Requirements—Logic Technologies  | 6   |

| 4.  | .1.   | Ground Rules Scaling                     | 6   |

| 4.  | 2.    | Performance Boosters                     | 9   |

| 4.  | .3.   | Performance-Power-Area (PPA) Scaling     | 13  |

| 4.  | 4.    | System-On-Chip (SoC) PPA Metrics         | 15  |

| 4.  | .5.   | Interconnect Technology Requirements     | 17  |

| 4.  | .6.   | Device Reliability                       | 19  |

| 4.  | .7.   | 3D Heterogeneous Integration             | 22  |

| 4.  | .8.   | Defectivity Requirements                 | 23  |

| 5.  | Tech  | nnology Requirements—Memory Technologies | 24  |

| 5.  | .1.   | DRAM                                     | 24  |

| 5.  | .2.   | NVM—Flash                                | 24  |

| 5.  | .3.   | NVM—Emerging                             | 26  |

| 6.  | Pote  | ential Solutions                         | 29  |

| 7.  | Cros  | ss Teams                                 | 30  |

| 8.  | Con   | clusions and Recommendations             | 30  |

| 9   | Refe  | erences                                  | 31  |

# ii Acknowledgments

# **List of Figures**

| Figure MM-1   | Big data and instant data                                                                                                                                                                                        | 1   |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

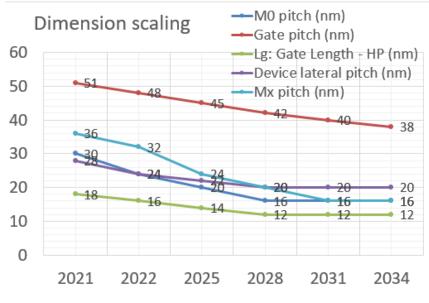

| Figure MM-2   | Projected scaling of key ground rules                                                                                                                                                                            |     |

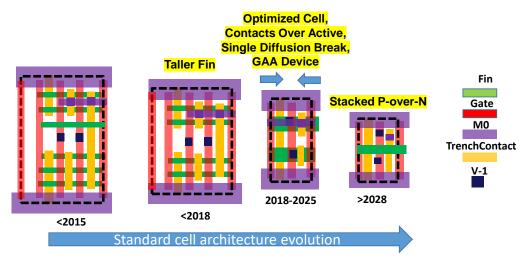

| Figure MM-3   | Scaling of standard cell height and width through fin depopulation and devertex stacking                                                                                                                         |     |

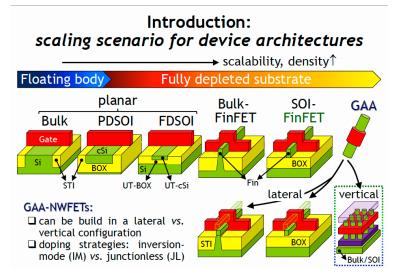

| Figure MM-4   | Planar to GAA transition [11]                                                                                                                                                                                    | 10  |

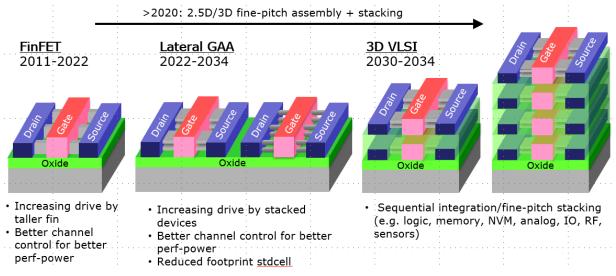

| Figure MM-5   | Evolution of device architectures in the IRDS More Moore roadmap                                                                                                                                                 | 10  |

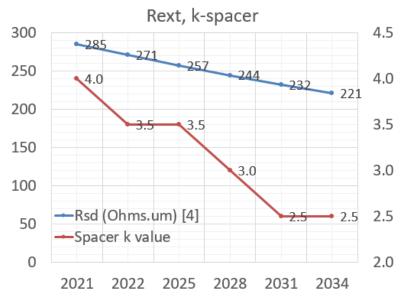

| Figure MM-6   | Scaling trend of device S/D access resistance (Rsd) and k-value of device spacer.[4]                                                                                                                             |     |

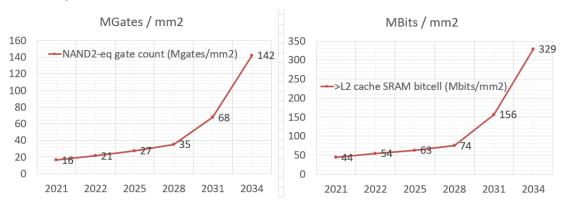

| Figure MM-7   | NAND2-equivalent standard cell count (left) and 111-bitcell (right) scaling 80mm <sup>2</sup> die                                                                                                                |     |

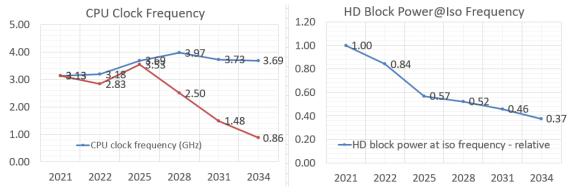

| Figure MM-8   | CPU clock frequency and power@iso- frequency (ref: 2021) scaling                                                                                                                                                 | 16  |

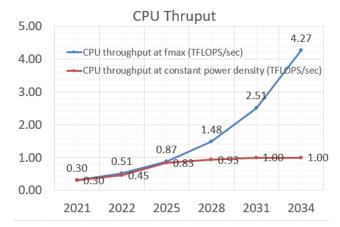

| Figure MM-9   | Scaling projection of computation throughput of CPU cores at the maximu frequency and at thermally constrained average frequency                                                                                 |     |

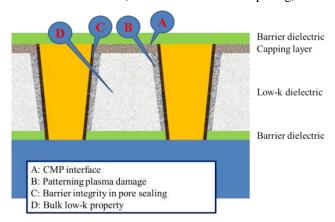

| Figure MM-10  | Degradation paths in low-к damascene structure                                                                                                                                                                   | 19  |

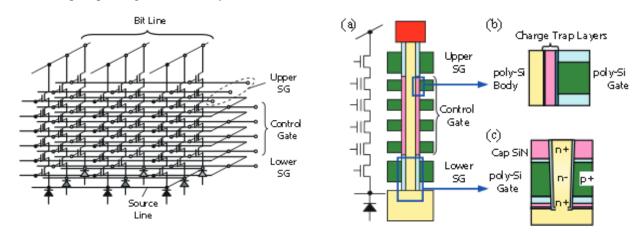

| Figure MM-11  | (left) A 3D NAND array based on a vertical channel architecture. (right) Bicost scalable) – a 3D NAND structure using a punch and plug process [41]                                                              | `   |

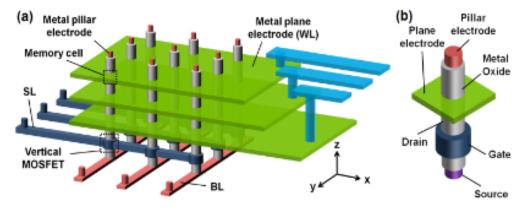

| Figure MM-12  | Schematic view of (a) 3D cross-point architecture using a vertical RRAM of (b) a vertical MOSFET transistor as the bit-line selector to enable the rand access capability of individual cells in the array [52]. | dom |

| List of Table | es                                                                                                                                                                                                               |     |

| Table MM-1    | More Moore—Logic Core Device Technology Roadmap                                                                                                                                                                  | 4   |

| Table MM-2    | More Moore—DRAM Technology Roadmap                                                                                                                                                                               | 4   |

| Table MM-3    | More Moore—Flash Technology Roadmap                                                                                                                                                                              | 4   |

| Table MM-4    | More Moore—NVM Technology Roadmap                                                                                                                                                                                | 4   |

| Table MM-5    | Difficult Challenges—Near-term                                                                                                                                                                                   | 4   |

| Table MM-6    | Difficult Challenges—Long-term                                                                                                                                                                                   | 5   |

| Table MM-7    | Device Architecture and Ground Rules Roadmap for Logic Devices                                                                                                                                                   | 7   |

| Table MM-8    | Device Roadmap and Technology Anchors for More Moore Scaling                                                                                                                                                     | 9   |

| Table MM-9    | Projected Electrical Specifications of Logic Core Device                                                                                                                                                         | 13  |

| Table MM-10   | Projected Performance-Power-Area (PPA) Metrics                                                                                                                                                                   | 14  |

| Table MM-11   | Power and Performance Scaling of SoC                                                                                                                                                                             | 16  |

| Table MM-12   | Interconnect Difficult Challenges                                                                                                                                                                                | 17  |

| Table MM-13   | Interconnect Roadmap for Scaling                                                                                                                                                                                 | 18  |

| Table MM-14   | Device Reliability Difficult Challenges                                                                                                                                                                          | 21  |

| Table MM-15   | Defectivity (D0) Requirements of an 80mm <sup>2</sup> Die                                                                                                                                                        | 24  |

| Table MM-16   | Potential Solutions—Near-term                                                                                                                                                                                    |     |

| Table MM-17   | Potential Solutions—Long-term                                                                                                                                                                                    | 29  |

# **ACKNOWLEDGMENTS**

# MORE MOORE TEAM

| U.S.A. & Canada       |                         |  |

|-----------------------|-------------------------|--|

| Anshul A. Vyas        | Applied Materials       |  |

| Arvind Kumar          | IBM                     |  |

| Bhagawan Sahu         | Global Foundries        |  |

| Charles Kin P. Cheung | NIST                    |  |

| Chorng-Ping Chang     | AMAT                    |  |

| Christopher Henderson | Semitracks              |  |

| Gennadi Bersuker      | Aerospace Corporation   |  |

| Gerhard Klimeck       | Purdue Univ.            |  |

| Huiming Bu            | IBM                     |  |

| James Stathis         | IBM                     |  |

| Jeongdong Cho         | Tech Insights           |  |

| Jim Fonseca           | Purdue Univ.            |  |

| Joe Brewer            | Univ. Florida           |  |

| Joel Barnett          | TEL                     |  |

| Kirk Prall            | Micron                  |  |

| Kwok Ng               | SRC                     |  |

| Lars Liebmann         | TEL                     |  |

| Masako Kodera         | Mosos Lake Industries   |  |

| Matthias Passlack     | TSMC                    |  |

| Mehdi Salmani         | Boston Consulting Group |  |

| Philip Wong           | Stanford Univ.          |  |

| Prasad Sarangapani    | Synopsys                |  |

| Qi Xiang              | Xilinx                  |  |

| Rich Liu              | Macronix                |  |

| SangBum Kim           | IBM                     |  |

| Saumitra Mehrotra     | NXP                     |  |

| Sergei Drizlikh       | Samsung                 |  |

| Siddharth Potbhare    | NIST                    |  |

| SungGeun Kim          | Microsoft               |  |

| Takeshi Nogami        | IBM                     |  |

| Wilman Tsai           | Stanford Univ.          |  |

| Witek Maszara         | V-tek Consulting        |  |

| Yanzhong Xu           | Microsoft               |  |

| Yuzo Fukuzaki         | Tech Insights           |  |

| ASIA                |                          |  |

|---------------------|--------------------------|--|

| Atsushi Hori        | Tokyo Inst of Technology |  |

| Digh Hisamoto       | Hitachi                  |  |

| Hajime Nakabasyashi | TEL                      |  |

| Hitoshi Wakabayashi | Tokyo Inst of Technology |  |

| Jiro Ida            | Kanazawa IT              |  |

| Kazuyuki Tomida     | Sony                     |  |

| Kunihiko Iwamoro    | ROHM                     |  |

| Kuniyuki Kakushima  | Tokyo Inst of Technology |  |

| Masahiko Ikeno      | Hitachi High-Tech        |  |

| Masami Hane         | Renesas                  |  |

| Shinichi Ogawa      | AIST                     |  |

| Shinichi Takagi     | University of Tokyo      |  |

| Takashi Matsukawa   | AIST                     |  |

| Tesuo Endo          | Tohoku University        |  |

| Tetsu Tanaka        | Tohoku University        |  |

| Toshiro Hiramoto    | University of Tokyo      |  |

| Yasuo Kunii         | Analysis Atelier         |  |

| Yasushi Akasaka     | TEL                      |  |

| Yoshihiro Hayashi   | Keio University          |  |

| Jongwoo Park        | Samsung                  |  |

| Moon-Young Jeong    | Samsung                  |  |

| Cheng-tzung Tsai    | UMC                      |  |

| Geoffrey Yeap       | TSMC                     |  |

| EUROPE                    |                        |  |

|---------------------------|------------------------|--|

| Christiane Le Tiec        | MKS Instruments        |  |

| Francis Balestra          | IMEP Grenoble          |  |

| Fred Kuper                | NXP                    |  |

| Gerben Doornbos           | TSMC                   |  |

| Herve Jaouen              | ST                     |  |

| Jurgen Lorenz             | Fraunhofer IISB        |  |

| Karim Cherkaoui           | Tyndall National Inst. |  |

| Kristin DeMeyer           | IMEC                   |  |

| Laurent Le-Pailleur       | ST                     |  |

| Malgorzata Jurczak        | LAM Research           |  |

| Mark van Dal              | TSMC                   |  |

| Mustafa Badaroglu (chair) | Qualcomm Technologies  |  |

| Olivier Faynot            | LETI                   |  |

| Paul Mertens              | IMEC                   |  |

| Peter Ramm                | Fraunhofer EMFT        |  |

| Ray Duffy                 | Tyndall National Inst. |  |

| Robert Lander             | NXP                    |  |

| Thierry Poiroux           | LETI                   |  |

| Yannick Le Tiec           | LETI                   |  |

# MORE MOORE

# 1. Introduction

System scaling enabled by Moore's scaling is increasingly challenged by the scarcity of resources such as power and interconnect bandwidth. This has become more challenging under the requirements of seamless interaction between big data and instant data (Figure MM-1). Instant data generation requires ultra-low-power devices with an "always-on" feature at the same time with high-performance devices that can generate the data instantly. Big data requires abundant computing, communication bandwidth, and memory resources to generate the service and information that clients need.

The More Moore International Focus Team (IFT) of the International Roadmap of Devices and Systems (IRDS) provides physical, electrical, and reliability requirements for logic and memory technologies to sustain power, performance, area, cost (PPAC) scaling for big data, mobility, and cloud (e.g., Internet-of-Things (IoT) and server) applications. This is done over a time horizon of 15 years for mainstream/high-volume manufacturing (HVM).

Figure MM-1 Big data and instant data

Following systems drivers is forecasted to impact the More Moore logic technologies:

#### Mobile

- Heterogenous integration

- Edge computing

- Extreme reality (VR/AR)

- Edge-AI (mobile phone, smart cameras/speakers)

Data and HPC servers – cache integration, memory, IO

- AI accelerators in enterprise/cloud

- Codec ASICs 24/7/365 continuous run of video and audio (codec), 5 years minimum time

- Networking Always-on, 500W power envelope

- Advanced driver assistance system (ADAS) chips Autonomous driving

- Memory and IO solutions for AI, graphics, HPC

#### Novel compute fabrics

- Neural processing unit

- Fine-pitch 3D stacking

#### 2 Introduction

- Reconfigurable compute fabrics

- Smart 2.5D interposers

#### 1.1. CURRENT STATE OF TECHNOLOGY

A major portion of semiconductor device production is devoted to digital logic that needs to support a technology platform for two device types: 1) high-performance logic, and 2) low-power/high-density logic. Key considerations for this technology platform are speed, power, density, and cost. The More Moore roadmap provides an enablement view for continued scaling of MOSFETs in order to maintain historical trends of improved device performance at reduced power and cost.

## 1.2. DRIVERS AND TECHNOLOGY TARGETS

The following applications drive the requirements of More Moore technologies that are addressed in the IRDS [1]:

- High-performance computing—more performance at constant power density (constrained by thermal)

- Mobile computing—more performance and functionality at constant energy (constrained by battery) and cost

- Autonomous sensing and computing (IoT)—targeting reduced leakage and variability

Technology drivers include following focal items:

- Logic technologies

- Ground rule scaling

- Performance boosters

- Performance-power-area (PPA) scaling

- 3D integration

- Memory technologies

- DRAM technologies

- Flash technologies

- Emerging non-volatile-memory (NVM) technologies

More Moore targets bringing PPAC value for node scaling every 2–3 years [2]:

- (P)erformance: >15% more operating frequency at scaled supply voltage

- (P)ower: >30% less energy per switching at a given performance

- (A)rea: >30% less chip area footprint

- (C)ost: <30% more wafer cost 15% less die cost for scaled die.

System scaling considers the co-integration of logic, memory and IO solutions bringing the following targets:

- 2x scaling of TOPSxTOPS/W for node scaling per frame, per inference, per training, and/or per Pocket

- TOPSxTOPS/W is an indicator of Energy-efficient performance (aka EDP: Energy Delay Product)

- TOPS (Tera Operations per Second): Throughput

- TOPS/W (TOPS per Watt): Energy efficiency

These scaling targets have driven the industry toward a number of major technological innovations, including material and process changes such as high- $\kappa$  gate dielectrics and strain enhancement, and in the near future, new structures such as gate-all-around (GAA); alternate high-mobility channel materials, and new 3D integration schemes allowing heterogeneous stacking/integration. These innovations will be introduced at a rapid pace, and hence understanding, modeling, and implementation into manufacturing in a timely manner is crucial for the industry.

It is important to note that both cost metric (15% less die cost) and market cadence necessitating new products every year are becoming more important targets in the mobile industry. As the applications strictly requiring all figure-of-merits (FoMs) are concurrently met, it is necessary to advance an effective list of process technologies for sustaining certain device architectures to their limits, such as pushing the finFET architecture for the next five years. This approach will also help in sustaining the cost at reduced risk while moving from one logic generation to another. This becomes more

difficult whenever the cost of wafer processing becomes more expensive with the increased number of steps because of multiple patterning lithography steps. However, we need to reduce the cost by more than 15% for the same of number of transistors, which can only be enabled by pitch scaling enabled by new advancements in channel material, device architecture, contact engineering, and device isolation. Increased process complexity must also be taken into account for the overall die yield. In order to compensate the cost of complexity, acceleration in design efficiency is needed to further scale the area to reach the die-cost scaling targets. These design-induced scaling factors were also observed in the earlier work of the System Drivers Technology Workgroup of ITRS and those were used as calibration factors to match the area scaling trends of the industry [2]. The design scaling factor is now considered as one of the key elements in this edition of More Moore technology roadmap.

# 2. SUMMARY AND KEY POINTS

The following are forecasted in the projected IRDS More Moore roadmap:

- Ground rule scaling is expected to slow down and saturate around 2028. Extreme-ultraviolet (EUV) technology

will be the enabler of ground rule scaling while keeping the cost under control and providing process complexity

reduction. Transition to 3D integration and use of beyond CMOS devices for complementary System-on-Chip

(SoC) functions are projected after 2028.

- Ground-rule scaling needs to be accompanied with the design-technology-co-optimization (DTCO) constructs

that accommodate the area reduction as well as tightening the critical design rules that limit the overall SoC area

scaling.

- A main challenge in 3D integration is how to partition the system to come up with better utilization of devices, interconnect, and sub-systems such as memory, analog, and input/output (I/O). Parasitics improvement will become a major knob for performance improvement for nodes spanning between 2021 and 2028, such as with the introduction of low-κ device spacer.

- SiGe and Ge channels are gaining importance as the high-mobility channels. III-V channel faces challenges of variability, band-to-band tunneling, and large investments in fab infrastructure.

- It becomes increasingly difficult to control interconnect resistance, electromigration (EM), and time-dependent-dielectric-breakdown (TDDB) limits. Interconnect resistance has now entered an exponential increase regime because of non-ideal scaling of barriers for Cu bringing less metallization volume and increased scattering at the surface and grain-boundary interfaces. Therefore, there is a need for new barrier materials and/or Cu alternative solutions. In addition to the resistance scalability, TDDB is putting a limit on the minimum space between the adjacent lines for a given low-κ dielectric, forcing a slow-down in the permittivity (κ-value) scaling.

- Performance across six nodes spanning from 2021 to 2034 is forecasted to improve on average for wireloaded datapaths, most of improvements taking place between 2021 and 2028, but it is forecasted to get worse after 2028.

- System-on-chip (SoC) level area across six nodes spanning from 2021 to 2034 is forecasted to improve, but less than 30%, node-to-node on average.

- Clocking frequency at nominal supply voltage is forecasted to be improve from 3.1 GHz in 2021 to 3.9 GHz in 2028, and 3.7 GHz at the end of this roadmap edition's timeframe (in 2034). This limited scaling is because of increasing parasitics, particularly interconnect resistance, and limited gate drive (Vgs-Vt) as a result of supply voltage scaling. Power density poses a significant challenge for scaling, particularly as a result of 3D integration after 2031. Therefore, it is necessary to factor in thermal considerations in device and architectures.

- Energy per switching reduction is expected to be limited less than 20% in a node-to-node basis on average. This is a critical challenge of scaling because of a slow-down in capacitance and supply voltage reduction.

- DRAM needs to maintain sufficient storage capacitance and adequate cell transistor performance is required to keep the retention time characteristic in the future. If efficiency of cost scaling becomes poor in comparison with introducing the new technology, DRAM scaling will be stopped, and 3D cell stacking structure will be adopted. Alternatively, a new DRAM concept could be adopted.

- 2D Flash memory density cannot be increased indefinitely by continued scaling of charge-based devices because

of controllability limits of threshold voltage distribution. Flash density increase will continue by stacking

memory layers vertically, leading to adoption of 3D Flash technology. Decrease in array efficiency due to

increased interconnection and yield loss from complex processing are challenges for further reducing the cost-

#### 4 Challenges

- per-bit benefit. Currently, 96 layers are already at volume production and there is optimism that 128 layers are achievable, with 192 and 256 layers possible.

- Ferroelectric RAM (FeRAM) is a fast, low power, and low voltage non-volatile memory (NVM) alternative and thus is sui for radio frequency identification (RFID), smart card, ID card, and other embedded applications. Processing difficulty limits its wider adoption. Recently, HfO<sub>2</sub>-based ferroelectric field-effect transistor (FET), for which the ferroelectricity serves to change the threshold voltage (Vt) of the FET and thus can form a 1T cell similar to Flash, has been proposed. If developed to maturity, this may serve as a low-power and very fast, Flash-like memory.

- Spin-transfer torque-magnetic RAM (STT-MRAM) to replace the stand-alone NAND Flash seems remote. However, its SRAM-like performance and much smaller footprint than the conventional 6T-SRAM have gained much interest in that application, especially in mobile devices that do not require high cycling endurance. Therefore, STT-MRAM is now mostly considered not as a standalone memory but an embedded memory. STT-MRAM would also be a potential solution for embedded Flash (NOR) replacement. This may be particularly interesting for low-power IoT applications. On the other hand, for other embedded systems applications using higher memory density, NOR Flash is expected to continue to dominate, since it is still substantially more cost-effective and well established for being able to endure the printed circuit board (PCB) soldering process (at ~250°C) without losing its preloaded code.

- 3D crosspoint memory has been demonstrated for the storage class memory (SCM) to improve I/O throughput and reduce power and cost. Since the memory including the selector device is completely fabricated in the backend-of-line (BEOL) process it is relatively inexpensive to stack multiple layers to reduce bit cost.

- High-density resistive RAM (ReRAM) development has been limited from the lack of a good selector device, since simple diodes have limited operation ranges. Recent advances in 3D cross point memory, however, seem to have solved this bottleneck and ReRAM could make rapid progress if other technical issues, such as erratic bits, are solved.

The links to the tables of technology roadmaps for Logic Core Device, DRAM, Flash, and NVM are below:

| Table MM-1 | More Moore—Logic Core Device Technology Roadmap |

|------------|-------------------------------------------------|

| Table MM-2 | More Moore—DRAM Technology Roadmap              |

| Table MM-3 | More Moore—Flash Technology Roadmap             |

| Table MM-4 | More Moore—NVM Technology Roadmap               |

# 3. CHALLENGES

The goal of the semiconductor industry is to be able to continue to scale the technology in overall performance at reduced power and cost. The performance of the components and the final chip can be measured in many different ways: higher speed, higher density, lower power, more functionality, etc. Traditionally, dimensional scaling had been adequate to bring about these aforementioned performance merits, but it is no longer the case. Processing modules, tools, material properties, etc., are presenting difficult challenges to continue scaling. We have identified these difficult challenges and summarized in Table MM-5 and Table MM-6. These challenges are divided into near-term 2021-2025 (Table MM-5) and long-term 2026-2034 (Table MM-6).

# 3.1. NEAR-TERM CHALLENGES

| Table MM-5   | Difficult Challenges—Near-term  |

|--------------|---------------------------------|

| Table Mini-3 | Difficult Challenges—Near-letin |

| Near-Term<br>Challenges:<br>2021-2025 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Power scaling                         | Voltage and capacitance scaling slow down and lack of solutions for power reduction.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                       | Introduction of gate-all-around (GAA) devices is a remedy to reduce the supply voltage, but not in a sustained manner that allows continuous scaling. Power scaling is also limited because of slow-down of loading capacitance scaling. This loading capacitance is becoming increasingly impacted by the parasitic components of the device with continuous scaling of ground rules. Therefore, an introduction of low-κ materials, design-technology-co-optimization (DTCO) introducing new |  |

| Near-Term<br>Challenges:<br>2021-2025 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | contact access schemes, as well as local interconnect schemes that allow lower parasitics, is needed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Parasitics                            | Maintaining control of increased parasitics in stacked devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| scaling                               | Stacked devices require high-aspect ratio contacts to access the bottom contact. This will increase both the contact resistance as well as the fringe capacitance between the gate and drain/source. Interface resistance will also require new silicidation schemes that conformally wrap the source/drain.                                                                                                                                                                                                                                                                                                      |

| Cost reduction                        | Cost-effective area scaling through EUV and DTCO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                       | Throughput and yield challenges of EUV necessitate a careful selection of ground rules that optimize the die cost as a significant part of cost is determined by the middle-of-line (MOL) and BEOL stack. Therefore, new process-enhanced design constructs that tighten the secondary design rules such as tip-to-tip and the P-N separation rule are necessary to allow a further shrink of the standard cell and bitcell area on top of ground rule scaling for low-cost die. Process integration of those design constructs might require new materials to allow better etch selectivity and self-deposition. |

| Integration enablement for            | Bitcell scaling is slowing down because of the slow-down of the device (e.g., fin) pitch and gate pitch (i.e., contacted poly pitch (CPP)).                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SRAM-cache applications               | New device schemes such as P-over-N stacked device or vertical devices bring an opportunity to significantly reduce the SRAM area. This is enabled because of optimized layouts that eliminate the critical design rules impacting the area.                                                                                                                                                                                                                                                                                                                                                                      |

|                                       | Option of embedded NVM in high-performance logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                       | Being able to integrate most of emerging memories (e.g., MRAM) at the interconnect stack also bring an opportunity for high-density memories. However, the stack as well as the materials should be compatible with BEOL.                                                                                                                                                                                                                                                                                                                                                                                         |

| Interconnect                          | Maintaining control of interconnect resistance and EM and TDDB limits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| scalability                           | Interconnect resistance has now entered an exponential increase regime because of non-ideal scaling of the barrier for Cu and increased scattering at the surface and grain-boundary interfaces. Therefore, there is a need for new barrier materials and Cu alternative solutions. In addition to resistance scalability, TDDBis putting a limit on the minimum space between the adjacent lines for a given low- $\kappa$ dielectric.                                                                                                                                                                           |

# 3.2. LONG-TERM CHALLENGES

Table MM-6 Difficult Challenges—Long-term

| Long-Term<br>Challenges:<br>2026-2034 | Description                                                                                                                                                                                                                                                                 |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power scaling                         | Power scaling—no solutions are left besides steep-subthreshold (SS) devices to enable complementary SoC functions bringing power reduction but replacing mainstream CMOS.                                                                                                   |

|                                       | However, most of steep-SS device candidates do not bring an adequate performance comparable to CMOS at nominal supply voltages. In order to maximize the performance of steep-SS device, new architectures are necessary to attain the performance through parallelization. |

| Use cases of vertical device          | Performance scaling and functional diversification with vertical devices and new architectures.  Using vertical devices at conventional logic and architectures will raise routing congestion and                                                                           |

## 6 Technology Requirements—Logic Technologies

| Long-Term<br>Challenges:<br>2026-2034                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| structures                                                 | increased parasitics. There is a need for new logic schemes and architectures that maximize the advantage of 3D capability.                                                                                                                                                                                                                                                                                                                                                 |

| Thermal issue due to increased power density               | Thermal challenges (e.g., power density and dark silicon) of 3D stacking.  Gate-all-around (GAA) devices have limited heat conductance due to confined architecture. Increased pin density due to aggressive standard cell height scaling and increased drive by stacked devices put a significant pressure on the power density.                                                                                                                                           |

| Cost reduction<br>with 3D<br>integration                   | Managing cost, yield, and process complexity of 3D integration.  Using vertical devices separated by the interconnect significantly increases the wafer cost and the number of masks (i.e., process complexity) adding pressure to the defectivity (e.g., D0) control. Architectures need to be refined for reducing the interconnect complexity between tiers as well as simplified integration and function per tier (e.g., I/O in one tier, SRAM in another tier, etc.). |

| Integration of<br>non-Cu<br>metallization to<br>replace Cu | Adoption of non-Cu interconnects for low-resistance, meeting EM/TDDB, and temperature budget compatibility with devices used in 3D integration.                                                                                                                                                                                                                                                                                                                             |

# 4. TECHNOLOGY REQUIREMENTS—LOGIC TECHNOLOGIES

# 4.1. GROUND RULES SCALING

The More Moore roadmap focuses on effective solutions to sustain the performance and power scaling at scaled dimensions and scaled supply voltage. Ground rule scaling drives die-cost reduction. However, this scaling increases the portion of parasitics in the total loading and brings diminishing returns of scale in performance and power scaling. Therefore, it is necessary to focus on technology scaling solutions that also scale the parasitics of device and interconnect. Ground-rule scaling needs to also enable DTCO constructs that accommodate the area reduction as well as tighten the critical design rules that limit the area scaling. Due to the rising costs and process complexity of multiple patterning, EUV is used as a remedy to pattern-tight ground rules in fewer process steps. The projected roadmap of ground rules as well as device architectures is shown in Table MM-7. Evolution of ground rules in shown Figure MM-2. There is not yet a consensus on the node naming across different foundries and integrated device manufacturers (IDMs); however, the projected rules give an indication of technology capabilities in line with the PPAC requirements. Key parameters in the ground rules are the gate pitch, metal pitch, fin pitch, and gate length, which are important factors in core logic area scaling.

Table MM-7 Device Architecture and Ground Rules Roadmap for Logic Devices.

Note: GxxMxx/Tx notation refers to Gxx: contacted gate pitch, Mxx: tightest metal pitch in nm, Tx: number of tiers. This notation illustrates the technology pitch scaling capability. On top of pitch scaling there are other elements such as cell height, fin depopulation, DTCO constructs, 3D integration, etc. that define the target area scaling (gates/mm²).

| YEAR OF PRODUCTION                                              | 2021   | 2022           | 2025        | 2028        | 2031        | 2034        |

|-----------------------------------------------------------------|--------|----------------|-------------|-------------|-------------|-------------|

|                                                                 | G51M30 | G48M24         | G45M20      | G42M16      | G40M16/T2   | G38M16/T4   |

| Logic industry "Node Range" Labeling (nm)                       | "5"    | "3"            | "2.1"       | "1.5"       | "1.0 eg"    | "0.7 eg"    |

| IDM-Foundry node labeling                                       | i7-f5  | i5-f3          | i3-f2.1     | i2.1-f1.5   | i1.5e-f1.0e | i1.0e-f0.7e |

| Logic device structure options                                  | FinFET | finFET<br>LGAA | LGAA        | LGAA        | LGAA-3D     | LGAA-3D     |

| Platform device for logic                                       | finFET | finFET         | LGAA        | LGAA        | LGAA-3D     | LGAA-3D     |

|                                                                 | Öxide  | Öxide          | Oxide       | Oxide       | Oxide       | Oxide       |

| LOGIC DEVICE GROUND RULES                                       |        |                |             |             |             |             |

| Mx pitch (nm)                                                   | 36     | 32             | 24          | 20          | 16          | 16          |

| M1 pitch (nm)                                                   | 34     | 32             | 23          | 21          | 20          | 19          |

| M0 pitch (nm)                                                   | 30     | 24             | 20          | 16          | 16          | 16          |

| Gate pitch (nm)                                                 | 51     | 48             | 45          | 42          | 40          | 38          |

| Lg: Gate Length - HP (nm)                                       | 18     | 16             | 14          | 12          | 12          | 12          |

| Lg: Gate Length - HD (nm)                                       | 20     | 18             | 14          | 12          | 12          | 12          |

| Channel overlap ratio - two-sided                               | 0.20   | 0.20           | 0.20        | 0.20        | 0.20        | 0.20        |

| Spacer width (nm)                                               | 7      | 6              | 5           | 4           | 4           | 4           |

| Contact CD (nm) - finFET, LGAA                                  | 19     | 20             | 21          | 22          | 20          | 18          |

| Contact CD (nm) - VGAA                                          |        |                |             |             |             |             |

| Device architecture key ground rules                            |        |                |             |             |             |             |

| FinFET pitch (nm)                                               | 28.0   | 24.0           |             |             |             |             |

| FinFET Fin width (nm)                                           | 6.0    | 5.0            |             |             |             |             |

| FinFET Fin height (nm)                                          | 50     | 64             |             |             |             |             |

| Footprint drive efficiency - finFET                             | 3.79   | 5.54           | 22.0        | 20.0        | 20.0        | 20.0        |

| Lateral GAA lateral pitch (nm)  Lateral GAA vertical pitch (nm) |        |                | 22.0        | 20.0        | 20.0        | 20.0        |

| Lateral GAA (nanosheet) thickness (nm)                          |        |                | 18.0<br>7.0 | 16.0<br>6.0 | 14.0<br>5.0 | 14.0<br>5.0 |

| Number of vertically stacked nanosheets                         |        |                | 3           | 3           | 4           | 5.0<br>4    |

| LGAA width (nm) - HP                                            |        |                | 30          | 25          | 20          | 15          |

| LGAA width (nm) - HP                                            |        |                | 15          | 11          | 6           | 6           |

| LGAA width (nm) - SRAM                                          |        |                | 7           | 6           | 6           | 6           |

| LGAA total height (nm)                                          |        |                | 53          | 48          | 57          | 57          |

| Footprint drive efficiency - lateral GAA - HP                   |        |                | 4.93        | 4.77        | 5.88        | 5.52        |

| Device effective width (nm) - HP                                | 106.0  | 133.0          | 222.0       | 186.0       | 200.0       | 160.0       |

| Device effective width (nm) - HD                                | 106.0  | 133.0          | 132.0       | 102.0       | 88.0        | 88.0        |

| Device lateral pitch (nm)                                       | 28     | 24             | 22          | 20          | 20          | 20          |

| Device height (nm)                                              | 50.0   | 64.0           | 53.0        | 48.0        | 57.0        | 57.0        |

| Device width (nm) - HP                                          | 6      | 5              | 30          | 25          | 20          | 15          |

| Device width (nm) - HD                                          | 6      | 5              | 15          | 11          | 6           | 6           |

| Device width (nm) - SRAM                                        | 6      | 5              | 7           | 6           | 6           | 6           |

$A cronyms\ used\ in\ the\ table\ (in\ order\ of\ appearance):\ LGAA-lateral\ gate-all-around-device\ (GAA),\ 3DVLSI-fine-pitch\ 3D\ logic\ sequential\ integration.$

Figure MM-2 Projected scaling of key ground rules

Ground rule scaling alone is not adequate to scale the cell height. It is necessary to bring the design scaling factor into practice [2][3]. For example, standard cell height will be further reduced by scaling the number/width of active devices in the standard cell as well as scaling the secondary rules such as tip-to-tip, extension, P-N separation, and minimum area rules. Similarly, the standard cell width can be reduced by focusing on critical design rules such as fin termination at the edge fin, etc., and enabling structures such as contact-over-active [4][5][6]. Also, the contact structure needs to be carefully selected to reduce the risk of increased current density at the junctions. It is expected that in 2028 P and N devices could be stacked on top of each other allowing a further reduction. This trend in standard cell scaling is shown in Figure MM-3.

Figure MM-3 Scaling of standard cell height and width through fin depopulation and device stacking

After 2031 there is no room for 2D geometry scaling, where 3D very large scale integration (VLSI) of circuits and systems using sequential/stacked integration approaches will be necessary. This is due to the fact that there is no room for contact placement as well as worsening performance as a result of gate pitch scaling and metal pitch scaling. It is projected that physical channel length would saturate around 12nm due to worsening electrostatics while gate pitch would saturate at 38nm to reserve sufficient width (~14nm) for the device contact, providing acceptable parasitics. 3D VLSI expects to bring PPAC gains for the target node as well as to pave ways for heterogeneous and/or hybrid integration. The challenge of such integration in 3D is how to partition the system to come up with better utilization of devices, interconnects, and sub-systems such as memory, analog, and I/O. That is why the functional scaling and/or significant

architectural changes are required after 2031. This would potentially be the time where Beyond CMOS and specialty technology devices/components would bring up the system scaling towards high system performance at unit power density and at unit cube volume

#### 4.2. Performance Boosters

In the early years before the 130nm node, transistors enjoyed Dennard scaling where equivalent oxide thickness (EOT), transistor gate length (Lg) and transistor width (W) were all scaled by a constant factor in order to provide a delay improvement at constant power density. Nowadays there are numerous input parameters that can be varied, and the output parameters are complicated functions of these input parameters. Other sets of projected parameter values (i.e., different scaling scenarios) may be found to achieve the same target. In order to maintain the scaling at low voltages, scaling in recent years focused on additional solutions to boost the performance such as the use of introducing strain to channel; stress boosters; high-κ metal gate; lowering contact resistance, and improving electrostatics. This was all done in order to compensate the gate drive loss while supply voltage needs to be scaled down for high-performance mobile applications.

A roadmap overview of device architecture, key modules, and performance boosters is shown in Table MM-8.

Table MM-8 Device Roadmap and Technology Anchors for More Moore Scaling.

| YEAR OF PRODUCTION                                   | 2021                            | 2022                                     | 2025                                     | 2028                                                                   | 2031                                                            | 2034                                          |

|------------------------------------------------------|---------------------------------|------------------------------------------|------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------|

|                                                      | G51M30                          | G48M24                                   | G45M20                                   | G42M16                                                                 | G40M16/T2                                                       | G38M16/T4                                     |

| Logic industry "Node Range" Labeling (nm)            | "5"                             | "3"                                      | "2.1"                                    | "1.5"                                                                  | "1.0 eq"                                                        | "0.7 eq"                                      |

| IDM-Foundry node labeling                            | i7-f5                           | i5-f3                                    | i3-f2.1                                  | i2.1-f1.5                                                              | i1.5e-f1.0e                                                     | i1.0e-f0.7e                                   |

| Logic device structure options                       | FinFET                          | finFET<br>LGAA                           | LGAA                                     | LGAA                                                                   | LGAA-3D                                                         | LGAA-3D                                       |

| Platform device for logic                            | finFET                          | finFET                                   | LGAA                                     | LGAA                                                                   | LGAA-3D                                                         | LGAA-3D                                       |

| Frequency scaling - node-to-node                     | -                               | 0.02                                     | 0.16                                     | 0.09                                                                   | -0.08                                                           | -0.01                                         |

| CPU frequency at constant power density (GHz)        | 3.13                            | 2.83                                     | 3.53                                     | 2.50                                                                   | 1.48                                                            | 0.86                                          |

| Power at iso frequency - node-to-node                | -                               | -0.16                                    | -0.27                                    | -0.05                                                                  | -0.06                                                           | -0.08                                         |

| Power density - relative                             | 1.00                            | 1.12                                     | 1.04                                     | 1.59                                                                   | 2.51                                                            | 4.27                                          |

| LOGIC TECHNOLOGY ANCHORS                             |                                 |                                          |                                          |                                                                        |                                                                 |                                               |

| Patterning technology inflection for Mx interconnect | 193i, EUV DP                    | 193i, EUV DP                             | 193i, EUV DP                             | 193i, High-NA<br>EUV                                                   | 193i, High-NA<br>EUV                                            | 193i, High-NA<br>EUV                          |

| Beyond-CMOS as complimentary to platform CMOS        | -                               | -                                        | -                                        | 2D Device,<br>FeFET                                                    | 2D Device,<br>FeFET                                             | 2D Device,<br>FeFET                           |

| Channel material technology inflection               | SiGe25%                         | SiGe50%                                  | SiGe50%                                  | Ge, 2D Mat                                                             | Ge, 2D Mat                                                      | Ge, 2D Mat                                    |

| Process technology inflection                        | Conformal<br>Doping,<br>Contact | Channel, RMG                             | Lateral/Atomic<br>Etch                   | Non-Cu Mx                                                              | 3DVLSI                                                          | 3DVLSI                                        |

| Stacking generation inflection                       | <b>2</b> D                      | 3D-stacking:<br>W2W, D2W<br>Mem-on-Logic | 3D-stacking:<br>W2W, D2W<br>Mem-on-Logic | 3D-stacking,<br>Fine-pitch<br>stacking, P-<br>over-N, Mem-<br>on-Logic | 3D-stacking,<br>3DVLSI:<br>Mem-on-Logic<br>with<br>Interconnect | 3D-stacking,<br>3DVLSI:<br>Logic-on-<br>Logic |

Mx—tight-pitch routing metal interconnect.

FinFET still remains the key device architecture that could sustain scaling until 2025 [4][6]. Electrostatics and fin depopulation (i.e., increasing fin height while reducing number of fins at unit footprint area) remain as the two effective solutions to improve performance. Parasitics improvement is expected to stay as a major knob for performance improvement as a result of tightening design rules. It is forecasted that the parasitics will remain as a dominant term in the performance of critical paths. For reduced supply voltage, a transition to GAA structures such as lateral nanosheets would be necessary to sustain the gate drive by improved electrostatics [8]. Lateral GAA structure would eventually evolve in hybrid form with the vertical GAA structure to gain back the performance loss due to increasing parasitics at tighter pitches as well as for specialized SoC functions such as memory selector. Sequential integration would allow stacking of devices on top of each other with the adoption of monolithic 3D (M3D) integration [9]. Scaling focus will shift from single-thread performance gain to power reduction and then evolve onto highly-parallel 3D architectures allowing low Vdd operation and more functions embedded at unit cube volume.

While device architectures are seeing changes, subsequent modules are expected to also evolve. These may include: 1) starting substrates such as Si to silicon-on-insultator (SOI) and strain-relaxation-buffer (SRB); 2) channel material evolving from Si to SiGe, Ge, IIIV; 3) contact module evolving from silicides to novel materials providing lower Schottky barrier height (SBH) and to wrap-around contact integration schemes to increase the contact surface area. Below is a list of these schemes.

#### 4.2.1. Transition to new device architectures

As mentioned earlier finFET is likely to sustain until 2025. Beyond 2022 a transition to lateral GAA devices is expected to start and potentially include vertical GAA devices in hybrid form with the lateral GAA, potentially for 3D hybrid memory-on-logic applications. This situation would be due to the limits of fin-width scaling (saturating the Lgate scaling to sustain the electrostatics control) and contact width. Parasitic capacitance penalty, effective drive width (Weff), and replacement metal gate (RMG) integration pose challenges in GAA adoption. One compromise solution could be the electrically GAA (EGAA) architecture with much reduced parasitic capacitance and increased effective width for better short channel control and stronger drive [10]. Projected evolution of device architectures is shown in Figure MM-54 and Figure MM-5. FinFET and GAA architectures are leading not only to fully depleted channels but also to fully inverted channels (volume inversion).

Figure MM-4 Planar to GAA transition [11].

Figure MM-5 Evolution of device architectures in the IRDS More Moore roadmap

#### 4.2.2. Starting Substrate

Bulk silicon will still remain the mainstream substrate while silicon-on-insulator (SOI) and strain-relaxation-buffer (SRB) will be used to support better isolation (e.g., RF co-integration) and defect-free integration of high-mobility channels, respectively.

# 4.2.3. High-mobility channels

High-mobility materials such as Ge and III-V bring promise in increasing drive current by means of an order of magnitude increase in intrinsic mobility. With the scaling in gate length, the impact of mobility on drain current becomes limited because of the velocity saturation. On the other hand, whenever gate length further scales down, the carrier transport becomes ballistic. This allows velocity of carriers, also known as "injection velocity," scaling with the mobility increase. Having drain current mostly ballistic increases the injection velocity because of lower effective mass, therefore results in increase of the drain current. However, low effective mass for the high mobility device can actually cause high tunneling current at higher supply voltage. This may degrade the effective performance of III-V devices at short channel after work function tuning (e.g., threshold voltage increase) to lower the leakage current (Ioff) to compensate for the tunneling current.

Another consideration for high mobility channel is the lower density of states. The current is proportional to the multiplication of drift velocity and carrier concentration in the channel [11]. This requires a correct selection of gate length (Lg), supply voltage (Vdd), and device architecture in order to maximize this multiplication, where the selection of those parameters will be different for the type of channel material used. This all needs to be holistically tackled [12][13]. A shift in the centroid of charge away from the gate potential adds to the equivalent oxide thickness (EOT), reducing the inversion capacitance, particularly in III-V high-mobility channels. Despite the fact that drive current of III-V might not be that high, the overall delay merit (CV/I) result can be better than Si and other high-mobility channels (e.g., Ge). On the other hand, Vt variability due to channel dimensions and composition appears to become a major impediment in using III-V channel material in scaled devices. Bandgap and thus Vt arehighly modulated by body thickness due to quantum confinement effects for device with body thickness/diameter around 5-6 nm. Si and Ge appear to have much less sensitivity to such channel dimension variations. Also the impact of chemical composition variation in ternary III-V, like InGaAs, might also cause Vt variation. Indium % change impacts bandgap, which also impacts Vt. The cost factor should also be considered, such as the requirement of new tools as well as an infrastructure for dealing with potentially toxic waste requiring substantial investment in new fabs. Thus, the improved performance needs to be weighed against the cost, as this could be a greater factor compared to other solutions.

It is likely that high-mobility channels will be used in sequential integration to co-integrate high-speed IOs, RF (e.g. 5G and beyond), and photonics co-integration.

# 4.2.4. Strain engineering

Strain engineering has been used as one of the most effective solutions in the last decade, as illustrated for the 32nm node and earlier [14]. However, the effect of those stressors may not extrapolate intuitively into newer nodes. With the scaling down of gate pitch, SiGe on the source/drain epitaxial (S/D EPI) contact and strain relaxation buffer (SRB) remain as effective boosters to scale mobility more than double on top of high-mobility channel material [15]. SiGe channel for PMOS and strained Si channel for NMOS has been successfully demonstrated on a 7nm CMOS platform using SRB [16]. On the other hand, SRB or S/D stressors may not be useful for channel stress generation in vertical devices. Other strain engineering techniques also contain gate stressor and ground plane stressors, which adopt the beneficiary vertical stress components for NMOS. Compressively strained SiGe channel is also shown in ultra-thin body and buried oxide fully depleted SOI (UTBB FDSOI) in order to boost pFET performance [17][18]. A high level of stress is maintained in the channel due to the planar configuration (with low aspect ratio, compared to finFET). Combined with the use of back-bias (to reduce Vdd and thus the dynamic power), it enables high-performance, low-power circuits on UTBB FDSOI.

#### 4.2.5. Reducing parasitic device resistance

Controlling source/drain series resistance within tolerable limits will become increasingly difficult. Due to the increase of current density, the demand for lower resistance with smaller dimensions at the same time poses a great challenge. It is estimated that in current technologies, series resistance degrades the saturation current by 40% or more. External resistance impact on the drive current is expected to become worse with the gate pitch scaling. In addition, increasing interconnect resistance by scaling is expected to necessitate much lower resistance values for the device contact. In order to maximize the benefits of high-mobility channels in the drain current, it becomes much more important to reduce the contact resistance. Silicide contacts are failing to maintain the required reduction of contact resistance with the gate pitch scaling and decreasing channel resistance with improved drive. One promising reduction is achieved by metal-insulator-semiconductor (MIS) contacts, which utilize an ultra-thin dielectric between the metal and semiconductor interface. This reduces the Fermi-level pinning and therefore reduces the Schottky Barrier Height (SBH) [19][20]. This SBH reduction occurs from the exponential decay of the metal induced gap states (MIGS) inducing charge density accumulation in the bandgap of the dielectric.

# 4.2.6. Reducing parasitic device capacitance

Parasitic capacitance between gate and source/drain terminal of the device is expected to increase with technology scaling. In fact, this component is getting more important than channel-capacitance-related loading whenever the standard cell context is considered and even more elevated in the GAA structures as a result of unused space between stacked devices. There is a need to focus on low-κ spacer materials and even air spacer. Those still need to provide good reliability and etch selectivity for S/D contact formation [21][22]. Also, there are significant limits in increasing finFET or lateral GAA device AC performance by increasing the height of the device (fin/nanosheet stack). Energy per switch vs. delay relationship seems to quickly saturate and then decline with increasing device height. Scaling trend of key parasitic improvements is shown Figure MM-6.

Figure MM-6 Scaling trend of device S/D access resistance (Rsd) and k-value of device spacer.[4]

Note: Rsd is the total parasitic series resistance (source plus drain) per micron of MOSFET width. These values include all components such as accumulation layer, spreading resistance, sheet resistance, and contacts. It is assumed that there is 15% improvement per each node cycle (every 2 years or 3 years).

# 4.2.7. Increasing drive per footprint

FinFET and lateral GAA devices enable a higher drive at unit footprint (by enabling drive in the third dimension) if device pitch can be aggressively scaled while increasing the fin height or number of stacked GAA devices [21][23]. This will then increase drive at unit footprint but bringing a trade-off between fringing capacitance between gate and contact, and series resistance. This trend in reducing the number of fins while balancing the drive with increased fin height is defined as fin depopulation strategy, which also simulataneously reduces the standard cell height, and therefore, the overall chip area.

# 4.2.8. Improving electrostatics

FinFET has better electrostatics integrity due to its tall narrow channel that is controlled by a gate from three-sides that allows relaxing the scaling requirements of fin thickness (i.e., body thickness) compared to UTBB FDSOI. In UTBB FDSOI electrostatic control could be done by using silicon (i.e., body) thickness and buried oxide (BOX) thickness where convergent scaling of both silicon thickness and BOX thickness enables electrostatics scaling (i.e., drain-induced barrier lowering (DIBL) <100 mV/V) down to Lgate beyond 10 nm. Thick buried oxide (Tbox) and thin Si (Tsi) scalings are typically kept at a compromise point between manufacturability and short-channel-effects control. Junction formation engineering, EOT scaling and density of interface traps (Dit) reduction are potential solutions to maintain the electrostatics control in the channel [24][25].

# 4.2.9. Improving device isolation

Besides the channel leakage induced by electrostatics, there are potentially other leakage sources such as sub-fin leakage or punchthrough current. This leakage current flows through the bottom part of the fin from source to drain. This gets

more problematic in Ge channels because of low effective mass of Ge. Ground plane doping and quantum well below the channel would potentially solve this leakage problem; therefore improving the electrostatics [26].

# 4.2.10. Reducing process and material variations

Reducing variability would further allow supply voltage (Vdd) scaling. Controlling channel length and channel thickness are important to maintain the electrostatics in the channel. This would require, for example, controlling the profile of the fin and lithography processes to reduce the CD uniformity (CDU), line width roughness (LWR), and line edge roughness (LER). Dopant-free channel and low-variability work-function metals would reduce the variations in the threshold voltage. With the introduction of high-mobility materials, gate stack passivation is needed to reduce the interface-related variations as well as maintaining the electrostatics and mobility.

# 4.2.11. Beyond CMOS for application-specific functions and architectures